# INTERNATIONAL STANDARD

ISO 17987-4

First edition 2016-09-01

# Road vehicles — Local Interconnect Network (LIN) —

Part 4: Electrical physical layer (EPL) specification 12 V/24 V

Véhicules routiers — Réseau Internet local (LIN) — Partie 4: Spécification de la couche électrique physique (EPL) 12V/24V

#### **COPYRIGHT PROTECTED DOCUMENT**

© ISO 2016, Published in Switzerland

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized otherwise in any form or by any means, electronic or mechanical, including photocopying, or posting on the internet or an intranet, without prior written permission. Permission can be requested from either ISO at the address below or ISO's member body in the country of the requester.

ISO copyright office Ch. de Blandonnet 8 • CP 401 CH-1214 Vernier, Geneva, Switzerland Tel. +41 22 749 01 11 Fax +41 22 749 09 47 copyright@iso.org www.iso.org

| Co                        | ntent    | ts                                                          | Page               |  |  |

|---------------------------|----------|-------------------------------------------------------------|--------------------|--|--|

| Fore                      | eword    |                                                             | iv                 |  |  |

| Foreword  Introduction  1 |          |                                                             |                    |  |  |

| 1                         | Scop     | ne                                                          | 1                  |  |  |

|                           | -        |                                                             |                    |  |  |

|                           |          |                                                             |                    |  |  |

| 3                         |          |                                                             |                    |  |  |

|                           |          |                                                             |                    |  |  |

|                           |          | · · ·                                                       |                    |  |  |

|                           |          |                                                             |                    |  |  |

| 4                         | Conv     | ventions                                                    | 6                  |  |  |

| 5                         | Elect    | trical physical layer requirements                          | 6                  |  |  |

|                           | 5.1      | Bit rate deviation                                          | 6                  |  |  |

|                           |          | 5.1.1 12 V LIN systems: Parameters                          | 6                  |  |  |

|                           |          | J                                                           |                    |  |  |

|                           | 5.2      |                                                             |                    |  |  |

|                           |          |                                                             |                    |  |  |

|                           |          | J 1                                                         |                    |  |  |

|                           |          | 1 0                                                         |                    |  |  |

|                           | 5.3      |                                                             |                    |  |  |

|                           |          |                                                             |                    |  |  |

|                           |          |                                                             |                    |  |  |

|                           |          |                                                             |                    |  |  |

|                           |          |                                                             |                    |  |  |

|                           |          |                                                             |                    |  |  |

|                           |          |                                                             |                    |  |  |

|                           |          | 5.3.7 12 V LIN systems, performance in non-operation supply | y voltage range 21 |  |  |

|                           |          | 5.3.9 Performance during fault modes                        | y voitage range21  |  |  |

|                           |          | 5.3.10 ESD/EMI compliance                                   |                    |  |  |

| Ann                       | ex A (in | nformative) LIN peripheral interface design considerations  |                    |  |  |

| Bibl                      | iograph  | hy                                                          | 27                 |  |  |

#### **Foreword**

ISO (the International Organization for Standardization) is a worldwide federation of national standards bodies (ISO member bodies). The work of preparing International Standards is normally carried out through ISO technical committees. Each member body interested in a subject for which a technical committee has been established has the right to be represented on that committee. International organizations, governmental and non-governmental, in liaison with ISO, also take part in the work. ISO collaborates closely with the International Electrotechnical Commission (IEC) on all matters of electrotechnical standardization.

The procedures used to develop this document and those intended for its further maintenance are described in the ISO/IEC Directives, Part 1. In particular the different approval criteria needed for the different types of ISO documents should be noted. This document was drafted in accordance with the editorial rules of the ISO/IEC Directives, Part 2 (see <a href="https://www.iso.org/directives">www.iso.org/directives</a>).

Attention is drawn to the possibility that some of the elements of this document may be the subject of patent rights. ISO shall not be held responsible for identifying any or all such patent rights. Details of any patent rights identified during the development of the document will be in the Introduction and/or on the ISO list of patent declarations received (see <a href="https://www.iso.org/patents">www.iso.org/patents</a>).

Any trade name used in this document is information given for the convenience of users and does not constitute an endorsement.

For an explanation on the meaning of ISO specific terms and expressions related to conformity assessment, as well as information about ISO's adherence to the World Trade Organization (WTO) principles in the Technical Barriers to Trade (TBT) see the following URL: <a href="www.iso.org/iso/foreword.html">www.iso.org/iso/foreword.html</a>.

The committee responsible for this document is ISO/TC 22, *Road vehicles*, Subcommittee SC 31, *Data communication*.

A list of all parts in the ISO 17987 series can be found on the ISO website.

#### Introduction

ISO 17987 (all parts) specifies the use cases, the communication protocol and physical layer requirements of an in-vehicle communication network called Local Interconnect Network (LIN).

The LIN protocol as proposed is an automotive focused low speed universal asynchronous receiver transmitter (UART) based network. Some of the key characteristics of the LIN protocol are signal-based communication, schedule table based frame transfer, master/slave communication with error detection, node configuration and diagnostic service transportation.

The LIN protocol is for low-cost automotive control applications, for example, door module and air condition systems. It serves as a communication infrastructure for low-speed control applications in vehicles by providing:

- signal-based communication to exchange information between applications in different nodes;

- bit rate support from 1 kbit/s to 20 kbit/s;

- deterministic schedule table-based frame communication;

- network management that wakes up and puts the LIN cluster into sleep state in a controlled manner;

- status management that provides error handling and error signalling;

- transport layer that allows large amount of data to be transported (such as diagnostic services);

- specification of how to handle diagnostic services;

- electrical physical layer specifications;

- node description language describing properties of slave nodes;

- network description file describing behaviour of communication;

- application programmer's interface.

ISO 17987 (all parts) is based on the open systems interconnection (OSI) Basic Reference Model as specified in ISO/IEC 7498-1 which structures communication systems into seven layers.

The OSI model structures data communication into seven layers called (top down) *application layer* (layer 7), *presentation layer*, *session layer*, *transport layer*, *network layer*, *data link layer* and *physical layer* (layer 1). A subset of these layers is used in ISO 17987 (all parts).

ISO 17987 (all parts) distinguishes between the services provided by a layer to the layer above it and the protocol used by the layer to send a message between the peer entities of that layer. The reason for this distinction is to make the services, especially the application layer services and the transport layer services, reusable also for other types of networks than LIN. In this way, the protocol is hidden from the service user and it is possible to change the protocol if special system requirements demand it.

ISO 17987 (all parts) provides all documents and references required to support the implementation of the requirements related to the following.

- ISO 17987-1: This part provides an overview of the ISO 17987 (all parts) and structure along with the use case definitions and a common set of resources (definitions, references) for use by all subsequent parts.

- ISO 17987-2: This part specifies the requirements related to the transport protocol and the network layer requirements to transport the PDU of a message between LIN nodes.

- ISO 17987-3: This part specifies the requirements for implementations of the LIN protocol on the logical level of abstraction. Hardware-related properties are hidden in the defined constraints.

- ISO 17987-4: This part specifies the requirements for implementations of active hardware components which are necessary to interconnect the protocol implementation.

- ISO/TR 17987-5: This part specifies the LIN application programmers interface (API) and the node configuration and identification services. The node configuration and identification services are specified in the API and define how a slave node is configured and how a slave node uses the identification service.

- ISO 17987-6: This part specifies tests to check the conformance of the LIN protocol implementation according to ISO 17987-2 and ISO 17987-3. This comprises tests for the data link layer, the network layer and the transport layer.

- ISO 17987-7: This part specifies tests to check the conformance of the LIN electrical physical layer implementation (logical level of abstraction) according to this document.

# Road vehicles — Local Interconnect Network (LIN) —

#### Part 4:

## Electrical physical layer (EPL) specification 12 V/24 V

#### 1 Scope

This document specifies the 12 V and 24 V electrical physical layers (EPL) of the LIN communications system.

The electrical physical layer for LIN is designed for low-cost networks with bit rates up to 20 kbit/s to connect automotive electronic control units (ECUs). The medium that is used is a single wire for each receiver and transmitter with reference to ground.

This document includes the definition of electrical characteristics of the transmission itself and also the documentation of basic functionality for bus driver devices.

All parameters in this document are defined for the ambient temperature range from -40 °C to 125 °C.

#### 2 Normative references

The following documents are referred to in the text in such a way that some or all of their content constitutes requirements of this document. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

IEC 61000-4-2, Electromagnetic compatibility (EMC) — Part 4-2: Testing and measurement techniques — Electrostatic discharge immunity test

#### 3 Terms, definitions, symbols and abbreviated terms

#### 3.1 Terms and definitions

For the purposes of this document, the following terms and definitions apply.

ISO and IEC maintain terminological databases for use in standardization at the following addresses:

- IEC Electropedia: available at <a href="http://www.electropedia.org/">http://www.electropedia.org/</a>

- ISO Online browsing platform: available at <a href="http://www.iso.org/obp">http://www.iso.org/obp</a>

#### 3.1.1

#### BR\_Range\_20K

LIN systems which operate at speeds up to 20 kbit/s

#### 3.1.2

#### BR\_Range\_20K 12 V

12 V LIN systems which operate at speeds up to 20 kbit/s

#### 3.1.3

#### BR\_Range\_20K 24 V

24 V LIN systems which operate at speeds up to 20 kbit/s

#### 3.1.4

#### BR\_Range\_10K

LIN systems which operate at speeds up to 10 417 kbits/s

#### 3.1.5

#### BR\_Range\_10K 12 V

12 V LIN systems which operate at speeds up to 10 417 kbits/s

#### 3.1.6

#### BR\_Range\_10K 24 V

24 V LIN systems which operate at speeds up to 10 417 kbit/s

#### 3.2 Symbols

% percentage

μs microsecond

C'<sub>LINE</sub> line capacitance

C<sub>BUS</sub> total bus capacitance

C<sub>MASTER</sub> capacitance of master node

C<sub>RXD</sub> RXD capacitance (LIN receiver, RXD capacitive load condition)

C<sub>SLAVE</sub> capacitance of slave node

d<sup>2</sup>V/dt<sup>2</sup> second derivative of voltage (Volt<sup>2</sup> per second<sup>2</sup>)

di/dt instantaneous rate of current change (amps per second)

D<sub>ser\_int</sub> serial internal diode at transceiver IC

D<sub>ser master</sub> serial master diode

F<sub>TOL\_RES\_MASTER</sub> master bit rate deviation from nominal bit rate

F<sub>TOL\_RES\_MASTER\_A</sub> master bit rate deviation from nominal bit rate in BR\_Range\_20K systems

$F_{TOL\_RES\_MASTER\_B} \qquad \quad \text{master bit rate deviation from nominal bit rate in BR\_Range\_10K systems}$

$F_{TOL\_RES\_SLAVE}$  slave bit rate deviation from nominal bit rate

F<sub>TOL\_RES\_SLAVE\_A</sub> slave bit rate deviation from nominal bit rate in BR\_Range\_20K systems

F<sub>TOL\_RES\_SLAVE\_B</sub> slave bit rate deviation from nominal bit rate in BR\_Range\_10K systems

$F_{TOL\_RES\_SLAVE\_1}$  slave node 1 bit rate deviation from nominal bit rate

$F_{TOL\_RES\_SLAVE\_2}$  slave node 2 bit rate deviation from nominal bit rate

$F_{TOL\_SLAVE\_to\_SLAVE}$  slave to slave bit rate deviation

$F_{TOL\_SYNCH}$  slave node bit rate deviation from master node bit rate after synchronization

F<sub>TOL</sub> SYNCH A slave node bit rate deviation from master node bit rate after synchronization

in BR\_Range\_20K systems

$F_{TOL\_SYNCH\_B}$  slave node bit rate deviation from master node bit rate after synchronization

in BR\_Range\_10K systems

$F_{TOL\_SYNCH\_1}$  slave node 1 bit rate deviation from master node bit rate after synchronization

F<sub>TOL\_SYNCH\_2</sub> slave node 2 bit rate deviation from master node bit rate after synchronization

$F_{TOL\_UNSYNCH}$  slave node bit rate deviation from nominal bit rate before synchronization

F<sub>TOL\_UNSYNCH\_A</sub> slave node bit rate deviation from nominal bit rate before synchronization in

BR\_Range\_20K systems

$F_{TOL\_UNSYNCH\_B}$  slave node bit rate deviation from nominal bit rate before synchronization in

BR\_Range\_10K systems

I<sub>BUS</sub> current into the ECU bus line

$I_{BUS\ LIM}$  current limitation for driver dominant state driver on  $V_{BUS} = V_{BAT\ max}$  into

ECU bus line

$I_{BUS\ NO\ BAT}$  current at ECU bus line when  $V_{BAT}$  is disconnected

$I_{BUS\_NO\_GND}$  current at ECU bus line when  $V_{GND\_ECU}$  is disconnected

I<sub>BUS\_PAS\_dom</sub> current at ECU bus line when driver off (passive) at dominant LIN bus level

I<sub>BUS\_PAS\_rec</sub> current at ECU bus line when driver off (passive) at recessive LIN bus level

GND<sub>Device</sub> GND of ECU

$k\Omega$  kilo ohm

kbit/s kilo bit per second

LEN<sub>BUS</sub> total length of LIN bus line

LIN<sub>Bus</sub> LIN network

ms millisecond

nF nano farad

pF pico farad

pF/m pico farad per meter (line capacitance)

R<sub>BUS</sub> total bus-resistor including all slave and master resistors

$R_{BUS} = R_{MASTER} || R_{SLAVE\_1} || R_{SLAVE\_2} ||$  to  $|| R_{SLAVE\_N} ||$

R<sub>MASTER</sub> master resistor

$R_{pull\_up}$  pull-up resistor

R<sub>SLAVE</sub> slave resistor

t<sub>BFS</sub> byte field synchronization time

t<sub>BIT</sub> basic bit times

t<sub>EBS</sub> earliest bit sample time

$t_{rx\_pd}$  propagation delay of receiver

$t_{rx\_sym}$  symmetry of receiver propagation delay rising edge propagation delay of

receiver

t<sub>LBS</sub> latest bit sample time

$t_{rx pdf(1)}$  propagation delay time of receiving node 1 at falling (recessive to dominant)

LIN bus edge

$t_{rx\_pdf(2)}$  propagation delay time of receiving node 2 at falling (recessive to dominant)

LIN bus edge

$t_{rx\_pdr(1)}$  propagation delay time of receiving node 1 at rising (dominant to recessive)

LIN bus edge

$t_{rx\_pdr(2)}$  propagation delay time of receiving node 2 at rising (dominant to recessive)

LIN bus edge

t<sub>SR</sub> sample window repetition time

$TH_{Dom(max)}$  max. dominant threshold of receiving node (Volt)

TH<sub>Dom(min)</sub> min. dominant threshold of receiving node (Volt)

TH<sub>Rec(max)</sub> max. recessive threshold of receiving node (Volt)

TH<sub>Rec(min)</sub> min. recessive threshold of receiving node (Volt)

V voltage

V<sub>ANODE</sub> voltage at the anode of the diode

V<sub>BAT</sub> voltage across the ECU supply connectors

V<sub>BATTERY</sub> voltage across the vehicle battery connectors

V<sub>BUS</sub> voltage on the LIN bus

V<sub>BUS CNT</sub> centre point of receiver threshold

V<sub>BUS rec</sub> receiver recessive voltage

$V_{\text{CATHODE}}$  voltage at the cathode of the diode

V<sub>GND\_BATTERY</sub> battery ground voltage

V<sub>GND ECU</sub> voltage on the local ECU ground connector with respect to vehicle battery

ground connector (V<sub>GND\_BATTERY</sub>)

V<sub>HYS</sub> receiver hysteresis voltage

V<sub>Rec</sub> recessive voltage

V<sub>SerDiode</sub> voltage drop at the serial diodes

V<sub>Shift BAT</sub> battery shift

V<sub>Shift Difference</sub> difference between battery shift and GND shift

V<sub>Shift\_GND</sub> GND shift

V<sub>SUP</sub> voltage at transceiver supply pins

$V_{SUP\_NON\_OP}$  voltage which the device is not destroyed; no guarantee of correct operation

$V_{th\_dom}$  receiver threshold voltage of the recessive to dominant LIN bus edge

$V_{th\_rec}$  receiver threshold voltage of the dominant to recessive LIN bus edge

$\Delta F/F_{MASTER}$  deviation of node bit rate from the master node bit rate

$\Delta F/F_{Nom}$  deviation from nominal bit rate

$\tau$  time constant

$\Omega$  ohm

#### 3.3 Abbreviated terms

AC alternate current

API application programmers interface

ASIC application specific integrated circuit

BFS byte field synchronization

DC direct current

EBS earliest bit sample

ECU electronic control unit

EMC electromagnetic compatibility

EMI electromagnetic interference

EPL electrical physical layer

ESD electrostatic discharge

EVT event

GND ground

LBS latest bit sample

Max. maximum

Min. minimum

OSI open systems interconnection

RC RC time constant  $\tau$  ( $\tau = C_{BUS} \times R_{BUS}$ )

RX Rx pin of the transceiver

RXD receive data

SR sample window repetition

TRX transceiver

Tx pin of the transceiver

TXD transmit data

Typ. typical

UART universal asynchronous receiver transmitter

#### 4 Conventions

ISO 17987 (all parts) and ISO 14229-7 are based on the conventions specified in the OSI Service Conventions (see ISO/IEC 10731) as they apply for physical layer, protocol, network and transport protocol and diagnostic services.

#### 5 Electrical physical layer requirements

#### 5.1 Bit rate deviation

The bit rate deviation of the LIN medium describes the bit rate deviation from a referenced bit rate. It is the sum of the following parameters:

- inaccuracy of setting the bit rate (systematic failure due to granularity of the configurable bit rate);

- clock deviation over temperature and supply voltage range;

- clock source stability of the slave node starting from the end of the sync byte field up to the end of the entire LIN frame (last sampled bit) when performing synchronization;

- bit time measurement failure of the slave node:

- clock source stability of the master node starting from the end of the sync byte field up to the end of the entire LIN frame (last transmitted bit).

On-chip clock may achieve a frequency deviation of better than  $\pm 14$  % with internal calibration. This bit rate deviation better than  $\pm 14$  % is sufficient to detect a break field in the message stream. The subsequent bit rate adaptation using the sync byte field ensures the proper reception and transmission of the message. The on-chip oscillator shall allow for accurate bite rate measurement and generation for the remainder of the message frame, taking into account effects of anything, which affects the bit rate, such as temperature and voltage drift during operation.

The bit rates on the LIN bus are specified in the range of 1 kbit/s to 20 kbit/s. The specific bit rate used on a LIN bus is defined as the nominal bit rate,  $F_{Nom}$ .

In case a non-LIN electrical physical layer (e.g. ISO 11898-1, ISO 11898-2) is used, the bit rate may have to be adjusted.

#### 5.1.1 12 V LIN systems: Parameters

Table 1 defines the bit rate deviation from nominal bit rate.

Table 1 — Bit rate deviation from nominal bit rate

| Number  | Bit rate deviation                                                                                                                                                        | Name                            | $\Delta F/F_{Nom}$ |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------|--|

| Param 1 | Master node (deviation from nominal bit rate)                                                                                                                             | F <sub>TOL_RES_</sub><br>MASTER | <±0,5 %            |  |

| Param 2 | Slave node without making use of synchronization (deviation from nominal bit rate)                                                                                        | F <sub>TOL_RES_SLAVE</sub>      | <±1,5 %            |  |

| Param 3 | Deviation of slave node bit rate from the nominal bit rate before synchronization; relevant for nodes making use of synchronization and direct break detection.           | F <sub>TOL_UNSYNCH</sub>        | <±14 %             |  |

|         | This parameter is microprocessor-based nodes with sync/break detection that is triggering the auto-bauding processing in software. It insures that the break is detected. |                                 |                    |  |

<u>Table 2</u> defines the slave node bit rate deviation from master node bit rate.

Table 2 — Slave node bit rate deviation from master node bit rate

| Number | Bit rate deviation                                                                                                                                                                                                                                  | Name                   | ΔF/F <sub>MASTER</sub> |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------|

|        | Deviation of slave node bit rate from the master node bit rate after synchronization; relevant for nodes making use of synchronization; any slave node shall stay within this deviation for all fields of a frame which follow the sync byte field. | F <sub>TOL_SYNCH</sub> | <±2 %                  |

<u>Table 3</u> defines the bit rate deviation for slave to slave communication.

Table 3 — Bit rate deviation for slave to slave communication

| Number  | Bit rate deviation                                                                                                                                                                                                   | Name                                | ΔF/F <sub>MASTER</sub> |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|------------------------|

| Param 5 | For communication between any two nodes (i.e. data stream from one slave to another slave), their bit rate shall not differ by more than $F_{TOL\_SLAVE\_to\_SLAVE}$ . The following condition shall be checked for: | F <sub>TOL_SLAVE_to_</sub><br>SLAVE | <±2 %                  |

|         | a)  FTOL_RES_SLAVE_1 - FTOL_RES_SLAVE_2  < FTOL_SLAVE_to_SLAVE;                                                                                                                                                      |                                     |                        |

|         | b)  F <sub>TOL_SYNCH_1</sub> - F <sub>TOL_SYNCH_2</sub>   < F <sub>TOL_SLAVE_to_SLAVE</sub> ;                                                                                                                        |                                     |                        |

|         | c)  (Ftol_res_master + Ftol_synch_1) - Ftol_res_slave_2                                                                                                                                                              |                                     |                        |

|         | < F <sub>TOL_SLAVE_to_SLAVE</sub> .                                                                                                                                                                                  |                                     |                        |

#### 5.1.2 24 V LIN systems: Parameters

The required accuracy is dependent on the used bit rate range. See <u>Table 15</u> and also ISO 17987-2.

<u>Table 4</u> defines the bit rate deviation from nominal bit rate in BR\_Range\_20K systems.

Table 4 — Bit rate deviation from nominal bit rate in BR\_Range\_20K systems

| Number   | BR_Range_20K bit rate deviation                                                                                                                                                       | Name                              | ΔF/F <sub>Nom</sub> |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------|

| Param 39 | master node (deviation from nominal bit rate. The nominal bit rate $F_{Nom}$ is defined in the LIN description file).                                                                 | F <sub>TOL_RES_</sub><br>MASTER_A | <±0,3 %             |

| Param 40 | slave node without making use of synchronization (deviation from nominal bit rate) For communication between any two nodes, their bit rate shall not differ by more than $\pm 0.6$ %. | FTOL_RES_SLAVE_A                  | <±0,3 %             |

| Param 41 | deviation of slave node bit rate from the nominal bit rate before synchronization; relevant for nodes making use of synchronization and direct break field detection.                 | FTOL_UNSYNCH_A                    | <±14 %              |

<u>Table 5</u> defines the bit rate deviation for slave nodes from master node in BR\_Range\_20K systems.

Table 5 — Bit rate deviation for slave nodes from master node in BR\_Range\_20K systems

| Number   | BR_Range_20K bit rate deviation                                                                                                                                                                                                                     | Name                    | ΔF/F <sub>MASTER</sub> |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------|

| Param 42 | Deviation of slave node bit rate from the master node bit rate after synchronization; relevant for nodes making use of synchronization; any slave node shall stay within this deviation for all fields of a frame which follow the sync byte field. | FTOL_SYNCH_A            | <±0,6 %                |

| Param 43 | For communication between any two nodes (i.e. data stream from one slave to another slave), their bit rate shall not differ by more than $F_{TOL\_SLAVE\_to\_SLAVE}$ . The following condition shall be checked for:                                |                         |                        |

|          | a)  F <sub>TOL_RES_SLAVE_1</sub> - F <sub>TOL_RES_SLAVE_2</sub>   < F <sub>TOL_SLAVE_to_SLAVE</sub> ;                                                                                                                                               | FTOL_SLAVE_to_<br>SLAVE | <±0,6 %                |

|          | b)  F <sub>TOL_SYNCH_1</sub> - F <sub>TOL_SYNCH_2</sub>   < F <sub>TOL_SLAVE_to_SLAVE</sub> ;                                                                                                                                                       |                         |                        |

|          | c)  (Ftol_res_master_a + Ftol_synch_1) - Ftol_res_slave_2                                                                                                                                                                                           |                         |                        |

|          | < F <sub>TOL_SLAVE_to_SLAVE</sub> .                                                                                                                                                                                                                 |                         |                        |

<u>Table 6</u> defines the Bit rate deviation from nominal bit rate in BR\_Range\_10K systems.

Table 6 — Bit rate deviation from nominal bit rate in BR\_Range\_10K systems

| Number   | BR_Range_10K bit rate deviation                                                                                                                                                  | Name                              | ΔF/F <sub>Nom</sub> |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------|

| Param 44 | master node (deviation from nominal bit rate. The nominal bit rate $F_{Nom}$ is defined in the LDF).                                                                             | F <sub>TOL_RES_</sub><br>master_b | <±0,5 %             |

| Param 45 | slave node without making use of synchronization (deviation from nominal bit rate) For communication between any two nodes, their bit rate shall not differ by more than ±2,0 %. | FTOL_RES_SLAVE_B                  | <±1,5 %             |

| Param 46 | deviation of slave node bit rate from the nominal bit rate before synchronization; relevant for nodes making use of synchronization and direct break field detection.            | F <sub>TOL_UNSYNCH_B</sub>        | <±14 %              |

<u>Table 7</u> defines the bit rate deviation for slave nodes from master node in BR\_Range\_10K systems.

| Number   | BR_Range_10K bit rate deviation                                                                                                                                                                                                                     | Name                     | ΔF/F <sub>MASTER</sub> |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------|

| Param 47 | Deviation of slave node bit rate from the master node bit rate after synchronization; relevant for nodes making use of synchronization; any slave node shall stay within this deviation for all fields of a frame which follow the sync byte field. | F <sub>TOL_SYNCH_B</sub> | <±2,0 %                |

| Param 48 | For communication between any two nodes (i.e. data stream from one slave to another slave), their bit rate shall not differ by more than $F_{TOL\_SLAVE\_to\_SLAVE}$ . The following condition shall be checked for:                                |                          |                        |

|          | a)  FTOL_RES_SLAVE_1 - FTOL_RES_SLAVE_2  < FTOL_SLAVE_to_SLAVE;<br>b)  FTOL_SYNCH_1 - FTOL_SYNCH_2  < FTOL_SLAVE_to_SLAVE:                                                                                                                          | FTOL_SLAVE_to_<br>SLAVE  | <±2,0 %                |

|          | c)  (FTOL_RES_MASTER_B + FTOL_SYNCH_1) - FTOL_RES_SLAVE_2   < FTOL_SLAVE_to_SLAVE.                                                                                                                                                                  |                          |                        |

Table 7 — Bit rate deviation for slave nodes from master node in BR\_Range\_10K systems

#### 5.2 Timing requirements

#### 5.2.1 Bit timing

If not otherwise stated, all bit times in this document use the bit timing of the master node as a reference.

#### 5.2.2 Synchronization procedure

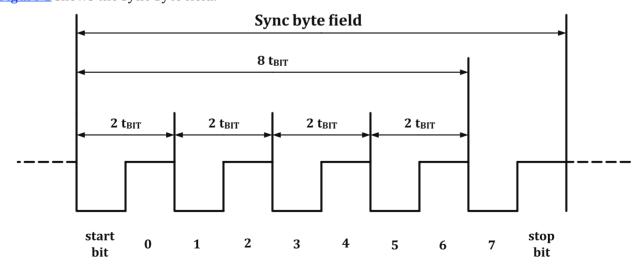

The sync byte field consists of the fixed data  $55_{16}$  inside a byte field. The synchronization procedure shall be based on time measurement between falling edges of the pattern. The falling edges are available in distances of 2 bit, 4 bit, 6 bit and 8 bit times which allows a simple calculation of the basic bit times,  $t_{\rm BIT}$ .

Figure 1 shows the sync byte field.

Figure 1 — Sync byte field

#### 5.2.3 Bit sample timing

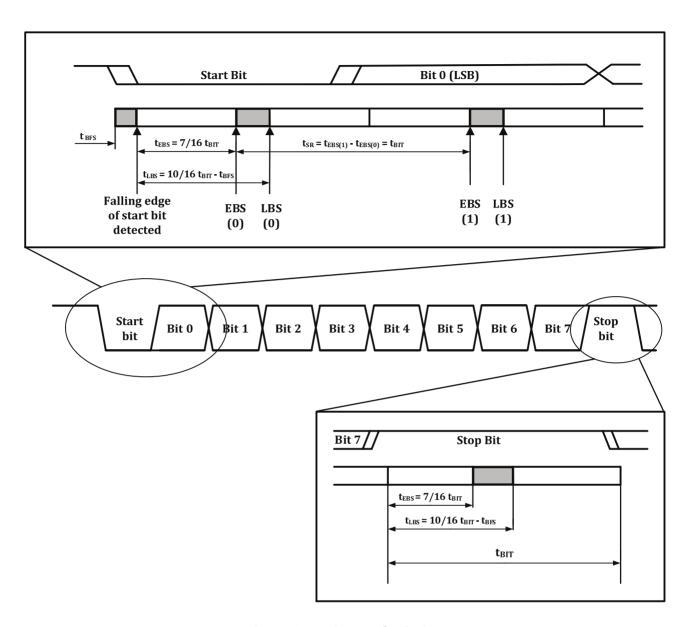

The bits of a byte field shall be sampled according to the following specification. In <u>Figure 2</u>, the bit sample timing of a byte field is illustrated. The corresponding timing parameters are listed in <u>Table 8</u>.

A byte field shall be synchronized at the falling edge of the start bit. The byte field synchronization (BFS) shall have an accuracy of  $t_{BFS}$ .

All methods for start bit sampling that met the byte field synchronization t<sub>BFS</sub> are allowed.

After the byte field synchronization on the falling edge of the start bit, the data bit itself shall be sampled within the window between the earliest bit sample (EBS) time,  $t_{EBS}$ , and the latest bit sample (LBS) time,  $t_{LBS}$ . The latest bit sample time,  $t_{LBS}$ , depends on the accuracy of the byte field synchronization,  $t_{BFS}$ . The dependency between  $t_{LBS}$  and  $t_{BFS}$  is given in Formula (1):

$$t_{LBS} = 10/16 t_{BIT} - t_{BFS}$$

(1)

The following bits shall be sampled within the same range as the sample window of the first data bit with the sample window repetition time,  $t_{SR}$ , respectively. The sample window repetition time,  $t_{SR}$ , is specified from the EBS of the former bit (n-1) to the EBS of the current bit; see Formula (2):

$$t_{SR} = t_{EBS(n)} - t_{EBS(n-1)} = t_{LBS(n)} - t_{LBS(n-1)} = t_{BIT}$$

(2)

#### Table 8 — Bit sample timing

| Number  | Parameter        | Min. | Тур. | Max. | Unit             | Comment/condition                                                                |

|---------|------------------|------|------|------|------------------|----------------------------------------------------------------------------------|

| Param 6 | t <sub>BFS</sub> | _    | 1/16 | 2/16 | t <sub>BIT</sub> | Value of accuracy of the byte field detection                                    |

| Param 7 | t <sub>EBS</sub> | 7/16 | _    | _    | t <sub>BIT</sub> | Earliest bit sample time, t <sub>EBS</sub> ≤ t <sub>LBS</sub>                    |

| Param 8 | t <sub>LBS</sub> | _    | _    | _    | t <sub>BIT</sub> | Latest bit sample [see <u>Formula (1)</u> ], t <sub>LBS</sub> ≥ t <sub>EBS</sub> |

For devices, which make use of more than one sample per bit, the bit sample majority shall determine the bit data. Furthermore, the sample majority shall be between the EBS and the LBS.

<u>Table 9</u> defines the bit sample timing example.

Table 9 — Bit sample timing example

| UART/SCI<br>cycles per t <sub>BIT</sub> | t <sub>BFS</sub>                               | t <sub>EBS</sub>                               | $t_{LBS}$ = 10/16 $t_{BIT}$ – $t_{BFS}$        |

|-----------------------------------------|------------------------------------------------|------------------------------------------------|------------------------------------------------|

| 16                                      | 1/16 t <sub>BIT</sub>                          | 7/16 t <sub>BIT</sub>                          | 9/16 t <sub>BIT</sub>                          |

| 8                                       | 1/8 t <sub>BIT</sub> (=2/16 t <sub>BIT</sub> ) | 4/8 t <sub>BIT</sub> (=8/16 t <sub>BIT</sub> ) | 4/8 t <sub>BIT</sub> (=8/16 t <sub>BIT</sub> ) |

Figure 2 shows the bit sample timing.

Figure 2 — Bit sample timing

#### 5.3 Line driver/receiver

#### 5.3.1 General configuration

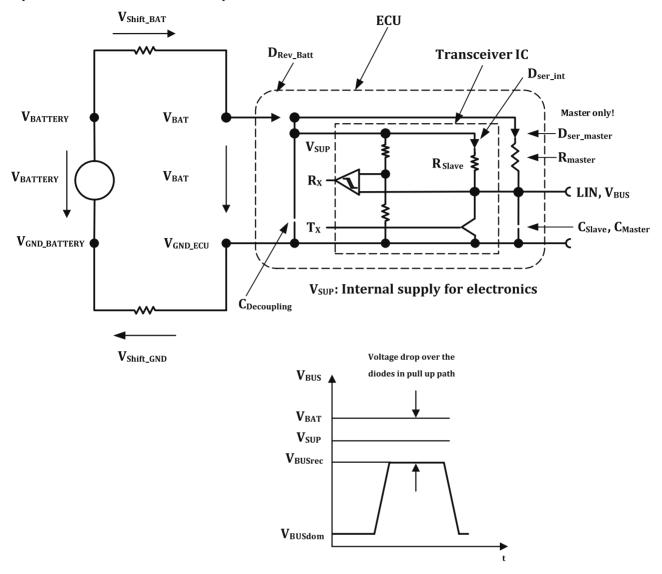

The bus line driver/receiver is based on ISO 9141. It consists of the bidirectional bus line LIN which is connected to the driver/receiver of every bus node, and is connected via a termination resistor and a diode to the positive transceiver supply voltage,  $V_{SUP}$  (see Figure 3). The diode is mandatory to prevent an uncontrolled power supply of the ECU from the bus in case of a "loss of battery".

It is important to note that the LIN specification refers to the voltages at the external electrical connections of the electronic control unit (ECU), and not to ECU internal voltages. In particular, the parasitic voltage drops of reverse polarity diodes shall be taken into account when designing a LIN transceiver circuit.

#### 5.3.2 Definition of supply voltages for the physical interface

$V_{BAT}$  denotes the supply voltage at the connector of the ECU. Electronic components within the unit may see an internal supply  $V_{SUP}$  being different from  $V_{BAT}$  (see Figure 3). This can be the result of protection

filter elements and dynamic voltage changes on the bus. This shall be taken into consideration for the implementation of semiconductor products for LIN.

Figure 3 — Illustration of the difference between external supply voltage,  $V_{BAT}$ , and the internal supply voltage,  $V_{SUP}$

#### 5.3.3 Signal specification

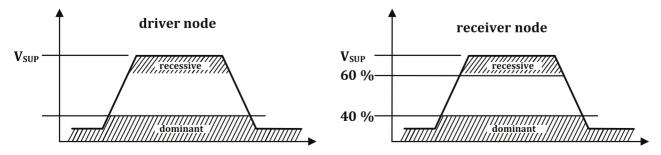

Figure 4 shows the voltage levels on the bus line.

Figure 4 — Voltage levels on the bus line

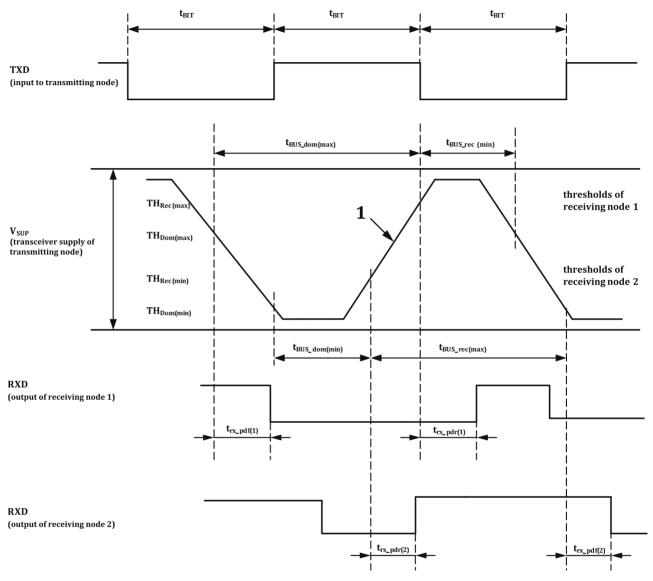

For a correct transmission and reception of a bit, it shall be asserted that the signal is available with the correct voltage level (dominant or recessive) at the bit sampling time of the receiver. Ground shifts as well as drops in the supply voltage shall be taken into consideration as well as symmetry failures in the propagation delay. Figure 5 shows the timing parameters that impact the behaviour of the LIN bus. The minimum and maximum values of the different parameters are listed in the following tables.

#### Key

1 LIN bus signal

Figure 5 — Definition of bus timing parameters

#### 5.3.4 12 V LIN systems: Electrical parameters

#### **5.3.4.1** DC parameters

The electrical DC parameters of the LIN electrical physical layer and the termination resistors are listed in <u>Tables 10</u> and <u>11</u>, respectively. Unless otherwise specified, all voltages are referenced to the local ECU ground and positive currents flow into the ECU.

In case of an integrated resistor/diode network, no parasitic current paths shall be formed between the bus line and the ECU-internal supply  $(V_{SUP})$ , for example by ESD elements.

<u>Table 10</u> defines the electrical DC parameters of the LIN electrical physical layer.

Table 10 — Electrical DC parameters of the LIN electrical physical layer

| Number   | Parameter                | Min.  | Тур. | Max.  | Unit             | Comment/condition                                                                                                     |

|----------|--------------------------|-------|------|-------|------------------|-----------------------------------------------------------------------------------------------------------------------|

| Param 9  | V <sub>BAT</sub> a       | 8     | _    | 18    | V                | ECU operating voltage range                                                                                           |

| Param 10 | V <sub>SUP</sub> b       | 7,0   | _    | 18    | V                | Supply voltage range                                                                                                  |

| Param 11 | V <sub>SUP_NON_OP</sub>  | -0,3  | _    | 40    | V                | Voltage range within which the device is not destroyed; no guarantee of correct operation                             |

| Param 12 | I <sub>BUS_LIM</sub> c   | 40    | _    | 200   | mA               | Current limitation for driver dominant state driver on $V_{BUS} = V_{BAT\_max}^{} d$                                  |

| Param 13 | I <sub>BUS_PAS_dom</sub> | -1    | _    | _     | mA               | Input leakage current at the receiver including pull-up resistor as specified in Table 11 Param 26 driver off         |

|          |                          |       |      |       |                  | $V_{BUS} = 0 V$                                                                                                       |

|          |                          |       |      |       |                  | V <sub>BAT</sub> = 12 V                                                                                               |

| Param 14 | I <sub>BUS_PAS_rec</sub> | _     | _    | 20    | μA               | Driver off                                                                                                            |

|          |                          |       |      |       |                  | 8 V < V <sub>BAT</sub> < 18 V                                                                                         |

|          |                          |       |      |       |                  | 8 V < V <sub>BUS</sub> < 18 V                                                                                         |

|          |                          |       |      |       |                  | $V_{BUS} \ge V_{BAT}$                                                                                                 |

| Param 15 | I <sub>BUS_NO_GND</sub>  | -1    | _    | 1     | mA               | Control unit disconnected from ground                                                                                 |

|          |                          |       |      |       |                  | $GND_{Device} = V_{SUP}$                                                                                              |

|          |                          |       |      |       |                  | 0 V < V <sub>BUS</sub> < 18 V                                                                                         |

|          |                          |       |      |       |                  | V <sub>BAT</sub> = 12 V                                                                                               |

|          |                          |       |      |       |                  | Loss of local ground shall not affect communication in the residual network.                                          |

| Param 16 | I <sub>BUS_NO_BAT</sub>  | _     | _    | 100   | μА               | V <sub>BAT</sub> disconnected                                                                                         |

|          |                          |       |      |       |                  | $V_{SUP} = GND$                                                                                                       |

|          |                          |       |      |       |                  | 0 < V <sub>BUS</sub> < 18 V                                                                                           |

|          |                          |       |      |       |                  | Node shall sustain the current that can flow under this condition. Bus shall remain operational under this condition. |

| Param 17 | V <sub>BUSdom</sub>      | _     | _    | 0,4   | $V_{SUP}$        | Receiver dominant state                                                                                               |

| Param 18 | V <sub>BUSrec</sub>      | 0,6   | _    |       | V <sub>SUP</sub> | Receiver recessive state                                                                                              |

| Param 19 | V <sub>BUS_CNT</sub>     | 0,475 | 0,5  | 0,525 | V <sub>SUP</sub> | $V_{BUS\_CNT} = (V_{th\_dom} + V_{th\_rec})/2^{e}$                                                                    |

| Param 20 | V <sub>HYS</sub>         | _     | _    | 0,175 | $V_{SUP}$        | $V_{HYS} = V_{th\_rec} - V_{th\_dom}$                                                                                 |

$<sup>^{</sup>a}$   $V_{BAT}$  denotes the supply voltage at the connector of the control unit and may be different from the internal supply,  $V_{SUP}$ , for electronic components (see <u>5.3.2</u>).

$<sup>^{\</sup>rm b}$  V<sub>SUP</sub> denotes the supply voltage at the transceiver inside the control unit and may be different from the external supply, V<sub>BAT</sub>, for control units (see <u>5.3.2</u>).

I<sub>BUS</sub>: current flowing into the node.

$<sup>^{</sup>m d}$  A transceiver shall be capable to sink at least 40 mA. The maximum current flowing into the node shall not exceed 200 mA under DC conditions to avoid possible damage.

$<sup>^{</sup>e}$   $V_{th\_dom}$ : receiver threshold of the recessive to dominant LIN bus edge.  $V_{th\_rec}$ : receiver threshold of the dominant to recessive LIN bus edge.

V<sub>ANODE</sub>: voltage at the anode of the diode. V<sub>CATHODE</sub>: voltage at the cathode of the diode.

g  $V_{BATTERY}$ : voltage across the vehicle battery connectors.  $V_{GND\_ECU}$ : voltage on the local ECU ground connector with respect to vehicle battery ground connector ( $V_{GND\_BATTERY}$ ).

h This constraint refers to duty cycle D1 and D2 only.

| I able I o recretifiatar | Table 10 | <i>(continue</i> | d) |

|--------------------------|----------|------------------|----|

|--------------------------|----------|------------------|----|

| Number   | Parameter                        | Min. | Тур. | Max.   | Unit             | Comment/condition                                                                                                                               |

|----------|----------------------------------|------|------|--------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Param 21 | V <sub>SerDiode</sub>            | 0,4  | 0,7  | 1,0    | V                | Voltage drop at the serial diodes                                                                                                               |

|          |                                  |      |      |        |                  | $D_{\text{ser\_master}}$ and $D_{\text{Rev\_Batt}}$ in pull-up path (Figure 3). $V_{\text{SerDiode}} = V_{\text{ANODE}} - V_{\text{CATHODE}}^f$ |

| Param 22 | V <sub>Shift_BAT</sub>           | 0    | _    | 11,5 % | V <sub>BAT</sub> | Battery shift                                                                                                                                   |

|          |                                  |      |      |        |                  | $V_{Shift\_BAT} = V_{BATTERY} - V_{Shift\_GND} - V_{BAT}^{g}$                                                                                   |

| Param 23 | V <sub>Shift_GND</sub>           | 0    | _    | 11,5 % | V <sub>BAT</sub> | GND shift                                                                                                                                       |

|          |                                  |      |      |        |                  | $V_{Shift\_GND} = V_{GND\_ECU} - V_{GND\_BATTERY}^{g}$                                                                                          |

| Param 24 | V <sub>Shift_Difference</sub> h  | 0    | _    | 8 %    | V <sub>BAT</sub> | Difference between battery shift and GND shift                                                                                                  |

|          |                                  |      |      |        |                  | $V_{Shift\_Difference} =  V_{Shift\_BAT} - V_{Shift\_GND} $                                                                                     |

| Param 82 | V <sub>BUS_MAX_</sub><br>RATINGS | -27  | _    | 40     | V                | The part should not suffer any damage.                                                                                                          |

$<sup>^{</sup>a}$   $V_{BAT}$  denotes the supply voltage at the connector of the control unit and may be different from the internal supply,  $V_{SUP}$ , for electronic components (see <u>5.3.2</u>).

<u>Table 11</u> defines the parameters of the pull-up resistors.

Table 11 — Parameters of the pull-up resistors

| Number   | Parameter           | Min. | Тур.  | Max.  | Unit | Comment/condition                             |

|----------|---------------------|------|-------|-------|------|-----------------------------------------------|

| Param 25 | R <sub>MASTER</sub> | 900  | 1 000 | 1 100 | Ω    | The serial diode is mandatory (see Figure 3). |

| Param 26 | R <sub>SLAVE</sub>  | 20   | 30    | 60    | kΩ   | The serial diode is mandatory.                |

#### 5.3.4.2 AC parameters

The electrical AC parameters of the LIN electrical physical layer are listed in <u>Tables 12</u>, <u>13</u> and <u>14</u>, with the parameters being defined in <u>Figure 5</u>. The electrical AC characteristics of the bus can be strongly affected by the line characteristics as shown in <u>5.3.3</u>. The time constant,  $\tau$ , (and thus the overall capacitance) of the bus (see <u>5.3.5</u>) shall be selected carefully in order to allow for a correct signal implementation under worst case conditions.

<u>Table 12</u> specifies the timing parameters for proper operation at 20 kbit/s.

$<sup>^{</sup>b}$   $V_{SUP}$  denotes the supply voltage at the transceiver inside the control unit and may be different from the external supply,  $V_{BAT}$ , for control units (see <u>5.3.2</u>).

c I<sub>BUS</sub>: current flowing into the node.

d A transceiver shall be capable to sink at least 40 mA. The maximum current flowing into the node shall not exceed 200 mA under DC conditions to avoid possible damage.

$<sup>^{</sup>e}$   $V_{th\_dom}$ : receiver threshold of the recessive to dominant LIN bus edge.  $V_{th\_rec}$ : receiver threshold of the dominant to recessive LIN bus edge.

f V<sub>ANODE</sub>: voltage at the anode of the diode. V<sub>CATHODE</sub>: voltage at the cathode of the diode.

$_{\rm SATTERY}$ : voltage across the vehicle battery connectors.  $V_{\rm GND\_ECU}$ : voltage on the local ECU ground connector with respect to vehicle battery ground connector ( $V_{\rm GND\_BATTERY}$ ).

This constraint refers to duty cycle D1 and D2 only.

Table 12 — Driver electrical AC parameters of the LIN electrical physical layer of BR\_Range\_20K 12 V LIN networks

| Number   | Parameter                                                                                                                | Min.  | Тур. | Max.  | Unit | Comment/condition                                  |  |  |  |  |  |

|----------|--------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|----------------------------------------------------|--|--|--|--|--|

|          | LIN driver, bus load conditions ( $C_{BUS}$ ; $R_{BUS}$ ): 1 nF; 1 k $\Omega$ /6,8 nF; 660 $\Omega$ /10 nF; 500 $\Omega$ |       |      |       |      |                                                    |  |  |  |  |  |

| Param 27 | D1                                                                                                                       | 0,396 | _    | _     | _    | $TH_{Rec(max)} = 0.744 \times V_{SUP};$            |  |  |  |  |  |

|          | (Duty Cycle 1)                                                                                                           |       |      |       |      | $TH_{Dom(max)} = 0.581 \times V_{SUP};$            |  |  |  |  |  |

|          |                                                                                                                          |       |      |       |      | $V_{SUP}$ = 7,0 V to 18 V; $t_{BIT}$ = 50 $\mu$ s; |  |  |  |  |  |

|          |                                                                                                                          |       |      |       |      | $D1 = t_{Bus\_rec(min)}/(2 \times t_{BIT})$        |  |  |  |  |  |

| Param 28 | D2                                                                                                                       | _     | _    | 0,581 | _    | $TH_{Rec(min)} = 0,422 \times V_{SUP};$            |  |  |  |  |  |

|          | (Duty Cycle 2)                                                                                                           |       |      |       |      | $TH_{Dom(min)} = 0.284 \times V_{SUP};$            |  |  |  |  |  |

|          |                                                                                                                          |       |      |       |      | $V_{SUP}$ = 7,6 V to 18 V; $t_{BIT}$ = 50 $\mu$ s; |  |  |  |  |  |

|          |                                                                                                                          |       |      |       |      | $D2 = t_{Bus\_rec(max)}/(2 \times t_{BIT})$        |  |  |  |  |  |

For improved EMC performance, exception is granted for speeds of 10 417 kbit/s or below. For details, see <u>Table 13</u>, which specifies the timing parameters for proper operation at 10 417 kbit/s.

Table 13 — Driver electrical AC parameters of the LIN electrical physical layer of BR\_Range\_10K 12 V LIN networks

| Number   | Parameter                                                                                                                             | Min.  | Тур. | Max.  | Unit | Comment/condition                                  |  |  |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|----------------------------------------------------|--|--|--|--|--|

|          | LIN driver, bus load conditions (C <sub>BUS</sub> ; R <sub>BUS</sub> ): 1 nF; 1 k $\Omega$ /6,8 nF; 660 $\Omega$ /10 nF; 500 $\Omega$ |       |      |       |      |                                                    |  |  |  |  |  |

| Param 29 | D3                                                                                                                                    | 0,417 | _    | _     | _    | $TH_{Rec(max)} = 0.778 \times V_{SUP};$            |  |  |  |  |  |

|          | (Duty Cycle 3)                                                                                                                        |       |      |       |      | $TH_{Dom(max)} = 0.616 \times V_{SUP}$             |  |  |  |  |  |

|          |                                                                                                                                       |       |      |       |      | $V_{SUP}$ = 7,0 V to 18 V; $t_{BIT}$ = 96 $\mu$ s; |  |  |  |  |  |

|          |                                                                                                                                       |       |      |       |      | $D3 = t_{Bus\_rec(min)}/(2 \times t_{BIT})$        |  |  |  |  |  |

| Param 30 | D4                                                                                                                                    | _     | _    | 0,590 | _    | $TH_{Rec(min)} = 0.389 \times V_{SUP};$            |  |  |  |  |  |

|          | (Duty Cycle 4)                                                                                                                        |       |      |       |      | $TH_{Dom(min)} = 0.251 \times V_{SUP};$            |  |  |  |  |  |

|          |                                                                                                                                       |       |      |       |      | $V_{SUP}$ = 7,6 V to 18 V; $t_{BIT}$ = 96 $\mu$ s; |  |  |  |  |  |

|          |                                                                                                                                       |       |      |       |      | $D4 = t_{Bus\_rec(max)}/(2 \times t_{BIT})$        |  |  |  |  |  |

Application specific implementations (ASICs) shall meet the parameters in <u>Table 12</u> and/or <u>Table 13</u>. If both sets of parameters are implemented, the proper mode shall be selected based on the bus bit rate.

Table 14 defines the receiver electrical AC parameters of the LIN electrical physical layer.

Table 14 — Receiver electrical AC parameters of the LIN electrical physical layer

| Number                                                                                                             | Parameter | Min. | Тур. | Max. | Unit | Comment/condition                                                               |  |  |

|--------------------------------------------------------------------------------------------------------------------|-----------|------|------|------|------|---------------------------------------------------------------------------------|--|--|

| LIN receiver, RXD load condition ( $C_{RXD}$ ): 20 pF; (if open drain behaviour: $R_{pull\_up}$ = 2,4 k $\Omega$ ) |           |      |      |      |      |                                                                                 |  |  |

| Param 31                                                                                                           | trx_pd    | _    | _    | 6    | μs   | propagation delay of receiver                                                   |  |  |

| Param 32                                                                                                           | trx_sym   | -2   | _    | 2    | μs   | symmetry of receiver propagation delay rising edge with respect to falling edge |  |  |

The EMC behaviour of the LIN bus depends on the signal shape represented by slew rate and other factors such as di/dt and  $d^2V/dt^2$ . The signal shape should be carefully selected in order to reduce emissions and allow for bit rates up to 20 kbit/s.

#### 5.3.5 24 V LIN systems: Electrical parameters

#### 5.3.5.1 DC parameters

The electrical DC parameters of the LIN electrical physical layer and the termination resistors are listed in <u>Tables 15</u> and <u>16</u>, respectively. Unless otherwise specified, all voltages are referenced to the local ECU ground and positive currents flow into the ECU.

In case of an integrated resistor/diode network, no parasitic current paths shall be formed between the bus line and the ECU-internal supply (V<sub>SUP</sub>), for example by ESD elements.

<u>Table 15</u> defines the electrical DC parameters of the LIN electrical physical layer.

Table 15 — Electrical DC parameters of the LIN electrical physical layer

| Number   | Parameter                                      | Min. | Тур. | Max. | Unit | Comment/condition                                                                                                                                  |

|----------|------------------------------------------------|------|------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Param 52 | V <sub>BAT_BR_Range_</sub><br>20K <sup>a</sup> | 16   | _    | 36   | V    | ECU operating voltage range in BR_<br>Range_20K 24 V LIN systems                                                                                   |

| Param 53 | V <sub>SUP_BR_</sub><br>Range_20K <sup>b</sup> | 15   | _    | 36   | V    | supply voltage range in BR_Range_20K 24 V LIN systems                                                                                              |

| Param 54 | V <sub>BAT_BR_Range_</sub><br>10K <sup>a</sup> | 8    | _    | 36   | V    | operating voltage range in BR_Range_10K<br>24 V LIN systems                                                                                        |

| Param 55 | V <sub>SUP_BR_</sub><br>Range_10K <sup>b</sup> | 7    | _    | 36   | V    | supply voltage range in BR_Range_10K 24 V<br>LIN systems                                                                                           |

| Param 56 | V <sub>SUP_NON_OP</sub>                        | -0,3 | _    | 58   | V    | voltage range within which the device is not destroyed; no guarantee of correct operation                                                          |

| Param 57 | I <sub>BUS_LIM</sub> c                         | 75   | _    | 300  | mA   | current limitation for driver dominant state driver on $V_{BUS} = V_{BAT\_max}^{} d$                                                               |

| Param 58 | I <sub>BUS_PAS_dom</sub>                       | -2   | _    | _    | mA   | input leakage current at the receiver including pull-up resistor as specified in Table 16 Param 71 driver off $V_{BUS}$ = 0 $V_{BAT}$ = 24 $V_{C}$ |

| Param 59 | I <sub>BUS_PAS_rec</sub>                       | _    | _    | 20   | μА   | driver off<br>8 V < V <sub>BAT</sub> < 36 V<br>8 V < V <sub>BUS</sub> < 36 V                                                                       |

|          |                                                |      |      |      |      | $V_{BUS} \ge V_{BAT}$                                                                                                                              |

$<sup>^{</sup>a}$   $V_{BAT}$  denotes the supply voltage at the connector of the control unit and may be different from the internal supply,  $V_{SUP}$ , for electronic components (see <u>5.3.2</u>).

b  $V_{SUP}$  denotes the supply voltage at the transceiver inside the control unit and may be different from the external supply  $V_{BAT}$  for control units (see 5.3.2).

c I<sub>BUS</sub>: current flowing into the node.

d A transceiver shall be capable to sink at least 75 mA. The maximum current flowing into the node shall not exceed 300 mA under DC conditions to avoid possible damage.

$<sup>^{</sup>e}$   $V_{th\_dom}$ : receiver threshold of the recessive to dominant LIN bus edge.  $V_{th\_rec}$ : receiver threshold of the dominant to recessive LIN bus edge.

$V_{ANODE}$ : voltage at the anode of the diode.  $V_{CATHODE}$ : voltage at the cathode of the diode.

$V_{BATTERY}$ : voltage across the vehicle battery connectors.  $V_{GND\_ECU}$ : voltage on the local ECU ground connector with respect to vehicle battery ground connector ( $V_{GND\_BATTERY}$ ).

h This constraint refers to duty cycle D1 and D2 only.

Table 15 (continued)

| Number   | Parameter                      | Min.  | Тур. | Max.   | Unit             | Comment/condition                                                                                                     |

|----------|--------------------------------|-------|------|--------|------------------|-----------------------------------------------------------------------------------------------------------------------|

| Param 60 | I <sub>BUS_NO_GND</sub>        | -2    | _    | 2      | mA               | control unit disconnected from ground                                                                                 |

|          |                                |       |      |        |                  | $GND_{Device} = V_{SUP}$                                                                                              |

|          |                                |       |      |        |                  | 0 V < V <sub>BUS</sub> < 36 V                                                                                         |

|          |                                |       |      |        |                  | V <sub>BAT</sub> = 24 V                                                                                               |

|          |                                |       |      |        |                  | loss of local ground shall not affect communication in the residual network.                                          |

| Param 61 | I <sub>BUS_NO_BAT</sub>        | _     | _    | 100    | μΑ               | V <sub>BAT</sub> disconnected                                                                                         |

|          |                                |       |      |        |                  | V <sub>SUP</sub> = GND                                                                                                |

|          |                                |       |      |        |                  | 0 < V <sub>BUS</sub> < 36 V                                                                                           |

|          |                                |       |      |        |                  | node shall sustain the current that can flow under this condition. Bus shall remain operational under this condition. |

| Param 62 | V <sub>BUSdom</sub>            | _     | _    | 0,4    | V <sub>SUP</sub> | receiver dominant state                                                                                               |

| Param 63 | V <sub>BUSrec</sub>            | 0,6   | _    | _      | $V_{SUP}$        | receiver recessive state                                                                                              |

| Param 64 | V <sub>BUS_CNT</sub>           | 0,475 | 0,5  | 0,525  | $V_{SUP}$        | $V_{BUS\_CNT} = (V_{th\_dom} + V_{th\_rec})/2^{e}$                                                                    |

| Param 65 | V <sub>HYS</sub>               | _     | _    | 0,175  | $V_{SUP}$        | $V_{HYS} = V_{th\_rec} - V_{th\_dom}$                                                                                 |

| Param 66 | $V_{SerDiode}$                 | 0,4   | 0,7  | 1,0    | V                | voltage drop at the serial diodes                                                                                     |

|          |                                |       |      |        |                  | $D_{ser\_master}$ and $D_{ser\_int}$ in pull-up path (Figure 3).                                                      |

|          |                                |       |      |        |                  | $V_{\text{SerDiode}} = V_{\text{ANODE}} - V_{\text{CATHODE}}^{\text{f}}$                                              |

| Param 67 | V <sub>Shift_BAT</sub>         | 0     | _    | 11,5 % | $V_{BAT}$        | battery-shift                                                                                                         |

|          |                                |       |      |        |                  | $V_{Shift\_BAT} = V_{BATTERY} - V_{Shift\_GND} - V_{BAT}g$                                                            |

| Param 68 | V <sub>Shift_GND</sub>         | 0     | _    | 11,5 % | $V_{BAT}$        | GND-shift                                                                                                             |

|          |                                |       |      |        |                  | $V_{Shift\_GND} = V_{GND\_ECU} - V_{GND\_BATTERY}^g$                                                                  |

| Param 69 | VShift_Difference <sup>h</sup> | 0     | _    | 8 %    | $V_{BAT}$        | difference between battery-shift and GND-shift                                                                        |

|          |                                |       |      |        |                  | $V_{Shift\_Difference} =  V_{Shift\_BAT} - V_{Shift\_GND} $                                                           |

| Param 83 | V <sub>BUS_MAX_RATINGS</sub>   | -6    | _    | 36     | V                | The part should not suffer any damage.                                                                                |

$<sup>^{</sup>a}$   $V_{BAT}$  denotes the supply voltage at the connector of the control unit and may be different from the internal supply,  $V_{SUP}$ , for electronic components (see 5.3.2).

<u>Table 16</u> defines the parameters of the pull-up resistors.

$<sup>^{\</sup>rm b}$  V<sub>SUP</sub> denotes the supply voltage at the transceiver inside the control unit and may be different from the external supply V<sub>BAT</sub> for control units (see <u>5.3.2</u>).

IBUS: current flowing into the node.

$<sup>^{</sup>m d}$  A transceiver shall be capable to sink at least 75 mA. The maximum current flowing into the node shall not exceed 300 mA under DC conditions to avoid possible damage.

$<sup>^</sup>e$   $V_{th\_dom}$ : receiver threshold of the recessive to dominant LIN bus edge.  $V_{th\_rec}$ : receiver threshold of the dominant to recessive LIN bus edge.

$V_{ANODE}$ : voltage at the anode of the diode.  $V_{CATHODE}$ : voltage at the cathode of the diode.

$v_{BATTERY}$ : voltage across the vehicle battery connectors.  $v_{GND\_ECU}$ : voltage on the local ECU ground connector with respect to vehicle battery ground connector ( $v_{GND\_BATTERY}$ ).

This constraint refers to duty cycle D1 and D2 only.

Table 16 — Parameters of the pull-up resistors

| Number   | Parameter           | Min. | Тур.  | Max.  | Unit | Comment/condition                             |

|----------|---------------------|------|-------|-------|------|-----------------------------------------------|

| Param 70 | R <sub>MASTER</sub> | 900  | 1 000 | 1 100 | Ω    | The serial diode is mandatory (see Figure 3). |

| Param 71 | R <sub>SLAVE</sub>  | 20   | 30    | 60    | kΩ   | The serial diode is mandatory.                |

#### 5.3.5.2 AC parameters

The electrical AC parameters of the LIN electrical physical layer are listed in <u>Tables 17</u>, <u>18</u> and <u>19</u> with the parameters being defined in <u>Figure 5</u>. The electrical AC characteristics of the bus can be strongly affected by the line characteristics as shown in <u>5.3.3</u>. The time constant  $\tau$  (and thus the overall capacitance) of the bus (see <u>5.3.5</u>) shall be selected carefully in order to allow for a correct signal implementation under worst case conditions.

<u>Table 17</u> specifies the timing parameters for proper operation at 20 kbit/s.

Table 17 — Driver electrical AC parameters of the LIN electrical physical layer of BR\_Range\_20K 24 V LIN networks

| Number   | Parameter                                                                                                                             | Min.  | Тур. | Max.  | Unit | Comment/condition                                   |  |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|-----------------------------------------------------|--|--|--|--|

|          | LIN driver, bus load conditions (C <sub>BUS</sub> ; R <sub>BUS</sub> ): 1 nF; 1 k $\Omega$ /6,8 nF; 660 $\Omega$ /10 nF; 500 $\Omega$ |       |      |       |      |                                                     |  |  |  |  |

| Param 72 | D1                                                                                                                                    | 0,330 | _    | _     | _    | $TH_{Rec(max)} = 0.710 \times V_{SUP};$             |  |  |  |  |

|          | (duty cycle 1)                                                                                                                        |       |      |       |      | $TH_{Dom(max)} = 0.554 \times V_{SUP};$             |  |  |  |  |

|          |                                                                                                                                       |       |      |       |      | $V_{SUP}$ = 15 V to 36 V; $t_{BIT}$ = 50 $\mu$ s;   |  |  |  |  |

|          |                                                                                                                                       |       |      |       |      | $D1 = t_{Bus\_rec(min)}/(2 \times t_{BIT})$         |  |  |  |  |

| Param 73 | D2                                                                                                                                    | _     | _    | 0,642 | _    | $TH_{Rec(min)} = 0.446 \times V_{SUP};$             |  |  |  |  |

|          | (duty cycle 2)                                                                                                                        |       |      |       |      | $TH_{Dom(min)} = 0.302 \times V_{SUP};$             |  |  |  |  |

|          |                                                                                                                                       |       |      |       |      | $V_{SUP}$ = 15,6 V to 36 V; $t_{BIT}$ = 50 $\mu$ s; |  |  |  |  |

|          |                                                                                                                                       |       |      |       |      | $D2 = t_{Bus\_rec(max)}/(2 \times t_{BIT})$         |  |  |  |  |

BR\_Range\_10K 24 V LIN systems operate at speeds of approximately 10 417 kbit/s or below. For details, see <u>Table 18</u>, which specifies the timing parameters for proper operation at 10 417 kbit/s.

Table 18 — Driver electrical AC parameters of the LIN electrical physical layer of BR\_Range\_10K 24 V LIN networks

| Number   | Parameter                                                                                                                             | Min.  | Тур. | Max.  | Unit | Comment/condition                                                       |  |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|-------------------------------------------------------------------------|--|--|--|--|

|          | LIN driver, bus load conditions (C <sub>BUS</sub> ; R <sub>BUS</sub> ): 1 nF; 1 k $\Omega$ /6,8 nF; 660 $\Omega$ /10 nF; 500 $\Omega$ |       |      |       |      |                                                                         |  |  |  |  |

| Param 74 | D3                                                                                                                                    | 0,386 | _    | _     | _    | $TH_{Rec(max)} = 0.744 \times V_{SUP};$                                 |  |  |  |  |