# INTERNATIONAL STANDARD

ISO 16845

First edition 2004-03-15

# Road vehicles — Controller area network (CAN) — Conformance test plan

Véhicules routiers — Gestionnaire de réseau de communication (CAN) — Plan d'essai de conformité

Reference number ISO 16845:2004(E)

### PDF disclaimer

This PDF file may contain embedded typefaces. In accordance with Adobe's licensing policy, this file may be printed or viewed but shall not be edited unless the typefaces which are embedded are licensed to and installed on the computer performing the editing. In downloading this file, parties accept therein the responsibility of not infringing Adobe's licensing policy. The ISO Central Secretariat accepts no liability in this area.

Adobe is a trademark of Adobe Systems Incorporated.

Details of the software products used to create this PDF file can be found in the General Info relative to the file; the PDF-creation parameters were optimized for printing. Every care has been taken to ensure that the file is suitable for use by ISO member bodies. In the unlikely event that a problem relating to it is found, please inform the Central Secretariat at the address given below.

## © ISO 2004

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from either ISO at the address below or ISO's member body in the country of the requester.

ISO copyright office Case postale 56 • CH-1211 Geneva 20 Tel. + 41 22 749 01 11 Fax + 41 22 749 09 47 E-mail copyright@iso.org Web www.iso.org

Published in Switzerland

| Coı        | Contents                                                                             |    |

|------------|--------------------------------------------------------------------------------------|----|

| Fore       | eword                                                                                | iv |

| 1          | Scope                                                                                | 1  |

| 2          | Normative references                                                                 |    |

| 3          | Terms and definitions                                                                | 1  |

| •          |                                                                                      |    |

| 4          | Abbreviated terms                                                                    |    |

| 5          | General                                                                              | 5  |

| 5.1<br>5.2 | Architecture of the test plan (TP)TP organization                                    |    |

| 5.3        | Hierarchical structure of tests                                                      |    |

| 6          | LT parameters                                                                        |    |

| 6.1        | Overview                                                                             |    |

| 6.2        | Description of parameters                                                            |    |

| 7          | Test type 1, received frame type                                                     | 10 |

| 7.1        | Test class 1, valid frame format                                                     | 10 |

| 7.2        | Test class 2, error detection                                                        |    |

| 7.3<br>7.4 | Test class 3, active error frame management  Test class 4, overload frame management |    |

| 7.4<br>7.5 | Test class 4, overload frame management                                              |    |

| 7.6        | Test class 6, error counter management                                               |    |

| 7.7        | Test class 7, bit timing class                                                       | 37 |

| 8          | Test type 2, transmitted frame                                                       | 42 |

| 8.1        | Test class 1, valid frame format                                                     | 42 |

| 8.2        | Test class 2, error detection                                                        |    |

| 8.3<br>8.4 | Test class 3, active error frame management  Test class 4, overload frame management |    |

| 8.5        | Test class 5, passive-error state and bus-off                                        |    |

| 8.6        | Test class 6, error counter management                                               |    |

| 8.7        | Test class 7, bit timing                                                             | 71 |

| 9          | Test type 3, bi-directional frame                                                    | 76 |

| 9.1        | Test class 1, valid frame format                                                     |    |

| 9.2        | Test class 2, error detection                                                        |    |

| 9.3<br>9.4 | Test class 3, active error frame management  Test class 4, overload frame management |    |

| 9.4<br>9.5 | Test class 5, passive-error state and bus-off                                        |    |

| 9.6        | Test class 6, error counter management                                               |    |

| 9.7        | Test class 7, bit timing                                                             | 77 |

ISO 16845:2004(E)

# **Foreword**

ISO (the International Organization for Standardization) is a worldwide federation of national standards bodies (ISO member bodies). The work of preparing International Standards is normally carried out through ISO technical committees. Each member body interested in a subject for which a technical committee has been established has the right to be represented on that committee. International organizations, governmental and non-governmental, in liaison with ISO, also take part in the work. ISO collaborates closely with the International Electrotechnical Commission (IEC) on all matters of electrotechnical standardization.

International Standards are drafted in accordance with the rules given in the ISO/IEC Directives, Part 2.

The main task of technical committees is to prepare International Standards. Draft International Standards adopted by the technical committees are circulated to the member bodies for voting. Publication as an International Standard requires approval by at least 75 % of the member bodies casting a vote.

Attention is drawn to the possibility that some of the elements of this document may be the subject of patent rights. ISO shall not be held responsible for identifying any or all such patent rights.

ISO 16845 was prepared by Technical Committee ISO/TC 22, Road vehicles, Subcommittee SC 3, Electrical and electronic equipment.

# Road vehicles — Controller area network (CAN) — Conformance test plan

# 1 Scope

This International Standard provides the methodology and abstract test suite necessary for checking the conformance of any CAN implementation of the CAN specified in ISO 11898-1.

## 2 Normative references

The following referenced documents are indispensable for the application of this document. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

ISO/IEC 9646-1:1994, Information technology — Open Systems interconnection — Conformance testing methodology and framework — Part 1: General concepts

ISO 11898-1:2003, Road vehicles — Controller area network (CAN) — Part 1: Data link layer and physical signalling

ISO 11898-2:2003, Road vehicles — Controller area network (CAN) — Part 2: High-speed medium access unit

## 3 Terms and definitions

For the purposes of this document, the following terms and definitions apply.

#### 3.1

## **ACK** delimiter

second bit of the ACK field

#### 3.2

## **ACK field**

last field before the EOF, used for message validation

#### 3.3

### acknowledgement error

error condition of the transmitter when it does not detect a dominant bit on the ACK slot

# 3.4

#### **ACK** slot

first bit of the ACK field

## 3.5

#### active error flag

first field of an active error frame

## 3.6

#### active error frame

error frame that starts with an active (dominant) error flag

# ISO 16845:2004(E)

## 3.7

#### active state

state of a node when it can transmit an active error frame

#### 3.8

# arbitration field

field starting after the SOF bit and finished with the RTR bit

#### 3.9

#### bit error

error condition encountered when the received bit does not correspond to the transmitted or expected bit

### 3.10

### conformance testing

application of the test plan to an IUT

#### 3.11

### **CRC** delimiter

last bit of the CRC field

### 3.12

## **CRC** error

error condition of a receiver when the received CRC code does not match the calculated CRC code

## 3.13

#### **CRC** field

field preceding the ACK field, consisting of the CRC code and the CRC delimiter

## 3.14

## end of frame

last field of a data or remote frame before the intermission field

#### 3.15

## error delimiter

second field of an error frame

## 3.16

## error flag

first field of an error frame

#### 3.17

#### error frame

formatted sequence of bits indicating an error condition

## 3.18

#### form error

error condition encountered in a fixed form field

## 3.19

#### idle state

CAN bus state where no frame is started after intermission field

## 3.20

## intermission field

field after EOF, error delimiter, or overload delimiter

# 3.21

## lower tester

tester that supervises the test suite

# 3.22

#### overload delimiter

second field of an overload frame

## 3.23

## overload flag

first field of an overload frame

#### 3.24

#### overload frame

formatted sequence of bits indicating an overload condition

#### 3.25

### passive error flag

first part of a passive error frame

#### 3.26

## passive state

state of the device when the value of the REC or the TEC has reached the error passive limit

### 3.27

## **REC** passive state

state of the device when the value of the REC has reached the error passive limit

## 3.28

## recessive state

state of the CAN bus when no CAN node drives a dominant value on the line

## 3.29

## stuff bit

bit inserted into the bit stream to increase the number of edges for synchronization purpose

#### 3.30

## stuff error

error condition encountered when an expected stuff bit is missing

#### 3.31

## suspend transmission field

waiting time added after the intermission field for an error passive transmitter, before it can start another transmission

## 3.32

# **TEC** passive state

state of the device when the value of the TEC has reached the error passive limit

#### 3.33

#### test case

specificly numbered and named test in the test suite

#### 3.34

#### test frame

CAN frame containing the test pattern specified

### 3.35

## test suite

check of the behaviour of the IUT for particular parameters of the CAN specification

# ISO 16845:2004(E)

## 3.36

### test type

specification of the direction of the test frames

**EXAMPLE** Specification of the behaviour of the IUT receiving and/or transmitting messages.

# 3.37

# time quantum

elementary time unit of the CAN bit time derived from the oscillator clock and the prescaler

#### 3.38

## upper tester

tester that acts as an user of the IUT

# **Abbreviated terms**

**ACK** Acknowledgement

**BRP** Bit rate prescaler

CAN Controller area network

**CRC** Cyclic redundancy check

**CTRL** Control

DLC Data length code

**EOF** End of frame

DIE Identifier extension bit

**IDEN CAN** identifier

**IPT** Information processing time

IUT Implementation under test

LLC Logical link control

LME Layer management entity

LT Lower tester

MAC Medium access control

MDI Medium dependent interface

NDATA Network data

NTQ Number of Time Quanta

PCO Point of control and observation PLS Physical layer signalling

PMA Physical medium attachment

REC Receive error counter

RTR Remote transmission request

RX Receiver signal

SJW Re-Synchronization jump width

SLIO Serial linked input/output

SOF Start of frame

SRR Substitute remote request

TEC Transmit error counter

TP Test plan

TQ Time quantum

TSYS System clock time (of the IUT)

UT Upper tester

## 5 General

# 5.1 Architecture of the test plan (TP)

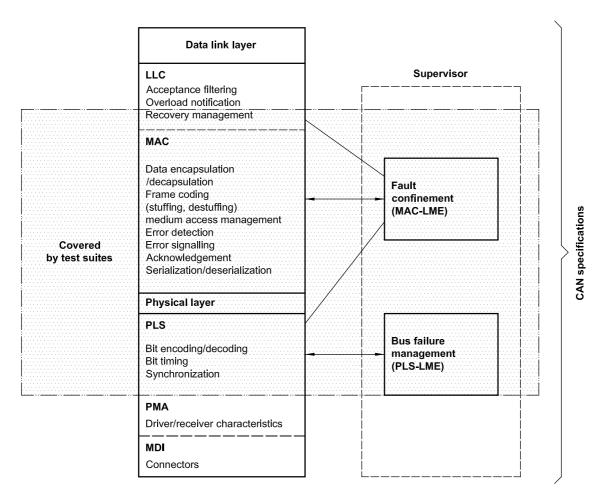

The architecture of the TP plan is as shown in Figure 1.

The TP is a specific application of ISO 9646-1 and is restricted to the single party testing mode. Since the upper service boundary of a CAN implementation is not standardized and in some cases may not be observed and controlled, because of an application specific behaviour embedded in this implementation, (e.g. CAN SLIO), the TP shall rely either on the coordinated test method or the remote test method.

Depending on the test method applied, the TP shall involve up to three test functions:

- an LT operating in way similar to the CAN IUT, running test suite and granting test verdict;

- an UT acting as user of the IUT (IUT-dependent);

- a test management protocol between the IUT and the LT, consisting of test coordination procedures.

The last two functions are only applicable to the coordinated test procedure.

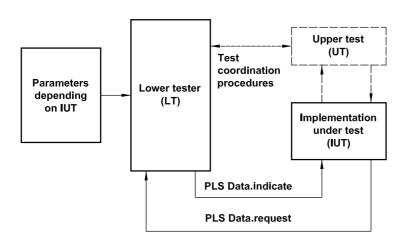

During testing, the LT may observe and control the standardized lower service boundary of the IUT (PCO) through the two service primitives provided by the PLS sub-layer, i.e. PLS Data.indicate and PLS Data.request, in most cases.

The environment that implements the TP is described in Figure 2.

Figure 1 — Architecture of the test plan

Figure 2 — CAN conformance TP environment

Using the network interface, the LT indicates to the UT the actions to be performed and the UT provides the LT with information concerning the internal behaviour of the IUT.

In order to allow the LT and the UT to communicate, it is necessary to specify some test coordination procedures between them. These procedures use the network to the exclusion of any other physical link. They are used to set up the UT and to verify the test results.

## 5.2 TP organization

## 5.2.1 General organization

The LT verifies if the IUT complies with the MAC, LLC, and PLS sub-layers of the CAN specification. The LT points out differences between what is expected according to the specification and the actual behaviour of the IUT.

The test suites of the TP are independent of one another. Each test suite may be used to check the behaviour of the IUT for a particular parameter of the CAN specification. Tests may be performed in sequence or separately.

Tests requiring variations of individual parameters (identifier, number of data, etc.) shall be repeated for each value of the parameter, these repetitions being known as elementary tests. A test including different elementary tests is valid only if all tests are passed.

## 5.2.2 Test organization

## 5.2.2.1 Elementary tests

## 5.2.2.1.1 Description

Each elementary test shall consist of three states:

|   | sei-up,       |

|---|---------------|

| _ | test;         |

|   | verification. |

At the PCO, these states involve interchanges of valid sequences of PLS service primitives [CAN frame(s)] or invalid sequences of PLS primitives (invalid CAN frames or noise).

Before the first elementary test is started the IUT shall be initialized into the default state.

## 5.2.2.1.2 Set-up state

The set-up state is the state the IUT shall be in before entering the test state.

## 5.2.2.1.3 Test state

The test state is the part of the elementary test in which the parameter or protocol feature is checked. This state needs one or several interchanges of frames, called test frames.

#### 5.2.2.1.4 Verification state

The verification state is made up of the data-reading frames, which verify that the data have been handled in accordance with the CAN specification.

For tests belonging to Classes 1 to 6 according to 5.3.3, the LT shall be able to detect the correct value of the bit.

For bit timing tests (Class 7 according to 5.3.3), the LT shall be able to detect a faulty synchronization of one time quantum.

#### 5.2.2.2 Default state

The default state is characterized by the following default values:

- both REC and TEC shall be equal to 0;

- no pending transmission shall be present;

## ISO 16845:2004(E)

- IUT shall be in idle state;

- PLS data.indicate and PLS data.request shall be recessive.

After the end of each elementary test, the default state shall be applied.

#### Hierarchical structure of tests

#### 5.3.1 Overview

The tests are grouped in categories in order to aid planning, development, understanding or execution of each test. Three levels of categories are specified test types, test classes and test cases.

## 5.3.2 Test types

Test types specify the direction of the frames. There are three types:

- Type 1, received frame, includes all tests evaluating the behaviour of the IUT for data frames and remote frames received by the IUT;

- Type 2, transmitted frame, includes all tests evaluating the behaviour of the IUT for data frames and remote frames transmitted by the IUT;

- Type 3, bi-directional frame, includes all tests with data frames or remote frames both received and transmitted by the IUT.

#### 5.3.3 Test classes

Each of the three test types given in 5.3.2 is divided into seven classes, grouping tests:

- Class 1, valid frame format, includes the tests involving only error free data or remote frames;

- Class 2, error detection, includes the tests that corrupt data or remote frames, which are used to check correct error detection by the IUT;

- Class 3, active error frame management, includes the tests verifying the IUT correct management of error-free and of corrupted active error frames;

- Class 4, overload frame management, includes the tests verifying the IUT correct management of error-free and of corrupted overload frames;

- Class 5, passive error state and bus-off, includes the tests verifying the IUT behaviour during passive error state and bus-off state:

- Class 6, error counter management, includes the tests verifying the correct management of the TEC and REC by the IUT in both active and passive error state;

- Class 7, bit timing, includes the tests verifying the correct management of bit timing by the IUT, and shall be applied only to those components performing recessive to dominant edge synchronization — if the dominant to recessive edge synchronization exists, it shall be disabled.

# 5.3.4 Test cases

Each and every basic entry of the test list is intended for checking a particular parameter of the harmonized CAN specification in the IUT.

Each test case is specified by a number and a particular name in order to differentiate the test cases and to easily summarize the goal of the test case. Some test cases may be subdivided into elementary tests that are repetitions of the test case for several values of the parameter tested.

# 6 LT parameters

### 6.1 Overview

The CAN specification allows several IUT implementations. Consequently, the LT shall be provided with parameters in order to indicate which kind of IUT is to be tested. These parameters are classified in two categories:

- communication parameters, specifying which tests can be executed for the IUT, and which test method shall be applied;

- application parameters, which specifies the features of the frames used for each test case selected according to the previous parameters.

NOTE LT applies to IUT performing only recessive to dominant edge synchronization and operating in single sampling mode.

# 6.2 Description of parameters

## 6.2.1 Communication parameters

## 6.2.1.1 Categories of communication parameter

Communication parameters are subdivided in three categories: implementation, timing and NDATA parameters.

## 6.2.1.2 Implementation parameters

Implementation parameters dependant on the IUT shall be specified in order to allow the LT to fit on the IUT. These implementation parameters are as follows.

- a) CAN\_VERSION indicates the version implemented in the IUT and may take three values.

- A: IUT handes 11 bit identifiers.

- B: IUT handles 11 and 29 bit identifiers.

- BP: IUT handes 11 identifiers and tolerates 29 bit identifiers.

- b) **Open/specific**, which indicates whether the IUT is open regarding the application layers or includes a specific application, and may be of two types.

OPEN: open IUT allowing the test coordination procedure to be implemented in an UT.

These IUT shall be tested with the coordinated test method according to ISO 9646-1.

SPECIFIC: IUT that can be tested only with the help of a specific configuration procedure.

These IUT shall be tested with the remote test method according to ISO 9646-1.

## 6.2.1.3 Timing parameters

The LT also requires that some timing parameters be in accordance with the IUT and the UT characteristics. These parameters are as follows.

- a) Timeout indicates the minimum duration time for which the LT shall wait in order to respect the following three conditions.

- The UT shall have enough time to put the IUT into the set-up state.

## ISO 16845:2004(E)

- The IUT shall have enough time to transmit a response frame after a remote frame.

- The LT shall consider an optional additional waiting time after the end of the minimum bus-off recovery sequence before the IUT enters error active state again.

- b) TSYS indicates the duration of the IUT system clock (clock used as input of the prescaler).

- c) BRP indicates the value of the prescaler (the duration of a TQ is  $T_Q = TSYS \times BRP$ ).

- d) NTQ indicates the number of time quanta per bit.

- e) Phase\_Seg2 indicates the number of time quanta for the phase buffer segment 2.

- f) SJW indicates the number of time quanta for the re-synchronization jump width. In all tests, the resynchronization jump width shall be programmed to its full range, up to its maximum value which is the minimum of Phase Seq1 and 4 TQ.

- g) IPT indicates the information processing time.

- h) IUT delay time shall be considered for bit timing class tests. It indicates the time difference between the response of the IUT and the response of an ideal IUT (without internal delays) to an edge causing synchronization. The IUT delay time is the sum of the IUT input and output delay time periods, measured according to ISO 11898-2.

# 6.2.1.4 NDATA parameter, a set of DLC values which an IUT accepts for data exchange with higher layers.

## 6.2.2 Application parameters

Except for tests for which a particular profile of application parameters is specified by the TP, the content of the application parameters used during the test shall be chosen by the user.

# 7 Test type 1, received frame type

# 7.1 Test class 1, valid frame format

## 7.1.1 Identifier and number of data in standard format

# 7.1.1.1 Purpose and limits of test case

This test case is applicable to CAN VERSION  $\in$  {A, B, BP}.

It is used to verify the behaviour of the IUT when receiving a correct data frame with different identifiers and different numbers of data bytes in a standard format frame.

Tested identifiers:  $\in [000h, 7EFh] \cup [7F0h, 7FFh],$

Tested number of data bytes:  $\in [0, 8]$

#### 7.1.1.2 Test case organization

Test case organization shall be in accordance with Table 1.

Table 1 — Identifier and number of data in standard format — Test case organization

| State        | Description                                                                                     |  |

|--------------|-------------------------------------------------------------------------------------------------|--|

| Set-up       | No action required, the IUT is left in the default state.                                       |  |

| Test         | A single test frame is used for each elementary test.                                           |  |

|              | The IUT shall not generate any error flag during the test.                                      |  |

| Verification | The IUT shall acknowledge the test frame.                                                       |  |

|              | The data received by the IUT during the test state shall match the data sent in the test frame. |  |

## 7.1.2 Identifier and number of data in extended format — Test case 1

## 7.1.2.1 Purpose and limits of this test case

This test case is applicable to CAN\_VERSION  $\in$  {B}.

It is used to verify the behaviour of the IUT when receiving a correct data frame with different identifiers and different numbers of data bytes in a extended format frame.

Tested identifiers:  $\in$  [00000000, 1FFFFFFh]

Tested number of data bytes:  $\in [0, 8]$

## 7.1.2.2 Test case organization

Test case organization shall be as shown in Table 2.

Table 2 — Identifier and number of data in extended format — Test case 1 organization

| State        | Description                                                                                                                                                                                          |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Set-up       | No action required, the IUT is left in the default state.                                                                                                                                            |  |

| Test         | A single test frame is used for each elementary test.                                                                                                                                                |  |

| Verification | The IUT shall not generate any error flag during the test. The IUT shall acknowledge the test frame. The data received by the IUT during the test state shall match the data sent in the test frame. |  |

## 7.1.3 Identifier and number of data in extended format — Test case 2

## 7.1.3.1 Purpose and limits of this test case

This test is applicable to CAN\_VERSION  $\in$  {BP}.

It is used to verify the behaviour of the IUT when receiving a correct data frame with different identifiers and different numbers of data bytes in a extended format frame.

Tested identifiers: ∈ [00000000, 1FFFFFFh]

Tested number of data bytes:  $\in [0, 8]$

## 7.1.3.2 Test case organization

Test case organization shall be in accordance with Table 3.

--\*\*\*,.,-\*-\*,,\*,,\*,,\*,.\*---

Table 3 — Identifier and number of data in extended format — Test case 2 organization

| State                                                      | Description                                                                                          |  |

|------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--|

| Set-up                                                     | No action required, the IUT is left in the default state.                                            |  |

| Test A single test frame is used for each elementary test. |                                                                                                      |  |

| Verification                                               | The IUT shall not generate any error flag during the test. The IUT shall acknowledge the test frame. |  |

## 7.1.4 Acceptance of non-nominal r1, r0 combination in standard format

#### 7.1.4.1 Purpose and limits of this test case

This test is applicable to CAN\_VERSION  $\in$  {A}.

Its purpose is to verify that the IUT accepts the non-nominal value of «r1, r0» bits in a valid standard frame.

Three (3) values shall be tested, as given in Table 4.

Table 4 — Values of r1 and r0 bits

| r1 | r0 |

|----|----|

| 1  | 1  |

| 1  | 0  |

| 0  | 1  |

#### 7.1.4.2 **Test case organization**

Test case organization shall be in accordance with Table 5.

Table 5 — Acceptance of non-nominal r1, r0 combination in standard format — Test case organization

| State                                                                                                                                                                                                                | Description                                                         |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--|

| Set-up                                                                                                                                                                                                               | No action required, the IUT is left in the default state.           |  |

| Test                                                                                                                                                                                                                 | A single test frame is used for each of the three elementary tests. |  |

| The IUT shall not generate any error flag during the test.  Verification  The IUT shall acknowledge the test frame.  The data received by the IUT during the test state shall match the data sent in the test frame. |                                                                     |  |

## 7.1.5 Acceptance of non-nominal IDE, r0 combination in standard format

#### 7.1.5.1 Purpose and limits of test case

This test is applicable to CAN\_VERSION  $\in$  {B, BP}.

Its purpose is to verify that the IUT accepts the non-nominal value of the IDE and r0 bits in a valid standard frame.

One (1) value shall be tested as specified in Table 6.

Table 6 — Non-nominal IDE

| IDE | r0 |

|-----|----|

| 0   | 1  |

## 7.1.5.2 Test case organization

Test case organization shall be in accordance with Table 7.

Table 7 — Acceptance of non-nominal IDE, r0 combination in standard format —

Test case organization

| State        | Description                                                                                                                                                                                               |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Set-up       | No action required, the IUT is left in the default state.                                                                                                                                                 |  |

| Test         | A single test frame is used for the elementary test.                                                                                                                                                      |  |

| Verification | The IUT shall not generate any error flag in this test frame.  The IUT shall acknowledge the test frame.  The data received by the IUT during the test state shall match the data sent in the test frame. |  |

# 7.1.6 Acceptance of non-nominal values of SRR, r1, r0 in extended format — Test case 1

## 7.1.6.1 Purpose and limits of test case

This test is applicable to CAN\_VERSION  $\in$  {B}.

Its purpose is to verify that the IUT accepts the non-nominal values of the SRR, r1 and r0 bits in a valid extended frame.

Seven (7) values shall be tested, in accordance with Table 8.

Table 8 — Non-nominal values of the SRR, r1 and r0 bits

| SRR | r1 | r0 |

|-----|----|----|

| 1   | 1  | 1  |

| 1   | 1  | 0  |

| 1   | 0  | 1  |

| 0   | 1  | 1  |

| 0   | 1  | 0  |

| 0   | 0  | 1  |

| 0   | 0  | 0  |

# 7.1.6.2 Test case organization

Test case organization shall be in accordance with Table 9.

Table 9 — Acceptance of non-nominal values of SRR, r1, r0 in extended format —

Test case 1 organization

| State        | Description                                                                                     |  |

|--------------|-------------------------------------------------------------------------------------------------|--|

| Set-up       | No action required, the IUT is left in the default state.                                       |  |

| Test         | A single test frame is used for each of the seven elementary tests.                             |  |

|              | The IUT shall not generate any error flag during the test.                                      |  |

| Verification | The IUT shall acknowledge the test frame.                                                       |  |

|              | The data received by the IUT during the test state shall match the data sent in the test frame. |  |

# 7.1.7 Acceptance of non-nominal values of SRR, r1 and r0 in extended format — Test case 2

# 7.1.7.1 Purpose and limits of test case

This test is applicable to CAN\_VERSION  $\in$  {BP}.

Its purpose is to verify that the IUT accepts the non-nominal value of the SRR, r1 and r0 bits in a valid extended frame.

Seven (7) values to test shall be tested, in accordance with Table 10.

Table 10 — Non-nominal values of SRR, r1, r0 bits

| SRR | r1 | r0 |

|-----|----|----|

| 1   | 1  | 1  |

| 1   | 1  | 0  |

| 1   | 0  | 1  |

| 0   | 1  | 1  |

| 0   | 1  | 0  |

| 0   | 0  | 1  |

| 0   | 0  | 0  |

## 7.1.7.2 Test case organization

Test case organization shall be in accordance with Table 11.

Table 11 — Acceptance of non-nominal values of SRR, r1 and r0 in extended format —

Test case 2 organization

| State        | Description                                                                                          |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------|--|--|--|

| Set-up       | No action required, the IUT is left in the default state.                                            |  |  |  |

| Test         | A single test frame is used for each of the 7 elementary tests.                                      |  |  |  |

| Verification | The IUT shall not generate any error flag during the test. The IUT shall acknowledge the test frame. |  |  |  |

# 7.1.8 DLC greater than 8

# 7.1.8.1 Purpose and limits of test case

This test is applicable to CAN VERSION  $\in$  {A, B, BP}.

It is used to verify the behaviour of the IUT when receiving a correct frame with a DLC field greater than eight (8).

Seven elementary tests shall be performed, for which DLC  $\in$  [9, Fh].

## 7.1.8.2 Test case organization

Test case organization shall be in accordance with Table 12.

Table 12 — DLC greater than 8 — Test case organization

| State        | Description                                                                                                                                                                                                                         |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Set-up       | No action required, the IUT is left in the default state.                                                                                                                                                                           |  |  |  |

| Test         | A single test frame is used for each of the elementary tests.                                                                                                                                                                       |  |  |  |

| Verification | The IUT shall not generate any error flag during the test.  The IUT shall acknowledge the test frame.  If 8 is an element of NDATA, the data received by the IUT during the test state shall match the data sent in the test frame. |  |  |  |

#### 7.1.9 Absent bus idle

## 7.1.9.1 Purpose and limits of test case

This test is applicable to CAN\_VERSION  $\in$  {A, B, BP}.

It is used to verify the behaviour of the IUT when receiving two consecutive frames not separated by a bus idle state.

Two cases shall be tested:

- the second frame starts after the second intermission bit of the first frame;

- the second frame starts after the third intermission bit of the first frame.

## 7.1.9.2 Test case organization

Test case organization shall be in accordance with Table 13.

Table 13 — Absent bus idle — Test case organization

| State        | Description                                                                                           |

|--------------|-------------------------------------------------------------------------------------------------------|

| Set-up       | No action required, the IUT is left in the default state.                                             |

| Test         | Two test frames are used for each of the two elementary tests.                                        |

| Verification | The IUT shall not generate any error flag during the test. The IUT shall acknowledge the test frames. |

# 7.1.10 Stuff acceptance — Test case 1

## 7.1.10.1 Purpose and limits of test case

This test is applicable to CAN\_VERSION  $\in$  {A, B, BP}.

It is used to verify the behaviour of the IUT when receiving a correct standard frame with particular data containing critical stuffing bit profiles in the different fields of the frame.

The fields of the tested frame shall be in accordance with Table 14.

15

Table 14 — Stuff acceptance — Test case 1 — Fields of the tested frame

| Frame | IDEN | RTR | CTRL | Data                              |

|-------|------|-----|------|-----------------------------------|

| 1     | 078h | 0   | 8    | 01h, E1h, E1h, E1h, E1h, E1h, E1h |

| 2     | 41Fh | 0   | 1    | 00                                |

| 3     | 707h | 0   | 1Fh  | 0Fh, 0Fh, 0Fh, 0Fh, 0Fh, 0Fh, 0Fh |

| 4     | 360h | 0   | 10h  |                                   |

| 5     | 730h | 0   | 10h  |                                   |

| 6     | 47Fh | 0   | 01h  | 1Fh                               |

| 7     | 758h | 0   | 00h  | _                                 |

| 8     | 777h | 0   | 01h  | 1Fh                               |

| 9     | 7Efh | 1   | 02h  | <del>-</del>                      |

| 10    | 3Eah | 1   | 1Fh  | <del>-</del>                      |

# 7.1.10.2 Test case organization

Test case organization shall be in accordance with Table 15.

Table 15 — Stuff acceptance — Test case 1 organization

| State        | Description                                                                                     |  |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------|--|--|--|--|

| Set-up       | lo action required, the IUT is left in the default state.                                       |  |  |  |  |

| Test         | A single test frame is used for each elementary test.                                           |  |  |  |  |

|              | The IUT shall not generate any error flag during the test.                                      |  |  |  |  |

| Verification | The IUT shall acknowledge the test frame.                                                       |  |  |  |  |

|              | The data received by the IUT during the test state shall match the data sent in the test frame. |  |  |  |  |

# 7.1.11 Stuff acceptance — Test case 2

# 7.1.11.1 Purpose and limits of this test case

This test is applicable to CAN\_VERSION  $\in$  {B, BP}.

It is used to verify the behaviour of the IUT when receiving a correct extended frame with particular data containing critical stuffing bit profiles in the different fields of the frame.

The fields of the tested frame shall be as given in the Table 16.

Table 16 — Stuff acceptance — Test case 2 — Fields of the tested frame

| Frame | IDEN 1 | SRR | IDEN 2 | RTR | CTRL | Data                                   |

|-------|--------|-----|--------|-----|------|----------------------------------------|

| 1     | 1F0h   | 1   | 30F0Fh | 0   | 8    | 3Ch, 3Ch, 3Ch, 3Ch, 3Ch, 3Ch, 3Ch      |

| 2     | 1F0h   | 1   | 0F0F0h | 0   | 1    | 00                                     |

| 3     | 078h   | 1   | 31717h | 0   | 1Fh  | 0Fh, 0Fh, 0Fh, 0Fh, 0Fh, 0Fh, 0Fh      |

| 4     | 078h   | 1   | 00FF0h | 0   | 3Ch  | 1Fh, 0Fh, E0h, F0h, 7Fh, E0h, FFh, 20h |

| 5     | 7EEh   | 1   | 0      | 0   | 01h  | A0h                                    |

| 6     | 02Fh   | 1   | 0540Fh | 1   | 20h  | _                                      |

| 7     | 557h   | 1   | 15557h | 1   | 3Fh  | _                                      |

## 7.1.11.2 Test case organization

Test case organization shall be in accordance with Table 17.

Table 17 — Stuff acceptance — Test case 2 organization

| State        | Description                                                                                                                                                                                          |  |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Set-up       | No action required, the IUT is left in the default state.                                                                                                                                            |  |  |  |  |

| Test         | A single test frame is used for each of the $n$ elementary tests.                                                                                                                                    |  |  |  |  |

| Verification | The IUT shall not generate any error flag during the test. The IUT shall acknowledge the test frame. The data received by the IUT during the test state shall match the data sent in the test frame. |  |  |  |  |

## 7.1.12 Message validation

## 7.1.12.1 Purpose and limits of test case

This test is applicable to CAN\_VERSION  $\in$  {A, B, BP}.

Its purpose is to verify the point of time at which a message is taken to be valid by the IUT.

## 7.1.12.2 Test case organization

Test case organization shall be in accordance with Table 18.

Table 18 — Message validation — Test case organization

| State        | Description                                                                                                                                                                                                                                       |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Set-up       | The IUT has to be initialized with data different from those used in the test frame.                                                                                                                                                              |  |  |  |

| Test         | A single test frame is used for the elementary test. The last bit of the EOF is forced to dominant state.                                                                                                                                         |  |  |  |

| Verification | The IUT shall not generate any error flag during the test.  The IUT shall acknowledge the test frame.  The IUT shall generate an overload frame.  The data received by the IUT during the test state shall match the data sent in the test frame. |  |  |  |

# 7.1.13 DLC not belonging to NDATA

## 7.1.13.1 Purpose and limits of test case

This test is applicable to CAN\_VERSION ∈ {A, B, BP}.

It is used to verify the behaviour of the IUT when receiving a correct frame with a DLC not belonging to NDATA and lower than a value of nine (9).

## 7.1.13.2 Test case organization

Test case organization shall be in accordance with Table 19.

Table 19 — DLC not belonging to NDATA — Test case organization

| State        | Description                                                                                          |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------|--|--|--|

| Set-up       | No action required, the IUT is left in the default state.                                            |  |  |  |

| Test         | A single test frame is used for each of the elementary tests.                                        |  |  |  |

| Verification | The IUT shall not generate any error flag during the test. The IUT shall acknowledge the test frame. |  |  |  |

--\*\*\*,,,-\*-\*,,\*,,\*,,\*,

# 7.2 Test class 2, error detection

## 7.2.1 Bit error in data frame

## 7.2.1.1 Purpose and limits of test case

This test is applicable to CAN\_VERSION  $\in$  {A, B, BP}.

It is used to verify that the IUT detects a bit error when the dominant ACK slot is forced to recessive state by LT.

# 7.2.1.2 Test case organization

Test case organization shall be in accordance with Table 20.

Table 20 — Bit error in data frame — Test case organization

| State        | Description                                                                                                                         |  |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Set-up       | No action required, the IUT is left in the default state.                                                                           |  |  |  |  |

|              | A single test frame is used for the elementary test. The dominant acknowledgement bit sent by the IUT is forced to recessive state. |  |  |  |  |

| Verification | The IUT shall generate an active error frame starting at the bit position following the bit error.                                  |  |  |  |  |

### 7.2.2 Stuff error — Test case 1

## 7.2.2.1 Purpose and limits of test case

This test is applicable to CAN\_VERSION  $\in$  {A, B, BP}.

It is used to verify that the IUT detects a stuff error whenever it receives six consecutive bits of the same value until the position of the CRC delimiter in a standard frame.

The frames used in this test shall be as given in Table 21.

Table 21 — Stuff error — Test case 1 — Frame specification

| Frame | IDEN | RTR | CTRL | Data                              |

|-------|------|-----|------|-----------------------------------|

| 1     | 078h | 0   | 8    | 01h, E1h, E1h, E1h, E1h, E1h, E1h |

| 2     | 41Fh | 0   | 1    | 00                                |

| 3     | 707h | 0   | 1Fh  | 0Fh, 0Fh, 0Fh, 0Fh, 0Fh, 0Fh, 0Fh |

| 4     | 360h | 0   | 10h  | _                                 |

| 5     | 730h | 0   | 10h  | _                                 |

| 6     | 47Fh | 0   | 01h  | 1Fh                               |

| 7     | 758h | 0   | 00h  | _                                 |

| 8     | 777h | 0   | 01h  | 1Fh                               |

| 9     | 7EFh | 1   | 02h  | _                                 |

| 10    | 3EAh | 1   | 1Fh  | _                                 |

## 7.2.2.2 Test case organization

Test case organization shall be in accordance with Table 22.

Table 22 — Stuff error — Test case 1 organization

| State        | Description                                                                                                                          |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Set-up       | No action required, the IUT is left in the default state.                                                                            |

| Test         | A single test frame is used for each elementary test. In each elementary test the LT forces one of the stuff bits to its complement. |

| Verification | The IUT shall generate an active error frame starting at the bit position following the stuff error.                                 |

## 7.2.3 Stuff error — Test case 2

## 7.2.3.1 Purpose and limits of test case

This test is applicable to CAN\_VERSION  $\in$  {B, BP}.

It is used to verify that the IUT detects a stuff error whenever it receives 6 consecutive bits of the same value until the position of the CRC delimiter in an extended frame.

The frames used in this test shall be as given in Table 23.

Table 23 — Stuff error — Test case 2 — Frame specification

| Frame | IDEN 1 | SRR | IDEN 2 | RTR | CTRL | Data                                   |

|-------|--------|-----|--------|-----|------|----------------------------------------|

| 1     | 1F0h   | 1   | 30F0Fh | 0   | 8    | 3Ch, 3Ch, 3Ch, 3Ch, 3Ch, 3Ch, 3Ch      |

| 2     | 1F0h   | 1   | 0F0F0h | 0   | 1    | 00                                     |

| 3     | 078h   | 1   | 31717h | 0   | 1Fh  | 0Fh, 0Fh, 0Fh, 0Fh, 0Fh, 0Fh, 0Fh      |

| 4     | 078h   | 1   | 00FF0h | 0   | 3Ch  | 1Fh, 0Fh, E0h, F0h, 7Fh, E0h, FFh, 20h |

| 5     | 7EEh   | 1   | 0      | 0   | 01h  | A0h                                    |

| 6     | 02Fh   | 1   | 0540Fh | 1   | 20h  | _                                      |

| 7     | 557h   | 1   | 15557h | 1   | 3Fh  | _                                      |

# 7.2.3.2 Test case organization

Test case organization shall be in accordance with Table 24.

Table 24 — Stuff error — Test case 2 organization

| State        | Description                                                                                                                          |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Set-up       | No action required, the IUT is left in the default state.                                                                            |

| Test         | A single test frame is used for each elementary test. In each elementary test the LT forces one of the stuff bits to its complement. |

| Verification | The IUT shall generate an active error frame starting at the bit position following the stuff error.                                 |

#### 7.2.4 CRC error

#### 7.2.4.1 Purpose and limits of this test case

This test is applicable to CAN VERSION ∈ {A, B, BP}

Its purpose is to verify

- that the IUT uses the specific CRC mechanism as in the CAN specification, and

- that an IUT detecting a CRC error generates an error frame at the correct position.

Two elementary tests shall be performed:

- a dominant bit in the CRC field is changed in a recessive one;

- a recessive bit in the CRC field is changed in a dominant one.

#### 7.2.4.2 **Test case organization**

Test case organization shall be in accordance with Table 25.

Table 25 — CRC error — Test case organization

| State        | Description                                                                                                                                         |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Set-up       | No action required, the IUT is left in the default state.                                                                                           |

| Test         | A single test frame is used for each elementary test. In each elementary test the LT modifies the frame according to 7.2.4.1.                       |

| Verification | The IUT shall not acknowledge the test frame The IUT shall generate an active error frame starting at the bit position following the ACK delimiter. |

## 7.2.5 Combination of CRC error and form error

#### 7.2.5.1 Purpose and limits of this test case

This test is applicable to CAN\_VERSION  $\in$  {A, B, BP}.

Its purpose is to verify that an IUT detecting a CRC error and a form error on the CRC delimiter in the same frame generates only a single, 6-bit long error flag starting on the bit following the CRC delimiter.

One elementary test shall be performed.

#### 7.2.5.2 **Test case organization**

Test case organization shall be in accordance with Table 26.

Table 26 — Combination of CRC error and form error — Test case organization

| State        | Description                                               |  |  |

|--------------|-----------------------------------------------------------|--|--|

| Set-up       | No action required, the IUT is left in the default state. |  |  |

| Test         | A single test frame is used for the elementary test.      |  |  |

| Verification | The IUT shall generate an active error frame.             |  |  |

## 7.2.6 Form error in data frame — Test case 1

## 7.2.6.1 Purpose and limits of test case

This test is applicable to CAN\_VERSION ∈ {A, B, BP}

It is used to verify that the IUT detects a form error when the recessive bit of CRC delimiter is forced to dominant state by LT.

One elementary test shall be performed.

### 7.2.6.2 Test case organization

Test case organization shall be in accordance with Table 27.

Table 27 — Form error in data frame — Test case 1 organization

| State        | Description                                                                                   |  |  |

|--------------|-----------------------------------------------------------------------------------------------|--|--|

| Set-up       | No action required, the IUT is left in the default state.                                     |  |  |

| Test         | A single test frame is used for the elementary test.                                          |  |  |

| Verification | The IUT shall generate an active error frame at the bit position following the CRC delimiter. |  |  |

### 7.2.7 Form error in data frame — Test case 2

## 7.2.7.1 Purpose and limits of test case

This test is applicable to CAN\_VERSION  $\in$  {A, B, BP}.

It is used to verify that the IUT detects a form error when the recessive ACK delimiter is forced to dominant state by LT.

One elementary test shall be performed.

### 7.2.7.2 Test case organization

Test case organization shall be in accordance with Table 28.

Table 28 — Form error in data frame — Test case 2 organization

| State        | Description                                                                                   |  |  |

|--------------|-----------------------------------------------------------------------------------------------|--|--|

| Set-up       | No action required, the IUT is left in the default state.                                     |  |  |

| Test         | A single test frame is used for the elementary test.                                          |  |  |

| Verification | The IUT shall generate an active error frame at the bit position following the ACK delimiter. |  |  |

### 7.2.8 Form error in data frame — Test case 3

# 7.2.8.1 Purpose and limits of test case

This test is applicable to CAN\_VERSION  $\in$  {A, B, BP}.

It is used to verify that the IUT detects a form error when one of six first recessive bits of EOF is forced to dominant state by LT.

Three elementary tests shall be performed, corrupting the first, last and 3rd bit position.

## 7.2.8.2 Test case organization

Test case organization shall be in accordance with Table 29.

Table 29 — Form error in data frame — Test case 3 organization

| State        | Description                                                                                   |  |  |

|--------------|-----------------------------------------------------------------------------------------------|--|--|

| Set-up       | No action required, the IUT is left in the default state.                                     |  |  |

| Test         | A single test frame is used for the elementary test.                                          |  |  |

| Verification | The IUT shall generate an active error frame at the bit position following the corrupted bit. |  |  |

## 7.2.9 Message non-validation

## 7.2.9.1 Purpose and limits of test case

This test is applicable to CAN VERSION  $\in$  {A, B, BP}.

Its purpose is to verify the point of time at which a message is still considered as non-valid by the IUT.

One elementary test shall be performed.

## 7.2.9.2 Test case organization

Test case organization shall be in accordance with Table 30.

Table 30 — Message non-validation — Test case organization

| State        | Description                                                                                                                                                                          |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Set-up       | The IUT has to be initialized with data different from those used in the test frame.                                                                                                 |  |  |

| Test         | A single test frame is used for the elementary test. The sixth bit of the EOF is forced to dominant.  A single test frame is used for the elementary test.                           |  |  |

| Verification | The IUT shall generate an active error frame.  The data initialized during the set-up state shall remain unchanged.  No frame reception is indicated to the upper layers of the IUT. |  |  |

## 7.3 Test class 3, active error frame management

# 7.3.1 Error flag longer than 6 bits

## 7.3.1.1 Purpose and limits of test case

This test is applicable to CAN\_VERSION  $\in$  {A, B, BP}.

It is used to verify that the IUT tolerates up to seven consecutive dominant bits after sending an active error flag.

Three elementary tests shall be performed, lengthening the error flag by one, four and seven dominant bits.

## 7.3.1.2 Test case organization

Test case organization shall be in accordance with Table 31.

Table 31 — Error flag longer than 6 bits — Test case organization

| State        | Description                                                                                             |  |  |

|--------------|---------------------------------------------------------------------------------------------------------|--|--|

| Set-up       | No action required, the IUT is left in the default state.                                               |  |  |

| Test         | The LT causes the IUT to generate an error frame. The LT lengthens the error flag generated by the IUT. |  |  |

| Verification | After sending the active error flag, the IUT sends recessive bits.                                      |  |  |

## 7.3.2 Data frame starting on third bit of intermission field

## 7.3.2.1 Purpose and limits of test case

This test is applicable to CAN\_VERSION ∈ {A, B, BP}.

The purpose of this test is to verify that an IUT accepts a frame starting after the second bit of the intermission following the error frame it has transmitted.

One elementary test shall be performed.

# 7.3.2.2 Test case organization

Test case organization shall be in accordance with Table 32.

Table 32 — Data frame starting on third bit of intermission field — Test case organization

| State        | Description                                                                                                                                |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Set-up       | No action required, the IUT is left in the default state.                                                                                  |

| Test         | The LT causes the IUT to generate an error frame. A single test frame is started two (2) bits after the end of the error delimiter.        |

| Verification | The IUT shall acknowledge the test frame.  The data received by the IUT during the test state shall match the data sent in the test frame. |

## 7.3.3 Bit error in error flag

## 7.3.3.1 Purpose and limits of test case

This test is applicable to CAN\_VERSION ∈ {A, B, BP}.

It is used to verify that the IUT detects a bit error when one of the six dominant bits of the error flag it transmits is forced to recessive state by LT.

Three elementary tests shall be performed, corrupting the first, third and sixth bit of the error flag.

## 7.3.3.2 Test case organization

Test case organization shall be in accordance with Table 33.

Table 33 — Bit error in error flag — Test case organization

| State        | Description                                                                                                                                                  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Set-up       | No action required, the IUT is left in the default state.                                                                                                    |

| Test         | The LT causes the IUT to generate an error frame.  The LT forces one of the above mentioned bits of the error frame generated by the IUT to recessive state. |

| Verification | The IUT shall restart with an active error frame at the bit position following the corrupted bit.                                                            |

## 7.3.4 Form error in error delimiter

#### 7.3.4.1 Purpose and limits of test case

This test is applicable to CAN VERSION  $\in$  {A, B, BP}.

It is used to verify that the IUT detects a form error when receiving an invalid error delimiter.

The LT replaces one of the eight recessive bits of the error delimiter by a dominant bit.

Three elementary tests shall be performed, corrupting the second, fourth and seventh bit of the error delimiter.

#### Test case organization 7.3.4.2

Test case organization shall be in accordance with Table 34.

Table 34 — Form error in error delimiter — Test case organization

| State        | Description                                                                                                                                              |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Set-up       | No action required, the IUT is left in the default state.                                                                                                |

| Test         | The LT causes the IUT to generate an error frame.  The LT replaces one of the above mentioned recessive bits of the error delimiter with a dominant bit. |

| Verification | The IUT shall restart with an active error frame at the bit position following the replaced bit.                                                         |

## Test class 4, overload frame management

## 7.4.1 MAC overload generation during intermission field

#### 7.4.1.1 Purpose and limits of test case

This test is applicable to CAN\_VERSION  $\in$  {A, B, BP}.

It is used to verify that the IUT generates an overload frame when detecting a dominant bit on one of the two first recessive bits of the intermission field.

Two elementary tests shall be performed.

#### 7.4.1.2 Test case organization

Test case organization shall be in accordance with Table 35.

Table 35 — MAC overload generation during intermission field — Test case organization

| State        | Description                                                                                                                                                            |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Set-up       | No action required, the IUT is left in the default state.                                                                                                              |

| Test         | One test frame is used for each of the two elementary tests.  The LT forces one of the two first bits of the intermission field of the test frame to a dominant value. |

| Verification | The IUT generates an overload frame at the bit position following the dominant bit.                                                                                    |

## 7.4.2 Last bit of EOF

#### Purpose and limits of test case 7.4.2.1

This test is applicable to CAN\_VERSION  $\in$  {A, B, BP}.

It is used to verify that the IUT generates an overload frame when detecting a dominant state on the last bit of EOF.

One elementary test shall be performed.

## 7.4.2.2 Test case organization

Test case organization shall be in accordance with Table 36.

Table 36 — Last bit of EOF — Test case organization

| State        | Description                                                                         |

|--------------|-------------------------------------------------------------------------------------|

| Set-up       | No action required, the IUT is left in the default state.                           |

| Test         | The LT forces the last bit of the EOF to a dominant state.                          |

| Verification | The IUT generates an overload frame at the bit position following the dominant bit. |

## 7.4.3 Eighth bit of an error and overload delimiter

## 7.4.3.1 Purpose and limits of test case

This test is applicable to CAN\_VERSION  $\in$  {A, B, BP}.

It is used to verify that the IUT generates an overload frame when detecting a dominant bit on the eighth bit of an error and overload delimiter it is transmitting.

Two elementary tests shall be performed.

## 7.4.3.2 Test case organization

Test case organization shall be in accordance with Table 37.

Table 37 — Eighth bit of an error and overload delimiter — Test case organization

| State        | Description                                                                                                                                |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Set-up       | No action required, the IUT is left in the default state.                                                                                  |

| Test         | The LT causes the IUT to generate an error frame or an overload frame.  The LT forces to a dominant state the eighth bit of the delimiter. |

| Verification | The IUT generates an overload frame starting at the bit position following the dominant bit forced by the LT.                              |

## 7.4.4 Bit error in overload flag

# 7.4.4.1 Purpose and limits of test case

This test is applicable to CAN VERSION ∈ {A, B, BP}

It is used to verify that the IUT detects a bit error when one of the six dominant bits of the overload flag it transmits is forced to recessive state by LT.

Three elementary tests shall be performed, corrupting the first, third and sixth bit of the overload flag.

### 7.4.4.2 Test case organization

Test case organization shall be in accordance with Table 38.

Table 38 — Bit error in overload flag — Test case organization

| State        | Description                                                                                                                                      |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Set-up       | No action required, the IUT is left in the default state.                                                                                        |

| Test         | The LT causes the IUT to generate an overload frame.  The LT forces one of the above mentioned bits of the overload flag to the recessive state. |

| Verification | The IUT shall generate an error frame at the bit position following the corrupted bit.                                                           |

#### 7.4.5 Form error in overload delimiter

#### 7.4.5.1 Purpose and limits of test case

This test is applicable to CAN\_VERSION  $\in$  {A, B, BP}.

It is used to verify that the IUT detects a form error when receiving an invalid overload delimiter.

The LT replaces one of the eight recessive bits of the overload delimiter by a dominant bit.

Three elementary tests shall be performed, corrupting the second, fourth and seventh bit of the overload delimiter.

#### 7.4.5.2 Test case organization

Test case organization shall be in accordance with Table 39.

Table 39 — Form error in overload delimiter — Test case organization

| State        | Description                                                                                                                                                    |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Set-up       | No action required, the IUT is left in the default state.                                                                                                      |

| Test         | The LT causes the IUT to generate an overload frame.  The LT replaces one of the above mentioned recessive bits of the overload delimiter with a dominant bit. |

| Verification | The IUT generates an error frame starting at the bit position following the replaced bit.                                                                      |

# Test class 5, passive-error state and bus-off

## 7.5.1 Passive-error flag completion — Test case 1

#### 7.5.1.1 Purpose and limits of test case

This test is applicable to CAN VERSION  $\in$  {A, B, BP}.

Its purpose is to verify that an error-passive IUT considers the passive-error flag as completed after the detection of six consecutive bits of the same value.

Three elementary tests shall be performed, superimposing the passive-error flag by an active-error flag starting at the first, the third and the sixth bits.

#### 7.5.1.2 **Test case organization**

Test case organization shall be in accordance with Table 40.

Table 40 — Passive-error flag completion — Test case 1 organization

| State        | Description                                                                                                                                                                                                                                           |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Set-up       | The IUT is set in passive state.                                                                                                                                                                                                                      |

| Test         | The LT causes the IUT to generate a passive-error frame.  During the passive-error flag sent by the IUT, the LT sends an active-error flag.  At the end of the active-error flag the LT waits for (8 + 2) bit time before sending a valid test frame. |

| Verification | The IUT shall acknowledge the test frame.                                                                                                                                                                                                             |

## 7.5.2 Data frame acceptance after passive-error frame transmission

## 7.5.2.1 Purpose and limits of test case

This test is applicable to CAN\_VERSION  $\in$  {A, B, BP}.

Its purpose is to verify that an error-passive IUT accepts a frame starting after the second bit of the intermission following the error frame it has transmitted.

One elementary test shall be performed.

## 7.5.2.2 Test case organization

Test case organization shall be in accordance with Table 41.

Table 41 — Data frame acceptance after passive-error frame transmission — Test case organization

| State        | Description                                                                                                                                                         |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Set-up       | The IUT is set in passive state.                                                                                                                                    |

| Test         | The LT causes the IUT to generate a passive-error frame.  At the end of the passive-error flag the LT waits for (8 + 2) bit time before sending a valid test frame. |

| Verification | The IUT shall acknowledge the test frame.                                                                                                                           |

# 7.5.3 Acceptance of 7 consecutive dominant bits after passive-error flag

# 7.5.3.1 Purpose and limits of this test case

This test is applicable to CAN\_VERSION  $\in$  {A, B, BP}.

Its purpose is to verify that an error-passive IUT does not detect any error when detecting up to 7 consecutive dominant bits starting at the bit position following the last bit of the passive-error flag.

Three elementary tests shall be performed, transmitting one, four or seven consecutive dominant bits.

## 7.5.3.2 Test case organization

Test case organization shall be in accordance with Table 42.

Table 42 — Acceptance of 7 consecutive dominant bits after passive-error flag — Test case organization

| State        | Description                                                                                                                                                                                                                                                  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Set-up       | The IUT is set in passive state.                                                                                                                                                                                                                             |

| Test         | The LT causes the IUT to generate a passive-error frame.  After the passive-error flag, the LT starts transmitting dominant bits according to 7.5.3.1.  After the dominant bit sequence the LT waits for (8 + 2) bit time before sending a valid test frame. |