Edition 1.0 2016-08

# **TECHNICAL REPORT**

Electrical interface specification for phase-cut dimmer in phase-cut dimmed lighting systems

# THIS PUBLICATION IS COPYRIGHT PROTECTED Copyright © 2016 IEC, Geneva, Switzerland

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from either IEC or IEC's member National Committee in the country of the requester. If you have any questions about IEC copyright or have an enquiry about obtaining additional rights to this publication, please contact the address below or your local IEC member National Committee for further information.

IEC Central Office Tel.: +41 22 919 02 11 3, rue de Varembé Fax: +41 22 919 03 00

CH-1211 Geneva 20 info@iec.ch Switzerland www.iec.ch

#### About the IFC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes International Standards for all electrical, electronic and related technologies.

#### About IEC publications

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the latest edition, a corrigenda or an amendment might have been published.

#### IEC Catalogue - webstore.iec.ch/catalogue

The stand-alone application for consulting the entire bibliographical information on IEC International Standards, Technical Specifications, Technical Reports and other documents. Available for PC, Mac OS, Android Tablets and iPad.

### IEC publications search - www.iec.ch/searchpub

The advanced search enables to find IEC publications by a variety of criteria (reference number, text, technical committee,...). It also gives information on projects, replaced and withdrawn publications.

## IEC Just Published - webstore.iec.ch/justpublished

Stay up to date on all new IEC publications. Just Published details all new publications released. Available online and also once a month by email.

#### Electropedia - www.electropedia.org

The world's leading online dictionary of electronic and electrical terms containing 20 000 terms and definitions in English and French, with equivalent terms in 15 additional languages. Also known as the International Electrotechnical Vocabulary (IEV) online.

#### IEC Glossary - std.iec.ch/glossary

65 000 electrotechnical terminology entries in English and French extracted from the Terms and Definitions clause of IEC publications issued since 2002. Some entries have been collected from earlier publications of IEC TC 37, 77, 86 and CISPR.

#### IEC Customer Service Centre - webstore.iec.ch/csc

If you wish to give us your feedback on this publication or need further assistance, please contact the Customer Service Centre: csc@iec.ch.

Edition 1.0 2016-08

# **TECHNICAL REPORT**

Electrical interface specification for phase-cut dimmer in phase-cut dimmed lighting systems

**INTERNATIONAL ELECTROTECHNICAL** COMMISSION

ICS 29.020 ISBN 978-2-8322-3551-5

Warning! Make sure that you obtained this publication from an authorized distributor.

# CONTENTS

| F         | DREWO        | RD                                                                                                                           | 4   |

|-----------|--------------|------------------------------------------------------------------------------------------------------------------------------|-----|

| IN        | TRODU        | CTION                                                                                                                        | 6   |

| 1         | Scop         | 9                                                                                                                            | 7   |

| 2         | Norm         | ative references                                                                                                             | 7   |

| 3         | Term         | s and definitions                                                                                                            | 7   |

| 4         | Gene         | ral description                                                                                                              | 9   |

| 5         | Gene         | ral requirements                                                                                                             | 9   |

|           | 5.1          | Voltage rating                                                                                                               | 9   |

|           | 5.2          | Frequency rating                                                                                                             | 9   |

|           | 5.3          | Marking of phase-cut dimmer                                                                                                  | 9   |

| 6         | Desc         | ription of the lighting system and its components                                                                            | 9   |

|           | 6.1          | Wiring method                                                                                                                | 9   |

|           | 6.2          | Wiring diagram                                                                                                               | 9   |

| 7         | Elect        | rical specification                                                                                                          | 10  |

|           | 7.1          | Overview                                                                                                                     | 10  |

|           | 7.2          | General                                                                                                                      |     |

|           | 7.3          | Electrical characteristics during the on state of a lighting system                                                          |     |

|           | 7.3.1        | General                                                                                                                      |     |

|           | 7.3.2        | Electrical characteristics for leading edge dimming method                                                                   |     |

|           | 7.3.3        | Electrical characteristics for trailing edge dimming method                                                                  |     |

| 8         |              | Electrical characteristics during the off state of a lighting system                                                         |     |

| 0         |              | General                                                                                                                      |     |

|           | 8.1<br>8.2   | Tests for leading edge phase-cut dimmers                                                                                     |     |

|           | 8.2.1        | General                                                                                                                      |     |

|           | 8.2.2        | Test related to the non-conducting phase                                                                                     |     |

|           | 8.2.3        | Test related to the transition from the non-conducting to the conducting                                                     | 20  |

|           | 0.2.0        | phase                                                                                                                        | 25  |

|           | 8.2.4        | Test related to the conducting phase                                                                                         | 26  |

|           | 8.3          | Tests for trailing edge phase-cut dimmers                                                                                    | 26  |

|           | 8.3.1        | General                                                                                                                      |     |

|           | 8.3.2        | Test related to the conducting phase                                                                                         | 26  |

|           | 8.3.3        | Test related to the transition from the conducting phase to the non-conducting phase and related to the non-conducting phase | 27  |

|           | 8.4          | Tests for characteristics during electronic off state                                                                        |     |

| Δr        |              | normative) Waveforms for AC voltage source                                                                                   |     |

| , (I      | A.1          | General                                                                                                                      |     |

|           |              | Waveform description – Leading edge                                                                                          |     |

|           |              | Waveform description – Trailing edge                                                                                         |     |

| Ar        |              | normative) Equivalent circuit for controlgear in on state (EC_CG)                                                            |     |

|           | •            | normative) Equivalent circuit for controlgear being in off state                                                             |     |

|           | •            | hy                                                                                                                           |     |

| וט        | unugrap      |                                                                                                                              | აა  |

| <u>_:</u> | auro 1       | Example of wiring diagram                                                                                                    | 10  |

| ~ (       | <b>:</b> ' − | LAGUIUE ULWIIIIU UIGUIGIII                                                                                                   | 117 |

| Figure 2 – Timing leading edge dimming method                                                                                           | 13 |

|-----------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3 – Timing trailing edge dimming method                                                                                          | 18 |

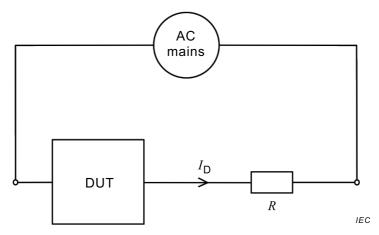

| Figure 4 – Circuit to test the properties of the phase-cut dimmer during the non-conducting phase (Method 1)                            | 24 |

| Figure 5 – Circuit to test the properties of the phase-cut dimmer during the non-conducting phase (Method 2)                            | 25 |

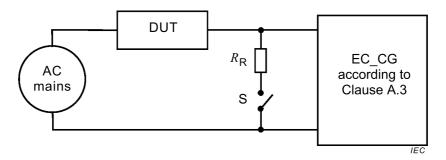

| Figure 6 – Circuit to test the properties of the phase-cut dimmer during the transition from the non-conducting to the conducting phase | 26 |

| Figure 7 – Circuit to test the properties of the phase-cut dimmer during the electronic off-state                                       | 28 |

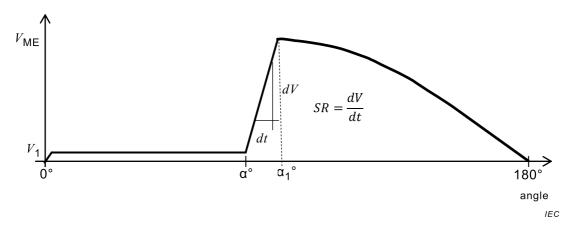

| Figure A.1 – Waveform of AC voltage source – Leading edge                                                                               | 29 |

| Figure A.2 – Waveform of AC voltage source – Trailing edge                                                                              | 30 |

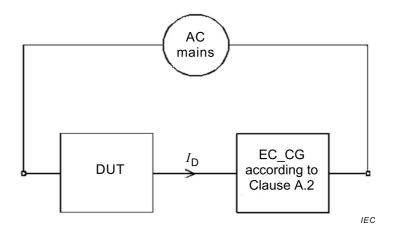

| Figure B.1 – Equivalent circuit for controlgear in the on state to be used during dimmer tests                                          | 31 |

| Figure C.1 – Equivalent circuit for controlgear being in off state                                                                      | 32 |

| Table 1 – Nominal mains voltage 100 V – Frequency 50 Hz or 60 Hz                                                                        |    |

| Table 2 – Nominal mains voltage 120 V – Frequency 50 Hz or 60 Hz                                                                        |    |

| Table 3 – Nominal mains voltage 200 V – Frequency 50 Hz or 60 Hz                                                                        |    |

| Table 4 – Nominal mains voltage 230 V – Frequency 50 Hz or 60 Hz                                                                        | 14 |

| Table 5 – Nominal mains voltage 277 V – Frequency 50 Hz or 60 Hz                                                                        |    |

| Table 6 – Slew rate for voltage decrease across the phase-cut dimmer                                                                    |    |

| Table 7 – Nominal mains voltage 100 V – Frequency 50 Hz or 60 Hz                                                                        |    |

| Table 8 – Nominal mains voltage 120 V – Frequency 50 Hz or 60 Hz                                                                        | 16 |

| Table 9 – Nominal mains voltage 200 V – Frequency 50 Hz or 60 Hz                                                                        | 16 |

| Table 10 – Nominal mains voltage 230 V – Frequency 50 Hz or 60 Hz                                                                       | 17 |

| Table 11 – Nominal mains voltage 277 V – Frequency 50 Hz or 60 Hz                                                                       | 17 |

| Table 12 – Nominal mains voltage from100 to 277 V – Frequency 50 Hz or 60 Hz                                                            | 19 |

| Table 13 – Nominal mains voltage 100 V – Frequency 50 Hz or 60 Hz                                                                       | 20 |

| Table 14 – Nominal mains voltage 120 V – Frequency 50 Hz or 60 Hz                                                                       | 20 |

| Table 15 – Nominal mains voltage 200 V – Frequency 50 Hz or 60 Hz                                                                       | 20 |

| Table 16 – Nominal mains voltage 230 V – Frequency 50 Hz or 60 Hz                                                                       | 21 |

| Table 17 – Nominal mains voltage 277 V – Frequency 50 Hz or 60 Hz                                                                       | 21 |

| Table 18 – Currents and voltages for controlgear during the electronic off state                                                        | 22 |

| Table 19 – Parameters for testing nurnoses                                                                                              | 23 |

#### INTERNATIONAL ELECTROTECHNICAL COMMISSION

\_\_\_\_\_

# ELECTRICAL INTERFACE SPECIFICATION FOR PHASE-CUT DIMMER IN PHASE-CUT DIMMED LIGHTING SYSTEMS

#### **FOREWORD**

- 1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as "IEC Publication(s)"). Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely with the International Organization for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- 2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC National Committees.

- 3) IEC Publications have the form of recommendations for international use and are accepted by IEC National Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

- 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter

- 5) IEC itself does not provide any attestation of conformity. Independent certification bodies provide conformity assessment services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any services carried out by independent certification bodies.

- 6) All users should ensure that they have the latest edition of this publication.

- 7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and members of its technical committees and IEC National Committees for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC Publications.

- 8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.

- 9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

The main task of IEC technical committees is to prepare International Standards. However, a technical committee may propose the publication of a technical report when it has collected data of a different kind from that which is normally published as an International Standard, for example "state of the art".

IEC TR 63036, which is a technical report, has been prepared by subcommittee 23B: Plugs, socket-outlets and switches, of IEC technical committee 23: Electrical accessories.

The text of this technical report is based on the following documents:

| Enquiry draft | Report on voting |

|---------------|------------------|

| 23B/1201/DTR  | 23B/1214/RVC     |

Full information on the voting for the approval of this technical report can be found in the report on voting indicated in the above table.

This publication has been drafted in accordance with the ISO/IEC Directives, Part 2.

The committee has decided that the contents of this publication will remain unchanged until the stability date indicated on the IEC website under "http://webstore.iec.ch" in the data related to the specific publication. At this date, the publication will be

- reconfirmed,

- withdrawn,

- replaced by a revised edition, or

- amended.

A bilingual version of this publication may be issued at a later date.

## **INTRODUCTION**

This document describes the technical requirements for phase-cut dimmers to work with controlgear and self ballasted lamps. For a complete picture of the technical requirements the reader should also refer to IEC TR 63037 that contains technical requirements and testing methods for controlgear and self ballasted lamps.

# ELECTRICAL INTERFACE SPECIFICATION FOR PHASE-CUT DIMMER IN PHASE-CUT DIMMED LIGHTING SYSTEMS

#### 1 Scope

This technical report specifies the electrical interface and test procedures for the control by mains voltage phase-cut dimming of the brightness of mains operated electronic lighting equipment intended to be controlled by mains voltage phase-cut dimmers, such as LED integrated lamps, and light sources with external control gear.

Electronic switches that use a comparable circuitry to a phase-cut dimmer but do not contain means for the adjustability of the phase-cut angle should fulfill the same requirements as a phase-cut dimmer.

Safety requirements are not covered by this document, but by respective product standards.

#### 2 Normative references

The following documents are referred to in the text in such a way that some or all of their content constitutes requirements of this document. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

IEC 60038, IEC standard voltages

IEC 60050-845, International Electrotechnical Vocabulary (IEV) – Part 845: Lighting (available at www.electropedia.org)

IEC 60364 (all parts), Low-voltage electrical installations

IEC 62504, General lighting – Light emitting diode (LED) products and related equipment – Terms and definitions

#### 3 Terms and definitions

For the purposes of this document, the terms and definitions given in IEC 62504 and IEC 60050-845 as well as the following apply.

### 3.1

#### lighting system

combination of a phase-cut dimmer and one or more controlgear and light sources

#### 3.2

#### off state

state of a lighting system when no light is emitted

#### 3.3

#### on state

state of a lighting system when light is emitted

#### 3.4

#### electrical interface

electrical parameters for supplying power and making the exchange of information between the phase-cut dimmer and controlgear possible

#### 3.5

#### phase-cut dimmer

electronic switch that is connected in series with a load and changes the supply voltage waveform applied to the load from the pure mains voltage waveform to a leading edge (forward phase) or a trailing edge (reverse phase) AC voltage waveform or is capable of switching between both waveforms

Note 1 to entry: The output voltage waveform of a phase-cut dimmer is applied to one or more loads.

Note 2 to entry: The conduction angle of the voltage waveform is adjustable.

Note 3 to entry: Within this document, where the term "dimmer" is used the term "phase-cut dimmer" is meant.

#### 3.6

#### two-wire phase-cut dimmer

phase-cut dimmer that is connected in series with the load and has no connection to neutral

#### 3.7

#### three-wire phase-cut dimmer

phase-cut dimmer that is connected in series with the load and has in addition a connection to neutral

#### 3.8

#### controlgear

device between the phase-cut dimmer and one or more lamps which may serve to transform the AC mains power, limit the current of the lamp(s) to the required value, provide starting voltage and preheating current, prevent cold starting, correct power factor or reduce radio interference

Note 1 to entry: Lamps may have integrated controlgear such as an integrated LED lamp. Any references to controlgear will include any such integrated lamps.

#### 3.9

#### load side

wire from the output of the phase-cut dimmer to the supply input of one or more controlgear

#### 3.10

#### conducting period

time period during which the phase-cut dimmer supplies power to a controlgear

#### 3.11

#### non-conducting period

time period during which the phase-cut dimmer does not supply power to a controlgear

#### 3.12

#### half wave

positive or negative 180° of an AC sine wave starting and ending at the zero crossing point

#### 3.13

#### phase angle

position within a half wave expressed in degree, being in the range of 0° to 180°, in reference to the beginning of the half wave

#### 4 General description

A phase-cut dimmer either cuts the mains voltage immediately after the zero crossing of the mains (leading edge) or towards the next projected zero crossing of the mains (trailing edge). The functionality of both methods may be implemented in one device (universal dimmers).

This document describes requirements for phase-cut dimmers during the on state of a lighting system. Specifications are provided dependent on the dimming method for the conducting period and the non-conducting period of the phase-cut dimmer and the transitions between conducting and non-conducting period.

In addition, this document describes requirements for phase-cut dimmers during the off state of a lighting system. Specifications are provided independently from the dimming method.

### 5 General requirements

#### 5.1 Voltage rating

This document applies to one or more of the following mains voltages:

100 V, 120 V, 200 V, 230 V, 277 V, according to IEC 60038.

#### 5.2 Frequency rating

This document applies to one or more of the following mains frequencies:

50 Hz or 60 Hz, according to IEC 60038.

#### 5.3 Marking of phase-cut dimmer

The following information should be provided by the manufacturer on the product or in the accompanying instruction sheets.

Phase-cut dimmers requiring more than one controlgear to function properly should be marked with the required minimum number of connected controlgear.

Phase-cut dimmers requiring a minimum load should be marked with the required minimum load.

Phase-cut dimmers should be marked with the following indication:

### 6 Description of the lighting system and its components

#### 6.1 Wiring method

The wiring of the devices is in accordance with the installation rules given in the IEC 60364 series and also with the national wiring rules applicable in the country where the devices are installed.

### 6.2 Wiring diagram

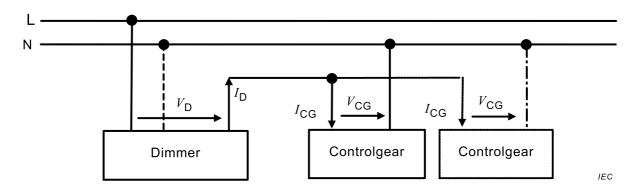

The wiring of the lighting system uses the traditional method of connecting the phase-cut dimmer to the mains and to the controlgear. Figure 1 is an example of a lighting system with one phase-cut dimmer and one or two controlgear(s).

Regarding the connections of the phase-cut dimmer shown in Figure 1, the drawn lines represent a two-wire installation and the dashed line represents the direct connection of the phase-cut dimmer to the mains which is used in three-wire installations.

The direct connection of the phase-cut dimmer to neutral (dashed line in Figure 1) will have consequences on the power supply requirements and synchronization to the phase-cut dimmer.

This document defines requirements that enable compatibility between phase-cut dimmers and controlgear in two-wire installations. However, all predications are also valid for three-wire phase-cut dimmers to ensure proper operation of controlgear.

Figure 1 – Example of wiring diagram

#### 7 Electrical specification

#### 7.1 Overview

To describe the electrical characteristics of the electrical interface, the following abbreviations are used:

- $\alpha_{\rm x}$   $\,$  Angle where the test voltage starts rising with the given slew rate SR as shown in Figure A.1

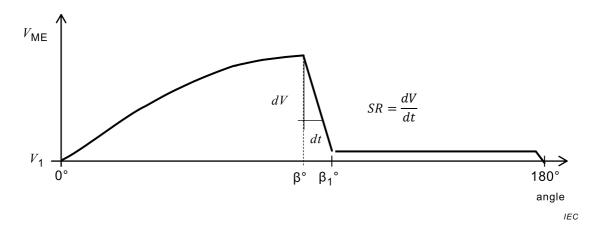

- $\beta_{\rm X}$  Angle where the test voltage starts falling with the given slew rate SR as shown in Figure A.2

- $C_{\rm f}$  Filter capacitor to reduce high frequency disturbances

- EC\_CG Equivalent circuit that represents a controlgear for phase-cut dimmer testing purposes

- EC\_D Equivalent circuit that represents a phase-cut dimmer for controlgear testing purposes

- $I_{\text{CG}}$  Current through the input terminals of the controlgear (see Figure 1)

- $I_{\text{CG pk}}$  Repetitive peak current of the controlgear in leading edge mode

- $I_{\text{CG SL}}$  Current-carrying capability of the controlgear with  $V_{\text{CG}} \leq V_{\text{SW}}$  in leading edge mode

- $I_{\text{CG STH}}$  Current -carrying capability of the controlgear with  $V_{\text{CG}} \leq V_{\text{SW}}$  in trailing edge mode

- $I_{CG-STL}$  Current-carrying capability of the controlgear with  $V_{CG} > V_{SW}$  in trailing edge mode

- $I_{\rm D}$  Current through the load side terminal of the phase-cut dimmer (see Figure 1)

- $I_{\rm D\_nc}$  Maximum current through the phase-cut dimmer during the non-conducting period, limited by the phase-cut dimmer

- $I_{PO}$  Minimum current carrying capability of the controlgear during the electronic off state

- $I_{\rm trans}$  Current sourced by the phase-cut dimmer during the transition from the conducting to the non-conducting state in trailing edge mode

- Required minimum number of controlgear connected with one phase-cut dimmer (named in phase-cut dimmer installation sheet)

- $P_{CG}$  Rated input power of the controlgear (as marked)

- $P_{\max}$  Maximum permissible nominal load of phase-cut dimmer (according to the installation sheet)

- $P_{\min}$  Minimum nominal load required by phase-cut dimmer (according to the installation sheet)

- $R_{\rm R}$  Resistance value of ohmic load R in relation to the relevant mains voltage according to Tables 7 to 11, representing the maximum permissible load of phase-cut dimmer  $P_{\rm max}$

- SR Absolute value of the slew rate of the decrease of the voltage across the input terminals of a controlgear in trailing edge dimming mode when the phase-cut dimmer switches off at time  $t_{\rm s1}$  (see Figure 3)

- SR<sub>L</sub> Absolute value of the slew rate of the increase of the voltage across the input terminals of a controlgear in leading edge dimming mode when the phase-cut dimmer under test switches on (according to Clause 8)

- $SR_{\mathsf{T}}$  Absolute value of the slew rate of the decrease of the voltage across the input terminals of a controlgear in trailing edge dimming mode when the phase-cut dimmer under test switches off (according to Clause 8)

- $t_{\rm HW}$  Time related to previous zero crossing of the mains to the subsequent zero crossing of the mains (duration of a half wave)

- t<sub>s</sub> Time related to previous zero crossing of the mains when leading edge phase-cut dimmer reduces its impedance towards zero by activating its power switch

- t<sub>s1</sub> Time related to previous zero crossing of the mains when trailing edge phase-cut dimmer increases its impedance towards infinite by deactivating its power switch

- $t_{\rm S2}$  Time related to previous zero crossing of the mains when the voltage  $V_{\rm CG}$  falls below  $V_{\rm SW}$  in trailing edge method

- $t_{\rm s3}$  Time related to previous zero crossing of the mains when the transition from the conducting period to the non-conducting period is finished

- $t_{\mathrm{SW}}$  Time related to previous zero crossing of the mains when voltage  $V_{\mathrm{CG}}$  crosses  $V_{\mathrm{SW}}$

- $t_{\rm t}$  Transition time for trailing edge mode, equals  $t_{\rm s2} t_{\rm s1}$

- $V_{\rm CG}$  Voltage across the input terminals of the controlgear (see Figure 1)

- $V_{\mathsf{D}}$  Voltage between the line side (L) and load side terminal of the phase-cut dimmer (see Figure 1)

- *V*<sub>M</sub> Mains voltage (rated nominal value)

- $V_{\rm ME}$  Phase-cut voltage for testing purposes, sinusoidal part of the waveform (α<sub>1</sub> to  $t_{\rm HW}$ , 0 to β) equivalent to mains voltage

- $V_{\mathsf{PO}}$  Lower limit for voltage across the input terminals of the controlgear to provide a current carrying capability  $I_{\mathsf{PO}}$  during the electronic off state

- $V_{\rm SW}$  Voltage across the input terminals of the controlgear at the time that leads to disabling ( $V_{\rm M}(t) > V_{\rm SW}$ ) or enabling ( $V_{\rm M}(t) < V_{\rm SW}$ ) a current path having a current carrying capability of  $I_{\rm CG\_SL}$  or  $I_{\rm CG\_STH}$

- $V_{\rm test}$  Value of test voltage (according to 8.3 of IEC TR 63037:-)

- xx(t) Instantaneous values of current or voltage xx

- $Z_{CG}$  Impedance across the input terminals of the controlgear

- $Z_{\mathsf{D}}$  Impedance between the line side (L) and the load side terminals of the phase-cut dimmer

- $Z_{D_{max}}$  Maximum impedance between the line side (L) and load side terminal of the phase-cut dimmer, defined by the technical properties of the phase-cut dimmer

$Z_{D_{min}}$  Minimum impedance between the line side (L) and the load side terminal of the phase-cut dimmer, defined by the power properties of the phase-cut dimmer

#### 7.2 General

All information given in this document is related to a half wave of the mains. Due to the polarity change between subsequent half waves, all values have to be regarded as absolute values.

The lighting system is either in on state or in off state. In on state, light sources controlled by controlgear being part of the lighting system emit light. In off state, light sources controlled by controlgear being part of the lighting system do not emit light.

The off state may be realized as mechanical off state by opening the current loop of the lighting system with mechanical means, for example a switch. For this case, no requirements need to be fixed.

Alternatively, the off state may be realized as electronic off state. In this case, the phase-cut dimmer increases its impedance (i.e. stops producing phase-cut) while continuing its operation, for example to keep its control interface activated. In this case, the connected controlgear is not energized sufficiently to operate a light source, but provides a current path that allows the phase-cut dimmer to draw current continuously from the mains.

NOTE Applications that provide a connection to neutral allow the use of a three-wire device, enabling the usage of lamps that do not provide a current carrying capability according to 7.3 and 7.4.

During the on state and the electronic off state, it should be ensured that the phase-cut dimmer is supplied sufficiently with power and that the synchronization of phase-cut dimmer and controlgear with the mains is ensured.

#### 7.3 Electrical characteristics during the on state of a lighting system

#### 7.3.1 General

For the on state of a lighting system, specifications are dependent on the dimming method, leading edge or trailing edge.

Each half wave is divided into two periods, the conducting period and the non-conducting period of the phase-cut dimmer.

During the conducting period of the phase-cut dimmer, the mains voltage is applied to the controlgear. During the non-conducting period, the voltage between terminals of the phase-cut dimmer is almost equal to the mains voltage  $(V_D \approx V_M)$ .

### 7.3.2 Electrical characteristics for leading edge dimming method

#### 7.3.2.1 **General**

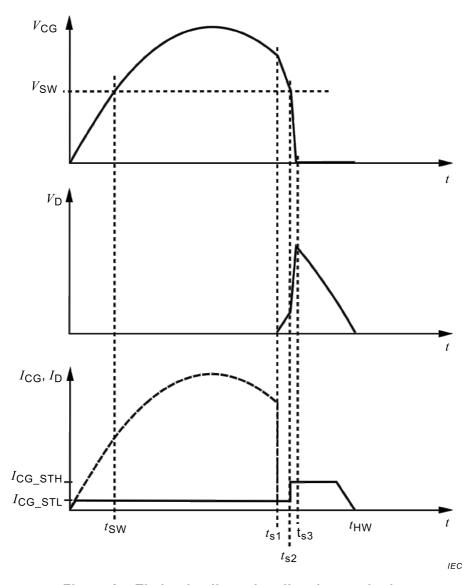

Starting from the mains zero crossing, the phase-cut dimmer remains in a non-conducting state until its timing element activates the power switch at  $t_{\rm s}$ . Afterwards, the phase-cut dimmer supplies power to the load for the entire remaining part of the mains half wave (see Figure 2).

To achieve synchronization with the mains and to control the phase-cut angle correctly, leading edge phase-cut dimmers need to draw a current also during the non-conducting state.

Thus, the controlgear is able to conduct a current  $I_{\text{CG\_SL}}$ , which allows synchronization of the phase-cut dimmer with the mains and ensures the supply of power to the phase-cut dimmer even in a two-wire installation.

Figure 2 – Timing leading edge dimming method

#### 7.3.2.2 Electrical characteristics during the non-conducting period

During the non-conducting period, the phase-cut dimmer should comply with the electrical characteristics listed in Tables 1 to 5.

The non-conducting period starts at the zero crossing of the mains and ends at time  $t_s$  when the timing element of the phase-cut dimmer activates the power switch.

During this period, the controlgear provides a current path with a minimum current-carrying capability of  $I_{\rm CG\ SL}.$

The controlgear may deactivate its current-carrying capability during the non-conducting period after it has not detected an input voltage waveform showing an unsteady waveform (leading edge characteristic) for 100 ms.

NOTE This is for reducing power losses in case a controlgear is used without a phase-cut dimmer.

During this period, the phase-cut dimmer should limit the current  $I_{\rm D}$  to n x  $I_{\rm D\_nc}$  as listed in the Tables 1 to 5, whereby  $I_{\rm D\_nc}$  is related to  $P_{\rm min}$  of the phase-cut dimmer.

EXAMPLE For Table 4:  $I_{\rm D}(t) \leq I_{\rm D-nc} = n \times 5.4$  mA/W x  $P_{\rm min}$  With n = 2(number of lamps),  $P_{\rm min}$  of the dimmer equals 3 W, then  $I_{\rm D}(t)$  is lower than 32,4 mA.

Table 1 - Nominal mains voltage 100 V - Frequency 50 Hz or 60 Hz

| Time related to previous zero crossing of mains voltage | Phase-cut dimmer:<br>Current limits                                                          |

|---------------------------------------------------------|----------------------------------------------------------------------------------------------|

|                                                         | $P_{\min}$ < 12 W:<br>$I_{D}(t) \le I_{D}$ =<br>$n \times 12,4 \text{ mÅ/W} \times P_{\min}$ |

| 0 to t <sub>s</sub>                                     |                                                                                              |

|                                                         | $P_{\min} \ge 12 \text{ W}:$ $I_{D}(t) \le I_{D_{nc}} = n \times 149 \text{ mA}$             |

|                                                         | $I_{D}(t) \le I_{D_nc} = n \times 149 \text{ mA}$                                            |

Table 2 - Nominal mains voltage 120 V - Frequency 50 Hz or 60 Hz

| Time related to previous zero crossing of mains voltage | Phase-cut dimmer:<br>Current limits                                     |

|---------------------------------------------------------|-------------------------------------------------------------------------|

|                                                         | P <sub>min</sub> < 12 W:                                                |

| 0 to t <sub>s</sub>                                     | $I_{D}(t) \le I_{D_{nc}} =$ $n \times 10.4 \text{ mA/W} \times P_{min}$ |

|                                                         | P <sub>min</sub> ≥ 12 W:                                                |

|                                                         | $I_{D}(t) \le I_{D_{nc}} = n \times 124,2 \text{ mA}$                   |

Table 3 - Nominal mains voltage 200 V - Frequency 50 Hz or 60 Hz

| Time related to previous zero crossing of mains voltage | Phase-cut dimmer:<br>Current limits                                |

|---------------------------------------------------------|--------------------------------------------------------------------|

|                                                         | P <sub>min</sub> < 12 W:                                           |

| 0 to t <sub>s</sub>                                     | $I_{D}(t) \le I_{D-DC} = n \times 6,2 \text{ mA/W} \times P_{min}$ |

|                                                         | P <sub>min</sub> ≥ 12 W:                                           |

|                                                         | $I_{\rm D}(t) \le I_{\rm D_nc} = n \times 74.5 \text{ mA}$         |

Table 4 - Nominal mains voltage 230 V - Frequency 50 Hz or 60 Hz

| Time related to previous zero crossing of mains voltage | Phase-cut dimmer:<br>Current limits                                                    |

|---------------------------------------------------------|----------------------------------------------------------------------------------------|

|                                                         | P <sub>min</sub> < 12 W:                                                               |

| 0 to <i>t</i> <sub>s</sub>                              | $I_{D}(t) \le I_{D-nc} = n \times 5,4 \text{ mA/W} \times P_{min}$                     |

|                                                         | P <sub>min</sub> ≥ 12 W:                                                               |

|                                                         | $P_{\min} \ge 12 \text{ W}:$<br>$I_{D}(t) \le I_{D_{nc}} = n \text{ x } 65 \text{ mA}$ |

Table 5 - Nominal mains voltage 277 V - Frequency 50 Hz or 60 Hz

| Time related to previous zero crossing of mains voltage | Phase-cut dimmer:<br>Current limits                                                              |

|---------------------------------------------------------|--------------------------------------------------------------------------------------------------|

|                                                         | P <sub>min</sub> < 12 W:                                                                         |

|                                                         | $P_{\min}$ < 12 W:<br>$I_{D}(t) \le I_{D_{nc}} =$<br>$n \times 4,5 \text{ mA/W} \times P_{\min}$ |

|                                                         | $n \times 4.5 \text{ mA/W} \times P_{\text{min}}$                                                |

| 0 to <i>t</i> <sub>s</sub>                              |                                                                                                  |

|                                                         | P <sub>min</sub> ≥ 12 W:                                                                         |

|                                                         | $P_{\min} \ge 12 \text{ W}:$ $I_{D}(t) \le I_{D_{nc}} = n \text{ x 54 mA}$                       |

# 7.3.2.3 Electrical characteristics during transition from the non-conducting to the conducting period

The transition from the non-conducting to the conducting state of the phase-cut dimmers starts at time  $t_{\rm S}$ .

Starting from time  $t_{\rm S}$ , the impedance  $Z_{\rm D}$  of the phase-cut dimmer decreases until its minimum  $Z_{\rm D\_min}$  is reached. The voltage  $V_{\rm CG}$  applied to the controlgear increases towards the instantaneous value  $V_{\rm M}(t)$  of the mains minus the voltage drop across the phase-cut dimmer.

The absolute value of the slew rate of the voltage change of  $V_{\rm D}$  during the transition period should not exceed the values as listed in Table 6 when the phase-cut dimmer is connected to the marked maximum resistive load.

The slew rate should be calculated based on the measurement of the voltage slope of  $V_{\rm D}$  by measuring the time (dt) between  $V_{\rm D}$  = 0,8 x  $V_{\rm D}(t_{\rm S})$  and  $V_{\rm D}$  = 0,1 x  $V_{\rm D}(t_{\rm S})$  and by calculating the differential voltage  $dV_{\rm D}$  = 0,8 x  $V_{\rm D}(t_{\rm S})$  - 0,1 x  $V_{\rm D}(t_{\rm S})$ .

When the voltage  $V_{\text{CG}}$  exceeds  $V_{\text{SW}}$ , the controlgear may deactivate its bypass circuitry (see Figure 2), thus possibly no current can flow through the controlgear.

NOTE Values for slew rate represent a compromise between EMC, repetitive peak current in the controlgear and switching losses in the phase-cut dimmer power semiconductors.

Table 6 – Slew rate for voltage decrease across the phase-cut dimmer

| <i>V<sub>M</sub></i> [V]            | 100   | 120   | 200   | 230   | 277   |

|-------------------------------------|-------|-------|-------|-------|-------|

| $dV_{\mathrm{D}}/dt$   [V/ $\mu$ s] | ≤ 6,5 | ≤ 300 | ≤ 6,5 | ≤ 6,5 | ≤ 300 |

#### 7.3.2.4 Electrical characteristics during the conducting period

During the conducting period, the phase-cut dimmer should comply with the electrical characteristics listed in Tables 7 to 11.

During this period, full power should be applied continuously to the controlgear from the phase-cut dimmer to allow power to be supplied to the controlgear.

During this period, independently from the current  $I_{\rm D}$  =  $I_{\rm CG}$ , the impedance  $Z_{\rm D}$  of the phase-cut dimmer should remain constantly at its minimum value  $Z_{\rm D min}$ .

The impedance  $Z_{\rm D}$  of the phase-cut dimmer is  $Z_{\rm D\_min}$  when the voltage  $V_{\rm D}(t)$  across the phase-cut dimmer is less than 0,1 x  $V_{\rm M}(t)$  during the entire conduction period.

NOTE Multiple switching cycles of the power switch during the conducting period result in non-constant  $Z_{\rm D}$  of the phase-cut dimmer. This is not desired.

Due to the low impedance of the phase-cut dimmer during the conducting period, the input voltage of the controlgear is almost equal to the mains voltage.

At time  $t_{sw}$ , the input voltage  $V_{CG}$  of the controlgear falls below  $V_{SW}$ .

From time  $t_{\rm SW}$  to the end of the period, the controlgear provides a current path with a minimum current-carrying capability of  $I_{\rm CG\_SL}$ .

Table 7 - Nominal mains voltage 100 V - Frequency 50 Hz or 60 Hz

| Time related to previous zero crossing of mains voltage | Phase-cut dimmer:<br>Impedance                                                                                                                |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| $t_{\rm s}$ to $t_{\rm sw}$                             | $Z_{\rm D} = Z_{\rm D\_min}$ $V_{\rm D}(t) < \max(0.1 \times V_{\rm M}(t), \ 10 \ \rm V)$ NOTE At $t_{\rm S}, \ Z_{\rm D}$ starts to decrease |

| $t_{sw}$ to $t_{HW}$                                    | $Z_{\rm D} = Z_{\rm D\_min}$<br>$V_{\rm D}(t) < \max(0.1 \times V_{\rm M}(t), 10 \text{ V})$                                                  |

Table 8 - Nominal mains voltage 120 V - Frequency 50 Hz or 60 Hz

| Time related to previous zero crossing of mains voltage | Phase-cut dimmer:<br>Impedance                                                                                                                 |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| $t_{\rm s}$ to $t_{\rm sw}$                             | $Z_{\rm D} = Z_{\rm D\_min}$ $V_{\rm D}(t) < \max(0.1 \times V_{\rm M}(t), 10 \text{ V})$ NOTE At $t_{\rm s}$ , $Z_{\rm D}$ starts to decrease |

|                                                         | NOTE At $t_s$ , $Z_D$ starts to decrease                                                                                                       |

| $t_{\rm sw}$ to $t_{\rm HW}$                            | $Z_{D} = Z_{D_{min}}$ $V_{D}(t) < \max(0.1 \times V_{M}(t), 10 \text{ V})$                                                                     |

Table 9 - Nominal mains voltage 200 V - Frequency 50 Hz or 60 Hz

| Time related to previous zero crossing of mains voltage | Phase-cut dimmer:<br>Impedance                                                                                                                 |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| $t_{\rm s}$ to $t_{\rm sw}$                             | $Z_{\rm D} = Z_{\rm D\_min}$ $V_{\rm D}(t) < \max(0.1 \times V_{\rm M}(t), 10 \text{ V})$ NOTE At $t_{\rm s}$ , $Z_{\rm D}$ starts to decrease |

| $t_{\rm sw}$ to $t_{\rm HW}$                            | NOTE At $t_s$ , $Z_D$ starts to decrease $Z_D = Z_{D_min}$ $V_D(t) < \max(0.1 \times V_M(t), 10 \text{ V})$                                    |

Table 10 - Nominal mains voltage 230 V - Frequency 50 Hz or 60 Hz

| Time related to previous zero crossing of mains voltage | Phase-cut dimmer:<br>Impedance                                                                                                                |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| $t_{\rm s}$ to $t_{\rm sw}$                             | $Z_{\rm D} = Z_{\rm D\_min}$ $V_{\rm D}(t) < \max(0.1 \times V_{\rm M}(t), \ 10 \ \rm V)$ NOTE At $t_{\rm s}, \ Z_{\rm D}$ starts to decrease |

| $t_{\rm s}$ to $t_{\rm sw}$                             | $Z_{\rm D} = Z_{\rm D\_min}$<br>$V_{\rm D}(t) < \max(0.1 \times V_{\rm M}(t), 10 \text{ V})$                                                  |

Table 11 - Nominal mains voltage 277 V - Frequency 50 Hz or 60 Hz

| Time related to previous zero crossing of mains voltage | Phase-cut dimmer:<br>Impedance                                                                                                                 |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| $t_{\rm s}$ to $t_{\rm sw}$                             | $Z_{\rm D} = Z_{\rm D\_min}$ $V_{\rm D}(t) < \max(0.1 \times V_{\rm M}(t), \ 10 \ \rm V)$ NOTE At $t_{\rm s}$ , $Z_{\rm D}$ starts to decrease |

| $t_{\rm s}$ to $t_{\rm sw}$                             | $Z_{\rm D} = Z_{\rm D\_min}$<br>$V_{\rm D}(t) < \max(0.1 \times V_{\rm M}(t), 10 \text{ V})$                                                   |

#### 7.3.3 Electrical characteristics for trailing edge dimming method

#### 7.3.3.1 General

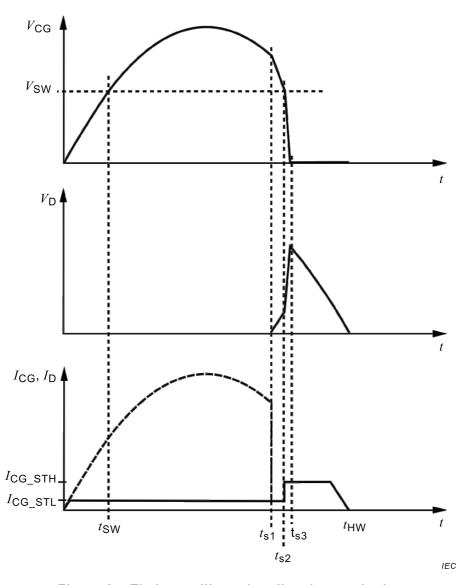

Starting from the mains zero crossing, the phase-cut dimmer operates in conducting state until its timing element deactivates the power switch at time  $t_{\rm S1}$ . Afterwards, the phase-cut dimmer is not significantly supplying power to the load for the entire remaining part of the mains half wave (see Figure 3).

To achieve synchronization with the mains and to control the phase-cut angle correctly, trailing edge phase-cut dimmers need to draw a current also during the non-conducting state.

Thus, the controlgear is able to conduct a current  $I_{\text{CG\_STH}}$ , which allows synchronization of the phase-cut dimmer with the mains and ensures the supply of power to the phase-cut dimmer even in a two-wire installation.

Since the negative voltage slope that is triggered by the switch-off of the power switch of the phase-cut dimmer is not only determined by the current  $I_{\text{CG\_STL}}$  that is conducted by the controlgear, but also by the effective capacitance of the wiring and the capacitance being effective in parallel to the phase-cut dimmer, the sum of these capacitances has to be considered.

This document and all listed values are based on systems having a maximum capacitance of the wiring of 10 nF being effective in parallel to the controlgear.

Figure 3 - Timing trailing edge dimming method

#### 7.3.3.2 Electrical characteristics during the conducting period

The conducting period starts at the zero crossing of the mains and ends at time  $t_{\rm S1}$  when the timing element of the phase-cut dimmer deactivates the power switch and the impedance of the phase-cut dimmer  $Z_{\rm D}$  increases towards  $Z_{\rm D-max}$ .

During the conducting period, the phase-cut dimmer should comply with the electrical characteristics listed in Table 12.

During this period, the phase-cut dimmer should continuously apply full power to the controlgear. Therefore, the impedance  $Z_{\rm D}$  of the phase-cut dimmer should remain continuously at its minimum value  $Z_{\rm D\_min}$ , independently from the current  $I_{\rm D}$  =  $I_{\rm CG}$ .

The impedance  $Z_{\rm D}$  of the phase-cut dimmer is  $Z_{\rm D\_min}$  when the voltage  $V_{\rm D}(t)$  across the phase-cut dimmer is less than 0,1 x  $V_{\rm M}(t)$  during the entire conduction period.

Due to the low impedance of the phase-cut dimmer during the conducting period, the input voltage of the controlgear is almost equal to the mains voltage.

From the zero crossing of the mains to time  $t_{\rm S1}$ , the controlgear provides a current path with a minimum current-carrying capability of  $I_{\rm CG-STL}$ .

Table 12 – Nominal mains voltage from 100 to 277 V – Frequency 50 Hz or 60 Hz

| Time related to previous zero crossing of mains voltage | Phase-cut dimmer:<br>Impedance                                             |

|---------------------------------------------------------|----------------------------------------------------------------------------|

| 0 to t <sub>s1</sub>                                    | $Z_{D} = Z_{D_{min}}$ $V_{D}(t) < \max(0,1 \times V_{M}(t), 10 \text{ V})$ |

# 7.3.3.3 Electrical characteristics during the transition from the conducting to the non-conducting period

The transition from the conducting to the non-conducting state of the phase-cut dimmer starts at time  $t_{s1}$  and ends at time  $t_{s3}$ .

At the time  $t_{\rm s1}$ , the impedance  $Z_{\rm D}$  of the phase-cut dimmer should start to increase towards  $Z_{\rm D\_max}$ . From time  $t_{\rm s1}$  to  $t_{\rm s2}$ , the phase-cut dimmer should limit the current  $I_{\rm D}$  to the value that is listed in Tables 13 to 17.

The minimum value for  $t_t = t_{s2} - t_{s1}$  should be as listed in Tables 13 to 17.

Since the controlgear provides a current path with a minimum current-carrying capability of  $I_{\text{CG\_STL}}$ , the voltage across the input terminals of the controlgear decreases towards zero and falls below the voltage  $V_{\text{SW}}$  at  $t_{\text{S2}}$  (see Figure 3).

NOTE 1 This requirement is to ensure that parasitic capacities of the installation, the active capacity  $C_{\rm f}$  between the terminals of the phase-cut dimmer (see Figure 3) and a capacitor that might be assembled inside the controlgear and that is connected directly with the mains terminals of the controlgear are discharged in a reasonable time to allow the phase-cut dimmer to supply itself sufficiently.

NOTE 2 The ratio between the values for the period  $t_{\rm s2}$  to  $t_{\rm HW}$  as given in Tables 13 to 17 for the different mains voltages is proportional to the ratio of the relevant mains voltages. The values for  $I_{\rm CG\_STH}$  scale inversely with the mains voltage. The value for  $I_{\rm D_nc}$  is always 10% lower than the relevant  $I_{\rm CG\_STH}$ .

The slew rate SR should be calculated based on the measurement of the voltage slope of  $V_{\rm CG}$  by measuring the time (dt) between  $V_{\rm CG}$  = 0,8 x  $V_{\rm CG}(t_{\rm S1})$  and  $V_{\rm CG}$  =  $V_{\rm SW}$  and by calculating the differential voltage d $V_{\rm CG}$  = 0,8 x  $V_{\rm CG}(t_{\rm S1})$  –  $V_{\rm SW}$ .

When the voltage  $V_{\rm CG}$  falls below  $V_{\rm SW}$  (time  $t_{\rm S2}$ ), the controlgear provides a current path with a minimum current-carrying capability of  $I_{\rm CG\_STH.}$

NOTE 3 The values for  $V_{\rm SW}$  and  $I_{\rm CG\_STH}$  are selected to achieve a good compromise between the ability of the phase-cut dimmer to supply itself on one side and the appearing power loss in the controlgear on the other side.

NOTE 4  $t_{\rm s2}$  is defined by the time at which  $V_{\rm CG}$  falls below  $V_{\rm SW}$ .  $V_{\rm CG}$  and  $I_{\rm D}$  can be measured simultaneously with a 4-channel oscilloscope, and the value of  $I_{\rm D}$  between  $t_{\rm S1}$  and  $t_{\rm S2}$  can be determined. The break in slope of  $V_{\rm D}$  at  $t_{\rm S2}$  (if such a break in slope exists) is not a criterion to define  $t_{\rm S2}$ .

Table 13 - Nominal mains voltage 100 V - Frequency 50 Hz or 60 Hz

| Time related to previous zero crossing of mains voltage             | Phase-cut dimmer:<br>Impedance                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $t_{s1}$ to $t_{s2}$                                                | $t = t_{s1}:$ $Z_{D} = Z_{D_{min}}$                                                                                                                                                                                                                                                                                                                 |

| $t_{s2} - t_{s1} \ge t_{t}$ $t_{t} = (1 / SR) \times V_{M}(t_{s1})$ | $\begin{array}{l} t=t_{\rm s1}:\\ Z_{\rm D}=Z_{\rm D\_min}\\ \\ t_{\rm s1} < t \leq t_{\rm s2}:\\ Z_{\rm D} \ {\rm increases} \ {\rm towards} \ Z_{\rm D\_max}\\ I_{\rm D} \leq (I_{\rm trans} \times P_{\rm min}) \ / \ {\rm W} \ {\rm with} \ dV_{\rm D}/dt \leq \\ 0.09 \ {\rm V/\mu s} \ {\rm and} \\ I_{\rm trans}=2.8 \ {\rm mA} \end{array}$ |

| $t_{s2}$ to $t_{HW}$                                                | $P_{\min} < 12 \text{ W}$ : $I_{D}(t) \le I_{D-nc} = n \times 12.4 \text{ mA/W} \times P_{\min}$ $P_{\min} \ge 12 \text{ W}$ : $I_{D}(t) \le I_{D-nc} = n \times 149 \text{ mA}$                                                                                                                                                                    |

Table 14 - Nominal mains voltage 120 V - Frequency 50 Hz or 60 Hz

| Time related to previous zero crossing of mains voltage             | Phase-cut dimmer:<br>Impedance                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $t_{s1}$ to $t_{s2}$                                                | $t = t_{s1}:$ $Z_{D} = Z_{D_{min}}$                                                                                                                                                                                                                                                                                                                                                        |

| $t_{s2} - t_{s1} \ge t_{t}$ $t_{t} = (1 / SR) \times V_{M}(t_{s1})$ | $\begin{array}{l} t = t_{\text{s1}}\text{:}\\ Z_{\text{D}} = Z_{\text{D_min}}\\ \\ t_{\text{s1}} < t \leq t_{\text{s2}}\text{:}\\ Z_{\text{D}} \text{ increases towards } Z_{\text{D_max}}\\ I_{\text{D}} \leq (I_{\text{trans}} \times P_{\text{min}}) \ / \ \text{W with } dV_{\text{D}}/\ dt \leq \\ 0,105 \ \text{V/}\mu\text{s and}\\ I_{\text{trans}} = 2,3 \ \text{mA} \end{array}$ |

| $t_{s2}$ to $t_{HW}$                                                | $P_{\min} < 12 \text{ W}$ :<br>$I_{D}(t) \le I_{D-nc} = n \times 10,4 \text{-mA/W} \times P_{\min}$<br>$P_{\min} \ge 12 \text{ W}$ :<br>$I_{D}(t) \le I_{D-nc} = n \times 124,2 \text{ mA}$                                                                                                                                                                                                |

Table 15 - Nominal mains voltage 200 V - Frequency 50 Hz or 60 Hz

| Time related to previous zero crossing of mains voltage            | Phase-cut dimmer:<br>Impedance                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $t_{s1}$ to $t_{s2}$                                               | $t = t_{s1}:$ $Z_{D} = Z_{D_{min}}$                                                                                                                                                                                                                                                                                                                                                    |

| $t_{s2} - t_{s1} \ge t_{t}$ $t_{t} = (1 / SR) \cdot V_{M}(t_{s1})$ | $\begin{array}{l} t = t_{\text{s1}} \\ Z_{\text{D}} = Z_{\text{D_min}} \\ \\ t_{\text{s1}} < t \leq t_{\text{s2}} \\ Z_{\text{D}} \text{ increases towards } Z_{\text{D_max}} \\ I_{\text{D}}(t) \leq \left(I_{\text{trans}} \times P_{\text{min}}\right) / \text{ W with } dV_{\text{D}}/dt \leq \\ 0,175 \text{ V/}\mu\text{s and} \\ I_{\text{trans}} = 1,4 \text{ mA} \end{array}$ |

| $t_{s2}$ to $t_{HW}$                                               | $P_{\min} < 12 \text{ W}$ :<br>$I_{D}(t) \le I_{D-nc} = n \times 6,2 \text{ mA/W} \times P_{\min}$<br>$P_{\min} \ge 12 \text{ W}$ :<br>$I_{D}(t) \le I_{D-nc} = n \times 74,5 \text{ mA}$                                                                                                                                                                                              |

Table 16 - Nominal mains voltage 230 V - Frequency 50 Hz or 60 Hz

| Time related to previous zero crossing of mains voltage            | Phase-cut dimmer:<br>Impedance                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $t_{s1}$ to $t_{s2}$                                               | $t = t_{s1};$ $Z_{D} = Z_{D_{min}}$                                                                                                                                                                                                                                                                                                                                                        |

| $t_{s2} - t_{s1} \ge t_{t}$ $t_{t} = (1 / SR) \cdot V_{M}(t_{s1})$ | $\begin{array}{l} t = t_{\text{S1}} : \\ Z_{\text{D}} = Z_{\text{D\_min}} \\ \\ t_{\text{S1}} < t \leq t_{\text{S2}} : \\ Z_{\text{D}} \text{ increases towards } Z_{\text{D\_max}} \\ I_{\text{D}}(t) \leq (I_{\text{trans}} \times P_{\text{min}}) \ / \ \text{W with } dV_{\text{D}} / \ dt \leq \\ 0.2 \ \text{V/} \mu \text{s and} \\ I_{\text{trans}} = 1,2 \ \text{mA} \end{array}$ |

| $t_{\rm s2}$ to $t_{\rm HW}$                                       | $P_{\min} < 12 \text{ W}$ : $I_{D}(t) \le I_{D-nc} = n \times 5,4 \text{ mA/W} \times P_{\min}$ $P_{\min} \ge 12 \text{ W}$ : $I_{D}(t) \le I_{D-nc} = n \times 65 \text{ mA}$                                                                                                                                                                                                             |

Table 17 - Nominal mains voltage 277 V - Frequency 50 Hz or 60 Hz

| Time related to previous zero crossing of mains voltage            | Phase-cut dimmer:<br>Impedance                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $t_{s1}$ to $t_{s2}$                                               | $t = t_{s1}:$ $Z_{D} = Z_{D_{min}}$                                                                                                                                                                                                                                                                                                                                     |

| $t_{s2} - t_{s1} \ge t_{t}$ $t_{t} = (1 / SR) \cdot V_{M}(t_{s1})$ | $\begin{array}{l} t = t_{\rm s1}: \\ Z_{\rm D} = Z_{\rm D\_min} \\ \\ t_{\rm s1} < t \leq t_{\rm s2}: \\ Z_{\rm D} \ {\rm increases} \ {\rm towards} \ Z_{\rm D\_max} \\ I_{\rm D}(t) \leq \left(I_{\rm trans} \ge P_{\rm min}\right) / \ {\rm W} \ {\rm with} \ dV_{\rm D}/dt \leq \\ 0.245 \ {\rm V/\mu s} \ {\rm and} \\ I_{\rm trans} = 1.0 \ {\rm mA} \end{array}$ |

| $t_{s2}$ to $t_{HW}$                                               | $P_{\min} < 12 \text{ W}$ : $I_{D}(t) \le I_{D-nc} = n \times 4,5 \text{ mA/W} \times P_{\min}$ $P_{\min} \ge 12 \text{ W}$ : $I_{D}(t) \le I_{D-nc} = n \times 54 \text{ mA}$                                                                                                                                                                                          |

#### 7.3.3.4 Electrical characteristics during the non-conducting period

During the non-conducting period, the phase-cut dimmer should comply with the electrical characteristics listed in Tables 13 to 17.

The non-conducting period ends at the next zero crossing of the mains at time  $t_{HW}$ .

During this period, the controlgear provides a current path with a minimum current-carrying capability of  $I_{\rm CG\ STH}$ . At small input voltages of the controlgear when  $I_{\rm CG\ STH}$  cannot be reached due to the characteristics of its input circuitry (e.g. inrush current limiting elements), only its impedance  $Z_{\rm CG}$  is defined.

During this period, the phase-cut dimmer should limit the current  $I_{\rm D}$  to n x  $I_{\rm D\_nc}$  as listed in Tables 13 to 17, whereby  $I_{\rm D\_nc}$  is related to  $P_{\rm min}$  of the phase-cut dimmer.

The controlgear may deactivate its current-carrying capability during the non-conducting period after it has not detected an input voltage waveform showing trailing edge characteristics for 100 ms.

NOTE This is for reducing power losses in case a controlgear is used without a phase-cut dimmer.

#### 7.4 Electrical characteristics during the off state of a lighting system

The off state of a lighting system is when no lamp connected with a controlgear is emitting light.

To set a controlgear in the off state, the phase-cut dimmer should increase its impedance  $Z_D$  until the controlgear is not sufficiently supplied with power to operate the lamp.

A phase-cut dimmer that needs no supply during the off state of all connected controlgear may open the current loop of the system, for example by means of a mechanical switch.

A phase-cut dimmer that needs a power supply also during the off state of all connected controlgear requires that the connected controlgear provide a current path, although no lamp is operated (electronic off state), in order to provide power to the electronic circuits within the dimmer to enable returning to the on-state when demanded.

If none of the connected controlgear is able to provide the current carrying capability due to insufficient power, the impedance  $Z_{\rm CG}$  of the controlgear will increase.

The phase-cut dimmer may reduce its impedance  $Z_{\rm D}$  to supply power to the connected controlgear in order to reestablish a current carrying capability that carries the needed supply current  $I_{\rm D}$  nc.

By reducing  $Z_{\rm D}$ , the voltage  $V_{\rm D}$  will decrease and the voltage  $V_{\rm CG}$  will increase, thus all connected controlgear is energized and the requested current path is generated in the system to carry the required supply current  $I_{\rm D}$  of the phase-cut dimmer.

The controlgear provides a minimum current carrying capability of  $I_{PO}$  when the voltage  $V_{CG}$  is in the range of  $V_{PO}$  to  $V_{SW}$  (see Table 18). For voltages  $V_{CG}$  smaller than  $V_{PO}$  and higher than  $V_{SW}$ , the current carrying capability of the controlgear is not defined.

The controlgear does not operate the lamp when the voltage  $V_{\rm CG}$  is below  $V_{\rm SW}$ , so no light is emitted.

The phase-cut dimmer should limit the current to a level that ensures that the voltage  $V_{\rm CG}$  that is applied to the controlgear does not exceed  $V_{\rm SW}$ .

Table 18 - Currents and voltages for controlgear during the electronic off state

| $V_{M}\left[V\right]$ | 100 | 120 | 200 | 230 | 277 |

|-----------------------|-----|-----|-----|-----|-----|

| V <sub>PO</sub> [V]   | 15  | 15  | 30  | 30  | 30  |

| I <sub>PO</sub> [mA]  | 20  | 20  | 10  | 10  | 10  |

| $I_{PO\_rms}  [mA]$   | 8   | 8   | 4   | 4   | 4   |

Values for voltages and currents are instantaneous values except  $I_{\rm PO\ rms}.$

#### 8 Test procedures

#### 8.1 General

Devices supporting leading and trailing edge operation such as so called universal phase-cut dimmers should be tested for both operation modes.

To simplify the description of the test setups and the test procedures, testing conditions for dimmers related to specific moments in time are defined in degree phase angle related to the mains zero crossings. Thus, a definition of different values for the moments in time such as, for example,  $t_{\rm S1}$ ,  $t_{\rm S2}$  or  $t_{\rm HW}$  is not necessary for different mains frequencies.

To test the phase-cut dimmer, in some tests equivalent controlgear (EC\_CG) should be used as indicated. This EC CG should be constructed as shown in Annex A.

$V_{\mathsf{M}}$  [V] 100 120 200 230 277  $V_{\rm M}^2$  $V_{\rm M}^2$  $V_{\rm M}^2$  $V_{\rm M}^2$  $V_{\rm M}^2$  $R_{\mathsf{R}}$  $^\prime P_{\sf max}$  $^\prime P_{\sf max}$  $P_{\mathsf{max}}$  $P_{\mathsf{max}}$  $P_{\mathsf{max}}$ 0 to 23 0 to 23 0 to 45 0 to 45 0 to 45  $V_{\mathsf{test}}\left[\mathsf{V}\right]$  $V_1$  [V] 8 8 8 8 8  $SR_{L}$  [V/ $\mu$ s] Refers to Table 6 90°  $\beta_{L}$ 120°  $SR_{T}$  [V/ms] 200 200 200 200 200 120°  $\alpha_T$

Table 19 - Parameters for testing purposes

#### 8.2 Tests for leading edge phase-cut dimmers

#### 8.2.1 General

Tests concerning electrical characteristics should ensure compliance of devices with this document in terms of electrical behavior of phase-cut dimmers during different periods of the mains waveform according to 7.3.2.

#### 8.2.2 Test related to the non-conducting phase

For this test, there are 2 different methods of testing the phase-cut dimmer current. Only one of these methods needs to be used when performing this test.

#### Method 1

A test circuit as shown in Figure 4 should be used to test the properties of the phase-cut dimmer during the non-conducting phase. The resistance of the resistor  $R_{\rm R}$  should be chosen according to Table 19.

Figure 4 – Circuit to test the properties of the phase-cut dimmer during the non-conducting phase (Method 1)

#### Pre-condition:

Control device applied to an AC test voltage source ( $V_{\rm ME}$ ) providing the relevant mains voltage according to Clause A.3 with the values of  $V_{\rm 1}$ ,  $\beta_{\rm L}$  and  $SR_{\rm T}$  as given in Table 19. Switch S1 is open. Adjust the phase-cut dimmer so that the switch in the phase-cut dimmer is switched on at the time  $t_{\rm S}$  ( $\beta$ 1). Close switch S1.

If necessary for the function of the phase-cut dimmer, apply for one minute the mains voltage  $V_{\rm M}$  (e.g. for the calibration of universal phase-cut dimmer). Adjust the phase-cut dimmer close to the phase angle of  $t_{\rm S}$ . S1 is opened in this phase. Change  $V_{\rm M}$  to  $V_{\rm ME}$  (according to Clause A.3) and close S1.

Time related to last zero crossing: 0 to  $t_s$

Test: Measure  $I_{\mathsf{D}}$

Expected result:

$I_{\rm D} \le I_{\rm D\_nc}$  as listed in Tables 1 to 5

$(I_{\rm D\_nc}$  depends on  $P_{\rm min}$  and n given by the specification of the manufacturer)

To keep the test as simple as possible, the dimmer is connected to a test voltage which represents the voltage across the dimmer.

This test method covers the worst case scenario by using the worst controlgear, without having any parasitic effects caused by synthetic loads.

Therefore the voltage across the dimmer looks like a trailing edge waveform.

To reduce the influence on the current through the load taken by the dimmer, the impedance of the test voltage source should be as low as possible.

Due to the overcurrent protection of the dimmer, S1 is closed after the test voltage has been applied to the dimmer.

#### Method 2

Applicable test circuit, see Figure 5.

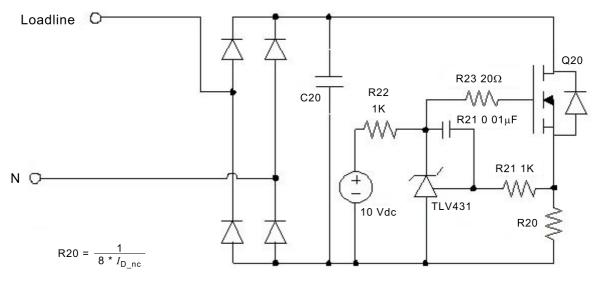

Figure 5 – Circuit to test the properties of the phase-cut dimmer during the non-conducting phase (Method 2)

Pre-condition:

Phase-cut dimmer loaded with the circuit of Figure B.1, system powered with relevant mains voltage. Values of R20 and C20 should be set according to Annex B using the values of  $I_{D_n}$  given in Tables 1 to 5.

Time related to last zero crossing: 0 to  $t_s$

Test: Measure  $I_{\mathsf{D}}$

Expected result:

$I_{\rm D} \leq I_{\rm D\_nc}$  as listed in Tables 1 to 5

$(I_{\mathrm{D}\ \mathrm{nc}}$  depends on the  $P_{\mathrm{min}}$  and n given by the specification of the manufacturer)

### 8.2.3 Test related to the transition from the non-conducting to the conducting phase

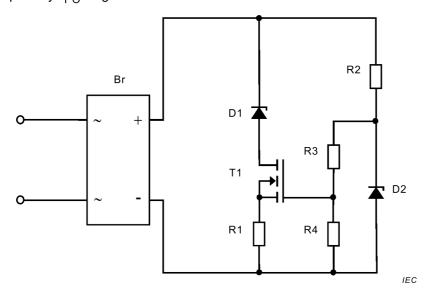

A test circuit as shown in Figure 6 should be used to test the phase-cut dimmer's properties during the transition from the non-conducting to the conducting phase.

Figure 6 – Circuit to test the properties of the phase-cut dimmer during the transition from the non-conducting to the conducting phase

#### Pre-condition:

Phase-cut dimmer loaded with a resistive load R having a maximum resistance  $R_R$  (see Table 19) as shown in Figure 6, system powered with relevant mains voltage, phase-cut dimmer adjusted to the conduction angle of  $90^{\circ}$ .

Time related to last zero crossing:  $t_s$

Test: Measure  $V_D$  or voltage across resistor R over time

Expected result:

Absolute value of voltage slope across the DUT ( $V_{

m D}$ ) or R does not exceed the limits given in Table 6.

#### 8.2.4 Test related to the conducting phase

A test circuit as shown in Figure 6 should be used to test the phase-cut dimmer's properties during the conducting phase.

#### Pre-condition:

A phase-cut dimmer loaded with a resistive load R having a maximum resistance  $R_R$  (see Table 19) as shown in Figure 6, system powered with relevant mains voltage, phase-cut dimmer adjusted to the conduction angle of  $120^{\circ}$

This test should be performed for the minimum and maximum load, such as  $R_{\rm Rmax}$  ( $V_{\rm M}^2/P_{\rm max}$ ) and  $R_{\rm Rmin}$  ( $V_{\rm M}^2/P_{\rm min}$ )

Time related to last zero crossing:  $t_{\rm S}$  to  $t_{\rm HW}$

Test: Measure  $V_{\mathsf{D}}$  over time

Expected result for  $V_{\rm M}(t) > 11$ V:

$V_{\rm D}(t) < \max(0.1 \text{ x } V_{\rm M}(t), 10 \text{V})$

#### 8.3 Tests for trailing edge phase-cut dimmers

#### 8.3.1 General

Tests concerning the electrical characteristics should ensure compliance of devices with this document in terms of electrical behavior of phase-cut dimmers during different periods of the mains waveform according to 7.3.3.

#### 8.3.2 Test related to the conducting phase

Applicable test circuit, see Figure 6.

#### Pre-condition:

Phase-cut dimmer loaded with a resistive load having a maximum resistance  $R_{\rm R}$  (see Table 7), system powered with relevant mains voltage, phase-cut dimmer adjusted to the conduction angle of 120°.

This test should be performed for the minimum and maximum load, such as  $R_{\rm Rmax}$  ( $V_{\rm M}^{~2}/P_{\rm max}$ ) and  $R_{\rm Rmin}$  ( $V_{\rm M}^{~2}/P_{\rm min}$ )

Time related to last zero crossing: 0 to  $t_{\rm s1}$

Test: Measure  $V_D$  over time

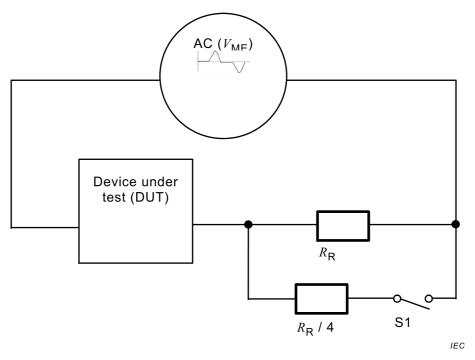

Expected result for  $V_{M}(t) > 11V$ :