Edition 1.0 2015-03

# TECHNICAL SPECIFICATION

# SPECIFICATION TECHNIQUE

Device embedded substrate – Part 2-3: Guidelines – Design guide

Substrat avec appareil(s) intégré(s) – Partie 2-3: Directives – Guide de conception

# THIS PUBLICATION IS COPYRIGHT PROTECTED Copyright © 2015 IEC, Geneva, Switzerland

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from either IEC or IEC's member National Committee in the country of the requester. If you have any questions about IEC copyright or have an enquiry about obtaining additional rights to this publication, please contact the address below or your local IEC member National Committee for further information.

Droits de reproduction réservés. Sauf indication contraire, aucune partie de cette publication ne peut être reproduite ni utilisée sous quelque forme que ce soit et par aucun procédé, électronique ou mécanique, y compris la photocopie et les microfilms, sans l'accord écrit de l'IEC ou du Comité national de l'IEC du pays du demandeur. Si vous avez des questions sur le copyright de l'IEC ou si vous désirez obtenir des droits supplémentaires sur cette publication, utilisez les coordonnées ci-après ou contactez le Comité national de l'IEC de votre pays de résidence.

IEC Central Office

Tel.: +41 22 919 02 11

3, rue de Varembé

Fax: +41 22 919 03 00

CH-1211 Geneva 20 info@iec.ch Switzerland www.iec.ch

#### About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes International Standards for all electrical, electronic and related technologies.

#### About IEC publications

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the latest edition, a corrigenda or an amendment might have been published.

#### IEC Catalogue - webstore.iec.ch/catalogue

The stand-alone application for consulting the entire bibliographical information on IEC International Standards, Technical Specifications, Technical Reports and other documents. Available for PC, Mac OS, Android Tablets and iPad

#### IEC publications search - www.iec.ch/searchpub

The advanced search enables to find IEC publications by a variety of criteria (reference number, text, technical committee,...). It also gives information on projects, replaced and withdrawn publications.

# IEC Just Published - webstore.iec.ch/justpublished

Stay up to date on all new IEC publications. Just Published details all new publications released. Available online and also once a month by email.

#### Electropedia - www.electropedia.org

The world's leading online dictionary of electronic and electrical terms containing more than 30 000 terms and definitions in English and French, with equivalent terms in 15 additional languages. Also known as the International Electrotechnical Vocabulary (IEV) online.

# IEC Glossary - std.iec.ch/glossary

More than 60 000 electrotechnical terminology entries in English and French extracted from the Terms and Definitions clause of IEC publications issued since 2002. Some entries have been collected from earlier publications of IEC TC 37, 77, 86 and CISPR.

#### IEC Customer Service Centre - webstore.iec.ch/csc

If you wish to give us your feedback on this publication or need further assistance, please contact the Customer Service Centre: csc@iec.ch.

#### A propos de l'IEC

La Commission Electrotechnique Internationale (IEC) est la première organisation mondiale qui élabore et publie des Normes internationales pour tout ce qui a trait à l'électricité, à l'électronique et aux technologies apparentées.

#### A propos des publications IEC

Le contenu technique des publications IEC est constamment revu. Veuillez vous assurer que vous possédez l'édition la plus récente, un corrigendum ou amendement peut avoir été publié.

#### Catalogue IEC - webstore.iec.ch/catalogue

Application autonome pour consulter tous les renseignements bibliographiques sur les Normes internationales, Spécifications techniques, Rapports techniques et autres documents de l'IEC. Disponible pour PC, Mac OS, tablettes Android et iPad.

### Recherche de publications IEC - www.iec.ch/searchpub

La recherche avancée permet de trouver des publications IEC en utilisant différents critères (numéro de référence, texte, comité d'études,...). Elle donne aussi des informations sur les projets et les publications remplacées ou retirées.

#### IEC Just Published - webstore.iec.ch/justpublished

Restez informé sur les nouvelles publications IEC. Just Published détaille les nouvelles publications parues. Disponible en ligne et aussi une fois par mois par email.

#### Electropedia - www.electropedia.org

Le premier dictionnaire en ligne de termes électroniques et électriques. Il contient plus de 30 000 termes et définitions en anglais et en français, ainsi que les termes équivalents dans 15 langues additionnelles. Egalement appelé Vocabulaire Electrotechnique International (IEV) en ligne.

#### Glossaire IEC - std.iec.ch/glossary

Plus de 60 000 entrées terminologiques électrotechniques, en anglais et en français, extraites des articles Termes et Définitions des publications IEC parues depuis 2002. Plus certaines entrées antérieures extraites des publications des CE 37, 77, 86 et CISPR de l'IEC.

#### Service Clients - webstore.iec.ch/csc

Si vous désirez nous donner des commentaires sur cette publication ou si vous avez des questions contactez-nous: csc@iec.ch.

Edition 1.0 2015-03

# TECHNICAL SPECIFICATION

# SPECIFICATION TECHNIQUE

Device embedded substrate – Part 2-3: Guidelines – Design guide

Substrat avec appareil(s) intégré(s) – Partie 2-3: Directives – Guide de conception

INTERNATIONAL ELECTROTECHNICAL COMMISSION

COMMISSION ELECTROTECHNIQUE INTERNATIONALE

ICS 31.180; 31.190 ISBN 978-2-8322-2403-8

Warning! Make sure that you obtained this publication from an authorized distributor.

Attention! Veuillez vous assurer que vous avez obtenu cette publication via un distributeur agréé.

# CONTENTS

| FOREWORD                                                                            | 4  |

|-------------------------------------------------------------------------------------|----|

| INTRODUCTION                                                                        | 6  |

| 1 Scope                                                                             | 7  |

| 2 Normative references                                                              | 7  |

| 3 Terms, definition and abbreviations                                               | 7  |

| 3.1 Terms and definitions                                                           | 7  |

| 3.2 Abbreviations                                                                   | 7  |

| 4 Structure of device embedded substrates                                           | 8  |

| 4.1 General                                                                         | 8  |

| 4.2 Specification of the top and bottom surfaces of a device embedded substrate     |    |

| 4.3 Definition of layers of a device embedded substrate                             |    |

| 4.4 Conductor spacing at a terminal                                                 |    |

| 5 Conditions to prepare base and embedding devices                                  |    |

| 5.1 Conditions for base                                                             |    |

| 5.2 Conditions for embedding devices                                                |    |

| 6 Recommendation for embedding devices                                              |    |

| 7 Design specification of device embedded substrate                                 |    |

| 7.1 General                                                                         |    |

| 7.2 Items to be included in the design specification                                |    |

| 7.2.2 Design specification template                                                 |    |

| Bibliography                                                                        |    |

|                                                                                     |    |

| Figure 1 – Definition of top and bottom surfaces of a device embedded substrate     | 8  |

| Figure 2 – Definition of top and bottom surfaces for mounting on a mother board     | 9  |

| Figure 3 – Names of layers in pad connection                                        | 9  |

| Figure 4 – Additional information concerning the interconnection position           | 10 |

| Figure 5 – Names of layers in via connection [I]                                    |    |

| Figure 6 – Names of layers in via connection [II]                                   |    |

| Figure 7 – Names of layers in via connection [III]                                  |    |

| Figure 8 – Definitions of dielectric gap and layer gap in the pad connection method |    |

| Figure 9 – Definitions of dielectric gap and layer gap in the via connection method |    |

| Figure 10 – Additional illustration of dielectric gap                               |    |

|                                                                                     |    |

| Figure 11 – Additional illustration of layer gap                                    |    |

| Figure 12 – Additional drawing                                                      |    |

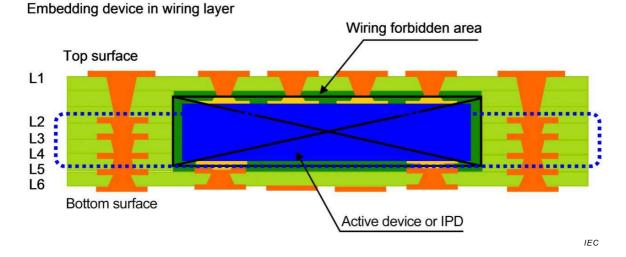

| Figure 13 – Forbidden wiring area                                                   | 20 |

| Table 1 – Name of layers of device embedded board                                   | 12 |

| Table 2 – Recommendation for device assembly to base substrate for device           | 12 |

| embedded boards                                                                     | 15 |

| Table 3 – Embedding recommendation                                                  | 16 |

| Table 4 – Mounting methods of semiconductor devices    | 17 |

|--------------------------------------------------------|----|

| Table 5 – Embedding device                             | 18 |

| Table 6 – Specification of device embedded substrate 1 | 21 |

| Table 7 – Specification of device embedded substrate 2 | 22 |

| Table 8 – Specification of device embedded substrate 3 | 23 |

# INTERNATIONAL ELECTROTECHNICAL COMMISSION

#### **DEVICE EMBEDDED SUBSTRATE -**

# Part 2-3: Guidelines – Design guide

# **FOREWORD**

- 1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as "IEC Publication(s)"). Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely with the International Organization for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- 2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC National Committees.

- 3) IEC Publications have the form of recommendations for international use and are accepted by IEC National Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

- 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter.

- 5) IEC itself does not provide any attestation of conformity. Independent certification bodies provide conformity assessment services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any services carried out by independent certification bodies.

- 6) All users should ensure that they have the latest edition of this publication.

- 7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and members of its technical committees and IEC National Committees for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC Publications.

- 8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.

- 9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

The main task of IEC technical committees is to prepare International Standards. In exceptional circumstances, a technical committee may propose the publication of a Technical Specification when

- the required support cannot be obtained for the publication of an International Standard, despite repeated efforts, or

- the subject is still under technical development or where, for any other reason, there is the future but no immediate possibility of an agreement on an International Standard.

Technical Specifications are subject to review within three years of publication to decide whether they can be transformed into International Standards.

IEC TS 62878-2-3, which is a Technical Specification, has been prepared by IEC technical committee 91: Electronics assembly technology.

The text of this Technical Specification is based on the following documents:

| Enquiry draft | Report on voting |

|---------------|------------------|

| 91/1143/DTS   | 91/1164A/RVC     |

Full information on the voting for the approval of this Technical Specification can be found in the report on voting indicated in the above table.

A list of all parts in the IEC 62878 series, published under the general title *Device embedded substrate*, can be found on the IEC website.

This publication has been drafted in accordance with the ISO/IEC Directives, Part 2.

The committee has decided that the contents of this publication will remain unchanged until the stability date indicated on the IEC website under "http://webstore.iec.ch" in the data related to the specific publication. At this date, the publication will be

- transformed into an International standard,

- reconfirmed,

- withdrawn,

- · replaced by a revised edition, or

- · amended.

IMPORTANT – The 'colour inside' logo on the cover page of this publication indicates that it contains colours which are considered to be useful for the correct understanding of its contents. Users should therefore print this document using a colour printer.

#### INTRODUCTION

This part of IEC 62878 provides guidance with respect to device embedded substrate, fabricated by embedding discrete active and passive electronic devices into one or multiple inner layers of a substrate with electric connections by means of vias, conductor plating, conductive paste, and printing. Within the IEC 62878 series,

- IEC 62878-1-1 specifies the test methods,

- IEC TS 62878-2-1 gives a general description of the technology,

- IEC TS 62878-2-3, provides guidance on design, and

- IEC TS 62878-2-4 specifies the test element groups.

The device embedded substrate may be used as a substrate to mount SMDs to form electronic circuits, as conductor and insulator layers may be formed after embedding electronic devices.

The purpose of the IEC 62878 series is to achieve a common understanding with respect to structures, test methods, design and fabrication processes and the use of the device embedded substrate in industry.

#### **DEVICE EMBEDDED SUBSTRATE -**

# Part 2-3: Guidelines – Design guide

#### 1 Scope

This part of IEC 62878 describes the design guide of device embedded substrates.

The design guide of device embedded substrate is essentially the same as that of various electronic circuit boards. This part of IEC 62878 enables a thorough understanding of circuit design, structure design, board design, board manufacturing, jisso (assembly processes) and tests of products.

This part of IEC 62878 is applicable to device embedded substrates fabricated by use of organic base material, which include for example active or passive devices, discrete components formed in the fabrication process of electronic wiring board, and sheet formed components.

The IEC 62878 series neither applies to the re-distribution layer (RDL) nor to the electronic modules defined as an M-type business model in IEC 62421.

#### 2 Normative references

The following documents, in whole or in part, are normatively referenced in this document and are indispensable for its application. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

IEC 60194, Printed board design, manufacture and assembly – Terms and definitions

### 3 Terms, definition and abbreviations

#### 3.1 Terms and definitions

For the purposes of this document, the terms and definitions given in IEC 60194 apply.

#### 3.2 Abbreviations

| AABUS | as agreed between user and supplier |

|-------|-------------------------------------|

| BGA   | ball grid array                     |

| IPD   | integrated passive device           |

| LGA   | land grid array                     |

| LSI   | large scale integration             |

| MEMS  | micro electro mechanical systems    |

| OSP   | organic solderability preservative  |

| SMD   | surface mount device                |

| TAB   | tape automated bonding              |

| WLP   | wafer level package                 |

#### 4 Structure of device embedded substrates

#### 4.1 General

The name of each part of a device embedded substrate is specified in Clause 4 to assist technical understanding of the structure and to avoid misinterpretation by engineers working in the relevant industry sectors.

# 4.2 Specification of the top and bottom surfaces of a device embedded substrate

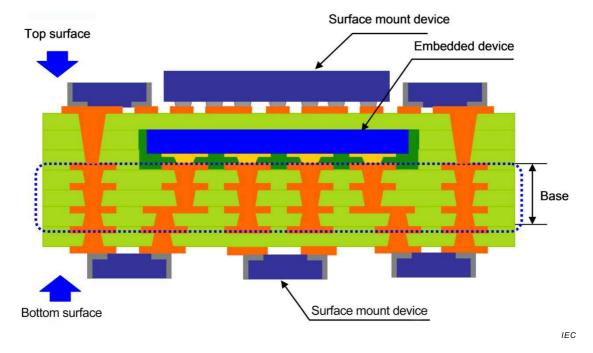

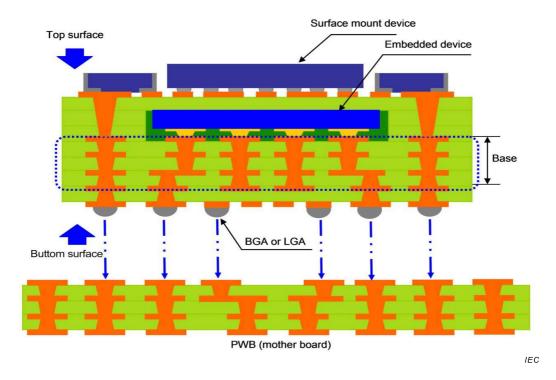

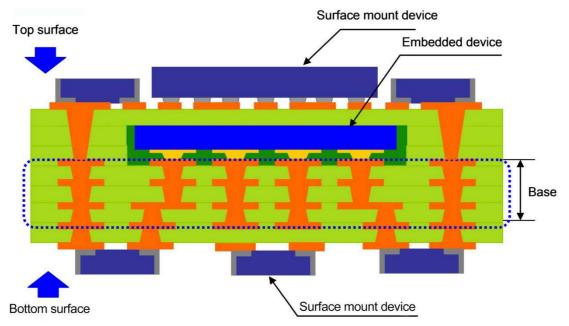

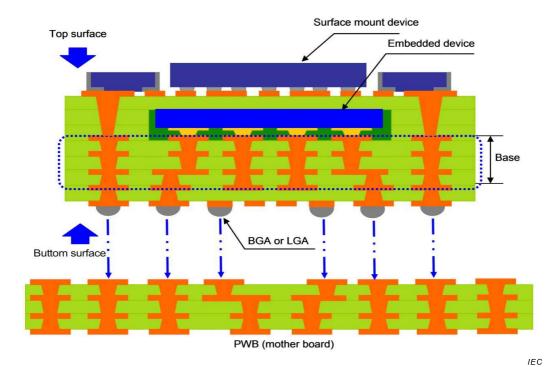

The definition of the top and bottom surfaces of a device embedded substrate depends on the number of devices mounted on the surface of the substrate, as shown in Figure 1. The surface on which more components are mounted is the top surface. If a substrate is mounted on a printed wiring board (hereafter referred to as mother board), the surface of the substrate connecting to the wiring board is defined as the bottom surface even if it contains more input/output terminals (pads) (see Figure 2). If the design of the top and bottom surfaces has been AABUS, this agreement takes priority, even if it differs from the definition stated in this part of IEC 62878.

Figure 1 – Definition of top and bottom surfaces of a device embedded substrate

Converget International Electrotechnical Commission

Figure 2 – Definition of top and bottom surfaces for mounting on a mother board

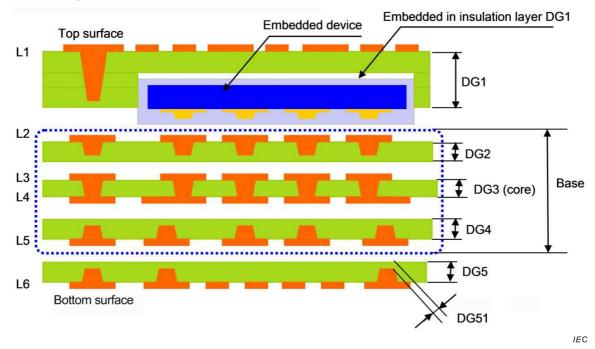

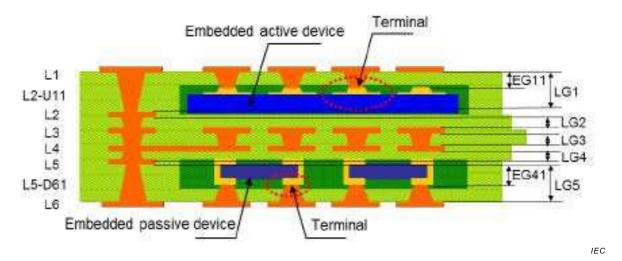

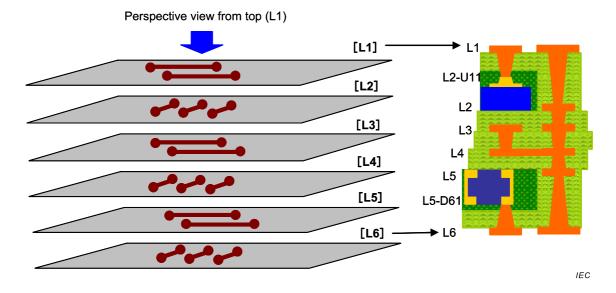

# 4.3 Definition of layers of a device embedded substrate

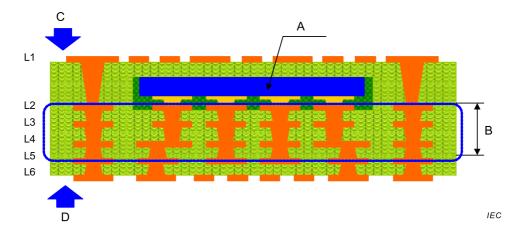

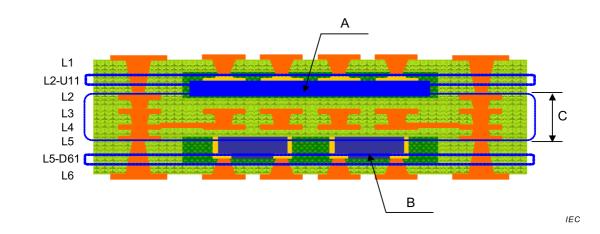

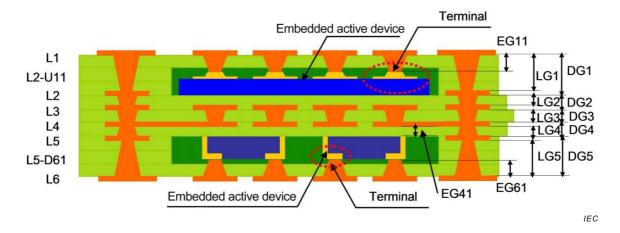

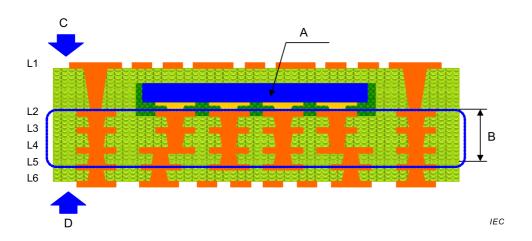

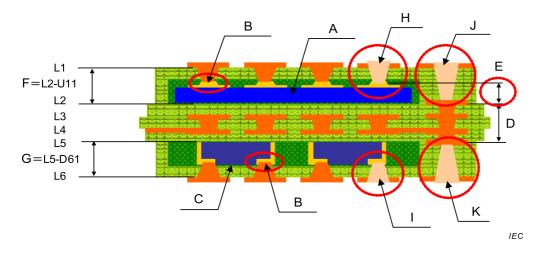

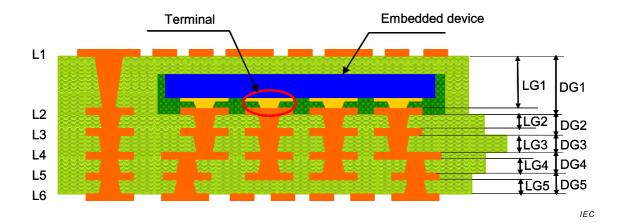

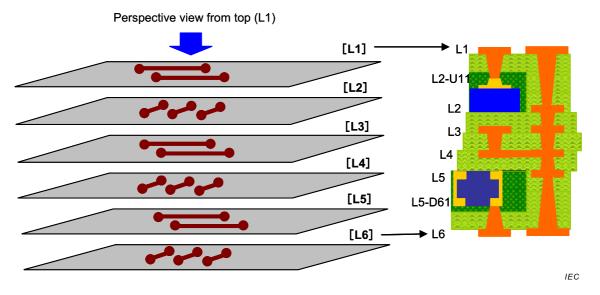

Names and symbols of layers in a device embedded board are illustrated in Figure 3. Each layer is numbered as L1, L2 to L6 (in case of 6 layers) from the top surface. The number indicates the order of the layer with respect to the top surface.

# Key

| Α | Embedded component | С | Top surface    |

|---|--------------------|---|----------------|

| В | Base               | D | Bottom surface |

Figure 3 - Names of layers in pad connection

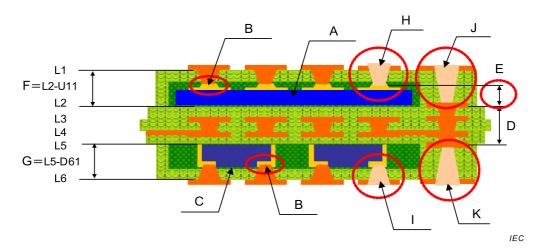

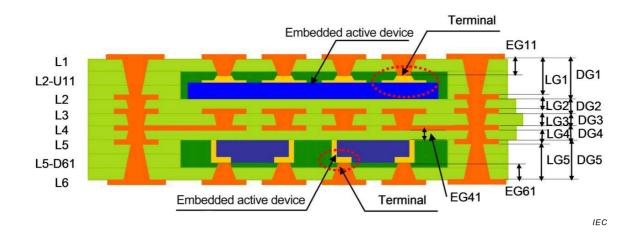

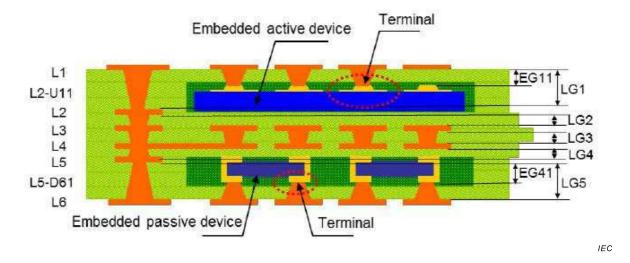

In the case of via connection, the position of connecting terminals of the embedded device is different from the surrounding layer number. The component symbol and connecting position(s) are defined as illustrated in Figure 4 in order to clarify the interconnecting positions of the embedded device and of its electrical terminals with respect to construction design, pattern design, board fabrication and jisso (assembly).

It is recommended to use the component symbols and names as shown in a circuit diagram to use 2 to 4 indications. The position of interconnection in the case of die-bonding or mounting

of a device embedded device may be expressed using another name in addition to the name of the layer in which the device is embedded.

The surface of a device is upward facing. Use upward (U) when connecting terminals are in the upward facing surface, and downward (D) when the terminals are in the downward facing surface.

A three digit number is used if multiple components are embedded and/or multiple connection terminals are in the same layer. The left side number indicates the interconnecting layer number and the right side number indicates the layer position of the embedded component. If there are multiple layers involved, numbers 1, 2 indicate the layers from the top for upward and numbers 1, 2 indicate the layers from the bottom for downward. The second number may be omitted if there is only one embedded component in a layer. See the example in Figure 4.

Figure 4 shows additional information on the interconnection position. The active device is mounted on the L2 layer and connected to the first layer with upward direction. In this case the name of the interconnection layer is expressed as L2-U11. The last digit 1 indicates the number of the embedded component. Passive components mounted on the L5 layer are connected to L6 with downward direction. In this case, the name of the interconnection layer is expressed as L5-D61.

A virtual layer is used as a virtual conductor layer and as the connecting points. The terminal connection design of an embedded device is carried out by first establishing the connection and hole machining data A and B, then the connection and hole machining data C and D for L2 and L5 (in the case of the above structure). The terminal setting may be omitted if a via connection and the positions of embedded device terminals and the conduction layer are the same.

| А | Embedded active device              | G | Name of the layer between L5 and L6                               |

|---|-------------------------------------|---|-------------------------------------------------------------------|

| В | Connecting terminal                 | Н | Connection and machining data from L1 to a virtual layer (L2-U11) |

| С | Embedded passive device             | 1 | Connection and machining data from L6 to a virtual layer (L5-D61) |

| D | Base                                | J | Connection and machining data from L1 to L2                       |

| E | Terminal position                   | К | Connection and machining data from L6 to L5                       |

| F | Name of the layer between L1 and L2 |   |                                                                   |

Figure 4 – Additional information concerning the interconnection position

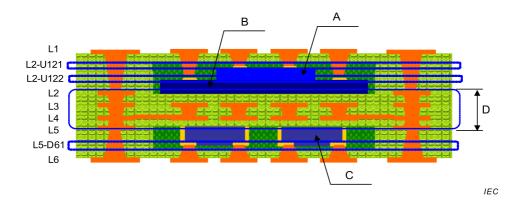

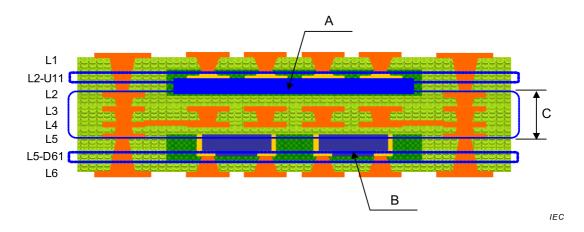

Figure 5 shows the interconnection position. Active device (xxxx) is mounted on the L2 layer and connected to the first layer with upward direction. In this case, the name of the interconnection position is expressed as xxxx-L2-U11. Passive components (yyyy) mounted

on the L5 layer are connected to L6 with downward direction. In this case, the name of the interconnection position is expressed as yyyy-L5-D61.

| Α | Embedded active device  | С | Base |

|---|-------------------------|---|------|

| В | Embedded passive device |   |      |

Figure 5 – Names of layers in via connection [I]

Figure 6 shows a chip-stacked case. Active device 2 (xxx2) is mounted on the L2 layer and active device 1 (xxx1) is stacked on active device 2. Both are connected to the L1 layer with upward direction. In this case the name of the interconnection position of active device 2 is expressed as xxx2-L2-U122. The name of the interconnection position of active device 1 is expressed as xxx1-L2-U121. The second digit from the right (2) shows the number of the embedded device.

| А | Embedded active device 1 | С | Embedded passive device |

|---|--------------------------|---|-------------------------|

| В | Embedded active device 2 | D | Base                    |

Figure 6 – Names of layers in via connection [II]

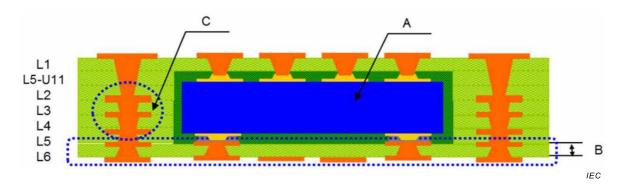

Figure 7 shows the interconnection position of an active device having multilayer connecting pads. Active device (xxxx) is mounted and connected to the L5 layer and pads on the other side are connected to the L1 layer with upward direction. Therefore, in this case, the name of the interconnection position of the active device is expressed as xxxx-L5-U11.

| Α | Embedded active device             |

|---|------------------------------------|

| В | Base                               |

| С | Conductor layer in embedding layer |

Figure 7 – Names of layers in via connection [III]

The content of Figure 4 to Figure 7 is summarized in Table 1.

Table 1 - Name of layers of device embedded board

|          | Embedded device |   |           |   | Embedding and connection of embedded device |   |                       |       |     |                   |

|----------|-----------------|---|-----------|---|---------------------------------------------|---|-----------------------|-------|-----|-------------------|

| Example  | Device          |   | Component |   | Layer                                       |   | Terminal<br>direction | Layer | l   | lo. of<br>ponents |

|          |                 |   | number    |   |                                             |   | airection             |       | No. | Layer             |

|          | Active          | - | A12       | - | L2                                          | - | U                     | 1     | 1   | Omit              |

| Figure 4 | Passive         | - | 1         | - | L5                                          | - | D                     | 6     | 1   | Omit              |

| Ciarra E | Active          | - | A13       | - | L2                                          | - | U                     | 1     | 1   | Omit              |

| Figure 5 | Passive         | - | 2         | - | L5                                          | - | D                     | 6     | 1   | Omit              |

|          | Active          | - | A13       | - | L2                                          | - | U                     | 1     | 2   | 1                 |

| Figure 6 | IPD             | - | 4         | - | L2                                          | - | U                     | 1     | 2   | 2                 |

| <b></b>  | Capacit<br>or   | - | 1         | - | L5                                          | - | D                     | 6     | 1   | Omit              |

| Figure 7 | IPD,            | - | 12        | - | L2                                          | - | U                     | 1     | 1   | Omit              |

|          | etc.            | - | B1        | - | L6                                          | - | D                     | 6     | 1   | Omit              |

Information on embedded components is necessary in embedded board design.

For example, in Figure 4 the interconnection position of active device A12 is expressed as A12-L2-U11.

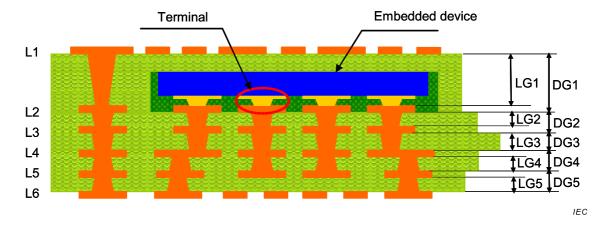

# 4.4 Conductor spacing at a terminal

Subclause 4.4 defines the insulation layer thickness, the conductor spacing and the distance between electrode and conductor spacing at a terminal. Conductor spacing is hereafter referred to as electrode.

The insulation layer thickness and the distance between each conductive layer are defined with respect to the position of each layer, as follows:

- a) The insulation layer thickness is defined as the layer separating the conductors. The thickness is not the thickness of each layer to be laminated but the thickness of the actual insulation layer of the substrate.

- b) The conductor spacing is defined as the distance between conductors formed on one layer.

- c) The spacing between the electrode and conductor is the thickness of the insulator between the terminals of the embedding device and the conductor layer to be connected.

d) The following terms are used to indicate each distance:

1) insulation layer thickness DG1 (dielectric gap);

2) spacing between conductor layers LG1 (layer gap);

3) spacing between terminal and conductor EG11 (device embedding gap).

The number used in the indication is the number of layers. The left number in 3) designates the conductor layer and the number on the right shows the step (first, second, etc.) of multi-device embedding into the substrate. See 4.3 for the definition of steps (layers).

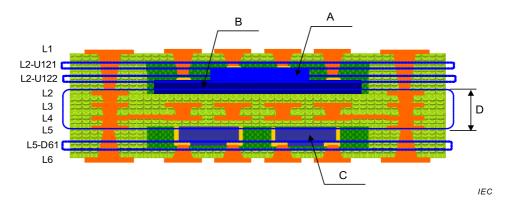

Figure 8 and Figure 9 show definition of layers of a device embedded substrate for pad and via connections. Additional remarks are added to Figure 10 and Figure 11 for dielectric gap, layer gap and device embedding gap.

Figure 8 – Definitions of dielectric gap and layer gap in the pad connection method

Figure 9 – Definitions of dielectric gap and layer gap in the via connection method

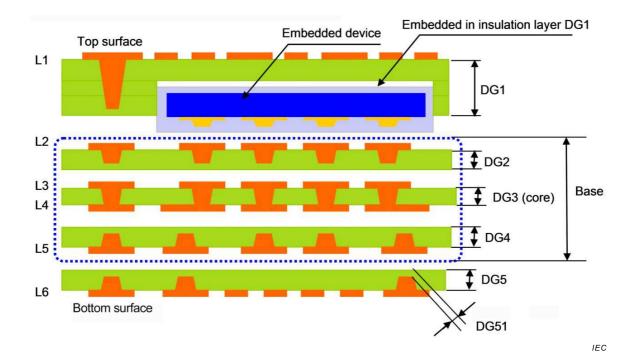

Figure 10 indicates structure of insulation layer prior to the lamination. The active device is embedded in the insulation layer DG1. DG51 indicates the minimum thickness of the insulation layer in DG5.

Figure 10 - Additional illustration of dielectric gap

Figure 11 shows conductor gap and electrode/connector gap. EG11 indicates the insulation gap between non-attached pads of the embedded active device to the conductor of the outer-layer. EG41 indicates the insulation gap between L4 and L5.

Figure 11 - Additional illustration of layer gap

Copyright International Electrotechnical Commissi

# 5 Conditions to prepare base and embedding devices

#### 5.1 Conditions for base

Base board and assembly conditions are given in Table 2.

Table 2 – Recommendation for device assembly to base substrate for device embedded boards

| lt-                            | em                             | Condition                                                                                                                                                                          | Remarks                                                     |  |  |  |  |

|--------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|--|--|--|

| Base                           | Base material                  | Organic: FR-4, FR-5, BT resin, polyimide, PPE, PTFE                                                                                                                                | Copper foil carrier, metal heat fin for                     |  |  |  |  |

|                                | Board structure                | Single sided, double sided, multilayer, build-up multilayer, single-sided flexible, double-sided flexible, multilayer flexible, electronic circuit substrate                       | heat radiation, film<br>type carrier,<br>silicon interposer |  |  |  |  |

|                                | Number of layers               | ber of layers 1 layer, 2 layers,, arbitrary number of layers                                                                                                                       |                                                             |  |  |  |  |

|                                | Copper foil                    | 5 μm, 9 μm, 12 μm, 18 μm, 35 μm, 70 μm                                                                                                                                             |                                                             |  |  |  |  |

|                                | Insulator                      | > 10 μm                                                                                                                                                                            |                                                             |  |  |  |  |

|                                | Maximum size                   | 610 mm × 510 mm                                                                                                                                                                    | Variable based on                                           |  |  |  |  |

|                                | Minimum size                   | 340 mm × 250 mm                                                                                                                                                                    | the capability of<br>die bonder and/or<br>chip mounter      |  |  |  |  |

| Embedded layer                 | Insulation material            | Prepreg such as FR-4, FR-5, BT resin, polyimide, PPE, PTFE (B stage type) Resin such as FR-4, FR-5, BT resin, polyimide, etc. Sealing resin used for semiconductor packages Others | A cut-off may be required for a thick embedding device      |  |  |  |  |

|                                | Number of layers               | 1 layer, 2 layers,, arbitrary number of layers                                                                                                                                     |                                                             |  |  |  |  |

|                                | Copper foil                    | 5 μm, 9 μm, 12 μm, 18 μm, 35 μm, 70 μm                                                                                                                                             |                                                             |  |  |  |  |

|                                | Board size                     | Depends on the base size                                                                                                                                                           |                                                             |  |  |  |  |

| Condition                      | Die bonder                     | Maximum: 330 mm $\times$ 250 mm $\times$ 2,5 mm<br>Minimum: 50 mm $\times$ 50 mm $\times$ 0,5 mm                                                                                   | A carrier may be necessary if the thickness is less         |  |  |  |  |

|                                | Mounter                        | Maximum: 510 mm × 460 mm × 4,0 mm<br>Minimum: 50 mm × 50 mm × 0,3 mm                                                                                                               | than 0,3 mm                                                 |  |  |  |  |

|                                | Fiducial mark                  | Fiducial mark shall be in accordance with customers' process capabilities                                                                                                          |                                                             |  |  |  |  |

|                                | Position accuracy              | To be agreed by customer based materials and process capabilities                                                                                                                  |                                                             |  |  |  |  |

| Condition for sheet components | Die bonder                     | Maximum: 25 mm $\times$ 25 mm $\times$ 0,5 mm<br>Minimum: 0,25 mm $\times$ 0,25 mm $\times$ 0,1 mm                                                                                 |                                                             |  |  |  |  |

|                                | Mounter                        | Maximum: 24 mm $\times$ 24 mm $\times$ 6,5 mm<br>Minimum: 0,4 mm $\times$ 0,2 mm $\times$ 0,12 mm                                                                                  |                                                             |  |  |  |  |

|                                | Thermal resistance             | Withstand for 120 min at 180 °C                                                                                                                                                    |                                                             |  |  |  |  |

|                                | Resistance to pressure         | 3 MPa to 4 MPa                                                                                                                                                                     |                                                             |  |  |  |  |

|                                | Resistance to chemical solvent | To be agreed by customer based materials and process capabilities                                                                                                                  |                                                             |  |  |  |  |

The above assembly recommendations are for reference purposes for the committee drafting the standard for device embedding substrate. Actual recommendations shall be AABUS.

# 5.2 Conditions for embedding devices

Work panel size, panel thickness and embedding condition are shown in Table 3 when automatic device embedding equipment is used.

Table 3 - Embedding recommendation

| Assembly    |          | ssembly Device     |                             | nection                   | Direction<br>(to       | Panel mm |          | Thickness<br>mm |      | Fiducial<br>mark <sup>a</sup> |

|-------------|----------|--------------------|-----------------------------|---------------------------|------------------------|----------|----------|-----------------|------|-------------------------------|

|             |          |                    |                             |                           | embedded<br>terminals) | Max.     | Min.     | Max.            | Min. |                               |

|             | Die      | Bare die           | WB                          |                           | Up                     | 267×90   | 90×15    | 0,9             | 0,1  | _                             |

|             | bonding  | Date die           | ТАВ                         |                           | Ор                     | _        | _        | _               | _    | _                             |

|             |          |                    |                             | US                        |                        | 330×250  | 50×50    | 2,5             | 0,5  | *1                            |

| Pad bonding |          |                    |                             | C4 *4                     |                        | 330×250  | 50×50    | 2,5             | 0,5  | *1                            |

|             |          |                    |                             |                           |                        | 510×460  | 50×50    | 4,0             | 0,3  | *2                            |

|             |          |                    |                             | GBS                       | _                      |          |          |                 |      |                               |

|             | Mounting | unting Bare die F0 | FC   I                      | ESC,<br>ESC5              | Down                   | 330×250  | 50×50    | 2,5             | 0,5  | *1                            |

|             |          |                    |                             | ACF(P)                    |                        |          |          |                 |      |                               |

|             |          |                    |                             | NCF(P)                    |                        |          |          |                 |      |                               |

|             |          |                    |                             | Others                    |                        | _        | _        | _               | _    | _                             |

|             |          | WLP                |                             |                           | Down                   |          |          |                 |      |                               |

|             |          | Rectangular chip   | ı                           | Reflow<br>Resin<br>onding |                        | 510×460  | 50×50 4, |                 |      |                               |

|             | Mounting | Rod                |                             | Silding                   | _                      |          |          | 4,0             | 0,3  | *2                            |

|             |          | Module Reflow Down |                             | Down                      |                        |          |          |                 |      |                               |

|             | Die      | Bare die           |                             |                           |                        | 210215   | 5020     | 2.0             | 0.1  | *3                            |

| ≤ia         | bonding  | WLP                |                             | opper                     |                        | 310×215  | 50×30    | 3,0             | 0,1  |                               |

| Via bonding | Mounting | Rectangular chip   | plating Up Conductive paste |                           | Up                     | 510×460  | 50×50    | 4,0             | 0.3  | *2                            |

| lg          |          | Module<br>MEMS     |                             |                           |                        | 310×400  | 50×50    | 4,0             | 0,3  | *2                            |

The above assembly recommendations are for reference purposes for the committee drafting the standard for device embedded substrate. Actual recommendations shall be AABUS.

NOTE \*4 (C4): on upper layer for terminal pitch  $\ge 0.3$  mm, on lower layer for terminal pitch > 0.3 mm.

Size — \*1: 0,25 mm to 0,8 mm; \*2: 0,5 mm to 1.6 mm; \*3: 0,2 mm to 1,6 mm

Shape — circle, cross, square

<sup>&</sup>lt;sup>a</sup> Size and shape of fiducial mark:

Table 4 shows the embedding methods of semiconductor devices and electronic devices.

Table 4 – Mounting methods of semiconductor devices

| Method              | Schematic diagram                  | Abbrevi-<br>ation | Name                                              | Explanation                                                                                                                                                                                                                                  |

|---------------------|------------------------------------|-------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Metal<br>bonding    | Ultrasound connection Underfill    | US                | Ultra sonic<br>bonding                            | Ultrasonic energy is applied between semiconductor terminal (bump) and board electrode to metal bond and then underfill thermosetting resin for mechanical reinforcement. Gold is often used for the bumps and connecting pads of the board. |

|                     | Solder bump, reflow soldering      | C4                | Controlled<br>collapse chip<br>connection         | Reflow solder bumps LSI with high temperature solder and underfill resin after cleaning the joints. Solder pre-coat, gold plating, OSP are used.                                                                                             |

|                     | Au bump, reflow soldering          | GBS               | Gold bump<br>soldering                            | LSI with Au bumps are pressed to board with solder pre-coated pads and heated to bond the junctions, then underfill to mechanical reinforcement curing                                                                                       |

|                     | Resin with solder powder           | ESC5              | Epoxy<br>encapsulated<br>solder<br>connection 5th | Use solder powder mixed thermosetting adhesive and press and heat to bond the device to board. Gold plating or OSP are used for the pads of board.                                                                                           |

|                     | Au bump, solder pre-coat           | ESC               | Epoxy<br>encapsulated<br>solder<br>connection     | Thermosetting resin is used between LSI bumps and solder pre-coated board pads. Press and heat to establish electrical interconnection.                                                                                                      |

| Compression bonding | Au bump pressed connection         | NCF (P)           | Non conductive film (paste)                       | Thermosetting resin is used between LSI Au bumps and board pads. Press and heat to establish electrical interconnection. Gold plating is usually used for pads on board.                                                                     |

|                     | Resin with conductive metal powder | ACF (P)           | Anisotropic<br>conductive film<br>(paste)         | Thermosetting resin mixed with conductive powder is applied to the connecting electrodes and then pressed and heated to obtain electrical connection. Au plating is usually used for pads on board.                                          |

| Reflow              | Solder paste reflow                | _                 | Soldering                                         | Bonding by reflow soldering.<br>It is necessary to wash out<br>all flux used in reflow<br>soldering.                                                                                                                                         |

| Method | Schematic diagram            | Initial | Name                        | Explanation                                                                                                                 |

|--------|------------------------------|---------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------|

|        | Resin with solder powder     | _       | Solder-resin<br>bonding     | Use solder powder mixed adhesive and reflow to bond the device to board.                                                    |

| Resin  | Resin with conductive powder | _       | Conductive adhesive bonding | Use conductive thermosetting adhesive and cure the resin after mounting a device on a board to attain electrical conduction |

# 6 Recommendation for embedding devices

Conditions for embedding device are given in Table 5 and shall be AABUS in actual application.

Table 5 - Embedding device

| Assembly                                                                                                                        |                                          | Device         | С                               | onnection              | direction (to mounting |              | oonent size<br>(l×w×h)<br>mm |  |

|---------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------|---------------------------------|------------------------|------------------------|--------------|------------------------------|--|

|                                                                                                                                 |                                          |                |                                 |                        | face)                  | max.         | min.                         |  |

|                                                                                                                                 | Die                                      | Bare die       | WB                              |                        | Up                     | 25×25×0,5    | 0,25×0,25×0,1                |  |

|                                                                                                                                 | bonding                                  | bare die       | TAB                             |                        | Up                     |              |                              |  |

|                                                                                                                                 |                                          |                |                                 | US                     | Down                   | 10×10×0,5    | 3,0×3,0×0,1                  |  |

|                                                                                                                                 |                                          |                |                                 | C4 *4                  | Down                   |              |                              |  |

|                                                                                                                                 |                                          |                |                                 | GBS                    | Down                   |              |                              |  |

|                                                                                                                                 | Mounting                                 | Bare die       | FC                              | ESC, ESC5              | Down                   | 20×20×0,5    | 1,0×1,0×0,1                  |  |

| Pad                                                                                                                             |                                          |                |                                 | ACF(P)                 | Down                   |              |                              |  |

| bon                                                                                                                             |                                          |                |                                 | NCF(P)                 | Down                   |              |                              |  |

| Pad bonding                                                                                                                     |                                          |                |                                 | Others                 | Down                   |              |                              |  |

| _                                                                                                                               |                                          | WLP            | Reflow<br>Resin b               | oonding                | Down                   | 24×24×6,5    | 0,4×0,2×0,12                 |  |

|                                                                                                                                 | Manustina                                | Rectangular    | Reflow<br>Resin b               | oonding                | Down                   | 62×45        | 0,4×0,2                      |  |

|                                                                                                                                 | Mounting                                 | Rod            | Reflow<br>Resin b               | onding                 | _                      | 62×45        | 16×08                        |  |

|                                                                                                                                 |                                          | Module<br>MEMS | Reflow                          | Down                   | 24×24×6,5              | 0,4×0,2×0,12 |                              |  |

| <i< td=""><td colspan="2">Bare die Copper plating Conductive paste</td><td>Up</td><td>25×25×0,5</td><td>0,25×0,25×0,1</td></i<> | Bare die Copper plating Conductive paste |                | Up                              | 25×25×0,5              | 0,25×0,25×0,1          |              |                              |  |

| Via bonding                                                                                                                     | bonding                                  | WLP            | Copper plating Conductive paste |                        | Up                     | 25×25×0,5    | 0,25×0,25×0,1                |  |

| ing                                                                                                                             | Mounting                                 | Rectangular    |                                 | plating<br>ctive paste | Up                     | 62×45        | 0,4×0,2                      |  |

The above assembly recommendations are for reference purposes for the committee drafting the standard for device embedded substrate. Actual recommendations shall be AABUS.

#### 7 Design specification of device embedded substrate

#### 7.1 General

In general, the term "design" has broad meanings. In order to avoid misunderstanding and confusion, it is recommended to include the follow items in the design specification:

- a) circuit design;

- b) structure design;

- c) device embedding board design;

- d) circuit pattern design.

# 7.2 Items to be included in the design specification

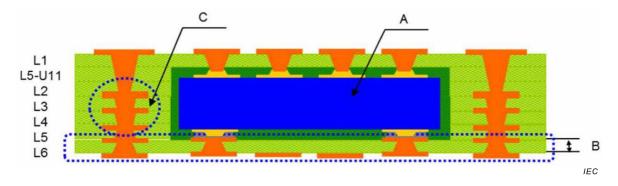

#### 7.2.1 Graphical indication of device embedding substrate

The following indications shall be stated:

a) Indication of external form of device embedded substrate, of design drawing and of CAD data is as follows. A perspective drawing seen from the top or bottom surface is used. State if the drawing is seen from top or bottom.

Example: A top perspective or bottom perspective drawing is shown in Figure 12.

It is recommended to clarify the position of the relevant layer in the cross section drawing.

Figure 12 – Additional drawing

- b) List of parts of device embedded substrate and items to be stated:

- 1) device name, device number, name of manufacturer;

- 2) possibility of embedding (if not possible, embedding inside of substrate or surface mounting, etc.);

- 3) table of parts of device embedded substrate and its structure.

- c) Organization and structure of device embedded substrate:

- 1) entire organization and structure of device embedded substrate;

- 2) number of layers and types of electronic circuit board;

- 3) thickness of each conductor layer (copper foil + copper plating, etc.);

- 4) distance between insulating layers, and between the conductor and insulating layers;

- **20 -**

- 5) position of layer where device is to be embedded;

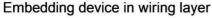

- 6) forbidden area(s) for wiring in each layer as illustrated in Figure 13;

- 7) thickness of the layer to embedded device(s).

- d) Specification of device embedded substrate:

- 1) size and thickness of the substrate;

- 2) treatment to the surface where the device is not embedded (embedding on one side only);

- 3) methods of embedding and connection to the device;

- 4) surface treatment to conductor surface (solder flux, gold plating, etc.).

- e) Embedding:

- 1) die bonding;

- 2) methods of mounting and interconnection;

- 3) special treatment:

- underfill;

- resin mold;

- potting;

- others.

Figure 13 – Forbidden wiring area

- f) Specification of device embedding:

- 1) embedding (resin embedding, stacking, etc.);

- 2) embedding material (resin, prepreg, etc.);

- 3) embedding conditions (heating, temperature, pressure, etc.);

- 4) mechanical loading condition.

Embedding condition shall be AABUS.

g) Design specification of electronic circuit board (pattern design).

The design principle of conductor gap, via diameter, via land diameter, etc. is basically the same as for regular PWB. Details of design specification are to be AABUS.

#### 7.2.2 Design specification template

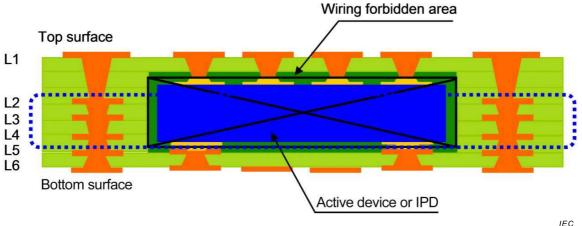

Table 6 to Table 8 show the template of a design specification.

Table 6 is an example of a specification of a device embedded substrate.

Table 6 – Specification of device embedded substrate 1

|           |                              |                   |       | L       | ist of emb     | edde    | d de         | vices          |       |                                      |     |         |                |         |               |  |

|-----------|------------------------------|-------------------|-------|---------|----------------|---------|--------------|----------------|-------|--------------------------------------|-----|---------|----------------|---------|---------------|--|

| No.       | Device                       | Name              | Dev   | ice #   | Manufact       | turer   | Manufacturer |                | rer   | Specification of<br>embedding device |     |         | Ren            | Remarks |               |  |

|           |                              |                   |       |         |                |         |              |                | S     | hall                                 | Yes | No      | Or             |         |               |  |

| Case 1    | Memory<br>IC                 | D-RAM             | MIC   | -002    | TM-DRAM        | 102     | Т            |                | 0     |                                      |     |         |                |         |               |  |

| Case 2    | Stacked capacitor            | Chip C            | CC-   | 003     | CCK-5V1        | 0       | М            |                |       |                                      |     |         | 0              |         |               |  |

| Case 3    | Stacked capacitor            | Electrolytic<br>C | DC-0  | 004     | DCK-5V2        | 00      | Р            |                |       |                                      |     | 0       |                | Low     | heat<br>tance |  |

| Device er | mbedded su                   | ubstrate – Co     | nstru | ction a | and structu    | ıre     |              |                |       |                                      |     |         |                |         |               |  |

| Layer #   | 6                            | Base 4            |       | Love    | er and its th  | siakna  |              |                | Diele | ctric                                | 1.0 | vor     | 100            | Device  |               |  |

| Туре      | Build-up                     | layer             |       | Laye    | and its ti     | IICKIIG | 33           | Embe           | gap   |                                      | La  | yer g   | r gap em<br>ga |         | mbedded<br>ap |  |

| Embeddir  | ng layer l                   | _2、L5             | N°    | Lay     | Conducto<br>μm | r       |              | dding<br>layer | Name  |                                      |     | Name    | $ _{t}$        | Name    | t             |  |

| Construct | tion and str                 | ucture            |       | er      | Copper<br>foil | Copp    |              |                | Name  | μm                                   | Na  | ıme     | μm             | Ivallie | μm            |  |

|           |                              |                   | _     |         | 10             | 00      |              |                | _     | -                                    | _   |         | _              | _       | -             |  |

| L1_       |                              | EG11 t            | 1     | L1      | 12             | 20      |              | _              | DG1   | 138                                  | LG  | ٠1      | 100            | EG11    | 40            |  |

| L2-U11    | <b>-</b>                     | LG1 DG1           | 2     | L2      | 18             | 20      |              | 0              | DGT   | 130                                  | LG  | ' '<br> | 100            | EGII    | 40            |  |

| L2        |                              | 1 62              |       |         | 10             |         |              |                | DG2   | 73                                   | LG  | 62      | 40             | _       | _             |  |

| L3        | 77 7                         | LG3 DG3           | 3     | L3      | 18             | 15      |              | _              |       |                                      |     |         |                |         |               |  |

| L4 L5 -   | 4                            | LG4 DG4           |       |         |                |         |              |                | DG3   | 80                                   | LG  | 3       | 80             | _       | _             |  |

| L5-D61    |                              | LG5 DG5           | 4     | L4      | 18             | 15      |              | _              |       |                                      |     |         |                |         |               |  |

| L6        |                              | <u> </u>          |       |         |                |         |              |                | DG4   | 73                                   | LG  | 64      | 40             | EG41    | 40            |  |

|           | \<br>EG41                    | EG61              | 5     | L5      | 18             | 20      |              | 0              |       |                                      |     |         |                |         |               |  |

|           | 1agnificatio                 |                   |       |         |                |         |              |                | DG-5  | 138                                  | LG  | 55      | 100            | EG61    | 40            |  |

|           | for vertical<br>I directions |                   | 6     | L6      | 12             | 20      |              | _              | _     | -                                    | -   |         | _              | _       | _             |  |

|           |                              |                   | Subs  | strate  | thickness      | (exclu  | ide s        | older re       | sist) | 0,5                                  | 7   |         |                |         |               |  |

Table 7 and Table 8 are examples of specifications of device embedded substrate

Table 7 – Specification of device embedded substrate 2

| Specification of device embedded substrate                  |          |                                     |           |                                                           |  |  |  |

|-------------------------------------------------------------|----------|-------------------------------------|-----------|-----------------------------------------------------------|--|--|--|

| Placement of embedded device and condition                  | NO       | Item                                |           | Specification                                             |  |  |  |

| Specification Fiducial mark                                 | 1        |                                     | Layers    | 4 layers                                                  |  |  |  |

| Specification Fiducial mark of each section of each section |          | embedded<br>substrate               | Size      | W: 250 mm × L: 320 mm                                     |  |  |  |

|                                                             |          |                                     | Thickness | t = 0,2 mm                                                |  |  |  |

|                                                             | 2        | Embedding s                         | urface    | Double/single side                                        |  |  |  |

|                                                             | 3        | Treatment of surface in single-side |           | □ with pattern formation □ without pattern                |  |  |  |

|                                                             |          | -                                   |           | formation                                                 |  |  |  |

|                                                             | 4        | Embedding m                         | nethod    | □ Die bonding                                             |  |  |  |

|                                                             |          |                                     |           | □ Mounting<br>□ Others                                    |  |  |  |

|                                                             | 5        | Interconnection                     | on        | □ Via connection (Cu<br>plating)                          |  |  |  |

|                                                             |          |                                     |           | □ Cu plating □ Conductive paste □ Others □ Pad connection |  |  |  |

|                                                             |          |                                     |           |                                                           |  |  |  |

| Fiducial mark                                               |          |                                     |           |                                                           |  |  |  |

| of the sheet Forbidden area Fiducial hole                   |          |                                     |           |                                                           |  |  |  |

| for assembly                                                |          |                                     |           | □ Cu plating                                              |  |  |  |

|                                                             |          |                                     |           | □ Conductive paste □ Others                               |  |  |  |

|                                                             |          |                                     |           | □ Others                                                  |  |  |  |

|                                                             | 6        | Solder resist                       |           | □ Yes □ No                                                |  |  |  |

|                                                             | 7        | Surface treat                       | ment      | □ Flux                                                    |  |  |  |

|                                                             | <b>'</b> | Currace treat                       | mont      | □ Anti-rust treatment                                     |  |  |  |

|                                                             |          |                                     |           | □ Other                                                   |  |  |  |

|                                                             | 8        | Reference ho                        | le        | □ Yes □ No                                                |  |  |  |

|                                                             | 9        | Fiducial mark                       |           | □ Yes □ No                                                |  |  |  |

|                                                             | 10       | Bending after<br>embedding %        |           | ±0,5                                                      |  |  |  |

|                                                             | 11       | Others                              |           |                                                           |  |  |  |

Table 8 - Specification of device embedded substrate 3

| Construction of device embedding and condition                                                         | No. | Item                       | Specification                                                                                                                        |

|--------------------------------------------------------------------------------------------------------|-----|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| ■ Die bonding ■ Mounting  Achesion Interconnection                                                     | 1   | Assembly                   | □ Die bonding □ Adhesives □ Others □ Mounting □ Soldering □ Conductive paste □ Others □ Special treatment □ Underfill □ Resin mold   |

| ■Special treatment<br>Reinforcement                                                                    |     |                            | □ Potting □ Others                                                                                                                   |

|                                                                                                        | 2   | Embedding method           | □ Stacking □ Resin molding □ Molding □ Others                                                                                        |

| 2 Structure of device embedded substrate  Device embedded section                                      | 3   | Embedding material         | <ul><li>□ Glass epoxy prepreg</li><li>□ Epoxy resin</li><li>□ Polyimide prepreg</li><li>□ Polyimide resin</li><li>□ Others</li></ul> |

| L1 Device embedding layer                                                                              | 4   | Treatment before embedding | □ Flux cleaning □ General cleaning □ Baking □ Others                                                                                 |

| L2<br>L3<br>L4                                                                                         | 5   | Embedding condition        | Temperature (≤ 160 °C)<br>Pressure (≤ 3 MPa to<br>4 MPa)                                                                             |

| L5 DC4                                                                                                 | 6   | Mechanical stress          | AABUS                                                                                                                                |

| L5-D61 <u>8</u> 99                                                                                     | 7   | Check of embedded device   | AABUS                                                                                                                                |

| Device embedding layer  Device embedded section                                                        | 8   | Others                     |                                                                                                                                      |

| Cutting of the embedded section may be different depending on the embedding method and is to be AABUS. |     |                            |                                                                                                                                      |

Properties of top and bottom surface after embedding, solder resist, surface treatment and alike should be in accordance with the general specification of electronic circuit boards.

# Bibliography

IEC 61189 (all parts), Test methods for electrical materials, printed boards and other interconnection structures

IEC 61249 (all parts), Materials for printed boards and other interconnecting structures

IEC 62421, Electronics assembly technology – Electronic modules

IEC 62878-1-1, Device embedded substrate – Part 1-1: Generic specification – Test methods<sup>1</sup> IEC TS 62878-2-1, Device embedded substrate – Part 2-1: Guidelines – General description of technology

IEC TS 62878-2-4, Device embedded substrate – Part 2-4: Guidelines – Test element groups (TEG)

<sup>1</sup> To be published.

# SOMMAIRE

| A'         | √ANT-I  | PROPOS                                                                                                                   | 28         |

|------------|---------|--------------------------------------------------------------------------------------------------------------------------|------------|

| IN         | ITROD   | UCTION                                                                                                                   | 30         |

| 1          | Don     | naine d'application                                                                                                      | 31         |

| 2          | Réfe    | érences normatives                                                                                                       | 31         |

| 3          | Terr    | nes, définitions et abréviations                                                                                         | 31         |

|            | 3.1     | Termes et définitions                                                                                                    | 31         |

|            | 3.2     | Abréviations                                                                                                             | 31         |

| 4          | Stru    | cture de substrats avec appareil(s) intégré(s)                                                                           | 32         |

|            | 4.1     | Généralités                                                                                                              | 32         |

|            | 4.2     | Spécifications des surfaces supérieure et inférieure d'un substrat avec appareil(s) intégré(s)                           | 32         |

|            | 4.3     | Définitions des couches d'un substrat avec appareil(s) intégré(s)                                                        | 33         |

|            | 4.4     | Distance entre conducteurs sur un terminal                                                                               |            |

| 5          | Con     | ditions pour la préparation de la base et intégration d'appareils                                                        | 40         |

|            | 5.1     | Conditions pour la base                                                                                                  |            |

|            | 5.2     | Conditions pour l'intégration des appareils                                                                              |            |

| 6          |         | ommandation pour l'intégration des appareils                                                                             |            |

| 7          | Spé     | cification de conception de substrat avec appareil(s) intégré(s)                                                         | 44         |

|            | 7.1     | Généralités                                                                                                              |            |

|            | 7.2     | Eléments à inclure dans la spécification de la conception                                                                |            |

|            | 7.2.    |                                                                                                                          |            |

| _          | 7.2.    | · ·                                                                                                                      |            |

| В          | bliogra | phie                                                                                                                     | 50         |

| <b>-</b> : | auro 1  | <ul> <li>Définitions des surfaces supérieure et inférieure d'un substrat avec</li> </ul>                                 |            |

|            |         | s) intégré(s)s                                                                                                           | 32         |

| Fi         | gure 2  | Définition des surfaces supérieure et inférieure pour le montage sur une re                                              |            |

|            |         | Noms des couches dans la connexion de plage                                                                              |            |