Edition 1.0 2008-09

# PUBLICLY AVAILABLE SPECIFICATION

Marking and labeling of components, PCBs and PCBAs to identify lead(Pb), Pb-free and other attributes

#### THIS PUBLICATION IS COPYRIGHT PROTECTED

#### Copyright © 2008 IEC, Geneva, Switzerland

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from either IEC or IEC's member National Committee in the country of the requester.

If you have any questions about IEC copyright or have an enquiry about obtaining additional rights to this publication, please contact the address below or your local IEC member National Committee for further information.

IEC Central Office 3, rue de Varembé CH-1211 Geneva 20 Switzerland

Email: inmail@iec.ch Web: www.iec.ch

#### About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes International Standards for all electrical, electronic and related technologies.

#### **About IEC publications**

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the latest edition, a corrigenda or an amendment might have been published.

■ Catalogue of IEC publications: <u>www.iec.ch/searchpub</u>

The IEC on-line Catalogue enables you to search by a variety of criteria (reference number, text, technical committee,...). It also gives information on projects, withdrawn and replaced publications.

■ IEC Just Published: www.iec.ch/online news/justpub

Stay up to date on all new IEC publications. Just Published details twice a month all new publications released. Available on-line and also by email.

■ Electropedia: <u>www.electropedia.org</u>

The world's leading online dictionary of electronic and electrical terms containing more than 20 000 terms and definitions in English and French, with equivalent terms in additional languages. Also known as the International Electrotechnical Vocabulary online.

■ Customer Service Centre: <u>www.iec.ch/webstore/custserv</u>

If you wish to give us your feedback on this publication or need further assistance, please visit the Customer Service Centre FAQ or contact us:

Email: csc@iec.ch Tel.: +41 22 919 02 11 Fax: +41 22 919 03 00

Edition 1.0 2008-09

# PUBLICLY AVAILABLE SPECIFICATION

Marking and labeling of components, PCBs and PCBAs to identify lead(Pb), Pb-free and other attributes

INTERNATIONAL ELECTROTECHNICAL COMMISSION

PRICE CODE

P

ISBN 2-8318-9989-3

#### **IPC/JEDEC J-STD-609**

Marking and Labeling of Components,

PCBs and PCBAs to Identify Lead(Pb),

Pb-Free and Other Attributes

A joint standard developed by the Marking, Symbols and Labels for Identification of Assemblies, Components and Devices Task Group (4-34b) and JEDEC Committee JC14.4 Quality Processes and Methods

#### Supersedes:

JESD97 - May 2004 IPC-1066 - January 2005 Users of this publication are encouraged to participate in the development of future revisions.

#### Contact:

**JEDEC**

**Solid State Technology Association** 2500 Wilson Boulevard

Arlington, VA 22201-3834 Tel 703 907.7500 Fax 703 907.7501

#### **IPC**

3000 Lakeside Drive, Suite 309S Bannockburn, Illinois 60015-1249 Tel 847 615.7100 Fax 847 615.7105

## **Table of Contents**

| IPC/JEDEC Foreword vii |                                                   |  |  |  |

|------------------------|---------------------------------------------------|--|--|--|

| 1                      | SCOPE1                                            |  |  |  |

| 1.1                    | Purpose1                                          |  |  |  |

| 2                      | REFERENCE DOCUMENTS1                              |  |  |  |

| 2.1                    | IPC1                                              |  |  |  |

| 2.2                    | JEDEC1                                            |  |  |  |

| 2.3                    | IEC1                                              |  |  |  |

| 2.4                    | European Parliament1                              |  |  |  |

| 2.5                    | ANSI1                                             |  |  |  |

| 3                      | TERMS AND DEFINITIONS 1                           |  |  |  |

| 3.1                    | 2D Code Label (Matrix) 1                          |  |  |  |

| 3.2                    | 2 Li (or 2LI)1                                    |  |  |  |

| 3.3                    | 2 Level Interconnect2                             |  |  |  |

| 3.4                    | 2 Level Interconnect Component Label2             |  |  |  |

| 3.5                    | 2 Level Interconnect Terminal Finish or Material2 |  |  |  |

| 3.6                    | Component2                                        |  |  |  |

| 3.7                    | Base Materials2                                   |  |  |  |

| 3.8                    | Halogen-Free Board2                               |  |  |  |

| 3.9                    | Homogeneous Material2                             |  |  |  |

| 3.10                   | intct (or INTCT)2                                 |  |  |  |

| 3.11                   | Linear Bar Code Label2                            |  |  |  |

| 3.12                   | Material Category2                                |  |  |  |

| 3.13                   | Maximum Component Temperature2                    |  |  |  |

| 3.14                   | "Pb-Free"                                         |  |  |  |

| 3.15                   | Pb-Free Symbol2                                   |  |  |  |

| 4                      | SYMBOLS, LABELS AND MARKS2                        |  |  |  |

| 4.1                    | Material Category Symbol2                         |  |  |  |

| 4.1.1                  | Size and Location2                                |  |  |  |

| 4.1.2                  | Color2                                            |  |  |  |

| 4.1.3                  | Font2                                             |  |  |  |

| 4.2                    | Pb-Free Symbol                                    |  |  |  |

| 4.3                    | 2 Level Interconnect Component Label              |  |  |  |

| 4.3.1                  | Size3                                             |  |  |  |

| 432                    | Color 3                                           |  |  |  |

| 5     | MARKING/LABELING CATEGORIES4                                                         |

|-------|--------------------------------------------------------------------------------------|

| 5.1   | PCB Base Material Categories4                                                        |

| 5.1.1 | Halogen-Free Base Material4                                                          |

| 5.2   | PCB Surface Finish Categories4                                                       |

| 5.2.1 | Pb-Containing4                                                                       |

| 5.2.2 | Pb-Free4                                                                             |

| 5.3   | 2 Level Interconnect Categories4                                                     |

| 5.3.1 | Pb-Containing4                                                                       |

| 5.3.2 | Pb-Free4                                                                             |

| 5.4   | Conformal Coating Categories4                                                        |

| 6     | COMPONENT MARKING AND LABELING4                                                      |

| 6.1   | Component Marking4                                                                   |

| 6.2   | Lowest Level Shipping Container Labeling4                                            |

| 7     | PCB/ASSEMBLY MARKING AND LABELING5                                                   |

| 7.1   | PCB Marking5                                                                         |

| 7.1.1 | PCB Shipping Container Labeling5                                                     |

| 7.2   | Assembly Marking5                                                                    |

| 7.2.1 | Assembly Shipping Container Labeling5                                                |

| 7.3   | Solder Category Marking Sequence5                                                    |

| 7.4   | Location5                                                                            |

| 7.5   | Size5                                                                                |

| 7.6   | Color5                                                                               |

| 7.7   | Font5                                                                                |

| 7.8   | Method5                                                                              |

| 7.9   | Marking Sequence5                                                                    |

| 7.10  | Re-Marking Changes in PCBA Materials6                                                |

| 8     | MARKING AND/OR LABELING OF LEAD (Pb)-CONTAINING COMPONENTS, PCBs, AND PCB ASSEMBLIES |

| 8.1   | Marking and Labeling of Components6                                                  |

| 8.2   | Marking and Labeling of PCBs6                                                        |

| 8.3   | Marking and Labeling of PCB Assemblies 6                                             |

| 9     | SUMMARY OF MARKING AND LABELING REQUIREMENTS 7                                       |

| Annex | A – Acknowledgment8                                                                  |

|       |                                                                                      |

#### **Figures**

| Figure 3-1 | Examples of Materials that Comprise the 2 <sup>nd</sup> Level Interconnect                                                                                                                                   | 2 |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Figure 4-1 | Example of Mark Indicating Material Category e2 and the Optional Circle, Ellipse, Underline or Parentheses                                                                                                   | 2 |

| Figure 4-2 | Pb-Free Symbol                                                                                                                                                                                               | 3 |

| Figure 4-3 | Example of 2 <sup>nd</sup> Level Interconnect Component Label Indicating a Pb-Containing Material                                                                                                            | 3 |

| Figure 4-4 | Example of 2 <sup>nd</sup> Level Interconnect Component<br>Label Indicating a Pb-Free e2 Material with a<br>Maximum Component Temperature of 260°C                                                           | 3 |

| Figure 4-5 | Example of 2 <sup>nd</sup> Level Interconnect Component Label Utilizing the Lead Free Symbol Indicating Both Pb-Free Material with Category and Maximum Component Temperature Indicated on an Adjacent Label | 3 |

| Figure 6-1 | Example of Component Marking                                                                                                                                                                                 | 5 |

| Figure 7-1 | Example of Board/Assembly Markings                                                                                                                                                                           | 6 |

|            |                                                                                                                                                                                                              |   |

|            | Tables                                                                                                                                                                                                       |   |

| Table 9-1  | Marking and Labeling Summary                                                                                                                                                                                 | 7 |

May 2007

IPC and JEDEC Standards and Publications are designed to serve the public interest through eliminating misunderstandings between manufacturers and purchasers, facilitating interchangeability and improvement of products, and assisting the purchaser in selecting and obtaining with minimum delay the proper product for his particular need. Existence of such Standards and Publications shall not in any respect preclude any member or nonmember of IPC or JEDEC from manufacturing or selling products not conforming to such Standards and Publications, nor shall the existence of such Standards and Publications preclude their voluntary use by those other than IPC or JEDEC members, whether the standard is to be used either domestically or internationally.

Recommended Standards and Publications are adopted by IPC or JEDEC without regard to whether their adoption may involve patents on articles, materials, or processes. By such action, IPC or JEDEC do not assume any liability to any patent owner, nor do they assume any obligation whatever to parties adopting the Recommended Standard or Publication. Users are also wholly responsible for protecting themselves against all claims of liabilities for patent infringement. The material in this joint standard was developed by the Marking, Symbols and Labels for Identification of Assemblies, Components and Devices Task Group (4-34b) of the Materials Identification Subcommittee (4-34).

For Technical Information Contact:

JEDEC Solid State Technology Association 2500 Wilson Boulevard Arlington, VA 22201-3834 Phone (703) 907-7560 Fax (703) 907-7501

3000 Lakeside Drive, Suite 309S Bannockburn, Illinois 60015-1249

Tel 847 615.7100 Fax 847 615.7105

**IPC**

May 2007

#### **IPC/JEDEC FOREWORD**

Directive 2002/95/EC of the European Parliament and of the Council on the restriction of the use of certain hazardous substances in electrical and electronic equipment, commonly referred to as the "RoHS Directive1", and other legislation are driving the electronics industry towards the use of lead free (Pb-free) solders and components with Pb-free 2<sup>nd</sup> level interconnect terminal finishes and materials.

There are different Pb-free solders being used for the various soldering operations in electronics. Each of these solders may require different processing temperatures for assembly, rework, and repair. Some means of communicating the identity of the Pb-free or Pb-containing solder must be provided so that those performing assembly, rework and repair are aware of the temperature capabilities and limitations of these solders, and are able to distinguish between Pb-free and Pb-containing solders.

Marking of components and/or labeling their shipping containers are needed to identify and distinguish Pb-containing and Pb-free 2<sup>nd</sup> level interconnect terminal finishes and materials. Labeling electronic assemblies using Pb-free solder materials will facilitate end-of-life recycling of electronic equipment. This standard sets forth minimum requirements and includes options for the provision of additional information.

This paradigm shift to Pb-free electronics has created a need for identification of traditional Pb-containing coatings, finishes and solders. This standard can be utilized to identify the presence of lead (Pb) for those markets as described in Clauses 5 (Marking/Labeling Categories) and 8 (Marking and/or Labeling of Pb-Containing Components, PCBs, and PCB Assemblies). This standard supersedes JESD97 and IPC-1066.

<sup>1.</sup> The RoHS Directive itself is not a law; rather, it is a direction to the European Union Member States to implement their own laws embodying the requirements of the Directive. These laws were required to be in effect as of July 1, 2006.

This Page Intentionally Left Blank

PAS 62588 © IEC:2008(E)

#### INTERNATIONAL ELECTROTECHNICAL COMMISSION

# Marking and Labeling of Components, PCBs and PCBAs to Identify Lead(Pb), Pb-Free and Other Attributes

#### **FOREWORD**

- 1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international cooperation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as "IEC Publication(s)"). Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely with the International Organization for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- 2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC National Committees.

- 3) IEC Publications have the form of recommendations for international use and are accepted by IEC National Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

- 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter.

- 5) IEC provides no marking procedure to indicate its approval and cannot be rendered responsible for any equipment declared to be in conformity with an IEC Publication.

- 6) All users should ensure that they have the latest edition of this publication.

- 7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and members of its technical committees and IEC National Committees for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC Publications.

- 8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.

- 9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

A PAS is a technical specification not fulfilling the requirements for a standard but made available to the public.

IEC-PAS 62588 was submitted by IPC/JEDEC and has been processed by IEC technical committee 91: Electronics assembly technology.

The text of this PAS is based on the following document:

This PAS was approved for publication by the P-members of the committee concerned as indicated in the following document

| Draft PAS  | Report on voting |

|------------|------------------|

| 91/767/PAS | 91/783/RVD       |

Following publication of this PAS, the technical committee or subcommittee concerned will investigate the possibility of transforming the PAS into an International Standard.

An IEC-PAS licence of copyright and assignment of copyright has been signed by the IEC and IPC/JEDEC and is recorded at the Central Office.

This PAS shall remain valid for an initial maximum period of 3 years starting from the publication date. The validity may be extended for a single 3-year period, following which it shall be revised to become another type of normative document, or shall be withdrawn.

This Page Intentionally Left Blank

# Marking and Labeling of Components, PCBs and PCBAs to Identify Lead (Pb), Pb-Free and Other Attributes

#### 1 SCOPE

This document applies to components and assemblies that contain Pb-free and Pb-containing solders and finishes. This document describes the marking of components and the labeling of their shipping containers to identify their 2<sup>nd</sup> level terminal finish or material, and applies to components that are intended to be attached to boards or assemblies with solder or mechanical clamping or are press fit. This document also applies to 2<sub>nd</sub> level terminal materials for bumped die that are used for direct board attach.

This document applies to boards/assemblies, to identify the type of Pb-free or Pb-containing solder used. This document documents a method for identifying board surface finishes and Printed Circuit Board (PCB) resin systems. This document applies to PCB base materials and for marking the type of conformal coating utilized on Printed Circuit Board Assemblies (PCBAs). Material and their containers previously marked or labeled according to JESD 97 or IPC-1066 need not be remarked unless agreed upon by the supplier and customer.

Labeling of exterior surfaces of finished articles, such as computers, printers, servers, and the like, is outside the scope of this document. However internal PCBs and PCBAs are covered by this document. Labeling of retail packages containing electronic products is also outside the scope of this document.

- **1.1 Purpose** This document provides a marking and labeling system that aids in assembly, rework, repair and recycling and provides for the identification of:

- (1) those assemblies that are assembled with Pb-containing or Pb-free solder;

- (2) components that have Pb-containing or Pb-Free 2<sup>nd</sup> level interconnect terminal finishes and materials;

- (3) the maximum component temperature not to be exceeded during assembly or rework processing;

- (4) the base materials used in the PCB construction, including those PCBs that use halogen-free resin;

- (5) the surface finish of PCBs; and

- (6) the conformal coating on PCBAs.

- 1. www.ipc.org

- 2. www.jedec.org

- 3. www.iec.ch

- 4. www.europa.eu.int/eur-lex/en/index.html

- 5. www.ansi.org

#### 2 REFERENCE DOCUMENTS

#### 2.1 IPC1

**IPC-T-50** Terms and Definitions for Interconnecting and Packaging Electronic Circuits

**IPC-CC-830** Qualification and Performance of Electrical Insulating Compound for Printed Wiring Assemblies (Conformal Coating)

**IPC-4101** Specification for Base Materials for Rigid and Multilayer Printed Boards

#### 2.2 JEDEC<sup>2</sup>

**JESD88 JEDEC** Dictionary of Terms for Solid State Technology

#### 2.3 IEC3

**IEC 61249-2-21** Materials for printed boards and other interconnecting structures - Part 2-21: Reinforced base materials, clad and unclad - Nonhalogenated epoxide woven E-glass reinforced laminated sheets of defined flammability (vertical burning test), copper-clad.

#### 2.4 European Parliament<sup>4</sup>

Directive 2002/95/EC of the European Parliament and of the Council on the Restriction of the Use of Certain Hazardous Substances in Electrical and Electronic Equipment.

#### 2.5 ANSI<sup>5</sup>

**ANSI 17-1981** Character Set for Optical Character Recognition (OCR-A)

#### **3 TERMS AND DEFINITIONS**

Other than those terms listed below, the definitions of terms used in this document are in accordance with IPC-T-50 and/or JESD88.

- **3.1 2D Code Label (Matrix)** A label that contains data in two dimensions as either stack or matrix types.

- **3.2 2 Li (or 2LI)** Abbreviation for 2<sup>nd</sup> level interconnect.

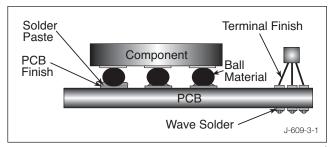

**3.3 2**<sup>nd</sup> **Level Interconnect** The connection made by attaching a component to a printed circuit board (see Figure 3-1). This connection is external to the component, not internal.

Figure 3-1 Examples of Materials that Comprise the 2<sup>nd</sup> Level Interconnect

- **3.4** 2<sup>nd</sup> Level Interconnect Component Label A label placed on boxes and bags that contain components with either Pb-containing or Pb-free terminal materials/finishes. The label includes the material category and maximum component temperature (see 3.12 and 3.13). See Figure 4-3 for label formats for components with Pb-containing finishes/materials and Figures 4-4 and 4-5 for components with Pb-free finishes/materials.

- **3.5** 2<sup>nd</sup> Level Interconnect Terminal Finish or Material The material at the component 2<sup>nd</sup> level termination referred to in Figure 3-1. Depending on the component type this material could refer to the terminal finish or ball material.

- **3.6 Component** An individual part such as a connector, capacitor, integrated circuit, socket, multichip module, and hybrid circuits, etc.

- **3.7 Base Materials** Base materials are the laminates and/or the prepregs used to fabricate the PCB.

- **3.8 Halogen-Free Board** Printed board resins plus reinforcement matrix that contain maximum total halogens of 1500 ppm, with less than 900 ppm bromine and less than 900 ppm chlorine (per IEC 61249-2-21).

- **3.9 Homogeneous Material** A material of uniform composition throughout that cannot be mechanically disjointed into different materials. Mechanically disjointed means that the materials can, in principle, be separated by mechanical actions such as: unscrewing, cutting, crushing, grinding, and abrasive processes.

- **3.10 intct (or INTCT)** Abbreviation for the word "interconnect."

- **3.11 Linear Bar Code Label** A label that gives information in a code consisting of parallel bars and spaces, each of various specific widths.

- **3.12 Material Category** Solder paste, lead/terminal finish, or terminal material/alloy of the solder balls used to make the 2<sup>nd</sup> level interconnect.

- **3.13 Maximum Component Temperature** The temperature that a component should not exceed during assembly as measured on the topside of the component body.

- **3.14 "Pb-Free"** Having a concentration of lead (Pb) with a maximum concentration value of 0.1% by weight in each homogeneous material.

**Note:** Component and end product suppliers may desire to clarify this important distinction (between 0% and 0.1% lead (Pb)) with their customers.

- **3.15 Pb-Free Symbol** A symbol that can be used in place of the phrase "Pb-free" (see Figure 4-2).

- 4 SYMBOLS, LABELS AND MARKS

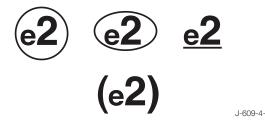

- **4.1 Material Category Symbol** This symbol (see Figure 4-1) is used to identify a terminal finish or material listed in 5.3.

Figure 4-1 Example of Mark Indicating Material Category e2 and the Optional Circle, Ellipse, Underline or Parentheses

- Note 1: If the Materials Category is used without a circle, ellipse, parentheses or underline, it must be made clear that the marking defines the category [e.g. "Category = e2", or "Solder = e2"]

- Note 2: The letter "e" would be replaced with a "b" for identifying surface finish material listed in 5.2 for PCBs.

- **4.1.1 Size and Location** The size and location are discretionary, but **shall** be legible to corrected, unmagnified vision.

- **4.1.2 Color** The color for the 'e' and category number should be selected to provide sufficient contrast to be legible to corrected, unmagnified vision. The color red should be avoided as red suggests a personal hazard.

- **4.1.3 Font** The font style should be "Arial," "OCR-A" or equivalent.

- **4.2 Pb-Free Symbol** This symbol (see Figure 4-2) can be used in addition to, or instead of, the phrase "Pb-free."

J-609-4-2

Figure 4-2 Pb-Free Symbol

### 2<sup>nd</sup> Level Interconnect

- 1. Category <u>e0</u>

If blank, see adjacent bar code label

- 2. Maximum component temp\_\_\_\_\_°C If blank, see adjacent label

Figure 4-3 Example of 2<sup>nd</sup> Level Interconnect Component Label Indicating a Pb-Containing Material

### 2<sup>nd</sup> Level Interconnect

- 1. Category <u>e2</u>

If blank, see adjacent bar code label

- 2. Maximum component temp <u>260</u> °C If blank, see adjacent label

J-609-4-4

Figure 4-4 Example of 2<sup>nd</sup> Level Interconnect Component Label Indicating a Pb-Free e2 Material with a Maximum Component Temperature of 260°C

## 2<sup>nd</sup> Level Interconnect is

- Category\_\_\_\_

If blank, see adjacent bar code label

- 2. Maximum component temp\_\_\_\_\_°C If blank, see adjacent label

J-609-4-5

Figure 4-5 Example of 2<sup>nd</sup> Level Interconnect Component Label Utilizing the Lead Free Symbol Indicating Both Pb-Free Material with Category and Maximum Component Temperature Indicated on an Adjacent Label

**4.3** 2<sup>nd</sup> Level Interconnect Component Label This label (see Figures 4-3, 4-4, and 4-5) is used to indicate the 2<sup>nd</sup> level interconnect terminal finish or material category (Clause 5) and maximum component temperature. The lead free (Pb-free) symbol (see 4.2) may be appended after the terms "2<sup>nd</sup> Level Interconnect" as indicated in Figure 4-5. This use of the Pb-free symbol applies only to the 2<sup>nd</sup> level interconnect and should not be interpreted as an indication that any other part of the component is Pb-free.

This label, if used, is placed/printed on the lowest level shipping container and any "ESD," "Dry pack," or other bag/box, excluding tubes, trays, reels or other carriers, within the lowest level shipping container.

- **4.3.1 Size** It is recommended that the label be a minimum of 75 mm by 50 mm.

- **4.3.2 Color** The label **shall** be black letters/symbols on a white or contrasting background.

#### **5 MARKING/LABELING CATEGORIES**

These categories are for the technical purposes of this document and are not to be used for determining regulatory compliance.

- **5.1 PCB Base Material Categories** The PCB base materials may be identified by using the classification system found in IPC-4101, where a unique Specification Sheet ("slash-sheet") number identifies a specific grade of material. Some of the common base materials expected to be used on PCBs are shown here. However, other grades of base materials are possible. These base materials have an epoxy resin system with woven-glass reinforcement, plus distinguishing properties.

- a) /92: Phosphorous flame retardant;  $T_{\rm g}$  110 to 150°C

- b) /95: Aluminum Hydroxide flame retardant;  $T_g$  150 to  $200^{\circ}C$

- c) /99: Bromine flame retardant; contains inorganic fillers;  $T_g$  150°C min.

- d) /126: Bromine flame retardant; contains inorganic fillers;  $T_{\rm g}$  170°C min.

For PCBs made with more than one grade of materials, mark or label the slash-sheet of the material with the lowest temperature rating.

- **5.1.1 Halogen-Free Base Material** If the base materials used in making the bare printed board are halogen-free, the label/marking "HF" **shall** be noted on the bare printed circuit board. If no "HF" is present, a halogen-containing base resin and reinforcement matrix are assumed. This marking applies only to the PCB base material and is not to be interpreted as an indication of a halogen-free (HF) assembly.

- **5.2 PCB Surface Finish Categories** The following categories describe the predominant surface finish on the bare board (prior to assembly).

#### 5.2.1 Pb-Containing

b0 – contains lead (Pb), traditional tin-lead (SnPb), hot air solder level (HASL) or solder reflow

#### 5.2.2 Pb-Free

- b1 lead (Pb) free HASL [tin (Sn) alloys with no bismuth (Bi) nor zinc (Zn)]

- b2 immersion silver (Ag)

- b3 tin (Sn) (electrolytic or immersion)

- b4 gold (Au) (immersion or electrolytic), electroless nickel immersion gold (ENIG), nickel gold (NiAu)

- b5 screened carbon (carbon ink)

- b6 organic solderability preservative (OSP)

- b7, b8 and b9 unassigned

**5.3** 2<sup>nd</sup> Level Interconnect Categories The following categories describe the 2<sup>nd</sup> level interconnect (see Figure 3-1) terminal finish or solder ball material of components or the solder paste/solder used in board assembly.

#### 5.3.1 Pb-Containing

e0 - contains intentionally added lead (Pb)6

#### 5.3.2 Pb-Free

- e1 tin-silver-copper (SnAgCu)

- e2 tin (Sn) alloys with no bismuth (Bi) nor zinc (Zn), excluding tin-silver-copper (SnAgCu)

- e3 tin (Sn)

- e4 precious metal [e.g., silver (Ag), gold (Au), nickel-palladium (NiPd), nickel-palladium-gold (NiPdAu) (no tin (Sn)]

- e5 tin-zinc (SnZn), tin-zinc-other (SnZnX) [all other alloys containing tin (Sn) and zinc (Zn) and not containing bismuth (Bi)]

- e6 contains bismuth (Bi)

- e7 low temperature solder (≤150°C) containing indium (In) [no bismuth (Bi)]

- e8 and e9 symbols unassigned

- **5.4 Conformal Coating Categories** The following categories (per IPC-CC-830) **shall** describe the conformal coating, if used:

ER – Epoxy Resin

UR - Urethane Resin

AR – Acrylic Resin

SR - Silicone Resin

XY – Paraxylylene

#### **6 COMPONENT MARKING AND LABELING**

**6.1 Component Marking** If space permits, the individual component **shall** be marked (per 5.3) on its topside with the Material Category designation enclosed within a circle, ellipse, underlined, or in parentheses (see 4.1). See Figure 6-1 for an example.

If the 2<sup>nd</sup> level interconnect termination finish or material is removed and replaced on a component, the original 'e' code marking on that physical component **shall** be obliterated and the component **shall** be remarked with the applicable 'e' code in accordance with this document.

**6.2 Lowest Level Shipping Container Labeling** The Material Category and the maximum component body temperature **shall** be indicated on the lowest level shipping container utilizing the 2<sup>nd</sup> level interconnect component

<sup>6.</sup> For Pb-containing 2<sup>nd</sup> level interconnect terminal finishes and materials, the lead (Pb) content for e0 is typically greater than or equal to 3% by weight. For Pb-containing solder, solder paste, and wave solder alloy, the lead (Pb) content is typically greater than 3% by weight and usually is 37% by weight.

Figure 6-1 Example of Component Marking

label (see 4.3). The use of the 2<sup>nd</sup> level interconnect component label is not required if the following information is included in human readable form on the bar code (linear or 2D) label or other nearby label:

- a) the words "2<sup>nd</sup> level interconnect" or equivalent abbreviation;

- b) the appropriate materials category from 5.3; and

- c) the maximum component body temperature.

The 2<sup>nd</sup> level interconnect component label applies only to components.

#### 7 PCB/ASSEMBLY MARKING AND LABELING

**7.1 PCB Marking** Any printed circuit board surface finish with lead (Pb) >0.1% **shall** be marked with the lead (Pb) category b0 (see 5.2.1).

Space permitting, the printed circuit board finish may be marked with the material categories defined in 5.2.2.

In addition, the base PCB material may also be marked with the material categories defined in 5.1. If specified by the purchaser, the PCB fabricator may be required to mark the PCB with the applicable category for solders (see 5.3) and/or conformal coating (see 5.4) to be used by the assembler.

- **7.1.1 PCB Shipping Container Labeling** The label on the lowest level PCB shipping container **shall** contain the information that is applicable to the bare board marking.

- **7.2 Assembly Marking** The solder paste/solder used **shall** be identified on an assembly, as defined in 5.3. If used, the conformal coating used **shall** be identified on an

assembly, per 5.4. If the PCB was previously marked with the applicable category for solders (see 5.3) and/or conformal coating (see 5.4) and the sequence written does not match the materials used during assembly, the PCBA **shall** be remarked in accordance with 7.10.

- **7.2.1 Assembly Shipping Container Labeling** The label on the lowest assembly level shipping container **shall** contain the information applicable to the assembly marking.

- **7.3 Solder Category Marking Sequence** If two or more solder alloy categories are used the category of the solders used **shall** be shown in the following sequence: Reflow, wave and other. For repair materials, refer to 7.10.

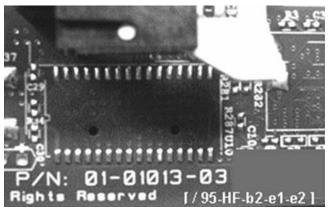

- **7.4 Location** The preferred location for marking the material categories on the board/assembly is on PCB layer 1 (topside) at the lower right-hand segment or next to the part/serial number on the board, or next to the company logo. The marking sequence **shall** be clearly identifiable and separate from other board markings. For instance, the marking sequence may be entirely within brackets or parentheses. See example in Figure 7-1. Alternative locations may be specified in procurement documentation.

- **7.5 Size** The size of the mark is optional but **shall** be legible to corrected, unmagnified vision.

- **7.6 Color** The color for the 'e' and category number **shall** be selected to provide sufficient contrast to be legible to corrected, unmagnified vision.

- **7.7 Font** The font style should be "Arial," "OCR-A" or equivalent.

- **7.8 Method** The methods for marking of the board (e.g., screen print, etch, laser, label, modification of existing bar code, etc.) are optional but **shall** be legible to corrected, unmagnified vision.

- **7.9 Marking Sequence** The sequence of marking, as required, **shall** be as follows:

- a) base material slash sheet number (see 5.1)

- b) halogen-free (see 5.1.1)

- c) PCB surface finish (see 5.2)

- d) reflow, wave and other solders (see 5.3)

- e) conformal coating (if applicable, see 5.4)

Figure 7-1 shows an example of board/assembly markings.

#### Examples:

Multifunctional epoxy, halogen-free FR-4 laminate PCB with immersion silver (Ag) surface finish; assembly used tin-silver-copper (SnAgCu) solder for reflow and a tin (Sn)

alloy with no bismuth (Bi) or zinc (Zn) excluding SnAgCu for wave attachment; no conformal coating.

/95 HF b2 e1 e2 or /95-HF-b2-e1-e2 or /95/HF/b2/e1/e2

Halogen containing epoxy FR-4 laminate PCB with Pb-containing surface finish; assembled with Pb-containing solder; epoxy conformal coating.

/99 b0 e0 ER or /99-b0-e0-ER or /99/b0/e0/ER

Figure 7-1 Example of Board/Assembly Markings

**7.10 Re-Marking Changes in PCBA Materials** If changes, rework, or repair to assemblies are made with a material finish category code different than marked, then the marking sequence in 7.3 **shall** be appended with the material code (see 7.3) for the rework or repair solder and/or conformal coating used.

#### 8 MARKING AND/OR LABELING OF LEAD (Pb)-CONTAINING COMPONENTS, PCBs, AND PCB ASSEM-BLIES

The use of any markings, labels, or symbols that contain the phrase "Pb-free" or the Pb-free symbol shown in Figure 4-2 for this clause is prohibited.

- **8.1 Marking and Labeling of Components** Suppliers whose customers require labeling and marking to indicate lead (Pb) content in 2<sup>nd</sup> level interconnect finishes and materials **shall** utilize the Material Category code established in 5.3.1 (e0). The alternate 2<sup>nd</sup> level interconnect component label as shown in Figure 4-3 **shall** be used unless the following information is included on the bar code (2D or linear) or other nearby label, in human readable form:<sup>7</sup>

- a) the words "2<sup>nd</sup> level interconnect" or equivalent abbreviation:

- b) the appropriate materials category from 5.3.1; and

- c) the maximum component body temperature.

The 2<sup>nd</sup> level interconnect component label applies only to components.

- **8.2 Marking and Labeling of PCBs** Suppliers whose customers require labeling and marking of PCBs to indicate lead (Pb) content in PCB surface finishes **shall** utilize the Material Category code(s) as established in 5.2.1 (b0). Solders to be used in assembly may be marked with category code (e0) on the PCB if specified by purchaser.

- **8.3 Marking and Labeling of PCB Assemblies** Suppliers whose customers require labeling and marking of the PCB assembly to indicate lead (Pb) content in assembly solders **shall** utilize the Material Category code(s) as established in 5.3.1 (e0).

<sup>7.</sup> If the required information is included on another label, the use of the 2<sup>nd</sup> level interconnect label becomes optional.

#### 9 SUMMARY OF MARKING AND LABELING REQUIREMENTS

Table 9-1 summarizes the marking and labeling requirements detailed previously in this document.

Table 9-1 Marking and Labeling Summary

|                                            |                                                                                                             | Marking or Labeling Content Requirements                                                                                                                                                            |                                                                                                                                           |                                                                                                                  |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| Item                                       | Preferred Location                                                                                          | Required                                                                                                                                                                                            | Optional                                                                                                                                  | Comments                                                                                                         |

| Component<br>Marking<br>(Clause 6)         | Component body, topside                                                                                     | Material category for<br>component terminal<br>finish or material (5.3)                                                                                                                             | Maximum component body temperature (3.13)                                                                                                 | Space permitting                                                                                                 |

| Component<br>Container Label<br>(Clause 6) | Lowest level shipping container AND any "ESD," "Dry Pack" or other bag or box within the shipping container | Material category for<br>component terminal<br>finish or material (5.3)      Maximum component<br>body temperature (3.13)                                                                           | <ul> <li>Pb-free symbol or the<br/>phrase 'Pb-free' (4.2)</li> <li>2<sup>nd</sup> Level Interconnect<br/>Component Label (4.3)</li> </ul> |                                                                                                                  |

| PCB Marking<br>(7.1)                       | Topside, lower right-<br>hand corner; or next<br>to part/serial number<br>or company logo                   | - PCB surface finish containing lead (Pb) (5.2.1), if applicable  - Halogen-free mark [HF] if applicable (5.1.1)  - Solders and conformal coating to be used by assembler if specified by purchaser | <ul><li>IPC 4101 slash-sheet<br/>number (5.1)</li><li>Pb-free PCB surface<br/>finish</li></ul>                                            | Sequence:<br>Slash-sheet, [HF],<br>PCB finish, solders,<br>[conformal coating] (7.9)                             |

| PCB Container<br>Label (7.1.1)             | Lowest level container holding PCBs                                                                         | Mark or label with the information applicable to the PCB                                                                                                                                            | Halogen-free mark [HF] if applicable (5.1.1)                                                                                              |                                                                                                                  |

| PCBA Marking<br>(7.2)                      | Topside, lower right-hand corner; or next to part/ serial number, or company logo                           | - Mark with material category for assembly solder type(s) used (5.3) in the order of application (7.3) - Conformal Coating, if any (5.4)                                                            |                                                                                                                                           | Pb-free symbol marking<br>or label cannot be used<br>on PCBA if any compo-<br>nent is not lead-free<br>(Pb-free) |

| PCBA Container<br>Label (7.2.1)            | Lowest level container holding PCBAs                                                                        | Mark or label with the information applicable to the PCBA                                                                                                                                           |                                                                                                                                           |                                                                                                                  |

#### Annex A

(informative)

#### **Acknowledgment**

Any document involving a complex technology draws material from a vast number of sources. While the principal members of the Marking, Symbols and Labels for Identification of Assemblies, Components and Devices Task Group (4-34b) are sshown below, it is not possible to include all of those who assisted in the evolution of this document. To each of them, the members of the IPC extend their gratitude.

Marking, Symbols and Labels for Identification of Assemblies, **Components and Devices Task Group**

**Technical Liaisons of the IPC Board of Directors**

**JEDEC COMMITTEE JC14.4 -Quality Processes and Methods**

Co-Chairs

Jasbir Bath Solectron Corporation

Intel Corporation

Jack McCullen

IMI Inc. Sammy Yi

Peter Bigelow

Flextronics International

Chair Curtis Grosskopf **IBM** Corporation

Lee R. Wilmot TTM Technologies

#### Marking, Symbols and Labels for Identification of Assemblies, Components and Devices Task Group

Jasbir Bath, Solectron Corporation Christine Blair, STMicroelectronics,

Les Bogert, Bechtel

Ana L. Campuzano-Contreras, BAE Systems

Mary Carter Berrios, KEMET **Electronics Corporation**

Marie Cole, IBM Corporation

Peter Cote, Hamilton Sundstrand

Don Dupriest, Lockheed Martin Missiles and Fire Control - Dallas

Stephen Edward, Merix Corporation

Adam Fogle, Spansion

Kevin Gallagher, LeeMAH Electronics

Andy Ganster, Crane Division, (NSWC)

Denis Gignac, Nortel

Curtis Grosskopf, IBM Corporation

Gregory Henshall, Hewlett Packard

Joseph Kane, BAE Systems

Theodore Krueger, Vishay General

Semiconductor

Nick Lycoudes, Freescale

Semiconductor

Karen McConnell, Lockheed Martin

Jack McCullen, Intel

Sean McDermott, Celestica

International Inc.

Arnold Offner, Phoenix Contact

Elvira Preecha, Qualcomm

Patrick Roubaud, Hewlett Packard Valerie St. Cyr, Teradyne, Inc.

Richard Shook, Agere

Harry Siegel, STMicroelectronics,

Kevin Weston, Celestica International

George Wilkish, Tyco Electronics/ MA/COM

Lee Wilmot, TTM Technologies

Linda Woody, Lockheed Martin Robert Vanderwiel, Lockheed Martin

Aero Fort Worth

# INTERNATIONAL ELECTROTECHNICAL COMMISSION

3, rue de Varembé PO Box 131 CH-1211 Geneva 20 Switzerland

Tel: + 41 22 919 02 11 Fax: + 41 22 919 03 00 info@iec.ch www.iec.ch