Edition 1.0 2007-11

LICENSED TO MECON Limited. - RANCHI/BANGALORE FOR INTERNAL USE AT THIS LOCATION ONLY, SUPPLIED BY BOOK SUPPLY BUREAU.

## INTERNATIONAL STANDARD

IEEE 1450.2™

Standard for Extensions to Standard Test Interface Language (STIL) for DC Level Specification

#### THIS PUBLICATION IS COPYRIGHT PROTECTED

#### Copyright © 2007 IEEE

All rights reserved. IEEE is a registered trademark in the U.S. Patent & Trademark Office, owned by the Institute of Electrical and Electronics Engineers, Inc.

Unless otherwise specified, no part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from the IEC Central Office.

Any questions about IEEE copyright should be addressed to the IEEE. Enquiries about obtaining additional rights to this publication and other information requests should be addressed to the IEC or your local IEC member National Committee.

IEC Central Office 3, rue de Varembé CH-1211 Geneva 20 Switzerland

Email: inmail@iec.ch Web: www.iec.ch The Institute of Electrical and Electronics Engineers, Inc

3 Park Avenue

US-New York, NY10016-5997

USA

Email: stds-info@ieee.org Web: www.ieee.org

#### About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes International Standards for all electrical, electronic and related technologies.

#### **About IEC publications**

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the latest edition, a corrigenda or an amendment might have been published.

Catalogue of IEC publications: www.iec.ch/searchpub

The IEC on-line Catalogue enables you to search by a variety of criteria (reference number, text, technical committee,...). It also gives information on projects, withdrawn and replaced publications.

IEC Just Published: www.iec.ch/online\_news/justpub

Stay up to date on all new IEC publications. Just Published details twice a month all new publications released. Available on-line and also by email.

■ Electropedia: www.electropedia.org

The world's leading online dictionary of electronic and electrical terms containing more than 20 000 terms and definitions in English and French, with equivalent terms in additional languages. Also known as the International Electrotechnical Vocabulary online.

Customer Service Centre: www.iec.ch/webstore/custserv

If you wish to give us your feedback on this publication or need further assistance, please visit the Customer Service Centre FAQ or contact us:

Email: csc@iec.ch Tel.: +41 22 919 02 11 Fax: +41 22 919 03 00

Edition 1.0 2007-11

### INTERNATIONAL STANDARD

IEEE 1450.2<sup>™</sup>

Standard for extensions to Standard Test Interface Language (STIL) for d.c. level specification

INTERNATIONAL ELECTROTECHNICAL COMMISSION

PRICE CODE

ICS 25.040

#### **CONTENTS**

| FOR | REWORD                                                                          | 4  |

|-----|---------------------------------------------------------------------------------|----|

| IEE | EE Introduction                                                                 | 7  |

| 1.  | Overview                                                                        | 8  |

|     | 1.1 Scope                                                                       | C  |

|     | 1.2 Purpose                                                                     |    |

|     | F                                                                               |    |

| 2.  | References                                                                      | 10 |

| 3.  | Definitions, acronyms, and abbreviations                                        | 10 |

|     | 3.1 Definitions                                                                 | 10 |

|     | 3.2 Acronyms and abbreviations                                                  | 13 |

| 4.  | Structure of this standard                                                      | 14 |

| 5.  | Extensions to Clause 6, STIL syntax description                                 | 14 |

|     | 5.1 Additional reserved words                                                   | 14 |

|     | 5.2 DC expressions and units (dc expr)                                          |    |

|     | 5.3 Additions to STIL name spaces and name resolution (IEEE Std 1450-1999, 6.10 |    |

| 6.  | Statement structure and organization of STIL information                        | 15 |

|     | 6.1 Top-level statements and required ordering                                  | 15 |

|     | 6.2 Optional top-level statements                                               |    |

| 7.  | Extensions to Clause 8, STIL statement                                          | 16 |

|     | 7.1 STIL syntax                                                                 | 17 |

|     | 7.2 STIL example                                                                |    |

| 8.  | Extensions to Clause 19, Spec and Selector blocks                               | 17 |

| 9.  | Extensions to Clause 16, PatternExec block                                      | 17 |

|     | 9.1 PatternExec block syntax                                                    | 17 |

|     | 9.2 PatternExec block example                                                   | 18 |

|     | 9.3 DCLevels and DCSets usage in PatternExec and Pattern blocks                 | 18 |

| 10. | DCLevels block                                                                  | 18 |

|     | 10.1 DCLevels block syntax                                                      | 19 |

|     | 10.2 DCLevels block example                                                     |    |

|     | 10.3 InheritDCLevels Processing                                                 |    |

|     | 10.4 InheritDCLevels example                                                    | 33 |

| 11. | DCSets block                                                                    |    |

|     | 11.1 DCSets block syntax                                                        | 34 |

|     | 11.2 DCSets statement example                                                   |    |

| 12.   | DCSequence block                                      | 24       |

|-------|-------------------------------------------------------|----------|

|       | 12.1 DCSequence block syntax 12.2 DCSequence example  | 25<br>26 |

| 13.   | Extensions to Clause 18, WaveformTable block          | 28       |

|       | 13.1 Event definition in WaveformTable block          | 28       |

|       | 13.2 Mapping of event integers to DCLevels statements | 29       |

|       | 13.3 DC levels switching example                      | 30       |

| 14.   | Extensions to Clause 22, STIL Pattern statements      | 31       |

|       | 14.1 DCLevels statement                               | 31       |

|       | 14.2 DCLevels statement example                       | 31       |

| Annex | A (informative) DCLevels and DCSets usage example     | 32       |

| Annex | B (informative) Bibliography                          | 38       |

| Annex | C (informative) List of participantss                 | 39       |

#### INTERNATIONAL ELECTROTECHNICAL COMMISSION

#### STANDARD FOR EXTENSIONS TO STANDARD TEST INTERFACE LANGUAGE (STIL) FOR DC LEVEL SPECIFICATION

#### **FOREWORD**

- 1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as "IEC Publication(s)"). Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely with the International Organization for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- 2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC National Committees.

- 3) IEC Publications have the form of recommendations for international use and are accepted by IEC National Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

- 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter.

- 5) IEC provides no marking procedure to indicate its approval and cannot be rendered responsible for any equipment declared to be in conformity with an IEC Publication.

- 6) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

International Standard IEC/IEEE 62527 has been processed through Technical Committee 93: Design automation.

The text of this standard is based on the following documents:

| IEEE Std     | FDIS        | Report on voting |

|--------------|-------------|------------------|

| 1450.2(2005) | 93/249/FDIS | 93/260/RVD       |

Full information on the voting for the approval of this standard can be found in the report on voting indicated in the above table.

The committee has decided that the contents of this publication will remain unchanged until the maintenance result date indicated on the IEC web site under "http://webstore.iec.ch" in the data related to the specific publication. At this date, the publication will be

- reconfirmed,

- withdrawn,

- replaced by a revised edition, or

- · amended.

#### **IEC/IEEE Dual Logo International Standards**

This Dual Logo International Standard is the result of an agreement between the IEC and the Institute of Electrical and Electronics Engineers, Inc. (IEEE). The original IEEE Standard was submitted to the IEC for consideration under the agreement, and the resulting IEC/IEEE Dual Logo International Standard has been published in accordance with the ISO/IEC Directives.

IEEE Standards documents are developed within the IEEE Societies and the Standards Coordinating Committees of the IEEE Standards Association (IEEE-SA) Standards Board. The IEEE develops its standards through a consensus development process, approved by the American National Standards Institute, which brings together volunteers representing varied viewpoints and interests to achieve the final product. Volunteers are not necessarily members of the Institute and serve without compensation. While the IEEE administers the process and establishes rules to promote fairness in the consensus development process, the IEEE does not independently evaluate, test, or verify the accuracy of any of the information contained in its standards.

Use of an IEC/IEEE Dual Logo International Standard is wholly voluntary. The IEC and IEEE disclaim liability for any personal injury, property or other damage, of any nature whatsoever, whether special, indirect, consequential, or compensatory, directly or indirectly resulting from the publication, use of, or reliance upon this, or any other IEC or IEEE Standard document.

The IEC and IEEE do not warrant or represent the accuracy or content of the material contained herein, and expressly disclaim any express or implied warranty, including any implied warranty of merchantability or fitness for a specific purpose, or that the use of the material contained herein is free from patent infringement. IEC/IEEE Dual Logo International Standards documents are supplied "AS IS".

The existence of an IEC/IEEE Dual Logo International Standard does not imply that there are no other ways to produce, test, measure, purchase, market, or provide other goods and services related to the scope of the IEC/IEEE Dual Logo International Standard. Furthermore, the viewpoint expressed at the time a standard is approved and issued is subject to change brought about through developments in the state of the art and comments received from users of the standard.

Every IEEE Standard is subjected to review at least every five years for revision or reaffirmation. When a document is more than five years old and has not been reaffirmed, it is reasonable to conclude that its contents, although still of some value, do not wholly reflect the present state of the art. Users are cautioned to check to determine that they have the latest edition of any IEEE Standard.

In publishing and making this document available, the IEC and IEEE are not suggesting or rendering professional or other services for, or on behalf of, any person or entity. Neither the IEC nor IEEE is undertaking to perform any duty owed by any other person or entity to another. Any person utilizing this, and any other IEC/IEEE Dual Logo International Standards or IEEE Standards document, should rely upon the advice of a competent professional in determining the exercise of reasonable care in any given circumstances.

Interpretations – Occasionally questions may arise regarding the meaning of portions of standards as they relate to specific applications. When the need for interpretations is brought to the attention of IEEE, the Institute will initiate action to prepare appropriate responses. Since IEEE Standards represent a consensus of concerned interests, it is important to ensure that any interpretation has also received the concurrence of a balance of interests. For this reason, IEEE and the members of its societies and Standards Coordinating Committees are not able to provide an instant response to interpretation requests except in those cases where the matter has previously received formal consideration.

Comments for revision of IEC/IEEE Dual Logo International Standards are welcome from any interested party, regardless of membership affiliation with the IEC or IEEE. Suggestions for changes in documents should be in the form of a proposed change of text, together with appropriate supporting comments. Comments on standards and requests for interpretations should be addressed to:

Secretary, IEEE-SA Standards Board, 445 Hoes Lane, P.O. Box 1331, Piscataway, NJ 08855-1331, USA and/or General Secretary, IEC, 3, rue de Varembé, PO Box 131, 1211 Geneva 20, Switzerland.

Authorization to photocopy portions of any individual standard for internal or personal use is granted by the Institute of Electrical and Electronics Engineers, Inc., provided that the appropriate fee is paid to Copyright Clearance Center. To arrange for payment of licensing fee, please contact Copyright Clearance Center, Customer Service, 222 Rosewood Drive, Danvers, MA 01923 USA; +1 978 750 8400. Permission to photocopy portions of any individual standard for educational classroom use can also be obtained through the Copyright Clearance Center.

NOTE – Attention is called to the possibility that implementation of this standard may require use of subject matter covered by patent rights. By publication of this standard, no position is taken with respect to the existence or validity of any patent rights in connection therewith. The IEEE shall not be responsible for identifying patents for which a license may be required by an IEEE standard or for conducting inquiries into the legal validity or scope of those patents that are brought to its attention.

IEEE Standard for Extensions to Standard Test Interface Language (STIL) (IEEE Std 1450<sup>TM</sup>-1999) for DC Level Specification

Sponsor

Test Technology Standards Committee of the IEEE Computer Society

Approved 11 December 2002

**IEEE-SA Standards Board**

**Abstract:** This standard extends IEEE Std 1450-1999 (STIL) to support the definition of DC levels. STIL language constructs are defined to specify the DC conditions necessary to execute digital vectors on automated test equipment (ATE). STIL language extensions include structures for: (a) specifying the DC conditions for a device under test; (b) specifying DC conditions either globally, by pattern burst, by pattern, or by vector; (c) specifying alternate DC levels; and (d) selecting DC levels and alternate levels within a period, much the same as timed format events.

**Keywords:** automated test equipment (ATE), comparator, DC levels, device power supply (DPS), device under test (DUT), driver, driver termination, dynamic load, functional test, parametric measurement unit (PMU), power sequence, slew rate, voltage clamp

#### **IEEE Introduction**

Standard Test Interface Language (STIL) (IEEE Std 1450-1999) was developed and approved with an intentionally constrained scope. While DC levels were explicitly excluded from that scope, it was apparent that DC levels were an area of interest and importance to the STIL user community. The P1450.2 Working Group was formed to address the extension of DC levels to the STIL standard.

Three main topics were identified as priorities for the work. These include per-pin reference levels for signal pins (e.g., VIH, VIL, VOH, VOL), device power supply levels (voltage and current), and power sequencing to the device under test. During the course of development, two other important topics were addressed. These included the capability for switching levels within a period, and for switching levels between vectors in a pattern.

# STANDARD FOR EXTENSIONS TO STANDARD TEST INTERFACE LANGUAGE (STIL) (IEEE Std 1450<sup>TM</sup>-1999) FOR DC LEVEL SPECIFICATION

#### 1. Overview

This standard extends IEEE Std 1450-1999<sup>1</sup> (STIL) to support the definition of DC levels. The DC levels information consists of the per-pin reference levels, the device power supply (DPS) levels, and the sequencing of these levels for powering up the device, powering down the device, or changing levels of the device. The DC level definitions may be defined as static states that are established prior to execution of a pattern. They also may be selected within a pattern.

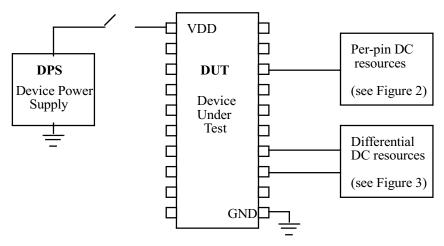

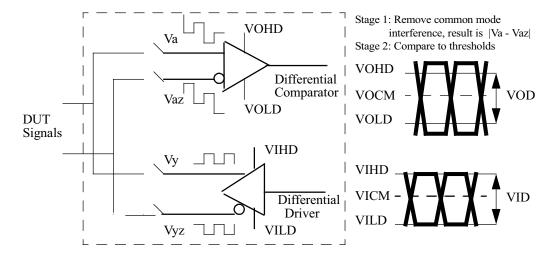

Figure 1 is a model of the test environment for a device under test (DUT) on an automatic test equipment (ATE) tester. Figure 2 is a model of the per-pin DC resources of an ATE tester. Figure 3 is a model of the differential DC resources of an ATE tester. The statements and blocks defined in this standard are defined relative to these models. Some functions represented by these models may not be available on some ATE systems. The DCSequence commands Apply and Connect load values into the hardware registers, e.g., VIL and VIH, and connect the tester resource, e.g., the driver, to the DUT, respectively.

Figure 1—STIL model of DUT test environment on ATE tester

<sup>&</sup>lt;sup>1</sup>Information on references can be found in Clause 2.

#### 1.1 Scope

This standard defines the following:

- a) Defines structures in STIL for specifying the DC conditions for a DUT. Examples of the DC conditions for device power supplies are DPS setup, power sequencing to the device, and power supply limiting/clamping. Examples of the DC conditions for commonly used signal references are VIL, VIH, VOL, VOH, IOL, IOH, VREF, VClampLow, and VClampHi.

- b) Defines structures in STIL such that the DC conditions may be specified either globally, by pattern burst, by pattern, or by vector.

- c) Defines structures in STIL to allow specification of alternate DC levels. Examples of commonly used alternate levels are VIHH, VIPP, and VILL.

- d) Defines structures in STIL such that the DC levels and alternate levels can be selected within a period, much the same as timed format events.

Figure 2—STIL model of per-pin DC resources of ATE tester

Figure 3—STIL model of differential DC resources of ATE tester

#### 1.2 Purpose

This effort will define constructs in STIL to specify the DC conditions necessary to execute the digital vectors on ATE. This will complement the IEEE Std 1450-1999 definition, which defines structures for specification of timing and format information but does not define the DC conditions under which this information should be applied.

#### 2. References

This standard shall be used in conjunction with the following standard. If the following standard is superseded by an approved revision, the revision shall apply.

IEEE Std 1450-1999, IEEE Standard Test Interface Language (STIL) for Digital Test Vectors. <sup>2, 3</sup>

#### 3. Definitions, acronyms, and abbreviations

#### 3.1 Definitions

For the purposes of this standard, the following terms and definitions apply. IEEE  $100^{\text{TM}}$  [B1]<sup>4</sup> should be referenced for terms not defined in this standard.

**3.1.1 alternate input high voltage (VIHH):** An alternate input high voltage forced by the ATE driver to the DUT.

<sup>&</sup>lt;sup>2</sup>The IEEE standards referred to in Clause 2 are trademarks owned by the Institute of Electrical and Electronics Engineers, Inc.

<sup>&</sup>lt;sup>3</sup>IEEE publications are available from the Institute of Electrical and Electronics Engineers, 445 Hoes Lane, P.O. Box 1331, Piscataway, NJ 08855-1331, USA (http://standards.ieee.org/).

<sup>&</sup>lt;sup>4</sup>The numbers in brackets correspond to those of the bibliography in Annex B.

- **3.1.2** alternate input high voltage (VIPP): An alternate input high voltage forced by the ATE driver to the DUT. This is typically used to generate programming pulses for electrically programmable memories and is synonymous with the commonly used term VPP in the context of programming voltage.

- **3.1.3 alternate input low voltage (VILL):** An alternate input low voltage forced by the ATE driver to the DUT.

- **3.1.4 automatic test equipment (ATE):** A system that provides a test capability for the automatic testing of one or more devices under test (DUT).

- **3.1.5 clamp current (IClamp):** The maximum current allowed for a DPS or PMU.

- **3.1.6 clamp voltage (VClamp):** The maximum voltage allowed for a DPS or PMU.

- **3.1.7 comparator:** A component of an ATE that senses voltage response from the DUT during functional testing.

- **3.1.8 device power supply (DPS):** A component of an ATE that provides DC voltage and/or current to the DUT power supply pins.

- **3.1.9 device under test (DUT):** An electronic component, typically an integrated circuit, to be tested by an ATE

- **3.1.10 differential comparator:** A component of an ATE that senses voltage difference between two DUT outputs during functional testing.

- **3.1.11 differential driver:** A component of an ATE that provides voltage difference to two DUT inputs during functional testing.

- **3.1.12 differential input high voltage (VIHD):** The differential input high voltage forced by the ATE driver to the DUT.

- **3.1.13 differential input low voltage (VILD):** The differential input low voltage forced by the ATE driver to the DUT.

- **3.1.14 differential input voltage (VID):** The differential input voltage forced by the ATE driver to the DUT. VID = |VIHD VILD|.

NOTE—See Figure 3.

- **3.1.15 differential output high voltage (VOHD):** The differential output high reference voltage used by the ATE comparator to define minimum output high voltage from the DUT.

- **3.1.16 differential output low voltage (VOLD):** The differential output low reference voltage used by the ATE comparator to define maximum output low voltage from the DUT.

- **3.1.17 differential output voltage (VOD):** The differential output voltage received by the ATE comparator from the DUT. VOD = |VOHD VOLD|.

NOTE—See Figure 3.

**3.1.18 driver:** A component of an ATE that provides voltage stimulus to the DUT during functional testing.

- **3.1.19 driver termination:** A component of an ATE that provides impedance matching between the ATE driver and the DUT during functional testing.

- **3.1.20 dynamic load:** A component of an ATE that provides current loading to the DUT during functional testing.

- 3.1.21 force current (IForce): The forcing current provided by a DPS or PMU to the DUT.

- 3.1.22 force voltage (VForce): The forcing voltage provided by a DPS or PMU to the DUT.

- **3.1.23 functional test:** The process of applying functional vectors to the DUT and verifying the expected response from the DUT using an ATE. Refer to 3.1.10 of IEEE Std 1450-1999, for definition of functional vector.

- 3.1.24 high clamp voltage (ClampHi): The voltage level set for the high clamp circuit.

- **3.1.25 input common mode voltage (VICM):** The input common mode voltage used to reference the differential input voltages forced by the ATE driver to the DUT. VICM = (VIHD + VILD)/2.

NOTE—See Figure 3.

- 3.1.26 input high voltage (VIH): The input high voltage forced by the ATE driver to the DUT.

- 3.1.27 input low voltage (VIL): The input low voltage forced by the ATE driver to the DUT.

- **3.1.28 LoadVRef:** The commutating voltage of the ATE dynamic load. When no current is flowing, this is the voltage applied to the DUT.

- 3.1.29 low clamp voltage (ClampLo): The voltage level set for the low clamp circuit.

- **3.1.30 negative terminal input voltage (Vyz):** The negative terminal differential input voltage from the ATE driver to the DUT. Vyz is the complement of Vy.

NOTE—See Figure 3.

**3.1.31 negative terminal output voltage (Vaz):** The negative terminal differential output voltage from the DUT. Vaz is the complement of Va.

NOTE—See Figure 3.

**3.1.32 output common mode voltage (VOCM):** The output common mode voltage used to reference the differential output voltages received by the ATE comparator from the DUT. VOCM = (VOHD + VOLD)/2.

NOTE—See Figure 3.

- 3.1.33 output high current (IOH): The output high current provided by the ATE dynamic load to the DUT.

- **3.1.34 output high voltage (VOH):** The output high reference voltage used by the ATE comparator to define minimum output high voltage from the DUT.

- **3.1.35 output low current (IOL):** The output low current provided by the ATE dynamic load to the DUT.

- **3.1.36 output low voltage (VOL):** The output low reference voltage used by the ATE comparator to define maximum output low voltage from the DUT.

- 3.1.37 parametric measurement unit (PMU): A component of an ATE that forces DC voltage or current to the DUT, and measures DC current or voltage from the DUT.

- 3.1.38 positive terminal input voltage (Vy): The positive terminal differential input voltage from the ATE driver to the DUT.

NOTE—See Figure 3.

3.1.39 positive terminal output voltage (Va): The positive terminal differential output voltage from the DUT.

NOTE—See Figure 3.

- **3.1.40 ResistiveTermination:** A specific resistance value for terminating the ATE driver.

- 3.1.41 slew rate for input high voltage (VIHSlew): The slew rate for the ATE driver when transitioning to the input high voltage, specified in units of volts per time.

- 3.1.42 slew rate for input low voltage (VILSlew): The slew rate for the ATE driver when transitioning to the input low voltage, specified in units of volts per time.

- **3.1.43 TermVRef:** The voltage to which the ATE driver is terminated using ResistiveTermination.

- **3.1.44 voltage clamp:** A protection circuit used to limit the voltage swing seen by the DUT and/or ATE.

#### 3.2 Acronyms and abbreviations

ATE automatic test equipment ClampHi high clamp voltage ClampLo low clamp voltage DPS device power supply device under test DUT **GND** device ground pin

clamp current for DPS or PMU **IClamp IForce** forcing current for DPS or PMU

output high current IOH IOL output low current

LoadVRef commutating voltage of dynamic load

**PMU** parametric measurement unit

ResistiveTermination resistance value for terminating ATE driver TermVRef termination voltage for ResitiveTermination Va positive terminal differential output voltage negative terminal differential output voltage Vaz

clamp voltage for DPS or PMU **VClamp**

VDD device power pin

VForce forcing voltage for DPS or PMU input common mode voltage VICM VID differential input voltage VIH

input high voltage

**VIHD** differential input high voltage VIHH alternate input high voltage VIHSlew slew rate for input high voltage

VIL input low voltage VILD differential input low voltage

VILL alternate input low voltage

VILSlew slew rate for input low voltage

VIPP alternate input high voltage

VOCM output common mode voltage

VOD differential output voltage

VOH output high reference voltage

VOHD differential output high reference voltage

VOL output low reference voltage

VOLD differential output low reference voltage

VPP programming voltage for electrically programmable memories

Vy positive terminal differential input voltage Vyz negative terminal differential input voltage

#### 4. Structure of this standard

This standard is structured as an adjunct to IEEE Std 1450-1999. Please refer to IEEE Std 1450-1999 for information with regard to the conventions used in this standard. In most cases, the clauses in this standard are to add new constructs to existing clauses in IEEE Std 1450-1999 and are so identified in the title. The DCLevels, DCSets, and DCSequence blocks are new constructs that are introduced in this standard. All clauses in this standard are normative. Example code is provided within each clause. More complete examples of code are provided in informative Annex A.

#### 5. Extensions to Clause 6, STIL syntax description

All constructs and restrictions for IEEE Std 1450-1999, Clause 6, are in effect here, with the following additions:

- Additional STIL reserved words specific within the context of this standard

- A new type of expression dc\_expr as defined in 5.2.

#### 5.1 Additional reserved words

Table 1 lists all STIL reserved words defined by this standard. Subsequent clauses in this standard identify the use and context of each of these additional reserved words.

#### 5.2 DC expressions and units (dc\_expr)

DC expressions follow the characteristics defined for timing expressions in 6.13 of IEEE Std 1450-1999. DC expressions are enclosed in single quotes and contain the same entities as timing expressions. Expressions that compute to units of volts, amps, or ohms may be used in a dc expression. In addition, complex expressions that are expressed as a ratio of two values (e.g., a slew rate of '1V/1ns') may be used in a dc expression.

There are three contexts where DC expressions may occur. The first context is in the Spec block as part of a spec variable definition. The second context is in the DCLevels block, to define a value associated with a DCLevels statement. The third context is in the DCSequence block, to define a value associated with a DCSequence operation.

#### Table 1—Additional STIL reserved words

-15-

| Apply                                                                                              |

|----------------------------------------------------------------------------------------------------|

| Clamp, ClampHi, ClampLo, Comparator, Connect                                                       |

| DCLevels, DCSequence, DCSets, Disconnect, Driver                                                   |

| EndOfProgram                                                                                       |

| ForceHi, ForceLo                                                                                   |

| IClamp, IForce, InheritDCLevels, InitHi, InitialSetup, InitLo, IOH, IOL                            |

| Load, LoadVRef                                                                                     |

| PMU, PowerLower, PowerRaise                                                                        |

| Ramp, ResistiveTermination                                                                         |

| Termination, TermVRef                                                                              |

| User                                                                                               |

| VClamp, VForce, VICM, VID, VIH, VIHD, VIHSlew, VIL, VILD, VILSlew, VOCM, VOD, VOH, VOHD, VOL, VOLD |

#### 5.3 Additions to STIL name spaces and name resolution (IEEE Std 1450-1999, 6.16)

DCLevels, DCSets, and DCSequence blocks augment the STIL name space as defined in Table 2. This table is incremental to IEEE Std 1450-1999, Table 6; all definitions present in that table remain unchanged.

Table 2—Additional STIL name space

| STIL block | Type of name            | Domain restrictions                                                                                                        |

|------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------|

| DCLevels   | DCLevels domain names   | Supports a single unnamed global block and domain name blocks.  Domain names shall be unique across all DCLevels blocks.   |

| DCSets     | DCSets domain names     | Supports a single unnamed global block and domain name blocks.  Domain names shall be unique across all DCSets blocks.     |

| DCSequence | DCSequence domain names | Supports a single unnamed global block and domain name blocks.  Domain names shall be unique across all DCSequence blocks. |

#### 6. Statement structure and organization of STIL information

This standard defines three additional top-level STIL blocks: DCLevels (Clause 10), DCSets (Clause 11), and DCSequence (Clause 12). These blocks relate to the top-level blocks of IEEE Std 1450-1999 as defined in 6.1 and 6.2.

#### 6.1 Top-level statements and required ordering

The DCLevels and DCSets blocks, if present, have a required ordering with respect to other STIL blocks defined in IEEE Std 1450-1999. This ordering is shown in Table 3. This table is incremental to Table 7 in IEEE Std 1450-1999 and indicates the required position of these two blocks with respect to definitions

present in IEEE Std 1450-1999. All other definitions and requirements specified in Table 7 of IEEE Std 1450-1999 remain unchanged.

Table 3—STIL top-level statements and ordering requirements

| Statement                          | Purpose                                                                                                                                                                                                                                                                                                                  |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Timing (from IEEE Std 1450-1999)   | As defined in IEEE Std 1450-1999.                                                                                                                                                                                                                                                                                        |

| DCLevels                           | Defines the DC levels to be applied to signal pins and power supply pins for each PatternExec. DC expressions in this block may reference variables defined in Spec blocks, but DC variables are not resolved until the PatternExec. DCLevels blocks shall precede any DCSets or PatternExec blocks that reference them. |

| DCSets                             | Identifies a set of DCLevels that may be referenced in a Pattern block. DCSets blocks shall precede any PatternExec blocks that reference them.                                                                                                                                                                          |

| Selector (from IEEE Std 1450-1999) | As defined in IEEE Std 1450-1999.                                                                                                                                                                                                                                                                                        |

#### 6.2 Optional top-level statements

DCSequence blocks, if present, do not have a **defined** order with respect to other STIL sections as defined in IEEE Std 1450-1999. DCSequence blocks may appear any place a top-level STIL statement is allowed. This is delineated in Table 4, which is provided to be complete with Table 8 in IEEE Std 1450-1999.

Table 4—Optional top-level statements

| Statement  | Purpose                                                                                                                                                                     |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DCSequence | Defines the timed sequence in which power is to be applied. DCSequence blocks, if referencing other STIL data, shall be defined after the blocks that define the STIL data. |

#### 7. Extensions to Clause 8, STIL statement

The STIL statement identifies the primary version of STIL (IEEE Std 1450-1999) information contained in an STIL file and the presence of one or more standard extension constructs. The primary version of STIL is defined in IEEE Std 1450-1999.

The extension to the STIL statement allows for a block containing extension identifiers that allow for additional constructs in the STIL file. There may be multiple extension statements present, to identify the presence of multiple extension environments. The extension name and the extension statements are defined in the individual documents for those standards.

All other constructs and restrictions for IEEE Std 1450-1999, Clause 8, are in effect here.

#### 7.1 STIL syntax

#### 7.2 STIL example

```

STIL 1.0 {

DCLevels 2002;

}

```

#### 8. Extensions to Clause 19, Spec and Selector blocks

All capabilities and constructs defined in IEEE Std 1450-1999, Clause 19, are maintained for this standard, with the addition that Spec blocks are also used to define the value of the variables and expressions that are used within dc expressions.

#### 9. Extensions to Clause 16, PatternExec block

The PatternExec block is extended to include two optional reference statements for specifying DC levels. The DCLevels block defines the DC levels for all signals referenced in the PatternExec. The DCSets block is a collection of DCLevels references which appear in the Pattern blocks associated with the PatternExec. The DCSets block is used to resolve references to DCLevels blocks in the Pattern blocks.

#### 9.1 PatternExec block syntax

```

PatternExec (PAT_EXEC_NAME) {

(DCLevels (DC_LEVELS_NAME);)

(DCSets (DC_SETS_NAME);)

}

```

**PatternExec**: This block defines all of the top-level information for a pattern execution. Refer to IEEE Std 1450-1999 for full definition of this block.

**DCLevels**: This specifies the DCLevels block that contains the DC level information to use for this Pattern-Exec. There may be multiple DCLevels blocks in an STIL file, but only one DCLevels block is associated with any given PatternExec. Any DCLevels block referenced in a PatternExec shall specify DC parameters for all signals referenced in that PatternExec except signals of type Pseudo, which are optionally specified as discussed in 9.3.

DC\_LEVELS\_NAME: This is an optional reference to a named DCLevels block. If no name is present, then this PatternExec shall use the unnamed DCLevels block.

**DCSets**: This specifies the DCSets block that is to be used to resolve all DCLevels references that appear in the Pattern blocks associated with this PatternExec. A DCSets reference statement in the PatternExec shall be present to reference any DCLevels in a Pattern. See 9.3 for additional information about the interaction of DCSets and DCLevels.

DC\_SETS\_NAME: This is an optional reference to a named DCLevels block. If no name is present, then this PatternExec shall use the unnamed DCLevels block.

#### 9.2 PatternExec block example

```

PatternExec func {

Category dc;

Selector dc_setup;

Timing slow;

DCLevels slow_dc;

DCSets all_sets;

PatternBurst dc_patts;

}

```

#### 9.3 DCLevels and DCSets usage in PatternExec and Pattern blocks

A DCLevels block referenced in a PatternExec with the DCLevels statement shall define DC parameters as necessary for all pertinent Signals referenced in the PatternExec. All constructs present in this block shall be applied to Signals before each Pattern referenced in this environment starts execution. When present, the DCLevels statement shall be applied even when DCSets information is also present. If no DCLevels statement is present in the PatternExec, and the DCSets statement is present in the PatternExec, then a DCLevels statement shall be present in each Pattern referenced by this PatternExec, before the first Vector statement of each Pattern. The DCLevels block referenced by this first DCLevels statement shall define DC parameters as necessary for all pertinent Signals. Subsequent DCLevels blocks referenced by DCLevels statements in a Pattern need to define only values for DC parameters that are different from the previous value established. See Annex A for a usage example of DCLevels and DCSets.

Pertinent Signals are defined to be all the In, Out, InOut, and Supply signals defined in the Signals block. When DCLevels information is provided, at least one DCLevels block shall define values as necessary across at least all of these Signals. Definitions are required even for Signals that are not referenced in a specific Pattern to define the levels information for the DefaultState value of those Signals. The effect of unspecified DCLevels values is implementation defined.

#### 10. DCLevels block

The DCLevels block defines the DC levels to be applied to signal pins and power supply pins for each test pattern. The DCLevels block defines specific data for each DC parameter for a set of signals. Each statement in the DCLevels block specifies the characteristics for one DC parameter. Each DC parameter shall be specified at most once for a specific signal, in a single DCLevels block. Refer to Figure 2 and Figure 3 for symbolic explanation of the DC parameters and their relationship to tester resources.

A related operation to DCLevels is the measurement of DC parametrics of the DUT signals using the parametric measurement unit (PMU) or of the DUT supply pins using measure capabilities of the DPS. The DCLevels block defines the forcing conditions of the PMU or DPS, but does not address how the measurement is to be performed.

The InheritDCLevels statement allows for defining the DC characteristics across a subset of all signals, combining these definitions into a single DCLevels block that is complete for all signals referenced in a specific PatternExec. The InheritDCLevels also supports incremental definition of DCLevels for a particular signal, and allows for redefining a DC parameter by overriding an inherited value with a local definition.

#### 10.1 DCLevels block syntax

```

(DCLevels (DC LEVELS NAME) {

// DCLevels block

(InheritDCLevels DC LEVELS REF;)*

(SignalGroups GROUPS_DOMAIN;)*

(sigref_expr {

// Signals of type In, Out, InOut, Supply

(VIH (dc_expr)+;)

(VIL (dc\_expr)+;)

(VICM dc_{expr};)

(VID dc_{expr};)

(VIHD dc_expr;)

(VILD dc_expr;)

(ForceHi;)

(ForceLo;)

(InitHi;)

(InitLo;)

(VIHSlew dc_expr;)

(VILSlew dc_expr;)

(VOH (dc\_expr)+;)

(VOL (dc\_expr)+;)

(VOCM dc\_expr;)

(VOD dc_expr;)

(VOHD dc_{expr};)

(VOLD dc_{expr};)

(IOH dc_{expr};)

(IOL dc_{expr};)

(LoadVRef dc_expr;)

(ClampHi dc_expr;)

(ClampLo dc_expr;)

(ResistiveTermination dc_expr;)

(TermVRef dc expr;)

(VForce dc expr;)

(IClamp dc\_expr;)

(IForce dc expr;)

(VClamp dc_expr;)

})*

})*

```

**DCLevels**: This is the start of a DCLevels block, which identifies DC parameters for a set of Signals of type In, Out, InOut, and/or Supply. DC parameters for signals of type Pseudo may be specified but are not required.

DC\_LEVELS\_NAME: This is the name of this DCLevels block. If no name is present, then this block is global and is used when a PatternExec references a DCLevels without a name.

**InheritDCLevels** DC\_LEVELS\_REF: This statement is optional and is used to define data inheritance from another DCLevels block. DC\_LEVELS\_REF is a reference to the name of a previously defined DCLevels block. All parameters specified for a particular signal in an inherited DCLevels block are applied to that sig-

nal in this block; a local definition of any DC parameter overrides any inherited definition of that parameter. If there are multiple InheritDCLevels statements, the last DCLevels definitions for each signal are the initial definitions for each signal in this block. Local DCLevels definitions override the inherited definitions; the last inherited DCLevels definitions are applied to any signal without local DCLevels defined.

**SignalGroups** GROUPS\_DOMAIN: This optional statement indicates the name of a SignalGroups block that is to be used in resolving signal group references in this DCLevels block. Referenced SignalGroups in the DCLevels block will typically be the same as those used in the Timing block and/or the PatternBurst block and require the same SignalGroup reference statements in this block to resolve *sigref\_expr*. If the application of DCLevels requires different grouping of signals, then unique SignalGroups blocks are referenced with this statement.

sigref\_expr: This is signal expression as defined in 6.14 of IEEE Std 1450-1999.

DC parameters for each *sigref expr* are specified using the following entities:

**VIH**: This defines the drive high voltage to be applied to Signals in the specified *sigref\_expr*. In most situations, a single dc\_expr is present. Multiple dc\_expr statements are present to support changing values during one Vector, as explained in Clause 13.

VIL: This defines the drive low voltage to be applied to Signals in the specified *sigref\_expr*. In most situations, a single dc\_expr is present. Multiple dc\_expr statements are present to support changing values during one Vector, as explained in Clause 13.

**VICM**: This defines the input common mode voltage for differential Signals in the specified *sigref\_expr*. VICM = (VIHD + VILD)/2 (see Figure 3).

**VID**: This defines the differential input voltage for Signals in the specified  $sigref\_expr$ . VID = |VIHD - VILD| (see Figure 3).

**VIHD**: This defines the drive high voltage to be applied to differential Signals in the specified *sigref\_expr* (see Figure 3).

**VILD**: This defines the drive low voltage to be applied to differential Signals in the specified *sigref\_expr* (see Figure 3).

Input voltages for differential Signals may be specified either by defining VICM and VID, or by defining VIHD and VILD.

$dc\_expr$ : This is a DC expression as defined in 5.2.

**ForceHi**: This specifies that the VIH level shall be applied as a static drive high voltage during pattern execution, overriding the pattern data.

**ForceLo**: This specifies that the VIL level shall be applied as a static drive low voltage during pattern execution, overriding the pattern data.

It is an error to define both ForceHi and ForceLo on the same signal. If ForceHi is present for a signal, then a VIH statement shall be present for that signal; if ForceLo is present for a signal, then a VIL statement shall be present.

**InitHi**: This specifies that the VIH level shall be applied as an initial drive high voltage before pattern execution begins.

**InitLo**: This specifies that the VIL level shall be applied as an initial drive low voltage before pattern execution begins.

It is an error to define both InitHi and InitLo on the same signal. If InitHi is present for a signal, then a VIH statement shall be present for that signal; if InitLo is present for a signal, then a VIL statement shall be present. The presence of an InitHi or InitLo statement does not replace STIL requirements for the presence of data on that signal.

**VIHSlew**: This defines input slew rate for drive high voltages, specified in units of volts per time (e.g., '1V/lns').

**VILSlew**: This defines input slew rate for drive low voltages, specified in units of volts per time (e.g., '1V/1ns').

**VOH**: This defines the compare high voltage to be applied to Signals in the specified *sigref\_expr*. In most situations, a single dc\_expr is present. Multiple dc\_expr statements are present to support changing values during one Vector, as explained in Clause 13.

**VOL**: This defines the compare low voltage to be applied to Signals in the specified *sigref\_expr*. In most situations, a single dc\_expr is present. Multiple dc\_expr statements are present to support changing values during one Vector, as explained in Clause 13.

**VOCM**: This defines the output common mode voltage for differential Signals in the specified  $signef\_expr$ . VOCM = (VOHD + VOLD)/2 (see Figure 3).

**VOD**: This defines the differential output voltage for Signals in the specified  $sigref\_expr$ . VOD = |VOHD - VOLD| (see Figure 3).

**VOHD**: This defines the compare high voltage for differential Signals in the specified *sigref\_expr* (see Figure 3).

**VOLD**: This defines the compare low voltage for differential Signals in the specified *sigref\_expr* (see Figure 3).

Output voltages for differential Signals may be specified either by defining VOCM and VOD, or by defining VOHD and VOLD. The differential comparator functions is a two-stage process. The first stage removes common mode interference from the DUT signals, resulting in |Va - Vaz| (see Figure 3). The second stage compares the result to the output thresholds.

**IOH**: This defines the output high load current to be applied to Signals in the specified *sigref\_expr*. IOH is typically a negative current value.

**IOL**: This defines the output low load current to be applied to Signals in the specified *sigref\_expr*. IOL is typically a positive current value.

**LoadVRef**: This defines the load threshold or commutating voltage. When the Termination statement in 14.1 and 17.1 of IEEE Std 1450-1999 is used, it defines how LoadVRef should be set in order for the Vectors in the associated PatternExec to execute successfully. A Termination attribute of TerminateHigh requires that LoadVRef be set to VOH for float-state measures. A Termination attribute of TerminateLow requires that LoadVRef be set to VOL for float-state measures. A Termination attribute of TerminateOff or TerminateUnknown requires that LoadVRef be set to the float-state voltage level.

**ClampHi**: This defines the voltage level set for the high clamp circuit.

ClampLo: This defines the voltage level set for the low-clamp circuit.

**ResistiveTermination**: This defines a specific resistance value for terminating the tester driver (e.g., 50 Ohm).

**TermVRef**: This defines the termination voltage for ResistiveTermination.

ResistiveTermination and TermVRef are typically used to provide impedance matching to the DUT. This capability is typically implemented on ATE by using the internal impedance of the tester driver. This is distinct from usage of the Termination statement in 14.1 and 17.1 of IEEE Std 1450-1999 (see LoadVRef).

**VForce**: This defines the forcing voltage for a DPS (for Signals of type Supply), or for Signals of type In, Out, Inout when using a PMU in place of the tester driver/receiver.

**IClamp**: This defines the maximum current allowed for a DPS (for Signals of type Supply) or for Signals of type In, Out, Inout when using a PMU in place of the tester driver/receiver.

**IForce**: This defines the forcing current for a DPS (for Signals of type Supply) or for Signals of type In, Out, Inout when using a PMU in place of the tester driver/receiver.

**VClamp**: This defines the maximum voltage allowed for a DPS (for Signals of type Supply) or for Signals of type In, Out, Inout when using a PMU in place of the tester driver/receiver.

Typically, VForce and IClamp are used together to force voltage, and IForce and VClamp are used together to force current.

#### 10.2 DCLevels block example

```

DCLevels dc func {

VDD {

VForce 'vdd';

IClamp 'iddmax';

VDDA {

VForce 'vdda';

IClamp 'iddamax';

ins {

VIH 'vih1';

VIL 'vil1';

VIHSlew '1V/1ns';

VILSlew '1V/1ns';

outs {

VOH 'voh1';

VOL 'vol1';

IOH 'ioh1';

IOL 'iol1';

LoadVRef 'vth1';

inouts {

VIH 'vih2';

VIL 'vil2';

```

```

VOH 'voh2';

VOL 'vol2';

IOH 'ioh2';

IOL 'iol2';

LoadVref 'vth2';

}

```

#### 10.3 InheritDCLevels Processing

The InheritDCLevels statement allows statements defined in one DCLevels block for a set of signals to be "inherited" in another block. The InheritDCLevels statement is defined only for the outermost level of the DCLevels block; only complete DCLevels blocks are inherited. Sections or segments of DCLevels blocks cannot be individually inherited (as is supported in IEEE Std 1450-1999 with the multiple Waveform Inherit options).

When information is inherited, each statement for each signal defined will be applied in this new block, unless that statement for a signal is redefined in this new block. Inherited information becomes part of the information contained in a DCLevels block, and that information is inherited by a successive block. This allows for a hierarchical organization of DCLevels information, where multiple DCLevels blocks may inherit successively from previous blocks, as shown in 10.4.

#### 10.4 InheritDCLevels example

```

DCLevels ate {

sig1 {

VOH '1V';

VOL '-0.3V';

}

}

DCLevels loadboard {

InheritDCLevels ate;

sig1 {

LoadVRef '0.2V';

ResistiveTermination '500hm';

TermVRef '-2V';

}

}

DCLevels dut {

InheritDCLevels loadboard;

sig1 {

LoadVRef '0.4V';

VOH '1.2V';

}

}

```

In the preceding example, sig1 is defined with only a VOH and VOL level for the DCLevels block named ate. The DCLevels block loadboard inherits these definitions and adds LoadVRef, ResistiveTermination, and TermVRef values into the definition for sig1. So sig1 in DCLevels block loadboard contains the following definitions: VOH='1V', VOL='-0.3V', LoadVRef='0.2V', ResistiveTermination='50Ohm', and Term-VRef='-2V'.

The DCLevels block dut inherits all definitions from the loadboard block, including those definitions that were inherited in that block itself. It also redefines the inherited value of LoadVRef and VOH. So in this block, sig1 contains VOH='1.2V', VOL='-0.3V', LoadVRef='0.4V', ResistiveTermination='50Ohm', and TermVRef='-2V'.

#### 11. DCSets block

The DCSets block identifies a set of DCLevels blocks that may be referenced in a Pattern block to change DCLevels between Vector statements. All DCLevels referenced in a Pattern associated with the PatternExec shall be identified in a single DCSets block. A DCSets reference statement in the PatternExec is required in order to reference any DCLevels in a Pattern. If no DCSets statement is present in the PatternExec then no reference to DCLevels is allowed in the associated Patterns. Refer to 9.3 for an explanation of requirements for defining DC parameters across signals in each DCLevels block identified in the DCSets block.

#### 11.1 DCSets block syntax

```

(DCSets (DC_SET_NAME) {

(DCLevels (DC_LEVELS_REF);)*

})*

```

**DCSets**: Start of a DCSets block, which identifies a set of DCLevels blocks that may be referenced in a Pattern block associated with the PatternExec.

DC\_SET\_NAME: Name of a DCSets block. If no name is present, then it is a global block to be used for all PatternExec statements that do not specifically identify a DCSets block name.

**DCLevels**: Reference to a DCLevels block, which may be referenced in a Pattern block associated with the PatternExec.

DC\_LEVELS\_REF: Name of a previously defined DCLevels block. If no name is present, then it is a reference to the global DCLevels block.

#### 11.2 DCSets statement example

```

DCSets set1 {

DCLevels switch1;

DCLevels switch2;

}

```

#### 12. DCSequence block

The DCSequence block defines the power sequences to be used when DCLevels are applied to the device. The DCSequence block names each power sequence and defines the timed sequence in which power is to be applied. The DCSequence block is not referenced in the PatternExec block. Rather, it is assumed that the DCSequence is referenced externally, either in the device test program or by the tester operating system. This is because different power sequences may be used for the same PatternExec depending on where in the test flow the PatternExec occurs.

#### 12.1 DCSequence block syntax

**DCSequence**: Start of the DCSequence block, which defines the timed sequence in which power is to be applied. Each DCSequence block may have a predefined or user-defined name, as described in the following paragraph. If no name is present, then it is a global DCSequence block.

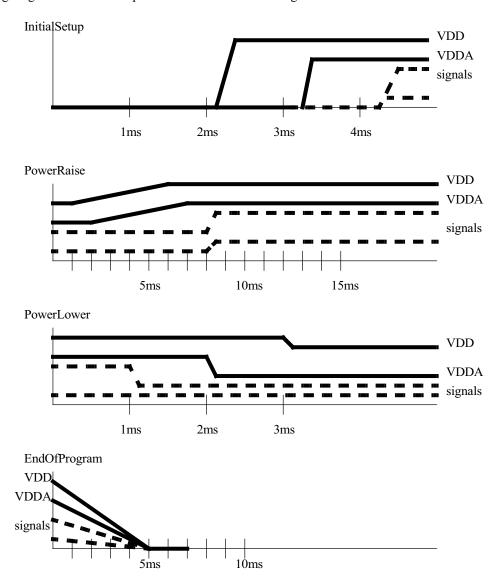

There are four predefined power sequence names: InitialSetup, PowerRaise, PowerLower, and EndOf-Program. These predefined names are not required to be used. When present, they define specific power sequence functions as explained in the following sentences. The contents of each of these is user defined. InitialSetup defines the initial power sequence used at the beginning of the test program. PowerRaise defines the power sequence used when the device power supplies are increasing in absolute value of voltage. PowerLower defines the power sequence used when the device power supplies are decreasing in absolute value of voltage. EndOfProgram defines the power sequence used to power down the device at the end of the test program. All other power sequence names are user defined.

User USER DEFINED: This identifies USER DEFINED as a user-defined name for this DCSequence.

**SignalGroups** GROUPS\_DOMAIN: This optional statement indicates the name of a SignalGroups block that is to be used in resolving signal group references in this DCSequence block. Referenced SignalGroups in the DCSequence block will typically be the same as those used in the Timing block and/or the Pattern-Burst block and require the same SignalGroup reference statements in this block to resolve *sigref\_expr*. If the application of DCSequence requires different grouping of signals, then unique SignalGroups blocks are referenced with this statement.

*time\_expr*: This is defined in IEEE Std 1450-1999. The first *time\_expr* for a given DCSequence is considered to be relative to time zero (the time at which the DCSequence starts). Each following *time\_expr* is relative to the start of the preceding one.

sigref\_expr: This is defined in IEEE Std 1450-1999. Each sigref\_expr identifies a set of Signals which will be sequenced together.

**Connect**: This specifies a physical connection to a tester resource (Supply, PMU, Driver, Comparator, Load, Termination, Clamp) (e.g., through a relay). If no resource is listed, all resources associated with each Signal referenced in this *time\_expr* block shall be connected. When multiple Connect statements are used, the physical connection is performed in the order the statements appear.

**Disconnect**: This specifies that the physical connection to a tester resource (Supply, PMU, Driver, Comparator, Load, Termination, Clamp) (e.g., through a relay) is to be disconnected. If no resource is listed, all resources associated with each Signal referenced in this *time\_expr* block shall be disconnected. When multiple Disconnect statements are used, the physical disconnection is performed in the order the statements appear.

**Apply**: This statement defines the target voltage or current value to apply to the specified Signals at this point in the power sequence. If no  $dc_{expr}$  is specified, the programmed voltage or current from the DCLevels block currently in effect (as determined by the device test program or tester operating system) shall be used.

**Ramp**: This statement shall only be used with Signals of type Supply. This statement defines the time duration used to arrive at the target voltage or current. The *time\_expr* specifies the total time duration. The optional *dc\_expr* specifies the target voltage or current. If no *dc\_expr* is specified, the programmed voltage or current from the DCLevels block currently in effect (as determined by the device test program or tester operating system) shall be used.

#### 12.2 DCSequence example

```

// Beginning of program

DCSequence InitialSetup {

'0s' 'VDD+VDDA' {

// T0

Apply '0V';

}

'1ms' 'VDD+VDDA' {

Connect Supply;

}

'1ms' VDD {

Apply '100mA';

// Apply line charge current

'100us' VDD {

Apply;

// Apply voltage programmed by test

}

'1ms' VDDA {

Apply '50mA';

// Apply line charge current

'100us' VDDA {

// Apply voltage programmed by test

Apply;

}

'1ms' signals {

Connect Load;

Connect Driver Comparator;

}

}

DCSequence PowerRaise {

// Increasing VDD

'1ms' VDD {

Ramp '5ms';

// Ramp to programmed voltage

}

'1ms' VDDA {

Ramp '5ms';

}

'6ms' signals {

// Apply new values to signals after supplies change

Apply;

}

DCSequence PowerLower {

// Decreasing VDD

'1ms' signals {

Apply; // Apply new values to signals before supplies change

'1ms' VDDA {

Apply;

// Apply voltage programmed by test

}

```

A timing diagram for the DCSequences in 12.2 is shown in Figure 4.

Figure 4—Timing diagram for DCSequence example

#### 13. Extensions to Clause 18, WaveformTable block

This clause defines an extension to the definition of event characters in the WaveformTable block. The purpose of the extension is to support switching DC levels within an STIL Vector.

The extension to the WaveformTable block is limited to an extension of the definition of the event construct defined in 18.1 of IEEE Std 1450-1999.

#### 13.1 Event definition in WaveformTable block

An "event" is an identifier that is used to signal a potential change in the state of the signal. All events have fixed definitions as specified in 18.2 of IEEE Std 1450-1999. The extension to the event definition is the

addition of an optional integer suffix (0 .. n), each of which shall specify a different voltage level. The voltage levels shall be defined in the DCLevels, using multiple values in the VIH/VIL/VOH/VOL statements. The order of appearance of the voltage levels in the VIH/VIL/VOH/VOL statements shall map to the corresponding event suffixes (0 .. n). The existing IEEE Std 1450-1999 multiple-bit vector data capability can be used to define the shape of the waveform resulting from the DC level switching.

#### 13.2 Mapping of event integers to DCLevels statements

Table 5 shows STIL events, as defined in Tables 9 and 10 of IEEE Std 1450-1999, which are extended in this standard to support an optional integer value following that event.

Table 5—STIL events referencing DCLevels statements

| STIL event                                   | DCLevels statement                                          |

|----------------------------------------------|-------------------------------------------------------------|

| U (or ForceUp)                               | references the current VIH levels statement for this signal |

| D (or ForceDown)                             | references the current VIL levels statement for this signal |

| H (or CompareHigh) h (or CompareHighWindow)  | references the current VOH levels statement for this signal |

| L (or CompareLow)<br>l (or CompareLowWindow) | references the current VOL levels statement for this signal |

It is an error for a STIL event not listed in Table 5 to have an integer value following that event.

An event identified in Table 5 that does not have an integer value following that event shall use the first dc\_expr statement present in the appropriate levels statement for that event if that levels statement is present for that signal.

The integer value following an STIL event is interpreted to reference a specific dc\_expr in the appropriate levels statement for that event. The first dc\_expr in the levels statement is referenced by the integer value 0 (or no integer value present), the second dc\_expr is referenced by 1, etc. It is an error to specify an integer value that does not have a matching dc\_expr specified.

#### 13.3 DC levels switching example

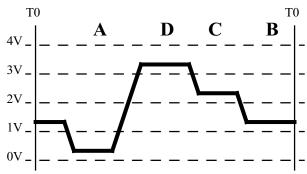

This example demonstrates switching DC levels within a cycle in order to generate the waveform in Figure 5.

Figure 5—Example waveform generated by switching DC levels within a cycle

The following STIL fragments produce the waveform in Figure 5.

The numbers in the circles (e.g., ① correspond to the example notes that follow.

```

DCLevels

pins {

mult {

VIH '0.2V', '1.4V', '2.2V', '3.6V'; // define multiple drive high levels

}

Timing slow {

WaveformTable wft1 {

Period '30ns';

Waveforms {

mult {

ABCD

'0ns'

U1;

'5ns'

U0/U1/U2/U3[0];

'10ns' U0/U1/U2/U3[1];

'15ns' U0/U1/U2/U3[2];

'20ns' U0/U1/U2/U3[3];

} } }

Pattern one {

W wft1;

{ mult = ADCB;

}

```

#### **NOTES**

- 1—In the multiple-bit waveform definition for ABCD, WaveformChar A maps to event U0, WaveformChar B maps to event U1, WaveformChar C maps to event U2, and WaveformChar D maps to event U3.

- 2—In the VIH definition for group mult, the first dc\_expr (0.2V) is referenced by event U0, the second dc\_expr (1.4V) is referenced by event U1, the third dc\_expr (2.2V) is referenced by event U2, and the fourth dc\_expr (3.6V) is referenced by event U3.

- 3—In the multiple-bit vector ADCB, WaveformChar A specifies that event U0 will be used for bit [0] at time 5ns, thereby referencing VIH level of 0.2V. Similarly, WaveformChar D specifies that event U3 will be used for bit [1] at time 10ns, referencing VIH level 3.6V. Also, WaveformChar C specifies that event U2 will be used for bit [2] at time 15ns, referencing VIH level 2.2V. And, WaveformChar B specifies that event U1 will be used for bit [3] at time 20ns, referencing VIH level 1.4V.

#### 14. Extensions to Clause 22, STIL Pattern statements

#### 14.1 DCLevels statement

The DCLevels statement is used to specify a DCLevels block on a vector-by-vector basis. This provides the capability for switching DCLevels within a Pattern.

The syntax of the DCLevels statement is

```

DCLevels (LEVELSNAME);

```

LEVELSNAME is the optional name of a DCLevels block. If LEVELSNAME is not present, the reference is to the global DCLevels block.

#### 14.2 DCLevels statement example

#### Annex A

(informative)

#### DCLevels and DCSets usage example

The following example demonstrates DCLevels and DCSets usage in PatternExec and Pattern blocks.

```

STIL 1.0 {

DCLevels 2002;

Signals {

en

In;

clk

In;

d1

In;

d2

In;

a0

InOut;

a1

InOut;

a2

InOut;

VDD Supply;

VDDS Supply;

}

SignalGroups {

ins

'en +d1+d2';

'clk';

clks

inouts 'a0+a1+a2';

'ins+clks+inouts';

}

Spec all_specs {

Category all cats {

per1 = '100ns';

dely1 = '10ns';

off1 = '25ns';

off2 = '50ns';

stb1 = '75ns';

per2 = '50ns';

dely2 = '5ns';

off3 = '12.5ns';

off4 = '25ns';

stb2 = '40ns';

vdd low = '1.5V';

vdds low = '2.7V';

vdd hi = '1.8V';

vdds hi = '3.3V';

iddmax = '500mA';

vih low = '2.5V';

vil low = '0V';

voh low = '2.4V';

```

The numbers in the circles (e.g., ①) correspond to the example notes that follow.

```

vol low = '0.3V';

ioh low = '1mA';

iol low = '1.5mA';

vth low = '1.4V';

vih hi = '3V';

vil hi = '0V';

voh hi = '2.9V';

vol_hi = '0.5V';

ioh hi = '2mA';

iol hi = '4mA';

vth_hi = '1.7V';

slew = '1V/1ns';

}

}

Timing slow {

WaveformTable ts1 {

Period 'per1';

Waveforms {

ins { LH { 'dely1' D/U; } }

clks { LC { 'Ons' D; 'off1' D/U; 'off2' D; } }

inouts { LH { 'dely1' D/U; } }

inouts { 01ZM { 'stb1' L/H/T/X; } }

}

}

WaveformTable ts2 {

Period 'per2';

Waveforms {

ins { LH { 'dely2' D/U; } }

clks { LC { 'Ons' D; 'off3' D/U; 'off4' D; } }

inouts { LH { 'dely2' D/U; } }

inouts { 01ZM { 'stb2' L/H/T/X; } }

}

DCLevels low vdd {

VDD {

VForce

'vdd_low';

IClamp

'iddmax';

VDDS {

VForce 'vdds low';

IClamp 'iddmax';

'ins+clks' {

VIH 'vih low';

VIL 'vil low';

VIHSlew 'slew';

VILSlew 'slew';

inouts {

```

```

VIH 'vih low';

VIL 'vil_low';

VIHSlew 'slew';

VILSlew 'slew';

VOH 'voh low';

VOL 'vol low';

IOH 'ioh_low';

IOL 'iol_low';

LoadVRef 'vth low';

}

}

DCLevels hi_vdd {

VDD {

VForce 'vdd_hi';

IClamp 'iddmax';

VDDS {

VForce 'vdds_hi';

IClamp 'iddmax';

'ins+clks' {

VIH 'vih hi';

VIL 'vil_hi';

VIHSlew 'slew';

VILSlew 'slew';

inouts {

VIH 'vih hi';

VIL 'vil_hi';

VIHSlew 'slew';

VILSlew 'slew';

VOH 'voh_hi';

VOL 'vol hi';

IOH 'ioh_hi';

IOL 'iol hi';

LoadVRef 'vth_hi';

}

}

DCSets all_sets {

DCLevels low vdd;

DCLevels hi vdd;

}

DCSequence User DefaultSequence {

'0s' 'VDD+VDDS+all' {

Connect;

Apply;

}

}

Selector all_typ {

per1

Typ;

```

```

dely1

Typ;

off1

Typ;

off2

Typ;

stb1

Typ;

per2

Typ;

dely2

Typ;

off3

Typ;

off4

Typ;

stb2

Typ;

vdd_low Typ;

vdds_low Typ;

vdd hi

Typ;

vdds_hi Typ;

iddmax

Typ;

vih_low Typ;

vil_low Typ;

voh_low Typ;

vol_low Typ;

ioh_low Typ;

iol_low Typ;

vth_low Typ;

vih_hi Typ;

vil_hi Typ;

voh_hi

Typ;

vol hi

Typ;

ioh hi

Typ;

iol hi

Typ;

vth_hi

Typ;

slew

Typ;

}

PatternBurst one pat {

PatList {

nolevels;

}

PatternBurst two pats {

PatList {

onelevel;

bothlevels;

}

}

PatternBurst all pats {

PatList {

nolevels;

onelevel;

bothlevels;

}

}

PatternExec first func {

```

```

Category all cats;

Selector all_typ;

Timing slow;

DCLevels low vdd;

PatternBurst one pat;

}

PatternExec second_func {

Category all cats;

Selector all typ;

Timing slow;

DCSets all sets;

PatternBurst two_pats;

}

PatternExec all_func {

Category all_cats;

Selector all_typ;

Timing slow;

DCLevels low vdd;

DCSets all sets;

PatternBurst all pats;

}

Pattern nolevels {

W ts1;

V { all = LLLLMMM }

V { all = LLHC001

V { all = HHHLZZZ

V { all = LHLC010 }

Pattern onelevel {

W ts1;

DCLevels hi_vdd;

V { all = LLLLMMM }

V { all = LLHC001 }

V { all = HHHLZZZ }

V { all = LHLC010 }

V { all = LHLC111 }

Pattern bothlevels {

W ts1;

DCLevels low vdd;

V { all = LLLLMMM }

V { all = LLHC001 }

V { all = HHHLZZZ }

V { all = LHLC010 }

W ts2;

DCLevels hi vdd;

V { all = LLLLMMM }

V { all = LLHC001 }

V { all = HHHLZZZ }

```

```

V { all = LHLC010 }

V { all = LHLC111 }

```

#### NOTES

- 1—Two DCLevels blocks are defined here, low vdd and hi vdd.

- 2—DCSets all sets is defined here, referencing both DCLevels blocks.

- 3—PatternExec first\_func references DCLevels low\_vdd and PatternBurst one\_pat. Since no DCSets block is referenced in the PatternExec, the Pattern contained in the PatternBurst cannot reference any DCLevels.

PatternExec second\_func does not reference any DCLevels blocks, but it does reference DCSets all\_sets. In this case, the Patterns contained in the PatternBurst two\_pats must have a DCLevels reference before the first Vector of each Pattern.

PatternExec all\_func references DCLevels low\_vdd and DCSets all\_sets. The Patterns contained in PatternBurst all\_pats can either reference no DCLevels blocks, in which case DCLevels low\_vdd is assumed, or can reference any DCLevels blocks in DCSets all\_sets.

4—Since Pattern nolevels does not contain any DCLevels references, no DCSets reference is needed in the corresponding PatternExec. In order to use DCLevels information with this Pattern, the corresponding PatternExec must contain a DCLevels reference.

Pattern onelevel references DCLevels hi\_vdd. The corresponding PatternExec must contain a DCSets reference which includes DCLevels hi\_vdd.

Pattern bothlevels references DCLevels low\_vdd and hi\_vdd. The corresponding PatternExec must contain a DCSets reference which includes both DCLevels.

#### **Annex B**

(informative)

#### **Bibliography**

[B1] IEEE 100, The Authoritative Dictionary of IEEE Standards Terms, Seventh Edition.

#### Annex C

(infomative)

#### List of participants

At the time this standard was approved, the P1450.2 Working Group had the following membership:

Gregg Wilder, Chair Greg Maston, Vice Chair

David Colby Bernhard Heibler Tony Taylor **David Dowding** Jim Showman Ernie Wahl

Other working group members included:

Francisco Hernandez Don Organ Douglas Sprague Rohit Kapur Sebastian Prassl Peter Wohl

The following members of the balloting committee voted on this standard. Balloters may have voted for approval, disapproval, or abstention.

| Neil Jacobson | Jim O'Reilly                                                            |

|---------------|-------------------------------------------------------------------------|

| Jake Karrfalt | Susumu Ohno                                                             |

| Brion Keller  | Mike Ricchetti                                                          |

| Adam Ley      | Gordon Robinson                                                         |

| Greg Maston   | Jim Showman                                                             |

| Yinghua Min   | Douglas Sprague                                                         |

| James Monzel  | Gregg Wilder                                                            |

|               | Jake Karrfalt<br>Brion Keller<br>Adam Ley<br>Greg Maston<br>Yinghua Min |

When the IEEE-SA Standards Board approved this standard on 11 December 2002, it had the following membership:

> James T. Carlo, Chair James H. Gurney, Vice Chair Judith Gorman, Secretary

| Sid Bennett       | Toshio Fukuda         | Nader Mehravari      |

|-------------------|-----------------------|----------------------|

| H. Stephen Berger | Arnold M. Greenspan   | Daleep C. Mohla      |

| Clyde R. Camp     | Raymond Hapeman       | William J. Moylan    |

| Richard DeBlasio  | Donald M. Heirman     | Malcolm V. Thaden    |

| Harold E. Epstein | Richard H. Hulett     | Geoffrey O. Thompson |

| Julian Forster*   | Lowell G. Johnson     | Howard L. Wolfman    |

| Howard M. Frazier | Joseph L. Koepfinger* | Don Wright           |

Also included are the following nonvoting IEEE-SA Standards Board liaisons:

Alan Cookson, NIST Representative Satish K. Aggarwal, NRC Representative

Savoula Amanatidis IEEE Standards Managing Editor

Peter H. Lips