Edition 1.0 2008-08

# TECHNICAL SPECIFICATION

Process management for avionics – Atmospheric radiation effects – Part 3: Optimising system design to accommodate the single event effects (SEE) of atmospheric radiation

#### THIS PUBLICATION IS COPYRIGHT PROTECTED

#### Copyright © 2008 IEC, Geneva, Switzerland

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from either IEC or IEC's member National Committee in the country of the requester.

If you have any questions about IEC copyright or have an enquiry about obtaining additional rights to this publication, please contact the address below or your local IEC member National Committee for further information.

Droits de reproduction réservés. Sauf indication contraire, aucune partie de cette publication ne peut être reproduite ni utilisée sous quelque forme que ce soit et par aucun procédé, électronique ou mécanique, y compris la photocopie et les microfilms, sans l'accord écrit de la CEI ou du Comité national de la CEI du pays du demandeur. Si vous avez des guestions sur le copyright de la CEI ou si vous désirez obtenir des droits supplémentaires sur cette publication, utilisez les coordonnées ci-après ou contactez le Comité national de la CEI de votre pays de résidence.

IEC Central Office 3, rue de Varembé CH-1211 Geneva 20 Switzerland Email: inmail@iec.ch Web: www.iec.ch

#### About IEC publications

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the latest edition, a corrigenda or an amendment might have been published.

Catalogue of IEC publications: <u>www.iec.ch/searchpub</u>

The IEC on-line Catalogue enables you to search by a variety of criteria (reference number, text, technical committee,...). It also gives information on projects, withdrawn and replaced publications.

IEC Just Published: <u>www.iec.ch/online\_news/justpub</u> Stay up to date on all new IEC publications. Just Published details twice a month all new publications released. Available on-line and also by email.

Electropedia: <u>www.electropedia.org</u>

The world's leading online dictionary of electronic and electrical terms containing more than 20 000 terms and definitions in English and French, with equivalent terms in additional languages. Also known as the International Electrotechnical Vocabulary online.

Customer Service Centre: www.iec.ch/webstore/custserv

If you wish to give us your feedback on this publication or need further assistance, please visit the Customer Service Centre FAQ or contact us:

Email: csc@iec.ch Tel.: +41 22 919 02 11 Fax: +41 22 919 03 00

Edition 1.0 2008-08

# TECHNICAL SPECIFICATION

Process management for avionics – Atmospheric radiation effects – Part 3: Optimising system design to accommodate the single event effects (SEE) of atmospheric radiation

INTERNATIONAL ELECTROTECHNICAL COMMISSION

PRICE CODE

Т

ICS 03.100.50; 31.020; 49.060

ISBN 2-8318-9992-3

#### CONTENTS

– 2 –

| FOI                                   | FOREWORD                                                        |                                                                              |    |  |  |  |  |  |

|---------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------|----|--|--|--|--|--|

| INT                                   | INTRODUCTION                                                    |                                                                              |    |  |  |  |  |  |

| 1                                     | Scope and object                                                |                                                                              |    |  |  |  |  |  |

| 2                                     | Norm                                                            | native references                                                            | 6  |  |  |  |  |  |

| 3                                     | Term                                                            | is and definitions                                                           | 6  |  |  |  |  |  |

| 4                                     | Process guidance (see Annex A)                                  |                                                                              |    |  |  |  |  |  |

| 5                                     | spheric radiation and electronic system faults                  | 10                                                                           |    |  |  |  |  |  |

|                                       | 5.1                                                             | Atmospheric radiation effects on avionics                                    |    |  |  |  |  |  |

|                                       | 5.2                                                             | Hard faults                                                                  |    |  |  |  |  |  |

|                                       | 5.3                                                             | Soft faults                                                                  | 12 |  |  |  |  |  |

| 6                                     | Aircra                                                          | aft safety assessment                                                        | 12 |  |  |  |  |  |

|                                       | 6.1                                                             | Methodology                                                                  | 12 |  |  |  |  |  |

|                                       | 6.2                                                             | Mitigation (see Annex B)                                                     | 13 |  |  |  |  |  |

|                                       | 6.3                                                             | Specific electronic systems (see Annex C)                                    | 13 |  |  |  |  |  |

|                                       |                                                                 | 6.3.1 Level A systems                                                        | 13 |  |  |  |  |  |

|                                       |                                                                 | 6.3.2 Level B systems                                                        |    |  |  |  |  |  |

|                                       |                                                                 | 6.3.3 Level C systems                                                        |    |  |  |  |  |  |

| _                                     |                                                                 | 6.3.4 Level D and E systems                                                  |    |  |  |  |  |  |

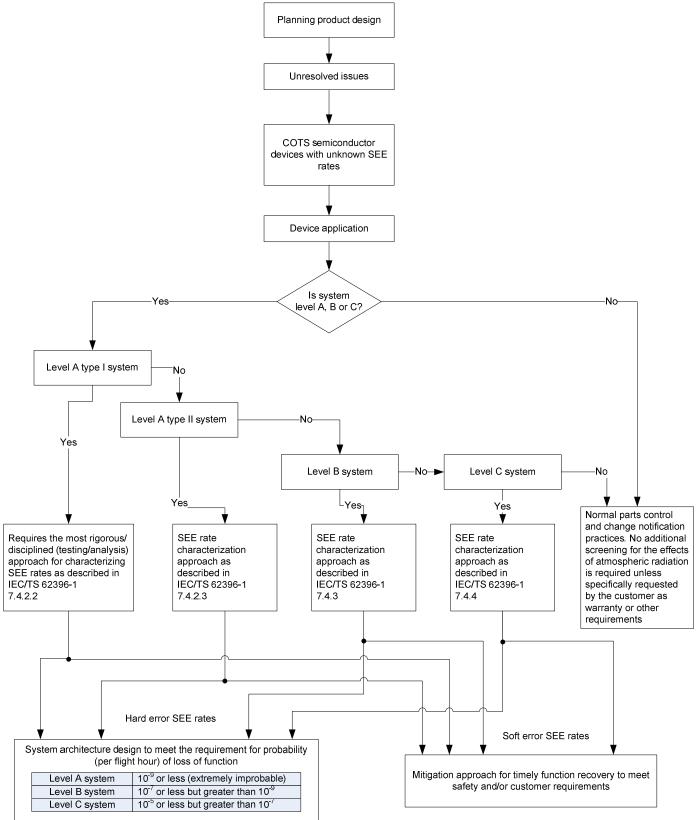

|                                       | Annex A (informative) Design process flow diagram for SEE rates |                                                                              |    |  |  |  |  |  |

|                                       |                                                                 | (informative) Some mitigation method considerations for single event effects |    |  |  |  |  |  |

| Annex C (informative) Example systems |                                                                 |                                                                              |    |  |  |  |  |  |

| Bib                                   | Bibliography2                                                   |                                                                              |    |  |  |  |  |  |

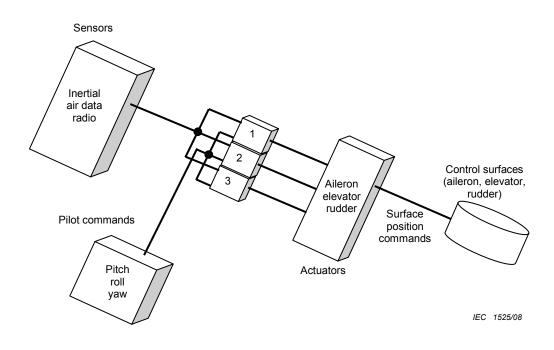

| Fig                                   | ire C                                                           | .1 – Electronic equipment (flight control computers)                         | 22 |  |  |  |  |  |

| -                                     |                                                                 |                                                                              |    |  |  |  |  |  |

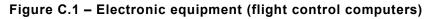

| -                                     | Figure C.2 – Electronic equipment (flight director computers)   |                                                                              |    |  |  |  |  |  |

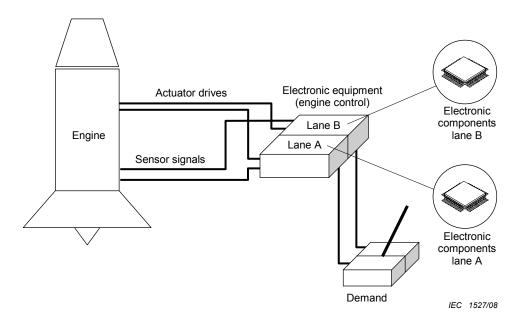

| -                                     | Figure C.3 – Electronic equipment (engine control)              |                                                                              |    |  |  |  |  |  |

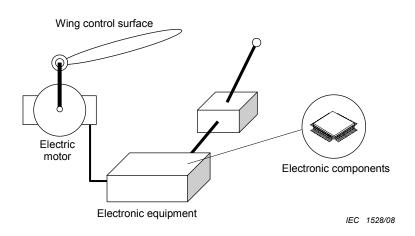

|                                       | Figure C.4 – Electronically powered surface                     |                                                                              |    |  |  |  |  |  |

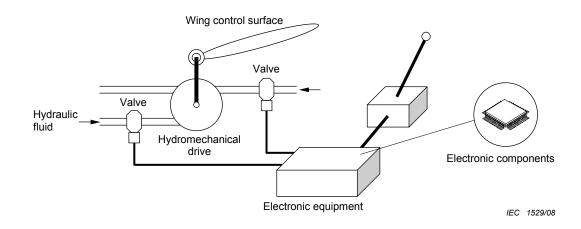

| Fig                                   | ure C.                                                          | 5 – Hydromechanical drive of surface – electronic valve control              | 24 |  |  |  |  |  |

| Tab                                   | le 1 –                                                          | - Failure effect and occurrence probability                                  | 13 |  |  |  |  |  |

#### INTERNATIONAL ELECTROTECHNICAL COMMISSION

#### PROCESS MANAGEMENT FOR AVIONICS – ATMOSPHERIC RADIATION EFFECTS –

## Part 3: Optimising system design to accommodate the single event effects (SEE) of atmospheric radiation

#### FOREWORD

- 1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as "IEC Publication(s)"). Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely with the International Organization for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC National Committees.

- 3) IEC Publications have the form of recommendations for international use and are accepted by IEC National Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

- 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter.

- 5) IEC provides no marking procedure to indicate its approval and cannot be rendered responsible for any equipment declared to be in conformity with an IEC Publication.

- 6) All users should ensure that they have the latest edition of this publication.

- 7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and members of its technical committees and IEC National Committees for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC Publications.

- 8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.

- 9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

The main task of IEC technical committees is to prepare International Standards. In exceptional circumstances, a technical committee may propose the publication of a technical specification when

- the required support cannot be obtained for the publication of an International Standard, despite repeated efforts, or

- The subject is still under technical development or where, for any other reason, there is the future but no immediate possibility of an agreement on an International Standard.

Technical specifications are subject to review within three years of publication to decide whether they can be transformed into International Standards.

IEC 62396-3, which is a Technical Specification, has been prepared by IEC technical committee 107: Process management for avionics.

This technical specification cancels and replaces IEC/PAS 62396-3 published in 2007. This first edition constitutes a technical revision.

The text of this standard is based on the following documents:

| Enquiry draft | Report on voting |

|---------------|------------------|

| 107/84/DTS    | 107/87/RVC       |

Full information on the voting for the approval of this standard can be found in the report on voting indicated in the above table.

This publication has been drafted in accordance with the ISO/IEC Directives, Part 2.

A list of all parts of the IEC 62396 series, under the general title *Process management for avionics – Atmospheric radiation effects*, can be found on the IEC website.

The committee has decided that the contents of this publication will remain unchanged until the maintenance result date indicated on the IEC web site under "http://webstore.iec.ch" in the data related to the specific publication. At this date, the publication will be

- transformed into an International standard,

- reconfirmed;

- withdrawn;

- replaced by a revised edition, or

- amended

A bilingual version of this publication may be issued at a later date.

#### INTRODUCTION

This industry-wide Technical Specification provides additional guidance to avionics systems designers, electronic equipment, component manufacturers and their customers to adopt a standard approach to optimise system design to accommodate atmospheric radiation single event effects. It builds on the information and guidance on the system level approach to Single Event Effects in IEC/TS 62396-1, considers some avionic systems and provides basic methods to accommodate SEE so that System Hardware Assurance levels may be met.

Atmospheric radiation effects are one factor that could contribute to equipment hard and soft fault rates. From a system safety perspective, using derived fault rate values, the existing methodology described in ARP4754 (accommodation of hard and soft fault rates in general) will also accommodate atmospheric radiation effect rates.

#### PROCESS MANAGEMENT FOR AVIONICS – ATMOSPHERIC RADIATION EFFECTS –

## Part 3: Optimising system design to accommodate the single event effects (SEE) of atmospheric radiation

#### 1 Scope and object

This Technical Specification is intended to provide guidance to those involved in the design of avionic systems and equipment and the resultant affects of Atmospheric Radiation induced Single Event Effects (SEE) on those avionic systems. The outputs of the activities and objectives described in this Technical Specification will become inputs to higher level certification activities and required evidences. It builds on the initial guidance on the system level approach to Single Event Effects in IEC/TS 62396-1, considers some avionic systems and provides basic methods to accommodate SEE so that System Development Assurance levels may be met.

#### 2 Normative references

The following referenced documents are indispensable for the application of this document, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

IEC/TS 62396-1, Process management for avionics – Atmospheric radiation effects – Part 1: Accommodation of atmospheric radiation effects via single event effects within avionics electronic equipment

IEC/TS 62239, Process management for avionics – Preparation of an electronic components management plan

#### 3 Terms and definitions

For the purpose of this document, the terms and definitions of the IEC/TS 62396-1, IEC/TS 62239 and the following apply

#### 3.1 Analogue Single Event Transient

ASET

deviation away from the expected operating output of the analogue device for a short duration due to the effects of a radiation deposited charge within the device.

#### 3.2 Could Not Duplicate CND

reported outcome of diagnostic testing on a piece of equipment. Following receipt of an error or fault message during operation, the error or fault condition could not be replicated during subsequent equipment testing.

3.3

## Double Error Correction Triple Error Detection DECTED

system or equipment methodology to test a digital word of information to determine if it has been corrupted, and if corrupted, to conditionally apply correction

NOTE This methodology can correct two bit corruptions and can detect and report three bit corruptions.

#### 3.4

#### firm error

term (see also soft error) used in the semiconductor community referring to a circuit cell failure within a device that cannot be reset other than by rebooting the system or by cycling the power

NOTE Such a failure could be manifest as a soft fault in that it could provide no fault found during subsequent test and impact the value for the MTBUR of the LRU.

#### 3.5

#### hard error

term used in the semiconductor community referring to permanent or semi-permanent damage of a circuit cell failure within a device by atmospheric radiation that is not recoverable even by cycling the power off and on

NOTE Hard errors could include SEB, SEGR and SEL. Such a fault would be manifest as a hard fault and could impact the value for the MTBF of the LRU.

#### 3.6

#### hard fault

term used at the aircraft function level safety analysis referring to the permanent failure of a component within an LRU

NOTE A hard fault results in the removal of the LRU affected and the replacement of the permanently damaged component before a system/system architecture can be restored to full functionality. Such a fault could impact the value for the MTBF of the LRU repaired.

#### 3.7

#### latch-up

condition where triggering of a parasitic pnpn circuit in semiconductor materials (including bulk CMOS) occurs, resulting in a state where the parasitic latched current exceeds the holding current. This state is maintained while power is applied

NOTE Latch-up could be a particular case of a soft fault (firm/soft error) or in the case where it causes device damage, a hard fault.

#### 3.8

#### Line Replaceable Unit

LRU

piece of avionics electronic equipment that may be replaced during the maintenance cycle of the system

#### 3.9

### Mean Time Between Failure MTBF

term from the world airlines technical glossary referring to the mean time between failure of equipment or a system in service such that it would require the replacement of a damaged component before a system/system architecture can be restored to full functionality and thus it is a measure of reliability requirements for equipment or systems.

#### 3.10

### Mean Time Between Unscheduled Removals MTBUR

term from the world airlines technical glossary referring to the mean time between unscheduled removal of equipment or a system in service that could be the result of soft faults and thus is a measure of reliability for equipment or systems

NOTE MTBUR values can have a major impact on airline operational costs.

#### 3.11 Multiple Bit Upset MBU

event which occurs when the energy deposited in the silicon of an electronic component by a single ionising particle causes upset to more than one bit

#### 3.12 No Fault Found NFF

reported outcome of diagnostic testing on a piece of equipment. Following receipt of an error or fault message during operation, the equipment is found to be fully functional and within specification during subsequent equipment testing.

#### 3.13

#### neutron

elementary particle with atomic mass number of one and carries no charge

NOTE It is a constituent of every atomic nucleus except hydrogen.

#### 3.14

## Single Error Correction Double Error Detection SECDED

system or equipment methodology to test a digital word of information to determine if it has been corrupted, and if corrupted, to conditionally apply correction

NOTE This methodology can correct one bit corruption and can detect and report two bit corruptions.

#### 3.15 Single Event Burn Out SEB

occurs when a powered electronic component or part thereof is burnt out as a result of the energy absorption triggered by an individual radiation event

#### 3.16 Single Event Effect SEE

is the response of a component to the impact of a single particle (for example cosmic rays, solar energetic particles, energetic neutrons and protons)

NOTE The range of responses can include both non-destructive (for example upset) and destructive (for example latch-up or gate rupture) phenomena.

#### 3.17 Single Event Functional Interrupt SEFI

upset in a complex device, for example, a microprocessor, such that a control path is corrupted, leading the part to cease to function properly

NOTE This effect has sometimes been referred to as lockup, indicating that sometimes the part can be put into a "frozen" state.

#### 3.18 Single Event Gate Rupture SEGR

event which occurs in the gate of a powered insulated gate component when the radiation charge absorbed by the device is sufficient to cause destructive gate insulation breakdown

#### 3.19 Single Event Latch-up SEL

condition where ionisation deposited by the interaction of a single particle of radiation in a device causes triggering of a parasitic pnpn circuit in semiconductor materials (including bulk CMOS) to occur, resulting in a state where the parasitic latched current exceeds the holding current, this state is maintained while power is applied

NOTE Latch-up could be a particular case of a soft fault (firm/soft error) or in the case where it causes device damage, a hard fault.

#### 3.20 Single Event Transient SET

spurious signal or voltage, induced by the deposition of charge by a single particle that can propagate through the circuit path during one clock cycle (see 6.3.1.3.3)

#### 3.21 Single Event Upset SEU

event which occurs in a semiconductor device when the radiation absorbed by the device is sufficient to change the logical state of a digital electronic logic cell(s) (memory bit cell, register bit cell, latch cell, etc.)

#### 3.22

#### soft error

term (see also firm error) refers to invalid state changes in digital electronic logic cell(s) that could be induced by atmospheric radiation and which are recoverable by cycling the power off and on

NOTE Soft error responses could include SEFI, SET and SEU. Such failures may not be manifest during subsequent test and therefore could impact the value for the MTBUR of the LRU.

#### 3.23 soft fai

soft fault

term used at the aircraft function level safety analysis that refers to the characteristic of invalid digital logic cell(s) state changes within digital hardware electronic circuitry

NOTE This is a fault that does not involve replacement of a permanently damaged component within an LRU, but it does involve restoring the logic cells to valid states before a system/system can be restored to full functionality. Such a fault condition has been suspected in the "no fault found" syndrome for functions implemented with digital technology and it would probably impact the value for the MTBUR of the affected LRU. If a soft fault results in the mistaken replacement of a component within the LRU, the replacement could impact the value for the MTBF of the LRU repaired.

#### 4 Process guidance (see Annex A)

In an attempt to achieve a high level of confidence in system safety, certification authorities mandate the use of defined design processes for the purpose of identifying and eliminating design faults and providing appropriate feedback mechanisms to ensure a continuous and closed loop development process. This Technical Specification defines methods and guidance to be appropriately used in accommodating SEE related issues in Avionics design. However, this is only one piece in the development assurance process.

To fully address design methodology as it pertains to SEE and the required evidence needed to validate designs, several different processes will require revision to address this design issue. The following is a partial list of the processes that may need revision depending on how processes are currently structured.

At a program management level, there are often processes in place. In many cases, it

may be necessary to address SEE issues generically at this level.

System level processes are likely to require addressing SEE issues and providing specific direction as to how these processes should be handled, communicated and fedback through the development process. This is important, because SEE issues in contrast to standard reliability numbers have been fed back into the design process that has resulted in design and requirements changes. These changes have been developed to mitigate various aspects of the effects and then resulted in revised SEE calculations made against the new design. This makes SEE an aspect of reliability and system reliability determination an iterative process in ways that never happened previously.

- 10 -

- Reliability/safety analysis processes will need (depending on system criticality) to address SEE issues and develop formal mechanisms to address the iterative design aspects that have taken place in ways not previously experienced.

- Component management plans will require modification to address SEE issues in initial parts selection and also as manufacturers revise parts. Some processes will need to be in place (also depending on system criticality) to ensure that new parts used in the manufacturing process will perform the same as the original parts from a SEE perspective.

Guidance for the integration of evolving processes to measure SEE rates and the accommodation of those rates in digital systems (flight controls, avionics, etc) into existing safety analysis/system design methodology (component reliability, redundancy, mitigation) is provided in Clauses 5 and 6.

#### 5 Atmospheric radiation and electronic system faults

#### 5.1 Atmospheric radiation effects on avionics

Atmospheric radiation affects the electronic parts of the system. The high energy secondary or thermal neutron radiation interacts with the silicon within semiconductor elements of an electronic component to produce charge which may cause a Single Event Effect (SEE) in the localised area within that device. Atmospheric radiation at aircraft altitudes has not been a significant problem in the past, prior to 1990, due to the relatively large feature sizes (above 1  $\mu$ m) with similarly large critical charge. Current avionic electronic systems use state-of-the-art electronic/digital devices with feature sizes well below 1  $\mu$ m, which makes SEE much more probable (energy transfer generated charge required to produce SEE becomes less) in these devices.

When aircraft functions are implemented using digital technology, atmospheric radiation effects can show up as digital device failures that in turn can propagate to failures within systems and possibly, failure of an aircraft function. The failure rate of each piece of electronic equipment which comprises a system is the aggregate rate of the components which make up that piece of electronic equipment. The failure rate of each component is the aggregate rate of all failure mechanisms of that component which dominate that failure rate. As the feature sizes of individual circuits within digital devices continue to decrease and the corresponding failure rate due to SEE rises, SEE mechanisms may become a dominant driver of the failure rates for these devices. The testing of small feature size IC components for secondary neutron SEE in suitable simulators or with terrestrial facilities is becoming more commonplace. Although this is more commonplace, it is still difficult and costly.

Although analogue parts are generally considered immune to atmospheric radiation effects, some device scaling has occurred in the technology. As a result, a neutron SEE event within the device may be sufficient to cause a short duration transient from the correct output. This kind of transient is referred to as an Analogue Single Event Transient (ASET).

Reliability engineering can calculate equipment failure rates from component failure rates and system engineering can design an architecture that will satisfy the reliability and availability requirements for the function. At a system architectural level, redundancy is a common strategy to achieve the required function reliability. In order for redundancy to be cost effective, equipment failure rates cannot exceed certain limits. Naturally, if the failure rates of

electronic devices become too great, equipment failure rates become prohibitively high. In the past atmospheric SEE rates have not been a noticeable driver in the failure rate of digital devices. Where SEE rates become a significant failure rate driver, these rates need to be included by reliability engineering in the equipment failure rate calculation. It should be recognized that, since SEE involves unique technology and associated specialists to determine component SEE rates, another engineering discipline would need to be in place to provide those rates to reliability and systems engineering.

From a system safety perspective, faults can essentially be categorized as:

- Hard, i.e. those which result in permanent failure of the affected LRU (s) and

- Soft, i.e. those which may be recovered with no loss of system functionality or redundancy.

These categories arise from the device SEE: the atmospheric radiation effects on components may result in soft faults where functionality may be recovered or hard faults resulting in permanent failure of the component. Soft fault effects may be accommodated by corrective actions within the electronic equipment. As identified in IEC/TS 62396-1, the most frequent SEE that produces soft faults and associated effects is Single Event Upset (SEU).

NOTE

- Reliability is the sum of hard fault failure rates,

- Availability is the sum of hard and the sum of soft faults.

Hard faults result in a piece of system equipment requiring repair/replacement to clear the hard fault (see 5.2). Significant hard fault rates can be induced within digital components by neutrons in the atmosphere.

Availability recognizes that soft faults can occur, but that they can also be corrected and within a defined period of time, the redundant system element can return to service and be counted in the original redundancy scheme (see 5.3). It is the inducing of significant soft fault rates within digital components that adds another dimension to reliability data and system engineering.

Since electronic technology may be included in all arms of any system using redundancy, it is important that the SEE rate to be accommodated is low enough to avoid impact on the overall system redundancy mitigation. Therefore to avoid a common mode failure when operating in the atmospheric neutron environment, a limit should be established on neutron induced soft (soft error, etc) and hard fault rates of any component technology used within the digital system. The component technology limit may be applied as a combined soft error rate per bit within a designated worst case in the application environment.

The perspective of this Technical Specification is SEE on aircraft functions due to SEE on the electronic systems that provide their implementation. In this Technical Specification, we will be using the terms 'hard faults' and 'soft faults' from the system safety community. There are a number of terms commonly used in the semiconductor and radiation effects communities to describe component errors/failures (for example, hard errors, soft error rate, firm errors, latch-up, burn out, upset, functional interrupt). All of these component errors/failures types (with their associated terminology) will be grouped into hard fault or soft fault categories. Those component failures that would impact the Mean Time Between Failure (MTBF) are categorized as hard faults. Those component failures that would impact the Mean Time Between Unscheduled Removal (MTBUR) rates and/or cause associated Could Not Duplicate/ No Fault Found (CND/NFF) situations, are categorized as soft faults.

#### 5.2 Hard faults

Hard faults refer to a damaged component whose effects cause a system malfunction and require repair or replacement of the component to clear the fault. When a repair or replacement action is taken, it reflects upon the MTBF rate history for that item. Within

electronic equipment, SEE induced permanent failures (component or device) are considered in exactly the same way as for other types of failure. For the failure rate criteria of the system to be met, the aircraft system allowable failure metrics for electronic equipment within that system shall be met, for example, the MTBF. Atmospheric radiation may produce hard faults including Single Event Latch (SEL) induced damage, Single Event Burnout (SEB), Single Event Gate Rupture (SEGR). There are suitable test methods available to determine the SEE induced hard fault susceptibilities of devices and electronic components. When rates are found to be too high, a more tolerant part should be selected.

#### 5.3 Soft faults

Soft faults are digital hardware (counter, register, memory, etc.) issues. A soft fault is a condition whereby a latch of some form within a digital device becomes set to an incorrect state. Since the device is not damaged, if the soft fault can be detected and corrected in a timely manner, then there is no impact on the performance of the system. If the soft fault is not corrected, there may be a significant impact on system performance or redundancy, which in turn, when reported will lead to removal of the faulty equipment for repair. However, upon removal and reapplication of power to the device, soft faults will always clear and therefore no fault will be found. Such attempted corrective actions negatively impact the MTBUR rate history for equipment. Unscheduled removals negatively impact system operational cost. A soft fault could certainly be a contributor to the CND/NFF categories for MTBUR metrics.

As their effects could be and often are mitigated and may not result in equipment repair, soft faults associated with SEE could be considered a departure from the traditional reliability approach. However, because of their potential negative effects on MTBUR and system functionality, digital device SEE-induced soft fault rates:

- should be characterised and mitigated in the system architecture design;

- along with failure modes, should be obtained by and be available from reliability engineering.

Components that are subject to SEE-induced soft faults which cannot be reset by hardware or the software it executes and persist as a fault while power remains applied are becoming more prevalent. Soft faults of this type and their system effects would need to be managed by appropriate mitigation. Note that a finite time will be taken for effective recovery of the system or device from such a fault. An example of this kind of soft fault would be a non-destructive SEL. In the semiconductor and radiation effects communities, a non-destructive SEL might be categorized as a firm error. Recovery from SEL could require independent hardware and software for detection and recycling power.

For the failure rate criteria of the system to be met (which, in turn, results in the aircraft function meeting allowable failure metrics), failure metrics for electronic equipment within that system shall be met, for example MTBUR. Without mitigation, soft fault rates could have a significant negative effect on the ability of a system to meet its allowable MTBUR.

#### 6 Aircraft safety assessment

#### 6.1 Methodology

In IEC/TS 62396-1 it is recognized that, within the systems which implement aircraft functions, the method of assessing the safety impact of radiation-induced effects on electronic (particularly digital) components should be identical to that used to assess functional hazards due to other failure modes and effects traditionally recognized. This is particularly the case for electronic equipment. This methodology is driven by requirements governing function failure effects and the probability per flight hour of their occurrence. As an example, Table 1 provides the probability requirement for the various types of failure effect for Part 23 (general aviation category airplanes - AC/AMJ 23.1309-1C) and Part 25 (transport category airplanes - AC/AMJ 25.1309-1C) of the airworthiness standards.

| Functional failure condition classification per AC1309 and ARP4754 | Probability (per flight hour) of occurrence     |

|--------------------------------------------------------------------|-------------------------------------------------|

| Catastrophic                                                       | 10 <sup>-9</sup> or less (extremely improbable) |

| Severe major/hazardous                                             | 10 <sup>-7</sup> or less                        |

| Major                                                              | 10 <sup>-5</sup> or less                        |

| Minor                                                              | $10^{-3}$ or less                               |

| No effect                                                          | No requirement                                  |

| Table 1 – Failure effe | ct and occurrence | probability |

|------------------------|-------------------|-------------|

|------------------------|-------------------|-------------|

#### 6.2 Mitigation (see Annex B)

Essentially, mitigation refers to some form of fault detection and correction. By suitable design at the system architecture and equipment level and also by careful selection and management (see IEC/TS 62396-1:2006 Subclauses 7.4 and 9.5.2) of electronic components employed within the design, the system level impact of SEE can be reduced to acceptable levels. The approach to system level optimization of design for mitigation of SEE may be conducted by considering the system at three levels.

- system architecture;

- individual electronic equipment within the system architecture;

- components and devices within the electronic equipment.

System development assurance levels drive the discipline and rigour needed throughout the development cycle of products associated with that system. Just as the failure effect of a function implemented by a system (particularly systems based in electronic technology) determines the required probability of such a failure, it also determines the assurance level associated with that system. In IEC/TS 62396-1, it is shown that systems are classified as level A when failures of such systems may have a catastrophic effect on the aircraft. Level A systems require the most rigorous approach to single event effects and parts control. Regarding rigour of approach, Level A systems are sub divided into Level A Type I and Type II. In order of reducing degree of requirement for compliance demonstration, the other significant assurance levels are classified as Level B, Level C and Level D.

For additional information regarding assurance levels, refer to IEC/TS 62396-1:2006, Clause 7 and the references within that technical specification. Regardless of assurance level, mitigation considerations will be in terms of hard and soft faults. As detailed in 5.3, soft fault effects appear as system performance degradation and they consist of faults or errors that clear (SEFI, SET, SEU, SHE) upon removal and reapplication of power or in some cases, upon refresh.

#### 6.3 Specific electronic systems (see Annex C)

#### 6.3.1 Level A systems

#### 6.3.1.1 General

These systems shall be designed so that the catastrophic failure rate of the function they provide is  $10^{-9}$  or less per flight hour. Systems that fall into the Type I implement functions in which the pilot is not part of the system control loop. Level A Type I systems require the most rigorous processes to achieve the  $10^{-9}$  function failure criteria. Level A type I systems would include a primary flight control system that is completely computer controlled

Some FADEC systems are also classified as Level A. FADEC systems installed on Part 25 aircraft have their software and complex electronic hardware classified as Level A due to the nature of the common mode threat. As to SEE, FADEC systems that implement certain critical functions (Overspeed, reverser control, etc) should also be considered Level A as well.

Level A Type II systems implement functions in which the pilot is in the control loop. The pilot closes the control loop through pilot/system information exchange from display systems, for example closing the flight control loop using information from a Primary Flight Director (PFD) system. It should be noted that the PFD system could provide catastrophically misleading information and is categorized Level A. Any other display system that could provide catastrophically misleading information would also be categorized Level A.

#### 6.3.1.2 Hard faults

#### 6.3.1.2.1 Recovery

Hard faults require device replacement to enable full recovery of system function or redundancy capability. Their effects can be mitigated at the system architecture, electronic equipment, or component/device level.

#### 6.3.1.2.2 System architecture

At the architecture level, redundancy and redundancy management techniques are employed to accommodate failures that would lead to catastrophic failure effects at the aircraft. Multiple control surfaces and multiple engines would be examples at the structure and propulsion aircraft level. Multiple actuators and associated electronic equipment would manage effector (aircraft control surface, engine valve, etc.) movement. When electronic system development assurance levels are met, redundancy within the system architecture ensures that there is no problem from a safety requirements aspect at the aircraft function level. It is the electronic equipment that is SEE sensitive; mechanical equipment would be inherently immune and is mentioned only to illustrate the concept of redundancy.

Since monitoring across redundant elements could be relatively easily implemented within computers, redundancy can be an effective means of detecting the occurrence of faults. The occurrence of a fault can be detected by monitoring across two or more redundant elements (e.g. effectors, actuators, computers, microprocessors).

However, the allocation of redundancy has an impact on the aircraft for several reasons. Redundancy of equipment will add weight and complexity due to the need for a method of active equipment choice. It will therefore also reduce reliability and increase power consumption, and thus affect overall cost. However, the impact of increased fault tolerance and system availability has allowed, for example, the use of twin-engine aircraft in some flight profiles where in the past three or four engine aircraft would have been mandated. Intuitively, the life cycle cost of a twin-engine aircraft should be significantly lower than a similar aircraft with three or more engines.

#### 6.3.1.2.3 Electronic equipment

At the electronic equipment level, redundancy may be used as a method of accommodating failure by removing the failed equipment from contributing to the system output; the pilot may be within the loop or not.

#### 6.3.1.2.4 Electronic component/device

System design may be optimized by limiting the range of components used. In space applications, components have been tested for potential latch-up in their radiation environment and in many applications component types that are subject to SEL have been avoided. Many other destructive failure modes have been identified, e.g. SEB and SEGR, see IEC/TS 62396-1. There are suitable test methods to determine non-destructive SEL susceptibility of devices. Such parts, once identified, are to be avoided if the level of susceptibility is unacceptable. This type of approach requires careful selection and control of electronic components throughout the equipment life cycle, see IEC/TS 62396-1:2006, Subclauses 7.4 and 9.5.2.

#### 6.3.1.3 Soft faults

#### 6.3.1.3.1 Recovery

Soft faults do not require digital device replacement to restore the system to full capacity. Their effects can be mitigated at the system, electronic equipment, or component/device level. Some soft fault detection/mitigation methods are mentioned in 6.3.1.3. Additional guidance regarding mitigation of SEE induced electronic equipment soft faults is found in Annex B.

#### 6.3.1.3.2 System architecture

Like hard faults, at the architecture level, redundancy and redundancy management can provide coverage for soft faults. Regarding mitigation, since monitoring across redundant elements could be relatively easily implemented within computers, redundancy can be an effective means to detect the occurrence of faults. The occurrence of a fault can be detected by monitoring across two or more redundant electronic elements (e.g. computers).

In addition to soft fault detection, systems can be designed to provide timely recovery from soft faults: the design objective for such recovery mechanisms is that there shall be no significant effect on function performance and are not noticeable by pilots.

#### 6.3.1.3.3 Electronic equipment

It is at electronic equipment level where the maximum benefits from optimised design to accommodate the SEE from electronic components can be gained. A number of techniques that enable the detection and correction of soft faults due to SEE at the component level are presented. As long as the hardware processing unit of a digital computer remains operational, software mitigation methods should be effective.

Soft faults at the component level, for example SEU (single/multiple Bit upset, etc.) can be generally detected at the equipment level and some method of accommodation applied within the equipment.

These accommodation methods require resources and time to complete the accommodation, therefore there will be a maximum rate at which soft errors can be accommodated within the equipment.

Rapid recovery refers to an electronic equipment methodology where soft faults are detected in a timely manner, so that:

- state data can be recovered from a protected source;

- computation can be restarted from an appropriate place in instruction execution such that equipment and system recovery would be transparent to the function performance.

When corrupted data or errors are detected at equipment level, a number of recovery methods may be chosen depending on system requirements. Upon error detection, the associated data may be:

- a) labelled as faulty;

- b) the data may be selectively ignored;

- c) the equipment may initiate a switch to a known uncorrupted redundant module;

- d) the data is deleted and the affected process re-initialised from known good data.

A SEE within the control paths of a complex device (including microprocessors and microcontrollers) could produce a number of word errors as a result of an interruption of normal operation. These errors can be detected by comparison between a number of separate parallel functions or by detection of the large number of SEE errors.

Generally, combinational logic has not been subject to atmospheric radiation SEE. However, because devices with reducing critical charges and with operating frequencies increasing above 50 MHz are being applied to avionics electronics, consideration of the effects of propagation of combinational logic errors is necessary. These SEE are very fast transits of signal level from the correct logic level (glitches). These normally occur for a short period of time with respect to the clock signal, and are called Single Event Transients (SET). SET can have a large impact on the clock signals where their edges may induce or terminate digital processes.

When the interruption of the device normal operation has been detected, the device can normally be recovered using a software reset. This takes a finite time and is dependent upon a sufficiently operational processing unit.

For the case of a non-operational processing unit, an independent hardware reset would be required. Again, as with a software reset, this would take a finite time. The status of equipment based upon complex electronic devices can be recovered from known good data. In order to provide recovery data a regularly refreshed atmospheric radiation tolerant memory may be employed.

Analogue Single Event Transient (ASET) detection could be by:

- a) comparison;

- b) rate-of-change. Where the maximum rate of change for an analogue parameter or value is limited within defined normal system operating conditions, any rapid change due to SEE may be detected.

#### 6.3.1.3.4 Electronic component/device

It would be possible to produce electronic controls in technology using larger feature sizes, and they would therefore be immune to SEE, but this would severely limit the capability and functionality of the equipment. Additionally, there may be problems with the availability of certain types of components in larger feature sizes, for example SRAM memory. At the component level, careful choice of certain component elements within the design can provide design benefits, for example the use of small amounts of atmospheric radiation tolerant devices as part of the total system memory.

Soft fault accommodation can be applied within a digital device:

- Random access memories typically can be configured to use some form of error detection and correction.

- The occurrence of a soft fault can be detected by monitoring across two or more redundant computing elements (triple modular redundant microprocessors are becoming common).

Alternatively, it is possible to design a complex system with current state-of-the-art technology accepting that SEU and MBU will occur and providing recovery mechanisms that may require the system to have a SEE tolerant memory backup storage for rapid recovery after detection of an event.

#### 6.3.2 Level B systems

These systems shall be designed such that the failure rate of the function they provide is  $10^{-7}$  or less, but may be greater than  $10^{-9}$  per flight hour. The architectural approach should be based upon either:

- a) Level A rigour/discipline, or

- b) Architectures based upon failure/fault rates traceable to SEE tests on similar parts using test results from non-neutron testing facilities (see IEC/TS 62396-1:2006, 7.4.3, 9.5.1 and 9.5.2).

TS 62396-3 © IEC:2008(E)

#### 6.3.3 Level C systems

These systems shall be designed such that the failure rate of the function they provide is  $10^{-5}$  or less but may be greater than  $10^{-7}$  per flight hour. The architectural approach should be based upon either:

- a) Level B rigour/discipline or

- b) Architectures based upon failure/fault rates traceable to testing results via a SEE failure/fault model (use of an average SEE error rate for all potentially sensitive components in these instances, the SEE error rate may be high for some components and low for others, but the overall equipment failure rate can be expected to be acceptable (see IEC/TS 62396-1:2006, 7.4.4, 9.5.1 and 9.5.2).

#### 6.3.4 Level D and E systems

These systems shall be designed such that the failure rate of the function they provide is  $10^{-3}$  per flight hour or less (level D), and for level E systems there is no requirement. Since from a safety perspective, their failure effects are minor or none, these systems can use architectural approaches consistent with that based upon normal parts control and change notification practices. See IEC/TS 62396-1:2006, 7.4.5, 9.5.1 and 9.5.2.

#### Annex A (informative)

- 18 -

#### Design process flow diagram for SEE rates

### Annex B

#### (informative)

#### Some mitigation method considerations for single event effects

The following guidelines offer some mitigation methods for the single event problems that may be experienced both by ground and avionics equipment.

NOTE 1 Mitigation schemes detect and correct soft faults so that the system continues to operate correctly in a seamless manner. Future designs would benefit from logging errors that occur at the device level which are being mitigated and do not propagate to be soft faults at the system level.

The most common mitigation approaches for protecting against SEUs in memories are error detection and correction mechanisms. By the use of additional support, bits within a single word and suitable coding, an SEU error may be corrected. Single Error Correction Double Error Detection (SECDED) utilises the smallest number of additional bits, and as its description indicates it can correct for single errors and can detect double errors. Increasing the number of support bits within a single word improves its ability for code to correct and detect errors. Double Error Correction Triple Error Detection (DECTED), as its name implies, can correct both single and double errors and detect triple errors in a word. "Scrubbing" is a technique used to periodically correct flipped bits in memory cells, where data is stored over the long term but only infrequently read, resulting in possible accumulation of errors due to multiple events. Scrubbing is typically run as a background task.

A number of mitigation techniques are applicable to memories; some typical examples are included below.

- Parity, capable of detecting single bit errors.

The data word has an additional single parity [odd or even] bit. When any bit within the word is changed, the word's parity changes and a parity error can be detected since the corrupted word parity will be different to the stored parity. This method detects single bit errors only. If two or more bits are unexpectedly changed within the word, the parity detection may fail to detect the error. As feature sizes and critical charge for SEE become smaller, the potential for Multiple Bit Upset (MBU) rises; a single high energy neutron may cause upset to several bits in a localised area. Where the individual bits in a word are stored together (contiguously), then it is possible to corrupt several bits in the same word, defeating parity error detection. For this reason, many manufacturers of digital memory devices store data in individual memory that is several rows apart (non-contiguously).

- Cyclic Redundancy Code, capable of detecting multiple bit errors.

- Hamming code, normally capable of detecting two bit errors and correcting one bit error.

- Reed-Solomon code, capable of correcting multiple symbol errors.

- Convolution codes, capable of correcting burst of errors.

- Selective use of SEU-immune digital cell (e.g. flip-flop, latch, memory, counter register).

Cell design options could include usage of large feature size transistors, energy storage within the cell structure, etc.

- RAM data use restrictions: data stored in RAM should not be assumed to be accurate, especially when that data has to be used for critical decisions/calculations - data could be recalculated instead of using the stored data. Many parameters may be only determined one time, such as at power on – such data is vulnerable to corruption, so use of such data should be minimized.

- Some designs read "program pins" only at power up and store this information in RAM. Instead of just relying on information in RAM, read hardware "constants" every frame.

- Consider replacing strictly greater than or less than with ≥ or ≤ respectively. Also, consider use "≥" or "≤" instead of "=", wherever possible. An example of this is in counter usage. Suppose a process is required to be executed every 30 frames and this is done with the following code:

begin module if count = 30 then turn all outputs on for 15 μs end if inc count end module

If the RAM location that stored the 8 bit variable "count" had an SEU in bit 5 (or 6 or 7), then the value of count would be greater than 30. This would continue until "count" reached 255, at which point the variable increment would cause a wrap back to 0. With a frame time of 100 ms, turning on of all outputs could take an additional 23,3 s, i.e. instead of every 2 s, the output would occur at 25,3 s once and then recover. This could result in a nuisance fault that would cause the unit to be returned to the manufacturer where no fault would be found.

Examples of mitigation approaches for protection against SEUs in bit cells other than memory (registers, counters etc.) are as follows:

- Watchdog timer, capable of detecting timing and scheduling errors. A "smart" WDT could expect a rotating 8 bit pattern, which could be written from several different software modules.

- Voting redundant outputs, capable of detecting and selecting most probable correct value.

If multiple analogue process paths are used or values are obtained through several monitored redundant loops then, in a similar way to the digital method, a deviating value can be detected by comparison. Triple modular and lockstep are examples of redundancy strategies used for digital processing electronics. Alternatively, the allowed analogue values may subject to constraint within predetermined limits and deviating values identified if outside these limits.

- Repeated calculations, capable of overcoming transient errors.

- Define constants in ROM locations.

- Write output states to hardware latches every frame. The hardware latch is susceptible to SEU.

- Continuously check the configuration state of devices that have been initialized by software. Data stored in SEU-susceptible locations in these devices defining the device configuration could be changed by an SEU. If the configuration state of a hardware device cannot be checked continuously, then reset the device and re-write the configuration state, if a continuous monitor detects a failure with the device.

- Rate of change. Where the maximum rate of change for a digital parameter or value is limited within defined normal system operating limits, any rapid change due to SEE corruption of a value may be detected.

- Filter input data. This includes ARINC 629 data, ARINC 429 data, discretes read in, and so on.

- Whenever BIT detects a failure, rerun the test to confirm the failure. A SEU could have caused the test to fail or changed the RAM location containing the pass-fail flag.

- When using bi-directional I/O ports (an I/O port that can be programmed to be used as an input port or an output port), the configuration of the I/O port should be periodically refreshed. Example: some microprocessors require that the states of a bi-directional I/O port's output buffers shall be all 1's when the port is to be used as an input. Typically, such buffers power up in the default state of all 1's, and if the design uses that port strictly as an input port and nowhere in the design is that state changed, then the design would never need to write 1's to the output buffer. However, if the output state is not refreshed periodically, a SEU could disable the port's ability to read inputs.

NOTE 2 The default power-up state should not be trusted; the required state should always be explicitly set by the system software.

- Where registers are used to define the CPU configuration, the configuration should be refreshed periodically.

- Pointers should be range-checked when used so that if corruption has occurred, the error may be detected. Similarly, integrator state values may need to be bounded and checked upon use.

- As the operating frequency of combinational logic has risen, the probability that "glitches" (very short duration deviations from the correct logic state) may be propagated through a logic block has risen. The effect of these glitches may be mitigated by using triple delay paths and voting at the end of the block. The three arms of the delay paths have staggered delays (direct, single delay, double delay), followed by majority voting. If the delay is longer than the glitch, then the signal is propagated glitch-free.

- For analogue signals, parallel signal and processing paths for the same function may be compared at a suitable stage to check that values are within expected tolerances of one another and within specified ranges.

#### Annex C (informative)

#### **Example systems**

#### C.1 Level A

#### C.1.1 Level A Type I

Primary Flight Controls:

The primary flight controls systems manipulate the positions of the aircraft flight control surfaces (elevator, ailerons, rudder for an airplane) in response to commands from the flight crew, autopilot, and flight management systems, to manoeuvre the aircraft as required by the desired the flight profile. Faults within the electronic units that implement primary flight controls have to be accommodated to maintain a safe flight path.

#### C.1.2 Level A Type II

Primary Flight Director:

The primary flight director provides information to the flight crew that is critical to aircraft safe flight and landing. In this case, the aircraft control loop is closed through the human pilot (captain or first officer of the flight crew).

- 23 -

Figure C.2 – Electronic equipment (flight director computers)

#### C.2 Level A or B

#### C.2.1 Engine controls

The engine controls govern engine thrust in response to prevailing engine conditions and flight deck commands according to flight profile requirements. Faults within the electronic engine control system (for example, a Full Authority Digital Engine Control (FADEC) system) that implements engine controls may be accommodated by the level of redundancy within the system, and if the aircraft has more than one engine, loss of engine thrust due to an engine failure may be accommodated by the level of engine redundancy. The engine equipment may be dual-redundant, and have two controlling channels (or "lanes"), either of which can perform the required function if the other fails. It should be recognized that, depending upon the circumstances, a FADEC system could be categorized as a Level A or C system. The level of engine redundancy could influence the category into which an associated FADEC system is categorised.

Figure C.3 – Electronic equipment (engine control)

#### C.2.2 Electronic secondary controls (flap/slat lift control)

The flow of air over the wing surfaces is controlled by flaps and slats. The positions of the majority of these are under the pilot's control; redundancy may be achieved by having more than one actuation method.

Figure C.4 – Electronically powered surface

Figure C.5 – Hydromechanical drive of surface – electronic valve control

#### **Bibliography**

- 1) ARP4754, Certification Considerations for Highly-Integrated or Complex Aircraft Systems

- 2) AC/AMJ 23.1309-1C, Equipment, Systems, and Installations (Part 23 Airplanes)

- 3) AC/AMJ 25.1309-1C, Equipment, Systems, and Installations (Part 25 Airplanes)

LICENSED TO MECON Limited. - RANCHI/BANGALORE FOR INTERNAL USE AT THIS LOCATION ONLY, SUPPLIED BY BOOK SUPPLY BUREAU.

LICENSED TO MECON Limited. - RANCHI/BANGALORE FOR INTERNAL USE AT THIS LOCATION ONLY, SUPPLIED BY BOOK SUPPLY BUREAU. INTERNATIONAL ELECTROTECHNICAL COMMISSION

3, rue de Varembé PO Box 131 CH-1211 Geneva 20 Switzerland

Tel: + 41 22 919 02 11 Fax: + 41 22 919 03 00 info@iec.ch www.iec.ch