# PUBLICLY AVAILABLE SPECIFICATION

# IEC PAS 62326-7-1

First edition 2007-04

Performance guide for singleand double-sided flexible printed wiring boards

Reference number IEC/PAS 62326-7-1:2007(E)

## THIS PUBLICATION IS COPYRIGHT PROTECTED Copyright © 2007 IEC, Geneva, Switzerland

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from either IEC or IEC's member National Committee in the country of the requester.

If you have any questions about IEC copyright or have an enquiry about obtaining additional rights to this publication, please contact the address below or your local IEC member National Committee for further information.

IEC Central Office 3, rue de Varembé CH-1211 Geneva 20 Switzerland Email: inmail@iec.ch Web: www.iec.ch

#### About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes International Standards for all electrical, electronic and related technologies.

#### **About IEC publications**

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the latest edition, a corrigenda or an amendment might have been published.

Catalogue of IEC publications: <u>www.iec.ch/searchpub</u>

The IEC on-line Catalogue enables you to search by a variety of criteria (reference number, text, technical committee,...).

It also gives information on projects, withdrawn and replaced publications.

• IEC Just Published: <u>www.iec.ch/online\_news/justpub</u> Stay up to date on all new IEC publications. Just Published details twice a month all new publications released. Available on-line and also by email.

Customer Service Centre: www.iec.ch/webstore/custserv

If you wish to give us your feedback on this publication or need further assistance, please visit the Customer Service Centre FAQ or contact us:

Email: <u>csc@iec.ch</u> Tel.: +41 22 919 02 11 Fax: +41 22 919 03 00

# PUBLICLY AVAILABLE SPECIFICATION

# IEC PAS 62326-7-1

First edition 2007-04

Performance guide for singleand double-sided flexible printed wiring boards

Commission Electrotechnique Internationale International Electrotechnical Commission Международная Электротехническая Комиссия PRICE CODE

For price, see current catalogue

Х

## CONTENTS

| FOI | OREWORD5              |                                                                                                                                       |     |

|-----|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1   | Scope6                |                                                                                                                                       |     |

| 2   | Normative references6 |                                                                                                                                       |     |

| 3   | Term                  | s and definitions                                                                                                                     | 6   |

| 4   | Test                  | methods                                                                                                                               | 6   |

| 5   | Perfo                 | rmance levels                                                                                                                         | 7   |

| 6   | Base                  | materials                                                                                                                             | 7   |

| 7   | Visua                 | Il inspection                                                                                                                         | 7   |

|     | 7.1                   | Test environment                                                                                                                      | 7   |

|     | 7.2                   | Test specimens                                                                                                                        |     |

|     | 7.3                   | Tools for testing                                                                                                                     | 7   |

|     | 7.4                   | Preparation of limit samples                                                                                                          | 7   |

|     | 7.5                   | Description of inspection                                                                                                             | 7   |

| 8   | Dime                  | nsional inspections                                                                                                                   | .23 |

|     | 8.1                   | Measurement of dimension                                                                                                              | .23 |

|     | 8.2                   | External dimension                                                                                                                    | .23 |

|     | 8.3                   | Thickness                                                                                                                             | .24 |

|     | 8.4                   | Hole diameter                                                                                                                         | .24 |

|     | 8.5                   | Conductor width                                                                                                                       | .24 |

|     | 8.6                   | Cumulative pattern pitch                                                                                                              | .24 |

|     | 8.7                   | Distance between hole centers                                                                                                         | .25 |

|     | 8.8                   | Design minimum distance between board edge and conductor                                                                              | .26 |

|     | 8.9                   | Position accuracy                                                                                                                     | .26 |

|     | 8.10                  | Registration of pressure sensitive or heatactivated adhesive (Including adhesive squeeze-out) to flexible printed board and stiffener | .28 |

| 9   | Elect                 | rical performance test                                                                                                                | .29 |

| 10  | Mech                  | anical performance test                                                                                                               | .30 |

| 11  | Envir                 | onmental performance                                                                                                                  | .31 |

| 12  | Chen                  | nical resistance                                                                                                                      | .31 |

| 13  | Clear                 | nliness                                                                                                                               | .31 |

| 14  | Flam                  | e resistance                                                                                                                          | .31 |

| 15  | Mark                  | ng, packaging, and storage                                                                                                            | .31 |

|     |                       | Marking on products                                                                                                                   |     |

|     |                       | Marking on package                                                                                                                    |     |

|     |                       | Packaging and storage                                                                                                                 |     |

| Anr | nex A                 | Handling instruction manual handling of polyimide-base FPC                                                                            | .33 |

| Anr | nex B                 | lon migration test                                                                                                                    | .35 |

| Anr | nex C                 | Whisker test                                                                                                                          | .36 |

| Anr |                       | Additional information – Explanation on JPCA performance guide for single-<br>louble-sided flexible printed wiring boards             | .38 |

| -   |                       | - Nicks and pinholes in conductor                                                                                                     |     |

| Fig | ure 2 -               | - Reduced area on land                                                                                                                | 8   |

| Figure 3 – Circumferential void at the component hole                                                                                                | 8  |

|------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 4 – Unnecessary copper between conductor/spur and nodule of conductor                                                                         | 9  |

| Figure 5 – Unnecessary copper, spurs and nodules in an open area and nodules of conductor corners                                                    | 9  |

| Figure 6 – Etched concave surface of the conductor and nodule at a conductor corner                                                                  | 10 |

| Figure 7 – Conductor delamination                                                                                                                    | 10 |

| Figure 8 – Scratch on conductor                                                                                                                      | 11 |

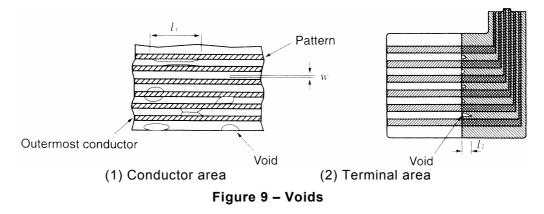

| Figure 9 – Voids                                                                                                                                     | 11 |

| Figure 10 – Foreign substance                                                                                                                        | 12 |

| Figure 11 – Lifting and delamination of coverlay and covercoat                                                                                       | 13 |

| Figure 12 – Allowable squeeze-out of coverlay adhesive and ooze-out of covercoat and photosensitive resist                                           |    |

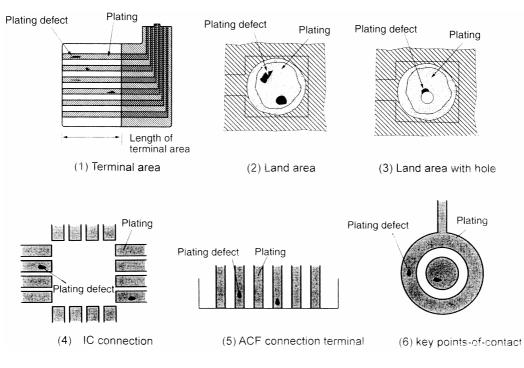

| Figure 13 – Plating defects                                                                                                                          | 14 |

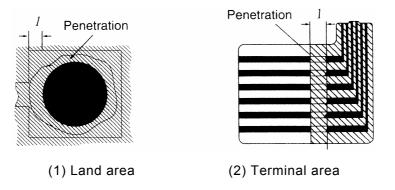

| Figure 14 – Penetration of plated metal or solder                                                                                                    | 16 |

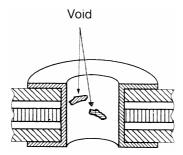

| Figure 15 – Plating voids in plated through hole                                                                                                     |    |

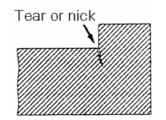

| Figure 16 – Tear and nick                                                                                                                            | 17 |

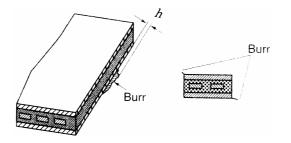

| Figure 17 – Burrs                                                                                                                                    | 17 |

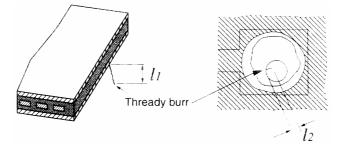

| Figure 18 – Thready burrs                                                                                                                            | 18 |

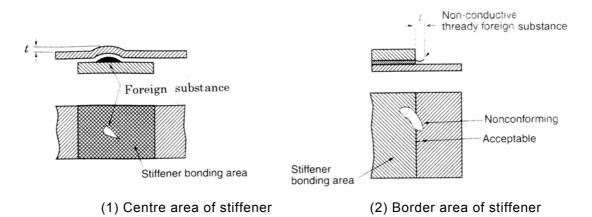

| Figure 19 – Foreign substance between board and stiffener                                                                                            | 18 |

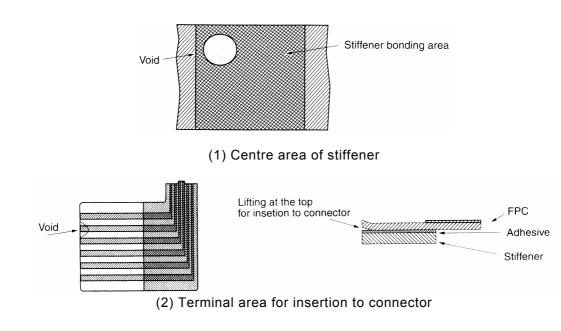

| Figure 20 – Voids between board and stiffener                                                                                                        |    |

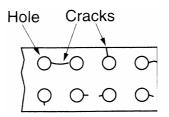

| Figure 21 – Cracks                                                                                                                                   | 19 |

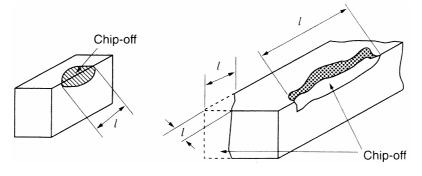

| Figure 22 – Chip-off                                                                                                                                 | 20 |

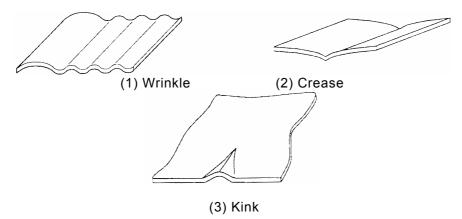

| Figure 23 – Protrusion and dent on flexible printed board                                                                                            |    |

| Figure 24 – Bow and twist                                                                                                                            | 22 |

| Figure 25 – Dent                                                                                                                                     |    |

| Figure 26 – Scratch on base film                                                                                                                     |    |

| Figure 27 – Cumulative pitch                                                                                                                         | 26 |

| Figure 28 – Misregistration of hole and land                                                                                                         | 26 |

| Figure 29 – Misregistration of land and coverlay (or covercoat)                                                                                      | 27 |

| Figure 30 – Registration of holes                                                                                                                    | 27 |

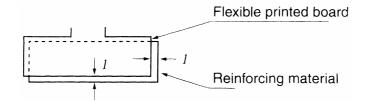

| Figure 31 – Registration of pressure-sensitive or heat-activated adhesive from flexible printed board and stiffener (including adhesive squeeze-out) |    |

| Figure 32 – Registration of pressure-sensitive or heat-activated adhesive from flexible printed board and stiffener (including adhesive squeeze-out) | 28 |

| Figure B.1 – Structure of specimen for ion migration test.                                                                                           | 35 |

| Figure C.1 – Basic structure of the test equipment                                                                                                   | 36 |

| Figure C.2 – Example of the construction of the test equipment                                                                                       | 36 |

| Table 1 – Allowable nicks and pinholes                                                                                                               | 8  |

| Table 2 – Allowable unnecessary copper, spur and nodule between conductors                                                                           | 9  |

| Table 3 – Allowable etched concave of the surface conductor                                                                                          | 10 |

| Table 4 – Allowable conductor delamination                                                                                                           | 10 |

| Table 5 – Allowable scratch on conductor                                                                                                             | 11 |

Table 6 – Allowable discoloration

11

- 3 -

| Table 7 – Allowable void                                                            | 12 |

|-------------------------------------------------------------------------------------|----|

| Table 8 – Allowable non-conductive foreign substance                                | 12 |

| Table 9 – Allowable squeeze-out of coverlay adhesive, and ooze-out of covercoat and | 40 |

| photosensitive register strike                                                      |    |

| Table 10 – Effective land width at a land                                           |    |

| Table 11 – Gold plating                                                             |    |

| Table 12 – Requirement for metal penetration between conductor and coverlay         |    |

| Table 13 – Requirements for metal penetration between conductor and base film       |    |

| Table 14 – Gold plating                                                             |    |

| Table 15 – Allowable plating voids                                                  |    |

| Table 16 – Cracks                                                                   |    |

| Table 17 – Thermosetting adhesive on surface                                        |    |

| Table 18 – Flux residue on surface                                                  |    |

| Table 19 – Residue of metal powder (solder, aluminum, copper, etc.)                 | 21 |

| Table 20 – Residue of adhesive                                                      | 21 |

| Table 21 – Dent                                                                     |    |

| Table 22 – Dent                                                                     | 22 |

| Table 23 – Allowable scratches on base film                                         |    |

| Table 24 – Dents on coverlay and covercoat                                          | 23 |

| Table 25 – Requirement for scratch on coverlay and covercoat                        | 23 |

| Table 26 – Tolerance of external dimension                                          | 24 |

| Table 27 – Thickness tolerance                                                      | 24 |

| Table 28 – Hole diameter and tolerance                                              | 24 |

| Table 29 – Conductor width and tolerance                                            | 24 |

| Table 31 – Tolerance of distance between hole centers                               | 25 |

| Table 32 – Design minimum distance between board edge and conductor                 | 26 |

| Table 33 – Effective land area                                                      | 27 |

| Table 34 – Allowable displacement between outlines of the stiffener and the FPC     | 27 |

| Table 35 – Registration of punched outline to conductor patterns                    | 28 |

| Table 36 – Electrical properties of flexible printed boards                         | 29 |

| Table 37 – Mechanical properties of flexible printed boards                         | 30 |

| Table 38 – Environmental tests and requirements                                     |    |

| Table 39 – Requirements for packaging                                               | 32 |

| Table A.1 – Recommended pre-drying conditions                                       |    |

|                                                                                     |    |

- 4 -

## INTERNATIONAL ELECTROTECHNICAL COMMISSION

## PERFORMANCE GUIDE FOR SINGLE- AND DOUBLE-SIDED FLEXIBLE PRINTED WIRING BOARDS

## FOREWORD

- 1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as "IEC Publication(s)"). Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely with the International Organization for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC National Committees.

- 3) IEC Publications have the form of recommendations for international use and are accepted by IEC National Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

- 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter.

- 5) IEC provides no marking procedure to indicate its approval and cannot be rendered responsible for any equipment declared to be in conformity with an IEC Publication.

- 6) All users should ensure that they have the latest edition of this publication.

- 7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and members of its technical committees and IEC National Committees for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC Publications.

- 8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.

- 9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

A PAS is a technical specification not fulfilling the requirements for a standard but made available to the public.

IEC-PAS 62326-7-1 was submitted by the JPCA (Japan Electronics Packaging and Circuits Association) and has been processed by IEC technical committee 91: Electronics assembly technology.

| The text of this PAS is based on the following document: | This PAS was approved for<br>publication by the P-members of the<br>committee concerned as indicated in<br>the following document: |

|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Draft PAS                                                | Report on voting                                                                                                                   |

| 91/615A/NP                                               | 91/643/RVN                                                                                                                         |

Following publication of this PAS, the technical committee or subcommittee concerned will investigate the possibility of transforming the PAS into an International Standard

This PAS shall remain valid for an initial maximum period of three years starting from 2007-04. The validity may be extended for a single three-year period, following which it shall be revised to become another type of normative document or shall be withdrawn.

## PERFORMANCE GUIDE FOR SINGLE- AND DOUBLE-SIDED FLEXIBLE PRINTED WIRING BOARDS

#### 1 Scope

This PAS provides the requirements for the single- and double-sided flexible printed wiring boards (hereinafter designated as "flexible printed board" or FPC).

In this document, an FPC means a single- or double-sided FPC prepared by lamination of a film of polyester or polyimide with copper foil(s) on one or both sides of a board including the type with no adhesive layer, and with conductor pattern formed by the subtractive method (etching of the copper foil), or possibly by the build-up method.

#### 2 Normative references

The following referenced documents are indispensable for the application of this document. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

IEC 60326-7:1981, Printed boards – Part 7: Specification for single- and double-sided flexible printed boards without through connections

IEC 60326-8:1981, Printed boards – Part 8: Specification for single- and double-sided flexible printed boards with through connections

JPCA-TD01:2000, Terms and definitions for printed circuits

JPCA-BM03:2003, *Flexible printed wiring boards (adhesive and adhesiveless types)*

JIS C 5016:1994, Test methods for flexible printed wiring boards

JIS C 5017:1994, Single- and double-sided flexible printed wiring boards

JIS C 5603:1993, Terms and definitions for printed circuits

JIS C 6471:1995, Test methods of copper-clad laminates for flexible printed wiring boards

JIS C 6472:1995, Copper-clad laminates for flexible printed wiring boards (polyester film, polyimide film)

JIS C 6515:1998, Copper foil for printed wiring boards

### 3 Terms and definitions

For the purposes of this document, the terms and definitions given in JIS C 5603, JIS C 5017, JIS C 5016, and JPCA-FC03 apply.

#### 4 Test methods

The test methods used in this document as specified below shall be in conformance with JIS C 5016.

- a) Test methods requiring complicated referencing procedures are reproduced in this document.

- b) Tests on through connection apply only to double-sided FPCs.

c) External appearance is the only requirement specified in this document for stiffeners affixed to FPCs.

### 5 Performance levels

The FPCs are classified into three levels, Levels 1, 2, and 3, and an additional special level, Level X, for applications requiring special attention. They are defined as:

Level 1 – FPCs requiring "ordinary" performance;

Level 2 – FPCs requiring "high" performance;

Level 3 – FPCs requiring "extra-high" performance;

Level X - FPCs requiring special performances which do not belong to the abovementioned three levels, and the specifications requiring an agreement between user and supplier.

A relevant level of the board is chosen for a specific application of the board. A different level can be selected for a specific section of the board when the required specification of the section is different from that of another part of the board.

#### 6 Base materials

The base materials used in FPCs shall satisfy the requirements specified in JPCA-BM03.

#### 7 Visual inspection

#### 7.1 Test environment

The test environment shall meet the requirements of JIS C 5016, Clause 3.

#### 7.2 Test specimens

The test specimens shall meet the requirements of JIS C 5016, Clause 4.

#### 7.3 Tools for testing

#### 7.4 Preparation of limit samples

Limit samples showing the required criteria to make technical judgments may be prepared under agreement between user and supplier for the application of this document.

#### 7.5 Description of inspection

Requirements, procedures, and illustration for visual inspections are given in 7.5.1 through 7.5.6. Requirements that are not designated for a specific performance level shall apply to all the performance Levels 1, 2 and 3.

## 7.5.1 Visual inspection of conductor

### 7.5.1.1 Open and short circuit

There shall be no open and/or short circuit on FPCs.

#### 7.5.1.2 Nicks and pinholes on conductor

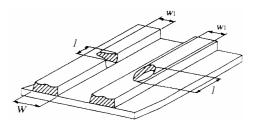

a) The allowable width  $(w_1)$  and length (l) of a nick and a pinhole of the conductor reducing conductor width, as shown in Figure 1, shall meet the requirement given in Table 1 for the finished conductor width (W) (see Note 1).

- 8 -

NOTE 1 The width of the finished conductors should be measured at the bottom of the conductor.

#### Figure 1 – Nicks and pinholes in conductor

#### Table 1 – Allowable nicks and pinholes

| Level   | Nicks and pinholes         |

|---------|----------------------------|

| 1 and 2 | $w1 \leq 1/2W$ $l \leq 2W$ |

| 3       | $w1 \leq 1/3W$ $l \leq W$  |

b) The void area on a land, as illustrated in Figure 2, shall not exceed 10 % of the effective exposed land area.

Figure 2 – Reduced area on land

c) The circumferential void of a lead insertion hole, as illustrated in Figure 3, shall not exceed one-third of the total circumference.

Figure 3 – Circumferential void at the component hole

### 7.5.1.3 Distance between conductor/spur and nodule of conductor

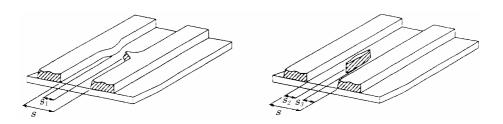

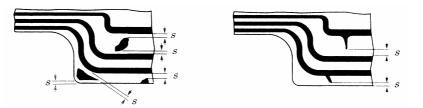

The distance  $(s_1)$  or  $(s_2 + s_3)$  in Figure 4 relative to the finished conductor spacing(s) shall meet the requirement given in Table 2.

Figure 4 – Unnecessary copper between conductor/spur and nodule of conductor

## Table 2 – Allowable unnecessary copper, spur and nodule between conductors

| Level   | Unnecessary copper, spurs and nodules, $s_1$ or ( $s_2$ + $s_3$ ) |

|---------|-------------------------------------------------------------------|

| 1 and 2 | $1/2 \ s_1 \leq a \ or \ (s_2 + s_3)$                             |

| 3       | $2/3 \ s_1 \leq a \ or \ (s_2 + s_3)$                             |

## 7.5.1.4 Unnecessary copper between conductor/spur and nodule of conductor in an open area

The spacing(s) between the board edges and the unnecessary copper or spur and nodule shall be larger than 0,125 mm in an open area where no conductor pattern is routed, as illustrated in Figure 5. The spacing(s) between the board edge and the unnecessary copper or spur and nodule shall be larger than 0,125 mm. The open area as stated in this clause shall have a width of no less than 0,375 mm.

Figure 5 – Unnecessary copper, spurs and nodules in an open area and nodules of conductor corners

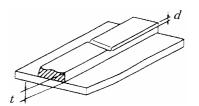

### 7.5.1.5 Etched concave surface of the conductor

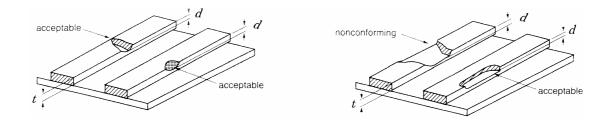

Etched concave surface (d) of the conductor relative to the conductor thickness (t), as illustrated in Figure 6, shall meet the requirement given in Table 3. The concave surface shall not run across the entire width of a conductor.

- 10 -

#### Figure 6 – Etched concave surface of the conductor and nodule at a conductor corner

#### Table 3 – Allowable etched concave of the surface conductor

| Level   | Etched concave surface of the conductor, <i>d</i><br>( <i>t</i> : conductor thickness) |

|---------|----------------------------------------------------------------------------------------|

| 1 and 2 | $d \leq 1/3 t$                                                                         |

| 3       | $d \leq 1/5 t$                                                                         |

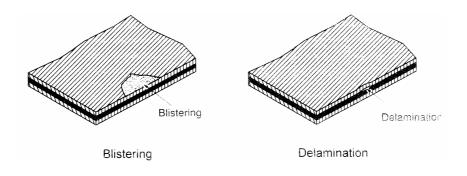

#### 7.5.1.6 Conductor delamination

The width  $(w_1)$  and length (l) of conductor delamination relative to the finished conductor width (W), as illustrated in Figure 7, shall meet the requirement given in Table 4.

Figure 7 – Conductor delamination

| Level   | Conductor delamination, length (I), width (w <sub>1</sub> )                            |

|---------|----------------------------------------------------------------------------------------|

| 1       | Coverlay laminated area                                                                |

|         | $l \leq W$ and $w 1/W \leq 1/3$ for flexing area                                       |

|         | $l \leq W$ and $w 1/W \leq 1/2$ for other area                                         |

|         | No coverlay laminated area                                                             |

|         | $l/W \leq 1/4$ and $w_1/W \leq 1/4$                                                    |

| 2 and 3 | There shall be no delamination in the conductor which can be observed by the naked eye |

PAS 62326-7-1 © IEC:2007(E) - 11 -

## 7.5.1.7 Conductor crack

There shall be no crack in the conductor.

### 7.5.1.8 Scratch on conductor

A scratch on a conductor surface, as illustrated in Figure 8, indicates the damage made by a sharp metal point and is harmful to the performance of the printed circuit. The depth (d) of a scratch shall meet the requirement given in Table 5 relative to the conductor thickness (t). The scratch shall not damage the bending property of the repeatedly flexing portion.

Figure 8 – Scratch on conductor

| Level   | Depth of scratch on conductor, <i>d</i> |

|---------|-----------------------------------------|

| 1 and 2 | $d \leq 1/3 t$                          |

| 3       | $d \leq 1/5 t$                          |

## 7.5.1.9 Discoloration

Discoloration shall meet the requirement given in Table 6.

#### Table 6 – Allowable discoloration

| Level   | Discoloration                                                                                                                                                                                            |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 and 2 | When discoloration is observed on a conductor laminated with coverlay, the discoloration shall be acceptable unless it is remarkably noticeable after conditioning at 40 $^\circ C$ with 90% RH for 96 h |

| 3       | The acceptable discoloration shall be agreed upon between user and supplier by means of a limit sample                                                                                                   |

## 7.5.2 Visual inspection of coverlay and covercoat

#### 7.5.2.1 Void

Void, as illustrated in Figure 9, shall meet the requirement given in Table 7.

- 12 -

| Level | Voids                                                                                                                                                                                                                                                                                                                                                                                       |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1     | A void extending over two or more conductors shall not exist. A void both on<br>the outline edge and to a conductor shall not exist. (A void at the terminal area,<br>as illustrated in Figure 9 (2), shall be acceptable even if it extends to two<br>conductors)                                                                                                                          |  |

|       | The maximum length $(l_2)$ of a void shall be 0,3 mm                                                                                                                                                                                                                                                                                                                                        |  |

| 2     | The length of a void $(l_i)$ shall be no longer than 10 mm. The width of a void $(w)$ shall be no longer than one-third of the spacing between the conductors.<br>There shall be no void in a contact extending to two neighbouring conductors.<br>The maximum length $(_2)$ of a void shall be 0,3 mm. A void at the repeatedly bending area shall not damage the flexibility of the board |  |

| 3     | There shall be no void                                                                                                                                                                                                                                                                                                                                                                      |  |

#### 7.5.2.2 Foreign substance

Foreign substance, as illustrated in Figure 10, shall meet the following requirements.

- a) **Conductive foreign substance:** Requirements 7.5.1.3 and 7.5.1.4 of this specification shall apply to conductive foreign substances.

- b) **Non-conductive foreign substance:** Non-conductive foreign substances shall meet the requirement given in Table 8.

Figure 10 – Foreign substance

| Jnit: mm |                 |                |                                                                             |

|----------|-----------------|----------------|-----------------------------------------------------------------------------|

| Level    | Thickness t     | Width w        | Length <i>l</i>                                                             |

| Level 1  | <i>t</i> ≦ 0,1  | <i>w</i> ≦ 0,3 | $l \leq 3$                                                                  |

| Level 2  | <i>t</i> ≦ 0,05 | <i>w</i> ≦ 0,2 | <i>l</i> ≦ 2                                                                |

| Level 3  | <i>t</i> ≦ 0,05 | w ≦ 0,05       | <i>l</i> ≦ 1                                                                |

|          |                 |                | A foreign sub-<br>stance shall not<br>extend to three or<br>more conductors |

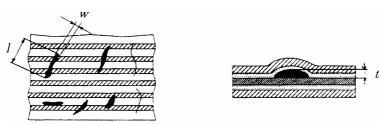

#### 7.5.2.3 Blistering and delamination

There shall be no visible blistering and delamination of coverlay or covercoat along the edge of the FPC, as illustrated in Figure 11. The covercoat shall not be peeled off when using the test tape specified in JIS C 5016, 8.5.1.

## Figure 11 – Lifting and delamination of coverlay and covercoat

## 7.5.2.4 Squeeze-out of adhesive of coverlay, ooze-out of covercoat and photosensitive register strike

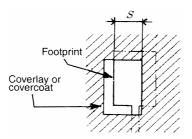

Squeeze-out of adhesive, ooze-out (l) of covercoat and photosensitive register strike, as illustrated in Figure 12, shall comply with the specification given in Table 9.

The squeeze-out and ooze-out at a land as illustrated in Figure 12-1 shall comply with the specification given in Table 10 for the effective land width (w), including possible printing and/or punching errors.

## Figure 12 – Allowable squeeze-out of coverlay adhesive and ooze-out of covercoat and photosensitive resist

## Table 9 – Allowable squeeze-out of coverlay adhesive, and ooze-out of covercoat and photosensitive register strike

| <u>Unit: mm</u> | it: mm                                                        |                                                 |  |  |

|-----------------|---------------------------------------------------------------|-------------------------------------------------|--|--|

| Level           | Squeeze-out of coverlay adhesive<br>and ooze-out of covercoat | Ooze-out of a photosensitive<br>register strike |  |  |

| 1 and 2         | <i>l</i> ≦ 0,3                                                | _                                               |  |  |

| 3<br>3          | $l \leq 0.2 \\ \leq 0.2$                                      | <i>l</i> ≦ 0,1<br>≦ 0,1                         |  |  |

#### Table 10 – Effective land width at a land

| Level | Effective land width, w                                                                                            |  |

|-------|--------------------------------------------------------------------------------------------------------------------|--|

| 1     | Squeeze-out/ooze-out contacting the hole edge is acceptable up to one-<br>third of the terminal hole circumference |  |

| 2     | 0,05 mm min.                                                                                                       |  |

| 3     | 0,1 mm min.                                                                                                        |  |

## 7.5.2.5 Skipping of covercoat photosensitive register strike

When tested in accordance with JIS C 5016, 10.4, no solder shall stick onto the conductor of the covercoat and photoresist in the skipped area.

- 14 -

## 7.5.3 Visual inspection of plating

## 7.5.3.1 Plating defect

Plating defect shall meet the requirements given in 7.5.3.1.1 and 7.5.3.1.2.

Figure 13 – Plating defects

## 7.5.3.1.1 Gold plating

Gold plating shall meet the requirement given in Table 11.

| Level | Gold plating                                                                                                                                                                                                     |                                 |                  | Examples<br>in Figure<br>13 |                       |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------------|-----------------------------|-----------------------|--|

| 1     | Plating defects on the land area, as shown in Figure 13 (2) and (3) shall be no<br>larger than 10 % of the total plated area (excluding the skipped plating area for a<br>defect caused by adhesive squeeze-out) |                                 |                  | (2), (3)                    |                       |  |

| 2     | The width $(w_1)$ and length $(l)$ of the plating defects in comparison to the finished line conductor width $(w)$ are specified in the table below                                                              |                                 |                  | the finished line           | (1), (5), (6)         |  |

|       |                                                                                                                                                                                                                  |                                 |                  |                             |                       |  |

|       | Width and length of plating defects                                                                                                                                                                              |                                 |                  |                             |                       |  |

|       | Unit: mm                                                                                                                                                                                                         |                                 |                  | -                           |                       |  |

|       | ItemFinished line width, w $w < 0,30$ $0,30 \le w \le 0,45$ $0,45 < w$                                                                                                                                           |                                 |                  |                             |                       |  |

|       |                                                                                                                                                                                                                  |                                 | w < 0,30         | 0,30 ≦ <i>w</i> ≦0,45       | 0,45 < w              |  |

|       | Terminals                                                                                                                                                                                                        | Width of plating defect $(w_1)$ | $w_1 \leq 1/2 w$ | w <sub>1</sub> ≦0,15        | w <sub>1</sub> ≦1/3 w |  |

|       | Length of plating defect $(l)$ $w_1 \leq w$                                                                                                                                                                      |                                 |                  |                             |                       |  |

|       | There shall be no defect of an area larger than 0,02 mm <sup>2</sup> for a terminal area of a large area such as a key contact                                                                                   |                                 |                  |                             |                       |  |

| 3     | There shall be no defect such as poor contact and pit (hole or dent) that can be detected using a magnifying glass of 3× to 10× in the area of direct contact                                                    |                                 |                  | (1), (4), (5)               |                       |  |

| Х     | The limit of a defect shall be agreed upon between user and supplier for special requirements                                                                                                                    |                                 |                  | -                           |                       |  |

## Table 11 – Gold plating

# 7.5.3.1.2 Solder plating (solder paste or dip solder plating including use of lead free solder)

The width of a plating defect at the terminal area, as shown in Figure 13(1), shall be no larger than one-half of the finished conductor width, and the length shall not exceed the width of the conductor.

Plating defects on land area, as shown in Figures 13(2) and (3), shall be less than 10 % of the total plated area (excluding the skipped plating area caused by adhesive squeeze-out).

Plating defects contacting the edge of a component hole, as shown in Figure 13(3), shall be no larger than one-third of the circumference. The area of a plating defect shall be covered with adhesive.

# 7.5.3.2 Penetration of plated metal or solder plating (Solder paste or dip solder plating including the use of lead free solder)

Penetration of plated metal or solder plating, as illustrated in Figure 14, shall meet the following requirements.

## Figure 14 – Penetration of plated metal or solder

a) The penetrated portion (*l*) between conductor and coverlay (covercoat and photosensitive resist) shall meet the requirement given in Table 12, as illustrated in Figure 14.

## Table 12 – Requirement for metal penetration between conductor and coverlay

| Unit: mm |                                             |

|----------|---------------------------------------------|

| Level    | Requirement for metal penetration, <i>l</i> |

| 1        | $l \leq 0,5$                                |

| 2        | $l \leq 0,3$                                |

| 3        | <i>l</i> ≦ 0,1                              |

b) The penetrated portion between the conductor and the base film shall meet the requirement given in Table 13.

### Table 13 – Requirements for metal penetration between conductor and base film

| Level   | Requirement for metal penetration     |

|---------|---------------------------------------|

| 1       | Shall meet the requirement of 7.5.1.6 |

| 2 and 3 | There shall be no visible penetration |

## 7.5.3.3 Surface condition of plated metal and solder plating

#### 7.5.3.3.1 Gold plating

Gold plating shall meet the requirement given in Table 14.

#### Table 14 – Gold plating

| Level   | Gold plating                                                                                                                                                                 |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 and 2 | Defect, such as stain, haze, and dirt which can be easily detected by the naked eye without the use of a magnification glass should be judged on the basis of a limit sample |

| 3       | There shall be no defect, such as stain, haze, discoloration, and dirt, detectable by observation with a magnification of 10×                                                |

| X       | The special requirement for any specific application shall be agreed upon between user and supplier                                                                          |

## 7.5.3.3.2 Solder plating (solder paste or dip solder plating including use of lead-free solder)

There shall be no darkened appearance (blackening discoloration).

### 7.5.3.3.3 Void in plated through hole

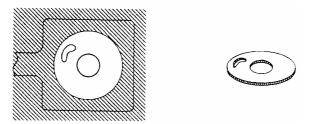

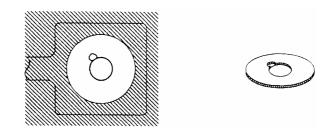

The number of plating voids illustrated in Figure 15 shall be no more than three per hole. The total area of voids for the entire hole wall ( $S_{sum}$ ) for the total inner wall area of a hole ( $S_{total}$ ) shall meet the requirement given in Table 15.

Figure 15 – Plating voids in plated-through hole

Table 15 – Allowable plating voids

| Level   | Total void area, S <sub>sum</sub> |

|---------|-----------------------------------|

| 1 and 2 | $S_{sum}$ < 1/3 $S_{total}$       |

| 3       | $S_{sum}$ < 10 $S_{total}$        |

### 7.5.4 Visual inspection of edges of outline and holes

#### 7.5.4.1 Tear and nick

There shall be no tear and nick except for slight cuts formed at the joining of blades which are allowed provided they are not visible without magnification, as illustrated in Figure 16.

Figure 16 – Tear and nick

#### 7.5.4.2 Burr

The height (*h*) of burr, as illustrated in Figure 17, shall be no larger than 0,1 mm.

Figure 17 – Burrs

## 7.5.4.3 Thready burr

Two types of non-conductive thready burrs are illustrated in Figure 18. The length of thready burr at the outline edge  $(l_1, l_2)$  shall be no longer than 1,0 mm. The length of burr at the hole edge  $(l_2)$  shall be no longer than 0,3 mm.

- 18 -

(1) Thready burr at outline edge

(2) Thready burr at hole edge

Figure 18 – Thready burrs

## 7.5.5 Visual imperfection related to stiffener bonding

## 7.5.5.1 Foreign substance between flexible printed board and stiffener

The bulge (t) of the FPC caused by a foreign substance sandwiched between the FPC and the stiffener, as illustrated in Figure 19, shall be no larger than 0,1 mm. The thickness of the stiffener shall also meet those specifications when the thickness of the printed board and stiffener are specified.

The size of the foreign substance shall be no larger than 5 % of the bonding area of the printed board and stiffener. There shall be no foreign substance in contact with the component hole or an outline edge of the board.

The length of a non-conductive thready foreign substance (l) protruding from the outline edge shall not exceed 1 mm.

Figure 19 – Foreign substance between board and stiffener

## 7.5.5.2 Void between flexible printed board and stiffener

When the stiffener is bonded to FPC with thermosetting adhesive, the total area of voids, as illustrated in Figure 22, shall be no larger than 10 % of the total area of the stiffener. When other types of adhesive are used, the total area of voids shall be no larger than one-third of the stiffener area. There shall be no lifting and swelling at the tip for insertion to the connector.

- 19 -

Figure 20 – Voids between board and stiffener

## 7.5.5.3 Defect of stiffener

## 7.5.5.3.1 Crack

Cracks, as illustrated in Figure 21, shall meet the requirement given in Table 16.

Figure 21 – Cracks

Table 16 – Cracks

| Level   | Cracks                                                                                               |

|---------|------------------------------------------------------------------------------------------------------|

| 1       | There shall be no crack that could affect practical use                                              |

| 2 and 3 | There shall be no crack that links two holes on the stiffener as well as a hole and the outline edge |

## 7.5.5.3.2 Chip-off

The length (l) of a chip-off of stiffener, as illustrated in Figure 22, shall be no larger than 1 mm.

- 20 -

Figure 22 – Chip-off

## 7.5.5.3.3 Scratch

The allowable scratch shall be agreed upon between user and supplier if necessary.

### 7.5.5.3.4 Bow and twist

Bow and twist causing no problem in board assembly and instalment are acceptable.

### 7.5.6 Other visual inspection

### 7.5.6.1 Fixed substance on surface (excluding the area of exposed conductor)

### 7.5.6.1.1 Thermosetting adhesive

Thermosetting adhesive on the surface shall meet the requirement given in Table 17.

| Level   | Thermosetting adhesive on the surface                                                                                                                                                                                                                                                                                                         |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 and 2 | Cured adhesive, chip of coverlay, covercoat or fibre stuck with adhesive hardly<br>adhered on the surface is acceptable, provided they do not fall off when rubbed with<br>an applicator impregnated with isopropyl alcohol. The thickness including the<br>adhesive on surface shall meet the requirement where total thickness is specified |

| 3       | There shall be no visible substance stuck to the adhesive on the surface                                                                                                                                                                                                                                                                      |

#### 7.5.6.1.2 Flux residues

Flux residue on the surface shall meet the requirement given in Table 18.

#### Table 18 – Flux residue on surface

| Level   | Thermosetting adhesive on the surface                                                                                                   |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 1 and 2 | When the surface is rubbed with an applicator impregnated with isopropyl alcohol, the applicator shall not be stained with flux residue |

| 3       | There shall be no visible flux residue on surface                                                                                       |

## 7.5.6.1.3 Residue of metal powder (solder, aluminum, copper, etc.)

The following requirement shall apply only when the metal powder falling off the board does not cause any problem in the performance of equipment mounted with the flexible printed circuit of the interest. The residue of the metal powder shall meet the requirement given in Table 19.

| Level | Residue of metal powder (solder, aluminum, copper, etc.)                                                             |

|-------|----------------------------------------------------------------------------------------------------------------------|

| 1     | The acceptable size and the number of metal grains shall be as follows:                                              |

|       | <ul> <li>– for the grain diameter of 0,1 mm or larger and smaller than 0,03mm: 3 or less per<br/>product;</li> </ul> |

|       | <ul> <li>– for the grain diameter of 0,05 mm or larger and smaller than 0,1mm: 10 or less per<br/>product</li> </ul> |

| 2     | There shall be no visible metal powder residue                                                                       |

| 3     | There shall be no metal powder residue detectable with a magnification 10×                                           |

Table 19 – Residue of metal powder (solder, aluminum, copper, etc.)

## 7.5.6.1.4 Residue of adhesive

The residue of the adhesive shall meet the requirement given in Table 20.

| Level   | Residue of adhesive                                                                    |

|---------|----------------------------------------------------------------------------------------|

| 1 and 2 | The acceptable size and the number of adhesive residue shall be as follows:            |

|         | - for the diameter of 1,0 mm or larger and smaller than 2,0 mm: 1 or less per product; |

|         | - for the diameter of 0,1 mm or larger and smaller than 1,0 mm: 5 or less per product  |

| 2       | There shall be no visible adhesive residue                                             |

## 7.5.6.2 Protrusion and dent

Wrinkle, uneven and crease which influence the characteristics on use and on the assembly process of a flexible print board are not permitted, even if there is no problem at the time of mounting and at use. A limit sample for these defects should be prepared if necessary. Examples of protrusions and dents are illustrated in Figure 23.

#### 7.5.6.3 Bow and twist

Bow, twist and the like, as illustrated in Figure 24, which may influence the characteristics on use and on the assembly process of a flexible print board are permitted if there is no problem at the time of mounting and at use in the field.

- 22 -

Figure 24 – Bow and twist

### 7.5.6.4 Conductor

Dent: Dent on a conductor, as illustrated in Figure 25, shall meet the requirement given in Table 21. Dent condition is usually difficult to judge (i.e., shape, size, and depth); accordingly, details should be agreed upon between user and supplier with reference to a limit sample prepared for evaluation.

Figure 25 – Dent

Table 21 – Dent

| Level   | Depth of a dent, d                                                                                                                                                                                            |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 and 2 | Depth (d) of a dent from the surface shall be $\leq 0,1$ mm. When depth is difficult to measure, the height (h) of the back protrusion of the base film shall be regarded as equal to the depth (d) of a dent |

| 2       | There shall be no dent visible from both sides                                                                                                                                                                |

## 7.5.6.5 Base film side

a) Dent: Dent on the base film, as illustrated in Figure 25, shall meet the requirement given in Table 22.

| Table 22 – De | ent |

|---------------|-----|

|---------------|-----|

| Level   | Dent                                                                                                                                                                                                                        |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 and 2 | Depth $(d)$ of a dent from the surface shall be no larger than 0,1 mm. When depth is difficult to measure, the height $(h)$ of the back protrusion of the base film shall be regarded as equal to the depth $(d)$ of a dent |

| 2       | There shall be no dent visible from both sides                                                                                                                                                                              |

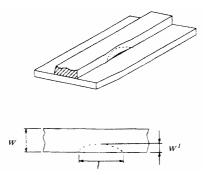

b) Scratch on base film: The depth (*d*) of a scratch on a base film relative to the film thickness (*t*), as illustrated in Figure 26, shall meet the requirement given in Table 23. There shall be no sharp pressed mark, cut, tear, or delaminated adhesive layer. These defects shall not damage the bending property of the repeatedly flexing part.

Figure 26 – Scratch on base film

| Level   | Scratch on base film |

|---------|----------------------|

| 1 and 2 | $d \leq 1/3 t$       |

| 3       | $d \leq 1/5 t$       |

#### Table 23 – Allowable scratches on base film

#### 7.5.6.6 Visual inspection of coverlay and covercoat

a) Dent on coverlay and covercoat: Dents on coverlay and covercoat, as illustrated in Figure 25, shall meet the requirement given in Table 24.

| Level   | Depth of a dent, d                                                                                                                                                                                                           |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 and 2 | Depth $(d)$ of a dent from the surface shall be no greater than 0,1 mm. When depth is difficult to measure, the height $(h)$ of the back protrusion of the base film shall be regarded as equal to the depth $(d)$ of a dent |

| 3       | There shall be no dent visible from both sides                                                                                                                                                                               |

b) Scratch on coverlay and covercoat: The depth (*d*) of a scratch on the coverlay and covercoat relative to the thickness (*t*) of coverlay or covercoat, as illustrated in Figure 26, shall meet the requirement given in Table 25. There shall be no sharp pressed mark, cut, tear, or delaminated adhesive layer on the surface of coverlay or covercoat. These defects shall not damage the bending property of the repeatedly flexing portion.

#### Table 25 – Requirement for scratch on coverlay and covercoat

| Level | Depth of a scratch, <i>d</i>             |  |

|-------|------------------------------------------|--|

| 1     | There shall be no exposure of conductor. |  |

| 2     | Depth (d) $\leq 1/3 t$                   |  |

| 3     | Depth (d) $\leq 1/5 t$                   |  |

NOTE The thickness of the covercoat should be calculated by subtracting the thickness of the FPC without covercoat from the total FPC thickness.

#### 7.5.6.7 Marking

Marking shall be legible.

#### 8 Dimensional Inspections

#### 8.1 Measurement of dimension

Measuring methods for dimensions of the flexible printed board shall be in accordance with JIS C 5016, Clauses 3, 4 and 5 and 6.3.

#### 8.2 External dimension

Measurement of external dimensions of the FPC shall meet the requirement given in Table 26.

| Level   | Tolerance of external dimension                             |           |

|---------|-------------------------------------------------------------|-----------|

| 1 and 2 | Tolerance of the external dimension of product:             |           |

|         | - for product size smaller than 100 mm in length:           | ±0,30 mm; |

|         | <ul> <li>– for product size of 100 mm or larger:</li> </ul> | ±0,3 %    |

| 3       | Requirement shall be agreed upon between user and supplier  |           |

#### Table 26 – Tolerance of external dimension

- 24 -

#### 8.3 Thickness

Thickness shall meet the requirements given in Table 27.

#### Table 27 – Thickness tolerance

| Level   | Thickness tolerance                                |  |

|---------|----------------------------------------------------|--|

| 1 and 2 | $\leq$ ±20 % of the total thickness of the product |  |

| 3       | To be agreed upon between user and supplier        |  |

#### 8.4 Hole diameter

Hole diameter shall meet the requirement given in Table 28.

#### Table 28 – Hole diameter and tolerance

Unit: mm

| Thickness, t         | Tolerance |

|----------------------|-----------|

| $0,8 \leq t$         | ±0,20     |

| 0,2 < <i>t</i> < 0,8 | ±0,10     |

| <i>t</i> ≦ 0,2       | ±0,05     |

#### 8.5 Conductor width

Tolerances of the width of the finished conductor for designed conductor width shall meet the requirement given in Table 29.

#### Table 29 – Conductor width and tolerance

```

Unit: µm

```

| Designed conductor width, w | Tolerance                                                      |

|-----------------------------|----------------------------------------------------------------|

| w < 50                      | The requirement shall be agreed upon between user and supplier |

| 50 ≦ <i>w</i> < 100         | ± 25                                                           |

| 100 ≦ <i>w</i> < 200        | ± 50                                                           |

| 200 ≦ <i>w</i>              | ± 100                                                          |

### 8.6 Cumulative pattern pitch

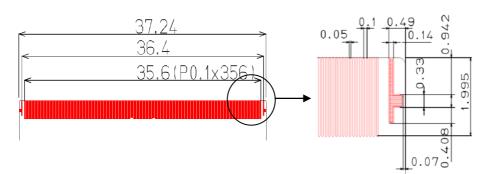

Table 30 gives the cumulative pitch as illustrated in the illustration.

|         | Conductor pitch, P   | Tolerance of the cumulative conductor pitch |

|---------|----------------------|---------------------------------------------|

|         | μm                   | %                                           |

| Level 1 | $300 \leq P$         | ± 0,3 %                                     |

| Level 2 | 150 ≦ <i>P</i> < 300 | ± 0,2 %                                     |

| Level 3 | 100 ≦ <i>P</i> < 150 | ± 0,15 %                                    |

| Level X | <i>P</i> < 100       | To be agreed upon between user and supplier |

| Table 30 – Cumulative | pattern | pitch | and | tolerance |

|-----------------------|---------|-------|-----|-----------|

|-----------------------|---------|-------|-----|-----------|

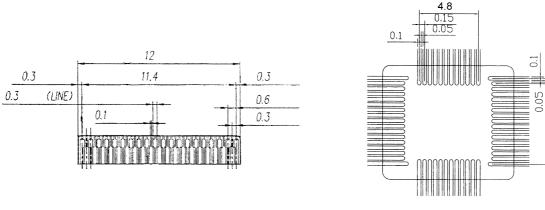

NOTE The length of each component is as follows. Connector: 11,4 mm, IC: 4,8 mm/side, and liquid crystal display: 35,6 mm.

Figure b – Connector terminals

Figure c – COF terminals

0.15

4.8

Figure 27 – Cumulative pitch

## 8.7 Distance between hole centres

The distance between hole centres shall meet the requirements given in Table 31.

| Level   | Tolerance of distance between hole centers                                     |

|---------|--------------------------------------------------------------------------------|

| 1 and 2 | For distance < 100 mm: ±0,30                                                   |

|         | 100 mm $\leq$ for distances: $\leq$ 0,3 % of the distance between hole centres |

| 3       | The requirements shall be agreed upon between user and supplier                |

| Table 31 – Tolerance of | distance between hole centres |

|-------------------------|-------------------------------|

## 8.8 Design minimum distance between board edge and conductor

Design minimum distance between a board edge and a conductor shall meet the requirement given in Table 32.

- 26 -

| Level   | Minimum distance between board edge and conductor                                            |

|---------|----------------------------------------------------------------------------------------------|

| 1 and 2 | Design minimum distance between the board edge and the conductor shall not be $\leqq$ 0,5 mm |

| 3       | The requirements shall be agreed upon between user and supplier                              |

Table 32 – Design minimum distance between board edge and conductor

#### 8.9 **Position accuracy**

#### 8.9.1 Position accuracy of holes

Position tolerance of a finished hole to the design position data shall be no larger than  $\pm 0.3$  mm for an external dimension of less than 100 mm, and shall be no larger than  $\pm 0.3$  % for an external dimension of over 100 mm, but except via holes.

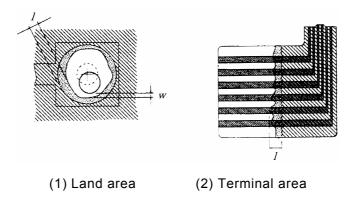

#### 8.9.2 Registration of hole to land

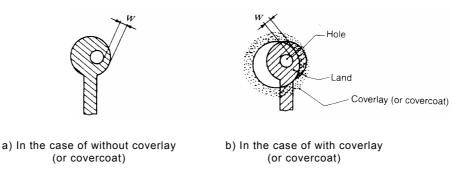

The minimum registration accuracy of a solderable finished land width (w), as illustrated in Figure 28, shall comply with the requirement given in Table 10.

#### Figure 28 – Misregistration of hole and land

#### 8.9.3 Registration of coverlay (or covercoat) to a land

The effective land area (*S*), as illustrated in Figure 29, shall comply with the requirement given in Table 10.

Figure 29 – Misregistration of land and coverlay (or covercoat)

| Level   | Effective land area, S                      |

|---------|---------------------------------------------|

| 1 and 2 | Larger than 50 % of the designed land area  |

| 3       | To be agreed upon between user and supplier |

## Table 33 – Effective land area

#### 8.9.4 Registration accuracy of stiffener to FPC

#### 8.9.4.1 Hole registration

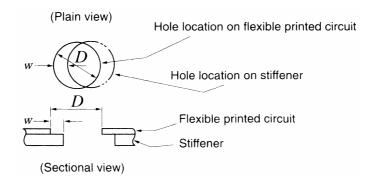

The deviation (w) between holes of the stiffener and the flexible printed circuit, as illustrated in Figure 30, shall be such that the difference (D-w) between the hole diameter (D) and the displacement (w) shall meet the tolerance requirement for the hole diameter (D).

Figure 30 – Registration of holes

#### 8.9.4.2 Displacement of the outer dimensions

The displacement (l) between outer dimensions shall meet the requirements given in Table 34, as illustrated in Figure 31.

Figure 31 – The displacement of the outer dimensions

#### Table 34 – Allowable displacement between outlines of the stiffener and the FPC

Unit: mm

| Level | Tolerance |  |

|-------|-----------|--|

| 1     | /≦ ±0,5   |  |

| 2     | /≦ ±0,3   |  |

| 3     | /≦ ±0,2   |  |

## 8.9.5 Registration of punched outline to conductor pattern

The registration of punched outline to conductor pattern shall meet the requirement given in Table 35.

- 28 -

| Level   | Requirement for registration                                                                                                                                                               |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 and 2 | The edges of the outline of the board shall not be in contact with conductors, except for plating lead(s), isolated land(s), and conductor(s) for mechanical reinforcement                 |

| 3       | The clearance between the outline edge and the conductor shall<br>be no smaller than 0,1 mm, except for plating lead(s), isolated<br>land(s) and conductor(s) for mechanical reinforcement |

Table 35 – Registration of punched outline to conductor patterns

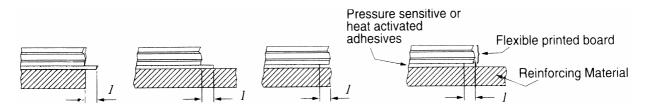

## 8.10 Registration of pressure sensitive or heat activated adhesive (including adhesive squeeze-out) to flexible printed board and stiffener

The displacement (*l*) of pressure-sensitive or heat-activated adhesives from the FPC and stiffener (including adhesive squeeze-out), as illustrated in Figure 32, shall be  $\pm$  0,5 mm. The registration of the adhesive at component holes shall meet the requirement for the tolerance of the hole diameter.

Figure 32 – Registration of pressure-sensitive or heat-activated adhesive from flexible printed board and stiffener (Including adhesive squeeze-out)

## 8.10.1 Plating thickness of copper plated-through holes

The thickness of the plated copper of the plated-through holes shall be 0,004 mm min.

## 9 Electrical performance test

The electrical performance of the FPC shall be tested in accordance with JIS C 5016. The test items and requirements are given in Table 36.

| Item No. | Item                                              |                   | Requirement                                                | Test method (JIS C 5016)                                   |

|----------|---------------------------------------------------|-------------------|------------------------------------------------------------|------------------------------------------------------------|

| 9.1      | Conductor resistance                              |                   | Shall be agreed upon between user<br>and supplier          | 7.1 (Conductor resistance)                                 |

| 9.2      | Insulation<br>resistance<br>of surface<br>layers  | As<br>received    | $5 \times 10^8 \Omega \leq$                                | According to 7.6 (Insulation resistance of surface layers) |

|          |                                                   | After<br>humidity | Level 1: shall retain the electrical functions.            | 9.4 (Temperature and humidity cycling test) and            |

|          |                                                   | test              | Level 2: 1 x $10^8 \Omega \leq$                            | according to 7.6                                           |

|          |                                                   |                   | Level 3: $5 \times 10^8 \Omega \leq$                       |                                                            |

| 9.3      | Dielectric withstanding voltage of surface layers |                   | There shall be no flashover when 500 V<br>a.c. is applied. | 7.5 (Dielectric withstanding voltage, surface layers)      |

| 9.4      | Open circuit of the conductor                     |                   | 1 kΩ*                                                      | 7.7.2 (Circuit continuity test)                            |

| 9.5      | Short circuit between conductors                  |                   | ≦ 100 kΩ*                                                  | 7.7.1 (Circuit isolation test)                             |

|          | iteria values<br>arily be these                   | •                 | rcuit and short circuit for judging the                    | product performance may no                                 |

## Table 36 – Electrical properties of flexible printed boards

## **10** Mechanical performance test

The mechanical performance of FPCs shall be tested in accordance with JIS C 5016. The test items and specifications are given in Table 37.

- 30 -

| Item No. |                                                      | ltem      | Property requirements                                                                                                                                                         | Test method (JIS C 5016)                                                                                                         |

|----------|------------------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| 10.1     | Peel                                                 | Conductor | 0,49 N/mm ≦                                                                                                                                                                   | 8.1 (Peel strength)                                                                                                              |

|          | strength                                             | Coverlay  | 0,34 N/mm ≦                                                                                                                                                                   | Specimen with coverlay<br>bonded on the shiny side of<br>the copper foil shall be tested<br>in accordance with 8.1,<br>method B. |

|          |                                                      | Stiffener | Thermosetting adhesives:<br>0,34 N/mm<br>Pressure sensitive adhesives:<br>0,15 N/mm ≦                                                                                         | Specimen with stiffener<br>bonded on the base film shall<br>be tested in accordance with<br>8.1, method B.                       |

| 10.2     | Pull-out strength for<br>plain hole and<br>footprint |           | Level 1:Not specifiedLevels 2 and 3:1 N/mm² $\leq$                                                                                                                            | 8.2 (Pull-out strength for plain<br>holes) and 8.3 (Pull-out<br>strength for footprints)                                         |

| 10.3     | Plating adhesion                                     |           | There shall be no peel-off                                                                                                                                                    | 8.4 (Plating adhesion)                                                                                                           |