Edition 1.0 2010-09

# PUBLICLY AVAILABLE SPECIFICATION

## **PRE-STANDARD**

Copyrighted material licensed to BR Demo by Thomson Reuters (Scientific), Inc., subscriptions.techstreet.com, downloaded on Nov-28-2014 by James Madison. No further reproduction or distribution is permitted. Uncontrolled when print

Printed boards – Part 14: Device embedded substrate – Terminology / reliability / design guide

### THIS PUBLICATION IS COPYRIGHT PROTECTED

### Copyright © 2010 IEC, Geneva, Switzerland

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from either IEC or IEC's member National Committee in the country of the requester.

If you have any questions about IEC copyright or have an enquiry about obtaining additional rights to this publication, please contact the address below or your local IEC member National Committee for further information.

IEC Central Office 3, rue de Varembé CH-1211 Geneva 20 Switzerland Email: inmail@iec.ch Web: www.iec.ch

#### About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes International Standards for all electrical, electronic and related technologies.

#### About IEC publications

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the latest edition, a corrigenda or an amendment might have been published.

Catalogue of IEC publications: <u>www.iec.ch/searchpub</u>

The IEC on-line Catalogue enables you to search by a variety of criteria (reference number, text, technical committee,...). It also gives information on projects, withdrawn and replaced publications.

IEC Just Published: <u>www.iec.ch/online\_news/justpub</u>

Stay up to date on all new IEC publications. Just Published details twice a month all new publications released. Available on-line and also by email.

Electropedia: <u>www.electropedia.org</u>

The world's leading online dictionary of electronic and electrical terms containing more than 20 000 terms and definitions in English and French, with equivalent terms in additional languages. Also known as the International Electrotechnical Vocabulary online.

Customer Service Centre: <u>www.iec.ch/webstore/custserv</u> If you wish to give us your feedback on this publication or need further assistance, please visit the Customer Service Centre FAQ or contact us:

Email: csc@iec.ch Tel.: +41 22 919 02 11 Fax: +41 22 919 03 00

Edition 1.0 2010-09

# PUBLICLY AVAILABLE SPECIFICATION

## **PRE-STANDARD**

Printed boards – Part 14: Device embedded substrate – Terminology / reliability / design guide

INTERNATIONAL ELECTROTECHNICAL COMMISSION

ICS 31.180

ISBN 978-2-88912-180-9

### CONTENTS

- 2 -

| FO | REWC                           | DRD                           |                                                                                                                                                                | 6  |  |  |  |

|----|--------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|

| 1  | Scop                           | e                             |                                                                                                                                                                | 8  |  |  |  |

| 2  | Norm                           | ative re                      | ferences                                                                                                                                                       | 8  |  |  |  |

| 3  | Gene                           | eral definitions              |                                                                                                                                                                |    |  |  |  |

|    | 3.1                            | Techno                        | blogy of the device embedded substrate                                                                                                                         | 9  |  |  |  |

|    | 3.2                            |                               | ate                                                                                                                                                            |    |  |  |  |

|    | 3.3                            |                               | nounting and interconnection                                                                                                                                   |    |  |  |  |

|    | 3.4                            |                               | ire and terminology                                                                                                                                            |    |  |  |  |

|    |                                | 3.4.1                         | General                                                                                                                                                        | 15 |  |  |  |

|    |                                | 3.4.2                         | Device embedding by conventional process                                                                                                                       | 17 |  |  |  |

|    |                                | 3.4.3                         | Electrical connection by vias after device embedding                                                                                                           | 19 |  |  |  |

|    |                                | 3.4.4                         | Embedding of various devices over multiple layers                                                                                                              | 20 |  |  |  |

| 4  | Test                           | method                        | S                                                                                                                                                              | 22 |  |  |  |

|    | 4.1                            | Genera                        | al                                                                                                                                                             | 22 |  |  |  |

|    | 4.2                            | Structu                       | re of TEG (Test Equipment Group – Test vehicle)                                                                                                                | 22 |  |  |  |

|    | 4.3 Test circuit               |                               | rcuit                                                                                                                                                          | 24 |  |  |  |

|    | 4.4                            | Test sp                       | pecimen (TEG) and example of test substrate                                                                                                                    | 26 |  |  |  |

| 5  | Test                           | Test items and test equipment |                                                                                                                                                                |    |  |  |  |

|    | 5.1                            | 5.1 General                   |                                                                                                                                                                |    |  |  |  |

|    | 5.2                            | Test fo                       | r resistance of conductor                                                                                                                                      | 28 |  |  |  |

|    | 5.3 Resistance to over current |                               | ance to over current                                                                                                                                           | 29 |  |  |  |

|    | 5.4                            | Withsta                       | and voltage                                                                                                                                                    | 30 |  |  |  |

|    | 5.5                            | Insulat                       | ion resistance                                                                                                                                                 | 30 |  |  |  |

|    | 5.6                            | Peeling                       | g strength of conductor                                                                                                                                        | 32 |  |  |  |

|    | 5.7                            |                               | f strength of plated through hole                                                                                                                              |    |  |  |  |

|    | 5.8                            |                               | vity of plated film                                                                                                                                            |    |  |  |  |

|    | 5.9                            |                               | ability                                                                                                                                                        |    |  |  |  |

|    | 5.10                           |                               | al shock (vapour phase cold heat cycle)                                                                                                                        |    |  |  |  |

|    | 5.11                           |                               | al shock (high temperature)                                                                                                                                    |    |  |  |  |

|    |                                |                               | ability                                                                                                                                                        |    |  |  |  |

|    |                                |                               | nd twist                                                                                                                                                       |    |  |  |  |

| ~  |                                | -                             | on                                                                                                                                                             |    |  |  |  |

| 6  |                                |                               | ackaging and storage                                                                                                                                           |    |  |  |  |

| 7  | Desig                          |                               |                                                                                                                                                                |    |  |  |  |

|    | 7.1                            |                               | al                                                                                                                                                             |    |  |  |  |

|    | 7.2                            |                               | re of device embedded substrate                                                                                                                                |    |  |  |  |

|    |                                | 7.2.1                         | General                                                                                                                                                        | 38 |  |  |  |

|    |                                | 7.2.2                         | Specification of the front and back surfaces of a device embedded substrate                                                                                    | 38 |  |  |  |

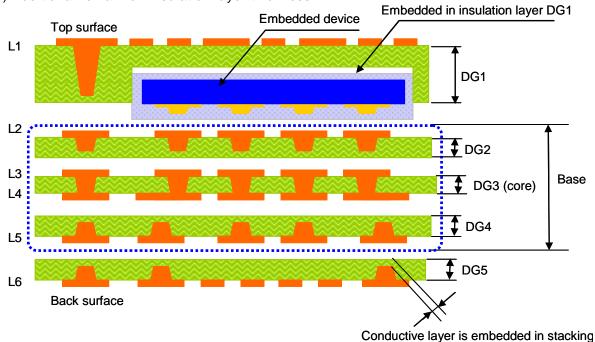

|    |                                | 7.2.3                         | Definition of layers of a device embedded substrate                                                                                                            | 40 |  |  |  |

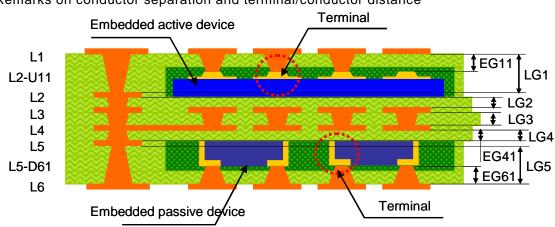

|    |                                | 7.2.4                         | Definitions of insulation layer thickness, conductor spacing and distance between electrode and conductor spacing (hereafter called "electrode") at a terminal | лл |  |  |  |

|    | 7.3                            | Condit                        | ions for base                                                                                                                                                  |    |  |  |  |

|    | 7.3<br>7.4                     |                               | ions for embedding devices                                                                                                                                     |    |  |  |  |

|    |                                | Conun                         |                                                                                                                                                                |    |  |  |  |

### PAS 62326-14 © IEC:2010(E)

| 7 5                     | Denvi               |                |                                                                                                                                                | <b>F</b> 4 |

|-------------------------|---------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 7.5<br>7.6              |                     |                | for embedding devices<br>fication of device embedded substrate                                                                                 |            |

| 7.0                     | 7.6.1               | •              | ral                                                                                                                                            |            |

|                         | -                   |                | to be included in the design specification                                                                                                     |            |

|                         |                     |                | Specimen for surface resistance measurement of electronic                                                                                      | 57         |

|                         |                     |                | Insulation resistance measurement of inner layer of electronic                                                                                 | 58         |

|                         |                     |                | Specimen for interlayer insulation resistance measurement t board                                                                              | 59         |

| Annex D                 | (informa            | ative)         | Electronic wiring board product system                                                                                                         | 60         |

|                         |                     |                | Steps of electronic circuit board assembly and main                                                                                            |            |

|                         |                     |                |                                                                                                                                                |            |

| Bibliograp              | ohy                 |                |                                                                                                                                                | 62         |

|                         |                     |                |                                                                                                                                                |            |

| -                       | -                   |                | device embedded substrate                                                                                                                      |            |

| -                       |                     |                | levice embedded substrate (pad connection)                                                                                                     |            |

|                         |                     |                | levice embedded substrate (via connection)                                                                                                     | 9          |

| embedde                 | d substr            | rate as        | a device embedded substrate using a passive device<br>a base and then a active and/or a passive device is mounted<br>sin (Pad connection type) | 10         |

| Figure 5 -<br>base (via | - Structi<br>connec | ure of tion ty | a device embedded substrate using a ceramic board as the pe)                                                                                   | 10         |

| Figure 6 -              | - Entire            | struct         | ure of device embedded substrate                                                                                                               | 15         |

| Figure 7 -              | - Base (            | typica         | l structure)                                                                                                                                   | 15         |

| Figure 8 -              | - Base (            | Cavity         | v structure)                                                                                                                                   | 15         |

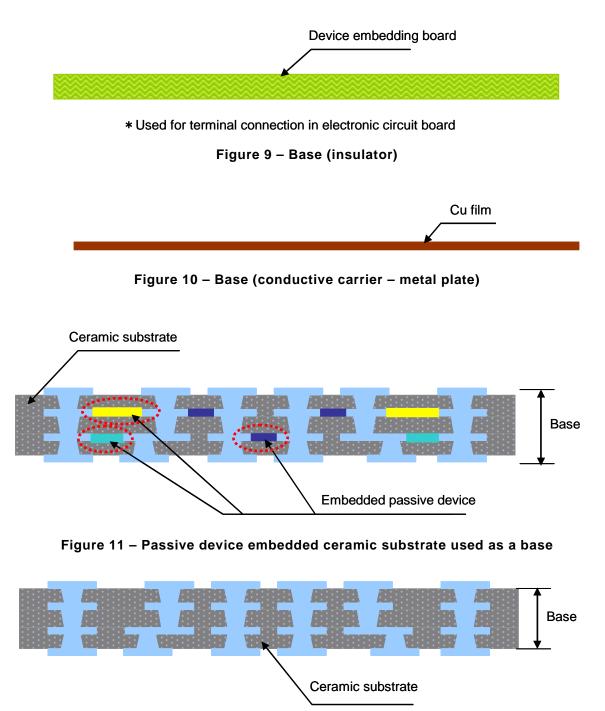

| Figure 9 -              | - Base (            | (insula        | tor)                                                                                                                                           | 16         |

| Figure 10               | – Base              | (cond          | uctive carrier – metal plate)                                                                                                                  | 16         |

|                         |                     |                | vice embedded ceramic substrate used as a base                                                                                                 |            |

| Figure 12               | – Cera              | mic bo         | ard used as base                                                                                                                               | 16         |

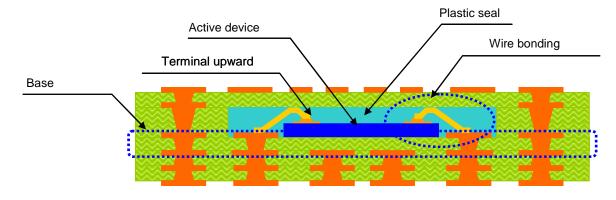

| Figure 13               | a – Wire            | e bond         | ling connection and embedding of active device bear chip                                                                                       | 17         |

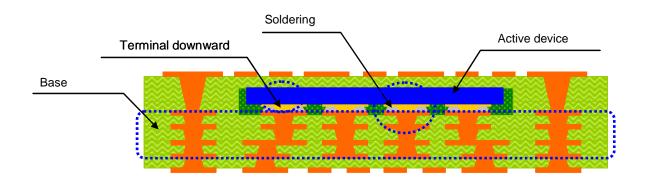

| Figure 13               | b – Solo            | dering         | connection and embedding of active device                                                                                                      | 17         |

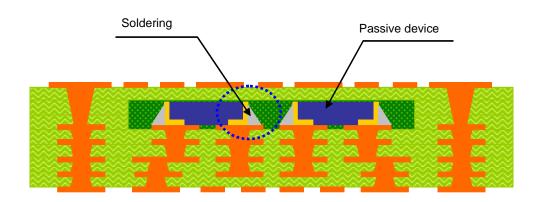

| Figure 13               | c – Solo            | dering         | connection of square type passive device                                                                                                       | 17         |

| Figure 13               | d – Con             | nductiv        | e resin connection and embedding of active device                                                                                              | 18         |

| •                       |                     |                | e resin connection and embedding of square type passive                                                                                        | 18         |

| Figure 13               | f – Sold            | ering          | connection into through hole and embedding of passive device                                                                                   | 18         |

| Figure 13               | – Embe              | edding         | of device by conventional methods                                                                                                              | 18         |

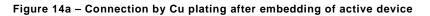

| Figure 14               | a – Con             | nectio         | n by Cu plating after embedding of active device                                                                                               | 19         |

| Figure 14               | b – Con             | nectio         | n by Cu plating after embedding of square type passive device                                                                                  | 19         |

| Figure 14               | c – Con             | ductiv         | e paste connection after embedding of active device package                                                                                    | 19         |

| Figure 14               | d – Con             | nductiv        | e paste connection after embedding of square type passive                                                                                      |            |

|                         | -                   |                | tion after embedding                                                                                                                           |            |

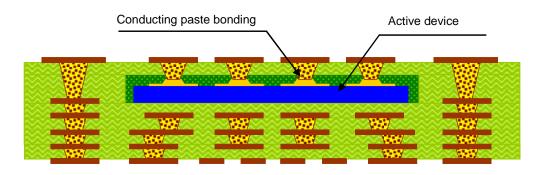

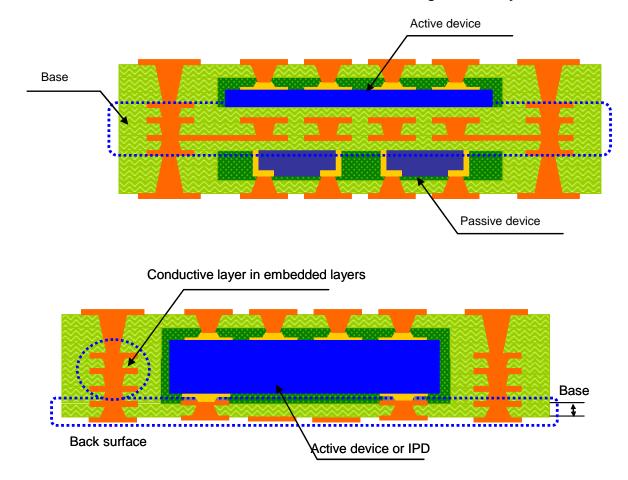

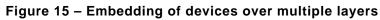

| -                       |                     |                | of devices over multiple layers                                                                                                                |            |

|                         |                     |                | substrate                                                                                                                                      |            |

| Figure 17 – Conductor and metal sheet/copper foil as the base substrate                                                         | 21 |

|---------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 18 – Device embedded substrate using passive device embedded ceramic substrates as the base                              | 21 |

| Figure 19 – Device embedded substrate using passive device embedded ceramic substrates as the base – second type                | 22 |

| Figure 20 – Schematic diagram of test circuit                                                                                   | 23 |

| Figure 21 – Multilayer wiring patterns                                                                                          | 24 |

| Figure 22 – Conceptual structure of test circuit, comb-type capacitor, detection pattern of impedance, insulation and migration | 25 |

| Figure 23 – Example of TEG                                                                                                      | 26 |

| Figure 24 – Example of test circuit for connection evaluation                                                                   | 26 |

| Figure 25 – Example of test circuit for insulation evaluation                                                                   | 27 |

| Figure 26 – Resistance per unit length of conductor pattern in relation with conductor width                                    | 28 |

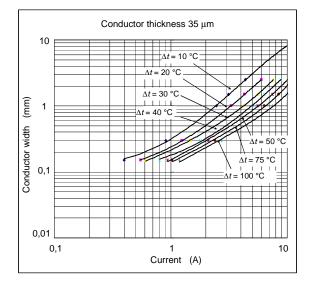

| Figure 27 – The relation of conductor width, conductor thickness and temperature rise with current                              | 29 |

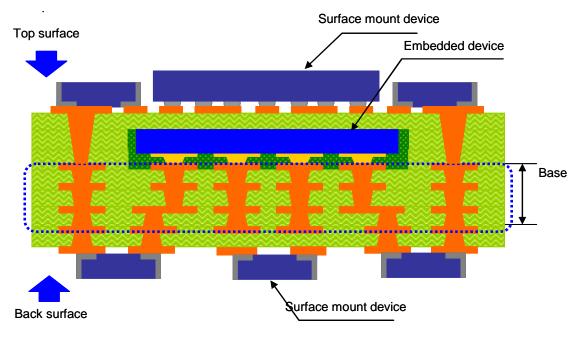

| Figure 28 – Definition of front and back surfaces of a device embedded substrate                                                | 39 |

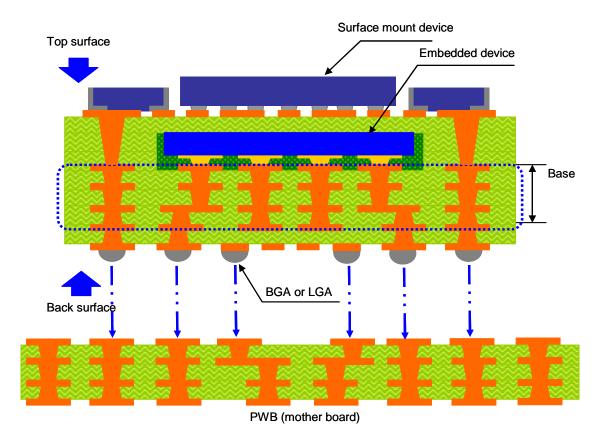

| Figure 29 – Definition of front and back surfaces of a device embedded substrate – substrate mounted on a mother board          | 39 |

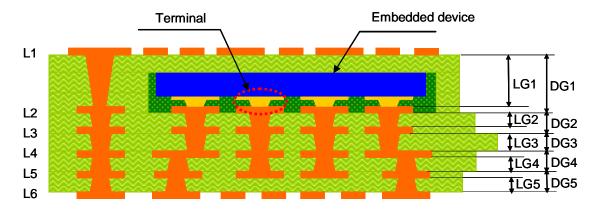

| Figure 30 – Definition of layers of a pad-connection substrate                                                                  | 40 |

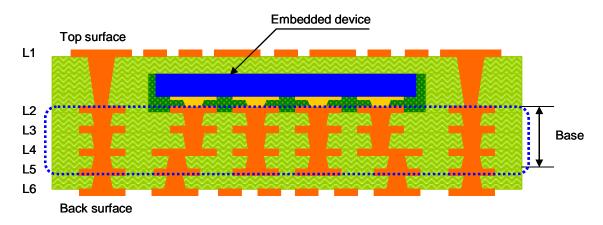

| Figure 31 – Illustration of virtual layers                                                                                      | 41 |

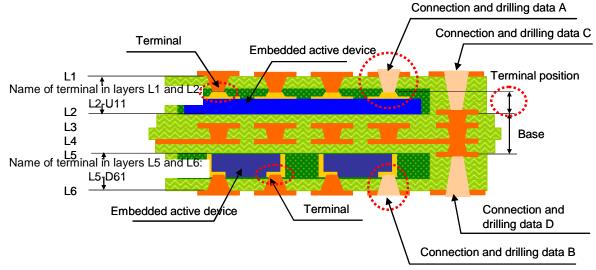

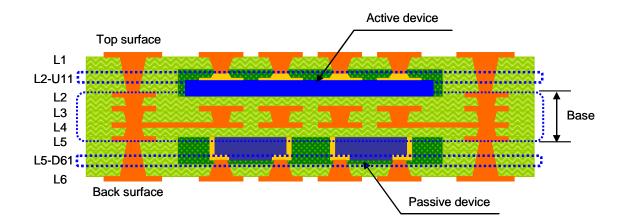

| Figure 32 – Layer names in the via interconnection (I)                                                                          | 41 |

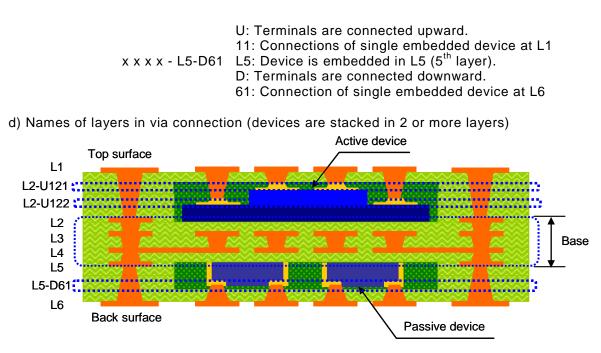

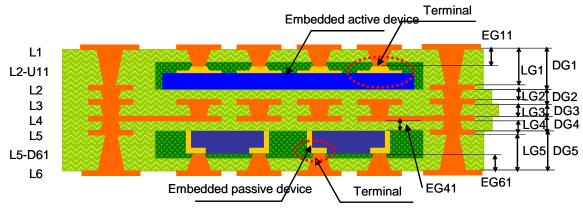

| Figure 33 – Layer names in the via interconnection (II)                                                                         | 42 |

| Figure 34 – Layer names in via connection (III)                                                                                 | 42 |

| Figure 35 – Definitions of dielectric gap and layer gap in the pad connection method                                            | 44 |

| Figure 36 – Definitions of dielectric gap and layer gap in the via connection method                                            | 45 |

| Figure 37 – Additional illustration of dielectric gap                                                                           | 45 |

| Figure 38 – Additional illustration of layer gap                                                                                | 46 |

| Figure 39 – Additional drawing                                                                                                  | 52 |

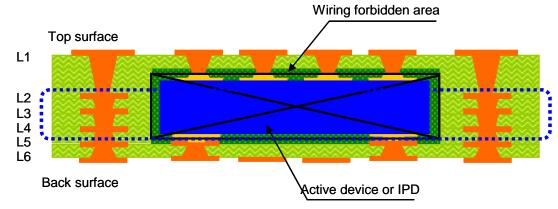

| Figure 40 – Forbidden wiring area                                                                                               | 53 |

| Figure A.1 – Test pattern for surface insulation resistance measurement                                                         | 57 |

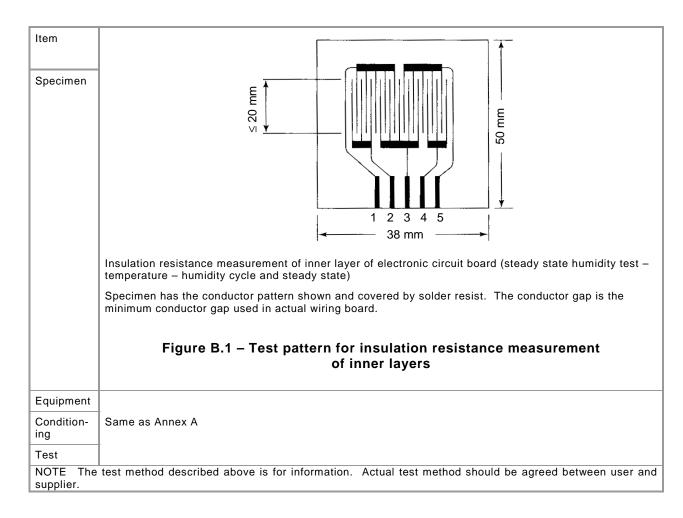

| Figure B.1 – Test pattern for insulation resistance measurement of inner layers                                                 | 58 |

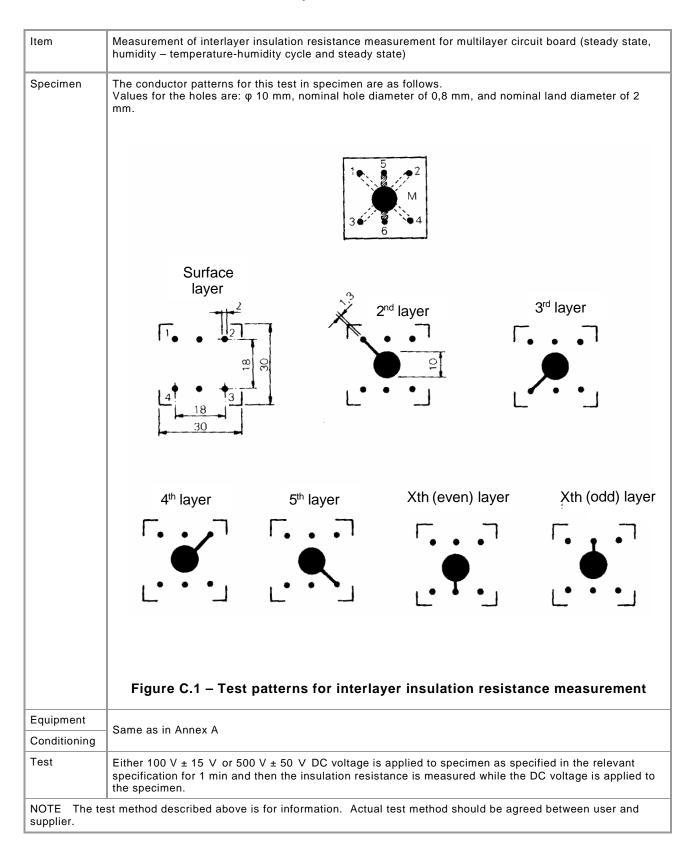

| Figure C.1 – Test patterns for interlayer insulation resistance measurement                                                     | 59 |

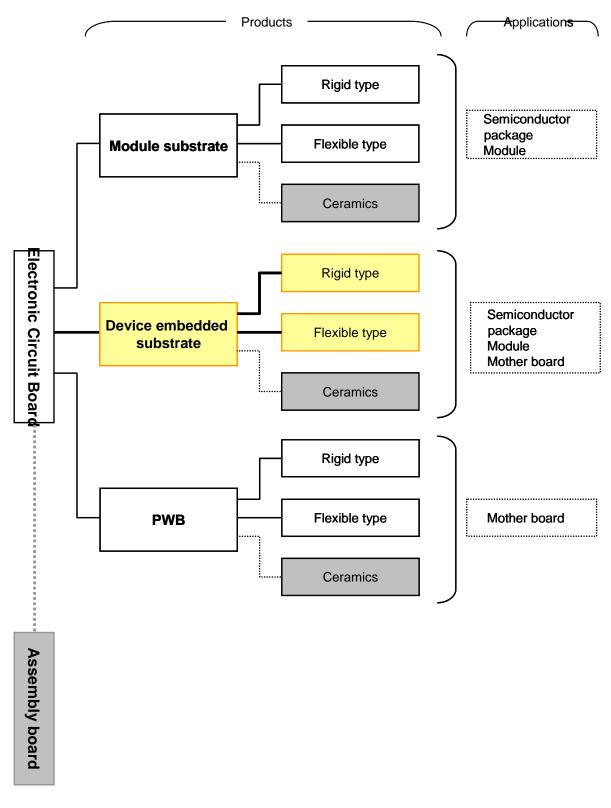

| Figure D.1 – Electronic wiring board product system                                                                             | 60 |

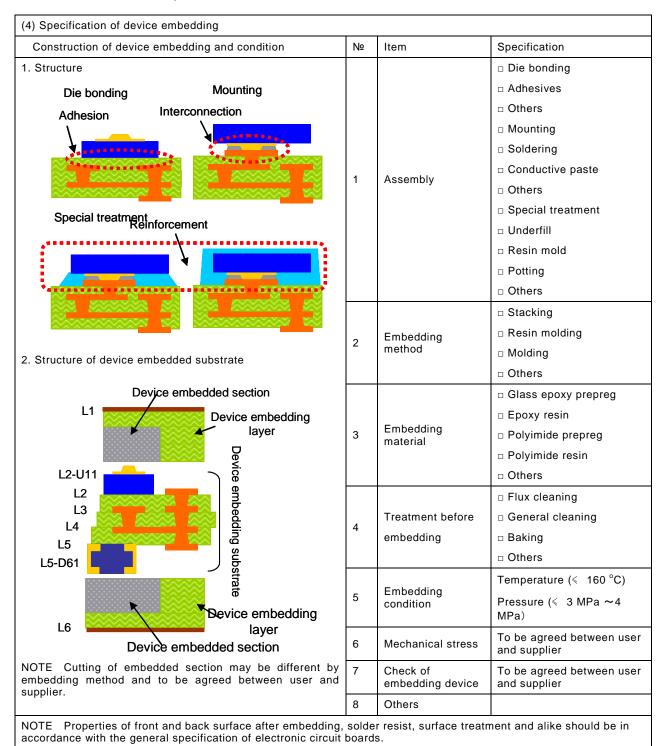

| Table 1 – Classification of device embedding                                                                                    |    |

| Table 1 – Classification of device embedding (continued)                                                                        |    |

| Table 2 – Embedded device structure and fabrication process                                                                     | 13 |

| Table 3 – Jisso mounting and interconnection of the device embedded substrate                                                   | 14 |

| Table 4 – Conduction test                                                                                                       |    |

| Table 5 – Resistance to over current and its test method                                                                        | 29 |

| Table 6 – Withstand voltage and test method                                                                                     |    |

| Table 7 – Test methods of insulation resistance                                                                                 |    |

| Table 8 – Peeling strength of conductor and test method                                                                         |    |

| Table 9 – Pull-off strength of plated through hole and test method                                                              | 32 |

- 4 -

| Table 10 – Adhesivity of plated film and test method                                   | 32 |

|----------------------------------------------------------------------------------------|----|

| Table 11 – Solderability and test method                                               | 33 |

| Table 12 – Characteristics and test method for thermal shock                           | 34 |

| Table 13 – Specification and test method for thermal shock                             | 35 |

| Table 14 – Flammability specification and test method                                  | 36 |

| Table 15 – Specification and test method for bow and twist                             | 36 |

| Table 16 – Specification and test method for migration                                 | 37 |

| Table 17 – Layer names of device embedding substrate                                   | 43 |

| Table 18 – Requirements to device assembly to base substrate of device embedded boards | 47 |

| Table 19 – Embedding requirement                                                       | 48 |

| Table 20 – Mounting methods of semiconductor devices                                   | 49 |

| Table 21 – Mounting method of devices                                                  | 50 |

| Table 22 – Embedding device                                                            | 51 |

| Table 23 – Specification of device embedded substrate                                  | 54 |

| Table 23 – Specification of device embedded substrate (continued)                      | 55 |

| Table 23 – Specification of device embedded substrate (continued )                     | 56 |

| Table E.1 – Steps of electronic circuit board assembly and main applications           | 61 |

### INTERNATIONAL ELECTROTECHNICAL COMMISSION

### PRINTED BOARDS – Part 14: Device embedded substrate – Terminology / reliability / design guide

### FOREWORD

- 1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as "IEC Publication(s)"). Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely with the International Organization for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC National Committees.

- 3) IEC Publications have the form of recommendations for international use and are accepted by IEC National Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

- 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter.

- 5) IEC itself does not provide any attestation of conformity. Independent certification bodies provide conformity assessment services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any services carried out by independent certification bodies.

- 6) All users should ensure that they have the latest edition of this publication.

- 7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and members of its technical committees and IEC National Committees for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC Publications.

- 8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.

- Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

A PAS is a technical specification not fulfilling the requirements for a standard, but made available to the public.

IEC-PAS 62326-14 was submitted by the JPCA (Japan Electronics Packaging and Circuits Association) and has been processed by IEC technical committee 91: Electronics assembly technology.

It is based on JPCA-EB01 (2009) 2<sup>nd</sup> edition. It is published as a double-logo PAS and JPCA.

| The text of this PAS is based on the following document: | This PAS was approved for<br>publication by the P-members of the<br>committee concerned as indicated in<br>the following document |

|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Draft PAS                                                | Report on voting                                                                                                                  |

| 91/893/PAS                                               | 91/910/RVD                                                                                                                        |

Following publication of this PAS, which is a pre-standard publication, the technical committee or subcommittee concerned may transform it into an International Standard.

PAS 62326-14 © IEC:2010(E)

This PAS shall remain valid for an initial maximum period of 3 years starting from the publication date. The validity may be extended for a single period up to a maximum of 3 years, at the end of which it shall be published as another type of normative document, or shall be withdrawn.

A list of all the parts in the IEC 62326 series, under the general title *Printed boards*, can be found on the IEC website.

IMPORTANT – The 'colour inside' logo on the cover page of this publication indicates that it contains colours which are considered to be useful for the correct understanding of its contents. Users should therefore print this document using a colour printer.

### PRINTED BOARDS – Part 14: Device embedded substrate – Terminology / reliability / design guide

### 1 Scope

This PAS is applicable to device embedded substrates fabricated by embedding discrete active and passive electronic devices into an inner layer of a substrate with electric connections by vias, conductor plating, conductive paste, and printing. The device embedded substrate may be used as a substrate to mount SMDs to form electronic circuits, as conductor and insulator layers may be formed after embedding electronic devices.

The purpose of this PAS is to obtain common understanding in design, fabrication and use of device embedded substrates in the industry.

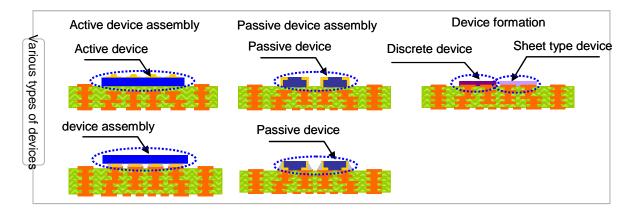

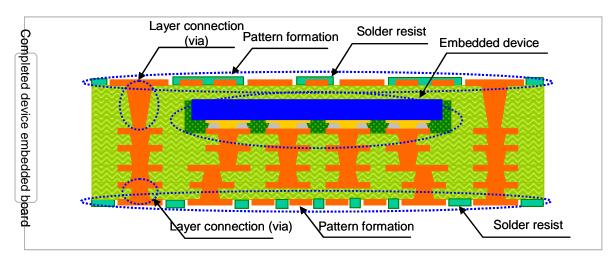

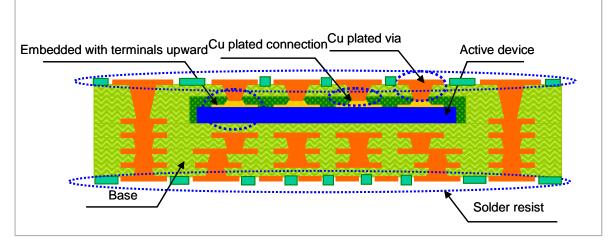

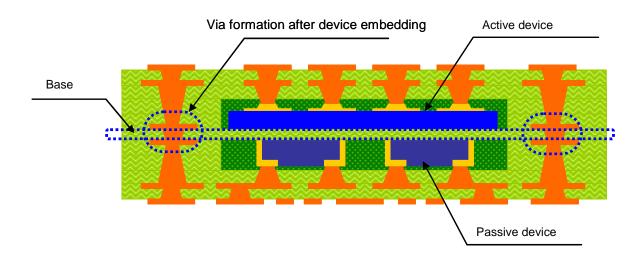

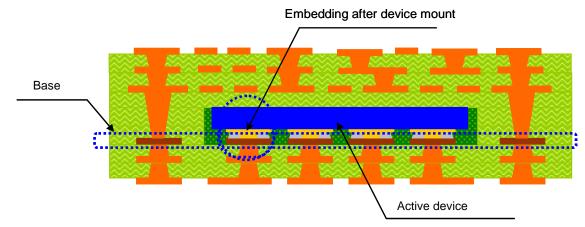

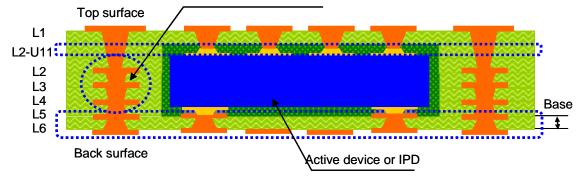

This PAS describes the substrate embedding devices including but not limited to module, integrated passive device (IPD), microelectrochemical systems (MEMS), discrete component formed in the fabrication process of the electronic wiring board, and sheet form component. Figure 1 shows examples of device embedding in the fabrication process of the device embedded substrate. Active and passive devices are connected to each other by interlayer vias and/or conductor patterns. Insulating layers are formed using insulating materials with vias for the connection of inside conductor patterns to the conductor patterns formed on the surface(s) of the substrate. Figure 2 shows the substrate with connections using pads, and Figure 3 shows the board using via connections.

The insulating layer includes rigid and flexible insulating resins such as phenol resin, epoxy resin, polyimide resin and modified polyimide resin, which are reinforced with glass cloth, aramid cloth or paper; and resins without reinforcement. Interconnections to the input and output terminals to the embedded device and the surface conductor pattern include conventional interconnection of the terminals of the embedded device to an interconnecting land for SMD, and formation of terminals on the surface of an embedded device by copper plating or vias using conductive paste.

This PAS does not specify the fabrication process of device embedded substrates, via diameter/via land diameter, conductor width/conductor spacing nor conductor line density.

### 2 Normative references

PAS 62326-14 © IEC:2010(E)

### 3 General definitions

### 3.1 Technology of the device embedded substrate

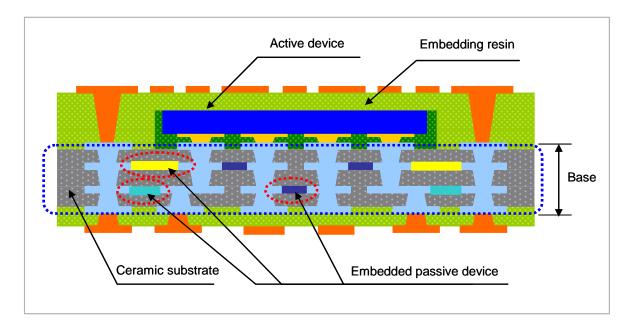

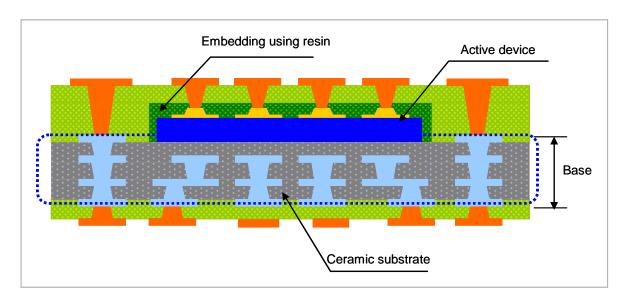

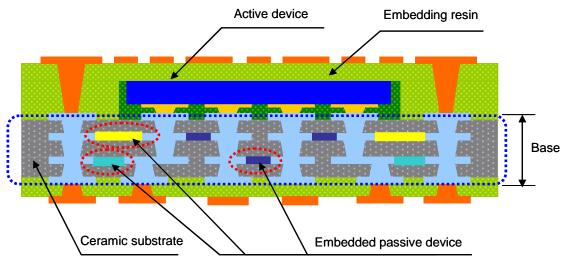

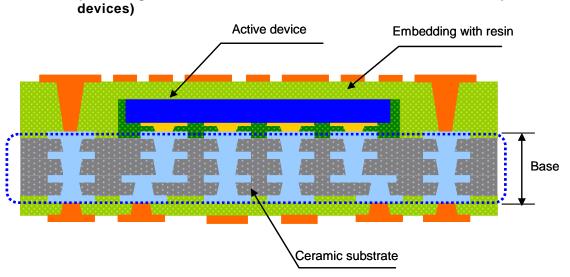

There are two types of device embedded substrates: one type consists in embedding an active and/or passive discrete device on a base substrate and covering it with organic resin and the other consists in forming a device on a substrate and then covering it with organic resin. The device embedded substrate also includes composite type substrates which consist of mass produced inorganic ceramic including LTCC (low temperature co-fired ceramics) substrates (hereafter they are called just ceramics) on which passive devices are embedded as shown in Figure 4, and the other type as shown in Figure 5 where the ceramic substrate is used as a base on which active and passive devices are mounted and the entire body is covered by organic resin; details of inorganic ceramics are not specified in this document. Such a ceramic is treated just handled as a base of a device embedded module.

Classification of device embedding is given in Table 1. Active devices include bare die, wafer-level package (WLP), BGA, LGA, and QFN. Passive devices include chip component, complex chip component like an array and integrated passive device (IPD). Module and MEMS are embedded onto the substrate after packaging and moulding into module and MEMS. The component formed during substrate formation is not covered in this document but also included in Table 1. There are two types of formed passive component embedding, one is to form passive components using thick film or thick film technology on the base of a silicon or compound semiconductor and/or on the stacked chip at the wafer level or on package-on-package (PoP), and the other is to use a sheet-type passive device on an organic substrate first and then to embed the other devices.

Figure 2 – Completed device embedded substrate (pad connection)

Figure 3 – Completed device embedded substrate (via connection)

- 10 -

Figure 4 – Structure of a device embedded substrate using a passive device embedded substrate as a base and then a active and/or a passive device is mounted and then covered by resin (Pad connection type)

Figure 5 – Structure of a device embedded substrate using a ceramic board as the base (via connection type)

| _ | 1 | 1 | _ |

|---|---|---|---|

|---|---|---|---|

| Classification    | ltem                     | Embedding            | Device<br>terminals                  | Bonding                            | Schematics |

|-------------------|--------------------------|----------------------|--------------------------------------|------------------------------------|------------|

|                   |                          | Die bonding          | Peripheral                           | Wire bonding                       |            |

|                   | Bare die                 | Flip chip<br>bonding | Peripheral area<br>array             | Flip chip<br>bonding               |            |

|                   |                          | Die bonding          | Peripheral area<br>array             | Via connection<br>(plating, paste) |            |

| Active device     | Wafer level              | Mounting             | Peripheral area<br>array             | Soldering<br>conductive<br>paste   |            |

|                   | package                  | Die bonding          | Peripheral area<br>array             | Via connection<br>(plating, paste) |            |

|                   | Package                  | Mounting             | BGA, LGA,<br>QFN                     | Soldering<br>conductive<br>paste   |            |

|                   |                          | Mounting             | BGA, LGA,<br>QFN                     | Via connection<br>(plating, paste) |            |

|                   | Chip component           | Mounting             | Rectangular<br>chip<br>Rod type chip | Through hole                       |            |

|                   |                          | Mounting             | Rectangular<br>chip<br>Rod type chip | Soldering<br>conductive<br>paste   |            |

|                   |                          | Mounting             | Rectangular<br>chip                  | Via connection<br>(plating, paste) |            |

| Passive<br>device | Module chip<br>component | Mounting             | Rectangular<br>chip                  | Soldering<br>conductive<br>paste   |            |

|                   |                          | Mounting             | Rectangular<br>chip                  | Via connection<br>(plating, paste) |            |

|                   | Integrated passive       | Mounting             | IPD                                  | Soldering<br>conductive<br>paste   |            |

|                   | device                   | Mounting             | IPD                                  | Via connection<br>(plating, paste) |            |

| Module            | Packaging and            | Mounting             | Arbitrary                            | Soldering<br>conductive<br>paste   |            |

| Module            | moulding                 | Mounting             | Arbitrary                            | Via connection<br>(plating, paste) |            |

| MEMS              | Packaging and            | Mounting             | Arbitrary                            | Soldering<br>conductive<br>paste   |            |

|                   | moulding                 | Mounting             | Arbitrary                            | Via connection<br>(plating, paste) |            |

### Table 1 – Classification of device embedding

| Classification | ltem   | Embedding                     | Device<br>terminals       | Bonding                            | Schematics |

|----------------|--------|-------------------------------|---------------------------|------------------------------------|------------|

| Active device  | Formed | Thin film<br>Sputtering       | Silicon                   | Via connection<br>(plating, paste) |            |

|                |        | Thick film<br>Screen printing | Semiconducting polymer    | Via connection<br>(plating, paste) |            |

|                |        | Double through hole           | Copper plating            | Via connection<br>(plating, paste) |            |

|                | Formed | Etching                       | Laminate<br>material      | Via connection<br>(plating, paste) |            |

| Passive        |        | Etching                       | Film                      | Via connection<br>(plating, paste) |            |

| device         |        | Screen printing               | Polymer                   | Via connection<br>(plating, paste) |            |

|                |        | Transfer                      | Ferromagnetic<br>Ceramics | Via connection<br>(plating, paste) |            |

|                |        | Lamination                    | Seeding                   | Via connection<br>(plating, paste) |            |

|                |        | Spin coating                  | Polymer                   | Via connection<br>(plating, paste) |            |

Table 1 - Classification of device embedding (continued)

- 12 -

### 3.2 Substrate

Structures and fabrication processes of device embedded substrates are illustrated in Table 2. A base substrate is necessary for the device embedded substrate to embed active and passive devices. Most of the base substrates are multilayer substrates and build-up substrates, but an insulating resin board, insulating sheet, metal sheet or film carrier can certainly also be used. Table 2 shows the method to embed the active or passive device and then connect the device to the surface conductor by vias made of copper plating and conductive paste and checking items during the fabrication process.

This document, however, does not cover active devices formed on a silicon interposer, a compound semiconductor substrate or a printed wiring board and passive device (resistor, capacitor or inductor) but it does cover inductors formed together with a conductor pattern and capacitor in its structure.

| Process | Item                                     | Stru        | cture          | To check                                                         |  |

|---------|------------------------------------------|-------------|----------------|------------------------------------------------------------------|--|

| FIDCess | item                                     | Pad bonding | Via connection | TO CHECK                                                         |  |

| 1       | Base                                     | 8838283     |                | Opening, short                                                   |  |

| 2       | Mounting                                 |             | 8 85 X 6 8 8 8 | Position accuracy                                                |  |

| 3       | Pad bonding                              |             | _              | Connection,<br>conduction                                        |  |

| 4       | Embedding                                |             |                | Microvoid<br>Board thickness<br>Flatness                         |  |

|         |                                          |             | I PAPER        |                                                                  |  |

| 5       | Via hole                                 |             |                | Hole position<br>Terminal position<br>Resistance to<br>chemicals |  |

| 6       | Via hole                                 | _           |                | Thicknesses of Cu<br>plating & conductive<br>paste<br>Micro void |  |

| 7       | Pattern formation<br>(multi-layer)       |             |                | Open, short                                                      |  |

| 8       | Surface treatment<br>(solder mask, etc.) |             |                | Observation                                                      |  |

### Table 2 – Embedded device structure and fabrication process

- 13 -

### 3.3 Jisso mounting and interconnection

There are two types of terminal connections; one is to connect terminals of an embedded device to connecting pads formed on the base, and the other is to form connecting vias on the device after embedding. The device is connected to the pads on the base using conventional semiconductor and SMD mounting techniques and then the device is embedded. The device is connected to the conductor pattern in the second case after embedding by copper plating or conductive paste.

Both of the device mountings can be classified into die-bonding and mounting methods as shown in Table 3.

| Jisso       | mounting    | Device             | Interco         | onnection                | Structure         |

|-------------|-------------|--------------------|-----------------|--------------------------|-------------------|

|             |             |                    | Process         | Interconnection          |                   |

| Pad bonding | Die bonding | Chip               | Wire bonding    | Wire melt-<br>connection |                   |

|             |             |                    | Flip-chip       | Metal bonding            | Metal bonding     |

|             |             |                    | bonding         | Contact connection       |                   |

|             |             |                    |                 |                          | Contact           |

|             |             |                    |                 |                          |                   |

|             | Mounting    | Wafer level        | Reflow          | Soldering                | Soldering         |

|             |             | packaging<br>(WLP) | Polymer bonding | Conductive paste         |                   |

|             |             | Package            | Reflow          | Soldering                | Conductive past   |

|             |             |                    | Polymer bonding | Conductive paste         |                   |

|             |             | Rectangular        | Reflow          | Soldering                | Soldering         |

|             |             | chip               | Polymer bonding | Conductive paste         |                   |

|             |             | Rod-type chip      | Reflow          | Soldering                | Conductive past   |

|             |             |                    | Polymer bonding | Conductive paste         |                   |

|             |             | Module             | Reflow          | Soldering                | Soldering         |

|             |             |                    | Polymer bonding | Conductive paste         |                   |

|             |             | MEMS               | Reflow          | Soldering                | Conductive past   |

|             |             |                    | Polymer bonding | Conductive paste         |                   |

| Via bonding | Die bonding | Chip               | Via connection  | Copper plating           | Conner plating    |

|             |             |                    |                 | Conductive paste         | Copper plating    |

|             |             | Wafer level        | Via connection  | Copper plating           |                   |

|             |             | package (WLP)      |                 | Conductive paste         | Conductive past   |

|             | Mounting    | Package            | Via connection  | Copper plating           |                   |

|             |             |                    |                 | Conductive paste         |                   |

|             |             | Rectangular        | Via connection  | Copper plating           | Copper plating    |

|             |             | chip               |                 | Conductive paste         | 1986 <b>- 198</b> |

|             |             | Rod-type chip      | Via connection  | Copper plating           | Conductive pas    |

|             |             |                    |                 | Conductive paste         | 1000 VIZ VIZ      |

|             |             | Module             | Via connection  | Copper plating           |                   |

|             |             |                    |                 | Conductive paste         |                   |

|             |             | MEMS               | Via connection  | Copper plating           |                   |

|             |             |                    |                 | Conductive paste         |                   |

### Table 3 – Jisso mounting and interconnection of the device embedded substrate

- 14 -

NOTE The shape and surface treatment of the terminals of the embedding device should be agreed upon between the user and the supplier of the device.

PAS 62326-14 © IEC:2010(E)

### 3.4 Structure and terminology

### 3.4.1 General

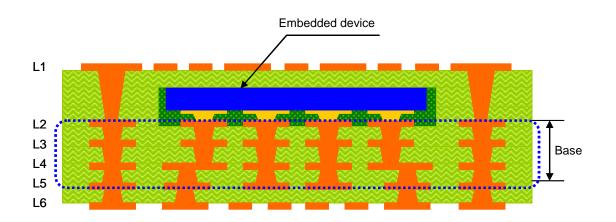

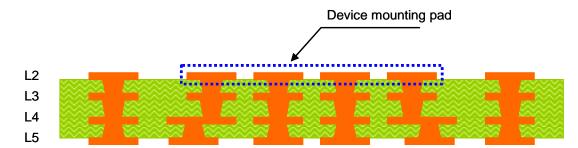

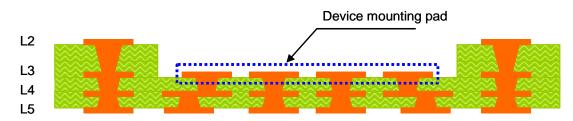

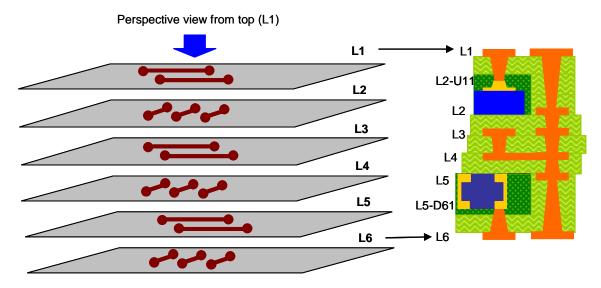

Figure 6 shows each section of the device embedded substrate and its name. See JPCA-TD01-2008, Terms and definitions in electronic circuits, and JIS C 5603, Terms and definitions in printed wiring boards. The number of layers is counted after completion of the device embedding as L1, L2 ~ L6 (in case of 6 layers) from the top layer.

- 15 -

The structure of the device embedded substrate is illustrated by means of the structure of the build-up substrate. See JPCA-BU01–2007, Build-up wiring board (Terms and test methods). Figure 7 shows the typical structure of the base and Figure 8 the cavity structure. Other structures are shown in Figure 9 with the insulating base, in Figure 10 for the base using a conductive carrier or a metal sheet. Figure 11 shows the structure of the device embedded ceramics and Figure 12 shows the standard ceramic board as the wiring board base.

Figure 6 – Entire structure of device embedded substrate

Figure 7 – Base (typical structure)

Figure 8 – Base (Cavity structure)

- 16 -

Figure 12 – Ceramic board used as base

Figure 13 to Figure 19 show various cases of device embedding in conventional mounting technique, electric connection after embedding various types of devices, embedding device over more than one layer, device embedding with resin base, and use of conductor layer and metal sheet/copper foil.

- 17 -

### 3.4.2 Device embedding by conventional process

Figure 13a – Wire bonding connection and embedding of active device bear chip

Figure 13b – Soldering connection and embedding of active device

Figure 13c – Soldering connection of square type passive device

- 18 -

Figure 13d – Conductive resin connection and embedding of active device

Figure 13e – Conductive resin connection and embedding of square type passive device

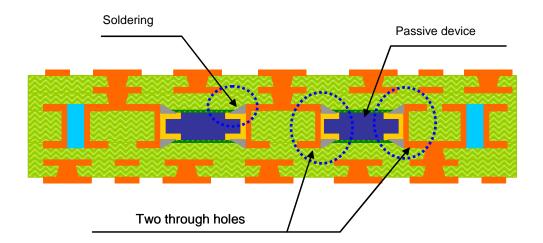

Figure 13f – Soldering connection into through hole and embedding of passive device

Figure 13 – Embedding of device by conventional methods

- 19 -

### 3.4.3 Electrical connection by vias after device embedding

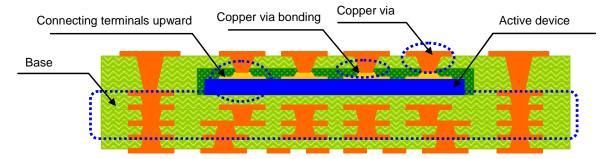

Figure 14b – Connection by Cu plating after embedding of square type passive device

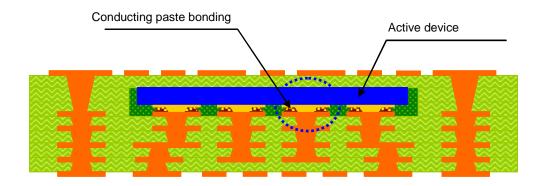

Figure 14c – Conductive paste connection after embedding of active device package

| <br>                        | Passive device           |                 |                              |  |  |

|-----------------------------|--------------------------|-----------------|------------------------------|--|--|

|                             |                          |                 |                              |  |  |

| <br>1989/<br>1999/<br>1999/ | - 5557<br>- 5727<br>- 72 | V<br>V<br>V V V | - 5555<br>- 7420/<br>- 7420/ |  |  |

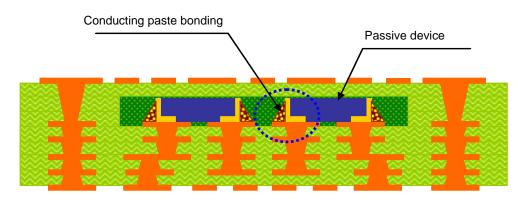

Figure 14d – Conductive paste connection after embedding of square type passive device chip

Figure 14 – Via connection after embedding

### 3.4.4 Embedding of various devices over multiple layers

### 3.4.4.1 Device embedded substrate of device embedding in multi-layers

- 20 -

### 3.4.4.2 Embedding of various devices onto resin base substrate

Figure 16 – Resin base substrate

## 3.4.4.3 Device embedding using conductor and metal sheet/copper foil base substrate

- 21 -

Figure 17 – Conductor and metal sheet/copper foil as the base substrate

3.4.4.4 Ceramic and resin composite device embedded substrate using passive device embedded ceramic substrates as the base

Figure 18 – Device embedded substrate using passive device embedded ceramic substrates as the base

# 3.4.4.5 Device embedded substrate using ceramic and LTCC substrates as the base (including ceramic and LTCC substrates which do not embed passive devices)

- 22 -

Figure 19 – Device embedded substrate using passive device embedded ceramic substrates as the base – second type

### 4 Test methods

### 4.1 General

The test methods for the un-embedded board are those for the board itself. The specifications and test methods for the embedded board are for the embedded board only and not for the embedded device. It is recommended to evaluate a TEG mounted board (test element group) to obtain assembly condition and library data for design. The TEG is less expensive than actual embedding semiconductor devices and can provide necessary technical data easily. Guarantee of reliability of a product shall be agreed between user and supplier. Embedding of device into board shall also be agreed upon between user and supplier basically based on the statement given in this document.

### 4.2 Structure of TEG (Test Equipment Group – Test vehicle)

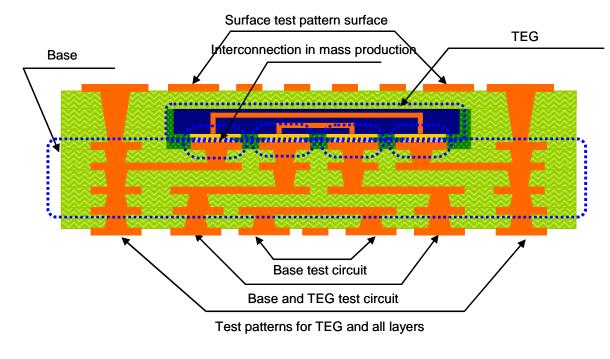

A schematic diagram of TEG is shown in Figure 20 for the evaluation of the conductor pattern on the base of a board, the interconnection between the base and the test specimen and the conductor pattern on the board surface. The characteristics of the device embedded board and test equipment shall also be agreed between user and supplier.

- 23 -

Figure 20 – Schematic diagram of test circuit

NOTE Test items, test methods, and test equipment are still under consideration in the standardization committee and there is a possibility that the description made in this document may be changed if necessary.

### 4.3 Test circuit

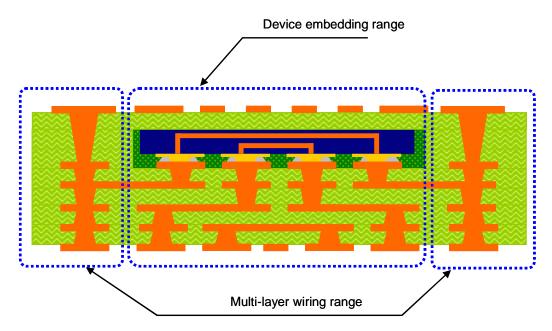

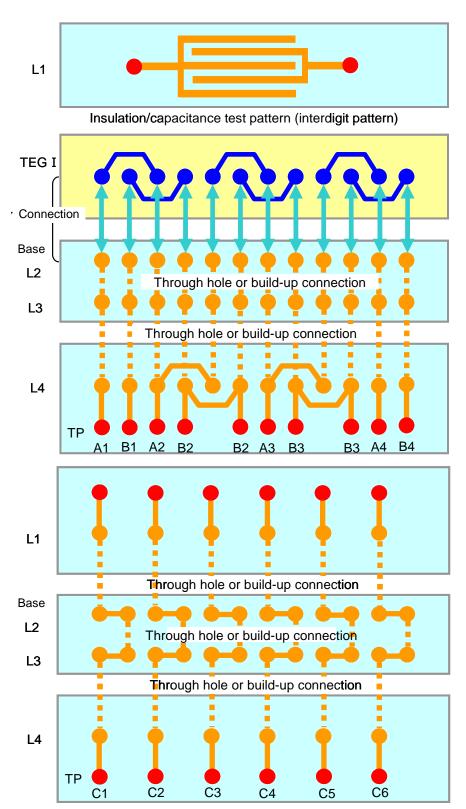

TEG, a dummy specimen of an embedding device, is embedded into board using the actual embedding condition; it is tested for the multilayer wiring patterns shown in Figure 21 similarly to the test of multilayer wiring board for interconnections between conductor pattern by means of through holes and/or vias using the Daisy chain pattern. It is recommended to use the circuit patterns made within the range of device embedding for the tests of inter-digital type capacitor, impedance, insulation and impurity migration as illustrated in Figure 22.

- 24 -

Size of test board, wiring specification of TEG and size as a replacement of embedding device, and wiring specification of the device embedding board shall be agreed between user and supplier.

Figure 21 - Multilayer wiring patterns

Figure 22 – Conceptual structure of test circuit, comb-type capacitor, detection pattern of impedance, insulation and migration

### 4.4 Test specimen (TEG) and example of test substrate

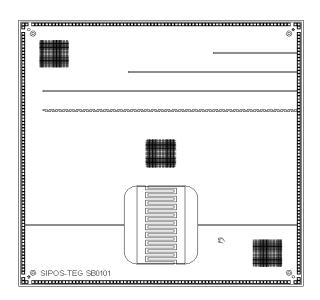

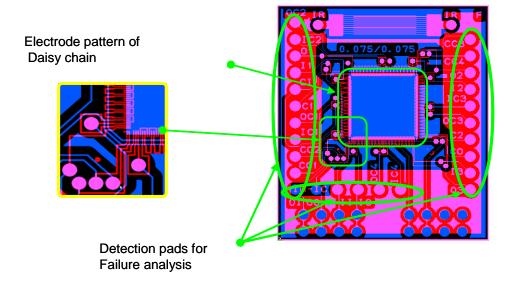

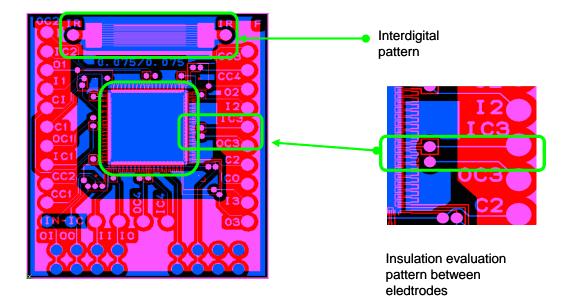

Figure 23 shows an example of specimen. It has a Daisy chain pattern in peripheral sections and interdigital capacitor, an impedance detection pattern and a bend detection pattern. Its die size is 10 mm x 10 mm and thickness is 0,15 mm. Electrode number is 316 with a pitch of 120  $\mu$ m. Electrode size is 110  $\mu$ m with an opening of 90  $\mu$ m x 90  $\mu$ m. Gold bump is used for connection. Figure 24 shows a test board. The conductor resistance (connection evaluation) test is made by the Daisy chain shown in the figure. Insulation resistance test is made using the pattern for evaluation of conductor resistance between conductors and the interdigital pattern shown in Figure 25.

- 26 -

Figure 23 – Example of TEG

Figure 24 – Example of test circuit for connection evaluation

- 27 -

Figure 25 – Example of test circuit for insulation evaluation

### 5 Test items and test equipment

### 5.1 General

Evaluation of device embedded board is basically the same to that of electronic circuit board (printed wiring board and module substrate) but there are some new mechanical and electric test items.

Each test is performed using a specimen embedding the TEG as in actual device embedding using a Daisy chain pattern connection of the TEG and the substrate conductor pattern. It is recommended to use pads independently arranged at corners where the risk of failure is considered relatively high. Evaluation items and test methods are listed in Table 4.

### – 28 –

### 5.2 Test for resistance of conductor

The test method for conduction is shown in Table 4.

### Table 4 – Conduction test

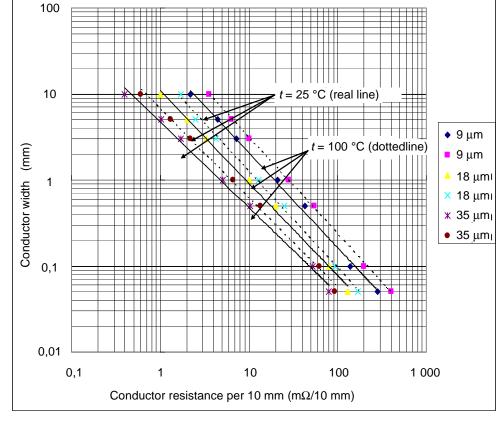

|                                            | Item                                                                                                                 | Specification                                                                                                                                                                                                                                                                        | Test method (JIS C 5012)                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Conduction<br>(conductivity<br>evaluation) | Inner conductor<br>Outer conductor<br>Plated through<br>hole and via hole<br>(copper plating or<br>conductive paste) | To be agreed between user and<br>supplier.<br>Relations between resistance and<br>conductor width, conductor thickness<br>and conductor temperature is shown<br>in Figure 26 for reference.<br>Conductivity of Cu is taken as<br>$\rho = 1.8 \times 10^{-6} \Omega \cdot \text{cm}.$ | As per 7.11 (conductor).<br>Shape and dimension of specimen should<br>be agreed between user and supplier.<br>1. Test method<br>• Daisy chain or resistance between<br>specified two points.<br>2. Equipment<br>• 4 terminal low resistance<br>measurement equipment<br>• High/low temperature bath<br>As per 7.13 (inner layer connection)<br>Ad per 7.12 (plated through hole) |

|                                            | Connection to<br>embedded device                                                                                     | To be agreed between user and supplier                                                                                                                                                                                                                                               | Use TEG for embedding device test.<br>Test for the connection to embedded<br>device is under consideration.                                                                                                                                                                                                                                                                      |

## Figure 26 – Resistance per unit length of conductor pattern in relation with conductor width

### 5.3 Resistance to over current

The test method for resistance over current is shown in Table 5.

| ltem                            |                                  | Specification                                                                                                                                                        | Test method (JIS C 5012)                                                                                                      |  |

|---------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|

| Resistance<br>to<br>overcurrent | Conductor                        | To be agreed between user and supplier                                                                                                                               | As per 7.2 (resistance to overcurrent of conductor)                                                                           |  |

|                                 | Plated through hole              |                                                                                                                                                                      | As per 7.3 (resistance to overcurrent of plated through hole)                                                                 |  |

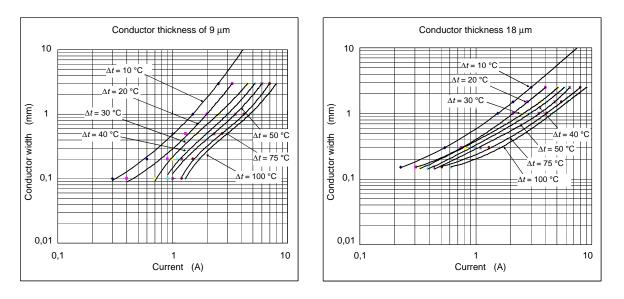

|                                 | Connection to<br>embedded device | To be agreed between user and<br>supplier<br>The relation of conductor width,<br>conductor thickness and temperature<br>rise with current are shown in<br>Figure 27. | Under consideration<br>Use TEG in place of embedded<br>device.<br>The test for the embedded device is<br>under consideration. |  |

Table 5 – Resistance to over current and its test method

Figure 27 – The relation of conductor width, conductor thickness and temperature rise with current

### 5.4 Withstand voltage

The test method is shown in Table 6.

| Item                 |                               | Specification                                                                    | Specification Test method (JIS C 5                                                                                                                                  |                   |  |

|----------------------|-------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--|

| Withstand<br>voltage | The same plane                | There should be no mechanical<br>damages, flush over, nor insulation<br>damages. | As per 7.4 (surface withstand voltage)<br>The test voltage is chosen from the<br>following table for both outer<br>(with/without solder resist) and inner<br>layers |                   |  |

|                      |                               |                                                                                  | Minimum conductor<br>gap<br>mm                                                                                                                                      | Test voltage<br>V |  |

|                      |                               |                                                                                  | 0,05≦ < 0,10                                                                                                                                                        | 50                |  |

|                      |                               |                                                                                  | 0,10≦ < 0,13                                                                                                                                                        | 100               |  |

|                      |                               |                                                                                  | 0.13≦ < 0,25                                                                                                                                                        | 200               |  |

|                      |                               |                                                                                  | 0,25≦ < 0,40                                                                                                                                                        | 350               |  |

|                      |                               |                                                                                  | 0,40≦                                                                                                                                                               | 500               |  |

|                      |                               |                                                                                  | NOTE Solder resist is as coating.                                                                                                                                   | not considered    |  |

|                      | Interlayer                    | There should be no mechanical<br>damages, flush over, nor insulation<br>damages. | As per 7.5 (Interlayer withstand voltage)<br>The test voltage is chosen from the<br>following table.                                                                |                   |  |

|                      |                               |                                                                                  | Interlayer distance<br>mm                                                                                                                                           | Test voltage<br>V |  |

|                      |                               |                                                                                  | 0,05≦ < 0,08                                                                                                                                                        | 250               |  |

|                      |                               |                                                                                  | 0,08≦ < 0,20                                                                                                                                                        | 500               |  |

|                      |                               |                                                                                  | 0,02≦                                                                                                                                                               | 1 000             |  |

|                      | Connection to embedded device | To be agreed between user and supplier                                           | Use TEG for embedding device test.                                                                                                                                  |                   |  |

|                      |                               |                                                                                  | Test for the connection to embedded device is under consideration.                                                                                                  |                   |  |

### 5.5 Insulation resistance

Test of the insulation resistance is made by using the electrode evaluation pattern made by combination of base and embedding board as in the case of the conductor resistance test. Test items are shown in Table 7.

|                       | Item                                                                                  |                                                                                                              | Specificat                                                       | ion                            | Test method (JI                                                                                                                                     | Test method (JIS C 5012) |  |

|-----------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--|

| Insulation resistance | The same Normal plane                                                                 | Normal                                                                                                       | Insulation resistance should be more than the value shown below. |                                | See Annex A of this specification.<br>See Annex B of this specification.                                                                            |                          |  |

|                       |                                                                                       |                                                                                                              | Minimum conductor<br>gap<br>mm                                   | Insulation<br>resistance<br>Ω  |                                                                                                                                                     |                          |  |

|                       |                                                                                       |                                                                                                              | 0,05≦ < 0,13                                                     | 1 ×10 <sup>8</sup>             |                                                                                                                                                     |                          |  |

|                       |                                                                                       | Resistance to<br>humidity<br>(temperature-<br>humidity cycle)<br>Resistance to<br>humidity<br>(steady state) | 0,13≦                                                            | 5 ×10 <sup>8</sup>             |                                                                                                                                                     |                          |  |

|                       |                                                                                       |                                                                                                              | Insulation resistance sho<br>than the value shown be             |                                | Test should be made as in the case of normal condition.                                                                                             |                          |  |

|                       |                                                                                       |                                                                                                              | Minimum insulation<br>thickness<br>mm                            | Insulation<br>resistance<br>Ω  |                                                                                                                                                     |                          |  |

|                       |                                                                                       |                                                                                                              | 0,05≦ < 0,20                                                     | 1 ×10 <sup>8</sup>             | 1                                                                                                                                                   |                          |  |

|                       |                                                                                       |                                                                                                              | 0,20≦                                                            | 5 ×10 <sup>8</sup>             |                                                                                                                                                     |                          |  |

|                       | Inter-layer                                                                           | Normal                                                                                                       | Insulation resistance sho<br>than the value shown be             |                                | See Annex C of this specification. The test voltage is given below.                                                                                 |                          |  |

|                       |                                                                                       |                                                                                                              | Minimum insulation<br>thickness<br>mm                            | Insulation resistance $\Omega$ | Minimum insulation<br>thickness                                                                                                                     | Test voltage<br>∨        |  |