Edition 1.0 2007-09

# INTERNATIONAL STANDARD

# NORME INTERNATIONALE

Integrated circuits – Measurement of electromagnetic immunity, 150 kHz to 1 GHz –

Part 3: Bulk current injection (BCI) method

Circuits intégrés – Mesure de l'immunité électromagnétique, 150 kHz à 1 GHz – Partie 3: Méthode d'injection de courant (BCI)

### THIS PUBLICATION IS COPYRIGHT PROTECTED

### Copyright © 2007 IEC, Geneva, Switzerland

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from either IEC or IEC's member National Committee in the country of the requester.

If you have any questions about IEC copyright or have an enquiry about obtaining additional rights to this publication, please contact the address below or your local IEC member National Committee for further information.

Droits de reproduction réservés. Sauf indication contraire, aucune partie de cette publication ne peut être reproduite ni utilisée sous quelque forme que ce soit et par aucun procédé, électronique ou mécanique, y compris la photocopie et les microfilms, sans l'accord écrit de la CEI ou du Comité national de la CEI du pays du demandeur.

Si vous avez des questions sur le copyright de la CEI ou si vous désirez obtenir des droits supplémentaires sur cette publication, utilisez les coordonnées ci-après ou contactez le Comité national de la CEI de votre pays de résidence.

IEC Central Office 3, rue de Varembé CH-1211 Geneva 20 Switzerland

Email: inmail@iec.ch Web: www.iec.ch

### About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes International Standards for all electrical, electronic and related technologies.

### **About IEC publications**

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the latest edition, a corrigenda or an amendment might have been published.

Catalogue of IEC publications: www.iec.ch/searchpub

The IEC on-line Catalogue enables you to search by a variety of criteria (reference number, text, technical committee,...). It also gives information on projects, withdrawn and replaced publications.

■ IEC Just Published: www.iec.ch/online\_news/justpub

Stay up to date on all new IEC publications. Just Published details twice a month all new publications released. Available on-line and also by email.

Electropedia: www.electropedia.org

The world's leading online dictionary of electronic and electrical terms containing more than 20 000 terms and definitions in English and French, with equivalent terms in additional languages. Also known as the International Electrotechnical Vocabulary online.

Customer Service Centre: www.iec.ch/webstore/custserv

If you wish to give us your feedback on this publication or need further assistance, please visit the Customer Service Centre FAQ or contact us:

Email: csc@iec.ch Tel.: +41 22 919 02 11 Fax: +41 22 919 03 00

### A propos de la CEI

La Commission Electrotechnique Internationale (CEI) est la première organisation mondiale qui élabore et publie des normes internationales pour tout ce qui a trait à l'électricité, à l'électronique et aux technologies apparentées.

### A propos des publications CEI

Le contenu technique des publications de la CEI est constamment revu. Veuillez vous assurer que vous possédez l'édition la plus récente, un corrigendum ou amendement peut avoir été publié.

■ Catalogue des publications de la CEI: <u>www.iec.ch/searchpub/cur\_fut-f.htm</u>

Le Catalogue en-ligne de la CEI vous permet d'effectuer des recherches en utilisant différents critères (numéro de référence, texte, comité d'études,...). Il donne aussi des informations sur les projets et les publications retirées ou remplacées.

Just Published CEI: www.iec.ch/online\_news/justpub

Restez informé sur les nouvelles publications de la CEI. Just Published détaille deux fois par mois les nouvelles publications parues. Disponible en-ligne et aussi par email.

■ Electropedia: <u>www.electropedia.org</u>

Le premier dictionnaire en ligne au monde de termes électroniques et électriques. Il contient plus de 20 000 termes et définitions en anglais et en français, ainsi que les termes équivalents dans les langues additionnelles. Egalement appelé Vocabulaire Electrotechnique International en ligne.

Service Clients: www.iec.ch/webstore/custserv/custserv\_entry-f.htm

Si vous désirez nous donner des commentaires sur cette publication ou si vous avez des questions, visitez le FAQ du Service clients ou contactez-nous:

Email: csc@iec.ch Tél.: +41 22 919 02 11 Fax: +41 22 919 03 00

Edition 1.0 2007-09

# INTERNATIONAL STANDARD

# NORME INTERNATIONALE

Integrated circuits – Measurement of electromagnetic immunity, 150 kHz to 1 GHz –

Part 3: Bulk current injection (BCI) method

Circuits intégrés – Mesure de l'immunité électromagnétique, 150 kHz à 1 GHz – Partie 3: Méthode d'injection de courant (BCI)

INTERNATIONAL ELECTROTECHNICAL COMMISSION

COMMISSION ELECTROTECHNIQUE INTERNATIONALE

PRICE CODE CODE PRIX

R

ICS 31.200 ISBN 2-8318-9320-8

### CONTENTS

| FO   | OREWORD3                                                                  |                                       |  |

|------|---------------------------------------------------------------------------|---------------------------------------|--|

|      |                                                                           |                                       |  |

| 1    | Scope and object                                                          |                                       |  |

| 2    | Normative references                                                      |                                       |  |

| 3    | Terms and definitions                                                     |                                       |  |

| 4    | General                                                                   | 5                                     |  |

| 5    | Test conditions                                                           | 6                                     |  |

|      | 5.1 General                                                               |                                       |  |

|      | 5.2 Test equipment                                                        |                                       |  |

| _    | 5.3 Test board                                                            |                                       |  |

| 6    | Test procedure                                                            |                                       |  |

|      | 6.1 Hazardous electromagnetic fields                                      |                                       |  |

|      | 6.2 Calibration of forward power limitation                               |                                       |  |

|      | 6.3 BCI test                                                              |                                       |  |

| 7    | Test report                                                               |                                       |  |

| •    |                                                                           | · · · · · · · · · · · · · · · · · · · |  |

| Δn   | nex A (informative) Examples for test levels and frequency step selection | 1.3                                   |  |

|      | nex B (informative) Example of BCI test board and set-up                  |                                       |  |

|      | nex C (informative) Example of RF test board and set-up                   |                                       |  |

| Λ    | mex o (informative) Example of N. test board and set-up                   |                                       |  |

| D:L  | oliography                                                                | 10                                    |  |

| DIL  | biography                                                                 | 18                                    |  |

|      |                                                                           |                                       |  |

| Fig  | gure 1 – Principal current path when using BCI                            | 6                                     |  |

| Fig  | gure 2 – Schematic diagram of BCI test set-up                             | 7                                     |  |

| Fig  | gure 3 – Example test board, top view                                     | 8                                     |  |

| Fig  | gure 4 – Calibration set-up                                               | 10                                    |  |

| Fig  | gure 5 – BCI test procedure flowchart for each frequency step             | 11                                    |  |

| Fig  | gure 6 – Impedance validation test set-up                                 | 11                                    |  |

|      | gure B.1 – General view                                                   |                                       |  |

| Fig  | gure B.2 – Example of top view of the test board                          | 16                                    |  |

|      | gure B.3 – Test board build-up                                            |                                       |  |

| _    | gure B.4 – Test board and copper fixture                                  |                                       |  |

| _    | gure B.5 – Example of a non-conductive probes support fixture             |                                       |  |

|      | gure C.1 – Compact RF coupling to differential IC ports                   |                                       |  |

| , 19 | gare 5.1 Compact it coupling to amore that to ports                       |                                       |  |

| т-   | bla A.4. Tast savarity lavals                                             | 4.0                                   |  |

|      | ble A.1 – Test severity levels                                            |                                       |  |

|      | ble A.3 Logarithmic frequency step                                        | 14<br>1 <i>4</i>                      |  |

| 10   | NIA A X — I OGSTITAMIC TRACIJANOV STAN                                    | 1/                                    |  |

### INTERNATIONAL ELECTROTECHNICAL COMMISSION

# INTEGRATED CIRCUITS – MEASUREMENT OF ELECTROMAGNETIC IMMUNITY, 150 kHz TO 1 GHz –

### Part 3: Bulk current injection (BCI) method

### **FOREWORD**

- 1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as "IEC Publication(s)"). Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely with the International Organization for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- 2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC National Committees.

- 3) IEC Publications have the form of recommendations for international use and are accepted by IEC National Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

- 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter.

- 5) IEC provides no marking procedure to indicate its approval and cannot be rendered responsible for any equipment declared to be in conformity with an IEC Publication.

- 6) All users should ensure that they have the latest edition of this publication.

- 7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and members of its technical committees and IEC National Committees for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC Publications.

- 8) Attention is drawn to the normative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.

- 9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

International Standard IEC 62132-3 has been prepared by subcommittee 47A: Integrated circuits, of IEC technical committee 47: Semiconductor devices.

The text of this standard is based on the following documents:

| FDIS         | Report on voting |

|--------------|------------------|

| 47A/773/FDIS | 47A/776/RVD      |

Full information on the voting for the approval of this standard can be found in the report on voting indicated in the above table.

This publication has been drafted in accordance with the ISO/IEC Directives, Part 2.

A list of all parts of the IEC 62132 series, published under the general title *Integrated circuits* – *Measurement of electromagnetic immunity, 150 kHz to 1 GHz* can be found on the IEC website.

The committee has decided that the contents of this publication will remain unchanged until the maintenance result date indicated on the IEC web site under "http://webstore.iec.ch" in the data related to the specific publication. At this date, the publication will be

- · reconfirmed,

- withdrawn,

- replaced by a revised edition, or

- amended.

# INTEGRATED CIRCUITS – MEASUREMENT OF ELECTROMAGNETIC IMMUNITY, 150 kHz TO 1 GHz –

### Part 3: Bulk current injection (BCI) method

### 1 Scope and object

This part of IEC 62132 describes a bulk current injection (BCI) test method to measure the immunity of integrated circuits (IC) in the presence of conducted RF disturbances, e.g. resulting from radiated RF disturbances. This method only applies to ICs that have off-board wire connections e.g. into a cable harness. This test method is used to inject RF current on one or a combination of wires.

This standard establishes a common base for the evaluation of semiconductor devices to be applied in equipment used in environments that are subject to unwanted radio frequency electromagnetic signals.

### 2 Normative references

The following referenced documents are indispensable for the application of this document. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

IEC 62132-1:2006, Integrated circuits – Measurement of electromagnetic immunity, 150 kHz to 1 GHz – Part 1: General conditions and definitions

### 3 Terms and definitions

For the purposes of this document, the terms and definitions given in IEC 62132-1 apply.

### 4 General

The characterization of RF immunity (or susceptibility) of an integrated circuit (IC) is essential to define the optimum design of a printed circuit board, filter concepts and for further integration into an electronic system. This document defines a method for measuring the immunity of ICs to RF current induced by electromagnetic disturbance.

This method is based on the bulk current injection (BCI) method used for equipment and systems [1, 2, 3]. The BCI method simulates the induced current as a result of direct radiated RF signals coupled onto the wires and cables of equipment and systems.

In general, in electronic systems, off-board wire connections or traces on the printed circuit board act as antennas for electromagnetic fields. Via this coupling path, these electromagnetic fields will induce voltages and currents at the pins of the IC and may cause interference. ICs are often used in various configurations dependent on their application. In this case, immunity levels of electronic equipment are closely linked to the ability of an IC to withstand the effects of an electromagnetic field represented.

To characterize the RF immunity of an IC, the induced current level necessary to cause the IC's malfunction is measured. The malfunction may be classified from A to E according to the performance classes defined in IEC 62132-1.

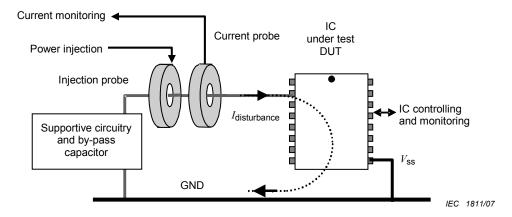

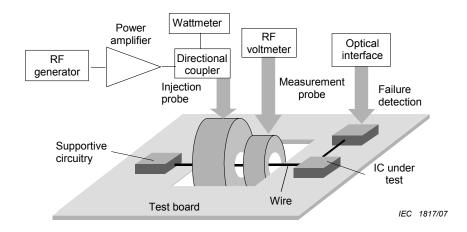

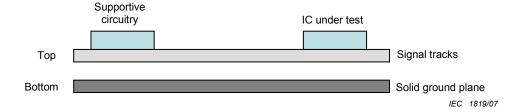

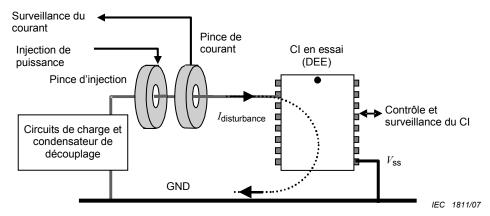

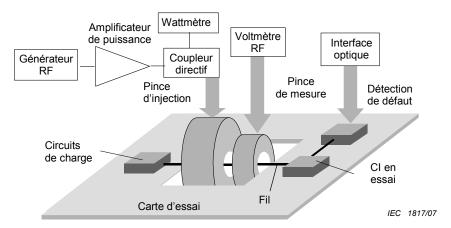

A principal set-up for the bulk current injection method is presented in Figure 1.

Figure 1 – Principal current path when using BCI

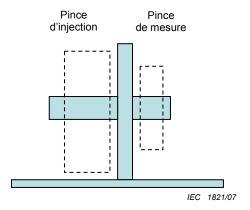

Two electrically shielded magnetic probes are clamped on one wires or a combination of wires that is/are connected to the device under test. The first probe is for the injection of RF power that induces  $I_{\rm disturbance}$  onto the wires. The second probe is used for monitoring the induced current on those wires.

The disturbance current flows in a loop comprising: wire(s), the selected IC's pin(s),  $V_{ss}$  terminal, ground path and supportive circuitry. This supportive circuit provides the IC functional elements as source and/or load(s). The supportive circuitry is directly connected to the IC. When the equivalent RF impedance of the supportive circuitry is larger than 50  $\Omega$ , then a by-pass capacitor is recommended. The by-pass capacitor, to be used at the supportive circuitry side, may also be needed to confine the loop area in which the induced current will be flowing. By default, the lumped by-pass capacitor of 1 nF shall be used. It represents the capacitance from the wire onto a cable harness or chassis. Deviation from using this bypass capacitor (e.g. as functional performance becomes affected) shall be given in the test report

The by-pass capacitor may be supplemented with optional decoupling network, see Figure 3, to achieve the required attenuation towards the supportive circuitry. The decoupling impedance is determined by the RF immunity of the supportive circuitry. It shall not adversely affect the response of the device under test, i.e. the result of the test.

The disturbance current  $I_{\text{disturbance}}$  induced into the wire(s) flows through the IC and may create a failure in the device's operation. This failure is defined by parameters called the immunity acceptance criteria, which are checked by a controlling and monitoring system.

### 5 Test conditions

### 5.1 General

The general test conditions are described in the IEC 62132-1.

During the immunity tests, either a continuous wave (CW) or an amplitude modulated (AM) RF signal shall be used as the disturbance signal. The device under test (DUT) shall be exposed at each frequency for sufficient dwell time. By default, an amplitude modulated RF signal using 1 kHz sinusoidal signal with a modulation index of 80 % is recommended for testing.

When an AM signal is used, the peak power shall be the same as for CW, see IEC 62132-1. When other modulation schemes are used, they shall be noted in the EMC IC test report.

The levels of disturbance current required to test the IC's immunity depend on the application environment. Table A.1 in Annex A gives some examples of typical values for disturbance current injection.

NOTE Where required by the customer, to satisfy high test levels, additional protection components could be used to permit high current injection. All other pins must be left loaded according to 6.4 of IEC 62132-1.

### 5.2 Test equipment

The test equipment comprises the following equipment and facilities:

- · ground reference plane;

- current injection probe(s);

- current measurement probe(s);

- RF signal generator with AM and CW capability;

- RF power amplifier(s). A minimum 50 Watt RF power amplifier is recommended;

- RF wattmeter or equivalent instrument, to measure the forward (and reflected) power;

- RF voltmeter or equivalent instrument which, together with the current measurement probe, measures the disturbance current induced;

- directional coupler;

- DUT monitoring equipment (optional: optical interface(s)).

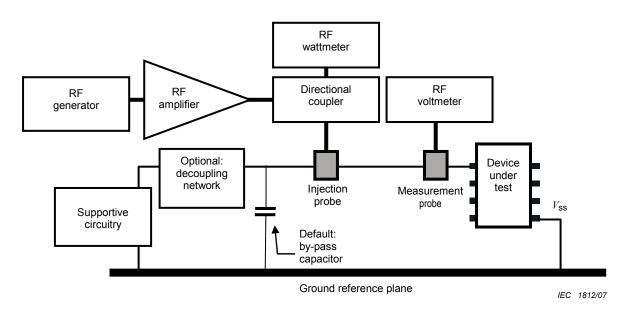

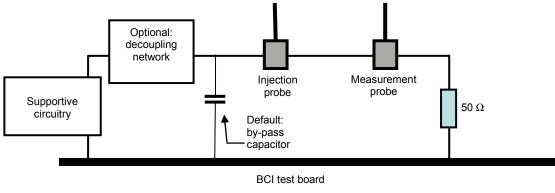

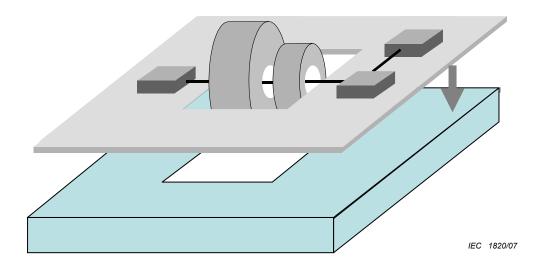

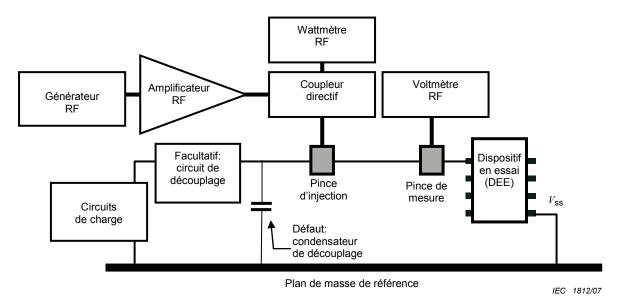

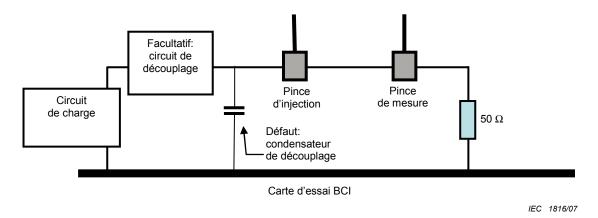

A schematic diagram of the test set-up is shown in Figure 2.

Figure 2 - Schematic diagram of BCI test set-up

An injection probe or set of probes capable of operating over the test frequency range is required to couple the disturbance signal into the connecting lines of the DUT. The injection probe is a transformer.

NOTE An optical interface can be used for monitoring the DUT response against the immunity criteria given. Use of optical interface is not mandatory but recommended.

### 5.3 Test board

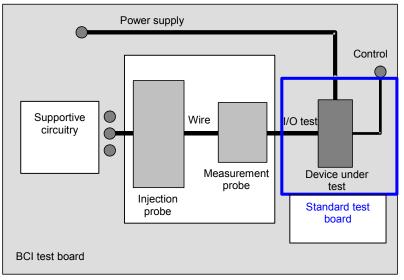

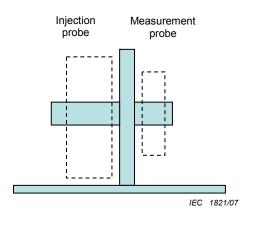

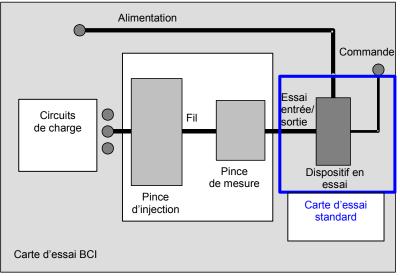

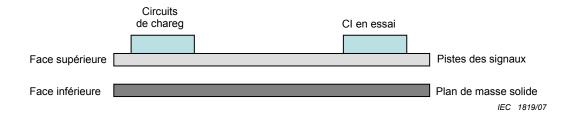

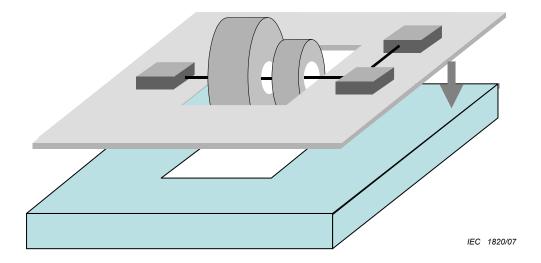

An example of a BCI test board is shown in Figure 3. This example of the BCI test board has an opening in the middle to accommodate the two current probes.

The standard test board as defined in IEC 62132-1 needs to be modified to fulfil the BCI test condition requirements. If the standard test board is used, a low impedance ground connection between standard test board and the BCI test board shall be made. Gasket, contact springs or multiple screws shall be used to contact the BCI test board to the BCI test fixture support at the inner hole when the GRP is not included with the BCI test board layer stack-up.

IEC 1813/07

Figure 3 – Example test board, top view

The wire(s) to which the current is injected to is/are connected at one end to the selected IC pin(s) and on the other end connected to the support circuitry. The support circuitry may comprise a load, a supply or a signal source necessary to operate the device under test as intended.

The BCI test board has the advantage of fixing the position of the probes resulting in a more reproducible measurement. The size of the holes and the injection wire length should be at least designed to the size of the probes used. The hole shall exceed the size of the probes on all sides by at least 10 mm, with a maximum of 30 mm. In general, the wire length shall be limited to a quarter of a wavelength at the maximum frequency used with the BCI test method ( $\approx$  75 mm in air at 1 GHz).

The BCI test board is placed on a copper test fixture connected to the ground reference plane (GRP), shown in Annex C. Size of GRP is typically table top size extended to a minimum of 0,1 m beyond the footprint of the test fixture. The copper test fixture needs to be high enough to allow the injection probe-carrying fixture.

NOTE 1 The GRP may also be incorporated in one of the BCI test board copper layers. In this case, the copper test fixture support is no longer necessary.

The shield of the injection probe and the measurement probe shall be grounded with a short connection underneath the copper test fixture to the GRP.

NOTE 2 Coaxial feed-through connectors can be mounted through the GRP (underneath the copper test fixture) to be connected to the current injection and measurement probes directly.

### 6 Test procedure

### 6.1 Hazardous electromagnetic fields

RF fields may exist within the test area. Care shall be taken to ensure that the requirements for limiting the exposure of human to RF energy are met. It is preferable to perform the RF immunity test in an enclosure providing sufficient RF shielding.

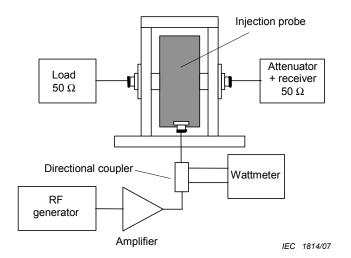

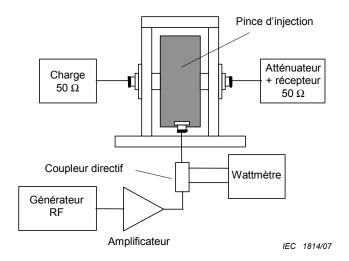

### 6.2 Calibration of forward power limitation

The required forward RF power from the RF generator and RF amplifier is determined in the BCI test set-up calibration procedure of the injection probe. In this process the level of forward RF power (in CW mode) supplied to the injection probe is established, which is necessary to generate the desired current  $I_{\rm disturbance}$ .

Calibration is performed in the calibration fixture, composed of an electrically short section of a transmission line. The short section permits the measurement of current in the central conductor of the line, while the current injection probe is clamped around the central conductor. The output terminals of the fixture are terminated with a 50  $\Omega$  load each with minimum of 0,5 W power dissipation, spectrum analyser or RF voltmeter. Measurement of the voltage established across the 50  $\Omega$  input impedance of RF receiver permits the calculation of current flowing in the central conductor.

The calibration procedure shall be as follows.

a) The injection probe shall be clamped in the calibration fixture as shown in Figure 6. Fix the probe in the central position, equidistant from either end of the fixture walls.

The calibration fixture will be terminated by a 50  $\Omega$  RF load at one end and a 50  $\Omega$  RF receiver (spectrum analyser, voltmeter, etc.) at the other, with an attenuator if necessary. Caution: use a load with an adequate power rating.

NOTE Lower power ratings can be used during calibration assuming that the system behaves linearly.

- b) Connect the components of test equipment as shown in Figure 4.

- c) Increase the amplitude of the test signal to the injection probe until the required current level, as measured by the RF receiver, is reached.

- d) Record the forward RF power necessary to generate the desired current  $I_{\rm disturbance}$ . This forward RF power is admitted as the maximum forward power limit,  $P_{\rm limit}$ .

- e) Repeat steps d) to e) for each frequency step within the specified frequency range.

Figure 4 - Calibration set-up

### 6.3 BCI test

For the RF immunity tests, a substitution method with power and current limitation is used, which allows keeping track of RF power and RF current up to the limits. Substitution method is well adapted in this IC immunity test method and related to the ISO method.

- Connect the current probes, other test equipment and test board.

- Supply the DUT and check for a proper operation.

- For each test frequency, increase the amplitude of the signal gradually to the injection probe until

- target test current limit level for  $I_{\rm disturbance}$  is reached as indicated by monitoring the output of the measurement current probe, or

- the calibrated maximum forward power  $P_{\text{limit}}$  supplied to the injection probe is reached. Also in this case, although the injected current level is not reached, the maximum current level is recorded, or

- the RF immunity level of the IC is found. If a failure of IC occurs or the limit for  $I_{\rm disturbance}$  is met or  $P_{\rm limit}$  target level is reached, in all cases the monitored current and the forward power are recorded.

NOTE 1 For the purpose of investigation, the details regarding the RF immunity determination could be recorded too.

NOTE 2 Assuming no glitches are generated during frequency transitions, the RF amplitude at the next frequency may be chosen e.g. 10 dB less than the previous level (taken into account the frequency dependency of the system) to speed up the test.

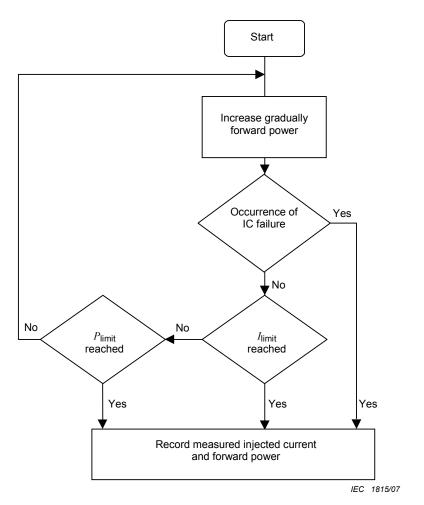

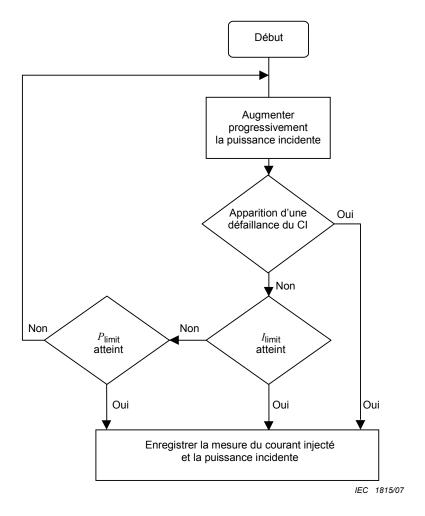

Test procedure is depicted in detail in the flowchart given in Figure 5. That flowchart applies for only one frequency step.

Figure 5 - BCI test procedure flowchart for each frequency step

### 6.4 BCI test set-up characterization procedure

In order to validate the BCI test board impedance, a validation procedure is required.

For this validation, all components of the test set-up shall be used, except for the device under test. The port represented by the selected pin(s) under IC test is replaced with a 50  $\Omega$  reference impedance. Figure 6 shows a schematic of the validation test set-up.

Figure 6 - Impedance validation test set-up

IEC 1816/07

During the validation over the whole frequency range, the value of injected current is fixed. A value of 10 mA for the disturbance current injected is recommended. For each frequency step, the RF forward power needed shall be noted.

Test board validation could be characterized by transfer impedance defined with:

$$Z(f) = \frac{P_{\text{forward}}(f)}{I^2}$$

In cases involving use of several test boards, the Z(f) values should be the same. That allows comparison of IC immunity tests results done under the same conditions.

### 7 Test report

The test report shall be prepared in accordance with the requirements given in IEC 62132-1.

Immunity acceptance criteria should be clearly described in the test report. The test board configuration should also be described in detail to reproduce the results.

In all cases, such parameters as injected RF current  $I_{\rm disturbance}$ , the applied forward RF power  $P_{\rm forward}$ , calibration power  $P_{\rm limit}$  and the current  $I_{\rm disturbance}$ , which are recorded during the calibration and measurement processes, shall be documented in the test report.

Additional critical items such as test board description and value of by-pass capacitor (default) and decoupling (when used) should be listed in the test report.

## Annex A

(informative)

### Examples for test levels and frequency step selection

### A.1 Typical values for current injection

The test signals severity level is the test current of the calibrated test current applied. These test severity levels are expressed in terms of the equivalent RMS (root-mean-square) mA value of the unmodulated current signal. These test levels are taken from the requirements for module testing in automotive/avionic applications. The levels applied at IC testing shall be provided by the end-user and are determined by the criticality of the function(s) controlled. Other application environments require less stringent limits.

Examples of severity levels are given in Table A.1. Levels of injected current are related to IC pin connection. Pins connected to external wiring could be tested with the highest current values, whereas pins with only local connections could be allowed to withstand the lower levels. Values should be clearly detailed in the IC test plan.

Table A.1 - Test severity levels

In case of use of additional protection components applied on the test board, in order to withstand higher current values, a description of this protection circuitry and its layout should be added in the IC test report.

### A.2 Frequency steps

Injected current induced by electromagnetic disturbances on wire is obtained at discrete frequencies. The distance between 2 test frequencies is defined as the frequency step.

The choice of the frequency steps should cover the whole immunity range of IC and avoid skipping frequencies on which an immunity problem may occur. In general, the root causes of IC disturbances are due to impedance resonances. These are often very narrow and the frequency step should take into account this phenomenon.

There are 2 ways to define frequency steps: with a linear or a logarithmic approach.

An example of a linear frequency step (automotive and aerospace applications) is given in Table A.2.

Table A.2 – Linear frequency step

| Frequency band    | Maximum frequency size step |

|-------------------|-----------------------------|

| 10 kHz to 100 kHz | 2 kHz                       |

| 100 kHz to 1 MHz  | 20 kHz                      |

| 1 MHz to 10 MHz   | 200 kHz                     |

| 10 MHz to 100 MHz | 2 MHz                       |

| 100 MHz to 1 GHz  | 5 MHz                       |

An example of a logarithmic frequency step (automotive applications) is given in Table A.3.

Table A.3 - Logarithmic frequency step

| Frequency<br>min. | Frequency<br>max. | Frequency step |

|-------------------|-------------------|----------------|

| 10 kHz            | 100 kHz           | 10 %           |

| 100 kHz           | 100 MHz           | 5 %            |

| 100 MHz           | 1 GHz             | 2 %            |

## Annex B (informative)

### Example of BCI test board and set-up

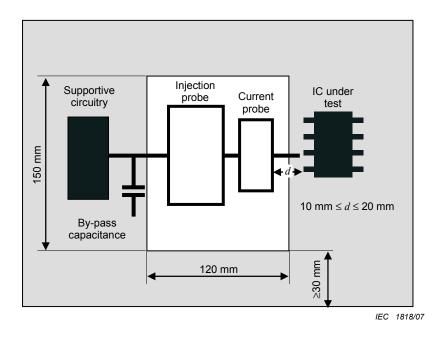

### B.1 Example of BCI test board and set-up

The BCI test set-up presented in this example uses injection probes, e.g. model F140 from FCC. The probes shall be able to inject high current values with a frequency range of 100 kHz to 1 GHz. Probes associated to a small current probe, e.g. 94111 model, allow the needs of the test to be covered.

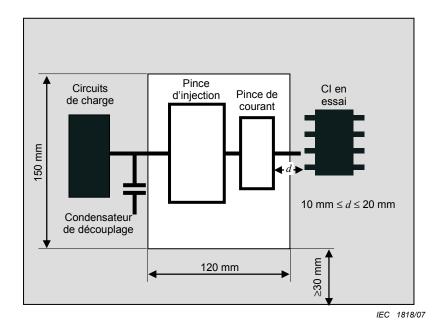

Due to the size of the two probes, 110 mm wide for both, a test board with an opening of 120 mm to put the two probes is required to allow the probes used in the lower frequency range

(< 500 MHz). Figure B.1 shows a general view of the test board. The recommended distance between probes is 10 mm.

Figure B.1 - General view

A hole, typical size:  $120 \text{ mm} \times 150 \text{ mm}$  shall permit placement of the two probes used in the lower frequencies, when using conventional BCI probes. Distance between probes may be limited to 1 mm.

When smaller injection and measurement probes are used to enable testing up to higher frequencies, a metal plate shall cover this hole in the test board with a hole exceeding these probes by 10 mm on each side. This sub-board shall make firm electrical contact at each edge of the test board.

The position of the current measurement probe should be close to the IC, required length less than 20 mm, which permit to measure the current injected in the IC. In this case, it is more appropriate to measure the surface currents induced in the differential lines than to create a discontinuity in the differential transmission line path. The distance between probes should be limited to 1 mm.

To minimize effects due to the test board, each side of the test board should be wide enough to be considered as a ground reference plane. Recommended size is minimum 30 mm, see Figure B.2.

Figure B.2 - Example of top view of the test board

The ground reference plane (GRP) is considered to be a solid ground plane. The disturbance current return path is considered through this GRP in the test set-up. Up to 1 GHz, this ground reference plane will have neglectable influence on the measurement set-up and can be disregarded.

The test board consists of at least two copper layers on an FR4 carrier material. The device under test, associated devices and tracks are placed on the topside. The bottom side is dedicated to a solid ground plane. A test board build-up is presented in Figure B.3.

Figure B.3 - Test board build-up

The test board bottom side, being a GND plane, is placed on the copper test fixture, connected to the ground reference plane as shown in Figure B.4. The copper test fixture shall be able to carry the BCI bottom test board conductively. The test fixture is placed on a copper ground reference plane (GRP). The shield of the injection probe has to be grounded underneath the copper test fixture to the GRP. It is recommended in order to ensure reproducibility, when large current probes have to be supported.

Figure B.4 - Test board and copper fixture

To fix the position of probes, a specific support is recommended. An example of that support is shown in Figure B.5. The probe support shall be made of non-conductive materials, with an  $\mathcal{E}_r$  of around 4.

Figure B.5 – Example of a non-conductive probes support fixture

# Annex C (informative)

### Example of RF test board and set-up

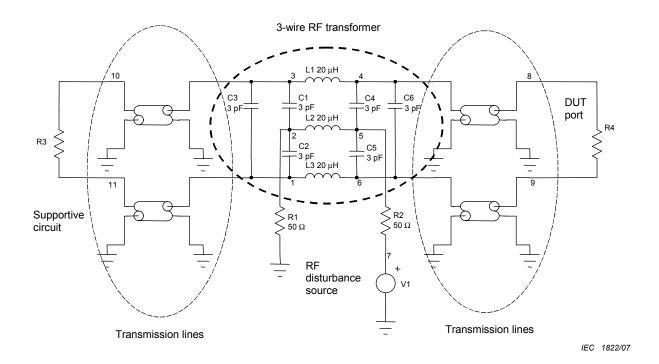

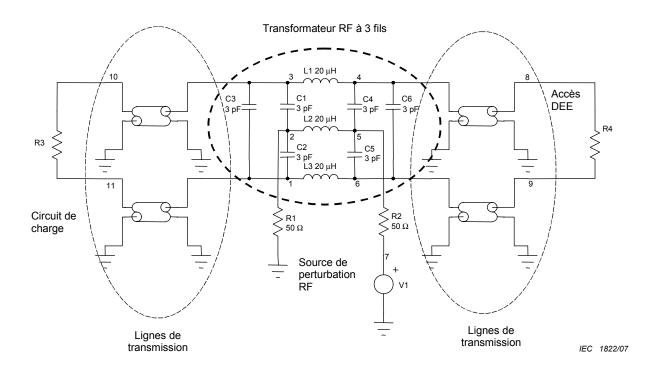

As an RF probe injection, a multi-wire RF transformer can be used, e.g. a SMD type. Coupling onto a differential transmission line with a ground plane underneath can be performed with a 3-wire RF transformer, and its frequency range can be extended by adding capacitive coupling (increase capacitances: C4/C5 in Figure C.1). The center wire is then used for injection where the off center wires are in series with the differential transmission line.

Figure C.1 - Compact RF coupling to differential IC ports

# LICENSED TO MECON Limited. - RANCHI/BANGALORE FOR INTERNAL USE AT THIS LOCATION ONLY, SUPPLIED BY BOOK SUPPLY BUREAU.

### **Bibliography**

- [1] ISO 11452-4:2005, Road vehicles Component test methods for electrical disturbances from narrowband radiated electromagnetic energy Part 4: Bulk current injection (BCI)

- [2] DO160D section 20.4: Conducted Immunity (CS) test

- [3] MIL-STD-461E: Requirements for the Control of Electromagnetic Interference Characteristics of Equipments and Subsystems (CS114)

### **SOMMAIRE**

| A۷   | VANT-PROPOS                                                                      | 21  |

|------|----------------------------------------------------------------------------------|-----|

| 1    | Domaine d'application et objet                                                   | 23  |

| 2    | Références normatives                                                            | 23  |

| 3    | Termes et définitions                                                            | 23  |

| 4    | Généralités                                                                      | 23  |

| 5    | Conditions d'essai                                                               | 24  |

|      | 5.1 Généralités                                                                  | 24  |

|      | 5.2 Matériel d'essai                                                             | 25  |

|      | 5.3 Carte d'essai                                                                | 26  |

| 6    | Modalités d'essai                                                                | 27  |

|      | 6.1 Champs électromagnétiques dangereux                                          |     |

|      | 6.2 Etalonnage de la limitation de puissance directe                             |     |

|      | 6.3 Essai BCI                                                                    |     |

| 7    | 6.4 Procédure de caractérisation du dispositif d'essai BCI                       |     |

| 7    | Rapport d'essai                                                                  | 30  |

| Anr  | nnexe A (informative) Exemples de niveaux d'essai et de choix de pas de fréquenc | e31 |

|      | nnexe B (informative) Exemple de carte d'essai BCI et mise en oeuvre             |     |

|      | nnexe C (informative) Exemple de carte d'essai RF et mise en oeuvre              |     |

|      | move a (miamatra) Example de carte à cocarrir et mos en coarre minimi            |     |

| Rih  | bliographiebliographie                                                           | 37  |

| טוט  | bliographie                                                                      |     |

| Fig  | gure 1 – Trajet du courant principal lors de l'utilisation du BCI                | 24  |

| Fig  | gure 2 – Schéma du montage d'essai BCI                                           | 25  |

|      | gure 3 – Exemple de carte d'essai, vue de dessus                                 |     |

| _    | gure 4 – Montage d'étalonnage                                                    |     |

| _    | gure 5 – Logigramme de la procédure d'essai BCI pour chaque échelon de fréquen   |     |

| _    | gure 6 – Montage d'essai de validation d'impédance                               |     |

| _    | gure B.1 – Vue générale                                                          |     |

| _    | gure B.2 – Exemple de vue de dessus de la carte d'essai                          |     |

| _    | gure B.3 – Assemblage de carte d'essai                                           |     |

| _    | gure B.4 – Carte d'essai et montage en cuivre                                    |     |

| _    | gure B.5 – Exemple de montage de support de pinces non conducteur                |     |

| _    | gure C.1 – Couplage RF compact aux accès différentiels du CI                     |     |

| ı ıy | gure O. 1 – Gouplage IVI compact aux acces umerenners du OI                      |     |

| Tab  | ableau A.1 – Niveaux de sévérité d'essai                                         | 31  |

| Tab  | ableau A.2 – Pas de fréquence linéaires                                          | 32  |

| Tah  | ableau A.3 – Pas de fréquence logarithmiques                                     | 32  |

### COMMISSION ÉLECTROTECHNIQUE INTERNATIONALE

### CIRCUITS INTÉGRÉS – MESURE DE L'IMMUNITÉ ÉLECTROMAGNÉTIQUE 150 kHz À 1 GHz –

Partie 3: Méthode d'injection de courant (BCI)

### **AVANT-PROPOS**

- 1) La Commission Electrotechnique Internationale (CEI) est une organisation mondiale de normalisation composée de l'ensemble des comités électrotechniques nationaux (Comités nationaux de la CEI). La CEI a pour objet de favoriser la coopération internationale pour toutes les questions de normalisation dans les domaines de l'électricité et de l'électronique. A cet effet, la CEI entre autres activités publie des Normes internationales, des Spécifications techniques, des Rapports techniques, des Spécifications accessibles au public (PAS) et des Guides (ci-après dénommés "Publication(s) de la CEI"). Leur élaboration est confiée à des comités d'études, aux travaux desquels tout Comité national intéressé par le sujet traité peut participer. Les organisations internationales, gouvernementales et non gouvernementales, en liaison avec la CEI, participent également aux travaux. La CEI collabore étroitement avec l'Organisation Internationale de Normalisation (ISO), selon des conditions fixées par accord entre les deux organisations.

- 2) Les décisions ou accords officiels de la CEI concernant les questions techniques représentent, dans la mesure du possible, un accord international sur les sujets étudiés, étant donné que les Comités nationaux intéressés sont représentés dans chaque comité d'études.

- 3) Les Publications de la CEI se présentent sous la forme de recommandations internationales et sont agréées comme telles par les Comités nationaux de la CEI. Tous les efforts raisonnables sont entrepris afin que la CEI s'assure de l'exactitude du contenu technique de ses publications; la CEI ne peut pas être tenue responsable de l'éventuelle mauvaise utilisation ou interprétation qui en est faite par un quelconque utilisateur final.

- 4) Dans le but d'encourager l'unification internationale, les Comités nationaux de la CEI s'engagent à appliquer de façon transparente, dans toute la mesure possible, les normes internationales de la CEI dans leurs normes nationales et régionales. Toutes divergences entre toutes Publications de la CEI et toutes publications nationales ou régionales correspondantes doivent être indiquées en termes clairs dans ces dernières.

- 5) La CEI n'a prévu aucune procédure de marquage valant indication d'approbation et n'engage pas sa responsabilité pour les équipements déclarés conformes à une de ses publications.

- 6) Tous les utilisateurs doivent s'assurer qu'ils sont en possession de la dernière édition de cette publication.

- 7) Aucune responsabilité ne doit être imputée à la CEI, à ses administrateurs, employés, auxiliaires ou mandataires, y compris ses experts particuliers et les membres de ses comités d'études et des Comités nationaux de la CEI, pour tout préjudice causé en cas de dommages corporels et matériels, ou de tout autre dommage de quelque nature que ce soit, directe ou indirecte, ou pour supporter les coûts (y compris les frais de justice) et les dépenses découlant de la publication ou de l'utilisation de cette Publication de la CEI ou de toute autre Publication de la CEI, ou au crédit qui lui est accordé.

- 8) L'attention est attirée sur les références normatives citées dans cette publication. L'utilisation de publications référencées est obligatoire pour une application correcte de la présente publication.

- 9) L'attention est attirée sur le fait que certains des éléments de la présente Publication de la CEI peuvent faire l'objet de droits de propriété intellectuelle ou de droits analogues. La CEI ne saurait être tenue pour responsable de ne pas avoir identifié de tels droits de propriété et de ne pas avoir signalé leur existence.

La Norme internationale CEI 62132-3 a été établie par le sous-comité 47A: Circuits intégrés, du comité d'études 47 de la CEI : Dispositifs à semi-conducteurs.

Le texte de cette norme est issu des documents suivants:

| FDIS         | Rapport de vote |

|--------------|-----------------|

| 47A/773/FDIS | 47A/776/RVD     |

Le rapport de vote indiqué dans le tableau ci-dessus donne toute information sur le vote ayant abouti à l'approbation de cette norme.

Cette publication a été rédigée selon les Directives ISO/CEI, Partie 2.

Une liste de toutes les parties de la série CEI 62132, sous le titre général *Circuits intégrés – mesure de l'immunité électromagnétique, 150 kHz à 1 GHz* est disponible sur le site Web de la CEI.

Le comité a décidé que le contenu de cette publication ne sera pas modifié avant la date de maintenance indiquée sur le site web de la CEI sous "http://webstore.iec.ch" dans les données relatives à la publication recherchée. A cette date, la publication sera

- · reconduite,

- · supprimée,

- · remplacée par une édition révisée, ou

- · amendée.

### CIRCUITS INTÉGRÉS – MESURE DE L'IMMUNITÉ ÉLECTROMAGNÉTIQUE 150 kHz À 1 GHz –

Partie 3: Méthode d'injection de courant (BCI)

### 1 Domaine d'application et objet

La présente partie de la CEI 62132 décrit une méthode d'essai d'injection de courant (BCI) en vue de mesurer l'immunité des circuits intégrés (CI) en présence de perturbations RF conduites, comme par exemple celles résultant de perturbations RF rayonnées. Cette méthode s'applique uniquement aux CI connectés sur des liaisons externes à la carte, par exemple sur des torons. Cette méthode d'essai est utilisée pour injecter un courant RF sur un ou plusieurs fils.

Cette norme établit une base commune pour l'évaluation des dispositifs à semi-conducteurs utilisés dans les matériels fonctionnant dans des environnements soumis à des signaux électromagnétiques à radiofréquences intempestifs.

### 2 Références normatives

Les documents de référence suivants sont indispensables pour l'application du présent document. Pour les références datées, seule l'édition citée s'applique. Pour les références non datées, la dernière édition du document de référence s'applique (y compris les éventuels amendements).

CEI 62132-1:2006, Circuits intégrés — Mesure de l'immunité électromagnétique, 150 kHz à 1 GHz — Partie 1: Conditions générales et définitions

### 3 Termes et définitions

Pour les besoins du présent document, les termes et les définitions donnés dans la CEI 62132-1 s'appliquent.

### 4 Généralités

La caractérisation de l'immunité (ou de la susceptibilité) RF d'un circuit intégré (CI) est essentielle pour définir la conception optimale du circuit imprimé d'une carte électronique, la définition de filtres et pour l'intégration ultérieure dans un système électronique. Ce document définit une méthode pour la mesure de l'immunité des CI aux RF induites par des perturbations électromagnétiques.

Cette méthode repose sur la méthode d'injection de courant (BCI) utilisée pour le matériel et les systèmes [1, 2, 3]. La méthode BCI simule le courant induit sous l'effet de signaux RF rayonnés directs couplés sur les fils et câbles des matériels et systèmes.

En général, dans les systèmes électroniques, les connexions de fils hors-carte ou les traces sur la carte à circuit imprimé servent d'antennes pour les champs électromagnétiques. Via ce trajet de couplage, ces champs électromagnétiques induiront des tensions et courants aux broches du CI et ils peuvent provoquer des perturbations de fonctionnement. Les CI sont souvent utilisés dans différentes configurations en fonction de leur application. Dans ce cas,

les niveaux d'immunité du matériel électronique sont étroitement liés à la capacité d'un CI à résister aux effets d'un champ électromagnétique.

Pour caractériser l'immunité RF d'un CI, le niveau de courant induit nécessaire à provoquer le dysfonctionnement de CI est mesuré. Le dysfonctionnement peut être classé de A à E selon les classes de performance définies dans la CEI 62132-1.

Un montage général pour la méthode d'injection de courant est présenté à la Figure 1.

Figure 1 – Trajet du courant principal lors de l'utilisation du BCIDeux pinces magnétiques avec blindage électrique sont fixées sur un fil ou plusieurs fils connectés au dispositif en essai. La première pince est utilisée pour l'injection de puissance RF qui induit  $I_{\text{disturbance}}$  sur les fils. La seconde pince est utilisée pour la surveillance du courant induit sur ces fils.

Le courant perturbateur circule dans une boucle formée par: un ou plusieurs fils, la ou les broches du CI, la broche  $V_{ss}$ , le retour de masse et les circuits de charge. Ces charges fournissent des éléments fonctionnels de CI comme source et/ou charge(s). Les circuits de charges sont directement raccordés au CI. Lorsque l'impédance RF équivalente des circuits de charge est supérieure à 50  $\Omega$ , alors un condensateur de découplage est recommandé. Le condensateur de découplage, à utiliser du côté des circuits de charge, peut également être nécessaire pour limiter la zone de la boucle dans laquelle le courant induit circule. Par défaut, un condensateur de découplage de 1 nF doit être utilisé. Cette valeur correspond à la capacitance d'un fil sur un toron ou un châssis. Toute exception à l'usage de ce condensateur de découplage (par exemple dans le cas où les performances fonctionnelles en seraient affectées) doit être signalée dans le rapport d'essai.

Le condensateur de découplage peut être complété par un découplage facultatif, voir la Figure 3, pour atteindre l'affaiblissement requis vers les circuits de charge. L'impédance du découplage est déterminée par l'immunité RF des circuits de charge. Elle ne doit pas exercer une influence défavorable sur le composant en essai, donc sur le résultat de l'essai.

Le courant perturbateur  $I_{\rm disturbance}$  induit dans le ou les fils circule à travers le CI et peut provoquer un défaut dans le fonctionnement du dispositif. Cette défaillance est définie par des paramètres nommés critères d'immunité, qui sont vérifiés par un système de contrôle et de surveillance.

### 5 Conditions d'essai

### 5.1 Généralités

Les conditions d'essai générales sont décrites dans la CEI 62132-1.

Au cours des essais d'immunité, le signal de perturbation est soit un signal à ondes entretenues (CW) soit un signal RF modulé en amplitude (AM). Le dispositif en essai (DEE) doit être exposé pour chaque pas de fréquence pendant un temps de maintien suffisant. Par

défaut, un signal RF modulé en amplitude utilisant un signal sinusoïdal de 1 kHz avec un indice de modulation de 80 % est recommandé pour les essais.

Quand un signal modulé en amplitude est utilisé, la puissance crête doit être la même que pour une onde sinusoïdale, voir la CEI 62132-1. Si d'autres types de modulation sont employés, ils doivent être notés dans le rapport d'essai du CI.

Le niveau des signaux perturbateurs requis pour l'essai d'immunité du CI dépend de l'environnement applicatif. Le Tableau A.1 de l'Annexe A donne certains exemples de valeurs typiques pour l'injection du courant perturbateur.

NOTE Sur exigences du client, pour satisfaire aux niveaux d'essais élevés, des composants de protection supplémentaires pourraient être utilisés pour permettre l'injection de courant élevé. Il faut laisser chargées toutes les autres broches, conformément à 6.4 de la CEI 62132-1.

### 5.2 Matériel d'essai

Le matériel d'essai comprend le matériel et les installations suivants:

- Plan de sol de référence

- Pince(s) d'injection de courant

- Pince(s) de mesure de courant

- Générateur de signaux RF avec options AM et CW

- Amplificateur(s) de puissance RF. Un amplificateur de puissance RF d'au moins 50 W est recommandé

- Wattmètre RF ou appareil de mesure équivalent, servant à mesurer la puissance directe (et réfléchie)

- Voltmètre RF ou appareil de mesure équivalent qui, avec la pince de mesure de courant, mesure le courant perturbateur induit

- Coupleur directif

- Matériel de surveillance du dispositif en essai (DEE) (facultatif: interface(s) optique(s))

Un schéma du montage d'essai est représenté à la Figure 2.

Figure 2 - Schéma du montage d'essai BCI

Une pince d'injection ou un ensemble de pinces capables de fonctionner sur la plage de fréquences d'essai est exigé pour coupler le signal de perturbation dans le circuit en essai (DEE). La pince d'injection est un transformateur.

NOTE Une interface optique peut être utilisée pour la surveillance de la réponse du DEE par rapport aux critères d'immunité donnés. L'utilisation de l'interface optique n'est pas obligatoire mais recommandée.

### 5.3 Carte d'essai

Un exemple de carte d'essai BCI est donné à la Figure 3. Cet exemple de carte d'essai BCI comporte une ouverture au milieu pour loger les deux pinces de courant.

La carte d'essai standard définie dans la CEI 62132-1 nécessite d'être modifiée pour répondre aux exigences de conditions d'essai BCI. Si la carte d'essai normalisée est utilisée, une connexion à la terre de faible impédance entre la carte d'essai normalisée et la carte d'essai BCI doit être effectuée. Joint, ressorts de contact ou vis multiples doivent être utilisés pour assurer le contact de la carte d'essai BCI avec l'assemblage de fixation d'essai BCI au niveau du trou central si le plan de masse de référence (GRP) n'est pas compris dans l'ensemble d'essai BCI.

IEC 1813/07

Figure 3 - Exemple de carte d'essai, vue de dessus

Le ou les fils auxquels le courant est injecté sont connectés à une extrémité à la ou aux broches CI, et à l'autre extrémité ils sont connectés aux circuits de charge. Les circuits de charge peuvent comprendre une charge, une alimentation ou une source de signaux nécessaires à faire fonctionner le dispositif en essai comme prévu.

La carte d'essai BCI comporte l'avantage de figer la position des pinces afin de fournir une mesure plus reproductible. Il convient que la taille des trous et la longueur des fils d'injection soient conçues au minimum pour la taille des pinces utilisées. Le trou doit avoir toutes ses dimensions d'au moins 10 mm de plus que celles des pinces, avec un maximum de 30 mm. En règle générale, la longueur des fils ne doit pas dépasser le quart de la longueur d'onde de la fréquence la plus grande de l'essai effectué avec la méthode BCI (≈ 75 mm dans l'air à 1 GHz).

La carte d'essai BCI est placée sur un dispositif d'essai en cuivre connecté au plan de masse de référence (GRP), comme décrit à l'Annexe C. La taille du GRP est typiquement celle d'une table augmentée d'un minimum de 0,1 m au-delà de l'encombrement du dispositif d'essai. Le dispositif d'essai en cuivre doit d'être suffisamment haut pour bien accepter les caractéristiques géométriques de la pince d'injection.

NOTE 1 Le plan de masse de référence peut être réalisé comme l'une des couches en cuivre de la carte d'essai BCI. Dans ce cas, le support d'essai en cuivre n'est plus nécessaire.

Le blindage de la pince d'injection et de la pince de mesure doit être mis à la terre avec une connexion courte en dessous du dispositif d'essai en cuivre au GRP.

NOTE 2 Les connecteurs de traversée coaxiaux peuvent être montés à travers le GRP (en dessous du dispositif d'essai en cuivre) pour être connectés directement aux pinces d'injection et de mesure du courant.

### 6 Modalités d'essai

### 6.1 Champs électromagnétiques dangereux

Des champs RF peuvent exister dans la zone d'essai. On doit veiller à ce que toutes les exigences pour limiter l'exposition des humains à l'énergie RF soient satisfaites. Il est préférable de réaliser l'essai d'immunité RF dans une enceinte ayant un blindage RF suffisant.

### 6.2 Etalonnage de la limitation de puissance directe

La puissance RF nécessaire en sortie du générateur et de l'amplificateur RF est déterminée lors de la procédure d'initialisation et de calibration de la pince d'injection de l'essai BCI. Dans ce processus, on établit le niveau de puissance RF directe (en mode ondes entretenues, CW) fournie à la pince d'injection de façon à générer le courant souhaité  $I_{\rm disturbance}$ .

L'étalonnage est réalisé dans le dispositif d'étalonnage, composé d'une section électriquement courte de ligne de transmission. La section courte permet la mesure du courant dans le conducteur central de la ligne, tandis que la pince d'injection de courant est fixée autour du conducteur central. Les sorties du dispositif sont chargées soit par un charge de 50  $\Omega$  d'au moins 0,5 W chacune, soit par un analyseur de spectre ou un voltmètre RF. La mesure de la tension établie aux bornes de l'impédance d'entrée du récepteur RF 50  $\Omega$  permet le calcul du courant circulant dans le conducteur central.

La procédure d'étalonnage doit être la suivante.

a) La pince d'injection doit être attachée au dispositif de calibration comme illustré sur la Figure 6. Fixer la pince en position centrale, à égale distance des flans du dispositif.

Le dispositif d'étalonnage sera terminé par une charge RF de 50  $\Omega$  à une extrémité et un récepteur RF de 50  $\Omega$  (analyseur de spectre, voltmètre, etc.) à l'autre extrémité, avec un atténuateur, si nécessaire.

Attention: utiliser une charge spécifiée pour la puissance envisagée.

NOTE Si le système se comporte linéairement, une charge de plus faible puissance peut être utilisée pendant l'étalonnage.

- b) Brancher les composants du matériel d'essai conformément aux indications de la Figure 4.

- c) Augmenter l'amplitude du signal d'essai à la pince d'injection jusqu'à ce que soit atteint le niveau de courant requis, tel que mesuré par le récepteur RF.

- d) Enregistrer la puissance RF directe nécessaire pour produire le courant souhaité  $I_{\rm disturbance}$ . Cette puissance RF directe est admise comme la limite de puissance directe maximale,  $P_{\rm limit}$ .

- e) Répéter les phases d) à e) pour chaque échelon de fréquence dans la plage de fréquences spécifiée.

Figure 4 - Montage d'étalonnage

### 6.3 Essai BCI

Dans la méthode d'essai d'immunité RF, une méthode par substitution avec la limitation de puissance et de courant est utilisée, ce qui permet de conserver un suivi de la limite de puissance RF à  $P_{\text{limit}}$ . La méthode de substitution est bien adaptée à la méthode d'essai de l'immunité des CI et est apparentée à la méthode ISO.

- Connecter les pinces de courant, les autres matériels d'essai et la carte d'essai.

- Alimenter le dispositif en essai (DEE) et vérifier le bon fonctionnement.

- Pour chaque fréquence d'essai, augmenter progressivement l'amplitude du signal au niveau de la pince d'injection jusqu'à ce que

- le niveau limite de courant de calibration  $I_{\text{disturbance}}$  soit atteint comme indiqué, en surveillant la sortie de la pince de courant de mesure, ou

- la puissance directe maximale étalonnée  $P_{\text{limit}}$  fournie à la pince d'injection soit atteinte. Egalement dans ce cas, bien que le niveau de courant injecté ne soit pas atteint, le niveau de courant maximal est enregistré, ou

- le niveau limite d'immunité du CI soit atteint. Si une défaillance de CI se produit ou si la limite pour  $I_{\rm disturbance}$  est satisfaite ou si le niveau de cible  $P_{\rm limit}$  est atteint, dans tous les cas, le courant surveillé et la puissance directe sont enregistrés.

NOTE 1 Dans le cadre d'une investigation, les détails concernant la détermination de l'immunité RF pourraient être enregistrés également.

NOTE 2 Si aucune impulsion transitoire n'est produite lors des changements de fréquence, l'amplitude RF à la fréquence suivante peut être choisie avec par exemple 10 dB de moins que le niveau précédent (en tenant compte de la dépendance du système à la fréquence) pour accélérer l'essai.

La procédure d'essai est donnée en détail dans le logigramme de la Figure 5. Ce logigramme ne s'applique qu'à un seul pas de fréquence.

Figure 5 – Logigramme de la procédure d'essai BCI pour chaque échelon de fréquenceProcédure de caractérisation du dispositif d'essai BCI

Afin de valider l'impédance de la carte d'essai BCI, une procédure de validation est requise.

Pour cette validation, tous les composants du montage d'essai doivent être utilisés, à l'exception du dispositif en essai. L'accès représenté par la ou les broches en essai de CI choisies est remplacé par une impédance de référence de 50  $\Omega$ . La Figure 6 montre un schéma du montage de validation.

Figure 6 - Montage d'essai de validation d'impédance

Au cours de la validation sur toute la plage de fréquences, on fixe la valeur du courant injecté. Une valeur de 10 mA pour le courant perturbateur injecté est recommandée. Pour chaque échelon de fréquence, la puissance incidente RF doit être notée.

La validation de la carte d'essai pourrait être caractérisée par une impédance de transfert définie par:

$$Z(f) = \frac{P_{\text{forward}}(f)}{I^2}$$

Dans le cas où plusieurs cartes d'essais sont utilisées, il convient que les valeurs Z(f) soient les mêmes. Cela permet de comparer les résultats d'essais d'immunité CI, effectués dans les mêmes conditions.

### 7 Rapport d'essai

Le rapport d'essai doit être préparé conformément aux exigences données dans la CEI 62132-1.

Il convient de décrire clairement dans le rapport d'essai les critères d'acceptation de l'immunité. Il convient de décrire également la configuration de la carte d'essai en détail pour reproduire les résultats.

Dans tous les cas, de tels paramètres comme le courant RF injecté  $I_{\rm disturbance}$ , la puissance RF incidente appliquée  $P_{\rm forward}$ , la puissance d'étalonnage  $P_{\rm limit}$  et le courant  $I_{\rm disturbance}$ , qui sont enregistrés au cours des processus d'étalonnage et de mesure, doivent être documentés dans le rapport d'essai.

Il convient d'énumérer dans le rapport d'essai les points critiques additionnels tels que la description de la carte d'essai, la valeur du condensateur de découplage (par défaut) et le circuit de découplage (si utilisé).

### Annexe A

(informative)

### Exemples de niveaux d'essai et de choix de pas de fréquence

### A.1 Valeurs typiques pour l'injection de courant

Le niveau de sévérité des signaux d'essai est le courant d'essai du courant d'essai étalonné appliqué. Ces niveaux de sévérité d'essai sont exprimés en valeur efficace en mA du signal de courant non modulé. Ces niveaux d'essai sont extraits des exigences d'essai dans les applications automobiles et avioniques. Les niveaux appliqués aux essais de CI doivent être fournis par l'utilisateur final et sont déterminés par la criticité de la ou des fonctions contrôlées. D'autres environnements applicatifs peuvent exiger des niveaux d'immunité moins sévères.

Des exemples de niveau de sévérité sont donnés dans le Tableau A.1. Les niveaux de courant injecté sont liés à la connexion de broches du Cl. La broche connectée au câblage externe pourrait être essayée avec les valeurs de courant les plus élevées, tandis qu'on pourrait permettre aux broches avec seulement des connexions locales de résister à des niveaux plus faibles. Il convient de détailler clairement les valeurs dans le plan d'essai Cl.

| Niveau de sévérité d'essai | Courant (onde continue) sans perte d'insertion                   |

|----------------------------|------------------------------------------------------------------|

| I                          | 50 mA                                                            |

| П                          | 100 mA                                                           |

| III                        | 200 mA                                                           |

| IV                         | 300 mA                                                           |

| V                          | Valeur spécifique convenue entre les utilisateurs de cette norme |

Tableau A.1 – Niveaux de sévérité d'essai

Dans le cas de l'utilisation de composants de protection supplémentaires placés sur la carte d'essai, pour résister à des valeurs de courant plus élevées, il convient d'ajouter dans le rapport d'essai CI une description de cet ensemble de circuits de protection et de sa disposition.

### A.2 Pas de fréquence

Le courant injecté induit par les perturbations électromagnétiques sur le fil est obtenu à des fréquences discrètes. L'intervalle entre 2 fréquences d'essai est défini comme le pas de fréquence.

Il convient que le choix des pas de fréquence couvre toute la gamme d'immunité du CI et évite des fréquences auxquelles des problèmes d'immunité pourraient se produire. En général, les causes premières des perturbations des CI sont liées aux résonances d'impédances. Ces dernières sont souvent très étroites sur la plage de fréquences et il convient que le pas de fréquence prenne en compte ce phénomène.

Il existe 2 façons de définir le pas de fréquence, avec une approche linéaire ou logarithmique.

Un exemple de pas de fréquence linéaire (applications automobile et aérospatiale) est donné au Tableau A.2.

Tableau A.2 – Pas de fréquence linéaires

| Bande de fréquences | Pas maximal de fréquence |

|---------------------|--------------------------|

| 10 kHz à 100 kHz    | 2 kHz                    |

| 100 kHz to 1 MHz    | 20 kHz                   |

| 1 MHz to 10 MHz     | 200 kHz                  |

| 10 MHz to 100 MHz   | 2 MHz                    |

| 100 MHz to 1 GHz    | 5 MHz                    |

Un exemple de pas de fréquence logarithmique (applications automobile) est donné au Tableau A.3.

Tableau A.3 – Pas de fréquence logarithmiques

| Fréquence<br>min. | Fréquence<br>max. | Pas de fréquence |

|-------------------|-------------------|------------------|

| 10 kHz            | 100 kHz           | 10 %             |

| 100 kHz           | 100 MHz           | 5 %              |

| 100 MHz           | 1 GHz             | 2 %              |

### Annexe B

(informative)

### Exemple de carte d'essai BCI et mise en oeuvre

### B.1 Exemple de carte d'essai BCI et mise en oeuvre

Le montage d'essai BCI présenté dans cet exemple utilise des pinces d'injection, par exemple le modèle F140 de FCC. Les pinces doivent être capables d'injecter des valeurs de courant élevé avec une plage de fréquences de 100 kHz – 1 GHz. Cette pince associée à une petite pince de courant, par exemple le modèle 94111, permet de couvrir les besoins de l'essai.

En raison de la taille des deux pinces, 110 mm de largeur pour les deux, une carte d'essai dotée d'une ouverture de 120 mm permettant de placer les deux pinces est requise pour couvrir la plage de fréquences plus basse (< 500 MHz). La Figure B.1 représente une vue générale de la carte d'essai. La distance recommandée entre les pinces est de 10 mm.

Figure B.1 - Vue générale

Un trou, taille typique: 120 mm  $\times$  150 mm doit permettre le placement des deux pinces, utilisées dans les fréquences plus basses, lors de l'utilisation de pinces BCI conventionnelles. La distance entre les pinces peut être limitée à 1 mm.

Lorsque des pinces d'injection et de mesure plus petites sont utilisées, pour permettre des essais jusqu'à des fréquences plus hautes, une plaque de métal doit couvrir ce trou dans la carte d'essai avec un trou laissant à ces pinces un espace de 10 mm de chaque côté. Cette sous-carte doit réaliser un très bon contact électrique sur chaque bord de la carte d'essai.

Il convient que la position de la pince de mesure du courant soit proche du CI, distance recommandée inférieure à 20 mm, ce qui permet de mesurer le courant injecté dans le CI. Dans ce cas, il est plus approprié de mesurer les courants de surface induits dans les lignes différentielles plutôt que de créer une discontinuité dans le trajet de ligne de transmission différentielle. Il convient que la distance entre les pinces soit limitée à 1 mm.

Pour réduire les effets dus à la carte d'essai, il convient que chaque côté de la carte d'essai soit assez large pour être considéré comme un plan de masse de référence. La taille recommandée est de 30 mm minimum, voir la Figure B.2.

Figure B.2 – Exemple de vue de dessus de la carte d'essai

Le plan de masse de référence (GRP) est considéré comme étant un plan de masse solide. Le chemin de retour du courant perturbateur est pris en compte à travers ce GRP du montage d'essai. Jusqu'à 1 GHz, ce plan de masse de référence aura une influence négligeable sur le montage de mesure et il peut être négligé.

Cette carte d'essai est constituée d'au moins deux couches de cuivre sur un matériau isolant type FR4. Le dispositif en essai, les dispositifs et les pistes associés sont placés sur la face supérieure. La face inférieure est dédiée à un plan de masse solide. Un empilage des couches de la carte d'essai est présenté à la Figure B.3.

Figure B.3 - Assemblage de carte d'essai

La face inférieure de la carte d'essai, étant un plan de masse (GND), est placée sur un support en cuivre, connectée au plan de masse de référence comme l'illustre la Figure B.4. Le support en cuivre doit être en contact électrique avec la face inférieure de la carte d'essai BCI pour assurer une bonne conductivité électrique. Le support d'essai est placé sur un plan de masse de référence en cuivre (GRP). L'écran de la pince d'injection doit être relié à la masse sous le montage d'essai en cuivre au GRP. Cela est recommandé pour assurer la reproductibilité lorsque des pinces de courant de grande taille doivent être utilisées.

Figure B.4 - Carte d'essai et montage en cuivre

Pour garantir la position des pinces, un support spécifique est recommandé. Un exemple de ce support est illustré à la Figure B.5. Le support de pince doit être réalisé dans un matériau non conducteur, avec un  $\mathcal{E}_r$  de l'ordre de 4.

Figure B.5 – Exemple de montage de support de pinces non conducteur

# Annexe C (informative)

### Exemple de carte d'essai RF et mise en œuvre

Comme pince d'injection RF, on peut utiliser un transformateur RF multifilaire, par exemple un modèle pour montage en surface. Le couplage sur une ligne de transmission différentielle, avec en dessous un plan de sol, peut être réalisé avec un transformateur RF à 3 fils et sa plage de fréquences peut être étendue en ajoutant un couplage capacitif (condensateurs d'accroissement: C4/C5 à la Figure C.1) Le fil du centre est ensuite utilisé pour l'injection alors que les fils excentrés sont en série avec la ligne de transmission différentielle.

Figure C.1 - Couplage RF compact aux accès différentiels du CI

# LICENSED TO MECON Limited. - RANCHI/BANGALORE FOR INTERNAL USE AT THIS LOCATION ONLY, SUPPLIED BY BOOK SUPPLY BUREAU.

### **Bibliographie**

- [1] ISO 11452-4:2005, Véhicules routiers Méthodes d'essai d'un équipement soumis à des perturbations électriques par rayonnement d'énergie électromagnétique en bande étroite Partie 4 : Méthodes d'injection de courant (BCI)

- [2] DO160D section 20.4: Conducted Immunity (CS) test

- [3] MIL-STD-461E: Requirements for the Control of Electromagnetic Interference Characteristics of Equipments and Subsystems (CS114)

# INTERNATIONAL ELECTROTECHNICAL COMMISSION

3, rue de Varembé P.O. Box 131 CH-1211 Geneva 20 Switzerland

Tel: + 41 22 919 02 11 Fax: + 41 22 919 03 00 info@iec.ch www.iec.ch