IEC 62026-2:2008(E)

Edition 2.0 2008-01

# INTERNATIONAL STANDARD

Low-voltage switchgear and controlgear – Controller-device interfaces (CDIs) – Part 2: Actuator sensor interface (AS-i)

# THIS PUBLICATION IS COPYRIGHT PROTECTED

#### Copyright © 2008 IEC, Geneva, Switzerland

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from either IEC or IEC's member National Committee in the country of the requester.

If you have any questions about IEC copyright or have an enquiry about obtaining additional rights to this publication, please contact the address below or your local IEC member National Committee for further information.

IEC Central Office 3, rue de Varembé CH-1211 Geneva 20 Switzerland Email: inmail@iec.ch Web: www.iec.ch

#### About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes International Standards for all electrical, electronic and related technologies.

#### **About IEC publications**

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the latest edition, a corrigenda or an amendment might have been published.

Catalogue of IEC publications: <u>www.iec.ch/searchpub</u>

The IEC on-line Catalogue enables you to search by a variety of criteria (reference number, text, technical committee,...). It also gives information on projects, withdrawn and replaced publications.

IEC Just Published: <u>www.iec.ch/online\_news/justpub</u>

Stay up to date on all new IEC publications. Just Published details twice a month all new publications released. Available on-line and also by email.

Electropedia: <u>www.electropedia.org</u>

The world's leading online dictionary of electronic and electrical terms containing more than 20 000 terms and definitions in English and French, with equivalent terms in additional languages. Also known as the International Electrotechnical Vocabulary online.

Customer Service Centre: <u>www.iec.ch/webstore/custserv</u>

If you wish to give us your feedback on this publication or need further assistance, please visit the Customer Service Centre FAQ or contact us:

Email: <u>csc@iec.ch</u> Tel.: +41 22 919 02 11 Fax: +41 22 919 03 00

Edition 2.0 2008-01

# INTERNATIONAL STANDARD

Low-voltage switchgear and controlgear – Controller-device interfaces (CDIs) – Part 2: Actuator sensor interface (AS-i)

INTERNATIONAL ELECTROTECHNICAL COMMISSION

ISBN 2-8318-9512-X

ICS 29.130.20

# CONTENTS

- 2 -

| FOI | REWC                                              | DRD                                                      | 7   |  |

|-----|---------------------------------------------------|----------------------------------------------------------|-----|--|

| 1   | Scop                                              | e and object                                             | 9   |  |

| 2   |                                                   | ative references                                         |     |  |

| 3   | Term                                              | s, definitions, symbols and abbreviations                | 11  |  |

| 4   | Classification                                    |                                                          |     |  |

|     | 4.1                                               | Overview                                                 |     |  |

|     | 4.2                                               | Components and interfaces                                |     |  |

| 5   | Characteristics                                   |                                                          |     |  |

|     | 5.1                                               | Overview                                                 |     |  |

|     | 5.2                                               | Signal characteristics                                   |     |  |

|     | 5.3                                               | Power and data distribution                              |     |  |

|     | 5.4                                               | AS-i topology and other components                       | 25  |  |

|     | 5.5                                               | Communication                                            |     |  |

|     | 5.6                                               | AS-i single transactions                                 |     |  |

|     | 5.7                                               | AS-i combined transactions                               | 42  |  |

|     | 5.8                                               | AS-i error detection                                     | 59  |  |

| 6   | Produ                                             | uct information                                          | 60  |  |

|     | 6.1                                               | Instructions for installation, operation and maintenance | 60  |  |

|     | 6.2                                               | Profiles                                                 | 60  |  |

|     | 6.3                                               | Marking                                                  | 61  |  |

| 7   | Normal service, mounting and transport conditions |                                                          |     |  |

|     | 7.1                                               | Normal service conditions                                | 62  |  |

|     | 7.2                                               | Conditions during transport and storage                  | 62  |  |

|     | 7.3                                               | Mounting                                                 | 63  |  |

| 8   | Cons                                              | tructional and performance requirements                  | 63  |  |

|     | 8.1                                               | AS-i transmission medium                                 | 63  |  |

|     | 8.2                                               | AS-i power supply                                        | 66  |  |

|     | 8.3                                               | AS-i repeater and other components                       | 68  |  |

|     | 8.4                                               | AS-i slave                                               | 69  |  |

|     | 8.5                                               | AS-i master                                              | 85  |  |

|     | 8.6                                               | Electromagnetic compatibility (EMC)                      |     |  |

| 9   | Tests                                             | 3                                                        | 90  |  |

|     | 9.1                                               | Kinds of tests                                           | 90  |  |

|     | 9.2                                               | Test of transmission medium                              |     |  |

|     | 9.3                                               | Test of the AS-i power supply                            |     |  |

|     | 9.4                                               | Test of an AS-i repeater and other components            |     |  |

|     | 9.5                                               | Test of an AS-i slave                                    |     |  |

|     | 9.6                                               | Test of a AS-i master                                    | 120 |  |

| Anr | nex A                                             | (normative) Slave profiles                               | 135 |  |

| Anr | nex B                                             | (normative) Master profiles                              | 213 |  |

| Fig | ure 1 -                                           | - AS-i components and interfaces                         | 19  |  |

| Fig | ure 2 ·                                           | - Transmission coding                                    | 21  |  |

| Figure 3 – Receiver requirements                                                                                             | 23 |

|------------------------------------------------------------------------------------------------------------------------------|----|

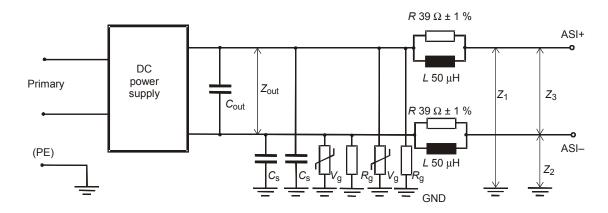

| Figure 4 – AS-i power supply                                                                                                 | 24 |

| Figure 5 – Equivalent schematic of symmetrization and decoupling circuit                                                     | 25 |

| Figure 6 – Model of the AS-i transmission medium                                                                             | 26 |

| Figure 7 – Transactions                                                                                                      | 28 |

| Figure 8 – Master and slave pause as viewed from master/slave point of view                                                  | 28 |

| Figure 9 – Representation of the master pause                                                                                | 29 |

| Figure 10 – Structure of a master request                                                                                    | 31 |

| Figure 11 – Structure of a slave response                                                                                    | 34 |

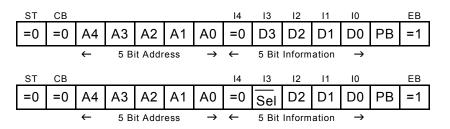

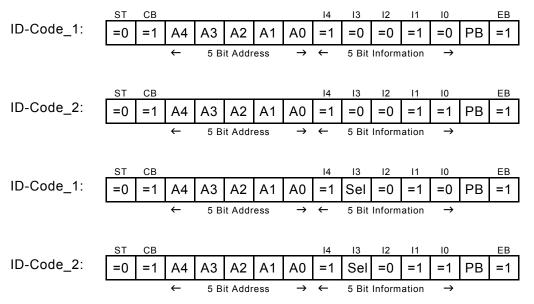

| Figure 12 – Structure of a data exchange request (top: standard address mode; bottom: extended address mode)                 | 34 |

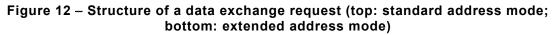

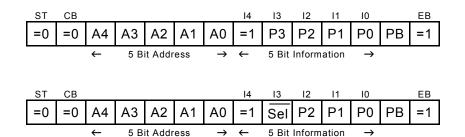

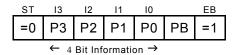

| Figure 13 – Structure of the slave response (Data_Exchange)                                                                  | 35 |

| Figure 14 – Structure of the Write_Parameter request (top: standard addressing mode; bottom: extended addressing mode)       | 35 |

| Figure 15 – Structure of the slave response (Write_Parameter)                                                                | 35 |

| Figure 16 – Structure of the Address_Assignment request                                                                      | 36 |

| Figure 17 – Structure of the slave response (Address_Assignment)                                                             | 36 |

| Figure 18 – Structure of the Write_Extended_ID-Code_1 request                                                                | 36 |

| Figure 19 – Structure of the slave response (Write_Extended_ID-Code_1)                                                       | 36 |

| Figure 20 – Structure of the Reset_Slave request (top: standard addressing mode; bottom: extended addressing mode)           | 37 |

| Figure 21 – Structure of the slave response (Reset_Slave)                                                                    | 37 |

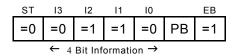

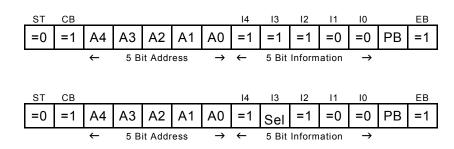

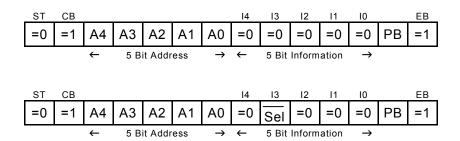

| Figure 22 – Structure of the Delete_Address request (top: standard addressing mode; bottom: extended addressing mode)        | 37 |

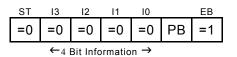

| Figure 23 – Structure of the slave response (Delete_Address)                                                                 |    |

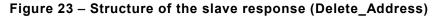

| Figure 24 – Structure of the Read_I/O_Configuration request top: standard addressing mode; bottom: extended addressing mode) |    |

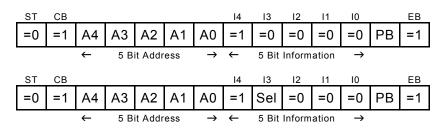

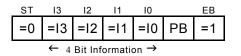

| Figure 25 – Structure of the slave response (Read_I/O_Configuration)                                                         |    |

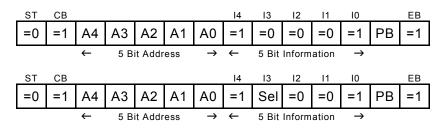

| Figure 26 – Structure of Read_Identification_Code request (top: standard addressing mode; bottom: extended addressing mode)  | 39 |

| Figure 27 – Structure of the slave response (Read_Identification_Code)                                                       |    |

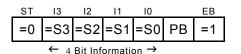

| Figure 28 – Structure of Read_Extended_ID-Code_1/2 Request (top: standard addressing mode; bottom: extended addressing mode) |    |

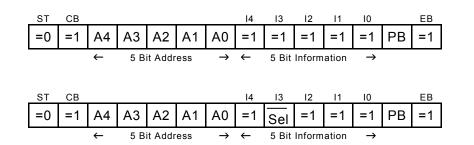

| Figure 29 – Structure of the slave response Read_Extended_ID-Code_1/2                                                        | 40 |

| Figure 30 – Structure of Read_Status request (top: standard addressing mode;<br>bottom: extended addressing mode)            |    |

| Figure 31 – Structure of the slave response (Read_Status)                                                                    |    |

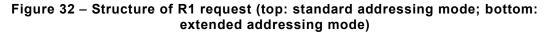

| Figure 32 – Structure of R1 request (top: standard addressing mode; bottom:<br>extended addressing mode)                     |    |

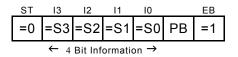

| Figure 33 – Structure of the slave response (R1)                                                                             |    |

| Figure 34 – Structure of the Broadcast (Reset) request                                                                       |    |

| Figure 35 – Definition of the I/O data bits in combined transaction type 1                                                   |    |

| Figure 36 – Definition of the parameter bits in combined transaction type 1                                                  |    |

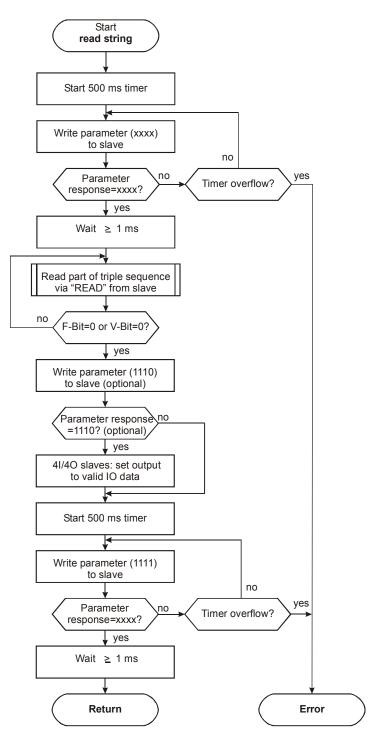

| Figure 37 – Function sequence to Read ID, Read Diagnosis, Read Parameter in                                                  |    |

| combined transaction type 1                                                                                                  | 46 |

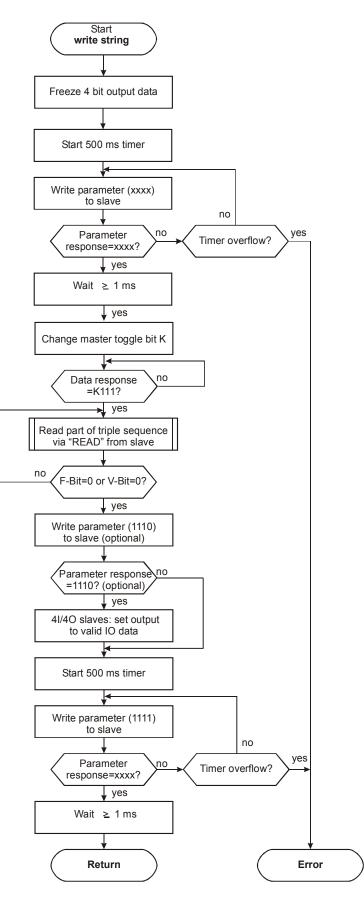

| Figure 38 – Function sequence to Write Parameter in combined transaction type 1                                                                                 | 47  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

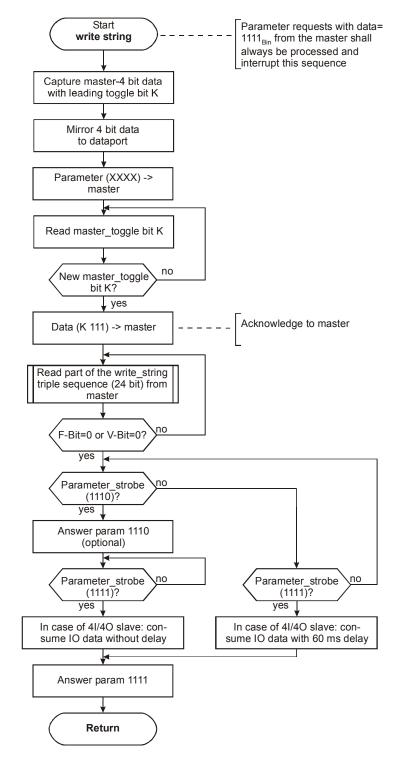

| Figure 39 – Behaviour of the slave receiving a complete parameter string from the master in combined transaction type 1                                         | 48  |

| Figure 40 – Definition of the I/O data bits in combined transaction type 2                                                                                      | 49  |

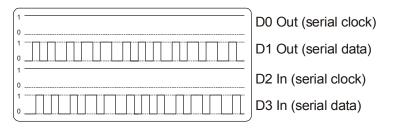

| Figure 41 – Typical combined transaction type 2 signals as viewed by an oscilloscope (both data channels run idle)                                              | 50  |

| Figure 42 – Typical combined transaction type 2 signals (the master transmits the byte 10101011 <sub>Bin</sub> , the slave transmits 01110101 <sub>Bin</sub> ): | 51  |

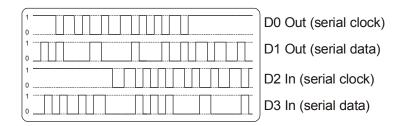

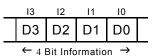

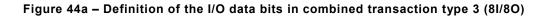

| Figure 43 – Definition of the I/O data bits in combined transaction type 3 (4I/4O)                                                                              | 52  |

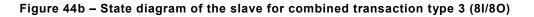

| Figure 44 – Definition and state diagram of the slave for combined transaction type 3                                                                           | 53  |

| Figure 45 – Definition of the I/O data bits in combined transaction type 4                                                                                      | 55  |

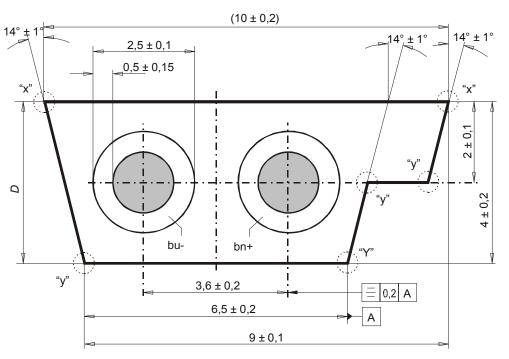

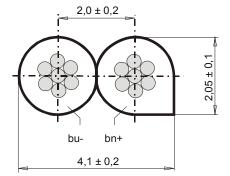

| Figure 46– AS-i standard cable for field installation                                                                                                           | 63  |

| Figure 47 – AS-i cabinet cable                                                                                                                                  | 64  |

| Figure 48 – Equivalent schematic of decoupling circuit                                                                                                          | 68  |

| Figure 49 – Decoupling circuit using a transformer                                                                                                              | 68  |

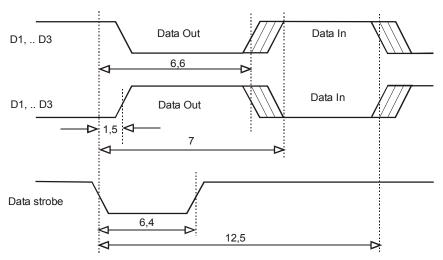

| Figure 50 – Typical timing diagram for bidirectional input/outputs (D1, D3 = voltage level at respective data port)                                             | 70  |

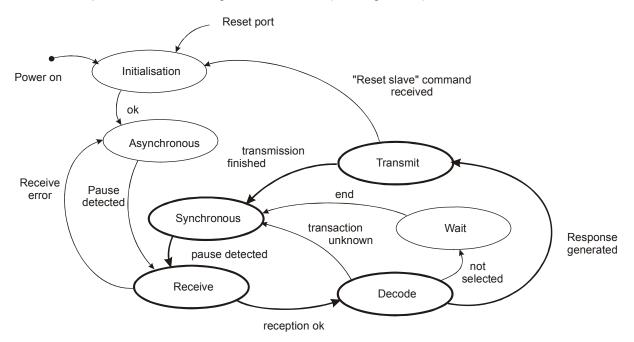

| Figure 51 – Main state diagram of an AS-i slave                                                                                                                 | 73  |

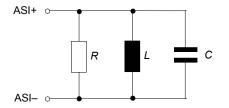

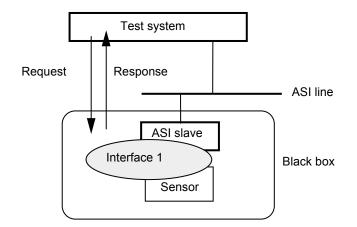

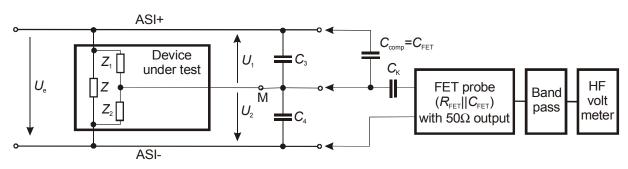

| Figure 52 – Equivalent circuit of a slave for frequencies in the range of 50 kHz to 300 kHz                                                                     | 81  |

| Figure 53 – A slave with C3 to compensate for Z1 = Z2                                                                                                           | 82  |

| Figure 54 – Status indication on slaves                                                                                                                         | 84  |

| Figure 55 – Structure of an AS-i master                                                                                                                         | 86  |

| Figure 56 – Impedances of the master                                                                                                                            | 87  |

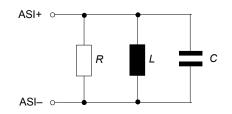

| Figure 57 – Equivalent circuit of a master for frequencies in the range of 50 kHz to 300 kHz                                                                    | 87  |

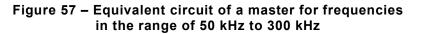

| Figure 58 – Transmission control state machine                                                                                                                  | 88  |

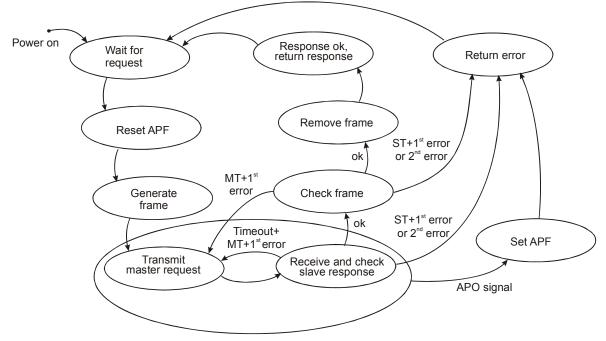

| Figure 59 – AS-i interfaces                                                                                                                                     | 91  |

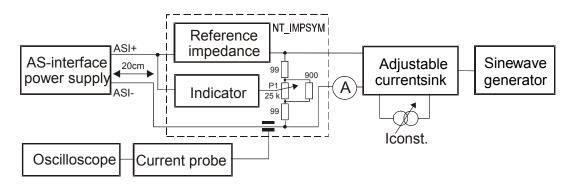

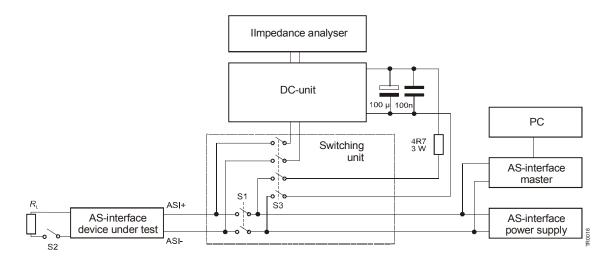

| Figure 60 – Test circuit for impedance measurement                                                                                                              | 92  |

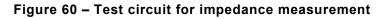

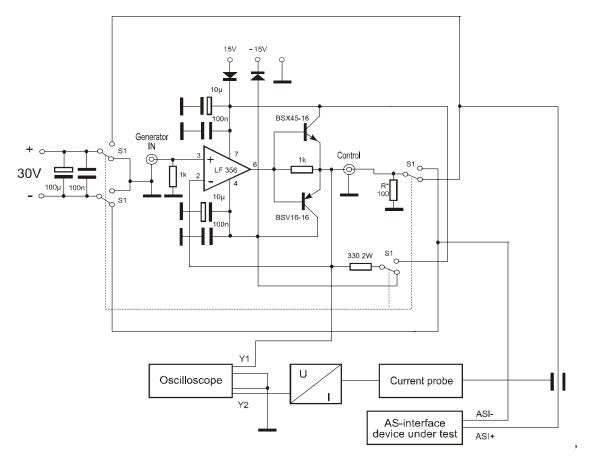

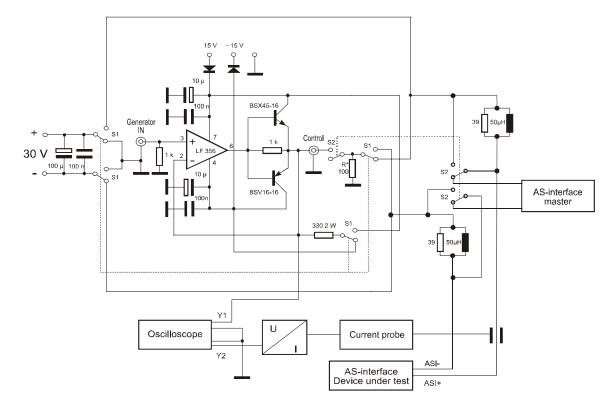

| Figure 61 – Adjustable current sink (test circuit: NT_MODSENKE)                                                                                                 | 93  |

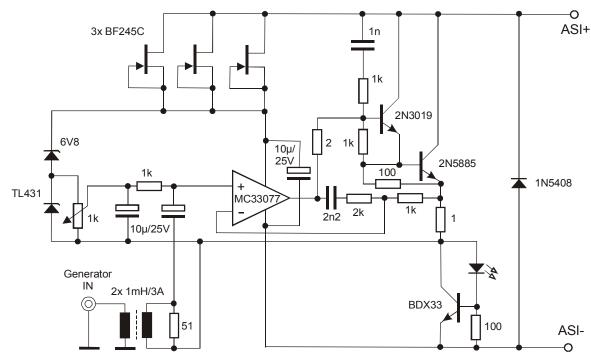

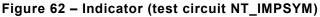

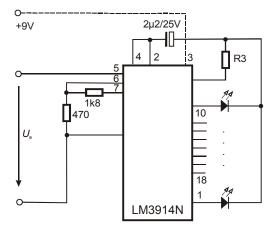

| Figure 62 – Indicator (test circuit NT_IMPSYM)                                                                                                                  | 93  |

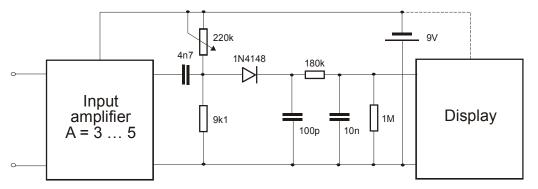

| Figure 63 – Display (part of test circuit NT_IMPSYM)                                                                                                            | 94  |

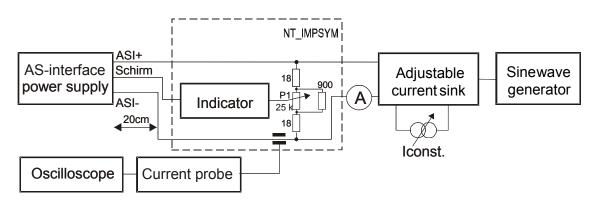

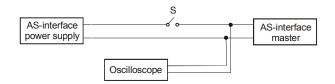

| Figure 64 – Test set-up for symmetry measurement                                                                                                                | 94  |

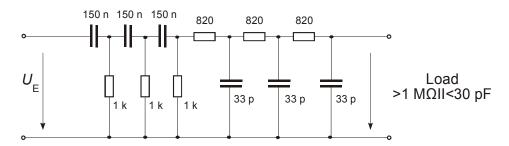

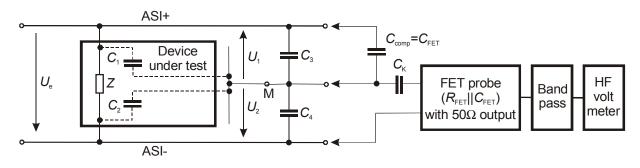

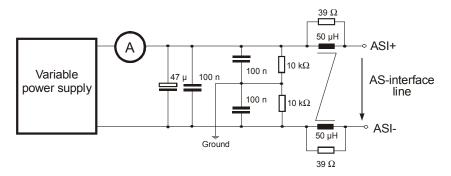

| Figure 65 – Test circuit for noise emission                                                                                                                     | 96  |

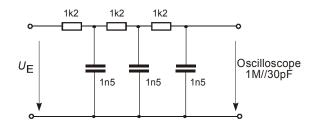

| Figure 66 – Filter A (low-pass filter 0 Hz to 10 kHz)                                                                                                           | 96  |

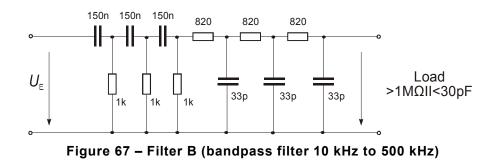

| Figure 67 – Filter B (bandpass filter 10 kHz to 500 kHz)                                                                                                        | 96  |

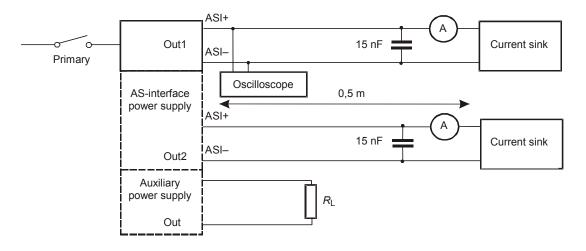

| Figure 68 – Test circuit for start-up behaviour                                                                                                                 | 97  |

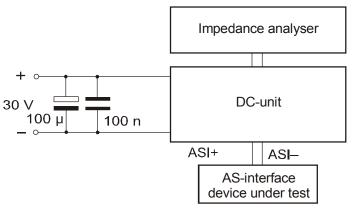

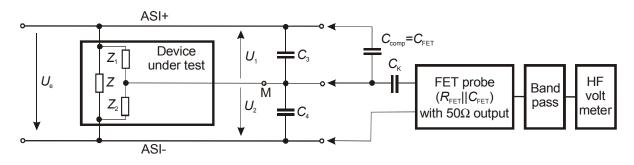

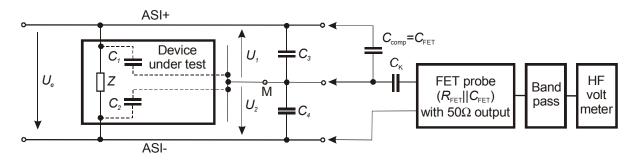

| Figure 69 – Measurement set-up for impedance measurement                                                                                                        | 99  |

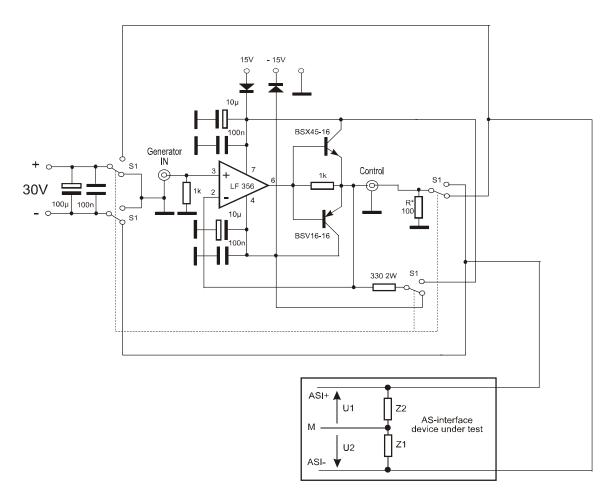

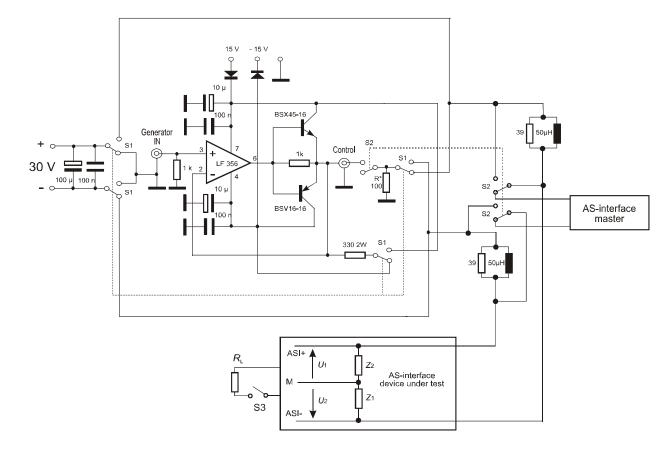

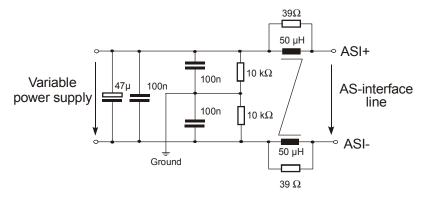

| Figure 70 – Test circuit for symmetry measurement                                                                                                               | 101 |

| Figure 71 – Test circuit (detail 1)                                                                                                                             | 102 |

| Figure 72 – Test circuit (detail 2)                                                                                                                             | 102 |

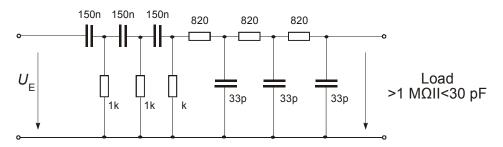

| Figure 73 – Bandpass (10 kHz 500 kHz)                                                                                                                           | 102 |

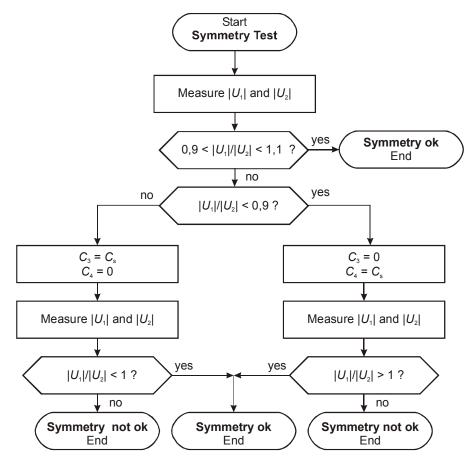

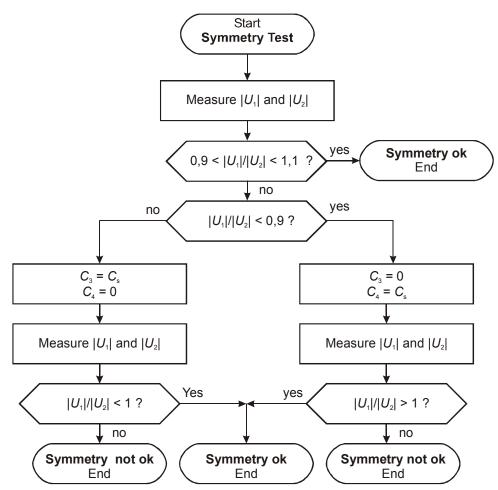

| Figure 74 – Procedure for symmetry test                                                                                                                         | 103 |

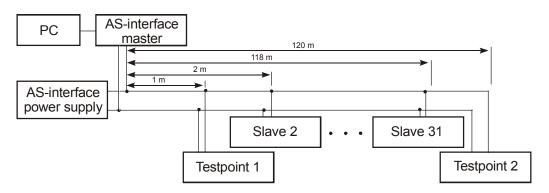

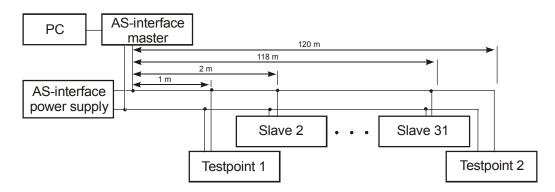

| Figure 75 – Test circuit for interoperability in AS-i networks                                                                                                  | 104 |

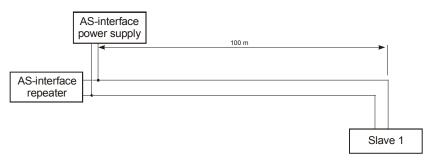

| Figure 76 – Additional test circuit 1 for repeater                                                                                                              | 105 |

| Figure 77 – Additional test circuit 2 for repeater                                    | 105 |

|---------------------------------------------------------------------------------------|-----|

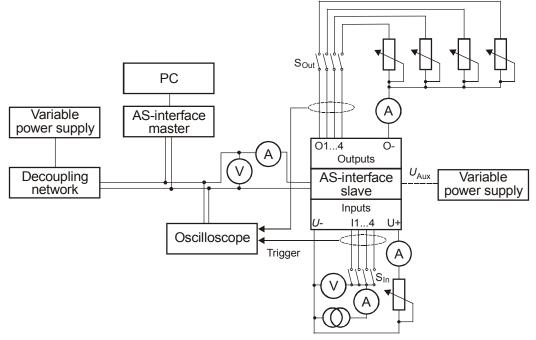

| Figure 78 – Test circuit                                                              | 106 |

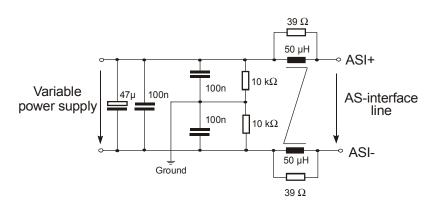

| Figure 79 – Test circuit decoupling network                                           | 107 |

| Figure 80 – Test circuit                                                              | 108 |

| Figure 81 – Test circuit decoupling network                                           | 108 |

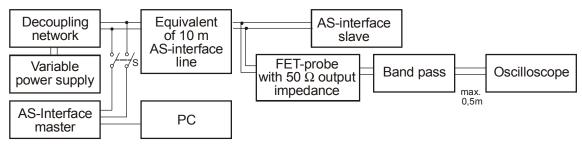

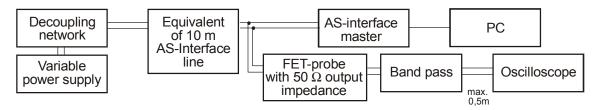

| Figure 82 – Test circuit (equivalent of 10 m AS-i line)                               | 108 |

| Figure 83 – Test circuit (bandpass 10 kHz to 500 kHz)                                 | 109 |

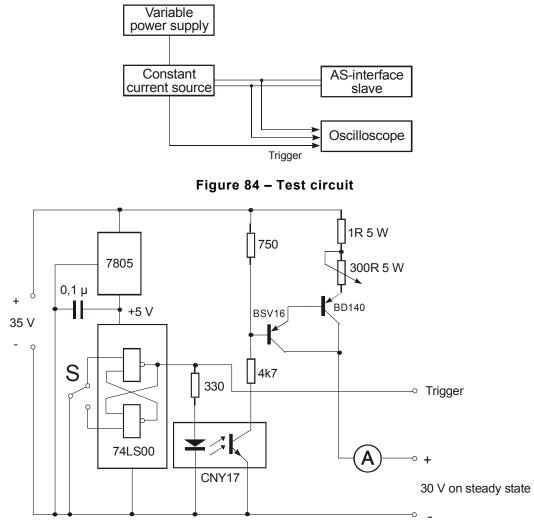

| Figure 84 – Test circuit                                                              | 110 |

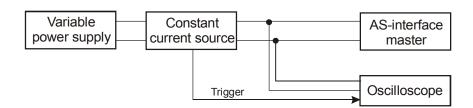

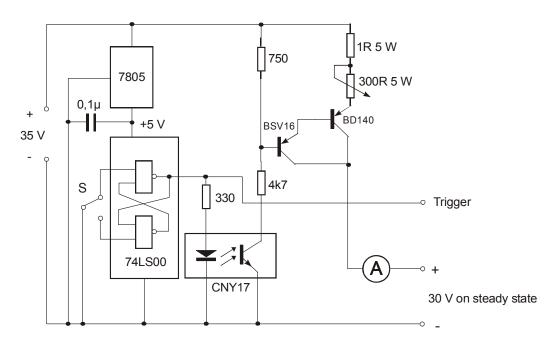

| Figure 85 – Constant current source                                                   | 110 |

| Figure 86 – Test circuit                                                              | 112 |

| Figure 87 – Test circuit                                                              | 114 |

| Figure 88 – Test circuit (detail 1)                                                   | 114 |

| Figure 89 – Test circuit (detail 2)                                                   | 115 |

| Figure 90 – Procedure for symmetry test                                               | 116 |

| Figure 91 – Test circuit AS-i network                                                 | 117 |

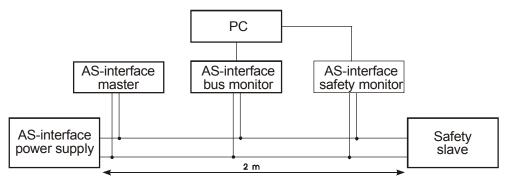

| Figure 92 – Test circuit for safety related slaves                                    | 118 |

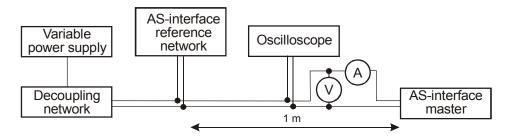

| Figure 93 – Test circuit for current consumption test                                 | 120 |

| Figure 94 – Decoupling network, ammeter and power supply                              | 120 |

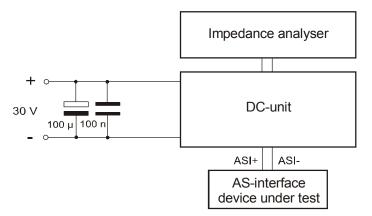

| Figure 95 – Test circuit noise emission AS-i master                                   | 121 |

| Figure 96 – Decoupling network                                                        | 122 |

| Figure 97 – Bandpass 10 kHz to 500 kHz                                                | 122 |

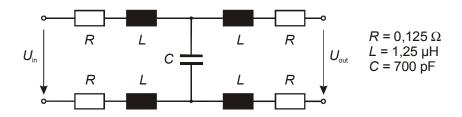

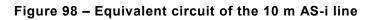

| Figure 98 – Equivalent circuit of the 10 m AS-i line                                  | 122 |

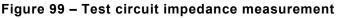

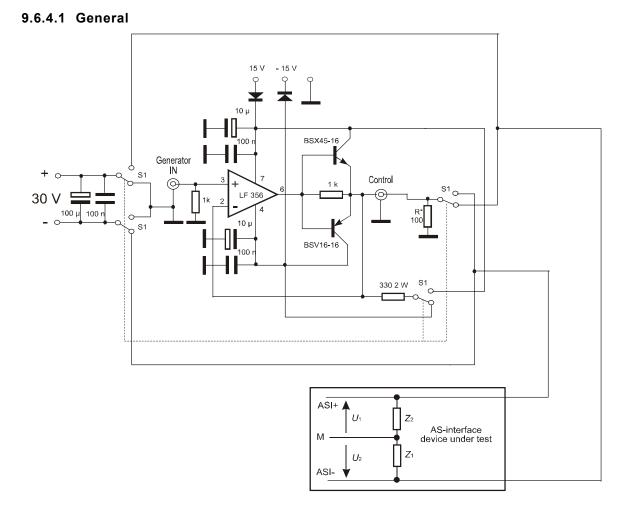

| Figure 99 – Test circuit impedance measurement                                        | 125 |

| Figure 100 – Master connection for symmetry measurement                               | 126 |

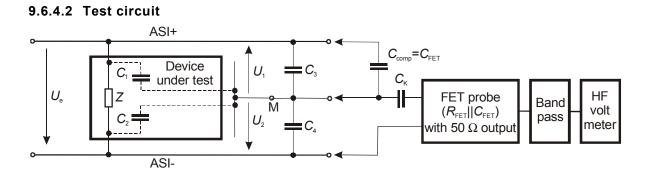

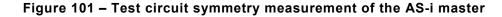

| Figure 101 – Test circuit symmetry measurement of the AS-i master                     | 127 |

| Figure 102 – Bandpass 10 kHz to 500 kHz                                               | 127 |

| Figure 103 – Procedure for symmetry test                                              | 128 |

| Figure 104 – Test circuit – On-delay                                                  | 129 |

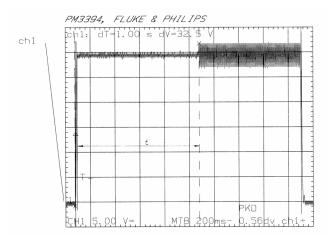

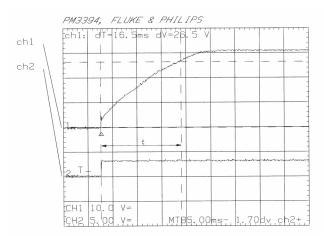

| Figure 105 – Oscillogram on-delay (example)                                           | 129 |

| Figure 106 – Block circuit diagram current consumption measurement of the AS-i master | 120 |

| Figure 107 – Constant current source with trigger output (KONST_I)                    |     |

| Figure 108 – Oscillogram current consumption (example)                                |     |

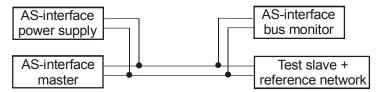

| Figure 109 – Test circuit for checking start-up operation                             |     |

| Figure 110 – Test circuit for checking normal operation                               |     |

| Figure 111 – Test circuit                                                             |     |

| Figure A.1 – Definition of the extended ID2 code bits for S-7.3                       |     |

| Figure A.2 – Definition of the extended ID2 code bits for S-7.4                       |     |

| Figure A.2 – Definition of the extended 1D2 code bits for 3-7.4                       |     |

|                                                                                       |     |

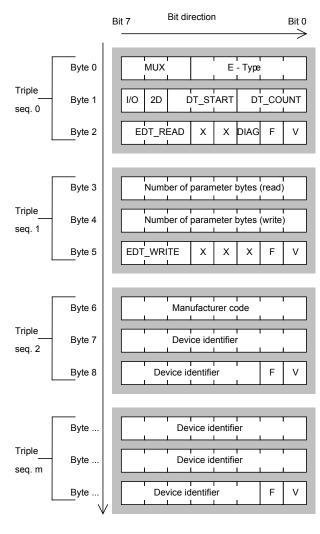

| Figure A.4 – Data structure of the diagnostic string (S-7.4)                          |     |

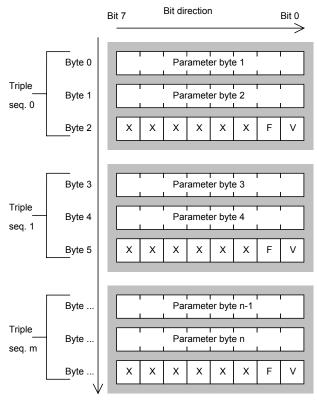

| Figure A.5 – Data structure of the parameter string (S-7.4)                           |     |

| Figure A.6 – Definition of the extended ID1 code bits for S-7.A.8 and S-7.A.9         |     |

| Figure A.7 – Connection of mechanical switches                                        | 211 |

| Table 1 – AS-i power supply specifications                                                              | 24  |

|---------------------------------------------------------------------------------------------------------|-----|

| Table 2 – Symmetrization and decoupling circuit specifications                                          | 25  |

| Table 3 – Bit strings of the master requests                                                            | 31  |

| Table 4 – Master requests (standard addressing mode)                                                    | 32  |

| Table 5 – Master requests in the extended addressing mode                                               | 33  |

| Table 6 – Bit strings of the slave responses                                                            | 34  |

| Table 7 – I/O Codes (IN = Input; OUT = Output; TRI = Tristate; I/O = Input/Output or Bidirectional (B)) | 39  |

| Table 8 – List of combined transaction types                                                            | 42  |

| Table 9 – Data transfer from slave to master in combined transaction type 1                             | 44  |

| Table 10 – Data transfer from master to slave in combined transaction type 1                            | 44  |

| Table 11 – Definition of serial clock and data in combined transaction type 2                           | 50  |

| Table 12 – Data transfer in combined transaction type 2                                                 | 50  |

| Table 13 – Definition of the ID2 code in combined transaction type 5                                    | 56  |

| Table 14 – Input states of safety related input slaves                                                  | 59  |

| Table 15 – Connection and wiring identification                                                         | 61  |

| Table 16 – AS-i power supply marking                                                                    | 62  |

| Table 17 – Environmental conditions (minimum conditions)                                                | 66  |

| Table 18 – General requirements for an AS-i power supply                                                | 67  |

| Table 19 – Physical and logical ports of an AS-i slave                                                  | 70  |

| Table 20 – Limits for R, L and C of the equivalent circuit of a slave                                   | 82  |

| Table 21 – Limits for R, L and C of the equivalent circuit of a master                                  | 87  |

| Table A.1 – Overview of existing slave profiles for standard slaves                                     | 137 |

| Table A.2 – List of existing profiles for standard slaves                                               | 137 |

| Table A.3 – Overview of existing slave profiles with extended address                                   | 138 |

| Table A.4 – List of existing profiles for slaves in extended address mode (ID=A)                        | 138 |

| Table A.5 – Profile catalogue of S-7.D profiles                                                         | 158 |

| Table A.6 – Overview of data of S-7.D profiles                                                          | 158 |

| Table A.7 – Profile catalogueue of S-7.E profile                                                        | 163 |

| Table A.8 – Overview of data of S-7.E profiles                                                          | 163 |

| Table A.9 – Commands for combined transaction type 2                                                    | 197 |

| Table A.10 – Acyclic write service request (Type 2)                                                     | 198 |

| Table A.11 – Acyclic read service request (Type 2)                                                      | 198 |

| Table A.12 – Acyclic write service response (Type 2)                                                    | 198 |

| Table A.13 – Acyclic read service response (Type 2)                                                     | 198 |

| Table A.14 – List of index 0 (mandatory): ID object (R)                                                 | 199 |

| Table A.15 – List of index 1 (mandatory): diagnosis object (R)                                          | 199 |

|                                                                                                         |     |

- 6 -

# INTERNATIONAL ELECTROTECHNICAL COMMISSION

# LOW-VOLTAGE SWITCHGEAR AND CONTROLGEAR – CONTROLLER-DEVICE INTERFACES (CDIs) –

## Part 2: Actuator sensor interface (AS-i)

## FOREWORD

- 1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as "IEC Publication(s)"). Their preparation is entrusted to technical committee; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC National Committees.

- 3) IEC Publications have the form of recommendations for international use and are accepted by IEC National Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

- 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter.

- 5) IEC provides no marking procedure to indicate its approval and cannot be rendered responsible for any equipment declared to be in conformity with an IEC Publication.

- 6) All users should ensure that they have the latest edition of this publication.

- 7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and members of its technical committees and IEC National Committees for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC Publications.

- 8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.

- 9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

International Standard IEC 62026-2 has been prepared by subcommittee 17B: Low-voltage switchgear and controlgear, of IEC technical committee 17: Switchgear and controlgear.

This second edition of IEC 62026-2 cancels and replaces the first edition published in 2000. This second edition constitutes a technical revision.

The main changes with respect to the previous edition are listed below:

- doubling the number of slaves from 31 to 62 by introduction of sub-addresses;

- introduction of AS-I safety system.

The text of this standard is based on the third edition and the following documents:

| FDIS          | Report on voting |

|---------------|------------------|

| 17B/1579/FDIS | 17B/1584/RVD     |

Full information on the voting for the approval of this standard can be found in the report on voting indicated in the above table.

This publication has been drafted in accordance with the ISO/IEC Directives, Part 2.

A list of all parts in the IEC 62026 series, under the general title *Low-voltage switchgear and controlgear – Controller-device interfaces (CDIs)*, can be found on the IEC website.

The committee has decided that the contents of this publication will remain unchanged until the maintenance result date indicated on the IEC web site under "http://webstore.iec.ch" in the data related to the specific publication. At this date, the publication will be

- reconfirmed;

- withdrawn;

- replaced by a revised edition, or

- amended.

A bilingual version of this publication may be issued at a later date.

# LOW-VOLTAGE SWITCHGEAR AND CONTROLGEAR – CONTROLLER-DEVICE INTERFACES (CDIs) –

## Part 2: Actuator sensor interface (AS-i)

## 1 Scope and object

This part of IEC 62026 specifies a method for communication between a single control device and switching elements, and establishes a system for the interoperability of components with the specified communication interfaces. The complete system is called "Actuator Sensor interface (AS-i)".

This standard describes a method for connecting switching elements, such as low-voltage switchgear and controlgear, standardized within IEC 60947, and controlling devices. The method may also be applied for connecting other devices and elements.

Where inputs and outputs I/O are described in this standard, their meaning is regarding the master, the meaning regarding the application is the opposite.

The object of this standard is to specify the following requirements for control circuit devices and switching elements:

- requirements for a transmission system and for interfaces between a slave, a master and electromechanical structures;

- requirements for a complete interoperability of different devices within any network, when meeting this standard;

- requirements for an interchangeability of devices within a network, when fulfilling the profiles of this standard;

- normal service conditions for the slaves, electromechanical devices and master;

- constructional and performance requirements;

- tests to verify conformance to requirements.

## 2 Normative references

The following referenced documents are indispensable for the application of this document. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

IEC 60068-2-6:1995, Environmental testing – Part 2-6: Tests – Test Fc: Vibration (sinusoidal)

IEC 60068-2-27:1987, Environmental testing – Part 2-27: Tests – Test Ea and guidance: Shock

IEC 60204-1:2005, Safety of machinery – Electrical equipment of machines – Part 1: General requirements

IEC 60227-2:1997, Polyvinyl chloride insulated cables of rated voltages up to and including 450/750 V – Part 2: Test methods Amendment 1 (2003)

IEC 60228:2004, Conductors of insulated cables

IEC 60304:1982, Standard colours for insulation for low-frequency cables and wires

IEC 60352-6:1997, Solderless connections – Part 6: Insulation piercing connections – General requirements, test methods and practical guidance

- 10 -

IEC 60364-4-41:2005, Low-voltage electrical installations – Part 4-41: Protection for safety – Protection against electric shock

IEC 60529:1989, *Degrees of protection provided by enclosures (IP code)* Amendment 1 (1999)

IEC 60947-1:2007, Low-voltage switchgear and controlgear – Part 1: General rules

IEC 60947-4-1:2000, Low-voltage switchgear and controlgear – Part 4-1: Contactors and motor-starters – Electromechanical contactors and motor-starters Amendment 1 (2002) Amendment 2 (2005)

IEC 60947-4-2:1999, Low-voltage switchgear and controlgear – Part 4-2: Contactors and motor-starters – AC semiconductor motor controllers and starters Amendment 1 (2001) Amendment 2 (2006)

IEC 60947-5-2:1997, *Low-voltage switchgear and controlgear – Part* 5-2: Control circuit devices and switching elements – Proximity switches Amendment 1 (1999) Amendment 2 (2003)

IEC 61000-4-2:1995 Electromagnetic compatibility (EMC) – Part 4-2: Testing and measurement techniques – Electrostatic discharge immunity test Amendment 1 (1998) Amendment 2 (2000)

IEC 61000-4-3:2006, *Electromagnetic compatibility (EMC) – Part 4-3: Testing and measurement techniques – Radiated, radio-frequency, electromagnetic field immunity test*

IEC 61000-4-4:2004, Electromagnetic compatibility (EMC) – Part 4-4: Testing and measurement techniques – Electrical fast transient/burst immunity test

IEC 61131-2:2007, Programmable controllers – Part 2: Equipment requirements and tests

IEC 61140:2001, *Protection against electric shock – Common aspects for installation and equipment* Amendment 1 (2004)

IEC 61508 (all parts), Functional safety of electrical/electronic/programmable electronic safety-related systems

IEC 61800-2:1998, Adjustable speed electrical power drive systems – Part 2: General requirements – Rating specifications for low-voltage adjustable frequency a.c. power drive systems

IEC/TS 61915:2003, Low-voltage switchgear and controlgear – Principles for the development of device profiles for networked industrial devices

IEC 62026-1:2007, Low-voltage switchgear and controlgear – Controller-device interfaces (CDIs) – Part 1: General rules

CISPR 11:2003, Industrial, scientific and medical (ISM) radio-frequency equipment – Electromagnetic disturbance characteristics – Limits and methods of measurement Amendment 1 (2004) Amendment 2 (2006)

## 3 Terms, definitions, symbols and abbreviations

For the purposes of this document, the terms, definitions, symbols and abbreviations given in IEC 62026-1 as well as the following apply.

А

## 3.1 Terms and definitions

Alphabetical index of definitions

| Active slave                      | .1.1  |

|-----------------------------------|-------|

| Actuator Sensor interface (AS-i)  |       |

| Address                           |       |

| Address assignment                |       |

| Analogue input data image (AIDI)  |       |

| Analogue output data image (AODI) |       |

| AS-i cycle                        |       |

| AS-i input                        |       |

|                                   |       |

| AS-i line                         |       |

| AS-i master                       |       |

| AS-i network                      |       |

| AS-i output                       |       |

| AS-i power supply                 |       |

| AS-i slave                        | 1.14  |

| В                                 |       |

| Dit time (offective)              | 1 4 5 |

| Bit time (effective)              | 1.15  |

| 5                                 |       |

| Configuration data (CD)           |       |

| Configuration data image (CDI)    |       |

| Controller                        |       |

| Controller interface              | 1.19  |

| D                                 |       |

| Data ayahanga phaga               | 1 20  |

| Data exchange phase               |       |

| Decoupling circuit                |       |

| Detection phase                   | 1.22  |

| E                                 |       |

| Earth fault detector              | 1 23  |

| Execution control                 |       |

| Extended addressing mode          |       |

| -                                 | 1.20  |

| F                                 |       |

| Field devices                     | 1.26  |

|                                   |       |

|                                   |       |

| I/O configuration (I/O code)      |       |

| Identification code (ID code)     |       |

| Input data image (IDI)            | 1.29  |

Reference

|                                | L      |

|--------------------------------|--------|

| List of activated slaves (LAS) |        |

|                                |        |

|                                |        |

|                                |        |

|                                |        |

|                                | Μ      |

| Master                         |        |

| Master pause                   |        |

| Master request                 |        |

|                                | Ν      |

|                                |        |

| Non-volatile stored data       |        |

|                                | 0      |

|                                | 0.4.00 |

| •                              |        |

|                                |        |

| Output data image (ODI)        |        |

|                                | Р      |

| Decemptor image (DI)           | 2.1.41 |

|                                |        |

| r-lauit                        |        |

|                                | R      |

| Repeater                       |        |

|                                |        |

|                                | S      |

| Select bit                     |        |

| Send pause                     |        |

|                                |        |

| Slave pause                    |        |

| Slave response                 |        |

| Symmetrizing circuit           |        |

|                                | т      |

|                                |        |

|                                |        |

| Transmission control           |        |

|                                | V      |

|                                |        |

| Volatile stored data           |        |

|                                | Z      |

| Zara address                   |        |

|                                |        |

– 12 –

# 3.1.1

active slave

slave connected to the AS-i line and capable to communicate properly

# 3.1.2

# Actuator Sensor interface (AS-i)

set of interfaces and serial communication method for the connection of low-voltage switchgear and controlgear, and other simple field devices with a controller

## address

numerical parameter out of the address space of the AS-i slaves which specifies a node of an AS-i network

NOTE Address 0 is reserved for slaves which have not had an address assigned.

## 3.1.4

#### address assignment

replacement of the existing address of the AS-i slave with a new address

## 3.1.5

#### Analogue Input Data Image (AIDI)

input data stored in the master, containing the latest actual copies of the received data from the inputs of all active slaves using combined transactions type 1 to 5

## 3.1.6

#### Analogue Output Data Image (AODI)

output data stored in the master to be transmitted cyclically to the active slaves with outputs using combined transactions types 1 to 5

## 3.1.7

#### AS-i cycle

set of up to 33 transactions

NOTE 1 A cycle may, in case of a detected communication failure, include one message retransmission.

NOTE 2 In the case of extended addressing mode, two cycles will be needed for data transfer of all slaves that are in extended addressing mode.

#### 3.1.8

## AS-i input

physical or logical slave port providing an input from the process

## 3.1.9

AS-i line

two-wire line for transferring information and power to the AS-i slaves and the AS-i master

### 3.1.10

#### AS-i master

unit on the AS-i line that manages the communication between the slaves and the controller

#### 3.1.11

#### AS-i network

network composed of an AS-i control circuit, interfaces and switching elements, for example master, slaves, power supply, cable, taps, repeaters

#### 3.1.12

### AS-i output

physical or logical slave port providing an output to the process

#### 3.1.13

#### AS-i power supply

special power supply combining a d.c. supply and a symmetrizing and decoupling circuit needed in an AS-i network

#### AS-i slave

physical and logical means to connect the application devices (actuator, sensor, or other components) to the AS-i line

NOTE A slave may be a stand alone device or part of another device.

# 3.1.15

#### bit time

$T_{\rm Bit}$

duration of the transmission of one bit

## 3.1.16

## configuration data (CD)

value of the I/O configuration and the identification code (optional extended identification codes) of a specific slave

## 3.1.17

#### configuration data image (CDI)

image of the configuration data of all slaves, stored in the AS-i master

## 3.1.18

#### controller

host or operator of the master, for example a programmable logic controller, a personal computer, a gateway, or a human operator

## 3.1.19

#### controller interface

logical interface between the master and the controller

## 3.1.20

## data exchange phase

period of time during which the master sends output data to the slaves and receives input data from the slaves

## 3.1.21

## decoupling circuit

part of the AS-i power supply for decoupling the d.c. source and the physical data transmission within the AS-i network

## 3.1.22

## detection phase

period of time when the execution control of the master tries to find all slaves connected and operating

NOTE All slaves found are listed in the list of detected slaves (LDS).

## 3.1.23

#### earth-fault detector

special insulation monitoring device compatible with the requirements of the AS-i transmission system which allows to detect the asymmetrical deterioration of the insulation between the AS-i network and ground

## 3.1.24

#### execution control

master function that controls the message exchange and provides several functions to the controller interface

#### extended addressing mode

doubles the maximum number of slaves from 31 (addresses in the range of 1 to 31) to 62 (addresses in the range of 1A/1B to 31A/31B)

#### 3.1.26

#### field devices

items connected to the AS-i slave, for example actuators, sensors, push-buttons, indicator lights, etc.

NOTE "intelligent" field devices also include integrated AS-i circuitry.

#### 3.1.27

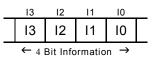

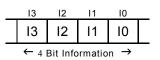

#### I/O-configuration (I/O-code)

set of four bits which defines the direction of data flow at the slave I/O ports.

### 3.1.28

#### identification code (ID-code)

set of four bits which defines the type of slave for a given I/O-configuration (optional: extended ID-codes consisting of additional 2x4bits)

#### 3.1.29

#### input data image (IDI)

input data stored in the master, received from the slaves

#### 3.1.30

#### list of active slaves (LAS)

list of all slaves at the AS-i line that are activated and capable of communicating properly with the master

NOTE The list is available in the master.

## 3.1.31

#### list of detected slaves (LDS)

list of all slaves actually detected by the master

NOTE The list is available in the master.

## 3.1.32

## list of peripheral faults (LPF)

list of all slaves with peripheral fault bit set to "1"

NOTE The list is available in the master.

## 3.1.33

#### list of projected slaves (LPS)

list of all configured slaves of the interface system as the target configuration

NOTE The list is available in the master and it includes the configuration data (CD) of all configured slaves.

# 3.1.34

#### master

control unit on the AS-i line that communicates serially with the slaves

# 3.1.35

## master pause

time between the last bit of a master request and the first bit of the slave response, measured at the master ports

#### master request

data or parameter or function sent from the master to a single slave (exception: broadcast)

NOTE The content of this master request is either data (to be moved to the output ports of the slave), parameters or a command

- 16 -

## 3.1.37

## non-volatile stored data

data that remains unchanged after power interruption

## 3.1.38

operation address

address of the AS-i slave other than the zero address

## 3.1.39

## output current limit

I<sub>Lim</sub>

output current of the power supply not to be exceeded under all environmental and load conditions

## 3.1.40

## output data image

ODI

output data stored in the master to be transferred to the AS-i slaves

## 3.1.41

## parameter image

ΡI

parameters (sets of 4 bits) that define the functionality of all the different slaves in the AS-i network

## 3.1.42

## p-fault

appliance in a slave for signalling peripheral faults to the master

NOTE In case of a peripheral fault and a "Read\_Status\_Request" of the master the slave response will be "1" in S1 bit.

## 3.1.43

## repeater

device that regenerates the AS-i signal and provides galvanic separation between parts of the AS-i network so that network lengths of more than 100 m are possible

## 3.1.44

## select bit

bit in the master request used in extended address mode to distinguish between the A-slave and B-slave

## 3.1.45

#### send pause

period after receipt of the slave response during which no subsequent transmission occurs

## 3.1.46

#### slave

network device or part of another device that provides an interface to the AS-i line and communicates with the master

#### slave pause

time between the last bit of a slave response and the start of sending the first bit of the next master request, measured at the master ports

#### 3.1.48

#### slave response

message from the slave to the master after a master request has been received and processed without error

NOTE The content of this response is either data or the result of a command.

#### 3.1.49

#### symmetrizing circuit

part of the AS-i power supply for conditioning the physical data transmission within the AS-i network

#### 3.1.50

#### transaction

(single) comprises a master request and a slave response within the master pause

NOTE Distinction is made between a single transaction, as defined above, and combined transactions of various types. The latter are combined of a series of several single transactions in which the information content is related in a well-defined way.

#### 3.1.51

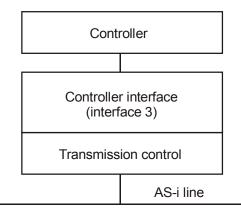

## transmission control

master function that controls the data transmission, transmission pauses and retransmissions in case of failures (e.g. transmission failures, missing response from the slave, invalid response received, etc.)

#### 3.1.52

#### volatile stored data

data that may change following power interruption

#### 3.1.53

#### zero address

special address reserved for the online assignment of a new address to an AS-i slave

#### 3.2 Symbols and abbreviations

- AIDI Analogue Input Data Image

- AODI Analogue Output Data Image

- APF AS-i power failure

- APM Alternating pulse modulation

- APO AS-i power ON

- AS-i Actuator Sensor Interface

- ASI+ positive potential of the AS-i network

- ASI- negative potential of the AS-i network

- CB control bit

- CD configuration data

- CDI configuration data image

- EB end bit

- IDI input data image

- *I*e rated current of AS-i power supply

- Ilim current limit of AS-i power supply

- LAS list of active slaves

- LDS list of detected slaves

- LPF list of slaves that signal peripheral fault condition

- LPS list of projected slaves

- MAN Manchester II code

- ODI output data image

- PB parity bit

- PCD permanent configuration data

- PI parameter image

- PP permanent parameter

- PSK phase shift keying

- SEL Select Bit used for extended addressing

- ST start bit

- T<sub>Bit</sub> bit time

- TS transaction status

- $00_{Hex}$  hexadecimal representation of values, for example  $1F_{Hex} = 31$ ,  $F_{Hex} = 15$

- $00_{Bin}$  binary representation of values, for example  $1100_{Bin} = 12$ ,  $0110_{Bin} = 6$

## 4 Classification

## 4.1 Overview

The Actuator Sensor Interface system will be applied mainly at the lowest level of a multi-level automation hierarchy. AS-i concentrates on the typical requirements for connecting binary elements with a controlling device. Thus, AS-i meets the requirements in machinery and plant construction, where real-time processing, cost effective design, installation, operating, maintenance, and service are essential.

AS-i can be used as an interface physically integrated into actuators, sensors, or other devices and elements themselves, opening an option for "intelligent" binary actuators, sensors, or other devices and elements. AS-i may, as well, be used in separate modules providing an interface for typically four conventional actuators, sensors or other devices and elements already available on the market.

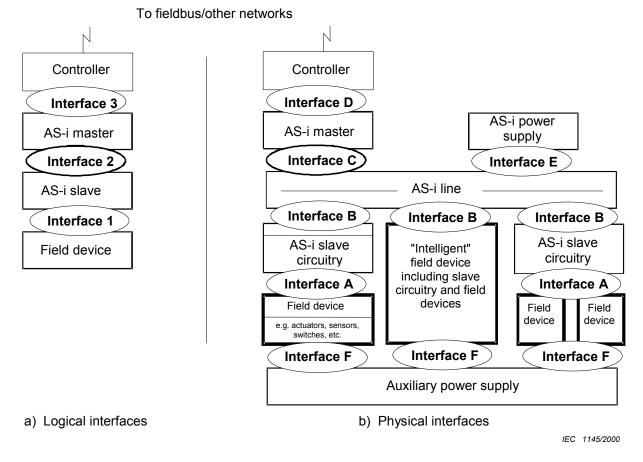

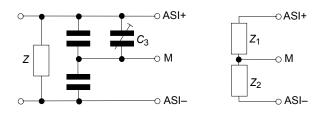

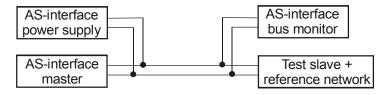

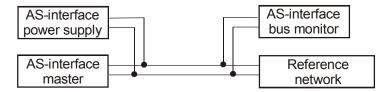

To connect this variety of actuators, sensors, or other devices and elements with a controlling device, AS-i is embedded in a structure of two different units which present three interfaces as shown in Figure 1.

Logically, the AS-i system is a master-slave communication system composed of a single master and up to 31 (62 with extended addressing) slaves. The master sends data and parameters to a specific slave. The slave passes the data to the output ports or processes the requested procedure (e.g. Reset\_Slave) and returns the input data or the result of the successful processed procedure to the master, respectively.

- 19 -

## Figure 1 – AS-i components and interfaces

The AS-i concept is independent of the specific type of actuators, sensors, or other devices and elements. It defines the mechanisms and all the components for the communication with a controlling device and it offers electromechanical structures for a standardized "plug and play technique" for installing very simply actuators, sensors, or other devices and elements into an AS-i-network.

The annexes define slave and master profiles of common types of actuators, sensors, or other devices and elements, that will often be used in AS-i systems.

## 4.2 Components and interfaces

As shown in Figure 1, the AS-i system comprises the following components and interfaces.

## 4.2.1 Components

**AS-i slave** The unit that can be accessed by the master via the AS-i line for data exchange, parametrization, and monitoring. The slave has a well-defined logical and functional behaviour. It responds immediately with slave response to a specific request from the master and it ensures that a malfunction of the attached actuator, sensor or other device or of the slave itself will not disturb the communication between the master and the other slaves in the network.

NOTE 1 The definition of an AS-i slave is logical in nature, but covers the physical requirements for data transmission through the AS-i network, too. The concrete realization of a slave depends on the implementation; for example a specific pinout of an integrated slave chip is not defined in this standard.

**AS-i master** The unit that organizes and monitors the network and schedules the exchange of data, parameters and commands with the AS-i slaves via the AS-i line. The master has a well-defined logical and functional behaviour. It sends master requests to the AS-i slaves and receives the immediate slave responses from them.

62026-2 © IEC:2008(E)

**AS-i power supply** Provides power to the AS-i network and includes the decoupling circuitry.

The 'Master Profiles' in Annex B define minimal sets of functions and commands of different master types.

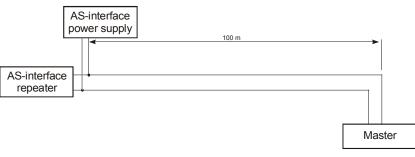

- AS-i repeater The unit that regenerates the AS-i signal and provides galvanic separation between parts of the AS-i network so that network lengths of more than 100 m are possible.

- AS-i line Provides the signalling and d.c. power connections between the AS-i devices.

#### 4.2.2 Logical interfaces

Interface 1 The slave interface to connect the AS-i slave with the actuators, sensors, or other devices and elements. It is characterized by several ports, which define the input, output or bi-directional input/output behaviour and the parametrization behaviour of the AS-i slave, the timing of the signals, and the power supply for actuators, sensors, or other devices and elements.

NOTE 1 Interface 1 is only a concept. The concrete representation of the interface depends mainly on the implementation. Only by the more restrictive slave profiles given in Annex A it is defined to some further extent.

Interface 2 The interface that provides all logical, physical, and mechanical requirements for data exchange and power distribution. It comprises signalling of encoded information, the AS-i transactions, mechanical and electrical requirements on the network and the AS-i power supply.

NOTE 2 Interface 2 is concrete in nature. It comprises the bus structure. The requirements of interface 2 are defined in this standard to ensure the interoperability of all components.

The interface between the controller and the AS-i master that provides all Interface 3 functions used by the controller to access the AS-i master for sending and receiving data to and from slaves, sending a cyclical command to a slave, to set or to obtain flags and values for several lists in the master. This interface allows the controller to manage the master's behaviour and thus the behaviour of the AS-i system. Supported functions are classically "set something" in the master, "get some information" from the master.

NOTE 3 Interface 3 is only a concept. The concrete representation of the interface depends on the implementation. To a large extent, it depends on features of the specific controller system.

#### 4.2.3 Physical interfaces

- Interface A Defines the physical connection between the field device and the AS-i slave circuitry including physical interface, signal levels and power requirements if any.

- Interface **B** Defines the physical connection of the AS-i slave circuitry to the AS-i line including physical interface (mechanical/electrical), signal characteristics and power requirements.

- Interface C Defines the physical connection of the AS-i master circuitry to the AS-i line including physical interface (mechanical/electrical), signal characteristics and power requirements.

- Interface D Definition of the physical interface is outside of the scope of this standard and shall be provided by the manufacturer.

- Interface E Defines the physical connection of the AS-i power supply including the signal decoupling circuit, to the AS-i line.

- Interface F Defines the physical interface between the field device and an external auxiliary power supply if any.

## **5** Characteristics

#### 5.1 Overview

The AS-i system defines digital, serial, multidrop data communication of a master with actuators and sensors or other devices including a power supply. Data and energy are transmitted on the same 2-wire cable.

The AS-i system is designed for protection class III (PELV) according to IEC 61140 (see 8.2). Therefore all components shall meet the corresponding requirements.

The AS-i transmission system provides the communication between up to 62 AS-i slaves and a single AS-i master, i.e. it represents the interface 2 between a master and the slaves (see Figure 1). The AS-i master shall call the individual slaves and get their responses immediately.

Subclauses 5.2 to 5.4 define the physical requirements and 5.5 to 5.7 the logical requirements of this transmission system (messages to be exchanged).

Additional requirements specific for the transmission medium (8.1), for the power supply (8.2), for the repeater and other components (8.3), for the slave (8.4) and for the master (8.5) are defined in the subclauses below.

#### 5.2 Signal characteristics

The characteristics of the transmitted signal and the modulation are defined in this subclause.

#### 5.2.1 Transmission coding

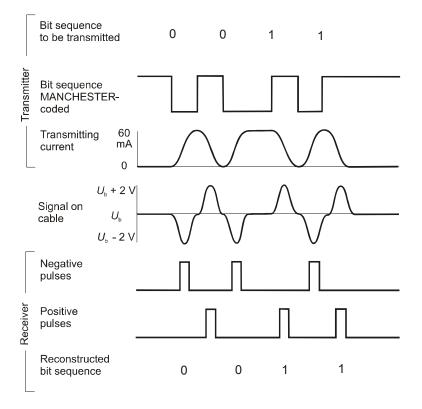

Figure 2 – Transmission coding

NOTE Because the information signal is superimposed on a d.c. supply voltage, a modulation must be employed that does not contain a d.c. voltage part. The transmission is asynchronous. To simplify synchronization of the slave a serially embedded synchronization information in the data signal flow is provided.

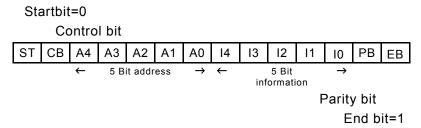

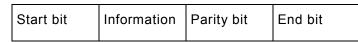

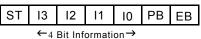

All messages are encoded in Manchester II format. Each message includes a start and an end bit. The idle state is represented by a "1". A "0" is encoded by a half bit time with high level followed by a half bit time of low level. A "1" is encoded by a half bit time of low level followed by a half bit time of high level.

The modulation shall be realized by the alternating pulse modulation (APM) with a sin<sup>2</sup> signal wave form. The rising edge of the Manchester II format shall be represented as a positive and the falling edge as a negative pulse.

The transmission encoding and decoding is shown in Figure 2.

## 5.2.2 Transfer speed

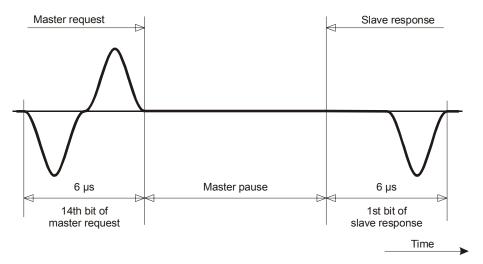

The bit time ( $T_{\text{Bit}}$ ) is defined as 6 µs. Thus, the bit sequence frequency shall be 166<sup>2</sup>/<sub>3</sub> kBit/s.

#### 5.2.3 Transmitter requirements

The transmitter in both the master and the slave shall be implemented as a current sink. The current signal is superimposed on the d.c. voltage of the AS-i network. A falling edge of the Manchester II coded signal shall cause a current of

$$i(t) = I_{\text{send}} * \left( \frac{t}{3\mu s} - \frac{1}{2\pi} \sin\left(\frac{2\pi}{3\mu s}t\right) \right)$$

A rising edge shall cause a current of

$$i(t) = I_{\text{send}} * \left( 1 - \frac{t}{3\mu s} + \frac{1}{2\pi} \sin\left(\frac{2\pi}{3\mu s}t\right) \right)$$

The amplitude  $I_{send}$  of the modulation current shall be between 55 mA and 68 mA.

The maximum deviation from the nominal bit time shall be less or equal to  $\pm$  0,1 % for the master and  $\pm$  0,2 % for the slave.

#### 5.2.4 Receiver requirements

Together with the decoupling inductances of the decoupling circuit in the power supply, the send current waveform as defined in 5.2.3 will lead to a negative (positive) voltage pulse at each rising (falling) edge. The waveform of the pulses will be ideally

$$u(t) \approx \pm U_{\text{send}} * \sin^2 \left(\frac{2\pi}{6\mu s}t\right)$$

with  $U_{\text{send}} = const \approx 2V$

NOTE 1 In a real AS-i System, the declining edge of the pulses is flattened due to the characteristics of the decoupling circuit. In addition, amplitudes and waveform will be influenced by the physical properties of the AS-i line. The receivers therefore must be able to detect a more complex pulse spectrum.

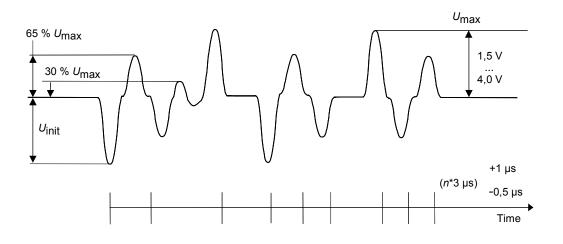

The receiver shall be able to receive and decode a message as described below (see Figure 3).

The maximum pulse amplitude  $U_{\rm max}$  of a message may vary between 1,5 V peak and 4 V peak.

– 23 –

NOTE 2 The differences in the amplitude  $U_{max}$  between consecutive Master requests will not vary in one configuration. Shown are the extreme values in different configurations and locations of the slave on the AS-i line. In a constant configuration, the relation of  $U_{max}$  between two slave responses at different locations of the line is up to 1:1,5.

The amplitude of a valid pulse within a message may vary from 65 % to 100 % of the maximum amplitude U<sub>max</sub>.

NOTE 3 For slaves according to previous versions of this standard it may vary from 80 % to 100 %.

Valid pulses start in a time window from  $(n^* 3 \mu s)^{+1.0 \mu s}_{-0.5 \mu s}$  in relation to the initial pulse  $U_{\text{init}}$ . These pulses shall be accepted by the receiver.

Pulses outside a window from  $(n * 3 \mu s)^{+1.6 \mu s}_{-0.8 \mu s}$  shall not be accepted by the receiver.

Pulses (noise, ringing) of up to 30 % of  $U_{\rm max}$  shall not disturb the message reception.

Figure 3 – Receiver requirements

NOTE 4 Pulse deviations from  $-0.8 \ \mu s$  up to  $+1.6 \ \mu s$  may occur due to a combination of different effects, for example capacitive load on the AS-i line, deviations from the oscillator frequency in the transmitter and in the receiver.

#### 5.3 Power and data distribution

#### 5.3.1 General

The simultaneous transmission of data and power on the AS-i line requires technical provisions for decoupling data and power.

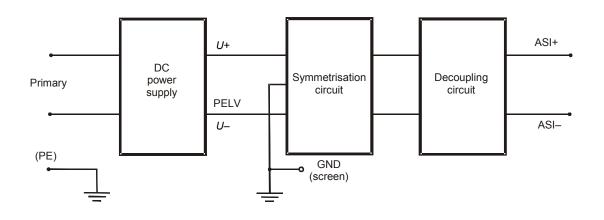

The AS-i power supply has to provide the d.c. power for the whole network. On the other hand, it has to realise the conditioning of physical data transmission within the system. This feature comprises symmetrization and forming and adapting transmission signals according to the signal requirements defined in 5.2. The adapting circuit will furthermore be called "decoupling circuit".

Although the functions of these components are independent, it is useful to combine them for practical reasons.

The combination of a d.c. power supply, a symmetrization circuit and a decoupling circuit is called "AS-i power supply".

- 24 -

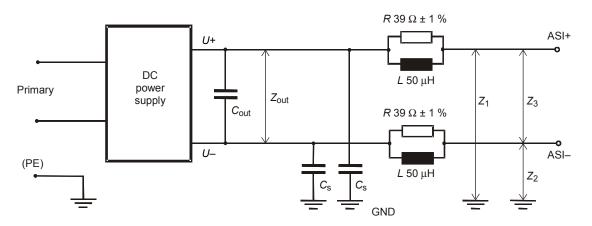

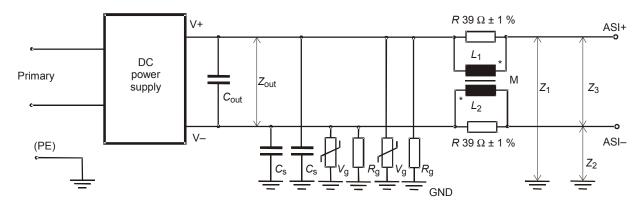

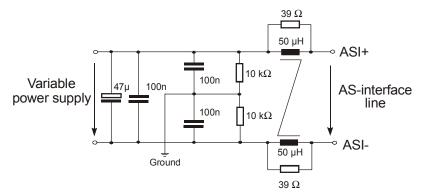

## Figure 4 – AS-i power supply

## 5.3.2 AS-i power supply requirements

The AS-i power supply requirements are shown in Table 1:

## Table 1 – AS-i power supply specifications

| Characteristic                                                                                            | Specification                                                                                       |  |  |

|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--|--|

| Output voltage at ASI+/ASI- (over the whole load range)                                                   | U <sub>ASI</sub> = 29,5 V d.c. to 31,6 V d.c.                                                       |  |  |

| Rated output current                                                                                      | I <sub>e</sub> as stated by the manufacturer                                                        |  |  |

| Additional current to meet charging processes for<br>connecting additional slaves during normal operation | $I_a$ = 0,4 A (12,5 mA for each standard slave / 6,5 mA for each slave in extended addressing mode) |  |  |

| Current limit                                                                                             | $I_{\text{lim}} > I_{\text{e}} + I_{\text{a}}$                                                      |  |  |

| Amplitude noise in the current range (measured at ASI+/ASI-)                                              | 50 mV <sub>pp</sub> within 10 kHz to 500 kHz (visible noise band on oscilloscope)                   |  |  |

| Low frequency ripple (except overload)                                                                    | 300 mV $_{pp}$ in the frequency range of 0 kHz to 10 kHz                                            |  |  |

| Power on delay                                                                                            | $\leq$ 2 s after reaching 5 V at output terminals                                                   |  |  |

NOTE Any regulation of input and load changes should not affect the communication on the AS-i line; the AS-i transmission activity should not affect the power supply. The total effect on the AS-i line should not exceed the value of 50 mV<sub>pp</sub> or 300 mV<sub>pp</sub>, respectively, see above.

## 5.3.3 Start-up behaviour

Within 2 s after reaching 5 V the first time, the voltage level shall reach the maximum value of the master starting voltage (26,5 V). The time span between the minimum master starting voltage (22,5 V -1 V, see 8.5.2.1) and the min. AS-i voltage level (29,5 V) shall be less than 1 s. The voltage level has to increase steadily from 5 V up to normal operation voltage (29,5 V to 31,6 V).

NOTE The second demand is important because the master begins to work if the voltage exceeds its starting voltage of 22,5 V  $\pm$  1 V.

During start-up the power supply shall supply an increased current to meet the charging process in the system. This additional load will be equal to a capacitance of 15 mF.

Beginning from a voltage level of 5 V, the power supply shall give the rated output current  $I_e$  plus an additional current to load the above mentioned capacitance of 15 mF to meet the time restrictions.

# 5.3.4 Symmetrization and decoupling circuit

The symmetrization and decoupling circuit ensures several functions of the AS-i transmission system:

- providing the d.c. power to the AS-i line;

- signal shaping;

- terminating impedance (for the physical line);

- symmetrizing the AS-i line with respect to GND;

- rejection of common mode noise.

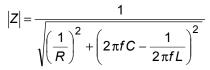

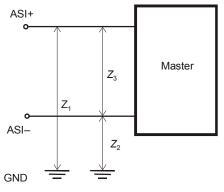

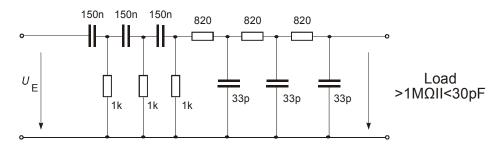

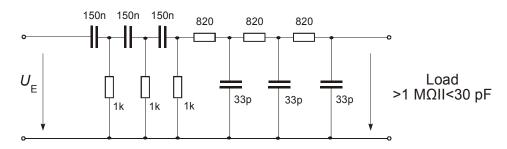

The equivalent decoupling network consists of two inductances and two resistors as well as the symmetrizing capacitors  $\rm C_s$  as shown in Figure 5.

Figure 5 – Equivalent schematic of symmetrization and decoupling circuit

The symmetry capacitors  $C_s$  shall be located as close as possible to the decoupling circuit. These capacitances provide a symmetrical relation of ASI+/ASI- to ground. Equal values of at least 100 nF are recommended.

| Characteristic                         | Specification                                                                      |  |  |

|----------------------------------------|------------------------------------------------------------------------------------|--|--|

| Inductance between ASI+/ASI-           | 100 μH ± 10 % (/ <sub>L</sub> =0 to / <sub>Lmax</sub> )                            |  |  |

| Short circuit / overload               | May be applied for infinite time without causing defects in the decoupling circuit |  |  |

| Symmetry of ASI+/- against GND         | $0.98 \le  Z_1  /  Z_2  \le 1.02$                                                  |  |  |

|                                        | within the frequency range of 10 kHz to 300 kHz and the whole load range           |  |  |

| Source impedance                       | $ Z_{\text{out}}  < 0.5 \Omega$ in the range of 10 kHz to 300 kHz                  |  |  |

| Decoupling impedance (C <sub>S</sub> ) | $ Z_{\rm S} $ < 5 $\Omega$ in the range above 300 kHz                              |  |  |

# 5.4 AS-i topology and other components

# 5.4.1 AS-i line (minimum requirements)

The AS-i transmission medium can be any cable, shielded or non-shielded at which the following characteristics shall be provided for the full operating range:

at a frequency of 167 kHz:

- R': < 90 m $\Omega$ /m

- C': < 80 pF/m

- Z : 70  $\Omega$  to 140  $\Omega$

- G': ≤ 5 µS/m

- L': 400 nH/m to 1 300 nH/m

- t':  $\leq 8,3 \text{ ns/m}$

The recommended cross-section is  $2 \times 1,5$  mm<sup>2</sup>.

For short trunk lines without further branching cables with other specifications are tolerable, if the d.c. voltage drop on these lines does not affect the function of the connected devices.

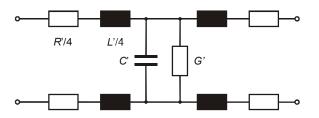

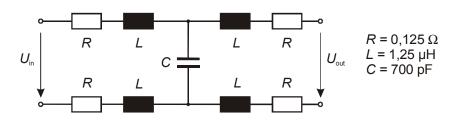

Figure 6 – Model of the AS-i transmission medium

NOTE 1 The characteristic impedance Z of a transmission line is defined by its distributed constants R', L', C', G' and the frequency in use by the equation

$$Z = \left| \sqrt{\frac{R' + j\omega L'}{G' + j\omega C'}} \right|$$

The distributed constants can be measured at an electrical short length of the transmission line with open (G', C') respectively, shorted (R', L') end. The additional limitations of Z and the propagation delay time t' result from excluding such combinations of distributed constants which would lead to unfavourable high or low values of the characteristic impedance.

NOTE 2 Any cable that meets the above mentioned data may be used as the AS-i line. Nevertheless, several requirements and tolerances of this standard are intended to meet a total voltage drop (d.c.) along the AS-i transmission medium of up to 3 V. It is recommend to use a cross-section so that no higher voltage drop will occur. If a cable is to be used as the AS-i-line that does <u>not</u> meet the above-mentioned data, the total length of 100 m for the complete network may be affected.

NOTE 3 The propagation delay of a signal on the AS-i line is defined by the equation

$$t' = \sqrt{L'C' - \frac{R'G'}{\omega^2}}$$

and is typically 0,6 µs/100 m in one direction.

#### 5.4.2 AS-i topology

The AS-i topology is the tree structure. The total length of the AS-i line shall not exceed 100 m. This length shall be calculated as the sum of all trunk lines.

There shall be no connection to GND in the network apart from the port GND at the power supply.

NOTE AS-i has been designed as a symmetrical system. The better the symmetry, the better the rejection of undesirable emission of AS-i signal components as well as incidence of AS-i relevant noise, even if the system is relatively large and distributed. This is important because the network is unshielded and may act as an antenna.

During normal operation, a voltage drop between the power supply and any point of the network of more than 3 V shall not occur unless a possibly higher voltage drop is specified in the product documentation of a particular slave.

#### 5.4.3 AS-i repeater

The total length of the AS-i line is restricted to 100 m. An AS-i repeater regenerates the AS-i signal and provides galvanic separation between parts of the AS-i network so that network lengths of more than 100 m are possible.

Because of timing restrictions, it is not allowed to connect more than two repeaters in series. It is possible, however, to use several repeaters in parallel as long as they are connected to different branches of the tree structure of the network.

#### 5.4.4 AS-i earth-fault detector

According to IEC 60204-1, earth faults on any control circuit shall not cause unintentional starting, potentially hazardous motions or prevent stopping of the machine. To fulfil this requirement, IEC 60204-1 indicates that control circuits that are not connected to the protective bonding circuit shall be provided with an insulation monitoring device that either indicates an earth fault or interrupts the circuit automatically after detecting an earth fault.

If an AS-i network is used to control potentially dangerous movements of a machine and IEC 60204-1 applies, an isolation monitoring device shall be installed. If the AS-i network is composed of separate parts that are isolated from each other, an insulation monitoring device shall be used for each isolated part of the network.

The insulation monitoring device used in AS-i networks shall be compatible with the requirements of the AS-i transmission system. Details are given in 8.3.2.

#### 5.5 Communication

#### 5.5.1 Communication principles

The AS-i system is a master-slave communication system composed of a single master and up to 31 (62 with extended addressing) slaves. Each slave shall have a unique address in the range of 1 to 31 (1A/1B to 31A/31B with extended addressing). This address is called operation address. The operation address shall be stored non-volatile. Only slaves with an operation address shall respond to data and parameter requests from the master.

The zero address is used during the change of a slave address. Normally, the zero address is stored volatile, except in factory new slaves. For details see 8.4.

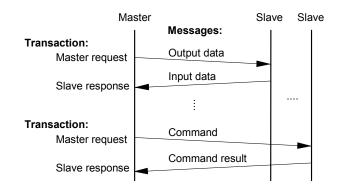

A single transaction is composed of a master request and a slave response. A combined transaction is composed of several single transactions.

#### 5.5.2 Transmission control

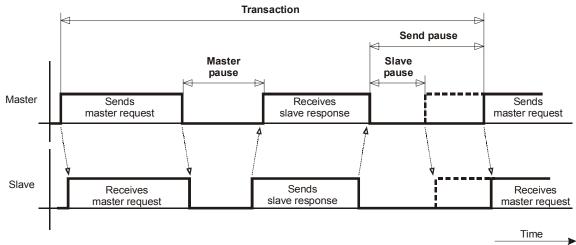

The exchange of data between the single master and up to 31 (62 with extended addressing) slaves is implemented by the processing of transactions (see Figure 7). A transaction starts with a master request. The master expects a slave response within a certain time. If the master does not receive a valid response from the slave within this time, it shall interpret this as a negative response. It may retransmit the master request once more. After receiving a valid response, the master shall start the next transaction after the send pause has elapsed. A slave shall not respond if it detects a faulty master request or if the master issues an unsupported request. The slave shall not give any negative response.

Figure 7 – Transactions

## 5.5.3 Timing requirements

All times specified in this paragraph are related to the signals on the AS-i line at the location of the master terminals.