# LICENSED TO MECON Limited. - RANCHI/BANGALORE FOR INTERNAL USE AT THIS LOCATION ONLY, SUPPLIED BY BOOK SUPPLY BUREAU.

# TECHNICAL REPORT

# IEC TR 62017-2

First edition 2001-02

Documentation on design automation subjects -

Part 2:

**EIAJ-EDA Technology Roadmap toward 2002**

Documentation sur les sujets d'automatisation de la conception –

Partie 2:

EIAJ-EDA Technology Roadmap toward 2002

# **Publication numbering**

As from 1 January 1997 all IEC publications are issued with a designation in the 60000 series. For example, IEC 34-1 is now referred to as IEC 60034-1.

### Consolidated editions

The IEC is now publishing consolidated versions of its publications. For example, edition numbers 1.0, 1.1 and 1.2 refer, respectively, to the base publication, the base publication incorporating amendment 1 and the base publication incorporating amendments 1 and 2.

# Further information on IEC publications

The technical content of IEC publications is kept under constant review by the IEC, thus ensuring that the content reflects current technology. Information relating to this publication, including its validity, is available in the IEC Catalogue of publications (see below) in addition to new editions, amendments and corrigenda. Information on the subjects under consideration and work in progress undertaken by the technical committee which has prepared this publication, as well as the list of publications issued, is also available from the following:

### IEC Web Site (<u>www.iec.ch</u>)

### • Catalogue of IEC publications

The on-line catalogue on the IEC web site (<a href="www.iec.ch/catlg-e.htm">www.iec.ch/catlg-e.htm</a>) enables you to search by a variety of criteria including text searches, technical committees and date of publication. On-line information is also available on recently issued publications, withdrawn and replaced publications, as well as corrigenda.

## • IEC Just Published

This summary of recently issued publications (<a href="www.iec.ch/JP.htm">www.iec.ch/JP.htm</a>) is also available by email. Please contact the Customer Service Centre (see below) for further information.

# • Customer Service Centre

If you have any questions regarding this publication or need further assistance, please contact the Customer Service Centre:

Email: <u>custserv@iec.ch</u>

Tel: +41 22 919 02 11

Fax: +41 22 919 03 00

# LICENSED TO MECON Limited. - RANCHI/BANGALORE FOR INTERNAL USE AT THIS LOCATION ONLY, SUPPLIED BY BOOK SUPPLY BUREAU.

# TECHNICAL REPORT

# IEC TR 62017-2

First edition 2001-02

Documentation on design automation subjects -

# Part 2:

**EIAJ-EDA Technology Roadmap toward 2002**

Documentation sur les sujets d'automatisation de la conception –

Partie 2: EIAJ-EDA Technology Roadmap toward 2002

© IEC 2001 — Copyright - all rights reserved

No part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from the publisher.

International Electrotechnical Commission 3, rue de Varembé Geneva, Switzerland Telefax: +41 22 919 0300 e-mail: inmail@iec.ch IEC web site http://www.iec.ch

Commission Electrotechnique Internationale International Electrotechnical Commission Международная Электротехническая Комиссия

PRICE CODE

# **CONTENTS**

|     |                                        |                                                                                                                                                                                                                                                                                                                                                                                              | Page           |

|-----|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| FO  | REW                                    | ORD                                                                                                                                                                                                                                                                                                                                                                                          | 4              |

| Cla | use                                    |                                                                                                                                                                                                                                                                                                                                                                                              |                |

| INT | ROD                                    | UCTION                                                                                                                                                                                                                                                                                                                                                                                       | 5              |

|     | 1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6 | Background Objectives. Definitions. Audience for the Roadmap Making of the Roadmap How to Utilize the Roadmap                                                                                                                                                                                                                                                                                | 677            |

| 2.  | Exe                                    | cutive Summary                                                                                                                                                                                                                                                                                                                                                                               | 10             |

|     | 2.1<br>2.2<br>2.3                      | Semiconductor Industry in 2002 2.1.1 Overview of Design Objects in 2002 2.1.2 Overview of Design Environments in 2002 EDA Technology in 2002 Outline of the Roadmap                                                                                                                                                                                                                          | 10<br>12<br>13 |

| 3.  | Req                                    | uirements for EDA Technology                                                                                                                                                                                                                                                                                                                                                                 | 19             |

|     | 3.1<br>3.2                             | Profile of Cyber-Giga-Chip                                                                                                                                                                                                                                                                                                                                                                   |                |

| 4.  | Prob                                   | olems and Targets of EDA Technology                                                                                                                                                                                                                                                                                                                                                          | 28             |

|     | 4.3<br>4.4                             | Problems and Targets of EDA Technology in Digital Circuit Design 4.1.1 System Design 4.1.2 Architecture Design 4.1.3 RTL/Logic Design 4.1.4 Circuit Design 4.1.5 Layout Design 4.1.6 Manufacture Interface Problems and Targets of EDA Technology in Analog Circuit Design Problems and Targets of EDA Technology in Software Design Problems and Targets of EDA Technology in Entire Design |                |

| 5.  | EDA                                    | Technology Roadmap                                                                                                                                                                                                                                                                                                                                                                           | 64             |

|     | 5.1<br>5.2                             | EDA Technology Roadmap for Cyber-Giga-Chip  5.1.1 Design flow of Cyber-Giga-Chip  5.1.2 EDA Technology Roadmap for Cyber-Giga-Chip  Cyber-Giga-Chip for Consumer Electronics                                                                                                                                                                                                                 | 64<br>68       |

| A   | cknov                                  | wledgements                                                                                                                                                                                                                                                                                                                                                                                  | 73             |

|     |                                        | nces                                                                                                                                                                                                                                                                                                                                                                                         |                |

| A   | Glos                                   | ssary                                                                                                                                                                                                                                                                                                                                                                                        | 75             |

| Paç                                                                                         | дe |

|---------------------------------------------------------------------------------------------|----|

| Figure 1 – Makimoto's Wave (Source: IEEE Spectrum Jan. 1992)                                | .6 |

| Figure 2 – Roadmap Development Concept                                                      | .9 |

| Figure 3 – Profile of Cyber-Giga-Chip in 20021                                              | 12 |

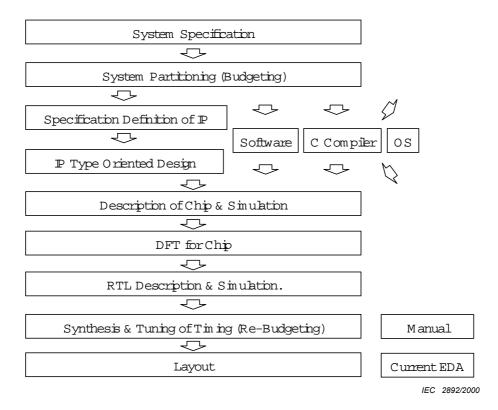

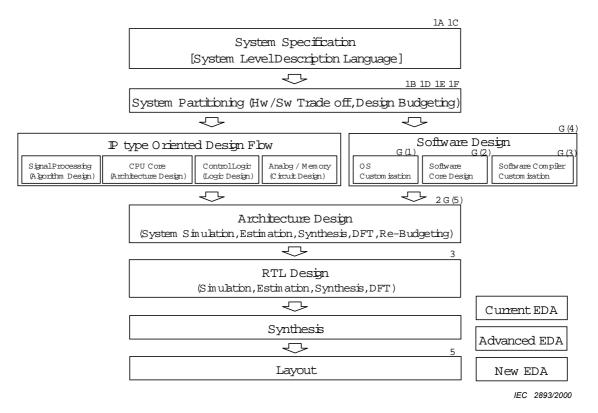

| Figure 4 – Design Flow of Core Based System LSIs1                                           | 13 |

| Figure 5 – Profile of Cyber-Giga-Chip in 20021                                              | 19 |

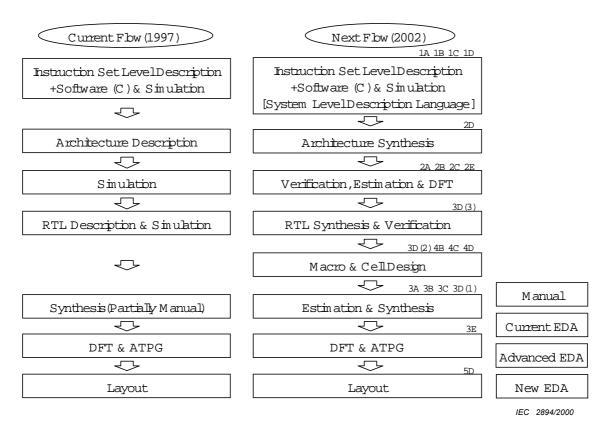

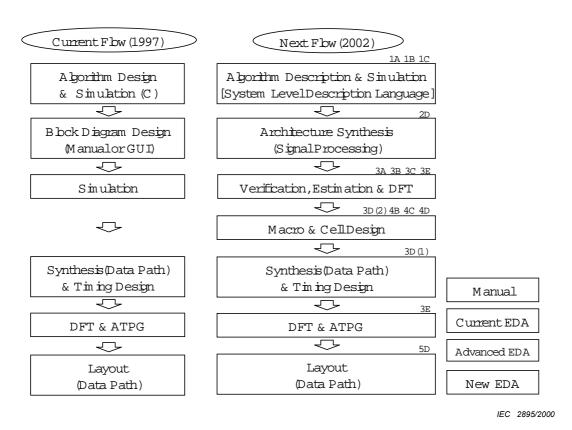

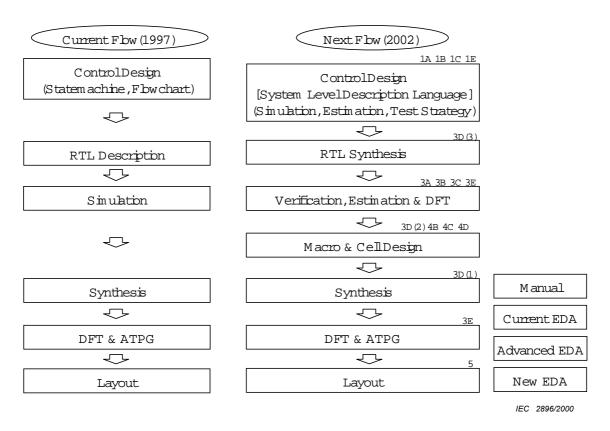

| Figure 6 – Design Flow of Cyber-Giga-Chip in 1997                                           | 34 |

| Figure 7 – Design Flow of Cyber-Giga-Chip in 2002                                           | 35 |

| Figure 8 – Design Flow of CPU Cores6                                                        | 36 |

| Figure 9 – Design Flow of Digital Signal Processing Cores                                   | 37 |

| Figure 10 – Design Flow of Controller Cores                                                 | 38 |

|                                                                                             |    |

| Table 1 – Member List of EDA Vision Working Group                                           |    |

| Table 2 – Institute of Systems & Information Technologies / KYUSHU                          |    |

| Table 3 – EDA Technology Problems of Digital Circuit Design                                 |    |

| Table 4 – EDA Technology Problems of Digital Circuit Design (RTL to Manufacture Interface)1 |    |

| Table 5 – EDA Technology Problems of Analog Circuit Design                                  | 17 |

| Table 6 – Problems of EDA Technology in Software Design and Entire design                   | 18 |

| Table 7 – Specification of Cores for Cyber-Giga-Chip                                        | 20 |

| Table 8 – LSI Design Requirements Table                                                     | 21 |

| Table 9 – Correspondence of design requirement items and EDA technology problems            | 27 |

| Table 10 – Problems of EDA Technology in System Design                                      | 28 |

| Table 11 – Problems of EDA Technology in Architecture Design                                | 33 |

| Table 12 – Problems of EDA Technology in RTL/Logic Design                                   | 38 |

| Table 13 – Problems of EDA Technology in Circuit Design                                     | 17 |

| Table 14 – Problems of EDA Technology in Layout Design                                      | 51 |

| Table 15 – Problems of EDA Technology in Manufacture Interface                              | 55 |

| Table 16 – Problems of EDA Technology in Analog Circuit Design                              | 56 |

| Table 17 – Problems of EDA Technology in Software Design                                    | 59 |

| Table 18 – Problems of EDA Technology in Entire Design                                      | 32 |

| Table 19 – Transition of EDA Technology (1)                                                 | 39 |

| Table 20 – Transition of EDA Technology (2)                                                 | 70 |

# INTERNATIONAL ELECTROTECHNICAL COMMISSION

# DOCUMENTATION ON DESIGN AUTOMATION SUBJECTS – Part 2: EIAJ-EDA Technology Roadmap toward 2002

### **FOREWORD**

- 1) The IEC (International Electrotechnical Commission) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of the IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, the IEC publishes International Standards. Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaising with the IEC also participate in this preparation. The IEC collaborates closely with the International Organization for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- 2) The formal decisions or agreements of the IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested National Committees.

- 3) The documents produced have the form of recommendations for international use and are published in the form of standards, technical specifications, technical reports or guides and they are accepted by the National Committees in that sense.

- 4) In order to promote international unification, IEC National Committees undertake to apply IEC International Standards transparently to the maximum extent possible in their national and regional standards. Any divergence between the IEC Standard and the corresponding national or regional standard shall be clearly indicated in the latter.

- 5) The IEC provides no marking procedure to indicate its approval and cannot be rendered responsible for any equipment declared to be in conformity with one of its standards.

- 6) Attention is drawn to the possibility that some of the elements of this technical report may be the subject of patent rights. The IEC shall not be held responsible for identifying any or all such patent rights.

The main task of IEC technical committees is to prepare International Standards. However, a technical committee may propose the publication of a technical report when it has collected data of a different kind from that which is normally published as an International Standard, for example "state of the art".

IEC 62017-2, which is a technical report, has been prepared by IEC technical committee 93: Design automation. It is based on the *EDA Technology Roadmap toward 2002* published by EIAJ.

The text of this technical report is based on the following documents:

| Enquiry draft | Report on voting |  |

|---------------|------------------|--|

| 93/115/CDV    | 93/119/RVC       |  |

Full information on the voting for the approval of this technical report can be found in the report on voting indicated in the above table.

This publication has not been drafted in accordance with the ISO/IEC Directives, Part 3.

This document which is purely informative is not to be regarded as an International Standard.

The committee has decided that the contents of this publication will remain unchanged until 2004. At this date, the publication will be

- · reconfirmed;

- withdrawn;

- · replaced by a revised edition, or

- amended.

# Introduction

# 1.1 Background

With the advancement of semiconductor technology, the possible number of transistors on a silicon chip is doubling every three years. Soon, it is estimated that over 10 million transistor circuits will be realized on a silicon chip of only 1 cm<sup>2</sup>. Now, with this progress in LSI manufacturing technology, it is time to consider what kind of system should be designed, which is an important issue for the future semiconductor industry.

Formerly, the principal products of the semiconductor industries, such as memories and microprocessors, were just "parts" of a system that make up the final product. Since the size of required by specification was over limitation of productivity, the main concern was how to design, produce and test the LSI, rather than what to design. In the next decade, however, it is expected that existing microprocessors with the highest performance and a large memory will be integrated on a single chip, and the whole system consisting of processors, memories and other logic could be implemented as a single LSI. The major problems on the design of LSIs will then shift to what kind of systems should be designed and specified. As we enter the era of System-On-Silicon (SOS) or System-On-Chip (SOC), new design methodologies are requested, which should be quite different from that for designing the "parts" and not the "system".

In the case of standard parts, such as memories, process technologies for manufacturing and internal circuit designing are more important than specification of the products. In the case of microprocessors, although it is a small-variation-mass-product type business, specification and design technologies are more important. However the number of designs was quite limited and much time and cost was spent on the design of the microprocessors. In ASIC (Application Specific Integrated Circuit) business, specifications of LSIs, which are extremely important, are given by the system designers. However, in design of system LSI, the design for the final product and LSI are inherited, as all functions will be implemented ultimately on a single chip. The specification of system LSI is also the specification of the final product. Therefore, it is important in semiconductor business as well as the final product business.

There are three principal changes of environment in system LSI design technology. First, as process technology advances, there is an exponential increase of investment in production lines and demand for new design technologies to resolve many problems caused by scaling down and improving performance. Second, design technologies to handle large scale, complicated systems are important concerns, since superiority of an LSI greatly depends on the quality of the system and its circuit design. Third, there is pressure from the market to shorten the time of system development and to improve design efficiency. Therefore, technology for the fast and efficient design of system LSIs is urgently required.

The future of LSI business will depend on how these requirements are dealt with. The LSI businesses may be divided into the following three species:

- 1) Fabrication business based on the advanced process technology,

- 2) Vertically integrated system business including both system design and fabrication,

- 3) Fabless System business.

In Japan, many companies have both system design and fabrication technology divisions. However, some of them will have no choice but to become simply fabricators or else fabless designers, if they can not resolve upcoming problems. To keep the style of vertically integrated structure and to enjoy the advantage of it, there is a need to develop a new design technology and construct a new style of business for the era of system LSIs. It is an urgent research and development task to establish a new design method, within which system designers and LSI designers may collaborate efficiently, with EDA tools supporting the collaboration.

This roadmap aims to clarify the direction of EDA technology to support design methods for system LSIs. It summarizes research and development targets of EDA technology in 2002, which may be reasonably easy to predict, and proposes scheme to reach them. We intend to give a foundation on which to start discussions on new design methods and the restructuring of the vertically integrated industries for a new technological environment.

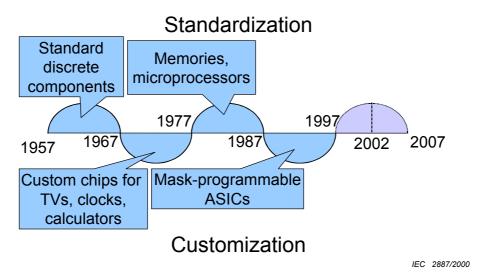

Figure 1 - Makimoto's Wave (Source: IEEE Spectrum Jan. 1992)

Technical revolutions in semiconductor business are illustrated as Makimoto's wave (Figure 1). Technology innovation (customization) and competition (standardization) have been repeated with a period of 20 years. After the innovation period of developing a new market, the technology is standardized and many products are available. When the market becomes saturated, new customized technologies are invented for product differentiation. From the macroscopic point of view, the decade from 1997 to 2007 will be the era of standardization, in which semiconductors are designed and produced using combinations of standardized technologies. 2002 will be the summit of the wave of standardization and the entrance of the era of practical system LSIs with several tens of millions of transistors. To manage the variety of specification of system LSIs, design reuse will be an important technology. The system LSI will be designed as a combination of well-design cores. Cores, interfaces between cores and interfaces between system LSIs will be standardized and large, high performance and complicated system LSIs will be designed flexibly in 2002. In other words, this is the era of custom system design utilizing standard components such as cores. Therefore, the next decade will mark a new phase for design technology, in which the customization of system design and the standardization of LSI design should be treated simultaneously.

From the viewpoint of EDA technology, standard tools are used in the era of customization, and superiority of an LSI strongly depends on its conception and planning. On the other hand, in an era of standardization, superiority of an LSIs is determined by design technologies and tools. In the next decade, design methodologies and tools will be a key to success in the semiconductor business.

Discussing the direction of semiconductor technologies and drawing a roadmap are important measures for the sound development of the semiconductor industry. In U.S., SIA published roadmaps [1] including various technologies related to semiconductor industries; and CFI published a roadmap [2] on EDA technology mainly for standardization. In Japan, ATLAS project of the Semiconductor Industry Research Institute Japan examines the ability of Japanese designers to create applications in 2010 [3]. However, there is no roadmap for EDA technology for the system LSI era. This roadmap summarizes the discussion in EIAJ on the future of EDA technology, in the hope that it will act as a guide for the next EDA technology innovations. This roadmap summarizes the discussion in EIAJ on the future of EDA technology innovations.

# 1.2 Objectives

The objective of the roadmap is to show the following by the 21<sup>st</sup> century:

- The target for system LSI in 2002, which we have called the Cyber-Giga-Chip (CGC),

- Design and test methodology to be used for system LSI,

- EDA technology to assist design and test the system LSI,

- An EDA roadmap for each important application area in 2002.

In order for the roadmap to be realistic and practical, we have focussed on:

- 1) Investigation of necessary technology by 2002,

- 2) Requirement analysis on EDA technology from the viewpoints of LSI designers.

The reason for setting 2002 as the deadline in the former policy is as follows:

- Core-based design will be the main stream in the age when the design rule becomes 0.18 to 0.13 μm,

- 2002 is the summit of "Standardization Age",

- 5 years is a reasonable period to draw up a realistic timetable for the various EDA topics.

The latter policy is adopted so that the roadmap will link the seed (i.e. the technology EDA engineers can offer) to the need (i.e. the requirements LSI designers must meet) for the proposed system LSI design.

# 1.3 Definitions

The terms listed below are used frequently from now on.

Cyber-Giga-Chip: A chip which forms the kernel of a piece of electronic equipment, and is composed of

various functional blocks.

Core: A sub circuit with certain function.

IP: Intellectual property, such as design property.

System Design: To design the specification of a system LSIs, and establish the means to realize target

functions in the hardware and software.

Architecture: To decide the hardware composition of the function that needs to be realized, under

some restrictions.

RTL/Logic Design: To select the hardware circuits and logic circuits of the function to be realized, subject

to constraints.

Circuit Design: To describe each circuit in terms of its basic parts, such as cell, analog and memory,

subject to constraints.

Layout Design: To position basic parts on a silicon chip, and to wire between them based on

connection information, in order to realize an electronic circuit. Placement and routing of the basic parts will directly influence electronic behavior in deep submicron era, so

it is important to perform place and route with electronic behavior in mind.

Test Design: To generate test data for an LSI tester to check whether the electric circuit

implemented on a silicon chip realizes the required functions. Design for test (DFT), for example, adding a circuit to make measurement convenient, may also be included

under this heading.

Test: To make measurements to see whether manufactured LSI actually performs its desired

function, using a LSI tester etc.

# 1.4 Audience for the Roadmap

The roadmap is suitable for all managers and/or engineers who are concerned with system design/test, semiconductor design/test, and EDA technology. Researchers in universities are also targeted.

# 1.5 Making of the Roadmap

The roadmap is made by EDA Technical Committee / EDA Vision Working Group of Electronic Industries Association of Japan (EIAJ), in cooperation with Institute of Systems and Information Technologies/KYUSHU (ISIT/KYUSHU), shown in Table 1 and Table 2, respectively.

Table 1 – Member List of EDA Vision Working Group

| Name                   | Representing                             | Participation                        |

|------------------------|------------------------------------------|--------------------------------------|

| Yoshiharu Furui        | Sony Corporation                         | Chair                                |

| Takashi Kambe          | Sharp Corporation                        | Co- Chair                            |

| Tsutomu Someya         | IK Technology Co., Ltd.                  | Working Member                       |

| Ichirou Yamamoto       | OKI Electric Industry Co., Ltd.          | EDA TechnoFare 98 Publication        |

| Kazuya Morii           | SANYO Electric Co., Ltd.                 | Working Member                       |

| Akihisa Yamada         | Sharp Corporation                        | Working Member                       |

| Takayuki<br>Yamanouchi | Sharp Corporation                        | Working Member                       |

| Tetsuya Fujimoto       | Sharp Corporation                        | Working Member                       |

| Masato Ikeda           | Zuken Incorporated                       | Working Member                       |

| Nobuto Ono             | Seiko Instruments inc.                   | Working Member                       |

| Masaru Kakimoto        | Sony Corporation                         | Working Member                       |

| Kenji Yoshida          | Toshiba Corporation                      | Advisory Member                      |

| Tamotsu Hiwatashi      | Toshiba Corporation                      | Leader of LSI Design Needs WG        |

| Akihiro Yamada         | Toppan Printing Co., Ltd.                | EDA TechnoFare 98 Publication        |

| Naoya Takahashi        | NEC Corporation                          | Working Member                       |

| Hiroko Yamamoto        | ViewLogic Japan                          | Working Member                       |

| Yoshio Ohshima         | Hitachi, Ltd.                            | Leader of EDA Requirement WG         |

| Noriyuki Itou          | Fujitsu Ltd.                             | WWW Publication                      |

| Michiaki Muraoka       | Matsushita Electric Industrial Co., Ltd. | Leader of Cyber-Giga-Chip Profile WG |

| Mitsuyasu Ohta         | Matsushita Electric Industrial Co., Ltd. | Working Member                       |

| Hideyuki Hamada        | Mitsubishi Electric Corporation          | Working Member                       |

| Mitsuhiro Kitta        | Mitsubishi Electric Corporation          | Leader of EDA Roadmap WG             |

| Itsuo Suetsugu         | Mentor Graphics Japan Co. Ltd.           | Working Member                       |

| Kousuke Shiba          | Mentor Graphics Japan Co. Ltd.           | Working Member                       |

| Masaharu Imai          | Osaka University                         | Advisory Member                      |

| Tokinori Kozawa        | STARC                                    | Advisory Member                      |

| Sagorou Hazama         | Fujitsu Ltd.                             | Advisory Member                      |

| Satoshi Kojima         | Hitachi Ltd.                             | Advisory Member                      |

| Tsuneo Shibazaki       | EIAJ                                     | Secretariat                          |

| Koji Kitada            | EIAJ                                     | Secretariat                          |

$Table\ 2-Institute\ of\ Systems\ \&\ Information\ Technologies\ /\ KYUSHU$

| Name                                              | Representing                       | Participation   |

|---------------------------------------------------|------------------------------------|-----------------|

| Hiroto Yasuura                                    | First Research Laboratory Director | Investigation   |

|                                                   | Also Prof. of Kyushu University    | Editing Roadmap |

| Hiroshi Date First Research Laboratory Researcher |                                    | Investigation   |

|                                                   | Doctor of Engineering              | Editing Roadmap |

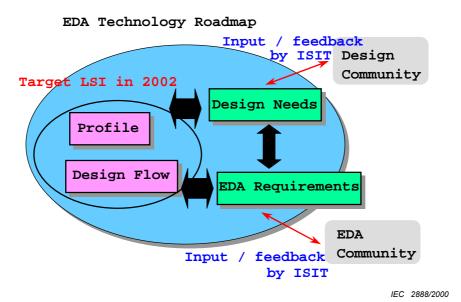

Figure 2 shows the roadmap development concept. In the EDA Vision Working Group, Cyber-Giga-Chip Profile WG and EDA Requirement WG are organized. Cyber-Giga-Chip Profile WG forecasted the profile and the design flow of Cyber-Giga-Chip in 2002. EDA Requirement WG analyzed the requirements of LSI designers from the viewpoint of EDA technology, and made a detailed roadmap toward 2002. Entrusted by EIAJ, ISIT/KYUSHU collected information from LSI designers, investigated the trend of EDA technology, and edited the roadmap. Specifically, ISIT/KYUSHU interviewed for LSI designers working for companies, which belonged to EDA Vision Working Group, and summarized the results as requirements of designers. This was followed by interviews with EDA engineers and investigation on EDA technology. Finally, EIAJ and ISIT/KYUSHU edited the content of the activity as a roadmap.

Figure 2 - Roadmap Development Concept

# 1.6 How to Utilize the Roadmap

Some suggested uses of the roadmap are:

- For system LSI designers: To determine the most suitable design environment for their system LSIs. The roadmap will suggest a design environment for each category of system LSI.

- For semiconductor manufacturers: To determine business strategies for system LSIs in their organizations. An LSI design tool will act as an important interface between users and semiconductor manufacturers. Each semiconductor manufacturer must decide its business tactics; whether to specialize in fabrication only; proceed with vertically integrated industries from system design to fabrication, or to take an intermediate course.

- For EDA engineers: To determine the most profitable EDA tool for system LSIs.

- For EDA researchers: To discuss what is the fundamental technology for future EDA.

# 2. Executive Summary

In this chapter, we present the basic policies of the EDA Technology Roadmap toward 2002. The main purpose of the roadmap is to predict:

- 1) The objects for the LSI design and their environment in 2002,

- 2) EDA technology in 2002.

# 2.1 Semiconductor Industry in 2002

In this section, we summarize interviews concerning, firstly what kind of LSI will be designed (the objects for the LSI design) in 2002 and, secondly how they will be designed (LSI design environment) in 2002.

# 2.1.1 Overview of Design Objects in 2002

The technique for designing a system LSI could be considered equivalent to that for designing a target system itself. The main question is what sort of system should be built by making use of several ten million transistors, and this decision may influence the future direction of the semiconductor industry. system LSIs will be used in a wide spectrum of applications, such as computers, electric appliances, toys, cars, optical machinery, industrial robots, and social systems. In this section, we will predict the potential application areas for system LSIs and examine the requirements of system LSIs specific to each application.

## 1) Embedded systems

Embedded systems are widely used in electric appliances, cars, industrial robots, communication devices and even toys (entertainment gadgets), all of which are basic commodities in modern day life. System LSIs will play a central role in embedded systems. Unfortunately, they cannot be designed and manufactured effectively enough in the current framework, and there is a call for a breakthrough in design methods to overcome the problems. The new design methods will be required to coordinate individual component technologies in software, hardware, package, display parts and machine parts and optimize the entire system. Each application has a different set of requirements. Safety and reliability are indispensable factors to medical equipment. On the other hand, promptness and productivity are important in electric appliances and entertainment gadgets, as their lifecycles have shortened dramatically in recent years. The design of system LSIs should reflect the needs of each application area.

## 2) Network devices

A variety of communication forms such as image, sound and text are used in network. This revolutionary move has created a new social structure sometimes termed as multimedia society. In order to send a mixed form of image, sound, and text across a network, data needs to be transformed. Such processing includes data compression and restoration, coding, encryption and decryption, etc. The same procedure must be performed at sending and receiving ends, since the standard protocols are defined in network communication. If the connected systems contain some human errors and cause malfunction, the entire network (in the worst case, the Internet which spans the globe) may behave abnormally. Communication circuits should be standardized and used as fixed parts in system LSIs. This will promote the reuse of communication circuits as well as stabilization of the network. With a view to such development, the reuse of integrated circuit design, the definitive procedure to claim integrated design as intellectual property, and suitable criteria for macro library are being discussed. In addition, analog circuits are thought to be important in radio/wireless communication.

# 3) Information technology for social infrastructure

Information technology for building the social infrastructure will be a potential market for system LSIs. What we call "information technology for social infrastructure" has two missions. One is an information system that monitors and controls the social infrastructure (buildings, traffic, railways, electricity, water, gas and telecommunication) This helps a smooth running of social activities. The other is the information system that deals with unpredictable catastrophes. This will assist effective data acquisition, assimilation, transmission, processing and controls in disasters. Real-time processing and safety are essential of the information system and embedded system LSIs. In addition, there is a desire for those systems to operate using reusable and environmental-friendly energy such as solar energy. Electric money is an application of system LSI in the economic system. This is an electric substitute for paper notes and metal coins and is usually stored in an IC card (Smartcard). Smartcard and its associated equipment are expected to create a big market for system LSI. The system LSI for smartcards must, above all, guarantee high reliability to protect the privacy of cardholders against deliberate attacks, fraud and forgery. This means that cryptographic technology must be incorporated in system LSI design. In addition, R&D efforts should be put into submicron technology, to increase the security level.

# 4) High performance computer systems

The computer system industry is the biggest marketplace for the semiconductor industry and has motivated the semiconductor industry to make epoch-making progress in high performance processors. The demands from supercomputing will continue to guide the development of high performance system LSIs. In particular, scientific computation in fields of genome analysis, molecular dynamics, fluid dynamics, and space development will put pressure on the improvement of high quality performance system LSIs. Massively parallel system will serve as a good design model for the forthcoming system LSI design. Mixed technology of DRAM and logic, and functional memory technology are expected to show enormous progress.

# 5) Personalized digital equipment

Personal computers have become a widespread commodity in the modern life due to their compactness and portability, and have contributed to the expansion of the semiconductor industry. This spread of personalized digital equipment will continue in aid of the Internet and multimedia technology. The requirements for those systems will not only be high performance, but also cost reduction and low power consumption. Moreover, the progress in sensor technology, digital/analog merged integrated circuits technology and high performance technology is important to meet the demands in multimedia and HCI (human-computer interaction) technology.

Having considered the above mentioned potential applications, system LSIs can be classified into the three categories.

# 1) Process-oriented LSI

Like the former DRAM, this LSI is relatively stable in terms of product specification, and can compete with others to achieve a world record by making good use of the latest process technology. It is designed for mass-product, and several years are usually spent in designing. Its performance is moderately high, combining the existing logic and circuits and aiming at mass-product.

### 2) Performance-oriented LSI

The LSI's specification, including those at the architecture level, are at the discretion of the design side, although its framework is fixed just like the microprocessor. It is designed by making good use of advanced design technology at every design level, such as architecture, logic, circuits and layouts. However, the latest processes are not necessarily used. So the difference in the design technology becomes quite apparent. Sometimes, several years are spent in designing. Such fields are called leading edge system LSI.

### 3) Market-oriented LSI

This is a widely used LSI, because many systems adopt it. Many LSIs that are used in various built-in systems and information telecommunication equipment, etc. are classified in this field. Most of them are being developed in a short period because their market value is decided by the time function. System LSI included in this classification should deal with various specifications of the system in addition to short-term development. It should be based on the technology which optimizes the performance of LSI by using a standard core for a specific usage. The system LSI which will become the main stream in the future will be included in this classification. Because of the unification of system and LSI design, the traditional design method cannot be applied. This LSI could be considered to have a form suitable for the vertical and integrated industrial structure in Japan.

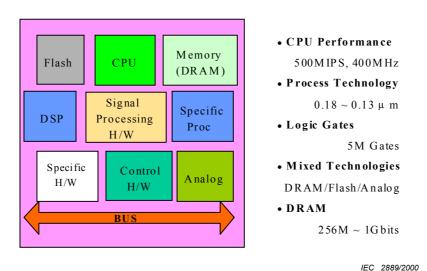

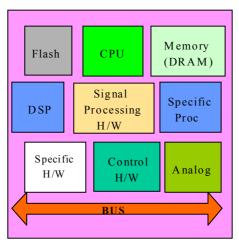

In this roadmap, we focus on a market oriented LSI, especially, a system LSI which has a core based on the leading edge technology in 2002. We named such a core-based system LSI as "Cyber-Giga-Chip(CGC)". Figure 3 shows the specification of CGC. CGC has several such cores, and is used as a kernel of a system. Chapter 3 explains the specification and summarizes the results from the interviews with LSI designers from the viewpoint of "what will be needed in EDA technology for the design of CGC".

Figure 3 – Profile of Cyber-Giga-Chip in 2002

# 2.1.2 Overview of Design Environments in 2002

With the progress and spread (wide acceptance) of network and database technology, various collaborated works between different organizations will be possible. The platform for parallel processing has advanced, which can be a potential candidate for the use of EDA tools in distributed environments.

In the case of process-oriented LSI, it is important to develop a good process and to utilize the characteristics of the process. Therefore, it is thought that the relation between the process technology and the EDA technology becomes stronger. As in the case of supercomputing, design methodology and EDA technology for the performance oriented system LSIs will be limited to a group of organizations. In market oriented system LSIs, design methodology and EDA technology will be supported by various industrial demands and EDA technology will therefore continue to develop. In application-specific system LSIs, CAD technology is seen as a fundamental technology for a two-way (upward and downward) silicon compiler between system level and process level. As application-specific system LSI design is involved in multi-level system descriptions, different styles of IP descriptions, and a hardware/software mixed system, and verification of design becomes important. Methods to distinguish "good" IPs from "bad" IPs are also required.

# 2.2 EDA Technology in 2002

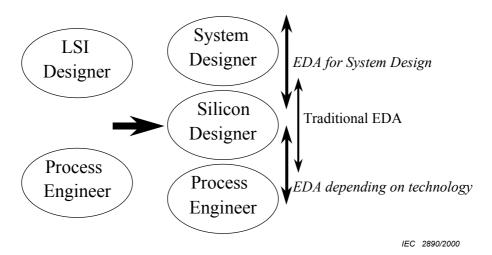

With a spread of system LSIs, LSI design method based on core processors will become main stream, as shown in Figure 4, and the LSI design flow will be changed accordingly. The design workload is partitioned into system designers, silicon designers and process designers. The current practice of LSI design is that several LSIs are used, and the job of a system designer is merely to combine these LSIs to produce an "optimal" system.

Therefore, LSI and process design are proceeded independently of each other. However, in order to design an "optimal" system LSI for "optimal" system, the system designer must consider the best means to achieve the "optimal" system at hand under the given circumstances. CAD tools for system designers are desirable to assist with this job. Once the specifications of the system LSI are fixed, silicon designers take part in designing each processor core using the existing CAD tools. At present, design rules are provided prior to system design, prohibiting the possibility of process design changes. Design rules may have to be modified to produce an optimal system LSI. Hence, new process-dependent CAD tools which can deal with modifications of the process technology are desirable.

Figure 4 – Design Flow of Core Based System LSIs

The application fields of system LSIs are various. Therefore, the priority of each EDA technology needed in 2002 changes according to the design target of the system LSI. Chapter 4 explains each item concerning EDA technology problems. Chapter 5 forecasts the design flow of CGC in 2002, and shows what kinds of EDA technology are necessary to design CGC. The following paragraphs show the outline of EDA technology problems in 2002. The details are described in Chapter 4.

The problems and the counter measures concerning EDA technology are summarized along the design flow of hardware and software. As for hardware design, we have divided it into digital circuits and analog circuits. Moreover, in digital circuit design, problems of EDA technology are classified into specification, estimation, verification, synthesis, and test.

Table 3 – EDA Technology Problems of Digital Circuit Design (System Design to Architecture Design)

|                 |                                                                               |                                                                      | Digital                                                                     |                                                  |                                                        |

|-----------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------------|

|                 | A Specification                                                               | B Estimation                                                         | C Verification                                                              | D Synthesis                                      | E Test                                                 |

| 1.              | 1A(1)                                                                         | 1B(1)                                                                | 1C(1)                                                                       | 1D(1)                                            | 1E(1)                                                  |

| System          | Standard System<br>Level Modeling                                             | Performance<br>Estimation of                                         | System Level<br>Simulation                                                  | Hardware/Software<br>Partitioning                | Test Strategy Decision for System (Hardware/ Software) |

|                 | 1A(2)<br>Standard System<br>Description<br>Language (SLDL<br>etc.)            | System (Application<br>Software/ Compiler/<br>Hardware)              | System Level Emulation  1C(3) Formal Verification (System Spec. vs. System) | 1D(2) System Level Library (IP Core, Middleware) |                                                        |

| 2. Architecture | 2A(1) Standard Architecture Level Modeling (Including Domain Specific Models) | 2B(1) Architecture Level Estimation (Area, Timing, Power, Floorplan) | 2C(1) Formal Verification (-System vs. Architecture)                        | 2D(1) Architecture Synthesis                     | 2E(1) Test Strategy Decision for Architecture          |

|                 | 2A(2) Standard Architecture Description Language (VerilogHDL, VHDL etc.)      | 2B(2) Budgeting (Area, Timing, Power, Floorplan) for RTL             | 2C(2) Validation Simulation                                                 | 2D(2)<br>Co-Synthesis                            | 2E(2) Architecture Level DFT                           |

Table 3 shows EDA technology problems in system design and architecture design of a digital circuit. In system design, it is necessary to deal with Standard System Level Modeling, Standard System Description Language (SLDL etc.), System Level Simulation, Performance Estimation of System (Application Software/ Compiler/ Hardware), System Level Emulation, Formal Verification (System Spec. - System), Hardware/Software Partitioning, System Level Library (IP Core, Middleware), and Test Strategy Decision for System (Hardware /Software). In architecture design, the items are Standard Architecture Level Modeling (Including Domain Specific Models), Standard Architecture Description Language (Verilog HDL, VHDL etc.), Architecture Level Estimation (Area, Timing, Power, Floorplan), Budgeting (Area, Timing, Power, Floorplan) for RTL, Formal Verification (System - Architecture), Validation / Simulation, Architecture Synthesis, Co-Synthesis, Test Strategy Decision for Architecture, and Architecture Level DFT.

Table 4 shows the technical issues of EDA ranging from RTL / logic design to manufacture interface in a digital circuit design. In RTL/logic design, it is necessary to consider problems, such as, Standard RTL (Synthesizable) Modeling (Including Graphical Model), Standard RTL Description Language (Verilog HDL, VHDL etc.), RTL Estimation (Area, Timing, Power, Floorplan), Budgeting (Area, Timing, Power, Floorplan) for Logic Synthesis, Power-rail Estimation, False path free Timing Analysis, Formal Verification (Architecture - RTL, RTL - Gate), Function/Timing Verification beyond Gate Level Simulation, Test Pattern Generation for Mixed IP Chip on Function and Timing Verification, Timing Driven Synthesis, Reverse Synthesis (from Gate to RTL), RTL Synthesis, Incremental Design Methodology, Logic Synthesis with Parameterized Cell/Macro Library (Vdd and Vth), Timing Budgeting and Function Porting for Mixed IP chip, Standard DFT Interface for both IPs and inter IPs, Design for Fault Diagnosis, and Multiple Fault Models & Test Methods. In the circuit, it is necessary to take account of the Process Variation Model (Accurate Circuit Simulation), Power/Noise/Electro-magnetic Analysis, Accurate Model for DSM Process, Parameter Extraction, Timing Verification on Real Environment (consider Package, Board etc), Transistor Circuit & Layout Synthesis (from RT/Gate Level), Parameterized Cell/Macro Library Generation and Simulation with Vdd and Vth Variation, and Performance Constraint Driven Process Migration. In a layout design, we have to consider Standard Physical Description Language, High-speed Verification, Power-rail Routing, Simulation based Layout Synthesis, High speed Mask Data Processing, Decision Support for Multi-Layer Routing, Layout Synthesis with Parameterized Cell/Macro Library (Vdd and Vth), and Layout Design for Test. Speeding-up of mask processing is a big problem concerning the interface to the manufacturing equipment.

Table 4 – EDA Technology Problems of Digital Circuit Design (RTL to Manufacture Interface)

|                                |                                                                     |                                                                | Digital                                                                        |                                                                                             |                                                                  |

|--------------------------------|---------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------|

|                                | A Specification                                                     | B Estimation                                                   | C Verification                                                                 | D Synthesis                                                                                 | E Test                                                           |

| 3.<br>RTL/Logic                | 3A(1)<br>Standard RTL<br>(Synthesizable)<br>Modeling (Including     | 3B(1)<br>RTL Estimation (Area,<br>Timing, Power,<br>Floorplan) | 3C(1) False path free Timing Analysis                                          | 3D(1)<br>Timing Driven<br>Synthesis                                                         | 3E(1)<br>Standard DFT<br>Interface for both IPs<br>and inter IPs |

|                                | Graphical Model)                                                    | 3B(2) Budgeting (Area, Timing, Power, Floorplan) for Logic     | 3C(2) Formal Verification (-Architecture vs. RTL)                              | 3D(2)<br>Reverse Synthesis<br>(from Gate to RTL)                                            |                                                                  |

|                                |                                                                     | Synthesis                                                      | (-RTL vs. Gate)                                                                | 3D(3)<br>RTL Synthesis                                                                      |                                                                  |

|                                | 3A(2)<br>Standard RTL<br>Description Language<br>(Verilog HDL, VHDL | 3B(3)<br>Power-rail Estimation                                 | 3C(3)<br>Function/Timing<br>Verification beyond<br>Gate Level Simulation       | 3D(4)<br>Incremental Design<br>Methodology                                                  | 3E(2) Design for Fault Diagnosis, Multiple Fault Models & Test   |

|                                | etc.)                                                               |                                                                | 3C(4)                                                                          | 3D(5)                                                                                       | Methods                                                          |

|                                |                                                                     |                                                                | Test Pattern Generation for Mixed IP Chip on Function and Timing               | Logic Synthesis with<br>Parameterized<br>Cell/Macro Library<br>(Vdd and Vth)                |                                                                  |

|                                |                                                                     |                                                                | Verification                                                                   | 3D(6) Timing Budgeting and Function Porting for Mixed IP chip                               |                                                                  |

| 4.<br>Circuit                  |                                                                     | 4B(1) Process Variation Model (Accurate Circuit Simulation)    | 4C(1)<br>Power, Noise, Electro-<br>magnetic Analysis                           | 4D(1) Transistor circuit & Layout Synthesis (from RT/Gate Level)                            |                                                                  |

|                                |                                                                     |                                                                | 4C(2) Accurate Model for DSM Process, Parameter Extraction                     | 4D(2) Parameterized Cell/Macro Library Generation and Simulation with Vdd and Vth Variation |                                                                  |

|                                |                                                                     |                                                                | 4C(3)                                                                          | 4D(3)                                                                                       |                                                                  |

|                                |                                                                     |                                                                | Timing Verification on<br>Real Environment<br>(consider Package,<br>Board etc) | Performance<br>Constraint Driven<br>Process Migration                                       |                                                                  |

| 5.                             | 5A(1)                                                               |                                                                | 5C(1)                                                                          | 5D(1)                                                                                       | 5E(1)                                                            |

| Layout                         | Standard Physical Description Language                              |                                                                | High-speed<br>Verification                                                     | Power-rail Routing                                                                          | Layout Design for Test                                           |

|                                | Best puon Eunguage                                                  |                                                                | , eminemon                                                                     | 5D(2)<br>Simulation based                                                                   |                                                                  |

|                                |                                                                     |                                                                |                                                                                | Layout Synthesis 5D(3)                                                                      |                                                                  |

|                                |                                                                     |                                                                |                                                                                | High speed Mask Data Processing                                                             |                                                                  |

|                                |                                                                     |                                                                |                                                                                | 5D(4)                                                                                       |                                                                  |

|                                |                                                                     |                                                                |                                                                                | Decision Support for<br>Multi-Layer Routing                                                 |                                                                  |

|                                |                                                                     |                                                                |                                                                                | 5D(5)                                                                                       |                                                                  |

|                                |                                                                     |                                                                |                                                                                | Layout Synthesis with<br>Parameterized<br>Cell/Macro Library<br>(Vdd and Vth)               |                                                                  |

| 6.<br>Manufacture<br>Interface |                                                                     |                                                                |                                                                                | 6D(1) Interface Technology for Mask Manufacturing                                           |                                                                  |

Table 5 - EDA Technology Problems of Analog Circuit Design

|                          | F Analog                                               |

|--------------------------|--------------------------------------------------------|

| 1. System                |                                                        |

| 2. Architecture          |                                                        |

| 3. RTL/Logic             | 3F(1)                                                  |

|                          | Standard Analog Modeling (for Mixed Signal Simulation) |

|                          | 3F(2)                                                  |

|                          | Analog/Digital Mixed Signal Simulation                 |

|                          | 3F(3)                                                  |

|                          | System Level Analog Modeling                           |

|                          | 3F(4)                                                  |

|                          | Synthesis from AHDL                                    |

| 4. Circuit               |                                                        |

| 5. Layout                | 5F(1)                                                  |

|                          | Analog Cell Generation                                 |

| 6. Manufacture Interface |                                                        |

Table 5 shows EDA technology problems in the analog circuit design. It is necessary to deal with Standard Analog Modeling (for Mixed Signal Simulation), Analog/Digital Mixed Signal Simulation, System Level Analog Modeling, Synthesis from AHDL, and Analog Cell Generation.

G Software H Entire design G(1)H(1)OS Generation/ Customization Design Re-use H(2) G(2)Software Core Generation/ Customization Design Flow Management G(3) H(3) Software Compiler Generation Asynchronous Circuit Design Unified Software Development Platform for various IP Cores G(5)

Table 6 - Problems of EDA Technology in Software Design and Entire design

Table 6 shows technological problems of EDA in the software design as well as the entire design. In the software design, it is necessary to deal with OS Generation/Customization, Software Core Generation/Customization, Software Compiler Generation, Unified Software Development Platform for various IP Cores, and Software/Hardware Co-Simulation. It is necessary to deal with Design Re-use, Design Flow Management, and Asynchronous Circuit Design over the entire design.

# 2.3 Outline of the Roadmap

Software/Hardware Co-Simulation

This roadmap employs two basic policies. Firstly, the roadmap is intended to be effective only for 5 years. The reason for this rather short period of time is a roadmap showed to be as realistic and practical as possible. 5 years is a good period to draw up a realistic timetable for various EDA foundation technologies. Secondly, the roadmap is intended to address the issues raised from not only EDA engineers but also from LSI designers. Thus we hope that the roadmap will encompass the seed (i.e. the technology EDA engineers can offer) and the need (i.e. the requirements LSI designers must meet) for future LSI design.

We employed the following research method to write the roadmap. Firstly, we interviewed active LSI designers on site and summarized their requirements in LSI design. Secondly, we proposed a model of system LSI for the next generation, named "Cyber-Giga-Chip". Lastly, We classified each system LSI into categories according to its business model. The roadmap suggests the ideal design method for each category and points out problems associated with the design method. The problems are examined on the basis of specification, performance estimate, verification, implementation, and testing from EDA technology perspective. We have also included our comments on each problem. The following describes the expected picture of the semiconductor industry in 2002 and analyzes the requirements of the semiconductor industry for EDA technology.

# 3. Requirements for EDA Technology

The purpose of this chapter is to specify the environment that surrounds the EDA technology. To be more specific, we define a system LSI called Cyber-Giga-Chip as a design target in 2002 and analyze the demand for EDA technology.

# 3.1 Profile of Cyber-Giga-Chip

In this roadmap, our target is the system LSI which is designed with the latest technology in its period. In order to provide basic information for defining the system LSI, the investigation result concerning the characteristic of the system LSI in 2002 is shown.

- 1) Merged memory and logic technology: Memories such as DRAM and SRAM, a processor, and a DSP are merged into a single chip. System LSI with 32-bit microcomputer and DRAM would be in the mainstream.

- (2) Mixed digital and analog technology: A digital circuit and an analog circuit are combined. The system realizes each function by a program, and analog technology is applied only at a minimum level. However, analog technology should be regarded as important for design, since it becomes the key of differentiation.

- (3) Combination of a sensor and an analog circuit: By combining a sensor and an analog circuit, a process unifying data compression and recognition is conducted within a chip.

- (4) Parallel Processing: On-chip RISC multiprocessor (MIMD) is the main type of CPU for system LSI. It is applied to a portable equipment for multimedia. In the system, the hardware is standard whereas the software is more diversified.

- (5) Fault-tolerant: Technology such as duplex control in a chip is used in the field where high reliability is required.

- (6) Wireless system core: A wireless system core is built in the system LSI for communication.

- (7) Specification of high-end processor: Listed below are the specifications of a high-end processor which were investigated to predict the spec of the system LSI in 2002. The results: clock frequency, 1GHz; the number of transistor, 500M-1G (including a logic part consisting of 50M-100M transistors); power consumption, 50-60W; power-supply voltage, 1-1.5V; and process technology, CMOS. It is worth nothing that the number of I/O pins of high performance processors for the super computer is 1000-2000 because of adoption of the multiprocessor.

The specification of the system LSI for specific uses in 2002 is defined based on these investigation results. It is called *Cyber-Giga-Chip*, abbreviated as CGC. CGC, whose profile is shown in Figure 5, consists of such cores as CPU, DSP, memory, and so on. Merged memory/logic technology and mixed digital/analog technology are important too.

- CPU Performance 500MIPS, 400MHz

- Process Technology

$0.18 \sim 0.13 \ \mu \ m$

• Logic Gates

5M Gates

- Mixed Technologies

DRAM/Flash/Analog

- DRAM

256M ~ 1Gbits

IEC 2891/2000

Figure 5 – Profile of Cyber-Giga-Chip in 2002

Table 7 shows the specification of the core in CGC. In 2002, the semiconductor manufacturing technology will use 0.13 to 0.18µm rule; the clock frequency of CPU cores will be 400MHz; the performance of DSP cores, 3GOPS; the transmission speed of the internal bus, 4 G bytes per second; the display performance for 3-dimensional graphics, 5GFLOPS; the power consumption of an analog / digital converter, 2 mW; the number of logic gates, 5M; and the size of DRAM, 256M to 1G bits. Process lines of CGC and high-end processors are different, because CGC consists of a various kind of cores. Therefore, the clock frequency of CPU cores is a half as compared with high-end processors.

Table 7 – Specification of Cores for Cyber-Giga-Chip

| Embedded Cores           | 1997                      | 2002                   | 2007                |

|--------------------------|---------------------------|------------------------|---------------------|

| Process                  | 0.25μm                    | $0.18 \sim 0.13~\mu m$ | $0.1\sim0.07~\mu m$ |

| СРИ                      | 100 MIPS<br>100 MHz       | 500 MIPS<br>400 MHz    | 3 GIPS<br>650 MHz   |

| DSP                      | 1 GOPS                    | 3 GOPS                 | 10 GOPS             |

| BUS                      | 3 GB                      | 4 GB                   | 10 GB               |

| 3 D Graphic<br>(Display) | 1 G Flops                 | 5 G Flops              | 60 G Flops          |

| Analog (ADC)             | 5 mW<br>(10 bits 20 MS/s) | 2 mW                   | -                   |

| DRAM                     | 64 Mbits                  | 256 M ~ 1 Gbits        | 1 ∼ 4 Gbits         |

MS/s = Mega Sample/second

# 3.2 Requirements for EDA Technology

This section summarized those requirements for the EDA technology that were obtained via the interview of LSI designers. The design process consists of system design, architecture design, RTL design, logic design, circuit design, layout design, test design, mask design, package design, and testing. It is classified into one group for each design phase and one more group for the entire design.

Table 8 summarizes the EDA requirements obtained from LSI designers. In the table, rows show the design targets and column show the design phases.

Category Power Funct TAT ΙP DSM Speed Reliab Others Size Sub-Design ility lion total Process Product Spec. System/Algorithm Architecture RTL Logic Circuit Test Layout Mask Package Testing Others Sub-total

Table 8 - LSI Design Requirements Table

The table shows the number of items pointed out as demands.

# **Requirements in System Design**

- (1) To date, software, analog circuits, digital circuits and memory are developed independently. Soon, an integrated system (system LSI) which implements all elements on a single chip will be on market. To respond to demands swiftly, optimization methods for those integrated systems will be necessary.

- (2) A standard system design description will be necessary. Writing comprehensive specifications is an important problem in system LSI design.

- (3) Semiconductor designers may have to develop software for the chip. In such circumstances, program development tools, such as compiler, on-chip debugger, or on-chip ICE (In Circuit Emulator) will be necessary.

- (4) The abilities to describe accurately, understand, and verify the specification, are vital to improve the efficiency of LSI design. In particular, It is important for silicon designers to communicate with system designers. Therefore, it is desirable to develop methods and tools that assist such communications.

- (5) It is necessary to develop EDA tools that assist Hardware/Software co-design using hard-cores and soft-cores.

- (6) The modeling for CPU cores becomes more important as more functions are implemented on a CPU core. Simulation models incorporating CPU cores or architecture-level simulator for pipeline will be necessary.

- (7) Design methods for CPU architecture, to minimize the program size, and communication tools for OS, compiler and LSI engineers will be necessary. Parts for communication will be reused as standard modules. A Hardware/Software co-design environment will be necessary, for instance high-speed emulator with FPGA that can debug on OS even if a chip is not completed.

- (8) It is difficult to improve multi-level circuits and analog circuits, because Vdd mould drop down. The use of analog circuits will be limited as much as possible. Using DC-DC converter, the user interface will be implemented using analog circuits, while inside will be implemented using digital circuits.

- (9) High-level design tool such as those for evaluating tradeoff between frequency and the number of gates will be necessary.

- (10) A power management system, which controls the internal voltage, will be introduce at various levels. A design tool for power management, such as sleep control, will be necessary. For example, a statement meaning "Shut off the power" should be included in the HDL (Hardware Design Language).

- (11) The discrepancy between architecture level and RT level must be resolved immediately. An automatic synthesis tool from architecture level to RT level, or verification tool within the architecture level will be necessary. Moreover tools that automatically inserts latches for pipeline processing will be necessary.

- (12) Layout tools, such as a placement and routing tool based on timing profiling simulator, a multi-layer placement and routing modeling and tool, and a tool for analyzing coupled wires, will be necessary.

### **Performance Estimation**

- (13) Currently, elements such as software, analog, digital, or memory are designed separately. However, in system LSI design, these are integrated into a chip as a consolidation system. Therefore, the performance estimation technology for consolidated system becomes important.

- (14) The performance of a high-speed processor depends heavily on the quality of its implementation. Therefore, performance estimation tools for the pipeline and the cash are necessary.

- (15) Power estimation technology in system level CAD (analog/digital total simulation) is also necessary.

- (16) Activation rate analysis tools which uses dynamic test patterns are necessary to estimate the power consumption of RAM and ROM.

- (17) In embedded system, the demand for product performance is severe such as fanless or finless. Accurate modeling of power consumption is demanded.

# **Analog Design**

- (18) Efficiently designing a analog circuit leads to the efficiency improvement of system LSI design. Partitioning technology of analog and digital, total verification of analog/mixed circuit, and analog HDL become important.

- (19) Design verification techniques for analog/mixed circuit, design for test, auto test pattern generation, and test pattern description are in new research fields. The development of a new design technology is expected. In particular, testing of the analog/mixed circuits including active components is a research and development object rife with difficult problems.

- (20) In analog/mixed circuit, digital noise is a big problem for the analog circuit. It is necessary to handle the noise as a system problem, including the substrate and the package. Analog/digital total simulation to analyze the noise and the noise simulation technology are necessary. Moreover, it is necessary to discuss how much knowledge the system designer should have.

- (21) How to speed up the external clock is also important. Speed-up of the interface, design and power supply of the board, and uniting of the internal chip technology and the board technology, are needed. Total simulation technology, including the board, is needed to achieve freedom from skew problems.

- (22) The techniques and tools are necessary to lead low power consumption design by appropriately using analog/digital/sensor circuit.

# **Design Property Reuse**

- (23) The design reuse technology of the digital circuit and the analog circuit is extremely important. It is necessary that the reused circuit need not be used as it is, but designers are able to modify it.

- (24) The enhancement of the modeling technology for CPU core becomes important, because CPU cores will become more multi-functional.

- (25) The reuse technology of the processor core will be important. The core of CPU and DSP will be standardized for efficient software development. Property designed in a language can be reused when it is well verified.