# LICENSED TO MECON Limited. - RANCHI/BANGALORE FOR INTERNAL USE AT THIS LOCATION ONLY, SUPPLIED BY BOOK SUPPLY BUREAU

# NORME INTERNATIONALE INTERNATIONAL STANDARD

CEI IEC 60677

Première édition First edition 1980-01

Transferts de bloc dans les systèmes CAMAC

**Block transfers in CAMAC systems**

### Numéros des publications

Depuis le 1er janvier 1997, les publications de la CEI sont numérotées à partir de 60000.

### Publications consolidées

Les versions consolidées de certaines publications de la CEI incorporant les amendements sont disponibles. Par exemple, les numéros d'édition 1.0, 1.1 et 1.2 indiquent respectivement la publication de base, la publication de base incorporant l'amendement 1, et la publication de base incorporant les amendements 1 et 2.

### Validité de la présente publication

Le contenu technique des publications de la CEI est constamment revu par la CEI afin qu'il reflète l'état actuel de la technique.

Des renseignements relatifs à la date de reconfirmation de la publication sont disponibles dans le Catalogue de la CEI.

Les renseignements relatifs à des questions à l'étude et des travaux en cours entrepris par le comité technique qui a établi cette publication, ainsi que la liste des publications établies, se trouvent dans les documents cidessous:

- «Site web» de la CEI\*

- Catalogue des publications de la CEI Publié annuellement et mis à jour régulièrement (Catalogue en ligne)\*

- Bulletin de la CEI

Disponible à la fois au «site web» de la CEI\*

et comme périodique imprimé

## Terminologie, symboles graphiques et littéraux

En ce qui concerne la terminologie générale, le lecteur se reportera à la CEI 60050: *Vocabulaire Electrotechnique International* (VEI).

Pour les symboles graphiques, les symboles littéraux et les signes d'usage général approuvés par la CEI, le lecteur consultera la CEI 60027: Symboles littéraux à utiliser en électrotechnique, la CEI 60417: Symboles graphiques utilisables sur le matériel. Index, relevé et compilation des feuilles individuelles, et la CEI 60617: Symboles graphiques pour schémas.

Voir adresse «site web» sur la page de titre.

### Numbering

As from 1 January 1997 all IEC publications are issued with a designation in the 60000 series.

### Consolidated publications

Consolidated versions of some IEC publications including amendments are available. For example, edition numbers 1.0, 1.1 and 1.2 refer, respectively, to the base publication, the base publication incorporating amendment 1 and the base publication incorporating amendments 1 and 2.

### Validity of this publication

The technical content of IEC publications is kept under constant review by the IEC, thus ensuring that the content reflects current technology.

Information relating to the date of the reconfirmation of the publication is available in the IEC catalogue.

Information on the subjects under consideration and work in progress undertaken by the technical committee which has prepared this publication, as well as the list of publications issued, is to be found at the following IEC sources:

- IEC web site\*

- Catalogue of IEC publications

Published yearly with regular updates

(On-line catalogue)\*

- IEC Bulletin

Available both at the IEC web site\* and as a printed periodical

## Terminology, graphical and letter symbols

For general terminology, readers are referred to IEC 60050: *International Electrotechnical Vocabulary* (IEV).

For graphical symbols, and letter symbols and signs approved by the IEC for general use, readers are referred to publications IEC 60027: Letter symbols to be used in electrical technology, IEC 60417: Graphical symbols for use on equipment. Index, survey and compilation of the single sheets and IEC 60617: Graphical symbols for diagrams.

\* See web site address on title page.

# LICENSED TO MECON Limited. - RANCHI/BANGALORE FOR INTERNAL USE AT THIS LOCATION ONLY, SUPPLIED BY BOOK SUPPLY BUREAU

# NORME INTERNATIONALE INTERNATIONAL STANDARD

CEI IEC 60677

Première édition First edition 1980-01

Transferts de bloc dans les systèmes CAMAC

**Block transfers in CAMAC systems**

© IEC 1980 Droits de reproduction réservés — Copyright - all rights reserved

Aucune partie de cette publication ne peut être reproduite ni utilisée sous quelque forme que ce soit et par aucun procédé, électronique ou mécanique, y compris la photocopie et les microfilms, sans l'accord écrit de l'éditeur.

No part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from the publisher.

International Electrotechnical Commission

Telefax: +41 22 919 0300

on 3, rue de Varembé Geneva, Switzerland e-mail: inmail@iec.ch IEC web site http://www.iec.ch

Commission Electrotechnique Internationale International Electrotechnical Commission Международная Электротехническая Комиссия

CODE PRIX

PRICE CODE

R

Pour prix, voir catalogue en vigueur For price, see current catalogue

### SOMMAIRE

|    |            |                                                                                                                                                                 | Pages    |

|----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| PR | ÉAME       | BULE                                                                                                                                                            | 4        |

|    |            | E                                                                                                                                                               | 4        |

| ۸  | icles      |                                                                                                                                                                 |          |

|    |            |                                                                                                                                                                 | 6        |

| i. | 1.1<br>1.2 | naine d'application et objet                                                                                                                                    | 6        |

| _  |            | oduction et classification                                                                                                                                      | 6        |

| 2. | 2.1<br>2.2 | Introduction et classification                                                                                                                                  | 6        |

| 3. | Mo         | des de transfert de bloc décrits dans la Publication 516 de la CEI                                                                                              | 14       |

|    | 3.1        | Mode UCS (Arrêt)                                                                                                                                                | 14<br>14 |

|    | 3.2        | Mode ACA (Scrutation d'adresses)                                                                                                                                | 16       |

|    |            | des de transfert de bloc supplémentaires                                                                                                                        | 16       |

| 4. | Mo         | Mode UCW (Arrêt-sur-un-mot)                                                                                                                                     | 18       |

|    | 4.2        | Mode ULS (Synchronisation par LAM, Arrêt)                                                                                                                       | 18       |

|    | 4.3        | Mode UDS (Synchronisation directe, Arrêt)                                                                                                                       | 20<br>20 |

|    | 4.4        | Mode MCA (Action multiregistre)                                                                                                                                 |          |

| 5. |            | mpatibilité                                                                                                                                                     | 22<br>24 |

|    | 5.1<br>5.2 | Mode de transfert de bloc MCA                                                                                                                                   | 24       |

|    | 5.3        | Modes de transfert de bloc ULS, UDS, ULC, UDC, UQC                                                                                                              | 24       |

|    | 5.4        | Modes de transfert de bloc ULS, UDS, ULW, UDW                                                                                                                   | 24       |

| 6. | Co         | nception du matériel                                                                                                                                            | 26       |

|    | 6.1        | Conception des modules — Réponse O                                                                                                                              | 26<br>30 |

|    | 6.2        | •                                                                                                                                                               | 32       |

|    | 6.3        |                                                                                                                                                                 | 34       |

| 7  | . Co       | nsidérations sur le logiciel                                                                                                                                    | 34       |

|    |            | XE A — Autres modes de transfert de bloc                                                                                                                        | 36       |

| ρ  | NNE:       | XE A — Autres modes de transiert de oloc                                                                                                                        | 50       |

| 7  | Table      | aux:                                                                                                                                                            |          |

|    |            | Notation du mode de transfert de bloc                                                                                                                           | 10       |

|    | II. N      | Noms des transferts de bloc                                                                                                                                     | 10       |

| I  | II. A      | Aspects de compatibilité des modes de fin de transfert de bloc sur Arrêt et Arrêt-sur-un-mot                                                                    | 22       |

| j  | v T        | Fransfert de bloc à module unique et à adresse unique: Méthode recommandée pour effectuer des transferts de                                                     |          |

|    | b          | bloc CAMAC dans le mode UCS (Arrêt) et le mode correspondant à synchronisation par LAM                                                                          | 26       |

|    | V. N       | Méthode recommandée pour effectuer des transferts de bloc CAMAC dans le mode ACA (Scrutation d'adresses) et le mode UQC (Répétitif)                             | 28       |

| ,  | VI. N      | Méthode pour effectuer des transferts de bloc CAMAC dans le mode UCW (Arrêt-sur-un-mot) et le mode corres-                                                      |          |

|    | F          | condant à synchronisation par LAM                                                                                                                               | 30       |

|    |            |                                                                                                                                                                 |          |

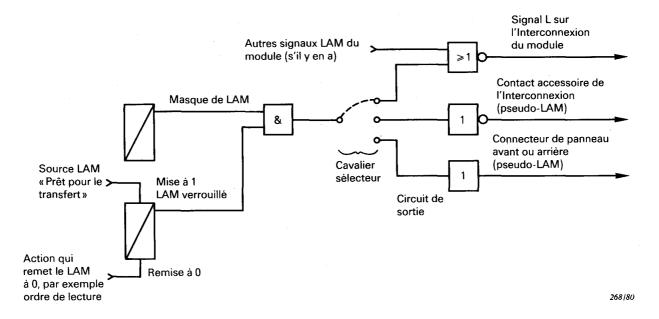

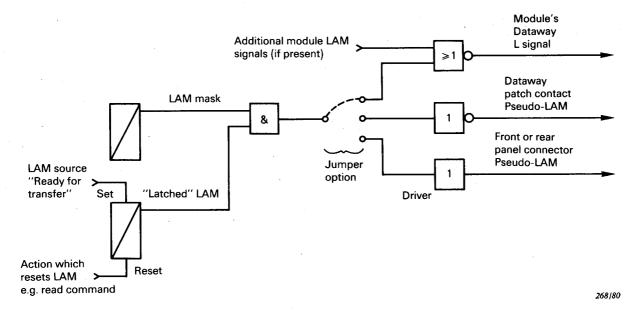

| 1  | FIG.       | <ol> <li>Mise en œuvre recommandée pour un signal LAM de module prévu pour la synchronisation d'un transfert<br/>de bloc. Schéma synoptique simplifié</li></ol> | 32       |

### **CONTENTS**

|     |                                                                                                             | Page   |

|-----|-------------------------------------------------------------------------------------------------------------|--------|

| Fo  | REWORD , ,                                                                                                  | 5      |

| PR  | EFACE                                                                                                       | 5      |

| Cla | isë                                                                                                         |        |

|     |                                                                                                             | _      |

| I.  | Scope and object                                                                                            | 7<br>7 |

|     | 1.1 Scope                                                                                                   | 7      |

|     |                                                                                                             | ,      |

| 2.  | Introduction and classification                                                                             | 7      |

|     | 2.1 Introduction                                                                                            | 7      |

|     | 2.2 Classification of Block Transfer Modes                                                                  | 9      |

| 3.  | Block Transfer Modes described in IEC Publication 516                                                       | 15     |

|     | 3.1 UCS (Stop) Mode                                                                                         | 15     |

|     | 3.2 ACA (Address Scan) Mode                                                                                 | 15     |

|     | 3.3 UQC (Repeat) Mode                                                                                       | 17     |

| 4   | Additional Diody Transfer Mades                                                                             | 17     |

| 4.  | Additional Block Transfer Modes                                                                             | 17     |

|     | 4.2 ULS (LAM Synchronized Stop) Mode                                                                        | 19     |

|     | 4.3 UDS (Direct Synchronized Stop) Mode                                                                     | 21     |

|     | 4.4 MCA (Multi-device Action) Mode                                                                          | 21     |

|     |                                                                                                             |        |

| 5.  | Compatibility                                                                                               | 23     |

|     | 5.1 Block Transfer Mode MCA                                                                                 | 25     |

|     | 5.2 Block Transfer Modes XCX, XLX, XDX                                                                      | 25     |

|     | 5.3 Block Transfer Modes ULS, UDS, ULC, UDC, UQC                                                            | 25     |

|     | 5.4 Block Transfer Modes ULS, UDS, ULW, UDW                                                                 | 25     |

| 6.  | Hardware design                                                                                             | 27     |

|     | 6.1 Module design — Q. Response                                                                             | 27     |

|     | 6.2 Module design — LAM Signal                                                                              | 31     |

|     | 6.3 Interface design                                                                                        | 33     |

| 7   | Software considerations                                                                                     | 25     |

| 7.  | Software considerations                                                                                     | 35     |

|     |                                                                                                             |        |

| A   | PPENDIX A — Other Block Transfer Mode                                                                       | 37     |

|     |                                                                                                             |        |

|     | ibles:                                                                                                      |        |

|     | Block Transfer Mode descriptor                                                                              | 11     |

|     | Block Transfer Names                                                                                        | 11     |

| п   | I. Compatibility Aspects of Stop and Stop-on-Word Block Transfer Termination Modes                          | 23     |

|     | 7. Single module, Single Address Block Transfer: Recommended Method for Performing UCS (Stop) Mode and      |        |

| 1   | corresponding LAM Synchronized CAMAC Block Transfers                                                        | 27     |

| ,   | 7. Recommended Method for Performing ACA (Address Scan) and UQC (Repeat) Mode CAMAC Block Transfers .       | 29     |

|     | . Recommended Method for Ferrorming ACA (Address scarr) and OQC (Repeat) Mode CAMAC Block Hallsters .       | 23     |

| v   | I. Method for Performing UCW (Stop-on-Word) Mode and Corresponding LAM Synchronized CAMAC Block             |        |

| ٧   | Transfers                                                                                                   | 31     |

|     |                                                                                                             | 31     |

| Б   | G. 1. — Recommended implementation of a Module's LAM Signal which is intended for Block Transfer Synchroni- |        |

| Г   | G. 1. — Recommended implementation of a Module's LAM Signal which is intended for Block Transfer Synchroni- | 22     |

### COMMISSION ÉLECTROTECHNIQUE INTERNATIONALE

### TRANSFERTS DE BLOC DANS LES SYSTÈMES CAMAC

### **PRÉAMBULE**

- 1) Les décisions ou accords officiels de la CEI en ce qui concerne les questions techniques, préparés par des Comités d'Etudes où sont représentés tous les Comités nationaux s'intéressant à ces questions, expriment dans la plus grande mesure possible un accord international sur les sujets examinés.

- 2) Ces décisions constituent des recommandations internationales et sont agréées comme telles par les Comités nationaux.

- 3) Dans le but d'encourager l'unification internationale, la CEI exprime le vœu que tous les Comités nationaux adoptent dans leurs règles nationales le texte de la recommandation de la CEI, dans la mesure où les conditions nationales le permettent. Toute divergence entre la recommandation de la CEI et la règle nationale correspondante doit, dans la mesure du possible, être indiquée en termes clairs dans cette dernière.

### **PRÉFACE**

La présente norme a été établie par le Comité d'Etudes N° 45 de la CEI: Instrumentation nucléaire.

Un premier projet fut discuté lors de la réunion tenue à Nice en 1978. A la suite de cette réunion, un projet, document 45(Bureau Central)129, fut soumis à l'approbation des Comités nationaux suivant la Règle des Six Mois en mai 1979.

Les Comités nationaux des pays ci-après se sont prononcés explicitement en faveur de la publication:

| Afrique du Sud (République d') | Finlande |

|--------------------------------|----------|

| Allemagne                      | France   |

| Australie                      | Italie   |

| Autriche                       | Pays-Bas |

| Belgique                       | Pologne  |

| Canada                         | Suède    |

Egypte Tchécoslovaquie

**Espagne** Turquie

Etats-Unis d'Amérique Union des Républiques Socialistes Soviétiques

Autres publications de la CEI citées dans la présente norme:

Publications nos 516: Système modulaire d'instrumentation pour le traitement de l'information; système CAMAC.

Système CAMAC — Organisation des systèmes multichâssis. Spécification de l'Interconnexion de branche et du contrôleur de châssis type A1.

Autre publication: IML: Définition de l'IML, langage à utiliser dans les systèmes CAMAC, ESONE/IML/01, octobre 1974, Secrétariat ESONE, et TID-26615, janvier 1975, DOE, Washington, D.C., Etats-Unis d'Amérique.

### INTERNATIONAL ELECTROTECHNICAL COMMISSION

### **BLOCK TRANSFERS IN CAMAC SYSTEMS**

### **FOREWORD**

- 1) The formal decisions or agreements of the IEC on technical matters, prepared by Technical Committees on which all the National Committees having a special interest therein are represented, express, as nearly as possible, an international consensus of opinion on the subjects dealt with.

- 2) They have the form of recommendations for international use and they are accepted by the National Committees in that sense.

- 3) In order to promote international unification, the IEC expresses the wish that all National Committees should adopt the text of the IEC recommendation for their national rules in so far as national conditions will permit. Any divergence between the IEC recommendation and the corresponding national rule should, as far as possible, be clearly indicated in the latter.

### **PREFACE**

This standard has been prepared by IEC Technical Committee No. 45: Nuclear Instrumentation.

A first draft was discussed at the meeting held in Nice in 1978. As a result of this meeting, a draft, Document 45(Central Office)129, was submitted to the National Committees for approval under the Six Months' Rule in May 1979.

The National Committees of the following countries voted explicitly in favour of publication:

Australia

Austria Netherlands Belgium Poland

Canada South Africa (Republic of)

Czechoslovakia Spain

Egypt Sweden

Finland Turkey

France Union of Soviet Socialist Republics

Italy

Germany United States of America

Other IEC publications quoted in this standard:

Publications Nos. 516: A Modular Instrumentation System for Data Handling; CAMAC System.

552: CAMAC—Organization of Multi-crate Systems. Specification of the Branch-highway and CAMAC Crate Controller Type A1.

Other publication: IML: A Language for use in CAMAC Systems, ESONE/IML/01, October 1974, ESONE Secretariat, and TID-26615, January 1975, DOE, Washington, D.C., U.S.A.

### TRANSFERTS DE BLOC DANS LES SYSTÈMES CAMAC

### 1. Domaine d'application et objet

### 1.1 Domaine d'application

La présente norme s'applique aux sous-programmes pour les systèmes CAMAC tels que définis dans la Publication 516 de la CEI: Système modulaire d'instrumentation pour le traitement de l'information; système CAMAC. Son application ne doit pas s'opposer ou provoquer d'opposition avec les dispositions obligatoires de la Publication 516 de la CEI.

### 1.2 Objet

Recommandations pour une pratique uniforme en ce qui concerne les transferts de bloc dans les systèmes CAMAC d'instrumentation modulaire et d'interface numérique de la Publication 516 de la CEI.

### 2. Introduction et classification

### 2.1 Introduction

La spécification CAMAC de base, Publication 516 de la CEI, définit une opération CAMAC simple comme l'activité qui se manifeste en réponse à un ordre CAMAC simple. Cette activité peut être le transfert d'un mot de données simple entre un module CAMAC et une mémoire d'ordinateur ou le changement de l'état d'un module (par exemple F(26), F(24)) ou le retour d'une valeur de Q résultant d'un contrôle fait sur le module ou toute autre combinaison compatible des activités qui viennent d'être mentionnées. Un transfert de bloc est défini comme une suite d'opérations CAMAC simples impliquant des données que l'utilisateur précise par un ordre dit d'un plus haut niveau qu'un ordre qui détermine une opération CAMAC simple. L'ordre de plus haut niveau contient toute l'information nécessaire pour la définition de la séquence voulue d'ordres CAMAC simples et est décodé par un canal qui régit l'activité de l'interconnexion CAMAC. L'information de contrôle, telle que la disponibilité de l'ordinateur pour participer à un transfert de données, l'état de la ligne Q et l'état de certains signaux LAM ou de certains signaux spéciaux de synchronisation, doit être rendue accessible au canal. L'utilisation de l'information de contrôle faite par le canal définit le mode de transfert de bloc. Si un module doit influencer la suite des opérations dans un transfert de bloc, il doit avoir les caractéristiques demandées par l'algorithme.

Un canal comprend une interface pour le système CAMAC ainsi qu'un moyen de choisir et d'exécuter les algorithmes des modes de transfert de bloc mis en œuvre. Un algorithme peut être mis en œuvre entièrement dans le matériel ou entièrement dans le logiciel ou par une combinaison du matériel et du logiciel. La possibilité de mise en œuvre par le logiciel d'un algorithme quelconque signifie que les transferts de bloc CAMAC peuvent trouver place dans un système qui n'a pas le matériel, tel l'accès direct à la mémoire requis par les transferts de bloc «ordinateurs». Il faut noter qu'un module se comporte de la même façon lorsqu'on y accède par un algorithme câblé que lorsqu'on accède par une entrée-sortie classique d'ordinateur programmé. Quelle que soit la méthode de mise en œuvre du canal, l'utilisation de ce dernier entraîne des réductions à la fois du temps d'unité centrale requis et de l'effort de programmation par l'usage d'algorithmes prédéfinis.

### **BLOCK TRANSFERS IN CAMAC SYSTEMS**

### 1. Scope and object

### 1.1 Scope

This standard covers requirements for subroutines for CAMAC systems as defined in IEC Publication 516: A Modular Instrumentation System for Data Handling; CAMAC System. Its application shall not conflict or cause conflict with the mandatory requirements of IEC Publication 516.

### 1.2 Object

Recommendations are presented for uniform practice with regard to block transfers in CAMAC modular instrumentation and digital interface systems of IEC Publication 516.

### 2. Introduction and classification

### 2.1 Introduction

The basic CAMAC specification, IEC Publication 516, defines a single CAMAC operation as the activity which occurs in response to a single CAMAC command. This activity may consist of the transfer of a single data word between a CAMAC module and computer memory or the changing of the status of a module (for example F(26), F(24)) or return of a value for Q as the result of a test made on the module, or any compatible set of the previously named activities. A block transfer is defined as a sequence of single CAMAC operations involving data which the user specifies by a command said to be of a higher level than one which specifies a single CAMAC operation. The higher-level command contains all the information required for the specification of the desired sequence of single CAMAC commands and is interpreted by a channel which governs the activity on the CAMAC highway. Control information, such as the readiness of the computer to participate in a data transfer, the state of the CAMAC Q line and the state of certain LAMs or special synchronizing signals must be made available to the channel. The use made of the control information by the channel defines the block transfer mode. If a module is to influence the sequence of operations within a block transfer, then it must have the features required by the particular mode.

A channel consists of an interface to the CAMAC system as well as a means for selecting and executing the algorithms of the block transfer modes that are implemented. An algorithm may be implemented wholly in hardware or wholly in software or by a combination of hardware and software. The possibility of software implementation of any algorithm means that CAMAC block transfers can take place on a system which does not have the hardware (such as direct memory access) required to carry out "computer" block transfers. Note that a module behaves in the same way when it is accessed by a hardware algorithm as it does when accessed by conventional programmed computer input-output. Regardless of the method of channel implementation, the use of the channel results in reductions in both the CPU time required and the programming effort, through the use of predefined algorithms.

On peut définir un grand nombre d'algorithmes (ou modes) de transfert de bloc différents, tous compatibles avec les spécifications CAMAC. Il est également possible de faire exécuter par un canal une suite d'ordres CAMAC n'impliquant pas le transfert de données. Un exemple d'un tel mode « Action multiple » est discuté dans l'annexe A. Beaucoup d'algorithmes utilisent l'information de contrôle transportée soit par un signal Q, soit par un signal L, soit par les deux. Les exigences affectées à ces signaux par un algorithme donné peuvent entrer en conflit avec celles qui leur sont affectées par un autre algorithme. D'où la possibilité que se présentent des problèmes de compatibilité entre modes et canaux. Cela est particulièrement vrai si on n'introduit pas de limitations dans le choix d'un algorithme de transfert de bloc approprié. Cependant l'expérience d'un grand nombre de systèmes CAMAC différents et une analyse approfondie du problème ont montré qu'un nombre réduit d'algorithmes de transfert de bloc peut satisfaire à peu près tous les besoins. En vue d'inciter à l'uniformité dans les conceptions futures de modules et de contrôleurs, l'utilisation de certains algorithmes est recommandée chaque fois que c'est possible et quelques algorithmes additionnels sont proposés pour des applications particulières qui ne peuvent être traitées de façon satisfaisante avec les algorithmes recommandés. L'utilisateur conserve la possibilité de définir d'autres algorithmes de transfert de bloc répondant à des besoins spéciaux.

Dans les articles suivants, on décrit les algorithmes de transfert de bloc recommandés. A l'article 3 sont décrits ceux qui sont donnés dans la Publication 516 de la CEI. Ces algorithmes sont bien établis et s'appuient sur du matériel existant, consistant à la fois en modules et en interfaces CAMAC convenant pour beaucoup de petits ordinateurs. L'article 4 décrit les nouveaux algorithmes.

L'utilisateur CAMAC doit se rappeler que les caractéristiques de transfert de bloc des modules, du contrôleur (commande de branche ou interface ordinateur-châssis), et du logiciel en ordinateur doivent être harmonisées de façon que les algorithmes de transfert de bloc soient mis en œuvre correctement. L'aptitude à opérer des transferts de bloc est une caractéristique de l'ensemble du système d'ordinateur et de ses interfaces.

### 2.2 Classification des modes de transfert de bloc

Les différents modes de transfert de bloc peuvent être classés en précisant la nature de chacune de trois caractéristiques fondamentales — manière de déterminer l'adresse CAMAC, source du signal de synchronisation et méthode utilisée pour terminer le transfert de bloc. Dans les articles suivants, on décrit ces caractéristiques et on définit une notation permettant une désignation concise des différents modes.

La notation est basée sur l'utilisation d'une lettre simple pour représenter la nature de chaque caractéristique. Les lettres sont écrites dans l'ordre dans lequel les caractéristiques ont été mentionnées ci-dessus et les trois lettres qui en résultent décrivent complètement un mode de transfert de bloc. Si une certaine caractéristique n'a pas besoin d'être spécifiée, on la représente par la lettre X. Ainsi le symbole XXX représente un mode de transfert de bloc dans lequel toutes les caractéristiques sont indéterminées. Le tableau I résume la signification de chaque lettre utilisée et le tableau II donne la liste des modes décrits dans ce document, les termes correspondants de la Publication 516 de la CEI et la définition du langage IML.

### 2.2.1 Séquence des adresses CAMAC

La première lettre de la notation du mode de transfert de bloc indique la méthode utilisée pour déterminer l'adresse CAMAC de l'opération CAMAC à venir.

Un transfert de bloc accédant à une adresse CAMAC qui demeure constante pendant le transfert est utilisé d'une manière habituelle pour l'accès à un tampon dans un module ou pour l'accès à un dispositif extérieur (tel qu'un périphérique d'ordinateur) à travers un module CAMAC. De tels transferts de bloc à adresse unique sont représentés par la lettre U.

Many different block transfer algorithms (or modes) may be defined, all of which are compatible with the CAMAC specifications. It is also possible to have a channel execute a sequence of CAMAC commands which does not involve the transfer of data. An example of such a "Multiple Action" mode is discussed in Appendix A. Many algorithms use control information conveyed by either a Q or an L signal or both. The requirements placed on these signals by one algorithm may conflict with those placed on them by another algorithm. Hence compatibility problems between modes and channels can occur. This is especially true if no restrictions are placed on the choice of a suitable block transfer algorithm. However, experience with many different CAMAC systems and extensive analysis of the problem has revealed that a restricted number of block transfer algorithms can satisfy nearly all needs. To encourage uniformity in future designs of modules and controllers, certain algorithms are recommended to be used whenever possible and some additional algorithms are suggested for special applications that cannot practicably be implemented with the recommended algorithms. The possibility remains for a user to define other block transfer algorithms to meet special needs.

In the following clauses, the recommended block transfer algorithms are discussed. In Clause 3, those given in IEC Publication 516 are described. These algorithms are well established and are supported by existing hardware, both in modules and in CAMAC interfaces available for many small computers. Clause 4 discusses the new algorithms.

The CAMAC user is reminded that the block transfer characteristics of the modules, the controller (branch driver or computer-crate interface), and the software in the computer must be matched in order for the block transfer algorithms to be carried out correctly. The ability to perform block transfers is a feature of the total computer system and its interfaces.

### 2.2 Classification of Block Transfer Modes

The various block transfer modes can be classified by specifying the nature of each of three fundamental characteristics—how the CAMAC address is determined, the source of the synchronizing signal, and the method used to terminate the block transfer. In the following clauses, these characteristics are described and a notation permitting a compact specification of the various modes is defined.

The notation is based on the use of a single letter to represent the nature of each characteristic. The letters are written in the order that the characteristics were mentioned above and the resulting three letters completely describe a block transfer mode. If a certain characteristic need not be specified, then it is denoted by the letter X. Thus the symbol XXX describes a block transfer mode in which all the characteristics are undefined. Table I summarizes the meaning of each letter used and Table II lists the modes described in this document, the corresponding terms in IEC Publication 516 and the IML language definition.

### 2.2.1 CAMAC Address Sequencing

The first letter of the block transfer mode descriptor indicates the method used to determine the CAMAC address of the next CAMAC operation.

A block transfer accessing a CAMAC address which stays constant during the block transfer is typically used to access a buffer within a module or to access an external device (such as a computer peripheral unit) through a CAMAC module. Such Uni-Address block transfers are denoted by the letter U.

TABLEAU I

Notation du mode de transfert de bloc

| Première lettre —  | Séquence des adresses CAMAC:                                                                                                                                                                        |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | <ul> <li>U Adresse unique</li> <li>M Adresse multiple (voir tableaux d'adresses calculées et données dans IML)</li> <li>A Scrutation d'adresses</li> <li>E Scrutation d'adresses étendue</li> </ul> |

| Deuxième lettre —  | - Source de synchronisation:                                                                                                                                                                        |

|                    | C Contrôleur Q Réponse Q L Signal LAM (Look-at-Me) D Signal pseudo-LAM                                                                                                                              |

| Troisième lettre — | Fin d'opération:  C Compte-mots du canal A Adresse finale atteinte S Q = 0 sur le dernier mot plus un W Q = 0 sur le dernier mot L Signal LAM (Look-at-Me) D Signal pseudo-LAM                      |

TABLEAU II

Noms des transferts de bloc

| Totation Publication 516 de la CEI |                                                                                                         |  |  |

|------------------------------------|---------------------------------------------------------------------------------------------------------|--|--|

| Mode arrêt                         | UBC                                                                                                     |  |  |

| Néant                              | UBC                                                                                                     |  |  |

| Mode répétitif                     | UBR                                                                                                     |  |  |

| Mode scrutation d'adresses         | MAD                                                                                                     |  |  |

| Néant                              | MA                                                                                                      |  |  |

| Néant                              | UBL                                                                                                     |  |  |

|                                    | Mode arrêt<br>Néant<br>Mode répétitif<br>Mode scrutation d'adresses<br>Néant<br>Néant<br>Néant<br>Néant |  |  |

Un transfert de bloc accédant à une suite d'adresses CAMAC est habituellement utilisé pour l'accès à un ensemble de registres localisés en des endroits différents d'un système CAMAC mais contenant des données en fonction de ces adresses. L'algorithme pour déterminer l'adresse CAMAC à venir peut dépendre de l'état d'une réponse Q résultant de l'opération précédente.

Le mode scrutation d'adresses (ACA) décrit dans le paragraphe 5.4.3.1 de la Publication 516 de la CEI constitue le principal exemple de cette technique, bien qu'il existe une variante, le mode de scrutation d'adresses étendue (ECA), décrit dans l'annexe A.

La suite de ces adresses CAMAC peut être également déterminée par une liste de toutes les adresses, ou par les paramètres: adresse de départ, incréments à appliquer à chaque partie d'adresse, et adresse finale. Ces deux méthodes correspondent aux tableaux donnés et calculés d'adresses CAMAC dans l'IML, et dans les deux cas on utilise la lettre M, pour adresse multiple.

TABLE I

Block Transfer Mode descriptor

| First letter —  | CA. | MAC address sequencing:                                        |

|-----------------|-----|----------------------------------------------------------------|

|                 | U   | Uni-Address                                                    |

|                 | M   | Multi-Address — see calculated and given address arrays in IML |

|                 | Α   | Address Scan                                                   |

|                 | E   | Extended Address Scan                                          |

| Second letter — | Syn | chronizing source:                                             |

|                 | C   | Controller                                                     |

|                 | Q   | Q Response                                                     |

|                 | Ĺ   | Look-at-Me (LAM) Signal                                        |

|                 | D   | Pseudo-LAM Signal                                              |

| Third letter —  | Ope | eration termination:                                           |

|                 | C   | Channel Word Count                                             |

|                 | Α   | Terminal Address Reached                                       |

|                 | S   | Q = 0 on last + one word                                       |

|                 | W   | Q = 0 on last word                                             |

|                 | L   | Look-at-Me (LAM) Signal                                        |

|                 | D   | Pseudo-LAM Signal                                              |

|                 |     |                                                                |

TABLE II

Block Transfer Names

| Descriptor                          | IEC Publication 516                                                                           | IML                                |

|-------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------|

| UCS UCW UQC ACA MCA ULS UDS ULW UDW | Stop Mode<br>None<br>Repeat Mode<br>Address Scan Mode<br>None<br>None<br>None<br>None<br>None | UBC UBC UBR MAD MA UBL UBL UBL UBL |

A block transfer accessing a sequence of CAMAC addresses is typically used to access a set of registers located at different places within a CAMAC system but containing related data. The algorithm for determining the next CAMAC address may depend on the state of Q resulting from the last operation.

The Address Scan (ACA) Mode described in Sub-clause 5.4.3.1 of IEC Publication 516 is the main example of this technique, although there is a variant, the Extended Address Scan (ECA) Mode, which is described in Appendix A.

The sequence of CAMAC addresses may also be determined either by a list of all the addresses or by the parameters: starting address, increments to be applied to each part of the address, and final address. These correspond to the Given and Calculated Arrays of CAMAC addresses in IML and both are indicated by the letter M for Multi-Address.

### 2.2.2 Source de synchronisation

La deuxième lettre de la notation d'un mode de transfert de bloc représente la source de synchronisation des transferts individuels. Dans quelques cas le module est prêt continûment à effectuer un transfert et le contrôleur de canal peut exécuter les ordres CAMAC à tout rythme adéquat. On dit alors que le transfert de bloc est «synchronisé par le contrôleur», et la notation pour tous les modes de ce type est de la forme XCX.

Dans d'autres cas le module n'est pas prêt continûment. Après un transfert particulier, un certain temps doit s'écouler avant qu'il puisse en effectuer un autre. Le rythme auquel le transfert de bloc se déroule est commandé par le module (ou les modules). Il en résulte que le module doit fournir de l'information de synchronisation au canal de façon qu'il puisse effectuer correctement sa part du processus de transfert de bloc. Pour de tels transferts de bloc «synchronisés par le module», on a identifié trois sources de signal de synchronisation. Ce sont:

- 1) la réponse Q comme dans le mode répétitif (voir paragraphe 5.4.3.2 de la Publication 516 de la CEI), représentée par Q;

- 2) un signal spécifique, interconnexions Look-at-Me (LAM), représenté par L;

- 3) un signal spécial (pseudo-LAM) envoyé directement du module au contrôleur et représenté par D.

### 2.2.3 Fin du transfert de bloc

La troisième et dernière lettre de la notation d'un mode de transfert de bloc représente le moyen par lequel il est mis fin au transfert de bloc. Un transfert de bloc donné peut être arrêté soit par le canal, soit par le module, selon les conditions existant au moment de l'action. On admet que tous les transferts de bloc seront exécutés avec une limitation du nombre de transferts autorisés; en addition à cette limitation du compte-mots dans le canal, il peut y avoir d'autres conditions se manifestant soit dans le canal, soit dans le module qui termineront le transfert. La première de telles conditions à se manifester met fin au processus.

Si un transfert de bloc peut être terminé uniquement par épuisement d'un compte-mots dans le canal, il est désigné par la lettre C. Si un transfert de bloc peut être terminé par le canal, soit parce qu'un compte-mots est épuisé, soit parce qu'une suite d'adresses dans un transfert à adresse multiple est épuisée, il est désigné par la lettre A.

Un transfert de bloc peut également être terminé par un signal d'état en provenance du module. Bien que, soit un signal L, soit un signal spécial envoyé directement au canal puisse être utilisé, tous les modes avec fin déterminée par le module décrit dans ce document utilisent la réponse Q associée à chaque opération CAMAC de transfert de bloc.

Un tel mode est décrit au paragraphe 5.4.3.3 de la Publication 516 de la CEI. Une réponse Q=1 est interprétée comme signifiant que l'opération a pris place dans le bloc. La première réponse Q=0 indique que la fin du bloc s'est produite sur l'opération précédente. Dans la Publication 516 de la CEI cela est appelé le mode Arrêt et on le désigne par la lettre S.

Une autre interprétation possible d'une réponse Q=0 est qu'elle accompagne la dernière opération dans le bloc. Pour des ordres d'écriture, le mot de données a été accepté par le module et pour des ordres de lecture, le mot de données a été transféré dans l'ordinateur. Cela est le mode Arrêt-sur-un-mot et on le désigne par la lettre W.

### 2.2.2 Synchronization source

The second letter of a block transfer mode descriptor indicates the source of synchronization of individual transfers. In some cases the module is continuously ready to effect a transfer and the channel controller may execute the CAMAC commands at any convenient rate. The block transfer is then said to be "controller synchronized", and the descriptor for all such modes is of the form XCX.

In other cases the module is not continuously ready. Following a particular transfer a certain time must elapse before it can effect another. The rate at which the block transfer proceeds is controlled by the module (or modules). Hence the module must provide synchronization information to the channel so that it can correctly execute its part of the block transfer process. For such "module synchronized" block transfers, three sources of synchronizing signal have been identified. They are:

- 1) the Q response as in the Repeat Mode (see Sub-clause 5.4.3.2 of IEC Publication 516) denoted by Q;

- 2) a specific Dataway Look-at-Me (LAM) signal, denoted by L;

- 3) a special signal (Pseudo-LAM) sent directly from the module to the controller, denoted by D.

### 2.2.3 Block Transfer Termination

The third and final letter of a block transfer mode descriptor indicates the means by which the block transfer is terminated. A given block transfer may be halted by either the channel or the module, depending on the conditions existing at the time of the action. It is assumed that all block transfers will be executed with a limit on the number of transfers permitted; in addition to this channel word-count limit there may be other conditions occurring either in the channel or the module which will terminate the transfer. The first such condition to occur terminates the process.

If a block transfer can be terminated only by exhausting a word count within the channel, it is designated by the letter C. If a block transfer can be terminated by the channel either because a word count is exhausted or because a sequence of addresses in a multi-address transfer is exhausted, it is designated by the letter A.

A block transfer can also be terminated by a status signal from the module. While either an L signal or a special signal sent directly to the channel could be used, all the module terminated modes described in this document use the Q response associated with each CAMAC operation of the block transfer.

In Sub-clause 5.4.3.3 of IEC Publication 516 such a mode is described. A response Q=1 is interpreted as meaning that the operation took place within the block. The first response Q=0 indicates that the end of block occurred on the previous operation. In IEC Publication 516 this is called the Stop mode and is designated here by the letter S.

Another possible interpretation of a response Q=0 is that it accompanies the last operation in the block. For write commands, the data word has been accepted by the module and for read command the data word has been transferred to the computer. This is the Stop-on-Word mode and is designated by the letter W.

### 3. Modes de transfert de bloc décrits dans la Publication 516 de la CEI

La norme CAMAC n'introduit pas de restrictions sur les modes qui peuvent être utilisés pour des transferts de bloc. Cependant, on donne comme exemples trois modes qui dépendent d'utilisations définies du signal de réponse Q. Ces modes ont été largement mis en œuvre, notamment pour des applications en physique des hautes énergies et de nombreux modules incorporant les dispositions appropriées sont disponibles.

### 3.1 Mode UCS (Arrêt)

(Transfert de bloc à adresse unique, synchronisation par le contrôleur, fin par la réponse Q)

L'algorithme, pour le module dans ce mode de transfert de bloc, est défini au paragraphe 5.4.3.3 de la Publication 516 de la CEI. Ce mode permet au canal de transférer une suite de mots de données entre une adresse simple CAMAC fixée et la mémoire de l'ordinateur, à un rythme fixé par le système ordinateur, mais avec la dimension du bloc fixée par le module CAMAC.

La réponse Q = 1 indique qu'un mot de données a été transmis par le module dans une opération de lecture ou accepté par le module dans une opération d'écriture, c'est-à-dire que le transfert a eu lieu à l'intérieur du bloc de mots de données.

La réponse Q = 0 indique une tentative de transfert au-delà de la fin du bloc. Cette réponse est utilisée pour mettre fin à un transfert de bloc en mode UCS. Dans une opération de lecture, il n'a pas été transmis de donnée valable par le module et la séquence doit être arrêtée par fermeture du canal. Comme le transfert d'un mot de données inexistant (ou sans signification) à la mémoire de l'ordinateur imposerait quelque forme de redressement, il ne faudrait pas que le canal effectue le transfert.

Une réponse Q = 0 dans une opération d'écriture indique que le module n'a pas accepté le mot de données.

Ce mode correspond au mode UBC, paragraphe 5.9 du système IML.

### 3.2 Mode ACA (Scrutation d'adresses)

(Transfert de bloc à adresse multiple, synchronisation et fin par le contrôleur)

L'algorithme pour le module dans ce mode de transfert de bloc est défini au paragraphe 5.4.3.1 de la Publication 516 de la CEI. Il a pour objet l'accès à des registres à des sous-adresses successives dans une suite de modules, sans qu'il soit nécessaire de connaître d'avance le nombre précis de modules ou de registres dans chaque module. Le contrôleur de canal, câblé ou programmé, lance le transfert en établissant une adresse CAMAC initiale, une adresse CAMAC finale et le code de fonctions donnant l'accès aux registres compris dans la structure d'adresses. Le contrôleur de canal donne accès à chaque registre à son tour par progressions successives des sous-adresses CAMAC. Une réponse Q=1 de la part d'un module indique la présence d'un registre compris dans la scrutation. La réponse Q=0 signifie l'absence de registre. Une réponse Q=0 d'une sous-adresse quelconque ou une réponse Q=1 de la sous-adresse A(15) oblige le contrôleur de canal à mettre à zéro la sous-adresse et à faire progresser d'un pas le numéro de station avant la tentative de transfert suivante.

Pour les deux opérations de lecture et d'écriture, le canal essaie d'effectuer les opérations CAMAC. La réponse Q résultant de chaque tentative est utilisée par le canal pour déterminer l'adresse suivante CAMAC à utiliser, aussi bien que pour indiquer à l'ordinateur ce qui doit être fait au sujet des transferts de données. La réponse Q=1 indique que le module a, soit transmis, soit accepté un mot de données. Une réponse Q=0 à une opération de lecture signifie qu'il n'y avait pas de mot de données disponible à l'adresse CAMAC indiquée et le canal n'entame pas de transfert vers la mémoire. Une réponse Q=0 à une opération d'écriture signifie que le mot

### 3. Block Transfer Modes described in IEC Publication 516

The CAMAC standard places no restrictions on the modes which may be used for block transfers. However, three modes which depend on defined uses of the Q response signal are given as examples. These modes have been widely implemented, particularly for high energy physics applications, and many modules are available with the appropriate features incorporated.

### 3.1 UCS (Stop) Mode

(Uni-address block transfer, controller synchronized, Q response terminated)

The algorithm for the module in this block transfer mode is defined in Sub-clause 5.4.3.3 of IEC Publication 516. This mode enables the channel to transfer a sequence of data words between a single fixed CAMAC address and computer memory at a rate determined by the computer system but with the block size determined by the CAMAC module.

The response Q = 1 indicates that a data word has been transmitted by the module in a read operation or accepted by the module in a write operation, i.e., the transfer occurred within the block of data words.

The response Q=0 indicates a transfer attempt beyond the end of the block. This response is used for terminating a UCS mode block transfer. In a read operation, no valid data has been transmitted by the module and the sequence is stopped by closing the channel. Since the transfer of a non-existent (or dummy) data word to computer memory would require some form of recovery, the channel should not complete the transfer.

A response Q = 0 in a write operation indicates that the module has not accepted the data word.

This mode is supported in Sub-clause 5.9 of IML by the UBC mode.

### 3.2 ACA (Address Scan) Mode

(Multi-address block transfer, controller synchronized and terminated)

The algorithm for the module in this block transfer mode is defined in Sub-clause 5.4.3.1 of IEC Publication 516. Its object is to access registers at successive sub-addresses in a sequence of modules without the need to know in advance the precise number of modules or registers in each module. The channel controller, either hardware or software, initiates the transfer by establishing an initial CAMAC address, final CAMAC address, and function code with which registers included in the address scan are to be accessed. The channel controller accesses each register in turn by sequentially incrementing through the CAMAC sub-addresses. A response Q = 1 from a module indicates that a register included in the scan is present. The response Q = 0 indicates register absent. A response Q = 0 from any sub-address or a response Q = 1 from sub-address A(15) causes the channel controller to set the sub-address to zero and increment the station number before the next transfer attempt.

For both read and write operations, the channel attempts to execute CAMAC operations. The Q response from each attempt is used by the channel to determine the next CAMAC address to be used, as well as to indicate to the computer what has to be done concerning data transfers. The response Q = 1 indicates that the module either transmitted or accepted a data word. A response Q = 0 to a read operation means that no data word was available at the CAMAC address accessed and the channel does not initiate a transfer to memory. A response Q = 0 to a write operation means that the data word was not accepted at the CAMAC address,

de données n'a pas été accepté à l'adresse CAMAC indiquée et le canal interdit à l'ordinateur de passer au mot de données suivant. Le transfert de bloc est terminé quand le contrôleur de canal atteint l'adresse CAMAC finale ou quand il s'est produit un nombre déterminé de transferts de données.

La réponse combinant Q=0 et X=0 peut légitimement survenir lorsque l'examen des adresses révèle une sous-adresse inoccupée. Cela rend le mode ACA potentiellement dangereux, et on le met habituellement en œuvre avec des précautions particulières, avec par exemple des mots de données uniques et connus en différents points de la séquence pour permettre de vérifier la présence de tous les modules. La combinaison Q=1, X=0 traduit une erreur.

Ce mode correspond au mode MAD, paragraphe 5.13 du système IML.

### 3.3 *Mode UQC (Répétitif)*

(Transfert de bloc à adresse unique, synchronisation par la réponse Q, fin par le contrôleur)

L'algorithme pour ce mode de transfert de bloc est défini pour le module au paragraphe 5.4.3.2 de la Publication 516 de la CEI. Le canal désigne une adresse CAMAC fixée et ne peut transférer des mots de données que lorsque le module est prêt, ce qui revient à dire que le rythme maximal est déterminé par le module.

La réponse Q=1 indique qu'un mot de données a été transmis dans une opération de lecture ou accepté dans une opération d'écriture, c'est-à-dire que le module était prêt. Pour des opérations de lecture, Q=0 indique que le module n'était pas en état de fournir un mot de données. Pour des opérations d'écriture, Q=0 indique que le mot de données n'a pas été accepté par le module. Par conséquent l'ordre devrait être répété avec le même mot de données jusqu'à obtention de la réponse Q=1.

Dans ce mode, la réponse Q ne peut pas indiquer la fin de la séquence, d'où la nécessité de quelque autre mécanisme, tel que l'arrêt de la séquence quand il a été atteint un nombre déterminé de transferts de données. De même, le module n'a aucun moyen d'indiquer qu'il ne possède pas de données; il y a donc un risque que l'opération CAMAC soit répétée indéfiniment dans l'attente d'une réponse Q=1. Comme cette situation peut aussi se rencontrer dans un cas d'erreur, le canal devrait comporter un dispositif anti-erreurs, tel que celui qui limite le nombre ou la durée d'opérations consécutives avec Q=0.

Ce mode est particulièrement utile, à la fois dans les opérations de lecture et d'écriture, pour les communications avec un tampon ou un équipement auxiliaire dont le rythme de transfert de données est légèrement inférieur à celui de système ordinateur. Il n'est pas recommandé quand il y a un grand écart entre les vitesses du module et du canal parce que l'efficacité du transfert peut devenir faible.

Ce mode correspond au mode UBR, paragraphe 5.10 du système IML.

### 4. Modes de transfert de bloc supplémentaires

Depuis la parution de la Publication 516 de la CEI, des modes de transfert de bloc supplémentaires ont été identifiés. Ils ne sont pas destinés à remplacer les modes discutés à l'article 3, mais plutôt à les compléter. Dans les paragraphes suivants, quelques-uns de ces modes supplémentaires sont décrits et des applications caractéristiques sont données en vue d'illustrer les conditions spéciales qui exigent ces modes.

and the channel does not allow the computer to step to the next data word. The block transfer is terminated when the channel controller accesses the final CAMAC address or when a specific number of data transfers have taken place.

The response combination Q = 0, X = 0 can occur legitimately when the address scan encounters an unoccupied sub-address. Because of this the ACA mode is potentially dangerous and is usually implemented with special precautions, for example unique and known data words at various points of the sequence to allow verification that all modules are present. The combination Q = 1, X = 0 is an error condition.

This mode is supported in Sub-clause 5.13 of IML by the MAD mode.

### 3.3 UQC (Repeat) Mode

(Uni-address block transfer, Q response synchronized, controller terminated)

The algorithm for this block transfer mode is defined for the module in Sub-clause 5.4.3.2 of IEC Publication 516. The channel addresses one fixed CAMAC address and is able to transfer data words only when the module is ready, i.e., with the maximum rate determined by the module.

The response Q=1 indicates that a data word has been transmitted in a read operation or accepted in a write operation, i.e., the module was ready. For read operations, Q=0 indicates that the module was unable to supply a data word. For write operations, Q=0 indicates that the data word was not accepted by the module. The command should, therefore, be repeated with the same data word until Q=1 is obtained.

In this mode the Q response cannot indicate the end of the sequence and hence some other mechanism is required, such as the sequence being terminated when a specified number of data transfers have been achieved. Similarly, the module has no method of indicating that it has no data; there is, therefore, a risk that the CAMAC operation will be repeated indefinitely while waiting for Q = 1. Since this situation may also be encountered in a fault condition, the channel should include an error-detecting feature, such as one that limits the number or duration of consecutive operations with Q = 0.

This mode is particularly useful in both read and write operations for communication with a buffer or auxiliary equipment whose data-transfer rate is marginally slower than the transfer rate of the computer system. It is not recommended when there is a wide discrepancy between module and channel speeds because transfer efficiency may become low.

This mode is supported in Sub-clause 5.10 of IML by the UBR mode.

### 4. Additional Block Transfer Modes

Since the issue of IEC Publication 516, additional block transfer modes have been identified. These are not intended to replace the modes discussed in Clause 3, but rather to complement them. In the following sub-clauses some of these additional modes are described and typical applications are given in order to illustrate the special conditions which require the modes.

### 4.1 Mode UCW (Arrêt-sur-un-mot)

(Transfert de bloc à adresse unique, synchronisation par le contrôleur, fin par la réponse Q)

Le mode UCW est utilisé pour le transfert d'un bloc de données entre une adresse CAMAC simple et la mémoire d'ordinateur à une vitesse fixée par le canal. Il est identique au mode UCS (Arrêt) à l'exception de l'interprétation des données qui accompagne la première réponse Q = 0. Cette interprétation différente de Q signifie que le mode UCW ne peut pas être utilisé avec la plupart des interfaces et des modules du début à moins que ne soient prises des précautions particulières. Il en résulte que son utilisation devrait être limitée aux cas que réclament toutes ses caractéristiques.

Dans un transfert de bloc UCS de N mots de données, le retour Q=0 a lieu sur le  $(N+1)^{\rm eme}$  transfert; c'est-à-dire qu'aucune donnée significative n'est transférée dans l'opération renvoyant Q=0. Dans certaines circonstances, une opération plus efficace est obtenue si le retour Q=0 a lieu sur le N<sup>ème</sup> transfert, c'est-à-dire en accompagnant le dernier mot réellement transféré. Dans ce cas, le mode est décrit comme mode UCW ou Arrêt-sur-unmot.

Sa mise en œuvre pour des opérations de lecture impose au contrôleur de canal d'envoyer à la mémoire d'ordinateur le mot reçu avec Q = 0. Pour les opérations d'écriture, le module répond avec Q = 0 au moment de l'opération qui complète le transfert de bloc.

Avec des modules travaillant comme périphériques d'ordinateur (par exemple pour une mémoire de masse), des blocs de longueur fixée sont souvent transférés dans les deux sens. En envoyant Q=0 avec le dernier transfert effectif (mode UCW), on obtient un mécanisme (compatible avec les périphériques d'ordinateur normalisés) par lequel on peut déterminer que le nombre voulu de transferts a été atteint.

Le mode Arrêt (UCS) présente l'avantage de pouvoir distinguer un module contenant un seul mot de données d'un module n'en contenant pas, au moment de la première tentative de transfert. Dans le mode UCW, une opération de contrôle préliminaire est nécessaire si cette question se pose pour un module particulier.

Les deux modes UCS et UCW correspondent au mode UBC, paragraphe 5.9 du système IML. Le canal affecté au transfert détermine si le transfert accompagné par Q = 0 est achevé ou non.

### 4.2 Mode ULS (Synchronisation par LAM, Arrêt)

(Transfert de bloc à adresse unique, synchronisation par signal LAM, fin par la réponse Q)

Les modules conçus pour travailler dans le mode UCS (Arrêt) peuvent être adaptés au mode synchronisation par signal LAM par adjonction d'un dispositif «Lancement d'appel par le module». Ce mode permet le transfert d'un bloc de données entre une adresse CAMAC unique et la mémoire de l'ordinateur avec chaque transfert individuel de mot de données demandé par un signal «Lancement d'appel par le module» (LAM) provenant du module. Ce signal LAM peut être utilisé comme signal de synchronisation pour le canal câblé ou programmé, c'est-à-dire sans provoquer nécessairement une interruption d'ordinateur. Ce mode est particulièrement indiqué pour des périphériques à faible vitesse (par exemple entrée-sortie de bande perforée ou scrutation détecteur/capteur) qui feraient sans cela des demandes répétées pour un sous-programme de traitement des interruptions.

Les modes à synchronisation par LAM peuvent utiliser le processus normal de gestion des LAM pour identifier le signal LAM spécifique et par conséquent le canal désiré. Dans une mise en œuvre utilisant le mécanisme des appels codés GL (voir le paragraphe 5.2 de la Publication 552 de la CEI: Organisation des systèmes multichâssis. Spécification de l'Interconnexion de branche et du contrôleur de châssis type A1) pour la gestion des LAM, l'activité du contrôleur

### 4.1 UCW (Stop-on-Word) Mode

(Uni-address block transfer, controller synchronized, Q response terminated)

The UCW mode is issued for the transfer of a block of data between a single CAMAC address and a computer memory at a speed determined by the channel. It is identical to the UCS (Stop) mode except for the interpretation of the data that accompanies the first Q=0 response. This different interpretation of Q means that the UCW mode cannot be used with many early interfaces and modules unless special precautions are taken. Hence its use should be restricted to those cases which require all its features.

In a UCS block transfer of N data words Q=0 is returned on the (N+1)th transfer; that is, no significant data is transferred in the operation returning Q=0. Under certain circumstances more efficient operation is obtained if Q=0 is returned on the Nth transfer; that is, accompanying the last word actually transferred. If Q=0 accompanies the last word transferred, then the mode is described as UCW or Stop-on-Word.

Its implementation for read operations requires the channel controller to pass to computer memory the word received with Q=0. For write operations, the module responds with Q=0 in the operation that completes the block transfer.

With modules acting as computer peripherals (e.g. for bulk storage) fixed length blocks are often transferred in both directions. By sending Q = 0 with the last successful transfer (UCW mode) a mechanism (compatible with standard computer peripherals) is obtained whereby it can be determined that the required number of transfers has been achieved.

Stop mode (UCS) has the advantage that it can distinguish between a module containing a single data word and no data word on the first transfer attempt. In UCW mode, a preliminary test operation is required if this is a problem for a particular module.

Both UCS mode and UCW mode are supported in Sub-clause 5.9 of IML by the UBC mode. Whether the transfer accompanied by Q=0 is completed or not is determined by the channel specified for the transfer.

### 4.2 ULS (LAM Synchronized Stop) Mode

(Uni-address block transfer, LAM synchronized, Q response terminated)

Modules designed to work in UCS (Stop) mode can be upgraded to LAM synchronized mode by adding a "Look-at-Me" feature. This mode allows the transfer of a block of data between a single CAMAC address and computer memory with each individual data word transfer demanded by a Look-at-Me (LAM) request from the module. This LAM request may be used as a synchronizing signal to the hardware or software channel, i.e. not necessarily generating a computer interrupt. The mode is particularly appropriate for low-speed devices (e.g. paper tape I/0 or detector-sensor scanning) which could otherwise make repeated demands for an interrupt-service routine.

LAM synchronized modes can use the normal LAM handling features to identify the specific LAM request, and hence the channel required. In an implementation using the Graded-L mechanism (see Sub-clause 5.2 of IEC Publication 552: Organization of Multi-crate Systems. Specification of the Branch-highway and CAMAC Crate Controller Type A1) for LAM handling it simplifies the controller activity if a specific GL number is dedicated to the block

est simplifiée si un numéro spécifique GL est attribué au transfert de bloc au moment de son exécution. L'opération effectuant le transfert demandé devrait également remettre à zéro le signal LAM. Cela donne une opération plus efficace quand l'accès au module se fait par un canal de transfert de bloc ou suivant un sous-programme de traitement des interruptions. Comme chaque canal est sollicité individuellement, de nombreux canaux de transfert de bloc différents peuvent travailler de concert sous réserve que chacun d'eux ait un signal LAM unique. De plus, ces canaux de transfert de bloc peuvent travailler en parallèle avec des opérations CAMAC commandées par programme utilisant des dispositions normales d'entréesortie.

Le transfert de bloc de mode ULS se termine soit quand il y a eu transfert d'un nombre prédéterminé de mots de données, soit par une réponse Q=0 en provenance du module. Pour des opérations de lecture ou d'écriture dans le mode ULS, le module émet un autre LAM après le transfert du dernier mot du bloc, de façon que soit transmise l'indication Q=0 de fin de bloc.

Un exemple d'utilisation de ce mode est l'entrée d'un message provenant d'un télétype. Chaque caractère est transféré à un tampon de message dans la mémoire de l'ordinateur en réponse à une demande LAM provenant du module d'interface. L'opération CAMAC qui lit le caractère remet aussi à zéro le signal LAM. Le transfert de bloc se poursuit jusqu'à ce que le tampon contienne un nombre prédéterminé de caractères ou jusqu'à ce que le module d'interface identifie un caractère spécifique, par exemple un retour-chariot, et renvoie Q=0 en réponse à l'opération de lecture lancée par le LAM.

Pour des applications particulières, le mode ULW (Synchronisation par LAM, Arrêt-sur-unmot) peut être utilisé. Il faut noter que, comme le mode UCW (paragraphe 4.1), ce mode ne peut pas être utilisé avec la plupart des interfaces et des modules de la première génération.

Le mode ULS correspond au mode UBL, paragraphe 5.8 du système IML.

### 4.3 Mode UDS (Synchronisation directe, Arrêt)

(Transfert de mode à adresse unique, synchronisation par signal spécial, fin par la réponse Q)

Ce mode est identique au mode ULS décrit au paragraphe 4.2 à l'exception du chemin d'accès au signal de synchronisation au canal. Dans le mode ULS, le signal de synchronisation passe par le mécanisme de gestion des LAM avant d'être utilisé par le canal pour lancer l'opération CAMAC demandée. Dans le mode UDS, le signal de synchronisation a les mêmes propriétés que le signal LAM du mode ULS, à ceci près que le signal est envoyé directement au canal, en court-circuitant le mécanisme de gestion des LAM du canal. Il en résulte que, pour un certain nombre de systèmes, le mode UDS peut avoir une réponse plus rapide à une demande de transfert que le mode ULS. Le signal de synchronisation peut être envoyé au canal par le biais d'un connecteur de panneau avant ou d'un contact accessoire (et/ou d'une ligne d'Interconnexion de branche d'usage libre si c'est justifié) et il est appelé un « pseudo-LAM ».

Pour des applications particulières, le mode UDW (Synchronisation directe, Arrêt-sur-unmot) peut être utilisé. Il faut noter que, comme le mode UCW (paragraphe 4.1), ce mode ne peut pas être utilisé avec la plupart des interfaces et modules de la première génération.

Le mode UDS correspond au mode UBL, paragraphe 5.8 du système IML.

### 4.4 Mode MCA (Action multiregistre)

(Transfert de bloc à adresse multiple, synchronisation et fin par le contrôleur)

Ce mode permet qu'une distribution aléatoire (tableau donné dans le système IML) ou qu'une distribution régulière (tableau calculé dans le système IML) d'adresses CAMAC soit traitée par le programmeur comme un élément matériel unique: la réponse Q des modules est

transfer at the time of its execution. The operation performing the requested transfer should also reset the LAM request. This gives more efficient operation where the module is accessed by a block transfer channel or an interrupt service routine. Because each channel is individually requested, many different block transfer channels can operate concurrently provided that each has a unique LAM request. In addition these block-transfer channels can operate in parallel with program controlled CAMAC operations using normal input-output facilities.

The ULS mode block transfer is terminated either by a pre-determined number of data words having been transferred or by a response Q=0 from the module. For read or write operations in the ULS mode, the module issues another LAM after the last word of the block has been transferred in order that the end-of-block indication Q=0 can be transmitted.

One example of the use of this mode is the input of a message from a teletypewriter. Each character is transferred to a message buffer in computer memory in response to a LAM request from the interface module. The CAMAC operation which reads the character also resets the LAM request. The block transfer continues until the buffer contains a predetermined number of characters or the interface module identifies a specific character, for example a carriage-return, and returns Q = 0 in response to the read operation initiated by the LAM request.

For special applications the ULW (LAM Synchronized Stop-on-Word) mode may be used. Note that, like the UCW mode (Sub-clause 4.1), this mode cannot be used with many earlier interfaces and modules.

The ULS mode is supported in Sub-clause 5.8 of IML by the UBL mode.

### 4.3 UDS (Direct Synchronized Stop) Mode

(Uni-address block transfer, special signal synchronized, Q response terminated)

This mode is identical to the ULS mode described in Sub-clause 4.2 with the exception of the way the synchronizing signal reaches the channel. In the ULS mode the synchronizing signal is processed by the LAM handling mechanism before it is used by the channel to initiate the required CAMAC operation. In the UDS mode the synchronizing signal has the same properties as the LAM signal in the ULS mode except that the signal is sent directly to the channel, bypassing the LAM handling mechanism of the channel. Hence the UDS mode can for some systems have a more rapid response to a transfer request than the ULS mode. The synchronizing signal can be sent to the channel via a front panel connector or a patch contact (and/or a free use Branch-highway line if appropriate) and is called a "Pseudo-LAM".

For special applications the UDW (Direct Synchronized Stop-on-Word) mode may be used. Not that, like the UCW mode (Sub-clause 4.1), this mode cannot be used with many earlier interfaces and modules.

The UDS mode is supported in Sub-clause 5.8 of IML by the UBL mode.

### 4.4 MCA (Multi-device Action) Mode

(Multi-address block transfer, controller synchronized and terminated)

This mode permits an arbitrary pattern, a Given-address Array in IML, or a regular pattern, a Calculated-address Array in IML, of CAMAC addresses to be treated as a single hardware array by the programmer. The Q response from the modules is ignored and no special module