#### THE KLUWER INTERNATIONAL SERIES IN ENGINEERING AND COMPUTER SCIENCE

#### ANALOG CIRCUITS AND SIGNAL PROCESSING Consulting Editor: Mohammed Ismail. Ohio State University

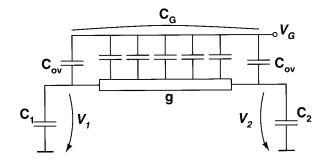

Related Titles:

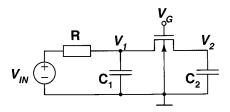

CMOS CIRCUIT DESIGN FOR RF SENSORS

Gudnason and Bruun ISBN: 1-4020-7127-2

ARCHITECTURES FOR RF FREQUENCY SYNTHESIZERS

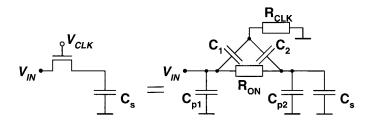

Vaucher

ISBN: 1-4020-7120-5

THE PIEZOJUNCTION EFFECT IN SILICON INTEGRATED CIRCUITS AND SENSORS

Fruett and Meijer ISBN: 1-4020-7053-5

CMOS CURRENT AMPLIFIERS; SPEED VERSUS NONLINEARITY

Koli and Halonen ISBN: 1-4020-7045-4

MULTI-STANDARD CMOS WIRELESS RECEIVERS

Li and Ismail

ISBN: 1-4020-7032-2

A DESIGN AND SYNTHESIS ENVIRONMENT FOR ANALOG INTEGRATED CIRCUITS

Van der Plas, Gielen and Sansen

ISBN: 0-7923-7697-8

RF CMOS POWER AMPLIFIERS: THEORY, DESIGN AND IMPLEMENTATION

Hella and Ismail ISBN: 0-7923-7628-5

DATA CONVERTERS FOR WIRELESS STANDARDS

C. Shi and M. Ismail ISBN: 0-7923-7623-4

DIRECT CONVERSION RECEIVERS IN WIDE-BAND SYSTEMS

A. Parssinen ISBN: 0-7923-7607-2

AUTOMATIC CALIBRATION OF MODULATED FREQUENCY SYNTHESIZERS

D. McMahill

ISBN: 0-7923-7589-0

MODEL ENGINEERING IN MIXED-SIGNAL CIRCUIT DESIGN

S. Huss

ISBN: 0-7923-7598-X

ANALOG DESIGN FOR CMOS VLSI SYSTEMS

F. Maloberti

ISBN: 0-7923-7550-5

CONTINUOUS-TIME SIGMA-DELTA MODULATION FOR A/D CONVERSION IN RADIO

RECEIVERS L. Breems, J.H. Huijsing

ISBN: 0-7923-7492-4

DIRECT DIGITAL SYNTHESIZERS: THEORY, DESIGN AND APPLICATIONS

J. Vankka, K. Halonen ISBN: 0-7923 7366-9

SYSTEMATIC DESIGN FOR OPTIMISATION OF PIPELINED ADCs

J. Goes, J.C. Vital, J. Franca ISBN: 0-7923-7291-3

OPERATIONAL AMPLIFIERS: Theory and Design

J. Huijsing

ISBN: 0-7923-7284-0

HIGH-PERFORMANCE HARMONIC OSCILLATORS AND BANDGAP REFERENCES

A. van Staveren, C.J.M. Verhoeven, A.H.M. van Roermund ISBN: 0-7923-7283-2

HIGH SPEED A/D CONVERTERS: Understanding Data Converters Through SPICE

A. Moscovici

ISBN: 0-7923-7276-X

ANALOG TEST SIGNAL GENERATION USING PERIODIC ZA-ENCODED DATA

# CIRCUIT TECHNIQUES FOR LOW-VOLTAGE AND **HIGH-SPEED A/D CONVERTERS**

Mikko E. Waltari

and

Kari A.I. Halonen

Helsinki University of Technology

KLUWER ACADEMIC PUBLISHERS BOSTON / DORDRECHT / LONDON

#### ISBN 1-4020-7244-9

Published by Kluwer Academic Publishers, P.O. Box 17, 3300 AA Dordrecht, The Netherlands.

Sold and distributed in North, Central and South America by Kluwer Academic Publishers, 101 Philip Drive, Norwell, MA 02061, U.S.A.

In all other countries, sold and distributed by Kluwer Academic Publishers, P.O. Box 322, 3300 AH Dordrecht, The Netherlands.

Printed on acid-free paper

All Rights Reserved

© 2002 Kluwer Academic Publishers, Boston

No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

Printed in the Netherlands.

| 1. | INT                | RODUCTION                          |   |

|----|--------------------|------------------------------------|---|

| 2. | LOW VOLTAGE ISSUES |                                    |   |

|    | 1                  | Signal-to-Noise Ratio              | : |

|    | 2                  | Circuit Speed                      | ( |

|    | 3                  | Power Consumption                  |   |

|    | 4                  | Matching                           | 1 |

|    | 5                  | Operational Amplifiers             | 1 |

|    | 6                  | MOS Switches                       | 1 |

|    | 7                  | Conclusions                        | 1 |

| 3. | SAN                | MPLE-AND-HOLD OPERATION            | 1 |

| -  | 1                  | S/H Basics and Performance Metrics | 1 |

|    | 2                  | Spectra of Sampled Signals         | 2 |

|    | 3                  | Noise Issues in S/H Circuits       | 2 |

|    | 4                  | Basic S/H Circuit Architectures    | 2 |

| 4. | A/D                | CONVERTERS                         | 3 |

|    | 1                  | A/D Conversion                     | 3 |

|    | 2                  | Flash ADC                          | 3 |

|    | 3                  | Subranging ADC                     | 3 |

|    | 4                  | Folding-and-Interpolating ADC      | 3 |

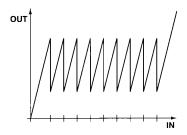

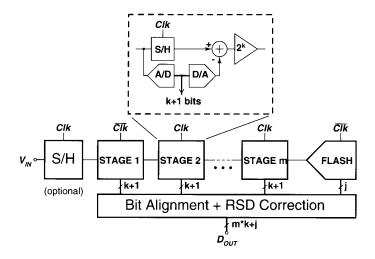

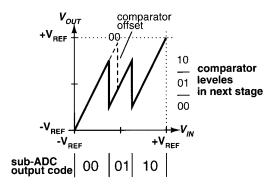

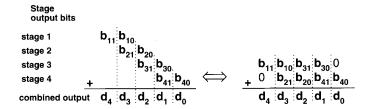

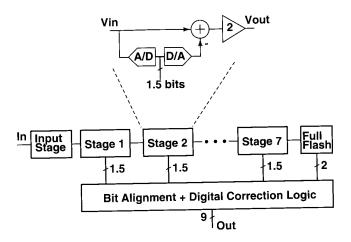

|    | 5                  | Pipelined ADC                      | 4 |

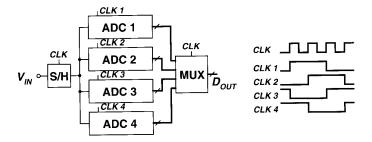

|    | 6                  | Time-Interleaved ADC               | 5 |

|    | 7                  | A/D Converters: Summary            | 5 |

| vi       |                        | CIRCUIT TECHNIQUES FOR LOW-VOLTAGE AND HIGH-SPEED     | ADCS |

|----------|------------------------|-------------------------------------------------------|------|

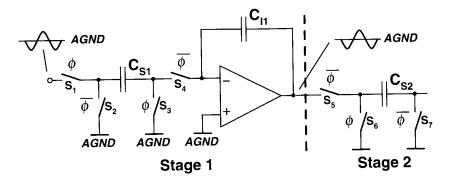

| 5.       | S/E                    | I CIRCUIT ARCHITECTURES                               | 57   |

|          | 1                      | Bipolar Architectures                                 | 58   |

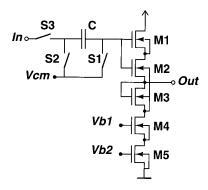

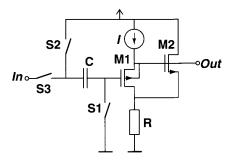

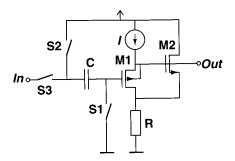

|          | 2                      | CMOS Architectures                                    | 59   |

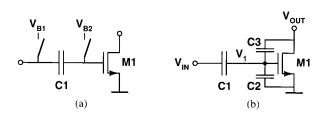

| 6.       | SA                     | MPLING WITH A MOS TRANSISTOR SWITCH                   | 69   |

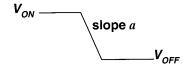

|          | 1                      | Voltage-Dependent Turn-Off Moment                     | 70   |

|          | 2                      | Charge Injection                                      | 71   |

|          | 3                      | Bottom Plate Sampling                                 | 75   |

|          | 4                      | Nonlinear Time Constant                               | 77   |

|          | 5                      | Sampling Function                                     | 88   |

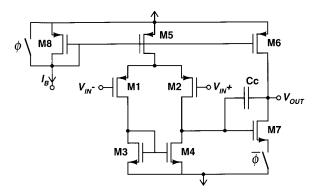

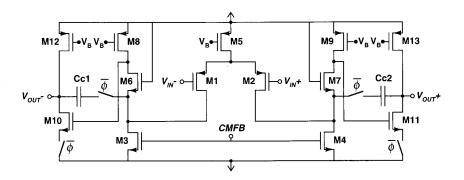

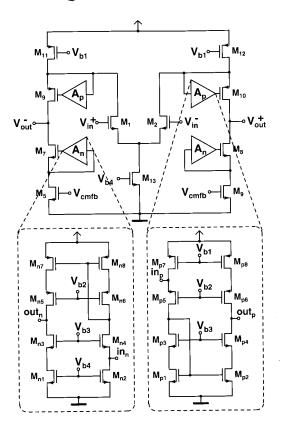

| 7.       | OPERATIONAL AMPLIFIERS |                                                       |      |

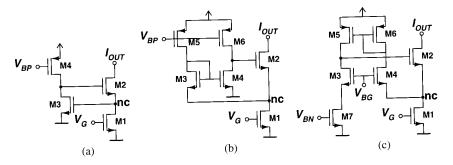

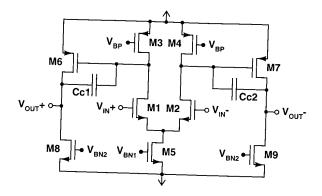

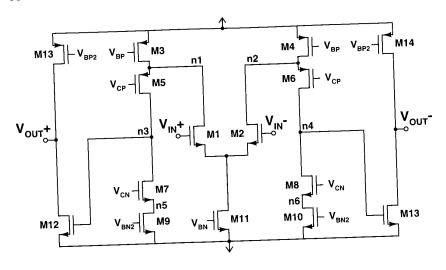

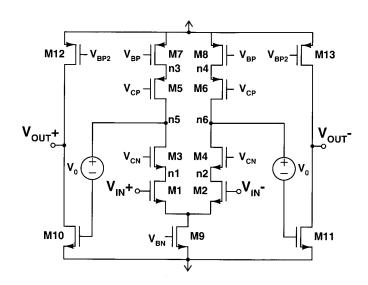

|          | 1                      | Requirements for SC Applications                      | 91   |

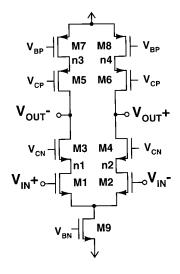

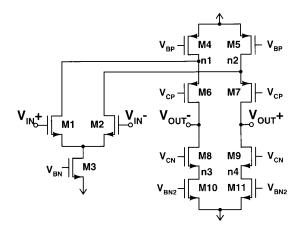

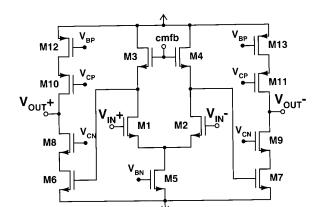

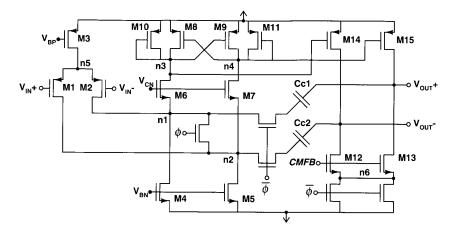

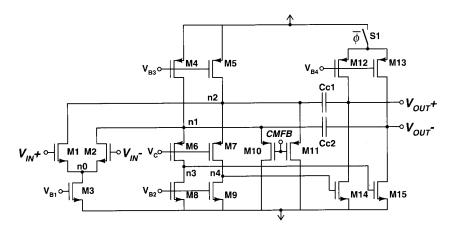

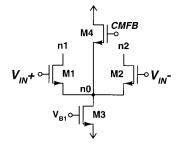

|          | 2                      | OTAs with Single High-Gain Stage                      | 95   |

|          | 3                      | Two-Stage Opamps                                      | 103  |

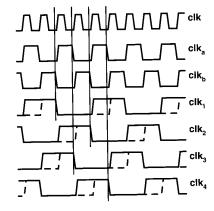

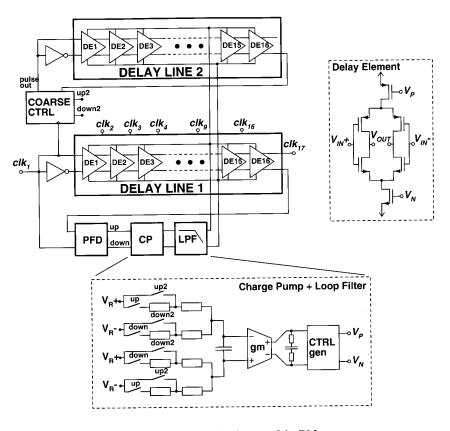

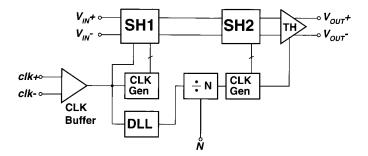

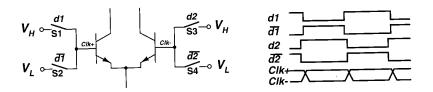

| 8.<br>9. | CL                     | OCK GENERATION                                        | 109  |

|          | 1                      | Jitter                                                | 109  |

|          | 2                      | Signal Crosstalk                                      | 113  |

|          | 3                      | Circuits                                              | 114  |

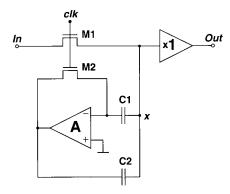

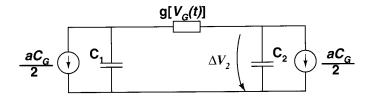

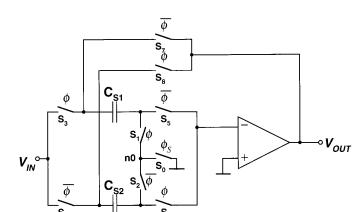

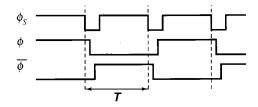

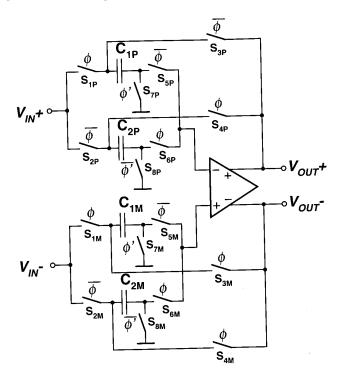

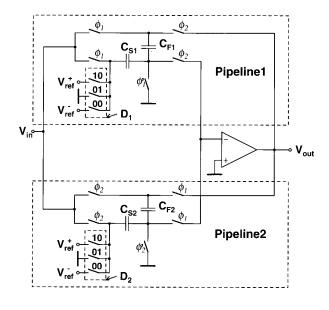

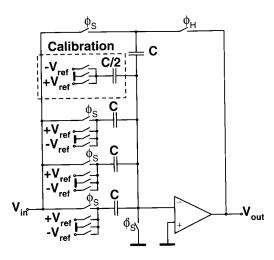

| 9.       | DC                     | OUBLE-SAMPLING                                        | 117  |

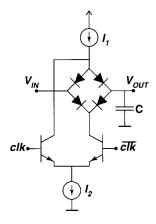

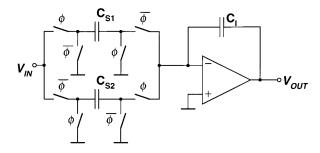

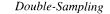

|          | 1                      | Principle                                             | 117  |

| 9.       | 2                      | Nonidealities                                         | 118  |

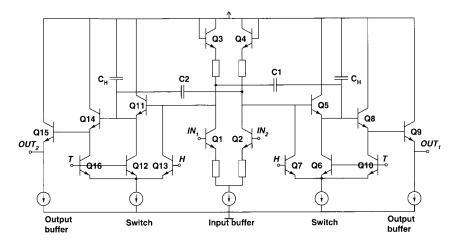

|          | 3                      | Skew-Insensitive Circuit                              | 126  |

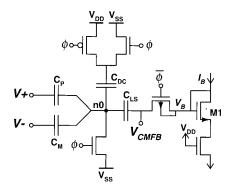

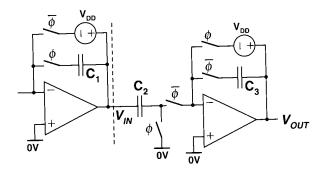

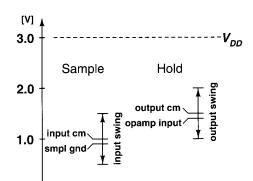

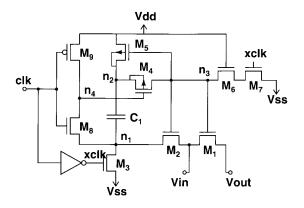

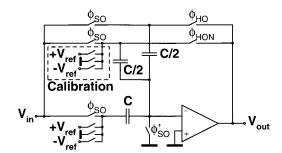

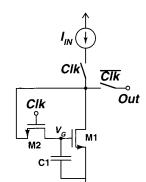

| 10       | . SV                   | VITCHED OPAMP TECHNIQUE                               | 129  |

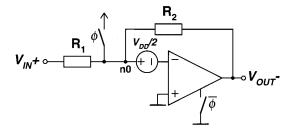

|          | 1                      | Operation Principle                                   | 129  |

|          | 2                      | Compensating for Common Mode Voltage Step             | 131  |

| 10.      | 3                      | Preventing Charge Leakage from Virtual Ground         | 131  |

|          | 4                      | Speed                                                 | 133  |

|          | 5                      | Power Supply Rejection and Noise                      | 135  |

|          | 6                      | Switchable Opamps                                     | 135  |

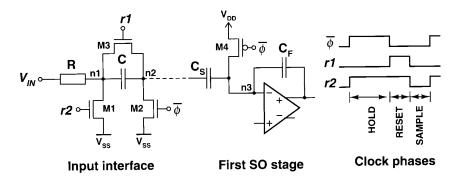

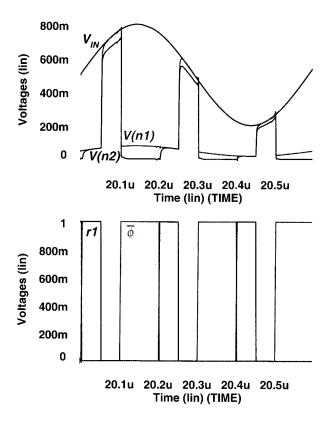

|          | 7                      | Input Interfaces for SO Circuits                      | 147  |

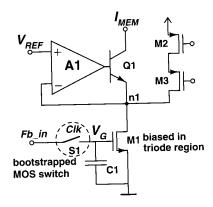

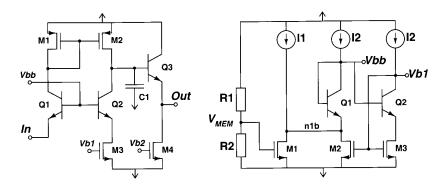

| 11       | . OI                   | THER LOW-VOLTAGE TECHNIQUES                           | 153  |

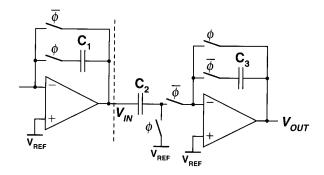

|          | 1                      | Low Voltage SC Technique with Unity-Gain-Reset Opamps | 153  |

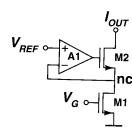

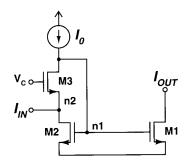

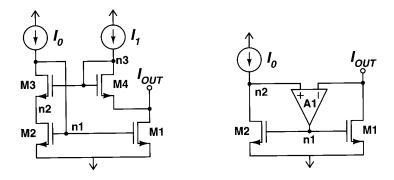

|          | 2                      | Current Sources and Mirrors                           | 155  |

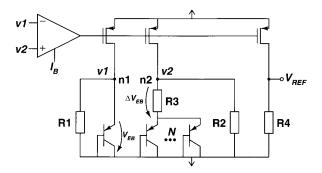

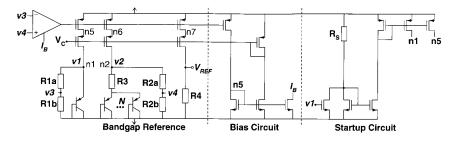

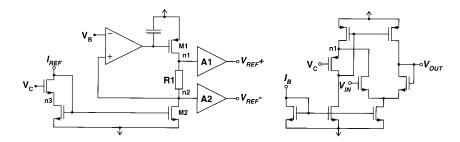

|          | 3                      | Bandgap References                                    | 156  |

| Conten                    | ts                                               | vii |

|---------------------------|--------------------------------------------------|-----|

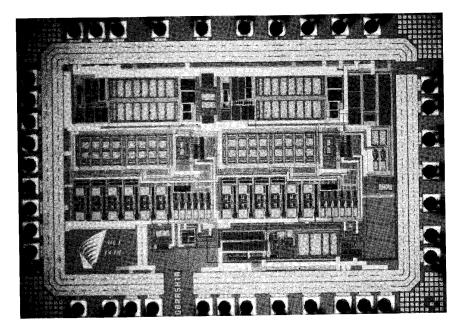

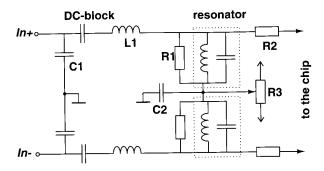

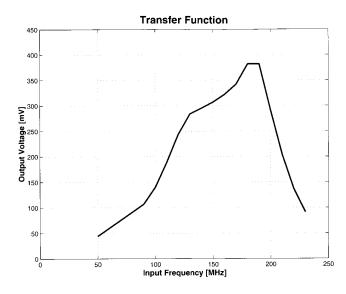

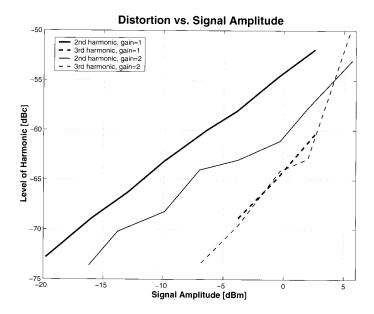

| 12. PR                    | OTOTYPES AND EXPERIMENTAL RESULTS                | 161 |

| 1                         | Measurement Setups and Methods                   | 161 |

| 2                         | S/H Circuit Using Double-Sampling                | 163 |

| 3                         | Timing Skew-Insensitive Double-Sampling S/H      | 170 |

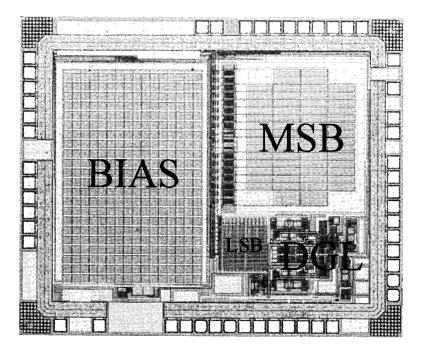

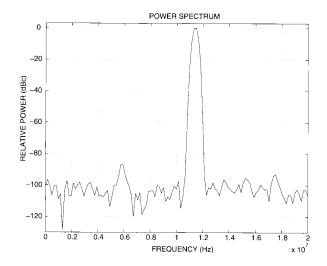

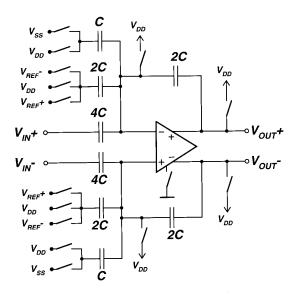

| 4                         | 10-Bit, 200-MS/s Parallel Pipeline ADC           | 173 |

| 5                         | 13-Bit Self-Calibrated IF-Sampling Pipelined ADC | 185 |

| 6                         | Deglitcher for Current Steering DACs             | 203 |

| 7                         | 1st Switched Opamp Pipelined ADC                 | 216 |

| 8                         | 2nd Switched Opamp Pipelined ADC                 | 221 |

| 13. CO                    | DNCLUSIONS                                       | 231 |

| Appen                     | dices                                            | 233 |

| De                        | rivation of OTA GBW Requirement                  | 233 |

| Optimum Input Capacitance |                                                  |     |

| Sat                       | uration Voltage                                  | 237 |

|                           |                                                  |     |

# Chapter 1

#### INTRODUCTION

For four decades the evolution of integrated circuits has followed Moore's law, according to which the number of transistors per square millimeter of silicon doubles every 18 months. At the same time transistors have become faster, making possible ever-increasing clock rates in digital circuits. This trend seems set to continue for at least another decade without slowing down. Thus, in the near future the processing power of digital circuits will continue to increase at an accelerating pace.

For analog circuits the evolution of technology is not as beneficial. Thus, there is a trend to move signal processing functions from the analog domain to the digital one, which, besides allowing for a higher level of accuracy, provides savings in power consumption and silicon area, increases robustness, speeds up the design process, brings flexibility and programmability, and increases the possibilities for design reuse. In many applications the input and output signals of the system are inherently analog, preventing all-digital realizations; at the very least a conversion between analog and digital is needed at the interfaces. Typically, moving the analog-digital boundary closer to the outside world increases the bit rate across it.

In telecommunications systems the trend to boost bit rates is based on employing wider bandwidths and a higher signal-to-noise ratio. At the same time radio architectures in many applications are evolving toward software-defined radio, one of the main characteristics of which is the shifting of the analog-digital boundary closer to the antenna.

Because of these trends, there is an urgent need for data converters with increasing conversion rates and resolution. A part of this needed performance upgrade comes with the technology evolution, but often the demand is higher than this alone can provide. Thus, there is still room, and a need, for innovations in circuit design.

#### CIRCUIT TECHNIQUES FOR LOW-VOLTAGE AND HIGH-SPEED ADCS

2

The increasing integration level leads to systems with a smaller number of chips, the ultimate goal being a single chip solution, the system on a chip (SoC). This means that analog and digital circuits have to live on the same silicon die, which brings additional challenges in analog design, such as mixed signal issues and limitations in the choice of technology. Data converters are inherently mixed signal circuits and face the same challenges on a smaller scale even without going as far as SoC. Furthermore, the evolution of technology has been driven by the microprocessor industry and hence does not always go in the best direction for the analog. However, the recent rapid growth of the wireless telecommunications devices market has given a boost to the development of advanced mixed signal technologies, such as silicon germanium-based BiCMOS.

The main challenges in data converter design are decreasing supply voltage, short channel effects in MOS devices, mixed signal issues, the development of design and simulation tools, and testability. In analog-to-digital converters (ADCs), they need to be met at the same time as the requirements for sampling linearity, conversion rate, resolution, and power consumption are becoming tighter.

This book concentrates on low voltage issues in ADCs by searching for and developing techniques and circuit structures suitable for today's and the future's low voltage technologies. In parallel, the increasing demands for ADCs have been answered by developing high-frequency high-linearity sampling techniques and applying them to ADC prototypes, which are presented in the last chapter.

# Chapter 2

#### LOW VOLTAGE ISSUES

The whole history of integrated circuits has followed a trend of descending supply voltage. For a long time the de facto standard was 5 volts. The migration to a 3.3-volt supply in the mid-'90s started a trend in which almost every new process generation has a lower nominal supply voltage than its predecessor. Today the 0.25- $\mu$ m generation uses a 2.5-V supply and, according to Semiconductor Industry Association's roadmap [16], it will be scaled down to 1.2 V by 2004 and to 0.9 V by 2008.

Table 2.1 shows process parameters for different technology generations. The data, including the effective channel length, supply voltage, oxide thickness, threshold voltage, and threshold voltage matching parameter, is collected from real processes. The table is reprinted from [17].

There are two main drivers for voltage scaling: technology and power. The shrinking technology feature size leads to lower break down voltages and thus

| Table 2.1. Technology data collected from different processes [1] | Table 2.1. | Technology data collected from different processes [1] | 7]. |

|-------------------------------------------------------------------|------------|--------------------------------------------------------|-----|

|-------------------------------------------------------------------|------------|--------------------------------------------------------|-----|

| $\overline{L_{min}}$ | $V_{DD}$ | $T_{ox}$ | $V_{th}$ | $A_{Vth}$ |

|----------------------|----------|----------|----------|-----------|

| 1.0                  | 5.0      | 250      | 0.95     | 20        |

| 0.8                  | 5.0      | 200      | 0.85     | 13        |

| 0.5                  | 3.3      | 135      | 0.73     | 11        |

| 0.35                 | 3.3      | 100      | 0.59     | •9.0      |

| 0.25                 | 2.5      | 60       | 0.52     | 6.0       |

| 0.18                 | 1.8      | 50       | 0.42     | 4.2       |

| 0.12                 | 1.2      | 42       | 0.32     | 3.8       |

| 0.10                 | 1.2      | 36       | 0.31     | 3.2       |

| 0.07                 | 0.9      | 30       | 0.30     | 2.5       |

4

Low Voltage Issues

supply voltage scaling is mandatory. Due to the ever-increasing integration level, which aims toward a system-on-a-chip (SoC), the power dissipation of a single chip tends to rise, which leads to severe heat problems and increased cooling system costs. On the other hand, the rapidly-growing market for portable battery-operated devices, such as laptops, PDAs, and cellular phones, demands high signal processing capacity together with low power dissipation.

The power dissipation of a logic gate is given by

$$P_{DIG} = \frac{1}{2} \cdot V_{DD}^2 \cdot C_L \cdot f_{clk} \cdot \alpha, \tag{2.1}$$

where  $V_{DD}$  is the supply voltage,  $C_L$  the load capacitance,  $f_{clk}$  the clock frequency, and  $\alpha$  the switching probability. It is obvious that as a result of the quadratic dependence, the most effective way to reduce power consumption is to lower the supply voltage. Although it affects the circuit speed, every new technology generation comes with enhanced device characteristics and the possibility of increasing parallelism in the logic, which together more than compensate for the speed loss.

The situation regarding analog circuits is much more complicated and, as will be shown later, not so bright. The fundamental limits of power consumption in different types of analog circuits are discussed in several papers: switched capacitor filters in [18], continuous time filters in [19, 20], and data converters in [21]. The common finding in these papers is that there is a certain energy needed to present the signal and the resulting power is proportional to the signal or clock frequency and the desired signal-to-noise ratio, but not dependent on the semiconductor devices used or the supply voltage. In reality that fundamental limit cannot be reached or even approached because of the limitations of the technology (speed, noise, parasitic capacitances, etc.) and the circuit topologies. Low-voltage circuit techniques for different applications have been compared and analyzed, e.g. for filters in [22], for analog and digital video signal processing [23], and for various applications from sensor readout circuits to RF circuits in [24].

The remainder of this chapter concentrates on analyzing how supply voltage scaling affects the analog circuits, when the limitations of a CMOS technology are taken into account. The analysis concentrates on SC circuits and their most important building blocks: opamps and switches. The opamp is assumed to dominate power consumption, while the speed is determined by both the opamp and the switches.

To simplify the calculations, the transistor current is assumed to follow the square-law model, which does not describe very accurately the behavior of the deep-submicron transistors. The short channel effects and their impact on the results are, however, also discussed briefly.

#### 1. Signal-to-Noise Ratio

One fundamental difference in analog signal processing compared to the digital is the significance of thermal noise [25], which sets a limit for the smallest distinguishable signal in the analog circuits. On the other hand, the supply voltage limits signal amplitude on the high side. The difference between these two boundaries determines the dynamic range, which is a key parameter in most systems. For a sinusoidal signal the peak signal-to-noise ratio is determined by

$$\sqrt{DR} = \sqrt{SNR_{max}} = \frac{V_{max}}{2\sqrt{2} \cdot \overline{V_n}} = \frac{V_{DD} - V_{margin}}{2\sqrt{2} \cdot \overline{V_n}},$$

(2.2)

where  $V_{max}$  is the maximum peak-to-peak signal amplitude and  $\overline{V_n}$  the rms noise voltage. In real circuits the signal can never go all the way from the negative supply rail to the positive one; thus the  $V_{margin}$  in the second form of the equation. The required margin is highly dependent on circuit topology and somewhat dependent on current levels and the process parameters. It is typically some hundreds of millivolts at its minimum, ranging up to several volts at its maximum.

Lowering the supply voltage leads to decreased signal-to-noise ratio unless the noise level is scaled down simultaneously. What the cost is of keeping the DR constant in terms of circuit speed and current consumption is discussed next.

The thermal noise in CMOS circuits originates mainly from two sources: the resistors and the transistors. Which one dominates is circuit-dependent. In switched capacitor circuits the dominant noise source is typically the switch on-resistance and the rms noise voltage is given by

$$\overline{V_n} = k_1 \sqrt{\frac{kT}{C}},\tag{2.3}$$

where k is Boltzmann's constant, T the absolute temperature, C the sampling capacitor, and  $k_1$  a constant dependent on circuit topology. For a given circuit the only way a designer can reduce the noise is to increase the capacitance.

The equation for gate-referred MOS transistor noise has the following form:

$$\overline{V_n} = \sqrt{\frac{4\gamma kTB}{g_m}},\tag{2.4}$$

where B is the noise bandwidth,  $g_m$  the transistor transconductance, and  $\gamma$  the noise excess factor. It will be shown later that in SC circuits  $g_m$  must be scaled linearly with the capacitance C to keep the circuit speed unaffected. This leads to the same type of supply voltage dependency in circuit speed and power

consumption as with the equation (2.3) and thus this case will not be discussed separately.

One hypothetical way to reduce thermal noise is cooling. However, substantial noise reduction is not obtained without extensive cooling. For example, cooling a circuit from room temperature (300 K) to the temperature of liquid nitrogen (77 K) reduces the noise by 6 dB or, alternatively, allows capacitor sizes to be reduced by a factor of four.

#### 2. Circuit Speed

The speed of analog circuits is not usually directly dependent on the supply voltage. However, if the dynamic range is kept constant while decreasing the supply voltage, the capacitances have to be larger and thus the circuit speed is reduced. In addition, low-voltage circuit topologies are, in many cases, inherently slower than their high-voltage counterparts. Furthermore, the value of the parasitic drain and source junction capacitance increase as the substrate doping level increases and the reverse bias voltage decreases.

In switched capacitor circuits the maximum clock frequency is inversely proportional to the settling time, which is determined by slew rate and opamp bandwidth. For a single stage opamp the gain bandwidth product is given by

$$GBW = \frac{g_m}{2\pi C_L} = \frac{g_m}{k_3 C},\tag{2.5}$$

where  $g_m$  is the transconductance of the input transistor and  $C_L$  the load capacitance, which can be approximated to be proportional to the sampling capacitor C with circuit-dependent proportionality factor  $k_3$ . Solving C from (2.3) and (2.2), and substituting it to (2.5) yields

$$GBW = \frac{g_m(V_{DD} - V_{margin})^2}{k_3 DR \cdot k_1^2 kT}.$$

(2.6)

Thus, when the settling time is dictated by the opamp GBW, the speed of an SC circuit decreases with the square of the supply voltage if DR is kept constant. It should be noted that the bandwidth loss can be compensated for by increasing the transconductance  $g_m$ .

Especially in moderate resolution circuits, the settling time can be dictated by the slew rate, which is given by

$$SR = k_4 \frac{V_{max}}{T_S} = \frac{I_{SR}}{C_L},\tag{2.7}$$

where  $T_S$  is the clock period and  $I_{SR}$  the available slewing current. Solving  $T_S$  and substituting  $C_L$  and  $V_{max}$  from (2.3) and (2.2) yields

$$T_S = \frac{k_4 V_{max} C_L}{I_{SR}} = \frac{k_1^2 k_3 k_4 D R^2 k T}{I_{SR} (V_{DD} - V_{margin})},$$

(2.8)

which indicates that the attainable clock rate decreases linearly with the supply voltage unless the slewing current is increased.

#### 3. Power Consumption

In the previous section it was shown that scaling down the supply voltage causes speed loss in the SC circuits unless the  $g_m$  of the opamp input transistor and/or the slewing current  $I_{SR}$  is/are increased. What the power consumption will be, if both the circuit speed and the DR are preserved while the supply voltage is reduced, is analyzed next.

#### 3.1 Saturated MOSFET in Strong Inversion

Let us first look at the case where the circuit speed is limited by the opamp GBW. The opamp is a single stage operational transconductance amplifier (OTA) and its input transistor is realized with a MOSFET biased in the saturation region. Thus, the transconductance is

$$g_m = \sqrt{\frac{I_D \mu C_{ox} W}{L}} = \sqrt{\frac{I_D \mu C_G}{L^2}},\tag{2.9}$$

where  $I_D$  is the drain current,  $\mu$  the carrier mobility,  $C_{ox}$  the gate oxide capacitance, and W and L the channel width and length. The second form of the equation is written using the expression for the gate capacitance  $C_G = C_{ox}WL$ . The gate capacitance appears between the opamp input and the ground and thus has an effect on the transfer function. It can be shown (see Appendix B) that in SC amplifiers (and integrators) there exists an optimum gate capacitance  $C_{G,opt}$ , which minimizes the settling time. This optimum is proportional to the sampling capacitor:  $C_{G,opt} = k_5 C$ , where  $k_5$  is a circuit-dependent proportionality factor.

Now equation (2.5) for GBW can be rewritten

$$GBW = \frac{\sqrt{\mu k_5} \sqrt{I_D}}{k_3 L \sqrt{C}}.$$

(2.10)

Solving  $I_D$  yields

$$I_D = \frac{k_3^2 L^2 G B W^2 C}{\mu k_5}. (2.11)$$

Using this the power consumption can be calculated to be

$$P_{SC,si} \propto I_D V_{DD} = \frac{k_3^2 k_1^2 L^2 GBW^2 DR \cdot kT}{\mu k_5} \cdot \frac{V_{DD}}{(V_{DD} - V_{margin})^2},$$

(2.12)

where the second form is obtained by substituting C from (2.3) and (2.2). Next it is necessary to ask, if  $V_{margin}$  depends on  $V_{DD}$ . An assumption valid in most cases is that  $V_{margin}$  is determined by the saturation voltage  $V_{dsat} = V_{GS} - V_{T}$  of the amplifier output stage transistors. An analysis carried out in Appendix C shows that, if the technology is fixed,  $V_{dsat}$  will be constant.

So it can be seen that for a given technology (fixed L) the power tends to increase when the supply voltage is decreased.

#### 3.2 Saturated MOSFET in Weak Inversion

In many low-power and low-to-medium speed circuits the transistors are biased in the weak inversion region, where the transconductance is linearly dependent on the drain current and independent of the transistor aspect ratio. The power consumption can be calculated as before, resulting in

$$P_{SC,wi} \propto \frac{k_3 k_1^2 GBW \cdot DR \cdot k^2 T^2 n}{q} \cdot \frac{V_{DD}}{(V_{DD} - V_{margin})^2}, \tag{2.13}$$

where n is the subthreshold slope factor and q the charge of an electron. The parameter n is only slightly dependent on the bias point and the technology line width, being approximately 1.3 in a bulk silicon technology and 1.0 in a fully depleted silicon on insulator (SOI) technology [26].

# 3.3 Slew Rate Limited Power Consumption

When the SC circuit speed is slew rate limited, the power consumption is proportional to the slewing current and can be calculated using (2.8):

$$P_{SC,sr} \propto \frac{k_3 k_4 k_1^2 DR \cdot kT \cdot V_{DD}}{T_S(V_{DD} - V_{margin})}.$$

(2.14)

It is interesting to note that  $V_{margin}$  is the only term in the equation that has some technology dependency.

### 3.4 Technology Impact

How do the previous equations change when the voltage is scaled along with the technology? At least down to the 0.07- $\mu m$  generation, the maximum supply voltage scales roughly linearly with the technology line width (see Table 2.1). Taking this into account by replacing the L proportionality with  $V_{DD}$  proportionality, the equation (2.12) for strong inversion can be rewritten

$$P_{SC,scaledL} \propto \frac{V_{DD}^3}{(V_{DD} - V_{maxain})^2}.$$

(2.15)

The analysis in Appendix C yields that  $V_{margin}$  is proportional to  $V_{DD}^{m}$ , m ranging from 1 to 1.5. Substituting this into the previous equation results in a curve that decreases linearly with  $V_{DD}$  for m=1 and decreases even faster if m is larger.

The technology scaling does not change the equations for weak inversion and slew-rate determined power except through  $V_{margin}$ . When m=1 the slew-rate limited power is constant.

What makes power reduction possible in strong inversion is the fact that supply voltage scaling forces one to increase sampling capacitor size, resulting, as a positive side effect, in a larger optimum transistor gate capacitance. At the same time, the scaled-down technology offers more transconductance for a fixed current and fixed gate capacitance. In practice, the transconductance up-grade is obtained by increasing the W/L ratio, which moves the bias point toward weak inversion. Eventually, the transistor enters into weak inversion, where transconductance is not dependent on the aspect ratio and thus the power starts to increase according to (2.13).

# 3.5 Power Consumption: Summary and Conclusions

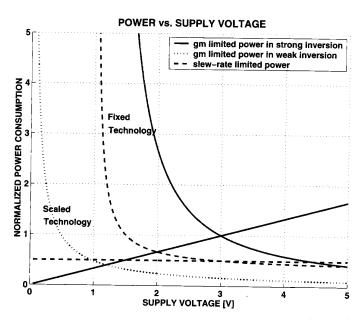

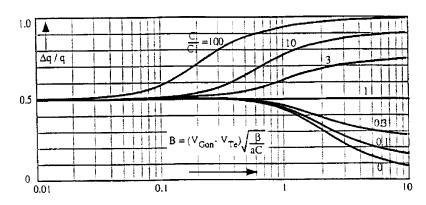

Figure 2.1 illustrates how the power consumption of thermal noise-limited SC circuits depends on the supply voltage, according to the previous equations. It is clear that, for a given technology, reducing the supply voltage increases the power consumption, the limiting factor being either opamp bandwidth or slew rate. When a scaled technology is utilized, with its nominal supply voltage, the slew rate-limited power is independent of the supply voltage, and the opamp bandwidth-limited power consumption decreases with the supply when the transistors are in strong inversion and increases when they are biased in the weak inversion. In practice, the power follows the curve which is largest and, as a result, there is an optimum technology after which further scaling leads to increased power consumption. The analysis presented in [20] shows a similar trend in continuous time circuits.

The analysis has not taken account of the short channel effects, the most important of which is velocity saturation. The carrier velocity saturates when the  $V_{GS}-V_T$  voltage reaches a certain value, which is several volts for long channel devices but decreases with technology scaling. In velocity saturation the transistor current does not follow the square law; instead it is given by [27]

$$I_D = v_{sat} C_{ax} W \left( V_{GS} - V_T \right).$$

(2.16)

Figure 2.1. The effect of supply voltage scaling on the power consumption an SC circuit. A case where the technology line width is scaled along the supply voltage is compared to a case where the technology is fixed.

Consequently, the transconductance is independent of the current. As the technology is scaled down, the strong inversion region—between the weak inversion and the velocity saturation—gets narrower and eventually vanishes altogether [28, 29].

In Appendix B it is shown that for a given current and fixed L the minimum settling time of an SC amplifier is obtained in the strong inversion region and, when it is absent, at the point where the weak inversion region turns into the velocity saturation region. In the latter case the power consumption follows the weak inversion curve.

#### 4. Matching

In most low-to-medium resolution circuits capacitor sizes are not limited by thermal noise but the matching. For example, in a 10-bit pipelined ADC with 2-V signal range the thermal noise sets the capacitor size below 0.1 pF, which is considerably smaller than typical capacitor sizes in 10-bit ADCs. In the signal transfer function capacitor ratios multiply voltages. Thus, the errors resulting from the mismatch do not depend on the absolute voltage values, making possible the scaling down of the supply and the signal range without changing the capacitor size. This results in a linear power reduction in opamp-bandwidth-

limited power consumption and an even larger reduction in the slew rate-limited power consumption, even without technology scaling. At some point the thermal noise floor will be reached and capacitor size has to be increased.

Another type of mismatch error is the comparator and opamp offset voltage, originating from transistor threshold voltage and  $\beta$  (=  $C_{ox}\mu W/L$ ) mismatch. In the signal transfer function the offset appears in an additive manner, thus causing larger relative error if the signal range is decreased. A widely accepted model for the threshold voltage mismatch of two transistors is given by [30, 31]

$$\sigma^{2} \left( \Delta V_{T} \right) = \frac{A_{Vth}^{2}}{WL} + S_{Vth}^{2} D^{2}$$

(2.17)

and for the  $\beta$  mismatch by

$$\sigma^2 \left( \frac{\Delta \beta}{\beta} \right) = \frac{A_\beta^2}{WL} + S_\beta^2 D^2. \tag{2.18}$$

In most analog circuits the last term, which depends on the distance D between the devices, is small compared to the first one in both the equations and thus can be neglected.

In today's technologies the threshold voltage mismatch is the dominant source of offset in typical analog circuits. From Table 2.1 it can be seen that the parameter  $A_{Vth}$  scales linearly with the line width, and thus technology scaling improves the matching. The  $\beta$  mismatch, however, does not improve significantly with the technology, and consequently at some point it starts to dominate [32], putting an end to the trend of improving matching. Although  $V_T$  matching improves with technology, the decreasing supply voltage and the increasing oxide capacitance result in worse matching with a given circuit speed and power consumption [33, 32].

Offset voltages are a major concern in flash and folding-and-interpolating ADCs, while pipelined ADCs are fairly robust against offsets. It has to be remembered that since mismatch is time invariant, it is fundamentally different from thermal noise. Therefore, various techniques can be used to reduce, correct, and calibrate the errors originating from mismatch. These techniques can be analog, digital, or mixed signal.

#### 5. Operational Amplifiers

When opamps are employed as building blocks in SC circuits, they can almost always be used in the inverting feedback configuration, where the signal swing in the opamp input is very small. Thus, the input structure does not limit the signal range. The opamp output stage, in contrast, sees the full signal swing and ultimately sets the maximum limit for it.

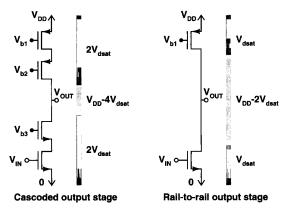

Figure 2.2. Output signal swing in different output stages.

Single-stage opamp topologies, such as the telescopic opamp or the folded cascode opamp, are regarded as the fastest and most power-efficient structures for integrated applications. In achieving the required high DC gain they rely on cascoding, which limits the output signal swing. When two or more gain stages are used, the required DC gain can be obtained without cascoded structures in the amplifier output. This type of opamp, for example, the traditional Miller opamp, requires somewhat more power to achieve the same bandwidth as single-stage opamps.

In Figure 2.2 two output stages and corresponding signal swings are shown: a cascoded output stage on the left and a rail-to-rail output stage on the right. Despite its name, the latter circuit cannot provide true rail-to-rail signal swing, since there is one transistor between the signal and the supply rail. This is, however, as close as it is possible to go: thus, the name is justified. For proper operation the transistors have to be in saturation, which requires the drain-source voltage to be at least equal to the saturation voltage  $V_{dsat}$ , which depends on the current level and technology line width. In typical opamp designs the values are some hundreds of millivolts. In practice, in addition to the  $V_{dsat}$ , some extra voltage margin has to be reserved to achieve robustness against inaccurate biasing and to get a decent output impedance.

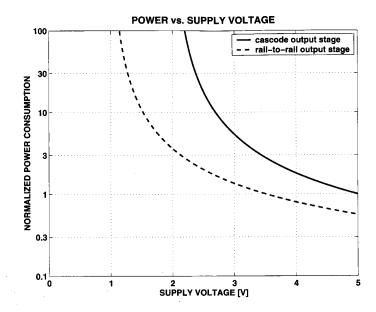

The reduction in signal swing in the cascode stage is twice that in the rail-to-rail stage. It is obvious that as the supply voltage gets lower the margin eats an increasing portion of the signal range. How this affects power consumption is illustrated in Figure 2.3. There the power consumption, given by equation (2.12), is plotted against the supply voltage for both output stages. The power is normalized in such a way that for the cascode circuit it is 1 at 5 V. The voltage margin in the rail-to-rail circuit is set to 1.0 V and in the cascode circuit to 2.0 V.

Figure 2.3. Power consumption of circuits using different types of opamp.

At 5 V the circuit with the cascode stage dissipates 78% more power, which will probably be compensated for in a more efficient opamp topology. When the supply voltage is lower, the penalty grows bigger, being 400% at 3 V, which undoubtedly favors the opamp with the rail-to-rail output stage. Thus, opamp topology has a significant effect on power consumption. Consequently, multistage opamps with rail-to-rail output stage are preferable choices in low-power low-voltage designs.

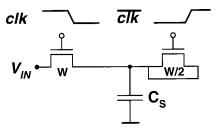

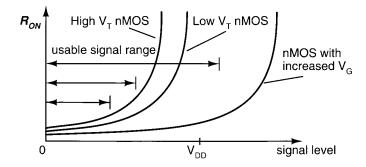

#### 6. MOS Switches

Another crucial building block in the SC circuits is the switch. An ideal switch has infinite resistance when it is open and zero resistance when it is closed. At high supply voltages (5 V and higher), a MOS transistor has been a good enough approximation of that. On the other hand, the finite on-resistance of a closed MOS switch has already caused problems in some applications with a 3-V supply and the problems are believed to get worse as the supply is scaled down. Whether these problems are due to increased circuit performance requirements or to the technology scaling is investigated next.

The on-resistance of a MOS switch can be written as

$$R_{ON} \approx \frac{L}{W\mu C_{ox}(V_{GS} - V_T)},\tag{2.19}$$

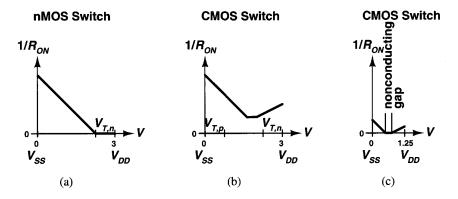

Figure 2.4. Inverse of the switch on-resistance as a function of the signal voltage for an nMOS (a) and a CMOS (b) switch with high supply voltage and a CMOS switch with low supply voltage (c).

where  $V_{GS}$  is the transistor gate-source voltage and  $V_T$  the threshold voltage. The equation is valid when  $V_{GS} \geq V_T$ ; with smaller gate-source voltages the resistance is infinite. To turn the switch properly on, its gate-source voltage has to be  $V_T$  plus some overdrive to make the on-resistance small enough.

A single-transistor switch cannot conduct over the whole rail-to-rail signal range, since, for example, an nMOS switch, whose gate is tied to  $V_{DD}$ , cuts off when the signal level is raised within a threshold voltage of  $V_{DD}$ . This is illustrated in Figure 2.4 (a), where the inverse of the on-resistance is plotted against the signal level. The whole range can be covered by putting an nMOS and a pMOS transistor in parallel to form a CMOS switch or a transmission gate (Figure 2.4 (b)). The on-resistance has its largest value in the mid-range between the supplies, when the overdrive voltage is approximately  $V_{DD}/2-V_T$ . Thus, the maximum on-resistance, which is given by

$$R_{ON,max} \propto \frac{L}{C_{ox}\mu W \left(V_{DD} - 2V_T\right)},$$

(2.20)

has a strong correlation with the supply voltage.

When  $V_{DD}$  becomes smaller than  $V_{T,n} + V_{T,p}$  a non-conducting gap appears in the mid-supply range (Figure 2.4 (c)). In most applications the switch becomes useless much earlier as a result of too-large on-resistance, which makes the settling times long. Another problem, especially in S/H circuits, is the signal-dependent nature of the resistance, which causes harmonic distortion when sampling continuous time signals. Consequently, the resistance has to be much smaller than in the case of a constant on-resistance.

What is the effect of technology scaling on the on-resistance? Because of increasing leakage current in digital circuits the threshold voltage cannot be scaled down linearly with the supply voltage, but the scaling rather follows a square root function. The threshold voltage values from 0.35- $\mu$ m generation to 0.07- $\mu$ m generation in Table 2.1 fit quite accurately to  $0.32 \cdot \sqrt{V_{DD}}$ . Using this and assuming a linear dependence between the line width and the supply voltage equation (2.20) can be rewritten

$$R_{ON,max} \propto \frac{V_{DD}^2}{C_G (V_{DD} - 0.64 \cdot \sqrt{V_{DD}})},$$

(2.21)

where  $C_G = C_{ox}WL$ .

Low Voltage Issues

Remembering that reducing the signal range increases the capacitances, the correct parameter to look at, is not the resistance, but the time constant, which is given by

$$\tau = RC \propto \frac{C}{C_G} \cdot \frac{V_{DD}^2}{(V_{DD} - 0.64 \cdot \sqrt{V_{DD}})}.$$

(2.22)

The parasitic capacitances of the switch are proportional to  $C_G$  and it is reasonable to assume that they can be allowed to grow at the same rate as the capacitance C. Thus, the first term in the equation is constant and the second one decreases linearly with the supply at high  $V_{DD}$  values, but starts to rise rapidly when the supply goes below  $0.9 \, \mathrm{V}$ .

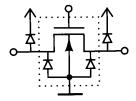

Methods to reduce the on-resistance can be divided into two categories: technology-based and circuit-based. The technology-based methods reduce the resistance by lowering the transistor threshold voltage, while the circuit-based methods increase the overdrive voltage.

One method is the use of a dual- $V_T$  process, which provides two types of transistors, with either a high or low threshold voltage. The idea of this technology is to improve the speed of digital logic by using low- $V_T$  transistors in critical places but at the same time keeping the leakage current small with high- $V_T$  transistors. In analog designs the low- $V_T$  transistors can be employed as switches. There are, however, at least two problems with this technology: it is not a mainstream technology—at least today—and so it costs more and is not necessarily available with analog extensions (capacitors and resistors). Circuits with low threshold switches may also suffer from charge leakage.

Another technology that may alleviate the switch problem is the siliconon-insulator (SOI) technology. SOI MOSFETs have inherently lower leakage current than their bulk CMOS counterparts and so with the same channel length the threshold voltage of an SOI transistor is typically smaller. The future will show whether this technology will become mainstream.

The methods that improve the switch by means of circuit techniques increase the overdrive voltage from  $0.5V_{DD} - V_T$ . The switch transistor gate-source

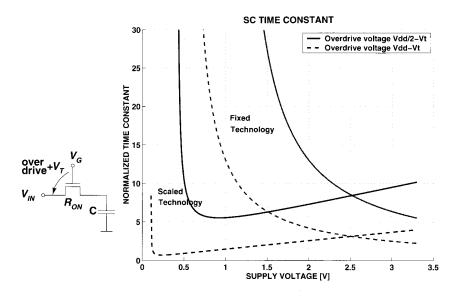

Figure 2.5. Time constant of a switched capacitor as a function of supply voltage.

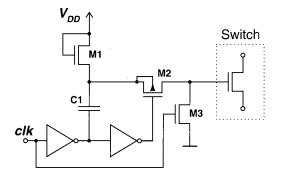

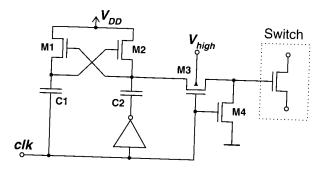

voltage can always be raised to at least  $V_{DD}$  without violating the technology specifications. A switch with a gate-source voltage of  $V_{DD}$  will have an overdrive voltage of  $V_{DD}-V_T$ , which is a substantial improvement on the earlier situation. One technique that can be used to realize this is gate-voltage bootstrapping. In this the voltage at the switch transistor gate is capacitively boosted above the supply voltage so that it follows the signal voltage with an offset equal to  $V_{DD}$ .

Another completely different circuit technique that also results in an overdrive of  $V_{DD}-V_{T}$  is the switched opamp technique [34]. In this the SC circuit and the opamp are modified in such a way that all the switches can operate against ground or virtual ground. Consequently, the switch does not see any voltage swing and the overdrive is always the maximum.

In Figure 2.5 the time constant is plotted as a function of the supply voltage with two different overdrive voltages, with and without technology scaling. It can be seen that technology scaling yields smaller SC time constants, even without any special techniques, down to a supply of 0.9 V. Increasing the overdrive brings a significant advantage by lowering the on-resistance in all supply voltages and extending switch usability to lower voltages.

Both bootstrapping and the switched opamp technique are discussed and analyzed more deeply in the following chapters.

#### 7. Conclusions

In today's world, where digital circuits offer more speed and capacity with reduced power consumption with every new technology generation, the expectations for analog circuits are similar. It has, however, been clear for a long time that the benefits of technology scaling are not so great for them, mainly because of the decreasing supply voltage. During recent times the question has rather been whether or not the technology scaling *degrades* the performance of the analog circuits.

The analysis of SC circuits presented in this chapter shows that there is, indeed, some benefit to be gained from technology scaling, at least for the next few technology generations. This, however, is probably not enough for the increased requirements and expectations that exist. Thus, there is an urgent need for techniques at the architectural and circuit levels for alleviating the problems associated with low voltage and more effectively taking advantage of the technology.

At the circuit level it is of the utmost importance to maximize the signal swing, which has a large impact on opamps and switches. In noise-limited circuits, using a supply voltage smaller than the maximum allowed does not bring any advantage at the circuit level. When accuracy is limited by capacitor matching, a lower supply may be justified.

Technology scaling is best exploited by doing things digitally. This does not only mean moving the signal processing functions from the analog domain to the digital one but also combining both techniques in realizing the system blocks. A good example is that of digitally self-calibrated pipelined ADCs, where technology scaling has made possible the incorporation of more and more complex digital calibration algorithms into ADCs. Similar types of techniques, to be used against mismatch and nonlinearity, can probably be developed for other applications as well in order to improve performance and permit more robust analog structures.

# Chapter 3

#### SAMPLE-AND-HOLD OPERATION

#### 1. S/H Basics and Performance Metrics

The main function of a sample-and-hold (S/H) circuit is to take samples of its input signal and hold these samples in its output for some period of time. Typically, the samples are taken at uniform time intervals; thus, the sampling rate (or clock rate) of the circuit can be determined.

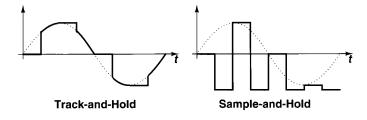

The operation of an S/H circuit can be divided into sample mode (sometimes also referred as acquisition mode) and hold mode, whose durations need not be equal. In hold mode, the output of the circuit is equal to the previously sampled input value. In sample mode, the output can either track the input, in which case the circuit is often called a track-and-hold (T/H) circuit, or it can be reset to some fixed value. In some circuits the output is held over the whole period of the sampling clock. This is achieved by having separate circuitry to perform the sampling and the holding operations.

The most common terms and performance metrics used in conjunction with S/H circuits ([35, 36]) are briefly introduced in the remainder of this section. Which of them are more important than the others greatly depends on the ap-

Figure 3.1. Output waveforms of different S/H circuits.

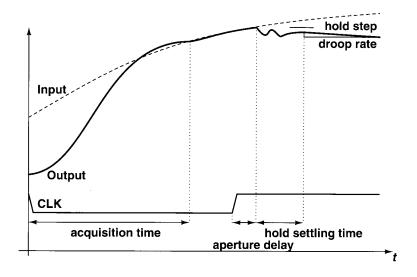

Figure 3.2. Time domain S/H circuit performance metrics.

plication of the S/H circuit. The technology utilized also has some effect on which parameters are usually given in circuit specifications. To fully characterize an S/H circuit, specifications both in the time domain and in the frequency domain have to be defined. Unfortunately, some of the terms used are not well-established and thus the definitions in different sources may be contradictory.

The *acquisition time* is the time from the command to switch from hold mode to sample mode to the moment when the circuit is ready to take a new sample, i.e. it tracks the input. Acquisition time is one of the parameters that define the maximum achievable sampling rate.

The *aperture time* or *aperture delay* is the fixed time from the sampling command to the moment when the sample is actually taken.

Random variation in the sampling moment is known as *aperture uncertainty* or *aperture jitter*.

The hold mode settling time determines the time from the sampling moment to the moment when the circuit output has settled within the specified accuracy of its steady state value. If the S/H circuit is used in front of an ADC, the ADC can digitize the S/H circuit output at that moment. The hold mode settling time has a major impact on the maximum sampling rate of the S/H circuit.

The signal may leak from the circuit when in hold mode. The rate of change in output that results from this is specified by the *droop rate*.

The *hold step* or *pedestal error* is usually defined for track-and-hold circuits. It is the difference in the output value at the end of the tracking and during

hold mode. The pedestal may be signal-dependent and thus produce harmonic distortion.

During hold mode the signal at the circuit input may couple to the output. The fraction of the input signal seen at the output is specified by the *hold mode feedthrough*.

Usually, S/H circuits have a unity gain (i.e. the amplitude of the output signal is equal to the amplitude of the input signal), but other gain values can be used as well. The *gain error* determines the deviation of the gain from the nominal value.

The *dynamic range* is the difference in decibels between the maximum allowed input voltage and the minimum input voltage that can be sampled with a specified level of accuracy.

Nonlinearity in the S/H circuit causes distortion. Measured with a sinusoidal input signal, the *total harmonic distortion* (*THD*) is the ratio of the sum of error energy in the frequencies harmonically related to the input frequency to the signal energy at the fundamental frequency. The THD can be given as a percentage or in decibels. In sampled data systems, aliasing complicates the identification of the harmonic frequencies in the spectrum.

The *spurious free dynamic range* (*SFDR*) is the ratio of the largest spurious frequency and the fundamental frequency.

The signal-to-noise ratio (SNR) is the ratio of noise energy to signal energy.

The *signal-to-noise-and-distortion ratio* (*SNDR* or *SINAD*) is the ratio of all error energy to signal energy. Quite often the term signal-to-noise ratio is used although SNDR is actually meant.

When an S/H circuit is employed in the ADC front-end it is meaningful to speak of *resolution*, which is expressed as a number of bits. Resolution is just another way to express the SNDR for the maximum input signal and it is obtained by (SNDR-1.76)/6.02.

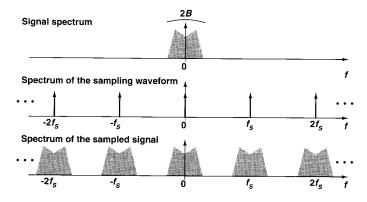

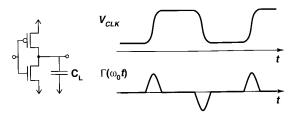

# 2. Spectra of Sampled Signals

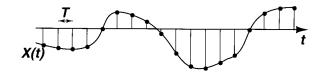

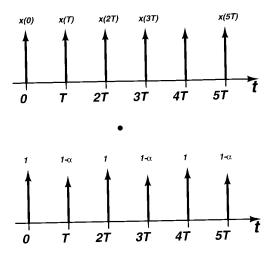

An ideal S/H circuit takes samples of an input signal at uniform intervals T. In the time domain this corresponds to multiplying the signal by an impulse train

$$y(t) = x(t) \cdot \sum_{n = -\infty}^{\infty} \delta(t - nT), \tag{3.1}$$

where  $\delta(t)$  represents Dirac's delta function. The result is a train of impulses whose values correspond to the instantaneous values of the input signal.

Figure 3.3. Sampling in time domain.

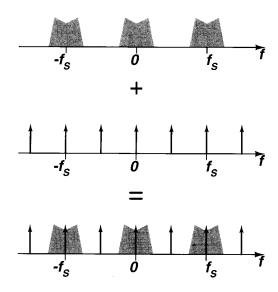

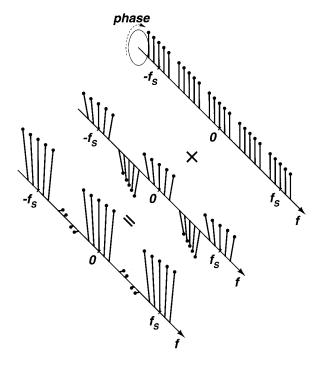

The spectrum of the sampled signal is a convolution of the input spectrum and the spectrum of the impulse train, which is also an impulse train

$$Y(f) = X(f) \star \sum_{n = -\infty}^{\infty} \frac{1}{T} \delta(f - \frac{n}{T}). \tag{3.2}$$

This is illustrated in Figure 3.4, where  $f_S$  is the sampling frequency and Bthe signal bandwidth. The resulting spectrum is the original spectrum plus an infinite number of images of the original spectrum centered at multiples of the sampling frequency. The figure also clearly shows that as long as the bandwidth of the input signal is less than half of the sampling frequency the images do not overlap and thus the original signal can be restored by filtering. If this condition—known as the Nyquist criterion—is not satisfied, a part of the image spectrum is aliased into the desired signal band, causing irreversible distortion. Because of this, the input signal usually has to be band limited before sampling in order to avoid the aliasing of noise and other unwanted signals present outside the desired signal band. In sub-sampling (or under-sampling) the aliasing is utilized to sample high frequency narrow-band signals. There, a signal band around some multiple of the sampling frequency is aliased to the baseband, which actually corresponds to down conversion. This can be used in radio receivers to digitize the intermediate frequency (IF) signal, using a relative narrow band ADC. In principle, the signal can be sub-sampled even at radio frequency (RF), but noise aliasing and sampling clock jitter limit performance and prevent the use of technique in most systems [37].

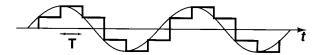

# 2.1 Spectrum of a Sampled and Held Signal

In practice, the output waveform of a sampling circuit cannot be a train of infinitely narrow impulses. In most practical implementations the sample is held in the output of the circuit until the next sample is taken (Figure 3.5). In that case the circuit is known as a sample-and-hold (S/H) circuit. Sometimes the output tracks the input for half of the sample period and is held in the sampled value for the other half. This type of circuit can be called a track-and-hold (T/H) circuit. However, inconsistent terminology is quite often seen.

Figure 3.4. Spectrum of a sampled signal.

Figure 3.5. A Sampled-and-held signal.

If the signal processing after a S/H circuit is performed in discrete time, which is, for instance, the case in ADCs with a front-end S/H circuit, the spectrum is the ideal periodic spectrum as in Figure 3.4. On the other hand, if the output waveform of the S/H circuit is used as a continuous time signal the spectrum is different. A deglitcher preceding a DAC is a typical example of this kind of circuit. A similar situation can also occur when measuring S/H circuits.

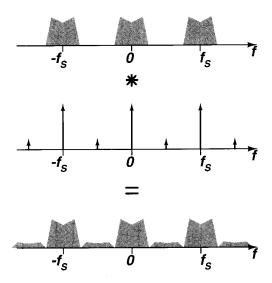

The time domain representation of a sampled-and-held signal is a convolution of the sampled signal (3.1) and a square pulse

$$y(t) = \left[ x(t) \cdot \sum_{n = -\infty}^{\infty} \delta(t - nT) \right] \star \Pi\left(\frac{t}{T} - \frac{1}{2}\right), \tag{3.3}$$

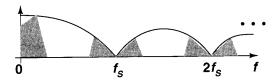

where  $\Pi(t/T-1/2)$  denotes a square pulse from t=0 to t=T. In the frequency domain the convolution corresponds to multiplication and thus the spectrum of the sampled-and-held signal is the spectrum of a sampled signal multiplied by the spectrum of the square pulse, which has the form of  $\sin(x)/x$ . Using this well-known relationship the spectrum of a sampled-and-held signal can be written as

$$Y(f) = e^{-j\pi fT} \cdot \frac{\sin(\pi fT)}{\pi fT} \sum_{n = -\infty}^{\infty} X(f - \frac{n}{T}). \tag{3.4}$$

Figure 3.6. Spectrum of sampled-and-held signal.

A power spectrum of this form is shown in Figure 3.6. In many cases the sinc attenuation is not tolerable and the signal has to be either predistorted before the hold operation or corrected after it.

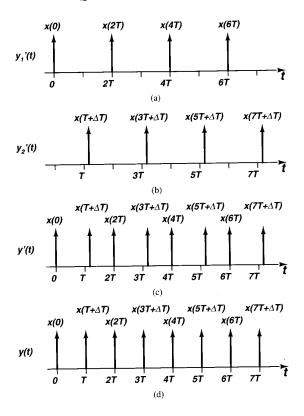

### 2.2 Sampling Function

When ideal impulses (Dirac's delta functions) are used to describe operations in analog continuous time signal processing, one should be on the alert. It turns out that it is impossible to realize a circuit performing the sampling according to (3.1). In practice, a circuit cannot pick the instantaneous value of its input signal, but rather it takes a weighted average of the input during a time window around the sampling moment. Mathematically, this is equal to integrating the product of the input signal and the sampling function from minus infinity to plus infinity in the time domain. For a single sample this can be written as follows:

$$y(t_0) = \int_{-\infty}^{\infty} x(t)h(t - t_0)dt,$$

(3.5)

where  $t_0$  is the sampling instant and h(t) the sampling function. The same for an infinite sequence of samples is

$$y(nT) = \sum_{n=-\infty}^{\infty} \int_{-\infty}^{\infty} x(t)h(t-nT)dt$$

(3.6)

$$= \sum_{n=-\infty}^{\infty} x(nT) \star h(-nT)$$

(3.7)

$$= [x(t) \star h(-t)] \sum_{n=-\infty}^{\infty} \delta(t - nT). \tag{3.8}$$

The integral in (3.6) can be identified as a convolution resulting (3.7). This can be interpreted as a sampled form of the convolution integral. In (3.8) the same is presented using the Dirac's delta function. Utilizing this, the frequency

domain signal can be easily obtained with the Fourier transform:

$$Y(f) = [X(f) \cdot H(-f)] \star \sum_{n = -\infty}^{\infty} \delta(f - \frac{n}{T}). \tag{3.9}$$

This shows that in the frequency domain the effect of the sampling function is seen as a multiplication by the conjugate of the Fourier transform of the sampling function. Since the Fourier transform of an impulse is 1 the equation (3.9) is consistent with (3.2). A more realistic sampling function than Dirac's delta function is a triangular pulse, whose Fourier transform is  $\sin^2(\pi f T_b/2)/(\pi f T_b/2)^2$ , where  $T_b$  is the width of the base of the triangle. In general it can be said that a real sampling function always adds a low-pass filtering effect to the sampling operation. The modeling of the limited tracking bandwidth can also be included in the sampling function [38].

#### 3. Noise Issues in S/H Circuits

#### 3.1 kT/C Noise

Any sampling circuit can be considered as consisting of at least a switch and a capacitor. The switch always has some finite on-resistance which generates thermal noise. The power spectral density of this noise is the well-known  $4kTR\ V^2/Hz$ , where k is Boltzmann's constant, T the absolute temperature, and R the resistance. The noise in the voltage sample is the resistor noise filtered by the low-pass circuit formed by the sampling capacitor and the switch on-resistance. Integrating the resistor noise spectral density weighted by the low-pass transfer function yields the mean square noise voltage on the capacitor

$$\sigma^2 = 4kTR \int_0^\infty \frac{1}{1 + (f2\pi RC)^2} df$$

(3.10)

$$= \frac{4kTR}{(2\pi RC)^2} \Big|_0^{\infty} 2\pi RC \arctan(f2\pi RC) = \frac{kT}{C}.$$

(3.11)

By looking at the result it becomes obvious why this noise is often referred to as kT/C noise. An interesting point is that the noise voltage does not depend on the value of the switch on-resistance, and thus the only parameter which can be used to control the noise is the value of the sampling capacitor. Although the desired signal bandwidth is typically at least an order of magnitude smaller than the noise bandwidth of the sampling circuit, the sampled noise is still determined by (3.11). This is due to the fact that the sampling operation aliases all the noise energy into the Nyquist band.

In ADCs a common requirement is that thermal noise power is smaller than the power of the quantization noise, which can be shown to be  $LSB^2/12$ . This

sets the lowest limit for capacitor value C as follows

$$C > \frac{kT \cdot 12}{LSB^2} = \frac{kT \cdot 12}{2^{-2N}V_{FS}^2},$$

(3.12)

where N is the number of bits and  $V_{FS}$  the voltage corresponding to the ADC full scale. Sometimes the requirement is more stringent, allowing only 1 dB of SNR degradation, which changes the factor 12 in the equation to 46.3. According to (3.12), in the case of 1-volt full-scale voltage, the capacitor values required for 10- and 16-bit resolution are 0.052 pF and 210 pF respectively, which indicates that the capacitor values for 16-bit resolution begin to be too large for practical integration. To overcome this, a popular solution in high-resolution applications is to use an oversampling ADC architecture, in which the capacitor size can be reduced linearly with the oversampling ratio.

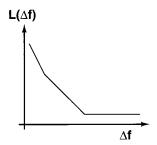

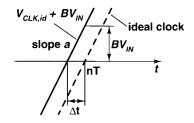

#### 3.2 Jitter in Sampling Clock

Random variation of the sampling instant is known as jitter. It originates from clock generator phase noise and sampling circuit noise. How the jitter is transformed to the amplitude error in the sampled voltages can be understood as follows: the error in the sampled voltage is equal to the change in the input voltage between the ideal sampling instant and the actual sampling instant. The voltage change in turn is proportional to the jitter and the rate of change of the input signal, i.e. its derivative. For a sinusoidal input the derivative is the cosine function multiplied by the corner frequency, which means that the voltage error is proportional to the frequency and the amplitude of the input signal. It can be shown [39] that the signal-to-noise ratio limited by jitter can be written as

$$SNR = -20\log(2\pi f \Delta t), \tag{3.13}$$

where f is the frequency of the input signal and  $\Delta t$  the rms value of the jitter. It can be seen that increasing the amplitude of the input signal does not improve SNR, since it also increases voltage error. Jitter is studied further in Chapter 8.

#### 3.3 Other Noise Sources

Most S/H circuits need a buffer amplifier or an opamp, at least when in hold mode. The internal noise sources of the amplifier add in power to the thermal noise of the switch on-resistances. In passive sampling the noise is band limited by the RC time constant of the sampling circuit. When an amplifier contributes to the circuit transfer function, which is usually the case in hold mode and, in some closed-loop S/H architectures, also in sampling mode, its finite bandwidth is likely to be the dominant band-limiting factor. To reduce the amount of aliased noise the bandwidth of the amplifier should be kept as small as is permitted by the settling requirements [40]. This is important, since if the S/H circuit is

followed by an ADC the S/H circuit noise during hold mode is also aliased due to the sampling performed by the ADC.

In addition to white noise, S/H circuits also suffer from flicker or 1/f noise. However, in high-speed applications (a clock frequency of several megahertz), the white noise typically dominates. This is further enhanced by noise aliasing. If the 1/f noise becomes a problem there are several techniques, such as correlated double sampling (CDS) or chopper stabilization to get rid of it [40].

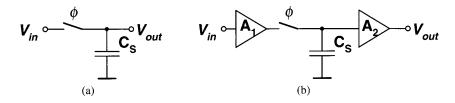

#### 4. Basic S/H Circuit Architectures

In hold mode an S/H circuit remembers the value of the input signal at the sampling moment, and thus it can be considered as an analog memory cell. The basic circuit elements that can be employed as a memory are capacitors and inductors, of which the capacitors store the signal as a voltage (or charge) and the inductors as a current. In addition to the inductor, a current memory needs a switch that is a good short circuit when it is closed. Similarly, a switch which is a good open circuit in its off-state is needed for a voltage memory. Since capacitors and switches with a high off-resistance are far easier to implement in a practical integrated circuit (IC) technology than inductors and switches with a very small on-resistance, all sample-and-hold circuits are based on voltage sampling. There also exists current mode S/H circuits, but they always include voltage-to-current and current-to-voltage converters which allow the sampled quantity to be voltage.

S/H circuit architectures can roughly be divided into open-loop and closed-loop architectures. The main difference between them is that in closed-loop architectures the capacitor, on which the voltage is sampled, is enclosed in a feedback loop, at least in hold mode.

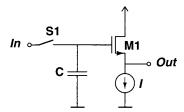

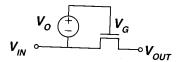

#### 4.1 Open-Loop Architectures

The simplest S/H circuit consists of a switch and a capacitor (Figure 3.7 (a)). In sample mode the switch is closed and the voltage on the capacitor tracks the input signal. During the transition to hold mode the switch is opened and the input voltage value at the switch opening moment stays on the capacitor. This circuit, however, is impractical since it is not capable of driving any load. Therefore a buffer has to be used to drive the load. An input buffer may also be needed to adjust the signal level to one suitable for the switch and to reduce hold mode feedthrough. An S/H circuit with an input and an output buffer is shown in Figure 3.7 (b).

The main advantage of this open-loop S/H architecture is its high speed. Accuracy, however, is limited by the harmonic distortion arising from the nonlinear gain of the buffer amplifiers and the signal-dependent charge injection from the switch. These problems are especially emphasized with a MOS technology.

Figure 3.7. A simple S/H circuit (a) and a practical S/H circuit (b).

Figure 3.8. A basic closed-loop S/H circuit.

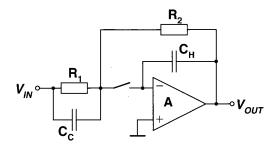

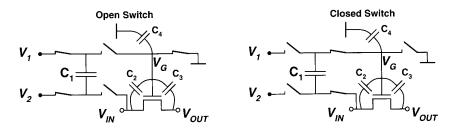

#### 4.2 Closed-Loop Architectures

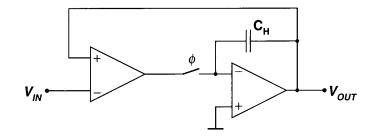

A well-known technique to improve linearity is the utilization of negative feedback. The feedback can be used internally in the buffer amplifiers in an open-loop architecture like the one in Figure 3.7 (b). However, this does not help with switch-induced distortion. The signal-dependent charge injection can be avoided by operating the switch at a constant potential, which can be realized by enclosing the switch in a feedback loop to create a virtual ground. Figure 3.8 shows a basic closed-loop S/H circuit following this idea [41, 42].

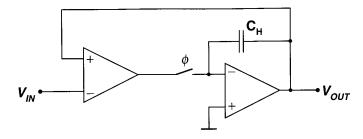

As a result of feedback the output tracks the input in sample mode. The switch is connected to the virtual ground provided by the second operational amplifier and thus it introduces only a constant error charge. When the switch is opened the global feedback loop is broken and the input voltage is sampled into the capacitor  $C_H$ . The capacitor is permanently connected in a feedback loop around the second operational amplifier, which is used as a buffer both in track mode and hold mode.

Since the feedback loop encloses two opamps in tracking mode the circuit has to be heavily compensated in order to avoid instability. This naturally reduces the speed of the circuit. Another potential disadvantage is hold mode feedthrough via the parasitic input capacitances of the first operational amplifier.

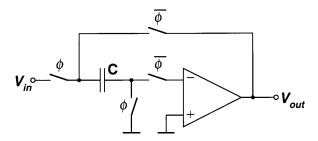

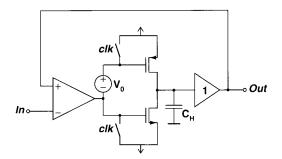

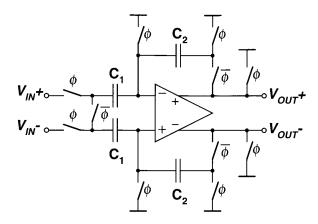

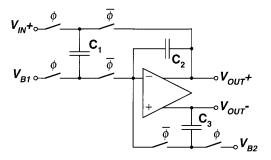

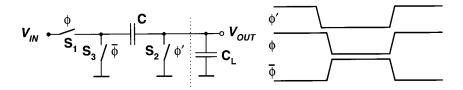

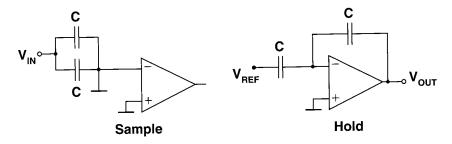

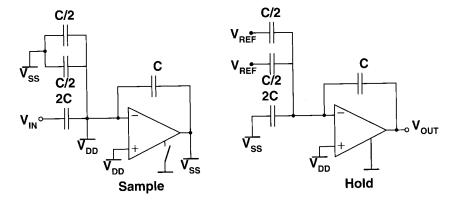

A closed-loop S/H architecture, commonly used in switched capacitor (SC) circuits and referred to as flip-around S/H, is shown in Figure 3.9. It performs

Figure 3.9. A switched capacitor S/H circuit.

the sampling passively, i.e. it is done without the opamp, which makes signal acquisition fast. In hold mode the sampling capacitor is disconnected from the input and put in a feedback loop around the opamp, as in the circuit shown in Figure 3.8. Signal-dependent charge injection from the switches is avoided by a technique called bottom plate sampling, which relies on special timing of the switch control signals. This technique is discussed in more detail in Chapter 6.

# Chapter 4

# A/D CONVERTERS

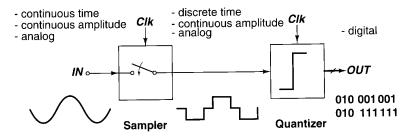

#### 1. A/D Conversion

Analog-to-digital (A/D) conversion can be separated into two distinct operations: sampling and quantization. Sampling transforms a continuous time signal into a corresponding discrete time signal, while quantization converts continuous amplitude distribution into a set of discrete levels, which can be expressed with digital code words. Figure 4.1 shows the principle of A/D conversion.

Some A/D converter (ADC) architectures, the flash for instance, can perform sampling and quantization simultaneously, and in some ADCs, which are targeted for DC signals, no sampling is needed at all. In high performance ADCs, however, sampling and quantization are usually separated to make it possible to optimize the circuitry for both tasks without compromises. Furthermore, the performance of many ADC architectures, which do not necessarily need a separate sampling circuit, can often be improved by adding one.

Figure 4.1. Principle of A/D conversion.

Figure 4.2. Piece-wise linear and nonlinear analog preamplification.

The sampling operation has already been discussed in Chapter 3 and the architectures of S/H circuits will be investigated in Chapter 5. In the remainder of this chapter the quantization operation is studied in more detail and the most common high-speed ADC architectures are introduced. There is also a bias is toward those architectures most suitable for CMOS technologies. Furthermore, the focus is on high-speed and medium- to high-resolution (8 bits or more) ADCs. Oversampling ADCs are not discussed.

#### 1.1 Direct Quantization

The most straightforward way to perform quantization is to compare the signal to a reference with a comparator. One comparison yields a one-bit result, telling whether the signal is larger or smaller than the reference. Thus, to get greater accuracy i.e. a larger number of bits, more comparisons are needed. For a single signal value, several successive comparisons can be made against different reference levels (successive approximation architecture), yielding at most as many bits as there are comparisons. Alternatively, with several parallel comparators the signal can be compared against many references at once (flash architecture), which gives a multibit result in one comparison phase. In the case of two-step flash these two methods are combined, requiring fewer comparators than flash ADC and being faster than successive approximation ADC.

In these architectures quantization accuracy is, to a large extent, determined by comparator accuracy. The larger their number and speed requirement are, the more difficult their realization at a reasonable cost in area and power becomes. As a result, architectures using analog signal preprocessing prior to quantization have been developed.

# 1.2 Quantization After Analog Preprocessing

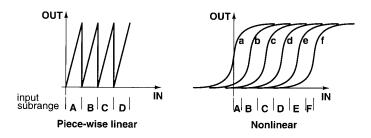

The preprocessor provides gain, which relaxes the comparator accuracy requirement. Since the signal range in ADCs is typically comparable to the supply voltage, a linear amplifier cannot provide significant gain. Thus, the

preprocessor either has a piece-wise linear transfer function (algorithmic and pipeline ADCs) or produces several shifted nonlinearly amplified signals, out of which one is selected automatically (flash with distributed preamplification) or depending on a coarse approximation of the signal (folding-and-interpolating ADC). The two different types of transfer functions are illustrated in Figure 4.2. The preprocessing can be realized in a continuous or discrete time domain.

Preprocessing also helps in reducing the number of comparators. This can be seen, for instance, from the piece-wise linear transfer function, which folds several incoming subranges into one output range, reducing the number of comparators in the final quantization by a factor equal to the number of folds. To prevent information loss, a coarse quantization has to be performed prior to or in parallel with the preprocessing to distinguish the correct input subrange. The accuracy requirement of the coarse quantization can be relaxed by using redundancy (overlapping subranges), and thus it does not affect the final quantization.

#### 1.3 ADC Figures of Merit

Some of the parameters used with ADCs are also found in the case of S/H circuits and hence have already been presented in the previous chapter. A more comprehensive presentation of ADC specifications than the one that follows can be found, for example, in [35].

The *sampling rate* tells how many samples the ADC can process in a time unit and the *latency* how many clock cycles there are between the sampling instant and the moment when the digital code is available at the ADC output.

The accuracy of the conversion is specified by its *resolution*, which is given in bits. Often, resolution is a synonym for the *number of output bits*, not all of which necessarily carry any valuable information. Thus, the real accuracy can be specified by an *effective number of bits (ENOB)*, which is just the *signal-to-noise-and-distortion ratio (SNDR)* expressed in bits.

Ideally, the SNDR is limited by the finite precision of the quantization, which leaves an error between the original non-quantized signal and the quantized signal. Often, this error is treated statistically and referred to as quantization noise as a consequence of its uniform amplitude distribution and virtually flat spectral density. Quantization noise limits the SNDR (with full-scale signal) to  $6.02 \cdot N + 1.76$  dB, where N is the resolution. In a practical ADC thermal noise, disturbing signals, and transfer function errors make the SNDR smaller. From this measured SNDR value the effective number of bits can be calculated:

$$ENOB = \frac{(SNDR - 1.76)}{6.02}. (4.1)$$

Figure 4.3. Errors in ADC transfer function.

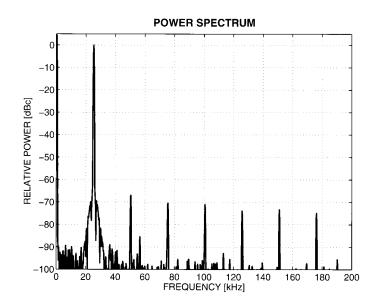

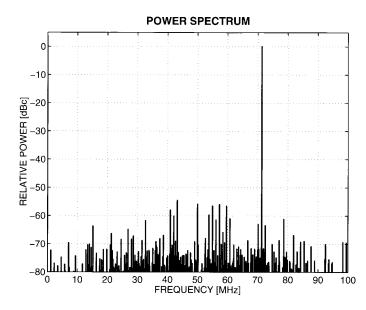

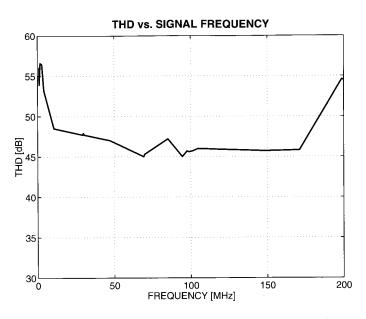

To gain more information about how the error energy is spectrally distributed, spurious free dynamic range (SFDR) and total harmonic distortion (THD) are often specified. Their definition is the same as with S/H circuits, and unless otherwise specified they are obtained with a full-scale input signal. The effective resolution bandwidth (ERB) is the input signal frequency, below which the ENOB is less than half a bit worse than its DC value.

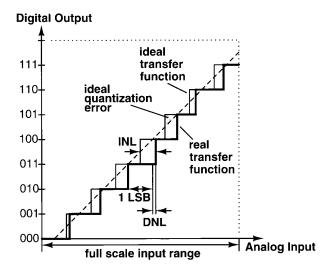

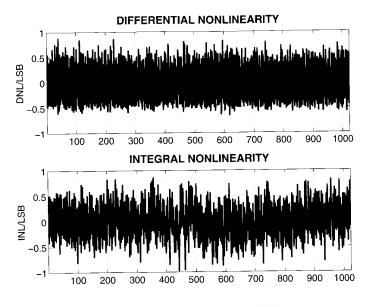

The full-scale signal range is expressed in volts. From it, the voltage step corresponding to the least significant bit (LSB) can be calculated:  $LSB = V_{FS}/2^N$ . The static errors in the transfer function are specified with differential non-linearity (DNL) and integral non-linearity (INL), both of which are referenced to the LSB. They can be either presented graphically as a function of the output code, or only the maximum value, which is a single number, can be given. The DNL is the error in the step size between two adjacent quantization levels, which is ideally 1 LSB. The INL is the cumulative DNL, and it is equal to the deviation from a straight line drawn between the end points of the transfer function. The DNL and INL are illustrated in Figure 4.3. In addition to these the ADC may also contain offset and gain error, which are not shown in the figure.

#### 2. Flash ADC

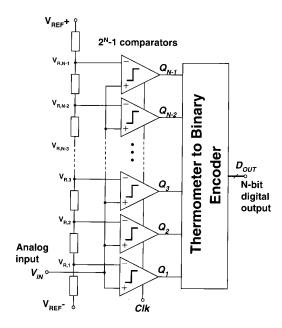

Flash ADC, which is the fastest and one of the simplest ADC architectures, is shown in Figure 4.4. It performs  $2^N$  -level quantization with  $2^N - 1$  comparators. The reference voltages for the comparators are generated using a resistor

Figure 4.4. N-bit flash ADC.

ladder, which is connected between the positive  $(V_{REF}+)$  and the negative  $(V_{REF}-)$  reference voltage determining the full-scale signal range. Together the comparator outputs form a  $2^N-1$ -bit code, where all the bits below the comparator whose reference is the first to exceed the signal value are ones, while the bits above are all zeros. This so-called thermometer code is converted to N-bit binary word with a logic circuit, which can also contain functions for removing bit errors (bubbles).

Since the input signal is directly connected to the inputs of the comparators, flash architecture is very fast; the speed is only limited by the comparators. Thus, the fastest reported ADCs are realized with this architecture. Flash ADC also has very low latency—typically one to two clock cycles—which allows it to be utilized in applications using feedback (e.g. gain control loop).

The most prominent drawback of flash ADC is the fact that the number of comparators grows exponentially with the number of bits. Increasing the quantity of the comparators also increases the area of the circuit, as well as the power consumption. Thus, very high resolution flash ADCs are not practical; typical resolutions are seven bits or below.

Other issues limiting the resolution and speed include nonlinear input capacitance, location-dependent reference node time constants, incoherent timing of comparators laid out over a large area, and comparator offsets. To man-

age the offsets the utilization of auto-zeroing comparators is often necessary. Alternatively, the offsets and input capacitance can be reduced by means of distributed preamplification combined with averaging [43, 44], and possibly also with interpolation [45], which can both be considered as exponents of the signal preprocessing discussed in the previous section.

In averaging each comparator is preceded by a preamplifier, whose output is coupled to the outputs of the adjacent preamplifiers via a resistive averaging network. As a result, the input signal for a comparator is not produced by its own preamplifier alone, but it is a weighted average of the outputs of the preamplifiers in a small neighborhood. Comparator offset is reduced by the preamplifier gain and the preamplifier offset is an average of the random offsets of all the amplifiers participating in the amplification.

Not every comparator needs to have a preamplifier of its own; instead, some (typically every other or three out of four) amplifiers can be eliminated and the missing signals generated by means of interpolation. Neither averaging nor interpolation reduces the number of the comparators, and thus it does not significantly extend flash architecture toward higher resolutions.

Recently, the main application of flash ADCs has been in disk drive read channel circuits and local area network interfaces. Typically, six-bit resolution with a sampling rate of several hundred megahertz is required. Even gigahertz rates seem to be within the reach of state-of-the-art CMOS technologies [46, 47].

#### 3. Subranging ADC

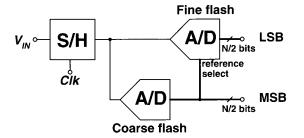

One way to reduce the number of comparators in flash ADC is to perform the quantization in two phases [48]. First a coarse quantization determines the subrange where the signal lies and then, in the second phase, the quantization is performed inside this range. Consequently, the number of comparators can be reduced from  $2^N-1$  to  $2\cdot \left(2^{N/2}-1\right)$ , assuming that the number of bits determined in each phase is the same. In an 8-bit ADC this means 30 comparators instead of 255. This type of architecture is known as either two-step flash or subranging architecture.

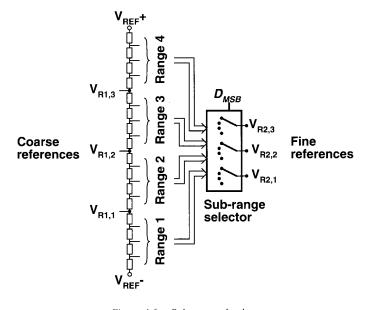

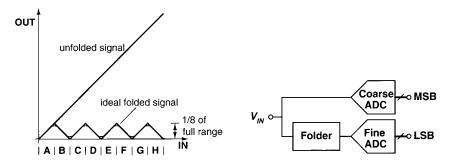

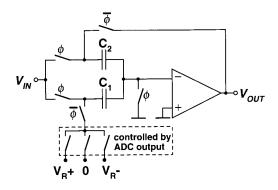

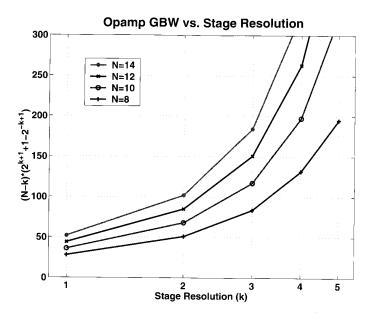

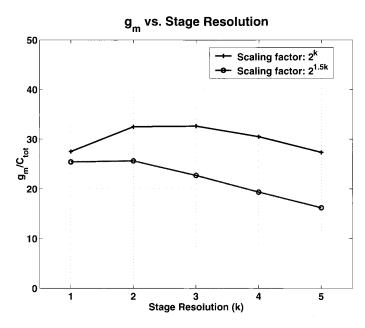

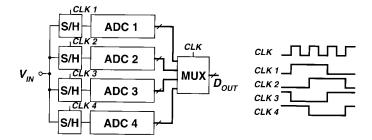

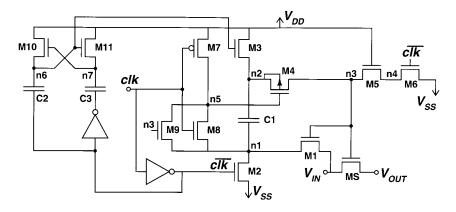

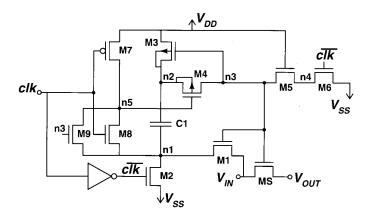

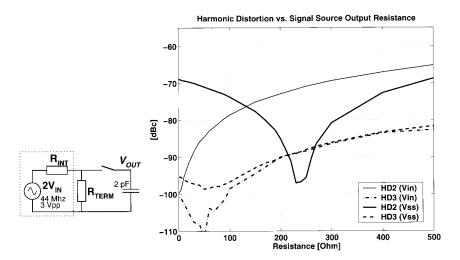

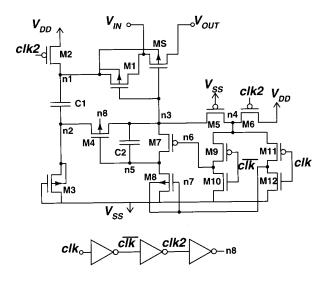

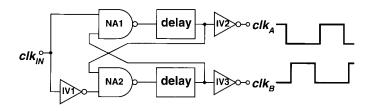

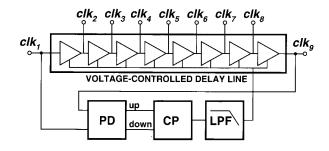

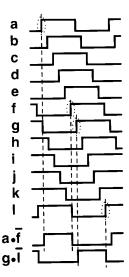

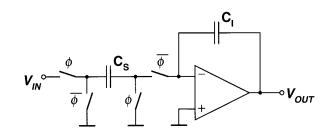

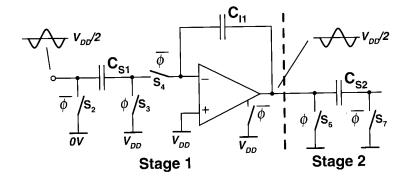

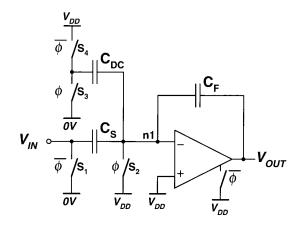

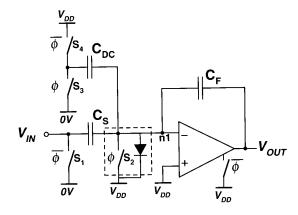

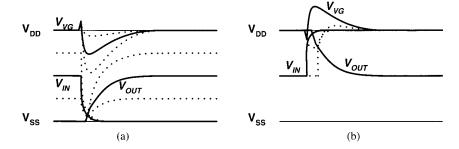

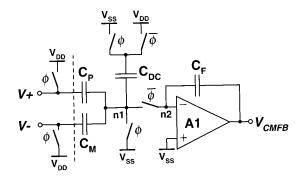

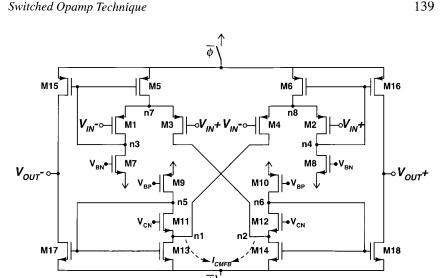

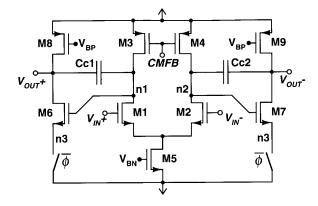

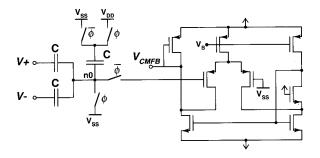

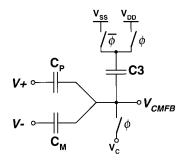

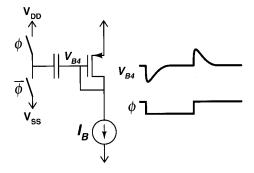

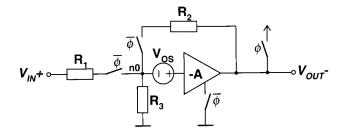

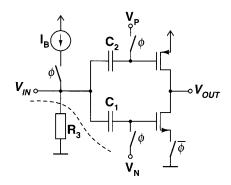

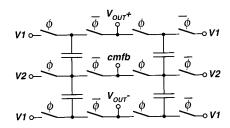

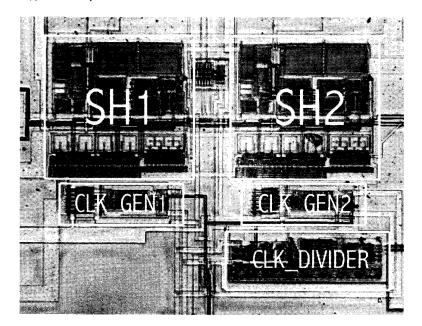

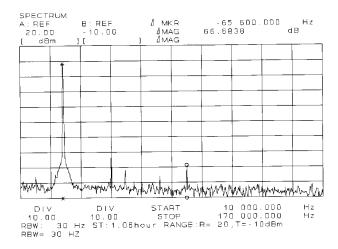

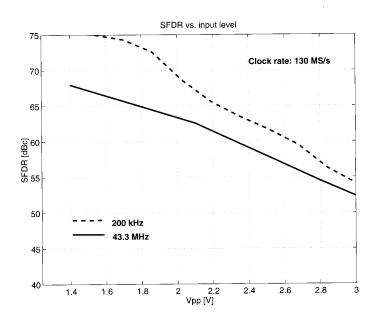

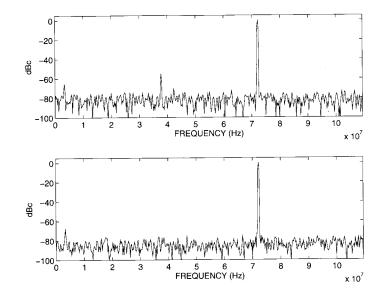

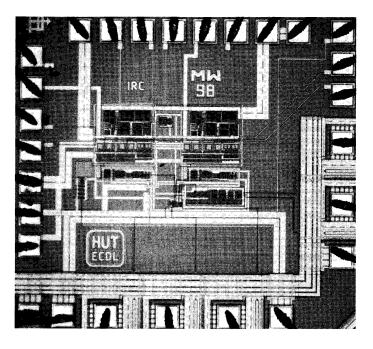

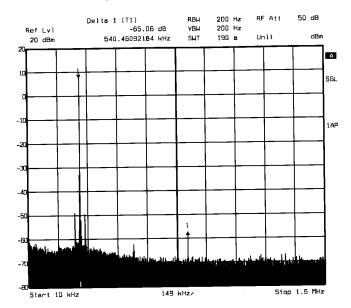

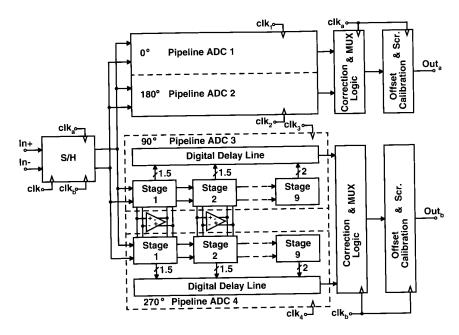

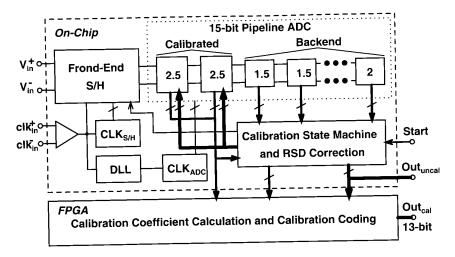

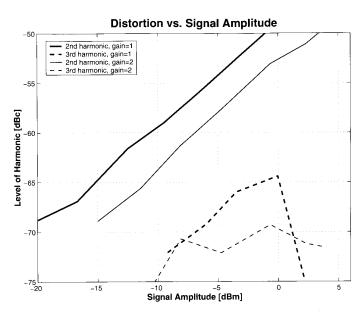

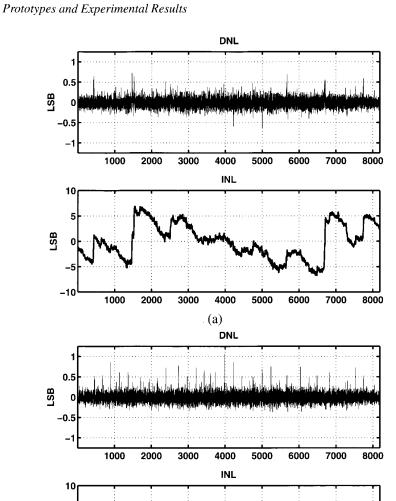

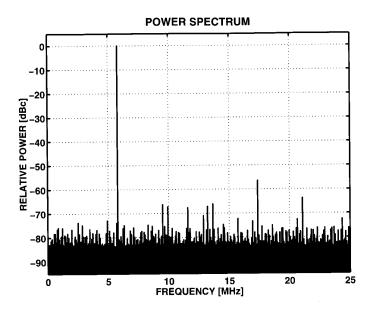

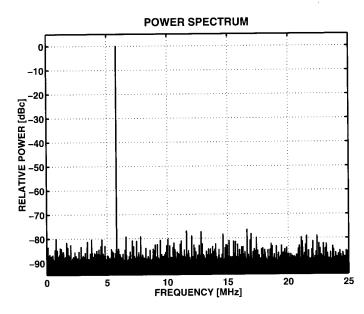

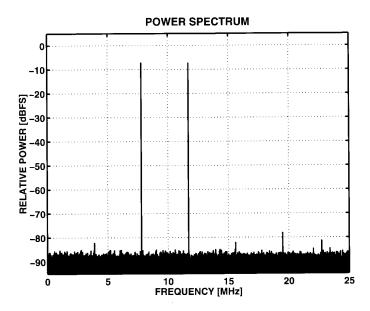

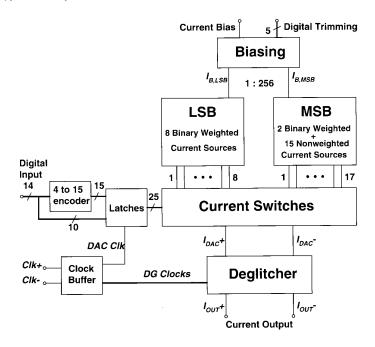

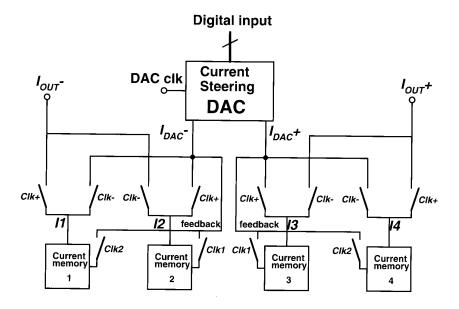

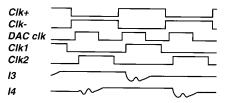

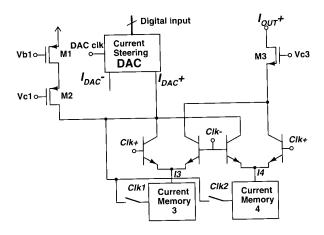

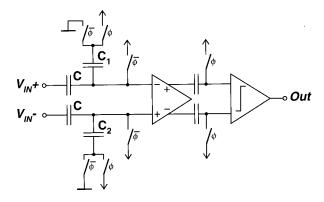

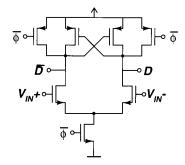

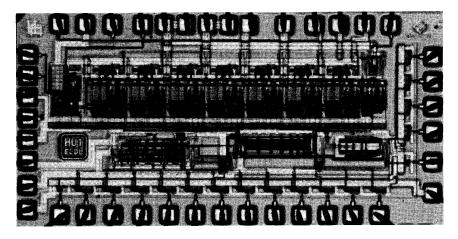

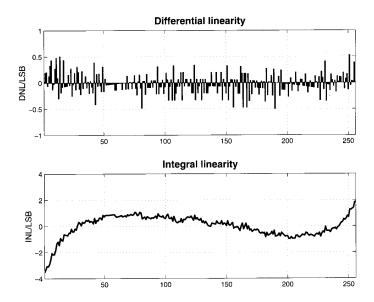

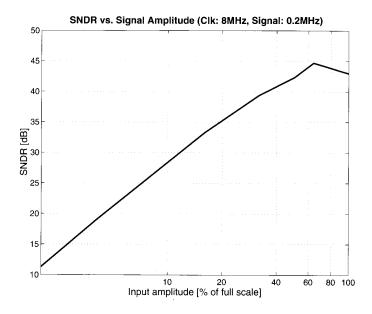

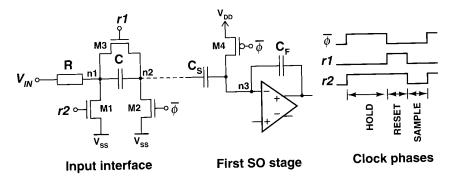

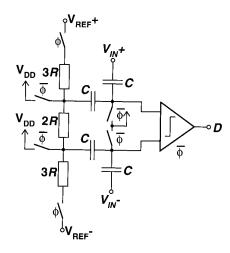

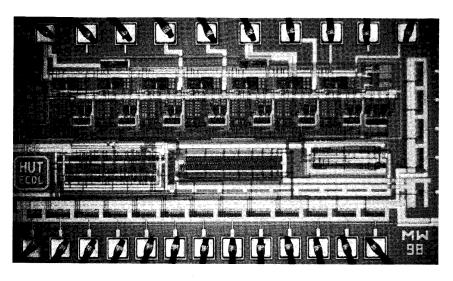

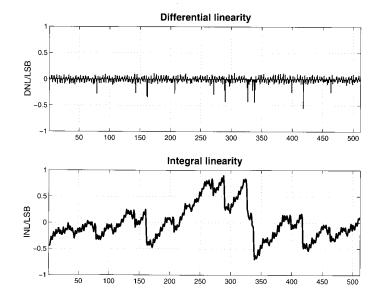

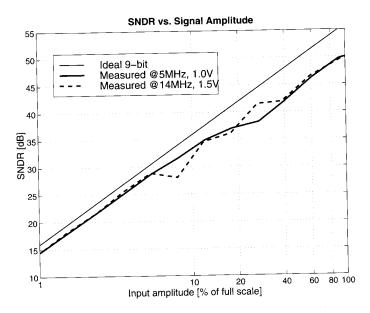

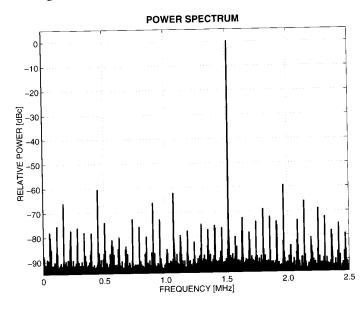

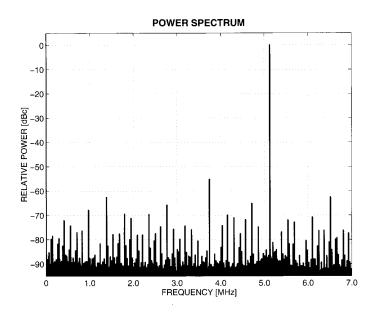

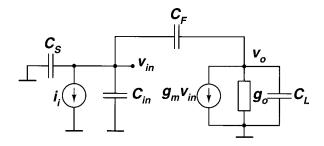

A block diagram of a subranging ADC is shown in Figure 4.5. There, the input signal is first sampled with a sample-and-hold circuit, which guarantees that both of the flashes have the same input signal. The first flash resolves the most significant bits (MSBs), which are also utilized for determining the coarse input range, according to which the reference voltages for the second flash are selected. A principal implementation of this selection, employing a common resistor ladder for both stages, is shown in Figure 4.6. For example, when the coarse A/D conversion tells us that the signal is between the first stage reference voltages  $V_{R1,2}$  and  $V_{R1,3}$ , the taps in range 3 are used as fine references.