Lecture Notes in Electrical Engineering 350

Vinod Pangracious Zied Marrakchi Habib Mehrez

# Three-Dimensional Design Methodologies for Tree-based FPGA Architecture

### Lecture Notes in Electrical Engineering

#### Volume 350

#### **Board of Series editors**

Leopoldo Angrisani, Napoli, Italy Marco Arteaga, Coyoacán, México Samarjit Chakraborty, München, Germany Jiming Chen, Hangzhou, P.R. China Tan Kay Chen, Singapore, Singapore Rüdiger Dillmann, Karlsruhe, Germany Haibin Duan, Beijing, China Gianluigi Ferrari, Parma, Italy Manuel Ferre, Madrid, Spain Sandra Hirche, München, Germany Faryar Jabbari, Irvine, USA Janusz Kacprzyk, Warsaw, Poland Alaa Khamis, New Cairo City, Egypt Torsten Kroeger, Stanford, USA Tan Cher Ming, Singapore, Singapore Wolfgang Minker, Ulm, Germany Pradeep Misra, Dayton, USA Sebastian Möller, Berlin, Germany Subhas Mukhopadyay, Palmerston, New Zealand Cun-Zheng Ning, Tempe, USA Toyoaki Nishida, Sakyo-ku, Japan Bijaya Ketan Panigrahi, New Delhi, India Federica Pascucci, Roma, Italy Tariq Samad, Minneapolis, USA Gan Woon Seng, Nanyang Avenue, Singapore Germano Veiga, Porto, Portugal Haitao Wu, Beijing, China Junjie James Zhang, Charlotte, USA

#### About this Series

"Lecture Notes in Electrical Engineering (LNEE)" is a book series which reports the latest research and developments in Electrical Engineering, namely:

- Communication, Networks, and Information Theory

- Computer Engineering

- Signal, Image, Speech and Information Processing

- Circuits and Systems

- Bioengineering

LNEE publishes authored monographs and contributed volumes which present cutting edge research information as well as new perspectives on classical fields, while maintaining Springer's high standards of academic excellence. Also considered for publication are lecture materials, proceedings, and other related materials of exceptionally high quality and interest. The subject matter should be original and timely, reporting the latest research and developments in all areas of electrical engineering.

The audience for the books in LNEE consists of advanced level students, researchers, and industry professionals working at the forefront of their fields. Much like Springer's other Lecture Notes series, LNEE will be distributed through Springer's print and electronic publishing channels.

More information about this series at http://www.springer.com/series/7818

Vinod Pangracious · Zied Marrakchi Habib Mehrez

## Three-Dimensional Design Methodologies for Tree-based FPGA Architecture

Vinod Pangracious Electrical and Computer Engineering Department, School of Engineering American University in Dubai Dubai United Arab Emirates

Zied Marrakchi Flexras Technologies Biocitech Romainville France Habib Mehrez University of Pierre and Marie Curie, Paris VI Paris France

ISSN 1876-1100 ISSN 1876-1119 (electronic) Lecture Notes in Electrical Engineering ISBN 978-3-319-19173-7 ISBN 978-3-319-19174-4 (eBook) DOI 10.1007/978-3-319-19174-4

Library of Congress Control Number: 2015941877

Springer Cham Heidelberg New York Dordrecht London © Springer International Publishing Switzerland 2015

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made.

Printed on acid-free paper

Springer International Publishing AG Switzerland is part of Springer Science+Business Media (www.springer.com)

To my wife Juliet Vinod, and my kids Liz, Lia and Yehoshua

## Preface

Three-dimensional integrated circuits (3D-ICs) design has become a major driving force in the modern VLSI design and manufacturing technology. It provides the best platform for design and manufacturing of high density and high performance chips and the field is continuing to grow at an amazing pace. The idea to write this book on 3D FPGAs using 3D technology originated from the research and experimental work done during my doctoral studies at University of Pierre and Marie Curie under the guidance of Professor Habib Mehrez. This book was written as a text that covers the foundations of 3D integrated circuits and high performance 3D reconfigurable FPGA architecture design. It was written for use in a core and elective course at the graduate level in field of Electrical Engineering, Computer Engineering, and doctoral research programs. Today, many universities upgrade their curriculum to include modern VLSI design methodologies and re-configurable system design. No previous background on 3D integration is required, nevertheless, fundamental understanding of 2D CMOS VLSI design is required. It is assumed that the reader has taken the core curriculum in Electrical Engineering or Computer Engineering, with courses like CMOS VLSI design, Digital System Design and Microelectronics Circuits being the most important. It is accessible for self-study by both senior students and professionals alike.

#### Scope and Coverage

A brief introduction and the concept of 3D integration is presented in Chap. 1. It begins with brief review of advanced VLSI design and technology scaling; Chap. 1 continues to establish the basic and fundamental needs of introducing threedimensional integrated circuits design into the modern VLSI technology. It also stress the needs for new and augmented 3D CAD tools to support designs such as, the *design for 3D*, to manufacture high performance 3D integrated systems and reconfigurable architecture. Three-dimensional (3D) integration is an emerging technology that is expected to lead to an industry paradigm shift due to its tremendous advantages over 2D integration in terms of density and performance. Academic and industrial research institutes around the world currently focus on technology innovations, simulation and design and product prototypes. Anticipated applications start with memory, portable device and high-performance computers, reconfigurable system design and extend to high-density multifunctional heterogeneous integration of infotech-nanotech-biotech systems. Chapter 2 focuss on the fundamentals and in-depth analysis of different 3D integration methodologies and design. This chapter also talks about potential benefits of 3D integration that can vary depending on approach; they include multi-functionality, increased performance, reduced power, small form factor, reduced packaging, increased yield and reliability, flexible heterogeneous integration and reduced overall costs.

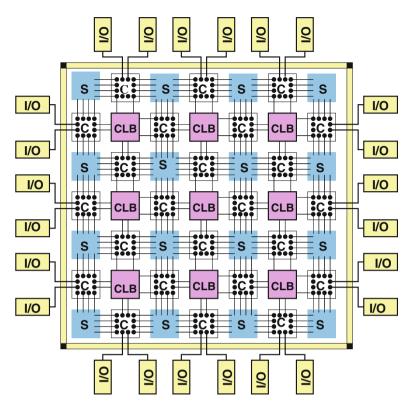

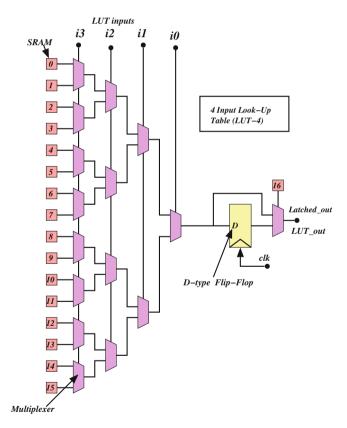

Today, FPGAs (Field Programmable Gate Arrays) have become important actors in the computational devices domain that was originally dominated by microprocessors and ASICs. The main challenge in 2D FPGA design is to find a good tradeoff between flexibility and performances. Three factors combine to determine the characteristics of an FPGA: quality of its architecture, quality of the CAD tools used to map circuits into the FPGA and its electrical technology design. A first look at the FPGA hardware is provided in Chap. 3. The chapter provides in-depth analysis of programmable logic components and interconnection blocks in FPGA design and how they are interconnected to function as a generic reconfigurable system. This chapter establishes the basic understanding that FPGAs are semiconductor devices and contain programmable logic components connected by a regular, hierarchical programmable interconnect system. The distinguishing characteristic of FPGAs is their on-field programmability, which allows the logic functionality of an FPGA to be re-programmed even after the manufacturing process. FPGAs are used for rapid prototyping of digital circuits. The design and test of digital systems are very time-efficient and cost-effective with FPGAs. It also discusses about the logic components in the FPGA, mostly consists of memory elements such as registers or even complete blocks of memory that can be configured to hold any desired state. As we know, FPGAs were used mostly for prototyping and emulation systems in the design process of digital system design and ASICs. However, recently, FPGAs have become popular for a variety of mainstream products in networking, telecommunication, digital signal processing and in consumer electronics. FPGAs can be classified based on the technology using to program it.

FPGA architectures have been intensely investigated over the past two decades. A major aspect of FPGA architecture research is the development of Computer Aided Design (CAD) tools for design and implementation of fast and high density FPGAs and mapping applications to it. It is well established that the quality of an FPGA-based implementation is largely determined by the effectiveness of accompanying suite of CAD tools. Benefits of an otherwise well-designed, feature-rich FPGA architecture might be impaired if the CAD tools cannot take advantage of the features that the modern FPGA design provides. Thus, CAD algorithm research is essential to the necessary architectural advancement to narrow the performance between **FPGAs** and other computational devices gaps like ASICs.

Two-dimensional CAD flow of mesh-based and tree-based FPGA architectures are described and analyzed in Chap. 4. This chapter provides a perfect starting point for FPGA designs to evaluate and understand the algorithms and data-structures used in designing the software for FPGA placement and routing.

Chapter 5 provides the study of the existing variants of 2D tree-based FPGA architecture and the impact of 3D migration on its topology. We have seen numerous studies showing the characteristics of tree-based interconnect networks. how they scale in terms of area and performance and empirically how they relate to particular designs. Nevertheless, we have not had any breakthrough in optimizing these network topologies to exploit the advantages in area and power consumption and neither know how to deal with the larger wire-length issues that impede performance of tree-based FPGA architecture. Through the course of this book, we try to make the readers understand that, it is nearly impossible to optimize the area and speed, unless we break the very backbone of the tree-based interconnect network and resurrect again by using 3D technology. The 3D-ICs can alleviate interconnect delay issues by offering flexibility in system design, placement and routing. A new set of 3D FPGA architecture exploration tools and technologies developed to validate the advance in performance and area. Modern FPGAs have become a viable alternative to cell-based design technology by providing reconfigurable computing platforms with improved performance and higher density. While the reconfigurability provides flexibility, two-dimensional FPGAs also lead to area and performance overhead in comparison to cell-based custom integrated circuits (ICs). Thus, to combine the advantages of both FPGAs and custom ICs, modern FPGAs have emerged as an attractive solution for system-on-chip implementations. Modern FPGAs include design components such as digital signal processors, on chip memory blocks, multipliers, adders and entire processors. In Chap. 6 our primary focus is on validation of architecture exploration and optimization methodologies of 3D homogeneous and heterogeneous tree-based and mesh-based FPGAs.

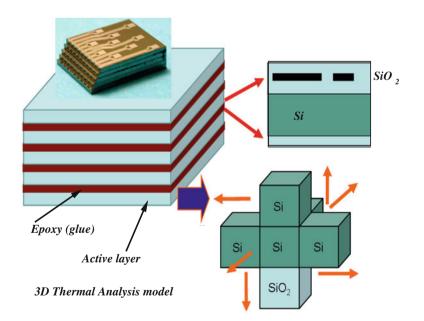

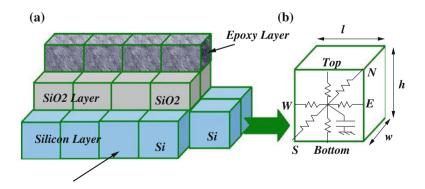

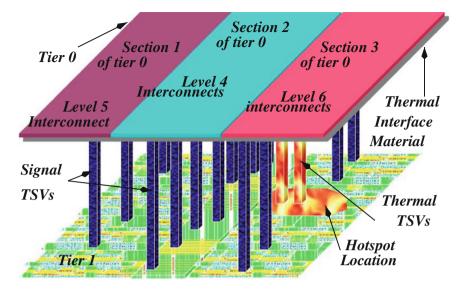

A 3D-IC system consists of disparate materials with considerably different thermal properties including semiconductor, metal, dielectric and possibly polymer layers used for inter-plane bonding. Although the power consumption of these circuits is expected to decrease due to the considerably shorter interconnects, the power density increases since there is a greater number of devices per unit volume compared to a 2D circuit. As the power density increases, the temperature of the planes non-adjacent to the heat sink of the package can rise, resulting in degraded performance or thermal gradients that can accelerate wear out mechanisms. Design methodologies at various stages of the IC design flow, such as synthesis, floorplanning, placement and routing, which maintain the temperature of a circuit within specified limits or alleviate thermal gradients among the planes of the 3D circuit, are therefore necessary. Two key elements are required to establish a successful 3D thermal management strategy: a 3D thermal model, to characterize the thermal behaviour of a circuit and design techniques that alleviate thermal gradients among the physical planes of a 3D-IC system, while maintaining the operating temperature within acceptable levels. The primary requirements of a thermal model are high accuracy, low complexity and reasonably fast, while thermal design techniques should produce high-quality circuits without incurring long computational design time. To reduce the complexity of the modelling process, standard methods to analyse heat transfer, such as finite difference, finite element and boundary element methods, have been adopted to evaluate the temperature of a 3D circuit. Simpler analytic expressions have also been developed to characterize the temperature within a 3D system. The discussion culminates in Chap. 7 where design and implementation three-dimensional thermal model and thermal design techniques to improve the thermal profile and 3D-IC system and Chap. 7 focus its attention more on thermal analysis of 3D FPGAs.

Design techniques for three-dimensional (3D) ICs considerably lag the significant strides achieved in 3D manufacturing technologies. Advanced design methodologies for two-dimensional (2D) circuits are not sufficient to manage the added complexity caused by the third dimension. Consequently, design methodologies that efficiently handle the added complexity and inherent heterogeneity of 3D circuits are necessary. These 3D design methodologies should support robust and reliable 3D circuits while considering different forms of vertical integration, such as system-in-package and 3D-ICs with fine grain vertical interconnections. Global signalling issues, such as clock and power distribution networks, are further exacerbated in vertical integration due to the limited number of package pins, the distance of these pins from other planes within the 3D system and the impedance characteristics of the through silicon vias (TSVs). In addition to these dedicated networks, global signalling techniques that incorporate the diverse traits of complex 3D systems are required. One possible approach, potentially significantly reducing the complexity of interconnect issues in 3D circuits, is by optimizing the number of vertical interconnects (TSVs). Design methodologies that exploit the diversity of 3D structures to further enhance the performance of multi-plane integrated systems are necessary. Chapter 8 introduce new 3D physical design methodology and verification tools developed. This chapter also discuss the development of 3D physical design methodology and tools using existing 2D CAD tools for the implementation of 3D tree-based FPGA demonstrator. During the course of design process, we addressed many specific issues that 3D designers will encounter dealing with tools that are not specifically designed to meet their needs. In contrast, the thermal performance is expected to worsen with the use of 3D integration. In this Chapter, we examined precisely how thermal behaviour scales in 3D integration and determine how the temperature can be controlled using thermal design techniques.

A concreted effort has been made to present three-dimensional integration and high performance tree-based FPGA design using newly developed 3D physical design tools and VLSI design methodologies. Three-dimensional integration is an interdisciplinary field that relies on many experts working together at every design level. Emphasis is placed on illustrating the interaction among the different field. For example, 3D thermalware physical design described in Chap. 7 is a classic case Preface

of thermal, mechanical and electrical engineers working together to develop high performance three-dimensional integrated circuits. Few emerging research areas and possible future lines of research and applications of 3D-IC described in Chap. 9.

Dubai, United Arab Emirates March 2015 Vinod Pangracious

## Acknowledgments

I would like to thank all members of the Electrical and Computer Engineering Department at American University in Dubai and Laboratoire d'Informatique de Paris 6 (LIP6) at University of Pierre et Marie Curie Paris VI, for their continued support in writing this book.

## Contents

| 1 | An ( | <b>Dverview of Three-Dimensional Integration and FPGAs</b> |  |

|---|------|------------------------------------------------------------|--|

|   | 1.1  | Introduction                                               |  |

|   |      | 1.1.1 More Moore (MM)                                      |  |

|   |      | 1.1.2 More Than Moore (MtM)                                |  |

|   | 1.2  | Technological Initiatives and Contribution                 |  |

|   |      | 1.2.1 Modified Tree-Based Interconnect                     |  |

|   |      | 1.2.2 Tree-Based Interconnect Partitioning                 |  |

|   |      | 1.2.3 3D FPGA Design and Implementation Methodology        |  |

|   |      | 1.2.4 Unified Mesh of Tree Architecture                    |  |

|   | 1.3  | Book Organization                                          |  |

|   | Refe | rences                                                     |  |

|   |      |                                                            |  |

| 2 | Thre | e-Dimensional Integration: A More Than Moore               |  |

|   | Tech | nology                                                     |  |

|   | 2.1  | Introduction                                               |  |

|   |      | 2.1.1 Opportunities for Three-Dimensional Integration      |  |

|   | 2.2  | Historical Evolution of 3D System Integration              |  |

|   | 2.3  | Vertical Interconnect Technology Development (TSV)         |  |

|   | 2.4  | 3D Integration: Manufacturing Methods                      |  |

|   | 2.5  | Challenges in 3D Physical Design                           |  |

|   |      | 2.5.1 Complexity of 3D Physical Design Tools               |  |

|   |      | and Their Limitations                                      |  |

|   |      | 2.5.2 TSV and Thermal Management                           |  |

|   |      | 2.5.3 Power and Clock Delivery in 3D-ICs                   |  |

|   |      | 2.5.4 TSV-Induced Design for Manufacturability Issues      |  |

|   |      | 2.5.5 Floorplanning for 3D Circuits                        |  |

|   |      | 2.5.6 Placement for 3D Circuits                            |  |

|   |      | 2.5.7 Routing for 3D Circuits                              |  |

|   | 2.6  | 3D-IC Design Verification.                                 |  |

|   | 2.7  | Summary.                                                   |  |

|   | Refe | rences                                                     |  |

| 3 | Field     | Programmable Gate Arrays: An Overview                      |

|---|-----------|------------------------------------------------------------|

|   | 3.1       | Introduction                                               |

|   | 3.2       | Introduction to FPGA Architectures 44                      |

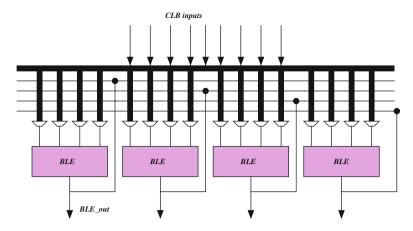

|   |           | 3.2.1 Configurable Logic Blocks 45                         |

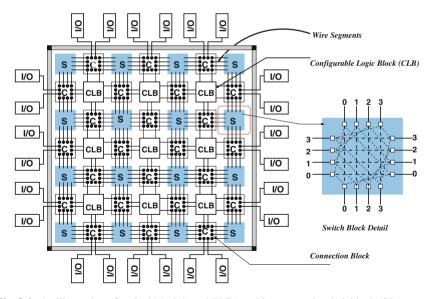

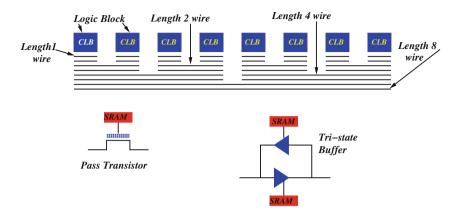

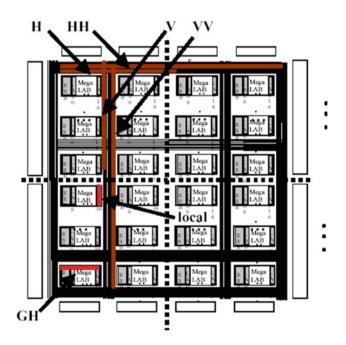

|   | 3.3       | FPGA Interconnect Topologies.48                            |

|   |           | 3.3.1 Mesh-Based Interconnect Network                      |

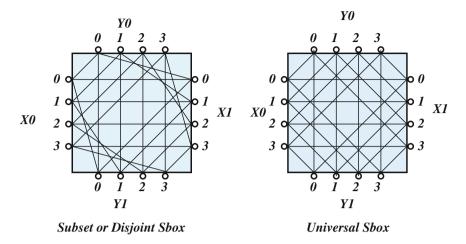

|   |           | 3.3.2 FPGA Switch Block 49                                 |

|   |           | 3.3.3 FPGA Routing Channels 51                             |

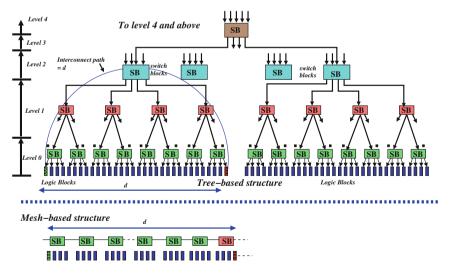

|   |           | 3.3.4 Multilevel Hierarchical Interconnect                 |

|   | 3.4       | Proposed FPGA Interconnect Architectures                   |

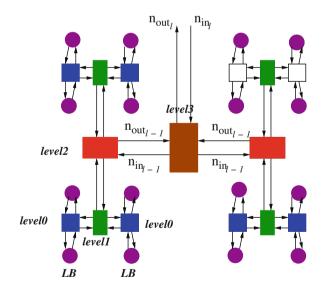

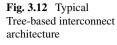

|   |           | 3.4.1 Evolution of Tree-Based Interconnect Architecture 56 |

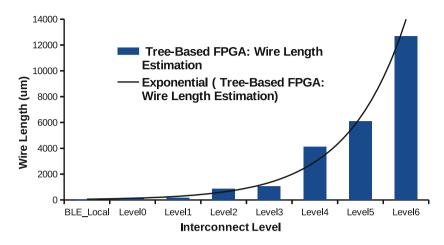

|   |           | 3.4.2 Wire Growth Model                                    |

|   |           | 3.4.3 Switch Growth Model                                  |

|   | 3.5       | Tree-Based Routing Interconnect 59                         |

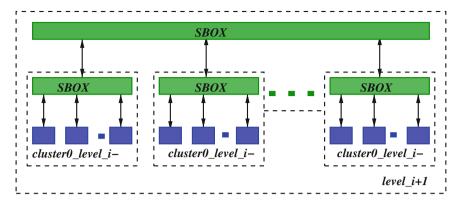

|   |           | 3.5.1 Tree-Based FPGA Architecture                         |

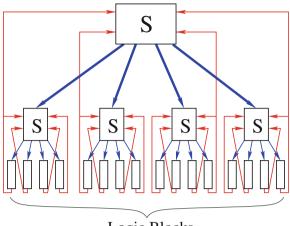

|   | 3.6       | Unified Mesh- and Tree-Based Interconnect 63               |

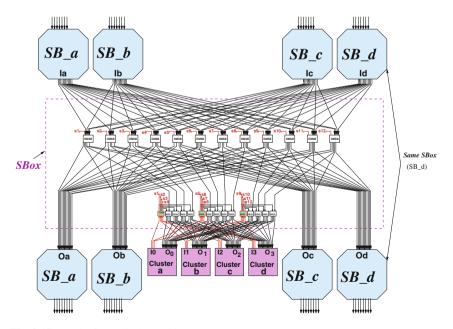

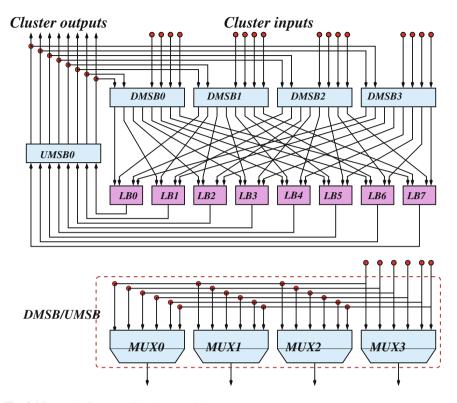

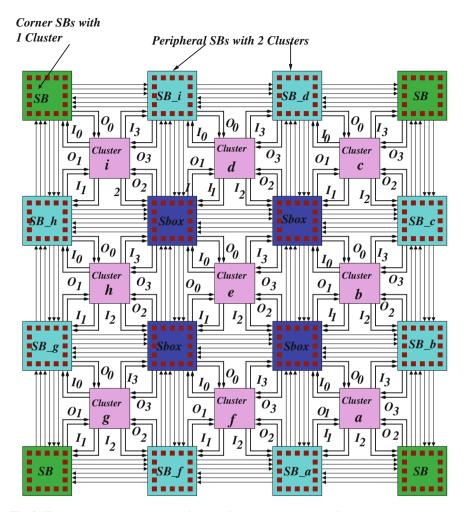

|   |           | 3.6.1 Cluster Local Interconnect                           |

|   |           | 3.6.2 Mesh-Based Routing Interconnect                      |

|   |           | 3.6.3 Input and Output Pads Connection                     |

|   | 3.7       | Summary                                                    |

|   | Refer     | ences                                                      |

|   |           |                                                            |

| 4 |           | Dimensional FPGAs: Configuration and CAD Flow         73   |

|   | 4.1       | Introduction                                               |

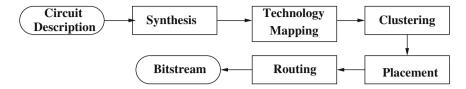

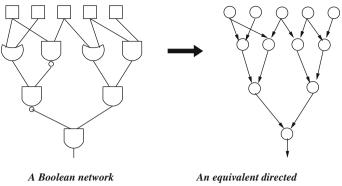

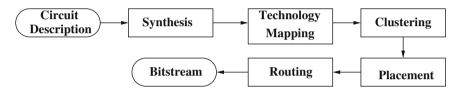

|   | 4.2       | Circuit Synthesis                                          |

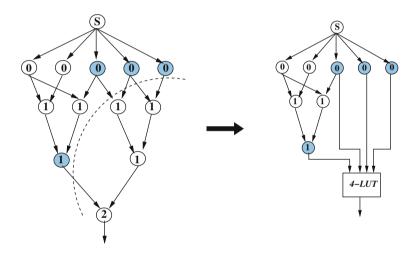

|   | 4.3       | Technology Mapping 74                                      |

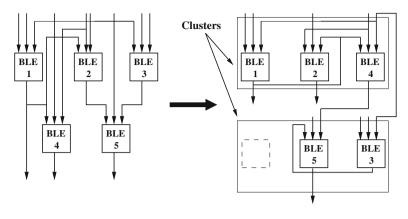

|   | 4.4       | Clustering                                                 |

|   |           | 4.4.1 Bottom-Up Approaches                                 |

|   |           | 4.4.2 Top-Down Approaches                                  |

|   | 4.5       | Placement         82                                       |

|   |           | 4.5.1 Simulated Annealing Based Approach 83                |

|   |           | 4.5.2 Partitioning Based Approach 84                       |

|   | 4.6       | Routing                                                    |

|   | 4.7       | Two-Dimensional CAD for Tree-Based Architecture            |

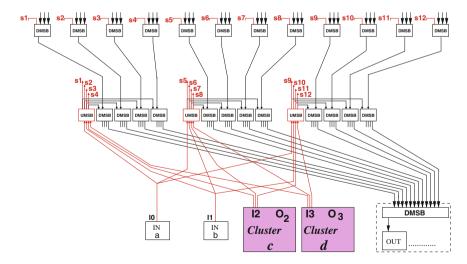

|   |           | 4.7.1 Synthesis and Mapping                                |

|   |           | 4.7.2 Clustering and Partitioning 88                       |

|   | 4.8       | Timing Analysis92                                          |

|   | 4.9       | Summary                                                    |

|   | Refer     | ences                                                      |

| 5 | <b>Th</b> | o Dimonsional EDCA as Configuration                        |

| 5 |           | e-Dimensional FPGAs: Configuration                         |

|   |           | CAD Development                                            |

|   | 5.1       | Introduction                                               |

|   | 5.2   | 3D FPGA Architectures: An Overview                      | 96  |

|---|-------|---------------------------------------------------------|-----|

|   |       | 5.2.1 FPGA Die Stacking                                 | 96  |

|   |       | 5.2.2 Monolithic FPGA Implementation                    | 98  |

|   | 5.3   | State-of-the-Art: 3D FPGA Implementation                | 99  |

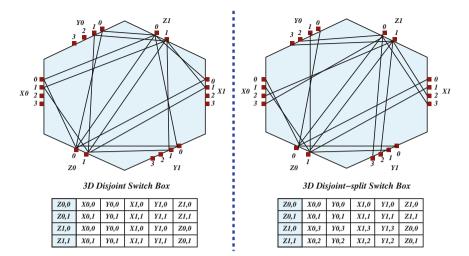

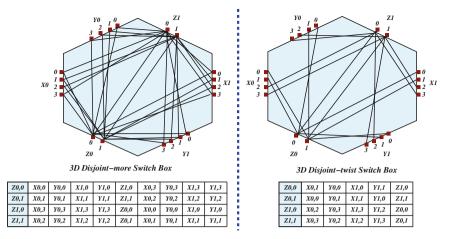

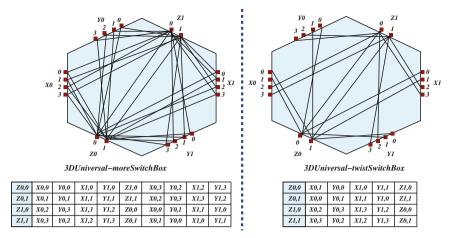

|   | 5.4   | 3D FPGA Interconnect Switch                             | 104 |

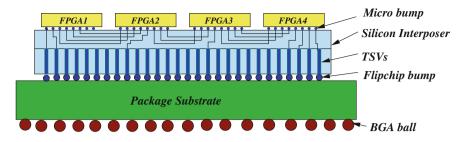

|   | 5.5   | 2.5D Integration: High Density Multi-FPGAs.             | 107 |

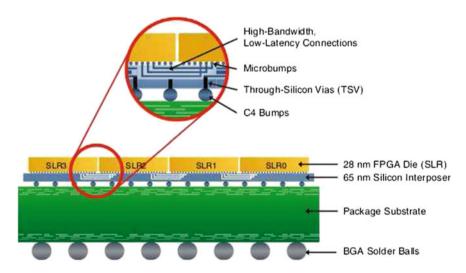

|   |       | 5.5.1 Industrial 2.5D Virtex-7 Interposer-Based FPGAs   | 109 |

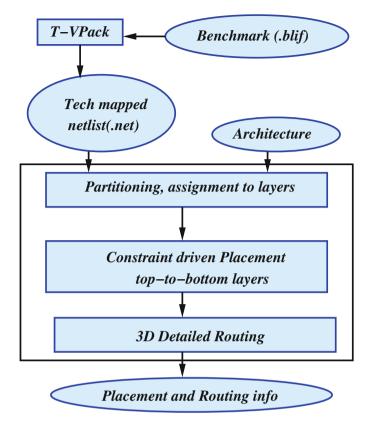

|   | 5.6   | Development of 3D Tree-Based FPGA CAD Tools             | 111 |

|   |       | 5.6.1 3D FPGA Physical Design Tools                     | 111 |

|   |       | 5.6.2 3D FPGA Architecture Exploration and Optimization | 113 |

|   | 5.7   | Summary                                                 | 114 |

|   | Refer | ences                                                   | 114 |

| 6 | Thre  | e-Dimensional Tree-Based FPGA: Architecture             |     |

|   | Expl  | oration Tools and Technologies                          | 117 |

|   | 6.1   | Introduction                                            | 117 |

|   | 6.2   | Tree-Based FPGA Interconnect Architecture               | 118 |

|   |       | 6.2.1 2D Tree-Based Interconnect: A Comparison          |     |

|   |       | with 2D Mesh-Based Interconnect                         | 119 |

|   | 6.3   | Tree-Based Interconnect Partitioning                    | 121 |

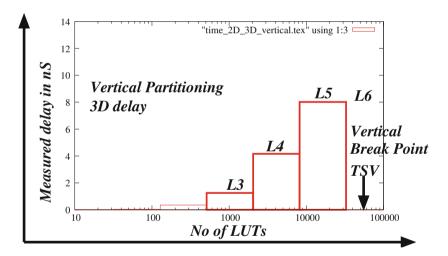

|   |       | 6.3.1 Vertical Partitioning                             | 122 |

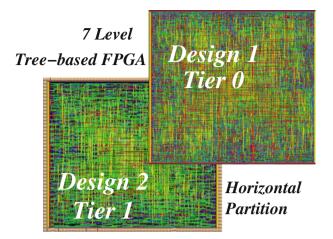

|   |       | 6.3.2 Horizontal Partitioning                           | 123 |

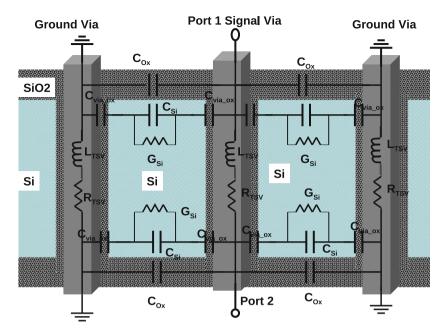

|   |       | 6.3.3 Through Silicon via (TSV) Modeling                | 124 |

|   | 6.4   | 3D Tree-Based Interconnect Optimization Methodology     | 125 |

|   | 6.5   | Interconnect Optimization: Homogeneous Tree             | 126 |

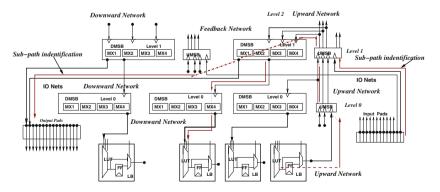

|   |       | 6.5.1 The Downward Programmable Network Model           | 127 |

|   |       | 6.5.2 The Upward Programmable Network Model             | 127 |

|   | 6.6   | Heterogeneous Tree-Based FPGA Architecture              | 132 |

|   |       | 6.6.1 Interconnect Optimization: Heterogeneous Tree     | 134 |

|   | 6.7   | Critical Path Delay Analysis                            | 136 |

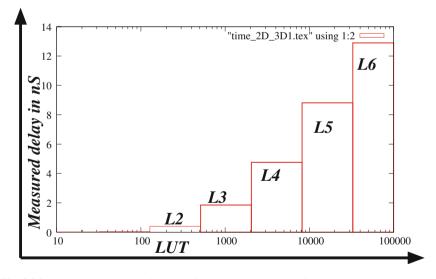

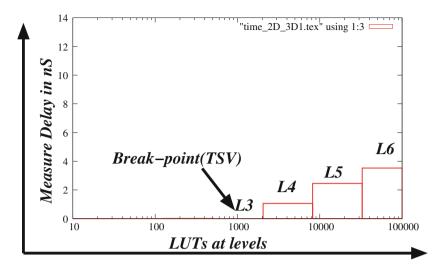

|   |       | 6.7.1 Delay Analysis: Homogeneous Tree                  | 136 |

|   |       | 6.7.2 Delay Analysis: Heterogeneous Tree                | 138 |

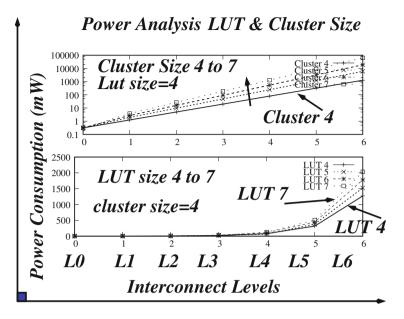

|   | 6.8   | LUT and Cluster Size Effect on Performance              | 140 |

|   | 6.9   | Power Optimization                                      | 143 |

|   | 6.10  | Summary                                                 | 145 |

|   | Refer | rences                                                  | 145 |

| 7 |       | e-Dimensional Thermal Modeling:                         |     |

|   |       | s and Methodologies                                     | 147 |

|   | 7.1   | Introduction: Thermal Fundamentals and Challenges       | 147 |

|   |       | 7.1.1 Heat Generation                                   | 148 |

|   |       | 7.1.2 Heat Transfer.                                    | 148 |

|   |       | 7.1.3 State of the Art: Thermal Modeling                | 151 |

|   |       |                                                         |     |

|   | 7.2            | 3D Thermal Modeling                                          | 151 |  |  |

|---|----------------|--------------------------------------------------------------|-----|--|--|

|   | 7.3            | Heat Transfer in 3D-ICs                                      | 154 |  |  |

|   | 7.4            | 3D Tree-Based FPGA Thermal Analysis Model                    | 156 |  |  |

|   |                | 7.4.1 3D Thermal Aware Design Techniques                     | 157 |  |  |

|   |                | 7.4.2 TSV Aware Thermal Control.                             | 159 |  |  |

|   | 7.5            | 3D FPGA Thermal Modeling: Capabilities                       | 161 |  |  |

|   | 7.6            | 3D FPGA Thermal Modeling: Simulation Results.                | 162 |  |  |

|   | 7.7            | Summary                                                      | 166 |  |  |

|   | Refe           | rences                                                       | 167 |  |  |

| 8 | Phys           | Physical Design and Implementation of 3D Tree-Based FPGAs 16 |     |  |  |

|   | 8.1            | Introduction                                                 | 169 |  |  |

|   | 8.2            | 3D Tree-Based FPGA Design Requirements                       | 170 |  |  |

|   |                | 8.2.1 Why Tree-Based Interconnect and Not Mesh               | 170 |  |  |

|   |                | 8.2.2 3D Tree-Based Interconnect: A Requirement              |     |  |  |

|   |                | for High Logic Density                                       | 173 |  |  |

|   | 8.3            | 2D Physical Design of Tree-Based FPGA                        | 174 |  |  |

|   |                | 8.3.1 Method 1: Coalesce Scalable Tree-Based                 |     |  |  |

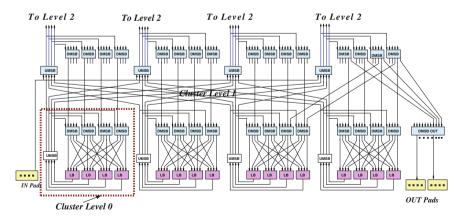

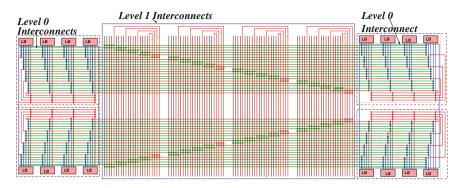

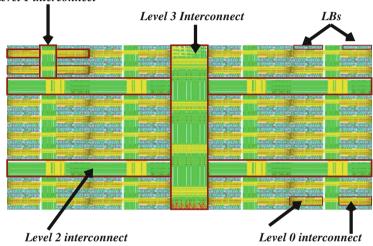

|   |                | 2D Layout Design                                             | 175 |  |  |

|   |                | 8.3.2 Method 2: Level-Wise 2D Tree Layout Design             | 176 |  |  |

|   | 8.4            | Sub-path Timing Characterization                             | 178 |  |  |

|   | 8.5            | 3D Design Methodologies                                      | 181 |  |  |

|   |                | 8.5.1 Vertical Partitioning                                  | 183 |  |  |

|   |                | 8.5.2 Horizontal Partitioning                                | 184 |  |  |

|   |                | 8.5.3 Through Silicon via (TSV) Modeling                     | 186 |  |  |

|   | 8.6            | 3D Tree-Based FPGA Physical Design Flow                      | 187 |  |  |

|   |                | 8.6.1 3D Stacking Methodologies                              | 189 |  |  |

|   |                | 8.6.2 3D FPGA Placement and Route                            | 191 |  |  |

|   |                | 8.6.3 3D Design Sign Off Analysis                            | 194 |  |  |

|   | 8.7            | 3D Timing Analysis                                           | 196 |  |  |

|   | 8.8            | 3 Summary 198                                                |     |  |  |

|   | References 198 |                                                              |     |  |  |

| 9 | Thre           | e-Dimensional FPGAs: Future Lines of Research                | 201 |  |  |

|   | 9.1            | Introduction: 3D FPGA Research                               | 201 |  |  |

|   | 9.2            | Tree-Based Interconnect Partitioning                         | 202 |  |  |

|   |                | 9.2.1 Vertical Partitioning                                  | 202 |  |  |

|   |                | 9.2.2 Horizontal Partitioning                                | 203 |  |  |

|   | 9.3            | 3D Physical Design Methodology and CAD Support               | 203 |  |  |

|   |                | 9.3.1 Interconnect Optimization Model                        | 204 |  |  |

|   |                | 9.3.2 3D FPGA Architecture Exploration Tools                 |     |  |  |

|   |                | and Technologies                                             | 204 |  |  |

| 9.4     | Direct   | ions for Future Work                                                                     | 205 |

|---------|----------|------------------------------------------------------------------------------------------|-----|

|         | 9.4.1    | Technology Research                                                                      | 206 |

|         | 9.4.2    | Alternative Memory Technology                                                            | 206 |

|         | 9.4.3    | Monolithic 3D-FPGA                                                                       | 207 |

|         | 9.4.4    | 3D Hybrid FPGA (3D-HFPGA):                                                               |     |

|         |          | CNT Based FPGA Interconnect                                                              | 207 |

|         | 9.4.5    | Mesh-of-Tree-based Embedded FPGA                                                         | 208 |

|         | 9.4.6    | 3D FPGA CAD Tools                                                                        | 208 |

| Refe    | rences . |                                                                                          | 208 |

| Appendi |          | PGA CAD Tool: 3D Homogeneous Tree-Based<br>PGA Architecture and Design Space Exploration | 211 |

| Appendi |          | PGA CAD Tool: 3D Heterogeneous<br>ree-Based FPGA Exploration                             | 215 |

| Appendi | ix C: Fl | PGA CAD Tool: 3D MoT-Based FPGA Exploration                                              | 221 |

| Appendi |          |                                                                                          |     |

## Acronyms

| 3DIC   | Three-Dimensional Integrated Circuits                          |

|--------|----------------------------------------------------------------|

| ASIC   | Application Specific Integrated Circuit                        |

| BFT    | Butterfly-Fat-Tree                                             |

| CMOS   | Complementry Metal Oxide Semiconductor Field Effect Transistor |

| DRC    | Design Rule Check                                              |

| EDA    | Electronic Design Automation                                   |

| FPGA   | Field Programmable Gate Array                                  |

| GaAs   | Gallium Arsenide                                               |

| HFPGA  | Hirarchical Field Programmable Gate Array                      |

| ITRS   | International Technology Roadmap for Semiconductors            |

| KGD    | Known Good Dies                                                |

| LVS    | Layout Versus Schematic                                        |

| MCNC   | Microelectronics Center of North Carolina                      |

| MM     | More Moore                                                     |

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor              |

| MtM    | More-than-Moore                                                |

| NRE    | Non-Recurring Engineering                                      |

| RF     | Radio Frequency                                                |

| SiP    | System in Package                                              |

| SiGe   | Silicon-Germanium                                              |

| SIA    | Semiconductor Industries Association                           |

| SoC    | System on Chip                                                 |

| SOI    | Silicon on Insulator                                           |

| SSI    | Silicon-Silicon Interconnect                                   |

| TSV    | Through Silicon Via                                            |

| VHDL   | Very High Speed Hardware Description Language                  |

| VLSI   | Very Large Scale Integration                                   |

|        |                                                                |

## Chapter 1 An Overview of Three-Dimensional Integration and FPGAs

**Abstract** The capabilities of many digital electronic devices are strongly linked to Moore's law: processing speed, memory and functional capacity and even the number and size of pixels in digital cameras. All of these are improving at roughly exponential rates as well. This exponential improvement has dramatically enhanced the impact of digital electronics in nearly every segment of the semiconductor industry, and is a driving force of technological and social change in the late 20th and early 21st centuries. This chapter discusses the historical evolution of semiconductor industry from 2D CMOS based technologies to today's three-dimensional (3D) integrated circuits using 3D vertical interconnects. Our main focus in this book is to explain the need and the development of tools and technologies that supports the utilization this emerging technology to improve the performance and manufacturability of high density Field Programmable Gate Arrays (FPGAs).

#### **1.1 Introduction**

The capabilities of many digital electronic devices are strongly linked to Moore's law: processing speed, memory and functional capacity and even the number and size of pixels in digital cameras. All of these are improving at roughly exponential rates as well. This exponential improvement has dramatically enhanced the impact of digital electronics in nearly every segment of the semiconductor industry, and is a driving force of technological and social change in the late 20th and early 21st centuries. Moore's Law is named after Intel co-founder Gordon E. Moore, who described the trend in his 1965 paper [1]. In it, Moore noted that the number of transistors in integrated circuits had doubled every year from the invention of the integrated circuit in 1958 until 1965 and predicted that the trend would continue for at least 10 years. Moore's prediction has proven to be uncannily accurate, in part because the law is now used in the semiconductor industry to guide long-term planning and to set targets for research and development. Historically, CMOS scaling has provided the means to realize higher performance with every technology node, as predicted by Moore's law. Ever since the 90 nm node, the gate length of MOSFETs (Metal-Oxide-Semiconductor-Field-Effect-Transistors) has entered the nano regime. The

<sup>©</sup> Springer International Publishing Switzerland 2015 V. Pangracious et al., *Three-Dimensional Design Methodologies* for Tree-based FPGA Architecture, Lecture Notes in Electrical Engineering 350, DOI 10.1007/978-3-319-19174-4\_1

45 nm technology has become the mainstream since 2008, and 22 nm technology with Tri-gate (FinFET) transistors in 2012 and 14 and 10 nm with similar transistor technology expected in 2015 and 2016 respectively.

In 1998, the SIA (Semiconductor Industries Association) was joined by corresponding industry associations in Europe, Japan, Korea, and Taiwan to participate in a 1998 update of the Roadmap and to begin work toward the first International Technology Roadmap for Semiconductors (ITRS), published in 1999. The overall objective of the ITRS is to present industry-wide consensus on the best current estimate of the industry's research and development needs out to a 15-year horizon. For more than half a century these scaling trends continued, and expected it to continue until at least 2020. However, the 2010 update to the ITRS has growth slowing at the end of 2015, after which time transistor counts and densities are to double only every 3 years. Accordingly, since 2007 the ITRS has addressed the concept of functional diversification under the title More than Moore (MtM). This concept addresses an emerging category of devices that incorporate functionalities that do not necessarily scale according to Moore's Law, but provide additional value to the end customer in different ways. The MtM approach typically allows for the non-digital functionalities e.g., RF communication, power control, passive components, sensors, actuators to migrate from the system board-level into a particular package-level SiP or chip-level SoC system solution. It is also hoped that by the end of this decade, it will be possible to augment the technology of constructing integrated circuits (CMOS) by introducing new devices that will realize some beyond CMOS capabilities. However, since these new devices may not totally replace CMOS functionality, it is anticipated that either chip-level or package-level integration with CMOS may be implemented.

#### 1.1.1 More Moore (MM)

The International Technology Roadmap for Semiconductors has emphasized in its early editions the *miniaturization* and its associated benefits in terms of performances and the traditional parameters in Moores Law. This trend for increased performances will continue, while performance can always be traded against power depending on the individual application, sustained by the incorporation into devices of new materials, and the application of new transistor concepts. This direction for further progress is labeled More Moore or MM. The multitude of new integration technologies opens many new possibilities for building an integrated electronic systems in a confined space and with high efficiency in terms of power dissipation and performance. In particular, the use of the third dimension in the backend/package allows combining products from different semiconductor as well as MEMS technologies. Thus, these advanced integration technologies link the requirements for high performance (More-Moore technologies or MM) with the demand for functional and technological diversity (More-than-Moore technologies or MtM). As we look at the years 2020-2025, we can see that the physical dimensions of CMOS manufacture are expected to be crossing below the 10 nm threshold. It is expected that as CMOS device

dimensions approach the 5–7 nm range it will be difficult to operate any transistor structure that is utilizing the metal-oxide semiconductor (MOS) physics as the basic principle of operation. Of course, we expect that new devices, like the very promising semiconductor tunnel transistors, will allow a smooth transition from traditional CMOS to this new class of devices to reach these new levels of high performance ultra scale device integration. However, it is becoming clear that fundamental geometrical limits will be reached in the above timeframe. By fully utilizing the vertical dimension, it will be possible to stack layers of transistors on top of each other, and this 3-Dimensional (3D) approach will continue to increase the number of components per square millimeter even when horizontal physical dimensions will no longer be amenable to any further reduction. It seems important, then, that we ask ourselves a fundamental question: *How will we be able to increase the computation and memory capacity when the device physical limits will be reached?* It becomes necessary to re-examine how we can get more information in a finite amount of space.

#### 1.1.2 More Than Moore (MtM)

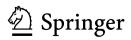

During the blazing progress propelled by Moore's Law of semiconductor logic and memory products, many complementary technologies have progressed as well, although not necessarily scaling to Moore's Law. Heterogeneous integration of multiple technologies has generated *added value* to devices with multiple applications, beyond the traditional semiconductor logic and memory products that had lead the semiconductor industry from the mid 60s to the 90s. A variety of wireless devices contain typical examples of this confluence of technologies, e.g. logic and memory devices, display technology, micro-electrico-mechanical systems (MEMS), RF and Analog/Mixed-signal technologies (RF/AMS), etc. It should be emphasized that *More-than-Moore or MtM* technologies do not constitute an alternative or even a competitor to the digital trend as described by Moores Law. In fact, it is the heterogeneous integration of digital and non-digital functionalities into compact systems that will be the key driver for a wide variety of application fields. Whereas MM may be viewed as the brain of an intelligent compact system, MtM refers to its capabilities to interact with the outside world and the users as illustrated in Fig. 1.1.

In recent years, however, several bottlenecks have appeared as we have continued to scale down to sub-nm technology nodes and the question is, if the traditional technology scaling method alone will be able to overcome the performance and cost issues of the future IC manufacturing caused by interconnect delay and latency issues. The ITRS roadmap predicts 3D integration as a key technology to solve this so-called wiring crisis [2]. Several semiconductor industries and research institutes have demonstrated 3D integration process [3, 4]. Even though there are still no commercial true 3D-IC application in the market, it has become apparent that there is a strong demand for such future application such as memories, processors and logic devices. In addition to enabling of the further improvement of transistor integration densities (*More-Moore*), 3D integration is a well accepted platform for

**Fig. 1.1** The need for integrating digital and non-digital functionalities in an integrated system is translated as a dual trend in the International Technology Roadmap for Semiconductors: miniaturization of the digital functions (More Moore) and functional diversification (More-than-Moore), 3D integration represent a convergence of SoC and SiP disciplines [2]

*More than Moore* applications with their essential need for integration of heterogeneous technologies. Three-dimensional integration technology increases the number of active layers and optimizes the interconnect network vertically. The main advantage of 3D-IC technology is that it significantly enhances interconnect resources and increases logic density. If used correctly, 3D-ICs provides improved bandwidth and throughput, as well as reduced wire length. For  $N_{layers}$  stacking, in the best scenario, if the inter-layer vias are ignored, average wire length would be expected to drop by a factor of  $(N_{layers})^{1/2}$ . Both wire resistance and wire (RC) delay would drop by a factor of  $(N_{layers})$ . It also allow integration of dissimilar materials, process technologies, and functions onto one platform.

Our main focus in this book is to explain the development of tools and technologies that supports the utilization this emerging technology to improve the performance and manufacturability of high density Field Programmable Gate Arrays (FPGAs). FPGA chips offer an attractive solution for improving the design productivity through re-use of the same silicon implementation for a wide rage of applications. FPGA is programmable and can be reconfigured for yield improvement and defect tolerance. These features become absolutely necessary when CMOS technology scales down to nanometer scale, because the yield of the fabrication of semiconductor components hardly ever reach 100 %. FPGA consist of configurable logic blocks and I/O blocks that are interconnected by a configurable routing network. FPGA is configured to

implement circuits by writing into the configuration memory that are embedded throughout the FPGA and defines the logical function of each block and connections within the configurable routing resources. Reconfigurability of FPGAs is fundamentally different from traditional general-purpose microprocessors. Microprocessors are attractive for their flexibility. An Application Specific Integrated Circuit (ASIC) is a device that is customized to a specific application. Since the exact nature of the application is known beforehand, ASIC hardware resources are designed to provide the highest performance implementation for the application. The price paid by ASICs because of their superlative performance characteristics is flexibility. Once an ASIC has been manufactured, it is impossible to modify it to implement another application, different from the one it was intended for. Further, since the Non-Recurring Engineering (NRE) costs involved in designing and manufacturing an ASIC are comparatively high, it is generally not feasible to design and fabricate ASICs in low volumes. Since their introduction in the mid eighties, FPGAs evolved from a simple, low-capacity gate array technology to devices [5, 6] that provide a mix of coarse-grained data path units, microprocessor cores, on chip A/D conversion, and gate counts by millions. Today, FPGAs become important actors in the computational devices domain that was originally dominated by microprocessors and ASICs. Just like microprocessors, FPGA-based systems can be reprogrammed on a perapplication basis. At the same time, FPGAs offer significant performance benefits over microprocessor implementations for a number of applications. Although these benefits are still generally an order of magnitude less than equivalent ASIC implementations, the low NRE costs, fast time-to-market, and flexibility of FPGAs make them an attractive choice for low-to-medium volume applications.

#### **1.2 Technological Initiatives and Contribution**

FPGAs are consistently improving in capacity and performance, and are now among the most popular devices in the market. With their regular structure, they also scale easily to future technologies. However, FPGAs are still facing serious challenges in terms of delay, power consumption, and logic density compared to ASICs. FPGA is estimated to be over ten times less efficient in logic density, over three times worse in delay, and over three times higher in power consumption compared to a functionally equivalent ASIC [7–11]. Despite of their design cost advantage, FPGAs impose large area overhead when compared custom integrated silicon alternatives (ASICs). To illustrate the magnitude of this problem, we refer to the work presented in [11] where authors measure the gap between FPGAs and ASICs in terms of logic density, circuit speed and power consumption. The major performance and power bottleneck of the FPGA is the programmable interconnects and routing elements inside FPGA, which have been found to account for up to 80% [9] of the total delay and up to 85% [12] of the total power consumption and consume almost 90% [13] of total silicon area, when both local and global interconnects are considered.

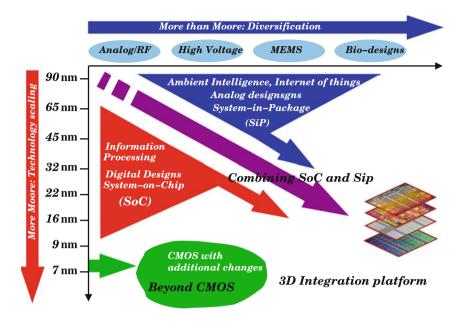

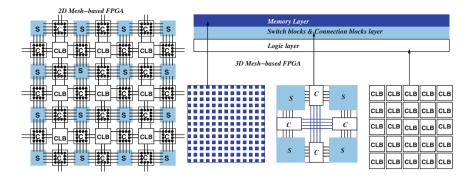

There is considerable demand for high performance FPGAs with low power consumption and area. One promising way to improve FPGA performance, logic density and power consumption is to incorporate three-dimensional (3D) integration, which increases the number of active layers and optimizes the interconnect network delay using vertical interconnects. There are few research initiatives for the design and implementation of 3D Mesh-based FPGAs [14–16]. For Mesh-based 3D FPGA, every layer in a 3D chip implements a normal 2D FPGA and this type of stacking reduces the average Manhattan distance between logic blocks, which leads to shorter interconnect resources. Consequently, 3D integration method is an attractive technology to improve the performance and density of FPGAs. Other gains, such as reduced design footprint and the ability to integrate different technologies, further favor 3D FPGAs. Used correctly, 3D integrated circuits provides improved bandwidth and throughput by reducing interconnect wire-length. However Mesh-based FPGA has a planer island style architecture which suites very well for a two-dimensional (2D) FPGA implementation. The major gains reported from the research and experimental demonstrations of 3D Mesh-based FPGA are not yet reached the scale of advantages and improvements expected according to ITRS roadmap [2], since the overall FPGA area and power consumption increases in 3D architecture, nevertheless the delay is reported to have reduced by 38 % [16]. Figure 1.2 presents the complexities involved in design and manufacturing of high density 3D chips. The true 3D implementation should bring holistic improvement in all areas of chip development starting from design to manufacturing. Many of the early designs and demonstrators of 3D FPGAs did not show much improvement in area and power consumption. In this book we try to revisit the traditional Tree-based FPGA architecture and main

Fig. 1.2 FPGA Design and implementation challenges: The future is in the 3rd dimension

stream industrial FPGA architectures to conduct a feasibility study using 3D technology to improve logic density, area, speed and power consumption. The Tree-based multilevel interconnect architecture is one of traditional routing architecture of FPGA and multiprocessor system on chip (MPSoC) based systems. However it is not implemented in any of the industrial FPGA or MPSoC systems due to the large wire delays associated with the interconnect impede the performance of the system.

#### **1.2.1 Modified Tree-Based Interconnect**

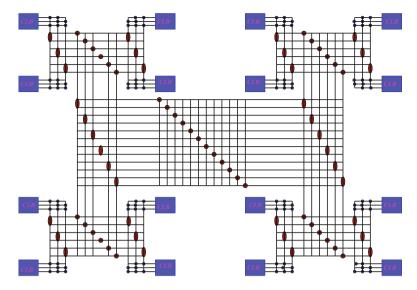

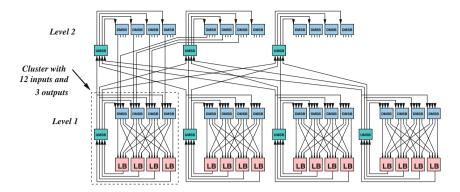

The aim of this book is to revisit the traditional and industrial FPGA architectures to propose a suitable interconnect architecture model to design and manufacture 3D FPGAs with improved logic density and speed. An efficient *butterfly-fat-tree* interconnection network structure is proposed in [17–20] to design and implement high density FPGAs. A detailed analysis of area and switch requirements of Mesh- and Tree-based FPGA architectures presented in [19, 20]. The reported results shows that the 2D Tree-based architecture improve total area by 56% and reduce the total switch requirement by 59% compared to 2D Mesh-based FPGA architecture. Never-theless the wire delay increases logarithmically as the Tree grows to higher level and this makes the 2D physical design implementation of Tree-based FPGA architecture a daunting task. The complexities associated with the development 2D Tree-based architecture layout is presented in [18]. In this book, we propose new design solutions and exploration methods using 3D technology to improve logic density, area, and power consumption of 3D FPGAs using Tree-based multilevel interconnect architecture. The main sections of 3D FPGA design presented in this book as follows.

#### **1.2.2 Tree-Based Interconnect Partitioning**

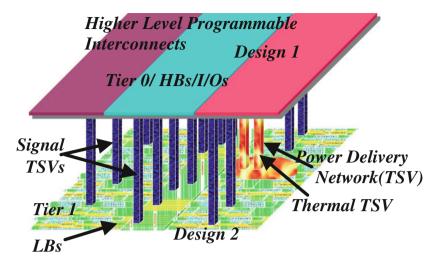

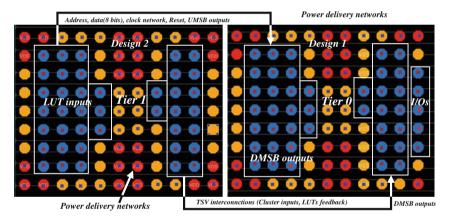

Interconnect network partitioning is the best way to reduce the length of interconnects and theirby improveing speed and power consumption. Two independent network partitioning methodologies are proposed to design and implement 3D Tree-based FPGA.

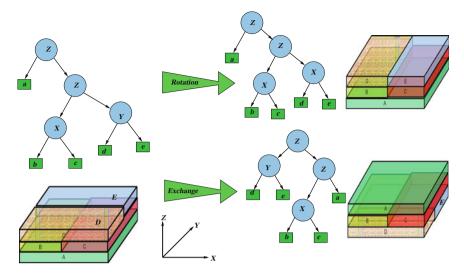

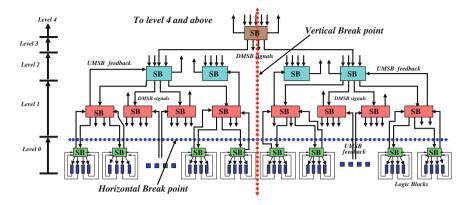

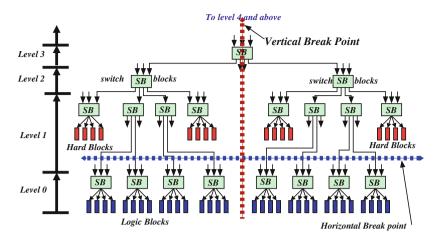

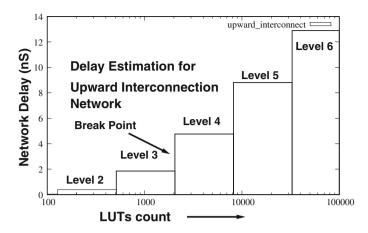

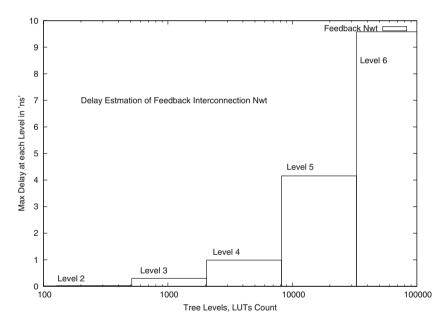

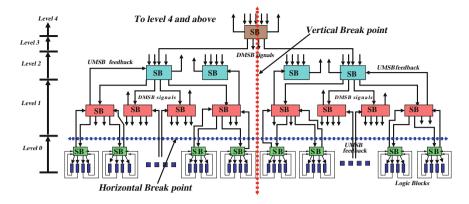

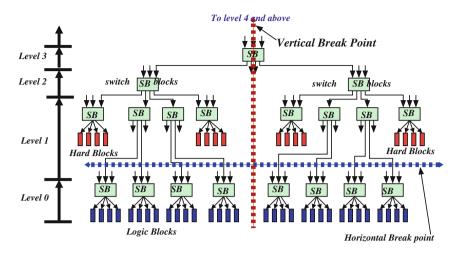

- *Vertical partitioning:* the programmable interconnect network is partitioned vertically by placing the *break-point* at the highest level  $\ell_v$  of the Tree-based programmable interconnect network to balance the silicon area and power consumption across multiple tiers of the 3D chip

- *Horizontal partitioning:* the main objective is to optimize the critical path delay and improve logic density. The horizontal *break-point* is placed at a particular tree level  $\ell_h$  based on the design and manufacturing constraints to achieve interconnect delay optimization using TSVs.

The location of the level  $\ell_v$  is always fixed at highest tree level, however the location of level  $\ell_h$  is decided based on the architecture and wire delay requirements.

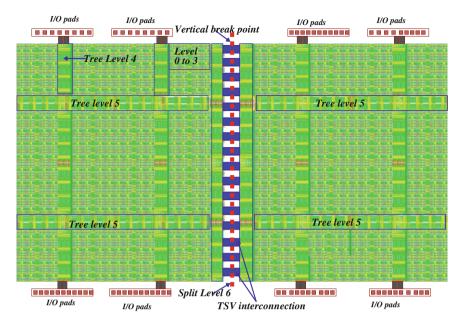

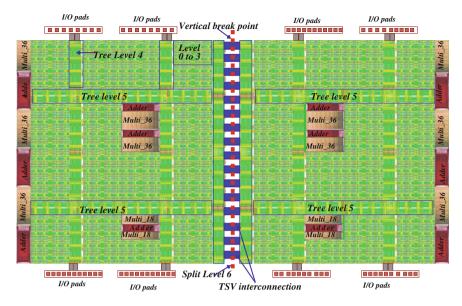

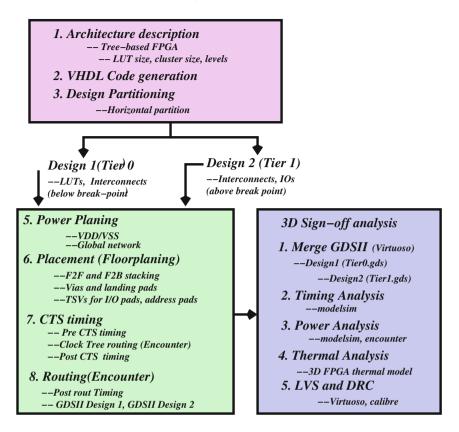

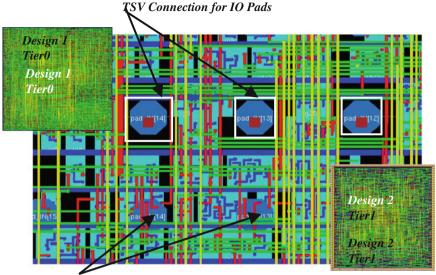

#### 1.2.3 3D FPGA Design and Implementation Methodology

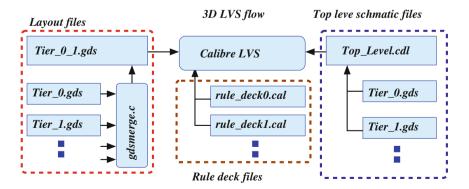

To design and implement 3D multi-tier Tree-based FPGA, we developed a set of 3D physical design methodology and tools using Global Foundries 130 nm technology node modified to use Tezzaron's TSV technology [21, 22]. The design flow covers all areas of 3D design, including the design partitioning, merging multiple tiers (gds files) and design sign-off analysis. In addition, we also address the specific issues that 3D designers will encounter dealing with tools that are not specifically developed to meet their needs. We developed additional design support programs to enable the designer to perform 3D DRC/LVS and TSV implementation using six metal back-end offline (BEOL) technology.

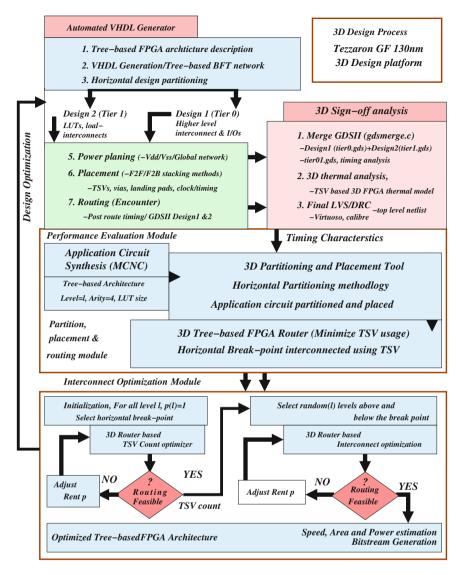

#### 1.2.3.1 3D FPGA Physical Design Tools

This book describe the development of an automated 3D physical design methodology including a VHDL code generator based on Tree-based FPGA architecture description and design constraints. The VHDL code generator is based on a hierarchical design approach that partitions the design into smaller sections, which implement clusters separately and assemble them together at the final design phase. The physical design is performed using Global Foundries 130 nm technology node (Tezzaron 3D Design platform). A timing evaluation system based on Mentor's circuit simulator *Eldo* is attached to design module to accurately estate the networks delays.

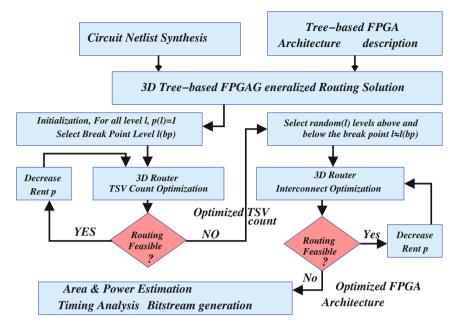

#### 1.2.3.2 3D FPGA Architecture Exploration Tools and Methodologies

Our goal through the development of this book is to develop an efficient placement and detailed routing tool for 3D Tree-based FPGAs. Using this tool, we investigate the impact of 3D integration on delay, area and power consumption, in addition to wire-length reduction because wire-length alone cannot be relied on as a metric for 3D integration benefits. The main features of the architecture exploration tool is mentioned below.

- Feasibility study of different network partitioning methods to find suitable interconnect architecture for 3D staking.

- 3D Tree-based FPGA architecture optimization tool: This tool is developed as an add-on facility to 3D place and rout tool to find minimum interconnect and TSV requirements for the implementation of 3D FPGA. A Rent's Rule [23, 24] based wire-length distribution model is used to design the architecture optimization tool.

• FPGAs are not really FPGAs any more instead, they are arrays of programmable gates plus DSP slices, ALUs and transceivers etc. The 3D Tree-based exploration is augmented to study 3D Heterogeneous Tree-based FPGAs as well. The tools have capabilities to analyze the the placement and location of *hard-blocks* to optimize the speed and area of the 3D FPGA chip.

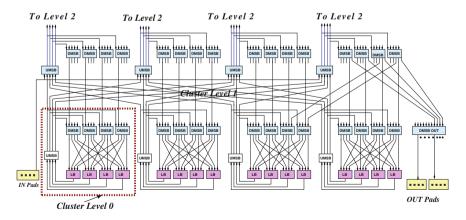

#### 1.2.4 Unified Mesh of Tree Architecture

Recently we have witnessed 2.5D and 3D FPGA product demonstrations from leading FPGA research institutions and manufacturing industries. These new FPGA architecture also introduces many opportunities and challenges to meet with the expectations of increasing functionality of modern FPGA chip designs. In this book we propose a variant of Tree-based FPGA architecture with qualities of both Mesh and Tree-based interconnect architectures. Our previous studies [19, 20] shows Treebased FPGA has better logic density and area advantage compared to Mesh-based FPGAs. In this study, we examine the possibility of unifying the advantages of modified Tree- and Mesh-based interconnect architecture into one platform to improve density, area, and speed of 3D FPGAs.

#### 1.2.4.1 Architecture Improvement, Tools and Methodologies

In this book we propose a 3D interconnect network implementation based on a modified Mesh-of-Trees (MoT) topology for FPGA architecture design as an extension of Tree-based FPGA architecture. We further optimized the MoT-based interconnect architecture using *long wire segments* with adjustable *span* to transform it into a viable architecture for the design and implementation of high density 2.5D multi-FPGA and 3D stacked multi-tier FPGA based systems. Exploration and physical design tool flows developed to demonstrate the performance improvement and area advantage of 2.5D and 3D MoT-based FPGA architecture. The two possible variants of MoT-based FPGA architecture implemented are as follows.

- 2.5D Multi-FPGA using Mesh of Tree Architecture: We developed exploration and validation tools to explore the impact of % of wires cut and no of cuts on performance and area of 2.5D multi-FPGA based systems.based of MoT-based FPGA architecture. Using the 2.5D tools flow, we can demonstrate the improvement in area and performance of 2.5D multi-FPGA with 1–3 cuts and different variants of interposer-based inter-FPGA connections.

- **3D** Multi-tier FPGA using Mesh of Tree Architecture: A 3D architecture exploration tool (place and route) developed to estimate the area and delay reduction in 3D stacked MoT-based FPGA architecture. We also implemented an MoT-based architecture optimization tool using Rent's Rule to find the optimal architecture to estimate the impact of % of long wires on channel width W of the 3D MoT-

based FPGA architecture. Unlike the other 3D Mesh-based FPGA architectures, in 3D MoT-based FPGA architecture, we have a direct relation between vertical interconnects and channel width. This relationship is established to optimize the horizontal and verticals routing resource requirements. This book will not discuss the deatils of the MoT-Based FPGAs, since the focus of this book is on 3D implementation of Tree-based FPGA architectures.

#### **1.3 Book Organization**

A brief overview of the contents of the book as follows. This Chapter provides a brief introduction about the main fcous theme, thrust area and contributions made to it for the development of high density 3D FPGAs. Chapter 2 starts with brief introduction to 3D integration and discusses the main challenges and opportunities of 3D technology in areas like process integration and CAD tools development. This chapter also discusses few new practical solutions to solve technological and CAD level issues in 3D physical designs process. The main purpose of this work is evaluate the interconnect architecture of traditional and mainstream FPGA architectures and to propose an alternative 3D interconnect architecture or suggest the required modification to design and manufacture high density FPGAs using 3D Technology. Chapter 3 discusses the pros and cons of different FPGA architectures and propose new architectural changes to the existing FPGA architectures. An interesting state of the art of CAD tools for the exploration of 2D Mesh- and Tree-based FPGA architectures presented in Chap.4. This chapter also report the importance of research and development of CAD algorithms for high density FPGA development. Chapter 5 presents the state of the art 3D FPGA. Many new ideas and implementations regarding 3D-ICs and FPGAs shows positive developments across the world to migrate the present day technology to the third dimension. This chapter also present the 3D design and architecture exploration methodology developed for the implementation of 3D Tree-based FPGAs.

The Chap. 6 provides a detailed analysis of the improvement in speed, area and optimization of 3D Tree-based FPGA architecture. Once an architecture is verified for its performance, its also curious to know how this architecture is going to behave when the few architectural parameters changes. This chapter also provides answers to those questions about the impact of LUT size and cluster size on performance of 3D FPGA chip. FPGAs have evolved dramatically over the past 10 years, as they have taken advantages of new process technologies and architectural exploration.

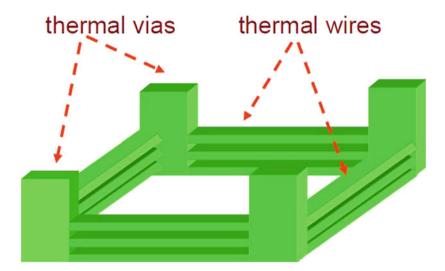

The power consumption of 3D-ICs is expected to decrease due to the interconnect length reduction. However the power density increases since the distance between

the devices decreases per unit volume as compared to a 2D layout. Consequently, the temperature also rises. Thermal aware design or hardware design techniques should be implements at various stages of the 3D-IC design flow, such as synthesis, floorplanning, placement and routing to maintain the temperature of the chip with acceptable limits. The Chap. 7 provides detailed description and analysis of different thermal aware design techniques and hardware-based methods developed to improve thermal profile of 3D Tree-based FPGAs. The development of 2D physical design for Tree-based FPGA interconnect is a daunting task. Chapter 8 sheds light into those issues designers face and also describe how to resolve them using 3D technology. This chapter provides two interesting network partitioning methodologies for Tree-based interconnect to mitigate the traditional long wire-length issues associated Tree-based interconnect architectures. Three-dimensional design and technology is famous for it ability to improve speed, power consumption and silicon footprint of semiconductor chips. This chapter introduce new 3D design and varification tools and methodologies of 3D FPGA design and implementation. The Chap. 9 narrates the summary of the thesis and provides future lines of research work.

#### References

- 1. G. Moore, Cramming more components onto integrated circuits. Proc. IEEE 86(2), 82-85 (1998)

- 2. SIA: Semiconductor Industries Association, *The International Technology Roadmap for Semi*conductor (SEMATECH, Austin, TX, 2009)

- P. Garrou, C. Bower, P. Ramm, Handbook of 3D Integration (Wiley-VCH, 2008). ISBN: 978-3-527-32034-9

- V.F. Pavlidis, E.G Friedman, *Three-Dimensional Integrated Circuit Design* (Morgen Kaufmann, 2009). ISBN: 978-0-12-374343-5

- 5. Altera, Stratix V device overview (2013), www.altera.com

- 6. Xilinx Inc, *Two flows for partial reconfiguration: module based or difference based* (2004), http://www.xilinx.com/bvdocs/appnotes/xapp290.pdf

- 7. J. Rose, R. Francis, D. Lewis, P. Chow, Architecture of field-programmable gate arrays: the effect of logic functionality on area efficiency. IEEE JSSC **25**(5), 1217–1225 (1990)

- V. Betz, J. Rose, How much logic should go in an FPGA logic block?. IEEE Des. Test Comput. 15(1), 10–15 (1998)

- E. Ahmed, J. Rose, The Effect of LUT and cluster size on deep-submicron FPGA performance and density. IEEE Trans. Very Large Scale Integr. VLSI Syst. 22(3), 288–298 (2004)

- M. Lin, A.E. Gamal, Y.-C. Lu, S. Wong, Performance benefits of monolithically stacked 3D FPGA, in *Proceedings of the 2006 ACM/SIGDA 14th International Symposium on Field Pro*grammable Gate Arrays, Monterey, California, USA, 22–24 Feb 2006, pp. 113–122

- I. Kuon, J. Rose, Measuring the gap between FPGAs and ASICs. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 26(2), 203–215 (2007), http://dx.doi.org/10.1109/TCAD. 2006.884574 (IEEE Council on Electronic Design Automation)

- F. Li, D. Chen, L. He, J. Cong, Architecture evaluation for power-efficient FPGAs, in *Proceedings of the ACM/SIGDA International Symposium on Field Programmable Gate Array*, Nov 2003, pp. 175–184

- A. DeHon, Reconfigurable Architectures for General-Purpose Computing, Ph.D. dissertation, Department of Elect Engg and Computer Science, Massachusetts Institute of Technology, 1996

- C. Ababei P. Maidee and K. Bazargan, Exploring potential benefits of 3D FPGA integration, in *Field Programmable Logic and Application*, vol. 3203 (Springer, Berlin, Germany, 2004), pp. 874–880

- K. Siozios, A. Bartzas, D. Soudris. Architecture level exploration of alternative schmes targeting 3D FPGAs: a software supported methodology. Int. J. Reconfig. Comput. 2008 (2008)

- K. Siozios, V.F. Pavlidis, D. Soudris, A Novel framework for exploring 3-D FPGAs with heterogeneous interconnect fabric. ACM Trans. Reconfig. Technol. Syst. 5(1) (2012)

- A. DeHon, Unifying mesh- and tree-based programmable interconnect. IEEE Trans. Very Large Scale Integr. VLSI Syst. 12(10), 1051–1065 (2004)

- A. DeHon, R. Rubin, Design of FPGA interconnect for multilevel metallization. IEEE Trans. Very Large Scale Integr. VLSI Syst. 12(10), 1038–1050 (2004)

- Z. Marrakchi, H. Mrabet, C. Masson, H. Mehrez, Mesh of tree: unifying mesh and MFPGA for better device performances, in *NOCS-2007*, pp. 243–252 (2007)

- Z. Marrakchi, H. Mrabet, U. Farooq, H. Mehrez, FPGA interconnect topologies exploration. Int. J. Reconfig. Comput. 2009 (2009)

- 21. S. Gupta, M. Hilbert, S. Hong, R. Patti, *Techniques for Producing 3D ICs with High-Density Interconnect* (Tezzaron Semiconductor, Naperville, IL, 2005)

- 22. R. Patti, Advances in 3D memory and logic devices, in *IMAPS International Conference on Device Packaging* (TAI3, Scottsdale, AZ, March 2010)

- B. Landman, R. Russo, On a pin versus block relationship for partitions of logic graphs. IEEE Trans. Comput. 20(12), 1469–1479 (1971)

- J. Pistorius, M. Hutton, Placement rent exponent calculation methods, temporal behaviour and FPGA architecture evaluation, in *Proceedings of the International Workshop on System Level Interconnect Prediction* (Monterey, Calif, USA, April 2003), pp. 31–38

## Chapter 2 Three-Dimensional Integration: A More Than Moore Technology

**Abstract** Three-dimensional integrated circuits (3D-ICs), which contain multiple layers of active devices, have the potential to dramatically enhance chip performance, functionality, and device packing density. They also provide for microchip architecture and may facilitate the integration of heterogeneous materials, devices, and signals and offer a promising solution for reducing both silicon footprint and interconnect length without shrinking the transistors. However, before these advantages can be realized, key technology and CAD challenges of 3D-ICs must be addressed. More specifically, the process required to build circuits with multiple layers of active devices and CAD tools used for design and validation of such circuits. Several such methodologies and CAD tools associated with the design fabrication of 3-D ICs are discussed in this chapter. Few successful 3D-IC design methods and CAD tools and benefits of applying 3D design to the future reconfigurable systems are also discussed in this chapter.

#### 2.1 Introduction

The ongoing demand for greater functionality resulting in multiple IC products, longer off-chip interconnects ravage the performance of microelectronic systems. The advent of System-on-Chip (SoC) in the mid 1990s primarily addressed the increasing delay of the off-chip interconnects. Integrating all of the components on a monolithic substrate enhances the overall speed of the system, while decreasing the power consumption. To assimilate disparate technologies, however several difficulties must be surmounted to achieve high yield for the entire system. Additional system requirements for the radio frequency (RF) circuitry, passive elements, and discrete components, such us decoupling capacitors, which are not easily integrated due to performance degradation or size limitations. While Moore's law [1] and the pursuit of ever increasing transistor counts is well known in IC design and manufacturing circles, what is seldom brought to light for others, are the escalating cost and technology challenges associated with this pursuit. Smaller transistors and larger dies have been reasonable answer to this quest in the past. Stacked dies using wire bond connections and flip-chips have even been employed to create system-in-package (SiP) solutions

<sup>©</sup> Springer International Publishing Switzerland 2015 V. Pangracious et al., *Three-Dimensional Design Methodologies for Tree-based FPGA Architecture*, Lecture Notes in Electrical Engineering 350, DOI 10.1007/978-3-319-19174-4\_2

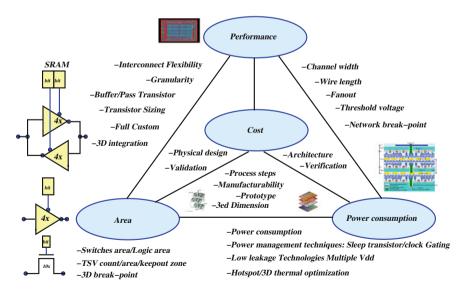

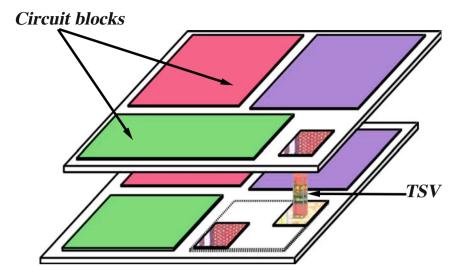

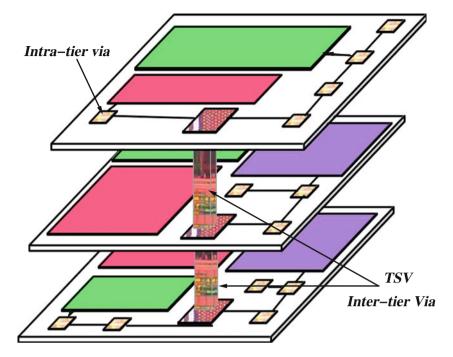

Fig. 2.1 Interconnects bond wires in typical System-in-package (SiP) and 3D-IC

that meet the needs of some. Looking for alternative solutions for next generation designs, that meet the performance, integration, form-factor, manufacturability, and cost requirements, may have begun to look at going up rather than out. With this trend, the Three-dimensional (3D) integration using through-silicon via (TSV) technology has gained much attention. Once the domain of specialist applications, more mainstream users, such as memories, microprocessors and specialized logic designs are now being considered as TSV candidates. The advantages of 3D-IC integration are better electrical performance, low power consumption, lower area and weight and high performance (Fig. 2.1).

#### 2.1.1 Opportunities for Three-Dimensional Integration

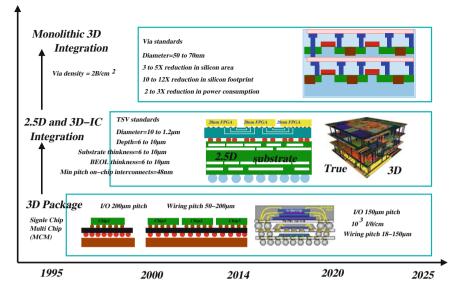

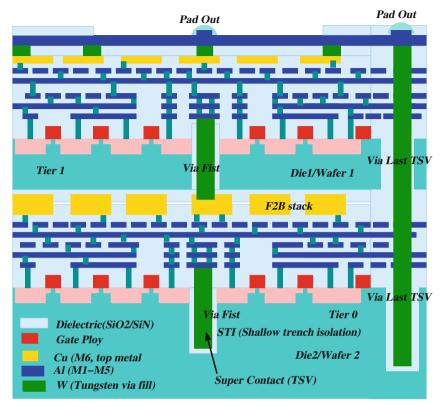

Performance requirements such as increased bandwidth, reduced latency, and lower power consumption are driving the adoptions of 3D-IC designs. A complete 3D-IC implementation is usually envisioned as a stack of active chips using TSVs to connect through each chip down to a package substrate. TSV designs represent a convergence of SoC and SiP disciplines, providing designers the means to significantly increases the bandwidth between the logic chip and the memory especially with wide memory interfaces that cannot be achieved with bond wires, as well as the ability to mix and match dies that not only use different process node, but also different manufacturing technologies such as SiGe, SOI, CMOS low voltage, CMOS high voltage, Biploar, GaAs, etc. The ability to combine different dies in a single stack enable to acquire needed functionality to provide high-quality, proven die. What is new in 3D-ICs is the ability to place vertical interconnections (TSVs) in a dense array, without the strict perimeter constraints imposed by an equivalent wire-bonded design. Utilizing stacked chips, particularly in memory-intensive designs, allows designers to stay at today's reasonable process nodes for each die and derive the benefit or proven volume manufacturing processes.

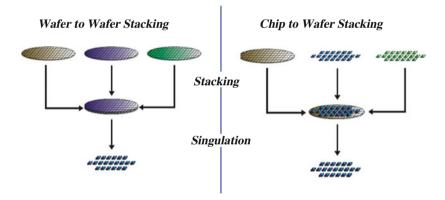

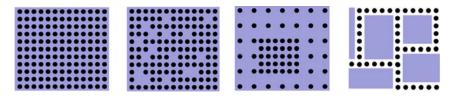

Three-dimensional (3D) die stacks and high-bandwidth silicon packaging technology using emerging through silicon vias (TSVs), thinned silicon, and fine-pitch silicon-silicon interconnections (SSIs) make use of a wide variety of technology structures, materials, and processes. Universities, consortia, and industry have driven research and early demonstrations for a decade. TSV and SSI interconnection density can scale in excess of six orders of magnitude, making the technology widely applicable from simple to very complex applications. At academic research institutes and semiconductor industries, new 3D test-vehicle (i.e., demonstrator) designs followed by manufacturing, assembly, and characterization studies continue to provide technologists with an understanding of structure and process-integration capabilities and limitations. Results from these technology studies provide guidance on 3D design rules, structures, processes, tests, and reliability, which can support the manufacturing of 3D products and provide data that we may use to determine technology directions. Practical technology fabrication and integration approaches need to consider targeted TSV and SSI interconnection density, silicon thickness, and power densities. In addition, decisions with respect to options such as TSV conductor material, SSI integration material, and use of die-on-die, die-on-wafer, or wafer-to wafer process approaches need to be made with regard to interconnection redundancy, die size, yield, cost, and test methodology.

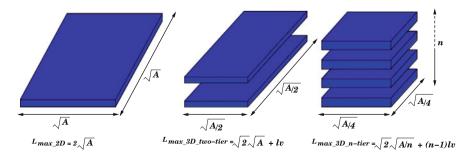

The inherent advantage of 3D integration is the drastic decrease in interconnect length, particularly the long global interconnects, which directly results in increased speed [2–6]. We can understand this by simple geometry analysis for 3D-ICs. A given squre area A has maximum Manhattan wirelength id  $2\sqrt{A}$ . The same area is split into two tiers reduces the wirelength to  $\sqrt{2}\sqrt{A} + l_v$  where  $l_v$  is the length of via between tiers. In general, n layers gives a maximum Manhattan wirelength of  $2\sqrt{\frac{A}{n}} + (n-1)l_v$ . Figure 2.2 illustrate the graphical representation of wire-length reduction which the original 2D chip implemented using 3D technology with n tiers. The interconnect power is also reduced as the capacitance of the wires decreases

Fig. 2.2 Illustration of wire-length reduction where the original 2D chip implemented using 3D technology

[7, 8]. Additionally, the total power dissipated by an interconnect system is further decreased as the number of repeaters inserted along the interconnect is reduced [9]. Finally, coupling among intraplane adjacent interconnects is lower due to decreased length, improving signal integrity. The 3D-IC based systems provides the capability to include disparate technologies [10], greatly extending the capabilities of modern systems-on-chip (SoC). This defining feature of 3D-ICs offers unique opportunities for highly heterogeneous and sophisticated systems [11, 12]. A vast pool of applications such as medical, wireless communications, military, and low-cost consumer products, exists for vertical integration, as the proximity of the system components caused by the third dimension is suitable for either the high performance or low power ends of the SoC application space [13]. This heterogeneity, however, greatly complicates the interconnect design process within a multi-tier system, as potential design methodologies need to manage the diverse interconnect impedance characteristics and process variations caused by the different fabrication processes and technologies employed in the different physical tiers.

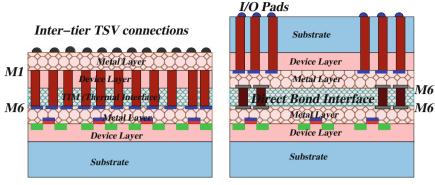

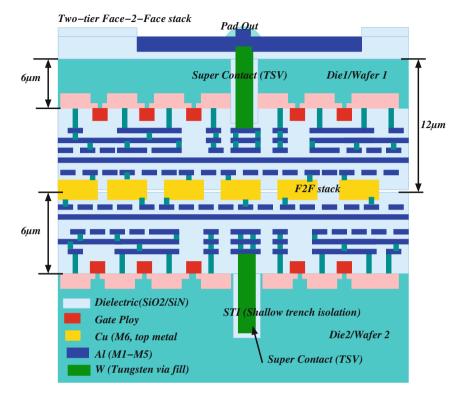

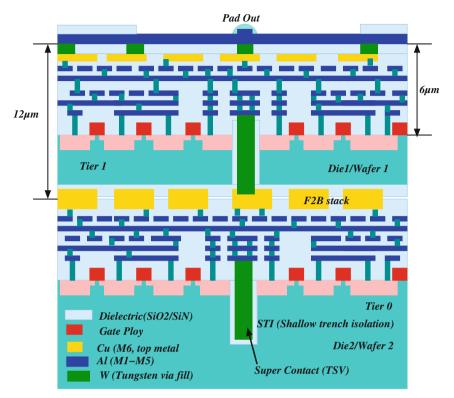

Three-dimensional circuits can be conceptualized as the bonding of multiple wafers or bare dice. The distinctive difference between an SiP and a 3D IC is the granularity of the vertical interconnects. Different bonding styles between the planes within a 3D system are also possible Face-to-Face (F2F), Face-to-Back (F2B), and Back-to-Back (B2B) [14, 15]. Examples of SiP structures and various bonding styles for 3D circuits are illustrated in Fig. 2.1. Each of these bonding styles is likely to include through silicon vias (or interplane vias) with different physical dimensions. Consequently, the density of the vertical interconnects can vary not only among different 3D circuits but also among the physical planes within a 3D circuit.

#### 2.2 Historical Evolution of 3D System Integration

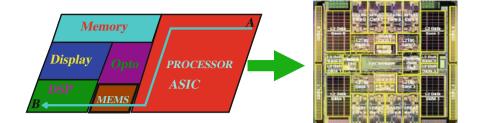

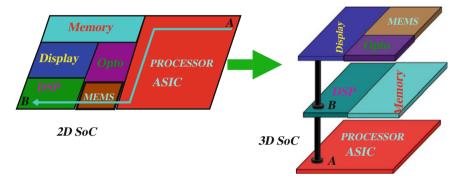

The proposal of doubling the number of transistors on an IC chip every 24 months by Gordon Moore in 1965 (Moores law) [1] has been the most powerful driver for the development of the microelectronics industry in the past 45 years. This law emphasizes lithography scaling and 2D integration of all functions on a single chip, perhaps through system-on-chip (SoC) as schematically shown in the left-hand side of Fig. 2.3. On the other hand, the integration all these functions can be achieved through 3D-IC integration [13, 16–18] as illustrated in Fig. 2.4.

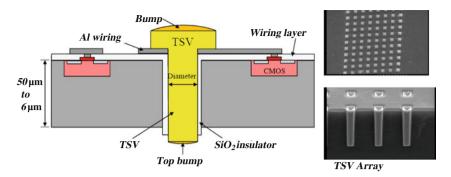

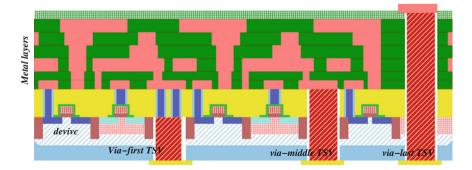

Through Silicon Via (TSV) is the heart 3D-IC integration [19]. Though the 1956 Nobel Laureate in Physics, William Shockley invented TSVs more than 50 years ago in U.S. Patent #3,044,909, filed in 1958 and issued in 1962, but it was not intended for 3D-IC integration and it took half a century for the production technology to reach the level of expertise that would actually permit making TSVs. From a die with hundreds of transistors in the 1960s to dies approaching billions of circuits in 2014, on-chip integration has continued to require lithographic advancements for circuit and increase in wire density has led to increasing the number of wiring levels on the chip. Over decades of semiconductor scaling, on-chip integration has far

Fig. 2.3 Typical 2D System-on-Chip (SoC) integration

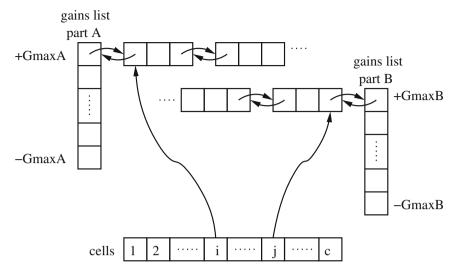

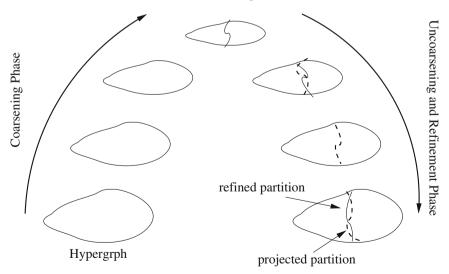

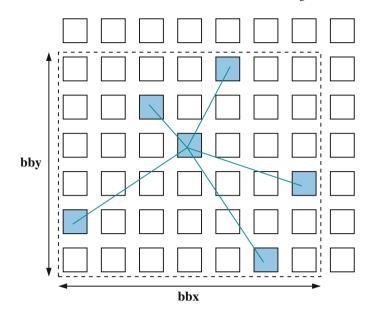

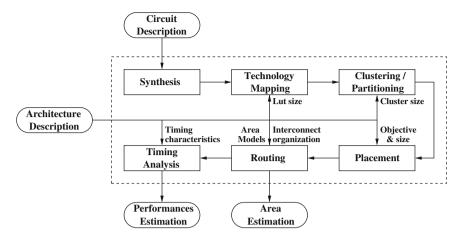

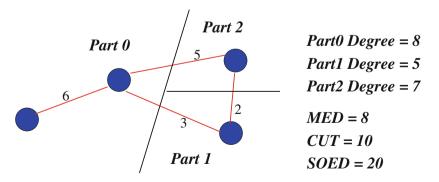

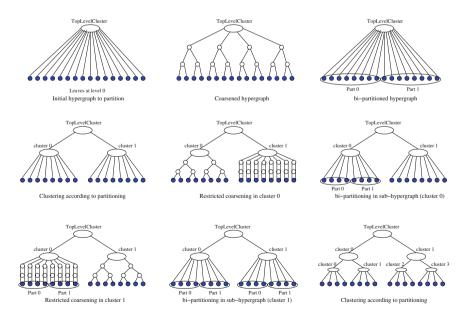

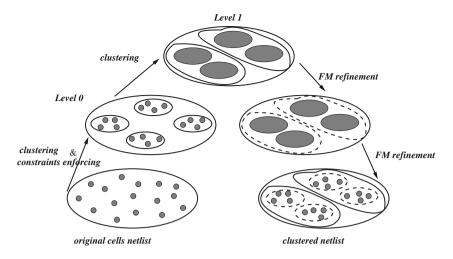

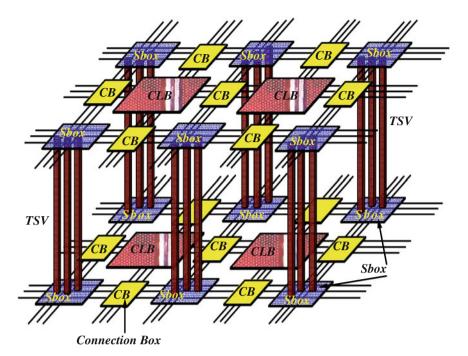

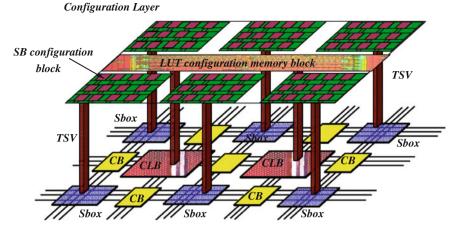

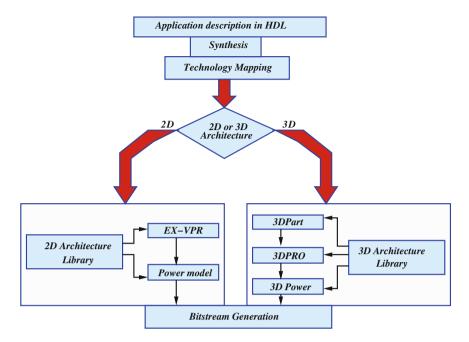

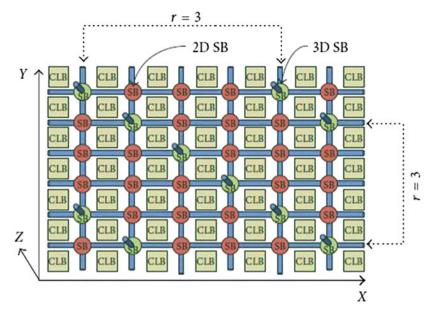

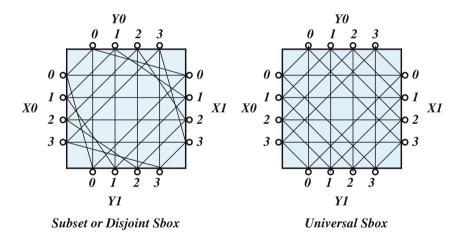

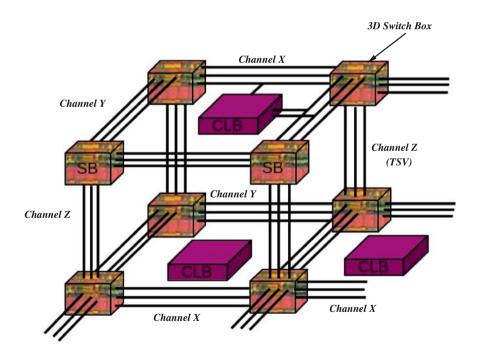

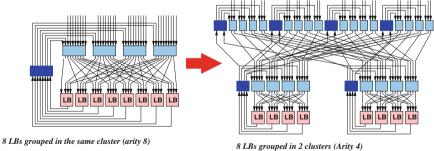

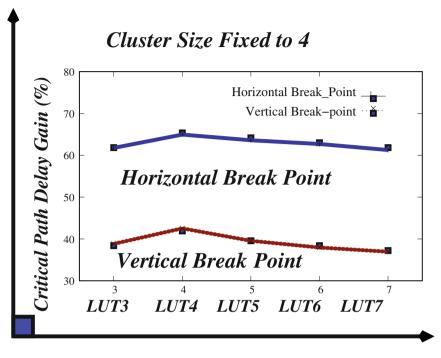

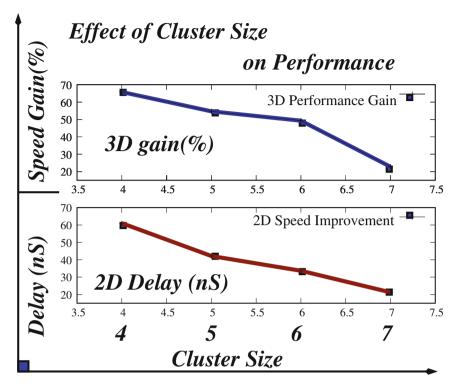

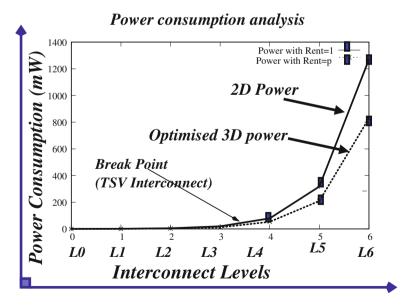

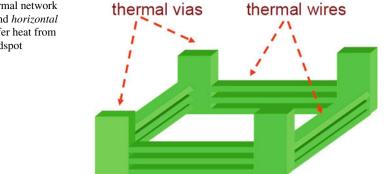

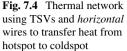

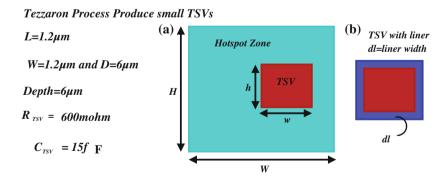

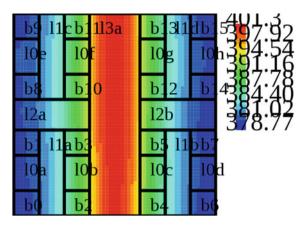

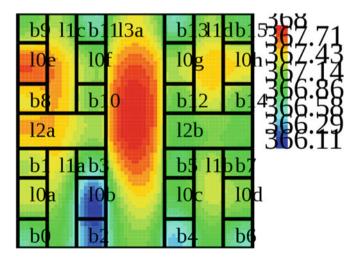

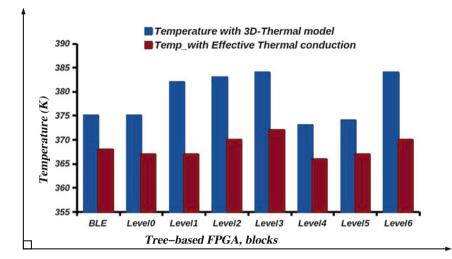

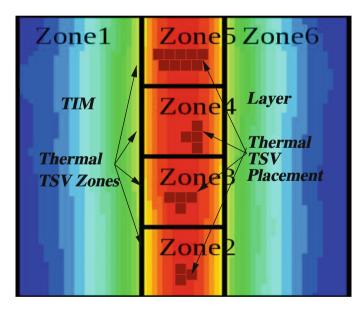

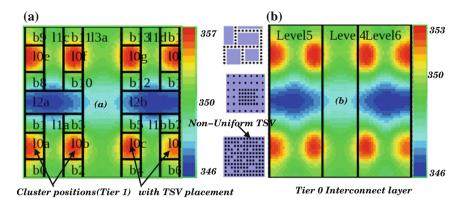

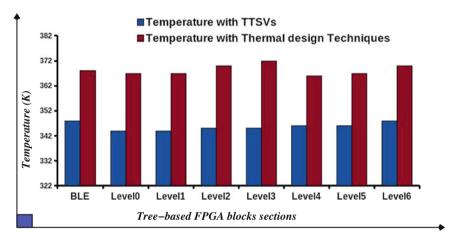

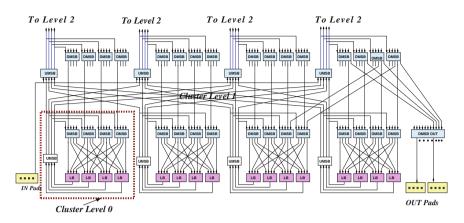

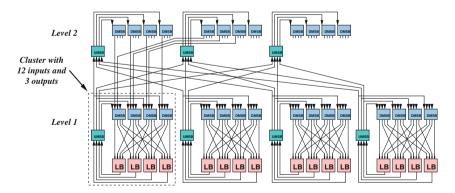

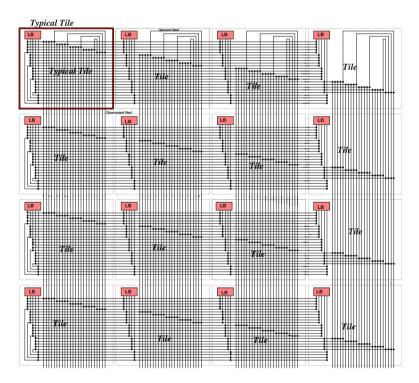

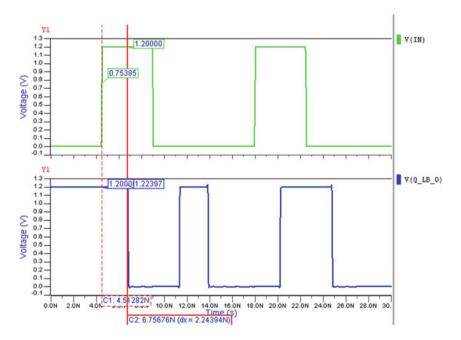

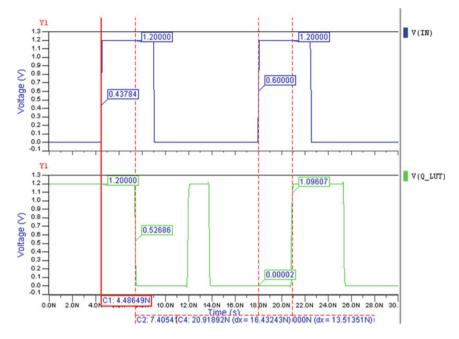

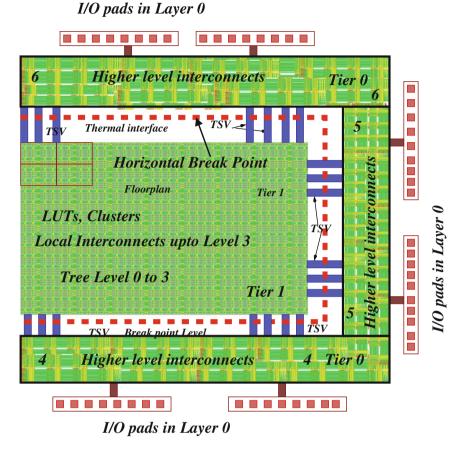

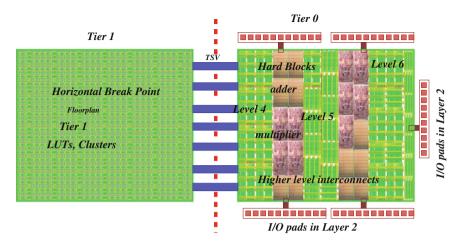

Fig. 2.4 The difference in wire length between 2D Soc and 3D SoC, the wire length between blocks A and C in 2D SoC and 3D SoC