Theory of Digital Automata

# International Series on INTELLIGENT SYSTEMS, CONTROL AND AUTOMATION: SCIENCE AND ENGINEERING

#### VOLUME 63

Editor

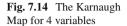

Professor S. G. Tzafestas, National Technical University of Athens, Greece

#### Editorial Advisory Board

Professor P. Antsaklis, University of Notre Dame, Notre Dame, IN, USA

Professor P. Borne, Ecole Centrale de Lille, Lille, France

Professor D.G. Caldwell, University of Salford, Salford, UK

Professor C.S. Chen, University of Akron, Akron, Ohio, USA

Professor T. Fukuda, Nagoya University, Nagoya, Japan

Professor S. Monaco, University La Sapienza, Rome, Italy

Professor G. Schmidt, Technical University of Munich, Munich, Germany

Professor F. Harashima, University of Tokyo, Tokyo, Japan

Professor N.K. Sinha, McMaster University, Hamilton, Ontario, Canada

Professor D. Tabak, George Mason University, Fairfax, Virginia, USA

Professor K. Valavanis, University of Denver, Denver, USA

For further volumes: http://www.springer.com/series/6259 Bohdan Borowik • Mykola Karpinskyy Valery Lahno • Oleksandr Petrov

# Theory of Digital Automata

Bohdan Borowik Department of Electrical Engineering University of Bielsko-Biala Bielsko-Biala, Poland

Valery Lahno Department of Computer Systems and Networks East-Ukrainian National University Luhansk, Ukraine

Reviewer Barbara Borowik Cracow University of Technology/ Faculty of Physics Mathematics and Computer Science Cracow, Poland Mykola Karpinskyy Computer Science Division University of Bielsko-Biala Bielsko-Biala, Poland

Oleksandr Petrov Department of Applied Computer Science AGH University of Science and Technology Krakow, Poland

ISBN 978-94-007-5227-6 ISBN 978-94-007-5228-3 (eBook) DOI 10.1007/978-94-007-5228-3 Springer Dordrecht Heidelberg New York London

Library of Congress Control Number: 2012951321

#### © Springer Science+Business Media Dordrecht 2013

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed. Exempted from this legal reservation are brief excerpts in connection with reviews or scholarly analysis or material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work. Duplication of this publication or parts thereof is permitted only under the provisions of the Copyright Law of the Publisher's location, in its current version, and permission for use must always be obtained from Springer. Permissions for use may be obtained through RightsLink at the Copyright Clearance Center. Violations are liable to prosecution under the respective Copyright Law.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

While the advice and information in this book are believed to be true and accurate at the date of publication, neither the authors nor the editors nor the publisher can accept any legal responsibility for any errors or omissions that may be made. The publisher makes no warranty, express or implied, with respect to the material contained herein.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

# Preface

Communication systems for most companies throughout the world have already gone digital or will certainly do so in the near future. For example, cell phones and other types of wireless communication such as television, radio, process controls, automotive electronics, consumer electronics, global navigation and military systems, to name only a few applications, depend heavily on digital electronics.

This book is designed to serve as a first course in digital automata and digital systems, providing students at the sophomore level a transition from the world of physics to the world of digital electronics and computation.

The book attempts to satisfy two goals: Combine the study of circuits and digital electronics into a single, unified treatment, and establish a strong connection with the contemporary worlds of both these types of digital systems.

These goals arise from the observation that the conventional approach to introducing digital electronics through a course in traditional circuit analysis is fast becoming obsolete. Our world has gone digital. Even those students who remain in core electrical engineering are heavily influenced by the digital domain.

Because of this elevated focus on the digital domain, basic electrical engineering education must change in two ways: First, the traditional approach to teaching circuits and electronics without regard to the digital domain must be replaced by one that stresses the foundations that are common to all circuits in both the digital and analog domains. Because most of the fundamental concepts in circuits and electronics are equally applicable to both the digital and the analog domains, this means that, primarily, we must change the way in which we motivate the study of circuits and electronics to emphasize their broader impact on digital systems.

Second, given the additional demands of computer engineering, many departments can ill-afford the luxury of separate courses on circuits and on electronics. Rather, they might be combined into one course.

The book attempts to form a bridge between the world of logic and the world of large digital systems.

# Contents

| 1 | Digi | tal and  | Analog Quantities                      | 1  |

|---|------|----------|----------------------------------------|----|

|   | 1.1  |          | g and Digital Quantities               | 1  |

|   | 1.2  |          | uring Machine                          | 4  |

| 2 | Nun  | nber Sy  | stems, Operations, and Codes           | 9  |

|   | 2.1  | Numb     | er Systems                             | 9  |

|   |      | 2.1.1    | The Decimal System                     | 9  |

|   |      | 2.1.2    | The Binary System                      | 10 |

|   |      | 2.1.3    | Hexadecimal Notation                   | 11 |

|   |      | 2.1.4    | Binary-Coded Decimal Code              | 12 |

|   | 2.2  | Conve    | rting Between Number Systems           | 13 |

|   |      | 2.2.1    | Converting Between Binary and Decimal  |    |

|   |      |          | (Between Decimal and Binary)           | 13 |

|   |      | 2.2.2    | Integers                               | 13 |

|   |      | 2.2.3    | Fractions                              | 14 |

|   |      | 2.2.4    | Integers                               | 16 |

|   |      | 2.2.5    | Fractions                              | 16 |

|   |      | 2.2.6    | Binary to BCD Conversion               | 18 |

| 3 | Bina | ary Arit | hmetic                                 | 19 |

|   | 3.1  | Binary   | Addition                               | 19 |

|   | 3.2  | Binary   | Subtraction                            | 20 |

|   | 3.3  | Binary   | Multiplication                         | 20 |

|   | 3.4  | Binary   | Division                               | 21 |

|   | 3.5  | BCD A    | Addition                               | 21 |

|   | 3.6  | Arithn   | netic Operations with Signed Numbers   | 22 |

|   |      | 3.6.1    | 1s and 2s Complements Forms            | 22 |

|   |      | 3.6.2    | 1s Complement                          | 23 |

|   |      | 3.6.3    | 2s Complement                          | 23 |

|   |      | 3.6.4    | Additional in the 1s Complement System | 24 |

|   |      | 3.6.5    | Additional in the 2s Complement System | 25 |

|   | 3.7<br>3.8<br>3.9                | BCD Subtraction27BCD Multiplication and Division29Floating-Point Numbers303.9.1 Floating-Point Arithmetic31                                                                                                   |

|---|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4 | Erro<br>4.1<br>4.2<br>4.3<br>4.4 | or Correction in Digital Systems       37         Parity Method for Error Detection       37         Cyclic Redundancy Check (CRC)       37         Reed-Solomon Block       38         Hamming Code       39 |

| 5 | Boo                              | lean Algebra                                                                                                                                                                                                  |

|   | 5.1                              | Laws of Boolean Algebra 46                                                                                                                                                                                    |

|   | 5.2                              | Disjunctive Normal Form                                                                                                                                                                                       |

| 6 | Basi                             | ic Logical Functions and Gates. Logic Design                                                                                                                                                                  |

| - | 6.1                              | Basic Logical Functions and Gates                                                                                                                                                                             |

|   |                                  | 6.1.1 The NOT Gate, or Inverter                                                                                                                                                                               |

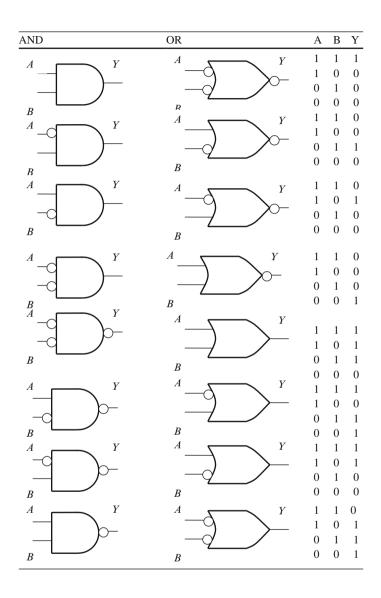

|   |                                  | 6.1.2 The AND Gate                                                                                                                                                                                            |

|   |                                  | 6.1.3 The OR Gate                                                                                                                                                                                             |

|   |                                  | 6.1.4 The NAND Gate                                                                                                                                                                                           |

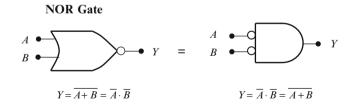

|   |                                  | 6.1.5 The NOR Gate                                                                                                                                                                                            |

|   |                                  | 6.1.6 The Exclusive-OR, or XOR Gate                                                                                                                                                                           |

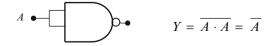

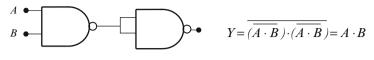

|   | 6.2                              | Universal Gates                                                                                                                                                                                               |

|   | 6.0                              | 6.2.1 Realization of Logic Function Using NOR Gates                                                                                                                                                           |

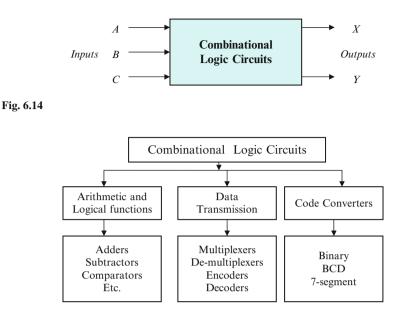

|   | 6.3                              | Combinational Logic Circuits                                                                                                                                                                                  |

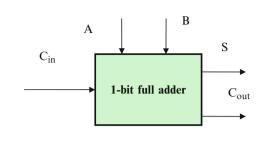

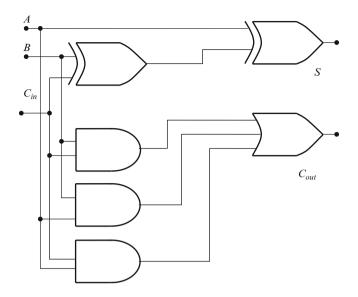

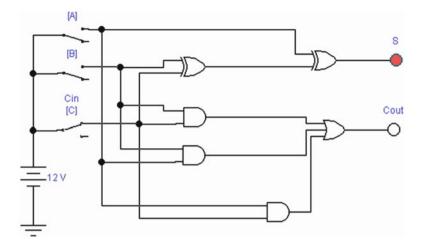

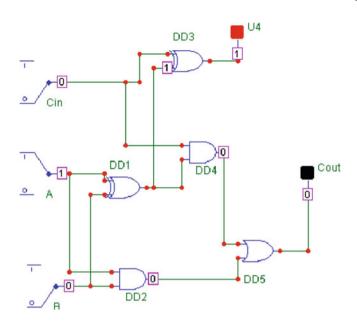

|   | 6.4                              | Full Adder                                                                                                                                                                                                    |

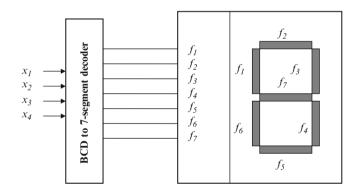

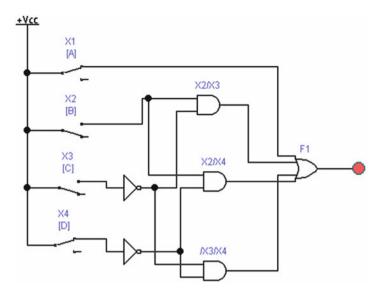

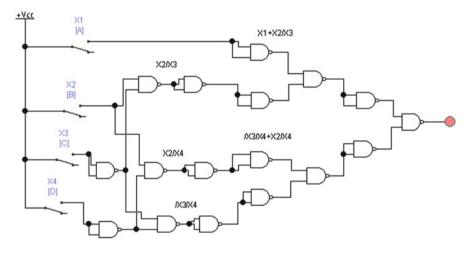

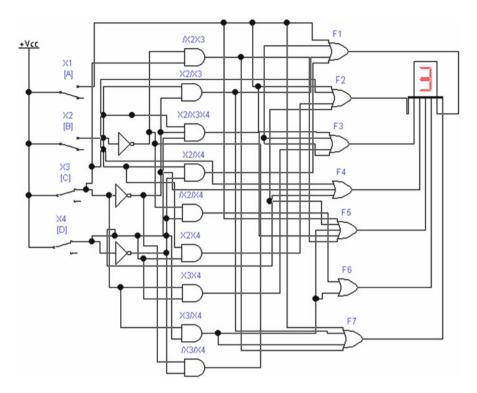

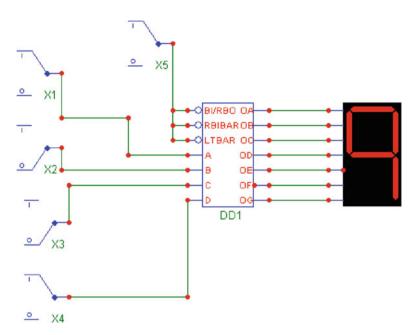

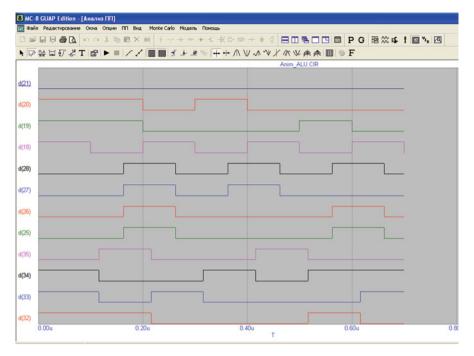

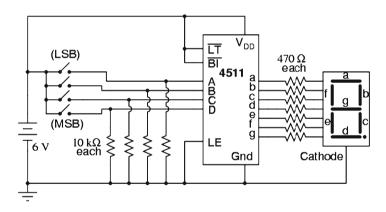

|   | 6.5<br>6.6                       | Seven-Segment Display63Design Combinational Logic Circuits65                                                                                                                                                  |

|   | 6.7                              | Design Combinational Logic Circuits65Evaluating Logic Circuit Outputs71                                                                                                                                       |

|   |                                  |                                                                                                                                                                                                               |

| 7 |                                  | imizing Boolean Functions 75                                                                                                                                                                                  |

|   | 7.1                              | Background and Terminology                                                                                                                                                                                    |

|   | 7.2                              | Karnaugh Maps                                                                                                                                                                                                 |

|   | 7.3                              | On Quine-Mccluskey Method                                                                                                                                                                                     |

| 8 | Late                             | ches, Flip-Flops, Counters, Registers, Timer,                                                                                                                                                                 |

|   | Mul                              | tiplexer, Decoder, Etc                                                                                                                                                                                        |

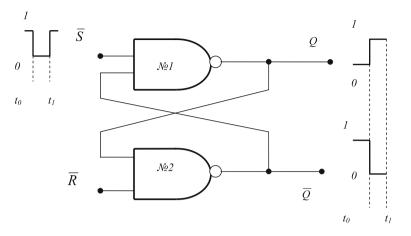

|   | 8.1                              | Latches 101                                                                                                                                                                                                   |

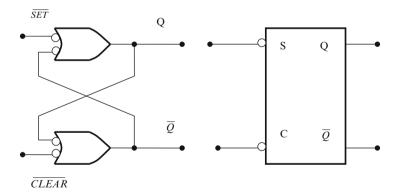

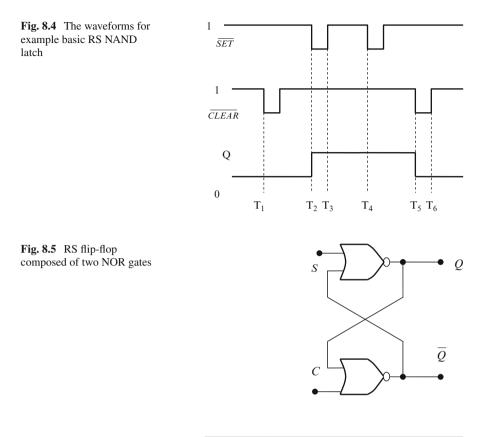

|   |                                  | 8.1.1 The Basic RS NAND Latch 102                                                                                                                                                                             |

|   |                                  | 8.1.2 The Basic RS NOR Latch                                                                                                                                                                                  |

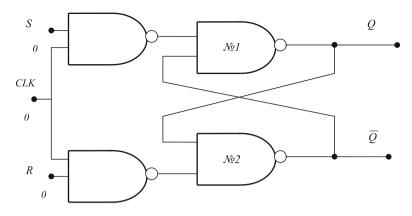

|   | 0.2                              | 8.1.3 The Clocked RS NAND Latch                                                                                                                                                                               |

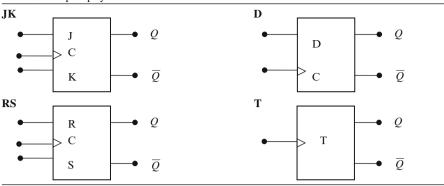

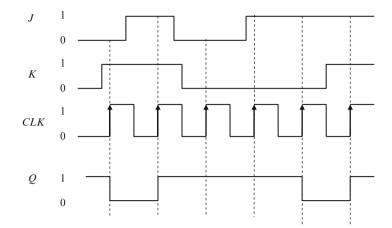

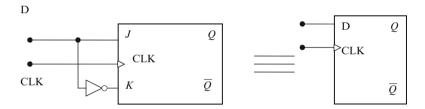

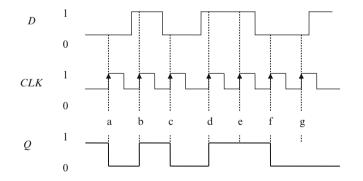

|   | 8.2                              | Edge-Triggered Flip-Flops                                                                                                                                                                                     |

|   |                                  | 8.2.1 Flip-Flop Symbols                                                                                                                                                                                       |

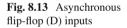

|   |                                  | 8.2.2 Asynchronous Preset and Clear Inputs 109                                                                                                                                                                |

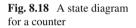

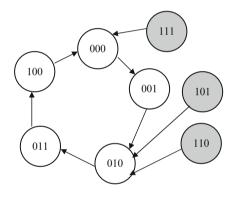

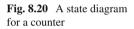

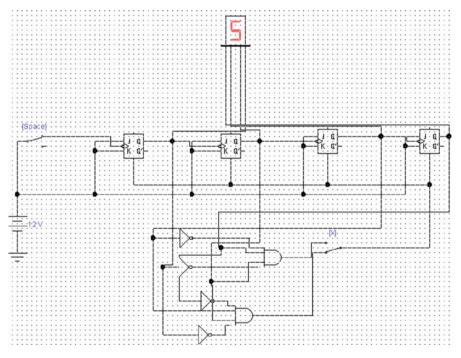

|     | 8.3   | Counte  | ers                                      | 111 |

|-----|-------|---------|------------------------------------------|-----|

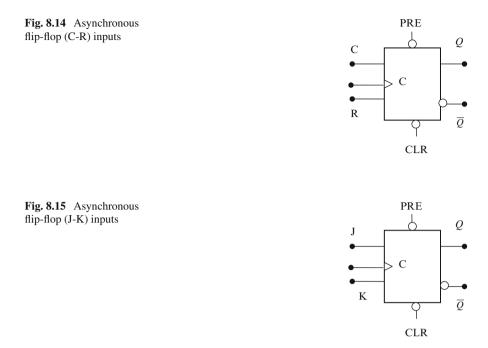

|     |       | 8.3.1   | A Basic Digital Counter                  | 111 |

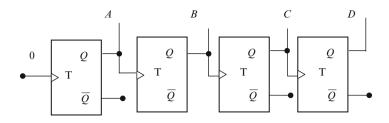

|     |       | 8.3.2   | Synchronous Counter                      | 112 |

|     |       | 8.3.3   | Decimal and Shorter Counts               | 113 |

|     |       | 8.3.4   | BCD Counter                              | 122 |

|     |       | 8.3.5   | The Johnson Counter                      | 123 |

|     | 8.4   | Registe | ers                                      | 125 |

|     |       | 8.4.1   | Serial-to-Parallel Shift Register        | 126 |

|     |       | 8.4.2   | Parallel-to-Serial Shift Register        | 126 |

|     |       | 8.4.3   | Using a Shift Register for Control       | 127 |

|     | 8.5   | Timer.  |                                          | 129 |

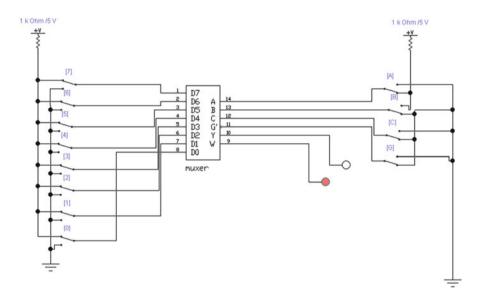

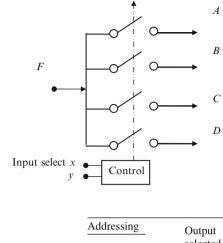

|     | 8.6   | Multip  | lexer and Demultiplexer                  | 132 |

|     |       | 8.6.1   | The Multiplexer.                         | 132 |

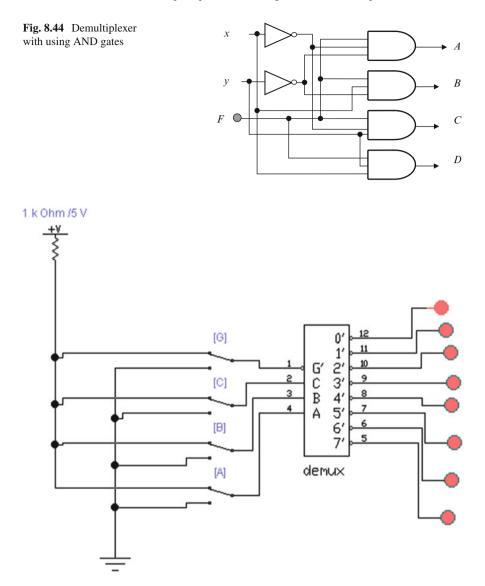

|     |       | 8.6.2   | The Demultiplexer                        | 134 |

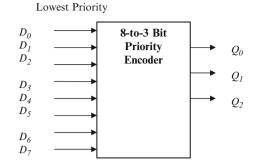

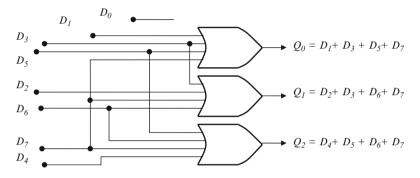

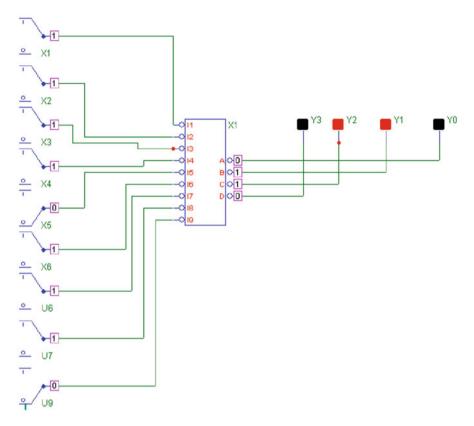

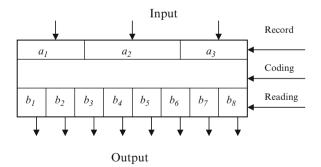

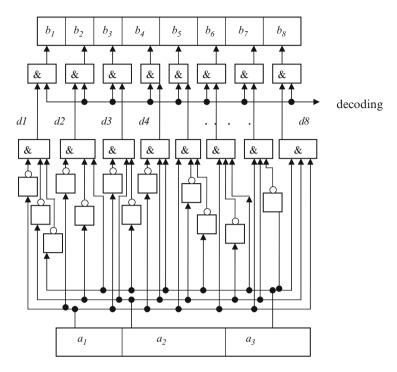

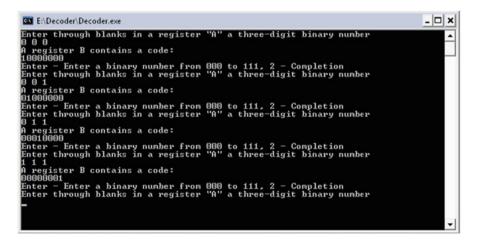

|     | 8.7   | Digital | Encoder and Decoder                      | 136 |

|     |       | 8.7.1   | The Digital Encoder                      | 136 |

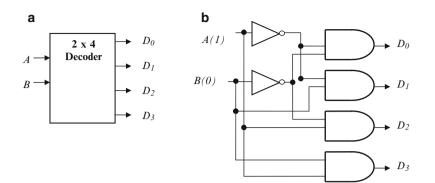

|     |       | 8.7.2   | Decoder                                  | 138 |

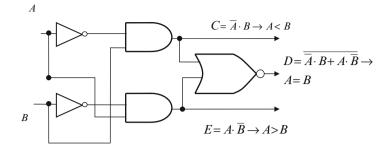

|     | 8.8   | Digital | l Comparator                             | 139 |

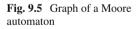

| 9   | Mac   | hines N | Ioore and Mealy                          | 143 |

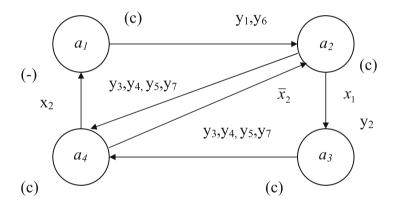

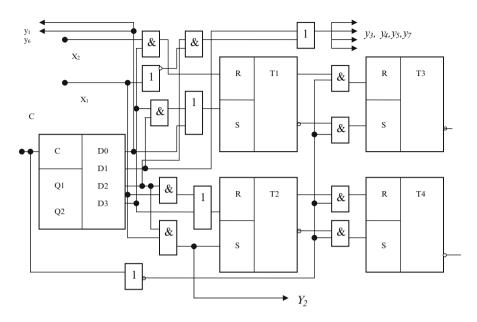

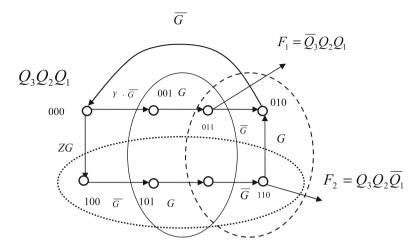

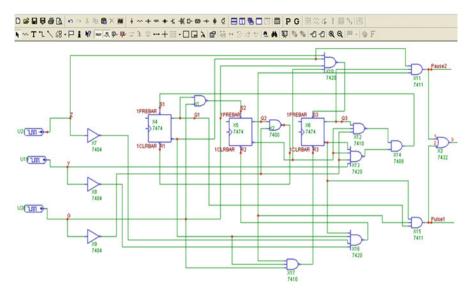

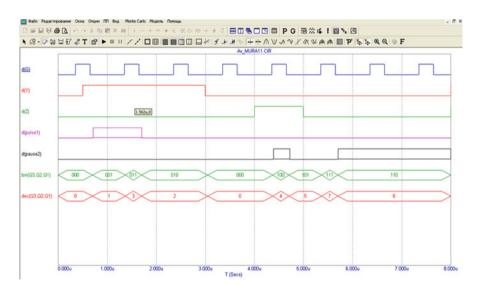

|     | 9.1   | Synthe  | esis of Moore Automata from Graph-Scheme | 143 |

|     | 9.2   |         | rst Version                              | 167 |

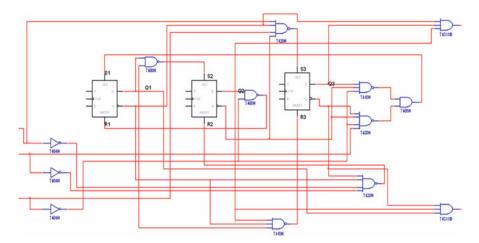

|     | 9.3   |         | econd Version                            | 170 |

|     |       | 9.3.1   | Machine, Implemented in Flip-Flops       |     |

|     |       |         | with Multiplex Controls                  | 170 |

| Ar  | opend | ices    |                                          | 173 |

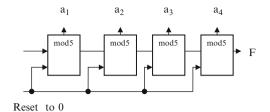

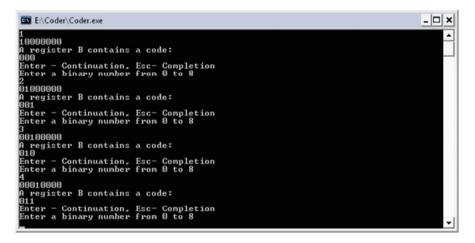

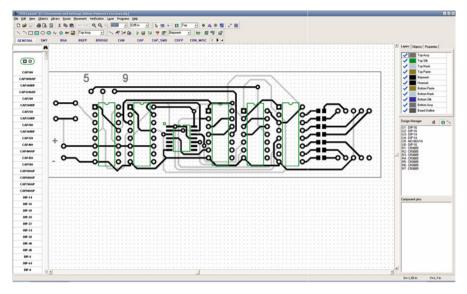

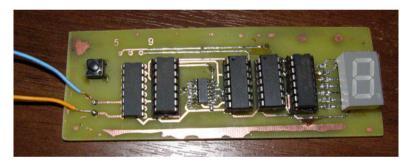

|     |       |         | : Counter Modulo 5                       | 173 |

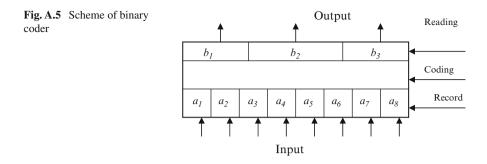

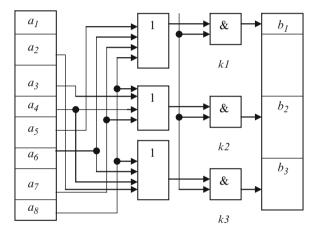

|     |       |         | : Full Adder Circuit                     | 186 |

|     |       |         |                                          | 187 |

|     |       |         | : Logic Symbols, Truth Tables            | 192 |

| Gl  | ossar | y       |                                          | 193 |

| R¢  | feren | ces     |                                          | 203 |

| 170 |       |         |                                          | 205 |

|     |       |         |                                          |     |

# Introduction

Early artificial intelligence theory was concerned with models (automata) used to simulate objects and processes. Automata theory helps with the design of digital circuits such as parts of computers, telephone systems or control systems.

The major advantages for Digital and Microprocessor systems are [1–5]:

- Stability and accuracy of control;

- Flexibility;

- Lower cost per function;

- Greater reliability and equipment life;

- Human factors favouring a Digital Interface.

The most general and versatile circuit that can be placed on a single Chip is the Digital Microprocessor. The Microprocessor is versatile because it can be programmed to perform an almost unlimited number of computing tasks.

#### **Application and Advantages of Digital Systems**

- The device used in a Digital Circuit generally operates in one of the two states, known as ON & OFF, resulting in a very simple operation.

- There are only a few basic operations in a Digital Circuit and they are very easy to understand.

- Digital Technique requires Boolean algebra which is very simple and easily to learn.

- Digital Circuit study requires the basic concept of Electrical Network Analysis, which is also easily learned.

- A large number of Integrated Circuits (IC) are available for performing various operations. They are highly reliable and accurate, with a very high speed of operations.

- Digital Circuits have a wide range of memory capability which makes them highly suitable for Computers, Calculators, and Electronic Watches etc.

- The display of data and other information is very convenient, accurate and elegant using digital techniques.

Many students have, in a wide range of studies, opportunities to learn programming of digital computers, hence they have a strong motivation to study the way digital hardware works.

# Chapter 1 Digital and Analog Quantities

**Abstract** This chapter discusses different digital representations commonly used to represent data. In electronic applications digital representations have certain advantages over analog representations. The chapter introduces also to analog and digital quantities and to Post–Turing machines.

### **1.1 Analog and Digital Quantities**

Electronic circuits can be divided into two broad categories, digital and analog. Digital electronics involves quantities with discrete values, and analog electronics involves quantities with continuous values.

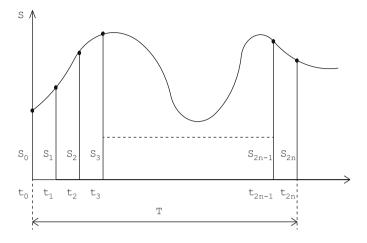

A digital quantity is one having a discrete set of values. Most things that can be measured quantitatively occur in nature in analog form. For example, S(t)=f(t), Fig. 1.1.

Analog and digital quantities – An analog signal is sampled or tested repeatedly over a period of time to determine the characteristic that contains the analog quantity. The sampled analog value is converted to the nearest binary value or quantity. The binary value is then encoded into a character stream acceptable to the digital equipment that is designed to use the data. Standardized binary words called BAMs (binary angular measurement) are used to transmit angular, range, and height values between digital equipment in shipboard combat direction systems. Other coding systems such as Gray code or binary-coded decimal (BCD) are also used to transmit converted values.

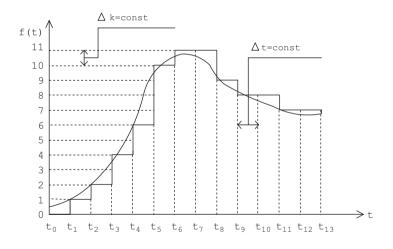

Advantage Digital representation has certain advantages over analog representation in electronics applications. For one thing, digital data can be processed and transmitted more efficiently and reliably than analog data. Also, digital data has a great advantage when storage is necessary. For example, music when converted to digital form can be stored more compactly and reproduced with greater accuracy and clarity than is possible when it is in analog form. Noise (unwanted voltage fluctuations) does not affect digital data nearly as much as it does analog signals, Fig. 1.2.

Fig. 1.1 Quantization of the analog quantity

Fig. 1.2 Digital representation

Sampled-value representation (quantization) of the analog quantity in Fig. 1.1. Each value represented by a dot can be digitized by representing it as a digital code that consists of a series of 1s and 0s:

$$S(t) = \sum_{k=-\infty}^{\infty} S\left(t - k \cdot \Delta t\right) \cdot \frac{\sin\left[2\pi \cdot F_m \cdot \left(t - k \cdot \Delta t\right)\right]}{2\pi \cdot F_m \cdot \left(t - k \cdot \Delta t\right)},$$

where  $k = (f_{max} - f_{min})/(q-1)$ ;  $\Delta t = 1/(2F_m)$  - step quantization; q - number step quantization;  $t_k = k/2 \cdot F_m = k \cdot \Delta t$ .

|                                              | Analog signals                                                                                                                                           | Digital signals                                                                                                                               |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Technology                                   | Analog technology records waveforms as they are.                                                                                                         | Converts analog waveforms<br>into set of numbers and<br>records them. The numbers<br>are converted into voltage<br>stream for representation. |

| Representation analog<br>and digital signals | Uses continuous range of values to represent information.                                                                                                | Uses discrete or discontinuous values to represent information.                                                                               |

| Uses analog<br>and digital signals           | Can be used in various computing<br>platforms and under operating<br>systems.                                                                            | Computing and electronics technology.                                                                                                         |

| Computer                                     | Analog computer uses changeable<br>continuous physical phenomena<br>such as electrical, mechanical,<br>hydraulic quantities so as to<br>solve a problem. | Digital computers represent<br>changing quantities<br>incrementally as and when<br>their values change.                                       |

Table 1.1 Analog versus digital quantities

Analog and digital signals are used to transmit information, usually through electric signals. In both these technologies, the information, such as any audio or video, is transformed into electric signals. The difference between analog and digital technologies is that in analog technology, information is translated into electric pulses of varying amplitude. In digital technology, translation of information is into binary format (0 or 1) where each bit is representative of two distinct amplitudes, see Table 1.1 [4–6].

All digital information possesses common properties that distinguish it from analog communications methods [1, 4]:

**Synchronization**: Since digital information is conveyed by the sequence in which symbols are ordered, all digital schemes have some method for determining the beginning of a sequence.

**Language**: All digital communications require a language, which in this context consists of all the information that the sender and receiver of the digital communication must both possess, in advance, in order for the communication to be successful.

**Errors**: Disturbances (noise) in analog communications invariably introduce some, generally small, deviation or error between the intended and actual communication. Disturbances in a digital communication do not result in errors unless the disturbance is so large as to result in a symbol being misinterpreted as another symbol or disturb the sequence of symbols. It is therefore generally possible to have an entirely error-free digital communication. Further, techniques such as check codes may be used to detect errors and guarantee error-free communications through redundancy or retransmission. Errors in digital communications can take the form of substitution errors in which a symbol is replaced by another symbol, or insertion/deletion errors in which an extra incorrect symbol is inserted into or

deleted from a digital message. Uncorrected errors in digital communications have unpredictable and generally large impact on the information content of the communication.

**Granularity**: When a continuously variable analog value is represented in digital form there is always a decision as to the number of symbols to be assigned to that value. The number of symbols determines the precision or resolution of the resulting datum. The difference between the actual analog value and the digital representation is known as quantization error.

**Copying**: Because of the inevitable presence of noise, making many successive copies of an analog communication is infeasible because each generation increases the noise. Because digital communications are generally error-free, copies of copies can be made indefinitely.

### **1.2 Post-turing Machine**

Although digital signals are generally associated with the binary electronic digital systems used in modern electronics and computing, digital systems are actually ancient, and need be neither binary nor electronic.

A beacon is perhaps the simplest non-electronic digital signal, with just two states (on and off). In particular, smoke signals are one of the oldest examples of a digital signal, where an analog "carrier" (smoke) is modulated with a blanket to generate a digital signal (puffs) that conveys information.

More recently invented, a modem modulates an analog "carrier" signal (such as sound) to encode binary electrical digital information, as a series of binary digital sound pulses. A slightly earlier, surprisingly reliable version of the same concept was to bundle a sequence of audio digital "signal" and "no signal" information (i.e. "sound" and "silence") on magnetic cassette tape for use with early home computers.

In 1936 Alan Mathison Turing gave his answer to the question "What is a computable number?" by constructing his now well-known Turing machines as formalizations of the actions of a human computer. Less well-known is the almost synchronously published result by Emil Leon Post, in which a quasi-identical mechanism was developed for similar purposes.

A post-turing machine uses a binary alphabet, an infinite sequence of binary storage locations, and a primitive programming language with instructions for bi-directional movement among the storage locations and alteration of their contents one at a time.

The instructions may require the worker to perform the following "basic acts" or "operations":

- Marking the box he is in (assumed empty);

- Erasing the mark in the box he is in (assumed marked);

- Moving to the box on his right;

Fig. 1.3 Machine E.L. Post

- Moving to the box on his left;

- Determining whether the box he is in, is or is not marked.

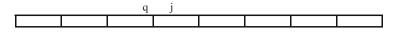

In the hypothetical machine E.L. Post, information is represented in a binary alphabet  $A = \{0,1\}$ . The machine has an informational tape of unlimited length – the machine memory. Each cell can hold **0** or **1**. The machine has a "read head" (special sensor), which examines the contents of the cell (*j*), Fig. 1.3.

An informational tape can move in both directions, so that each move places the head in front of a particular cell.

The machine has a control unit, which at any one time is in a particular state -q. Tape is moved discretely so the head would stop in front of the cell.

Instruction set of the abstract machine:

- 1. Head to move to the right;

- 2. Head to move to the left;

- 3. Record label;

- 4. To erase the label;

- 5. To transfer control;

- 6. Stop.

For example, because the program looks for the hypothetical machine E.L. Post:

| Move the control unit        | Command number, i | Reference number, u |                   |

|------------------------------|-------------------|---------------------|-------------------|

| right, 1 step                | 1                 | 3                   | run i No 3        |

| right, 1 step                | 2                 | 4                   | run <i>i</i> No 4 |

| Record label                 | 3                 | 2                   | run <i>i</i> No 2 |

| The command transfer control | 4                 | 5                   |                   |

| Stop                         |                   |                     |                   |

Each command is executed in one step, after which the command whose number is indicated in the *u*.

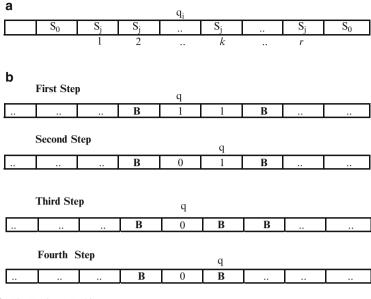

The Turing Machine differs from the Post machine in that the alphabet may have more than two characters, Fig. 1.4.

Each square of the tape holds exactly one of the symbols, also called input symbols or machine characters. It is assumed that one of the input symbols is a special one, the blank, denoted by  $\mathbf{B}$ .

At any moment of time, the machine, being in one of its states and looking at one of the input symbols in some square, may act or halt. The action means that, in the next moment of time, the machine erases the old input symbol and writes a new input symbol on the same square (it may be the same symbol as before, or a new symbol; if the old one was not  $\mathbf{B}$  and the new one is  $\mathbf{B}$ , the machine is said to erase

Fig. 1.4 The Turing Machine

| Table 1.2   Turing machine program |   |                           |           |           |                |  |  |  |

|------------------------------------|---|---------------------------|-----------|-----------|----------------|--|--|--|

|                                    | А | 0                         | 1         | *         | S <sub>0</sub> |  |  |  |

| Q                                  |   | <u> </u>                  |           |           | 0              |  |  |  |

| $q_2$                              |   | _                         | $q_2 0 L$ | $q_1 * L$ | $Q_0 S$        |  |  |  |

| $q_1$                              |   | q <sub>2</sub> 1L<br>Stop | -         | -         | -              |  |  |  |

| $\underline{q}_0$                  |   | Stop                      |           |           |                |  |  |  |

the old symbol), changes the state to a new one (again, it is possible that the new state will be equal to the old one), and finally moves the head one square to the left, or one square to the right, or stays on the same square as before.

where:

$S_0$  – an empty cell;

$S_{j1}^{0}$  – state (content) of the first non-empty left cell;  $S_{jk}^{0}$  – state of the cell, which was seen at a given time;

r – The number of occupied cells;

$q_i$  – state control device,  $i=0,1,\ldots,m$ .

A Turing machine program can be defined as a table (Table 1.2). Assume that the initial configuration of the machine has the form:  $s_0 q_2 1 * 0 s_0$ . Then

| $q_1 1 \rightarrow q_2 0 \Pi$              | $s_0 0 q_2 * 0 s_0$       |                         |

|--------------------------------------------|---------------------------|-------------------------|

| $q_2^* \rightarrow q_1^* \Pi$              | $s_0 0 * q_1 0 s_0$       |                         |

| $q_1^{}  0 \!\rightarrow\! q_1^{}  1  \Pi$ | $s_0 0 * 1 q_2 s_0$       |                         |

| $q_2 s_0 \rightarrow q_0 s_0 C$            | $s_0^0 0 * 1 q_0^0 s_0^0$ | The final configuration |

|                                            |                           | of the machine          |

#### 1.2 Post-turing Machine

For some pairs of states and input symbols the action is not specified in the description of a Turing machine; thus the machine halts. In this case, symbols remaining on the tape form the output, corresponding to the original input, or more precisely, to the input string (or sequence) of input symbols. A sequence of actions, followed by a halt, is called a computation. A Turing machine accepts some input string if it halts on it. The set of all accepted strings over all the input symbols is called a language accepted by the Turing machine. Such languages are called recursively enumerable sets.

Another automaton is a nondeterministic Turing machine. It differs from an ordinary, deterministic Turing machine in that for a given state and input symbol, the machine has a finite number of choices for the next move. Each choice means a new input symbol, a new state, and a new direction to move its head.

A linear bounded automaton is a nondeterministic Turing machine which is restricted to the portion of the tape containing the input. The capability of the linear bounded automaton is smaller than that of a Turing machine.

# Chapter 2 Number Systems, Operations, and Codes

**Abstract** In this chapter various number systems and conversions between them are presented and explained. The number systems concerned here are: the decimal system, the binary system, the hexadecimal system and the binary-coded decimal (BCD) code (i.e. an encoding for decimal numbers, in which each digit is represented by its own binary sequence to allow easier conversion to decimal digits and faster decimal calculations). The chapter, besides providing examples explaining conversions of whole numbers also shows the way of converting binary fractions to decimal ones (and opposite).

#### 2.1 Number Systems

Convenient as the decimal number system generally is, its usefulness in machine computation is limited because of the nature of practical electronic devices. In most present digital machines, the numbers are represented, and the arithmetic operations performed, in a different number system called the binary number system. This chapter will help you more easily understand the structure of the binary number system, which is important in computers and digital electronics.

#### 2.1.1 The Decimal System

In everyday life we use a system based on decimal digits (0, 1, 2, 3, 4, 5, 6, 7, 8, 9) to represent numbers and refer to the system as the decimal system. Consider what the number 62 means. It means six tens plus two:

$$62 = (6 \cdot 10) + 2.$$

The number 2678 means two thousands, six hundreds, seven tens, plus eight:

$$2678 = (2 \cdot 1000) + (6 \cdot 100) + (7 \cdot 10) + 8.$$

The decimal system is said to have a **base**, or **radix**, of 10. This means that each digit in the number is multiplied by 10 raised to a power corresponding to that digit's position:

$$62 = (6 \cdot 10^{1}) + (2 \cdot 10^{0});$$

$$2678 = (2 \cdot 10^{3}) + (6 \cdot 10^{2}) + (7 \cdot 10^{1}) + (8 \cdot 10^{0}).$$

*Example*: *A* = 123,45.

$$A = 1 \cdot 10^{2} + 2 \cdot 10^{1} + 3 \cdot 10^{0} + 4 \cdot 10^{-1} + 5 \cdot 10^{-2},$$

$$A = 1964, 52_{10} = 1 \cdot 10^3 + 9 \cdot 10^2 + 6 \cdot 10^1 + 4 \cdot 10^0 + 5 \cdot 10^{-1} + 2 \cdot 10^{-2}.$$

In general, for the decimal representation of  $A = \{ \dots d_2 d_1 d_0 \cdot d_{-1} d_{-2} d_{-3} \dots \}$ , the value of A is

$$A = \sum_{i} d_i \cdot 10^i$$

#### 2.1.2 The Binary System

In the decimal system, 10 different digits are used to represent numbers with a base of 10. In the binary system, we have only two digits, 1 and 0. Thus, numbers in the binary system are represented to the base 2.

The binary numeral system, or base-2 number system, represents numeric values using two symbols, 0 and 1. Owing to its straightforward implementation in digital electronic circuitry using logic gates, the binary system is used internally by all modern computers.

The digits 1 and 0 in binary notation have the same meaning as in decimal notation:

$$0_2 = 0_{10}$$

$1_2 = 1_{10}$

To represent larger numbers, as with decimal notation, each digit in a binary number has a value depending on its position:

$$10_{2} = (1 \cdot 2^{1}) + (0 \cdot 2^{0}) = 2_{10};$$

$$11_{2} = (1 \cdot 2^{1}) + (0 \cdot 2^{0}) = 3_{10};$$

$$100_{2} = (1 \cdot 2^{2}) + (0 \cdot 2^{1}) + (0 \cdot 2^{1}) = 4_{10}.$$

#### 2.1 Number Systems

| Decimal | Binary | Hexadecimal | Decimal | Binary | Hexadecimal | Decimal | Binary | Hexadecimal |

|---------|--------|-------------|---------|--------|-------------|---------|--------|-------------|

| 0       | 0      | 0           | 11      | 1011   | В           | 22      | 10110  | 16          |

| 1       | 1      | 1           | 12      | 1100   | С           | 23      | 10111  | 17          |

| 2       | 10     | 2           | 13      | 1101   | D           | 24      | 11000  | 18          |

| 3       | 11     | 3           | 14      | 1110   | Е           | 25      | 11001  | 19          |

| 4       | 100    | 4           | 15      | 1111   | F           | 26      | 11010  | 1A          |

| 5       | 101    | 5           | 16      | 10000  | 10          | 27      | 11011  | 1B          |

| 6       | 110    | 6           | 17      | 10001  | 11          | 28      | 11100  | 1C          |

| 7       | 111    | 7           | 18      | 10010  | 12          | 29      | 11101  | 1D          |

| 8       | 1000   | 8           | 19      | 10011  | 13          | 30      | 11110  | 1E          |

| 9       | 1001   | 9           | 20      | 10100  | 14          | 31      | 11111  | 1F          |

| 10      | 1010   | А           | 21      | 10101  | 15          | 32      | 100000 | 20          |

Table 2.1 Decimal Binary and Hexadecimal numbers system

and so on. Again, fractional values are represented with negative powers of the radix:

$$1001, 1101_{2} = 1 \cdot 2^{3} + 0 \cdot 2^{2} + 0 \cdot 2^{1} + 1 \cdot 2^{0} + 1 \cdot 2^{-1} + 1 \cdot 2^{-2} + 0 \cdot 2^{-3} + 1 \cdot 2^{-4}.$$

In general, for the binary representation of  $B = \{\dots b_2 b_1 b_0 \cdot b_{-1} b_{-2} b_{-3} \dots\}$ , the value of *B* is

$$B = \sum_{i} b_i \cdot 2^i.$$

#### 2.1.3 Hexadecimal Notation

Because of the inherent binary nature of digital computer components, all forms of data within computers are represented by various binary codes. However, no matter how convenient the binary system is for computers, it is exceedingly cumbersome for human beings. Consequently, most computer professionals who must spend time working with the actual raw data in the computer prefer a more compact notation.

What notation to use? One possibility is the decimal notation. This is certainly more compact than binary notation, but it is awkward because of the tediousness of converting between base 2 and base 10.

Instead, a notation known as hexadecimal has been adopted. Binary digits are grouped into sets of four. Each possible combination of four binary digits is given a symbol, as follows (Table 2.1):

Because 16 symbols are used, the notation is called **hexadecimal**, and the 16 symbols are the hexadecimal digits.

A sequence of hexadecimal digits can be thought of as representing an integer in base 16.

Thus,

$$2C_{16} = (2_{16} \cdot 16^{1}) + (C_{16} \cdot 16^{0}) = (2_{10} \cdot 16^{1}) + (2_{10} \cdot 16^{0}) = 44.$$

| Symbols<br>ANCII | Decimal code | Binary code | Hexadecimal code |

|------------------|--------------|-------------|------------------|

| 0                | 48           | 0110000     | 30               |

| 1                | 49           | 0110001     | 31               |

| 2                | 50           | 0110010     | 32               |

| А                | 65           | 1000001     | 41               |

| В                | 66           | 1000010     | 42               |

| F                | 70           | 1000110     | 46               |

| :                | 58           | 0111010     | 3F               |

| (                | 40           | 0101000     | 28               |

Table 2.2 ANCII, Decimal, Binary and Hexadecimal code

Each hexadecimal digit represents four binary digits (bits). For example, byte values can range from 0 to 255 (decimal) but may be more conveniently represented as two hexadecimal digits in the range 00 through FF. Hexadecimal is also commonly used to represent computer memory addresses.

Hexadecimal notation is used not only for representing integers. It is also used as a concise notation for representing any sequence of binary digits, whether they represent text, numbers, or some other type of data, Table 2.1. The reasons for using hexadecimal notation are:

- It is more compact than binary notation.

- In most computers, binary data occupy some multiple of four bits, and hence some multiple of a single hexadecimal digit.

- It is extremely easy to convert between binary and hexadecimal (Table 2.2).

#### 2.1.4 Binary-Coded Decimal Code

In computing and electronic systems, binary-coded decimal (BCD) or, in its most common modern implementation, packed decimal, is an encoding for decimal numbers in which each digit is represented by its own binary sequence. Its main virtue is that it allows easy conversion to decimal digits for printing or display, and allows faster decimal calculations. Its drawbacks are a small increase in the complexity of circuits needed to implement mathematical operations. Uncompressed BCD is also a relatively inefficient encoding -it occupies more space than a purely binary representation.

In BCD, a digit is usually represented by four bits which, in general, represent the decimal digits 0 through 9. Other bit combinations are sometimes used for a sign or for other indications (e.g., error or overflow). To encode a decimal number using the common BCD encoding, each decimal digit is stored in a 4-bit nibble, Table 2.3.

| Decimal | BCD  | Decimal | BCD       | Decimal | BCD       |

|---------|------|---------|-----------|---------|-----------|

| 0       | 0000 | 10      | 0001 0000 | 20      | 0010 0000 |

| 1       | 0001 | 11      | 0001 0001 | 21      | 0010 0001 |

| 2       | 0010 | 12      | 0001 0010 | 22      | 0010 0010 |

| 3       | 0011 | 13      | 0001 0011 | 33      | 0011 0011 |

| 4       | 0100 | 14      | 0001 0100 | 34      | 0011 0100 |

| 5       | 0101 | 15      | 0001 0101 | 45      | 0100 0101 |

| 6       | 0110 | 16      | 0001 0110 | 56      | 0101 0110 |

| 7       | 0111 | 17      | 0001 0111 | 67      | 0110 0111 |

| 8       | 1000 | 18      | 0001 1000 | 78      | 0111 1000 |

| 9       | 1001 | 19      | 0001 1001 | 89      | 1000 1001 |

Table 2.3 Examples of binary-coded decimal code

Although uncompressed BCD is not as widely used as it once was, decimal fixed-point and floating-point are still important and continue to be used in financial, commercial, and industrial computing.

## 2.2 Converting Between Number Systems

## 2.2.1 Converting Between Binary and Decimal (Between Decimal and Binary)

It is a simple matter to convert a number from binary notation to decimal notation. In fact, we showed several examples in the previous subsection. All that is required is to multiply each binary digit by the appropriate power of 2 and add the results.

To convert from decimal to binary, the integer and fractional parts are handled separately.

#### 2.2.2 Integers

For the integer part, recall that in binary notation, an integer is represented by

$$b_{m-1}b_{m-2}\dots b_2b_1b_0$$

$b_i = 0$  or 1.

Suppose it is required to convert a decimal integer A into binary form. If we divide A by 2, in the decimal system, and obtain a quotient  $A_1$  and a remainder  $R_0$ , we may write

$$A = 2 \cdot A_1 + R_0$$

$R_0 = 0$  or 1

Next, we divide the quotient  $A_1$  by 2. Assume that the new quotient is  $A_2$  and the new remainder  $R_1$ . Then

$$A_1 = 2 \cdot A_2 + R_1$$

$R_1 = 0$  or 1

so that

$$A = 2 \cdot (2 \cdot A_2 + R_1) + R_0 = (A_2 \cdot 2^2) + (R_1 \cdot 2^1) + R_0.$$

If next,

$$A_2 = 2 \cdot A_3 + R_2.$$

Because  $A > A_1 > A_2 > \cdots$ , continuing this sequence will eventually produce a quotient  $A_{m-1} = 1$  (except for the decimal integers 0 and 1, whose binary equivalents are 0 and 1, respectively) and a remainder  $R_{m-2}$ , which is 0 or 1. Then

$$A = (1 \cdot 2^{m-1}) + (R_{m-2} \cdot 2^{m-2}) + \dots + (R_2 \cdot 2^2) + (R_1 \cdot 2^1) + R_0$$

which is the binary form of A. Hence, we convert from base 10 to base 2 by repeated divisions by 2. The remainders and the final quotient, 1, give us, in order of increasing significance, the binary digits of A.

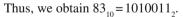

*Example*. Example of Converting from Decimal Notation to Binary Notation for Integers

#### 2.2.3 Fractions

For the fractional part, recall that in binary notation, a number with a value between 0 and 1 is represented by

$$0.b_{-1}b_{-2}b_{-3}\dots b_{-m}$$

$b_{i} = 0$  or 1

and has the value

$$(b_{-1} \cdot 2^{-1}) + (b_{-2} \cdot 2^{-2}) + (b_{-3} \cdot 2^{-3}) + \dots + (b_{-m} \cdot 2^{-m})$$

This can be rewritten as

$$2^{-1} \cdot (b_{-1} + 2^{-1} \cdot (b_{-2} + 2^{-1} \cdot (b_{-3} + 2^{-1} \cdot (\dots + 2^{-1} \cdot (b_{-m+1} + 2^{-1} \cdot b_{-m}) \dots))))$$

This expression suggests a technique for conversion. Suppose we want to convert the number F (0<F<1) from decimal to binary notation. We know that F can be expressed in the form

$$F = 2^{-1} \cdot (b_{-1} + 2^{-1} \cdot (b_{-2} + 2^{-1} \cdot (b_{-3} + 2^{-1} \cdot (\dots + 2^{-1} \cdot (b_{-m+1} + 2^{-1} b_{-m}) \dots))))$$

We can say that  $(2 \cdot F) = b_{-1} + F_1$ , where  $0 < F_1 < I$  and where

$$\mathbf{F}_{1} = 2^{-1} \cdot (b_{-2} + 2^{-1} \cdot (b_{-3} + 2^{-1} \cdot (\dots + 2^{-1} \cdot (b_{-m+1} + 2^{-1} b_{-m}) \dots)))$$

To find  $b_{-2}$ , we repeat the process. Therefore, the conversion algorithm involves repeated multiplication by 2. At each step, the fractional part of the number from the previous step is multiplied by 2. The digit to the left of the decimal point in the product will be 0 or 1 and contributes to the binary representation, starting with the most significant digit. The fractional part of the product is used as the multiplicand in the next step.

*Example*. Example of converting from decimal notation to binary notation for fractions

| x0,3125                |

|------------------------|

| x0,6250                |

| $\frac{2}{x^{1,2500}}$ |

| $\frac{2}{x^{0,5000}}$ |

| 1,0000                 |

|                        |

Thus, we obtain  $0,3125_{10} = 0,0101_2$ .

This process is not necessarily exact; that is, a decimal fraction with a finite number of digits may require a binary fraction with an infinite number of digits. In such cases, the conversion algorithm is usually halted after a prespecified number of steps, depending on the desired accuracy.

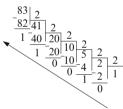

**Example.** Convert number 118, 376<sub>10</sub> from decimal code in binary code.

## 2.2.4 Integers

Thus, we obtain  $118_{10} = 1110110_2$ .

#### 2.2.5 Fractions

$$\begin{array}{c} 0, \ 376_{10} \\ \underline{x} \\ 2 \\ 0, \ 752_{10} \\ \underline{x} \\ 1, \ 504_{10} \\ \underline{x} \\ 2 \\ 1, \ 008_{10} \end{array}$$

Thus, we obtain  $0.376_{10} \approx 0.011_2$ . The final result 118,  $376_{10} \approx 1110110.011_2$ .

*Example*. Example of converting from binary notation to decimal notation for integers

$$100111 = 1 \cdot 2^5 + 0 \cdot 2^4 + 0 \cdot 2^3 + 1 \cdot 2^2 + 1 \cdot 2^1 + 1 \cdot 2^0 = 32 + 4 + 2 + 1 = 39.$$

Example. Example of converting from binary notation to decimal notation

$$1011,01101 = 1 \cdot 2^{3} + 0 \cdot 2^{2} + 1 \cdot 2^{1} + 1 \cdot 2^{0} + 0 \cdot 2^{-1} + 1 \cdot 2^{-2} + 1 \cdot 2^{-3} + 0 \cdot 2^{-4} + 1 \cdot 2^{-5}$$

$$= 8 + 2 + 1 + \frac{1}{4} + \frac{1}{8} + \frac{1}{32} = 11\frac{13}{32}.$$

The decimal value of any binary number can be found by adding the weights of all bits that are 1 and discarding the weights of all bits that are 0.

Example. Convert the binary whole number 10111010 to decimal.

In order to represent the 10 decimal digits 0, 1,..., 9, it is necessary to use at least 4 binary digits. Since there are 16 combinations of 4 binary digits, of which 10 combinations are used, it is possible to form a very large number of distinct codes.

| Weight:         | 1     | 2     | 3     | 4     | 5     | 6     | 7     | 8     | 9     |

|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| 1               | 1     | 2     | 3     | 4     | 5     | 6     | 7     | 8     | 9     |

| 10              | А     | 14    | 1E    | 28    | 32    | 3C    | 46    | 50    | 5A    |

| 10 <sup>2</sup> | 64    | C8    | 12C   | 190   | 1F4   | 258   | 2BC   | 320   | 384   |

| 10 <sup>3</sup> | 3E8   | 7D0   | BB8   | FA0   | 1388  | 1770  | 1B58  | 1F40  | 2328  |

| $10^{4}$        | 2710  | 4E20  | 7530  | 9C40  | C350  | EA60  | 11170 | 13880 | 15F90 |

| 105             | 186A0 | 30D40 | 493E0 | 61A80 | 7A120 | 927C0 | AAE60 | C3500 | DBBA0 |

Table 2.4

*Example*:  $1234 = 1000 + 200 + 30 + 4 = (3E8)_{16} + (C8)_{16} + (1E)_{16} + (4)_{16} = (4D2)_{16}$

Of particular importance is the class of weighted codes, whose main characteristic is that each binary digit is assigned a decimal "weight," and, for each group of four bits, the sum of the weights of those binary digits whose value is 1 is equal to the decimal digit which they represent.

| Binary number: | 1   | 0       | 1  | 1       | 1              | 0              | 1  | 0       |

|----------------|-----|---------|----|---------|----------------|----------------|----|---------|

| Weight:        | 27  | $2^{6}$ | 25 | $2^{4}$ | 2 <sup>3</sup> | 2 <sup>2</sup> | 21 | $2^{0}$ |

| Result         | 128 | 0       | 32 | 16      | 8              | 0              |    |         |

Thus, we obtain 128 + 0 + 32 + 16 + 8 + 0 + 2 + 0 = 186.

$Result - 10111010_2 = 186_{10}$ .

**Converting between Decimal (Binary) code and hexadecimal code** (Table 2.4)

*Example*. Hexadecimal number 9F2<sub>16</sub> converted in Binary code:

| 9    | F    | 2    |

|------|------|------|

| Ļ    | Ļ    | Ļ    |

| 1001 | 1111 | 0010 |

Thus, we obtain  $9F2_{16} = 100111110010_2$ .

*Example*. Hexadecimal number IFA,C24<sub>16</sub> converted in Binary code:

| Ι    | F    | А,    | С    | 2    | 4    |

|------|------|-------|------|------|------|

| Ļ    | Ļ    | ↓ Î   | Ļ    | Ļ    | Ļ    |

| 0001 | 1111 | 1010, | 1100 | 0010 | 0100 |

Thus, we obtain IFA,  $C24_{16} = 111111010, 110000100100_2$ .

Example. Binary number 10110110001101, converted in Hexadecimal code:

$10110110001101_2 = 0010 1101 1000 1101 = 2D8D_{16}$

#### 2.2.6 Binary to BCD Conversion

The basic idea is to shift data serially into a shift register. As each bit is shifted in, the accumulated sum is collected. Each shift effectively doubles the value of the binary number in the four-bit shift register which is going to hold the converted BCD digit.

Each time a bit is shifted in, the value in the shift register is doubled. After 4 bits have been shifted in, if the original value is 0, 1, 2, 3, or 4, then the result is within the 0-9 range of a BCD digit and there is no action required.

If the value is 5, 6, 7, 8, or 9, then the doubled result is greater than 10, so a carry out (called ModOut in the code) is generated to represent the overflow into the tens column (i.e. into the next BCD digit).

|                |   |   |   |   |   |   |   |   | 110001 |

|----------------|---|---|---|---|---|---|---|---|--------|

| (1) Shift      |   |   |   |   |   |   |   | 1 | 10001  |

| (2) Shift      |   |   |   |   |   |   | 1 | 1 | 0001   |

| (3) Shift      |   |   |   |   |   | 1 | 1 | 0 | 001    |

| (4) Shift      |   |   |   |   | 1 | 1 | 0 | 0 | 01     |

| and correction |   |   |   |   |   |   |   |   |        |

| +0110          |   |   |   |   | 0 | 1 | 1 | 0 |        |

| Result         |   |   |   | 1 | 0 | 0 | 1 | 0 | 01     |

| (5) Shift      |   |   | 1 | 0 | 0 | 1 | 0 | 0 | 1      |

| (6) Shift      |   | 1 | 0 | 0 | 1 | 0 | 0 | 1 |        |

| Result         | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 |        |

*Example*.  $A = 49_{10} = 110001_2$ .

The material on number systems is available in almost all elementary texts on algebra, switching theory, and digital computers. An extensive discussion of computer arithmetic is available in [5-11].

# Chapter 3 Binary Arithmetic

**Abstract** This chapter introduces to the methods for adding and multiplying binary numbers. The topic is developed by first considering the binary representation of unsigned numbers (which are the easiest to understand), and then binary representation of signed numbers and fractions (the hardest to understand) are concerned. Binary arithmetic is essential in all digital computers and in many other types of digital systems. To understand digital systems, the basics of binary addition, subtraction, multiplication, and division must be known.

## 3.1 Binary Addition

Adding binary numbers is a very simple task, and very similar to the longhand addition of decimal numbers. As with decimal numbers, you start by adding the bits (digits) one column, or place weight, at a time, from right to left.

| 0.0010 (2,0)              | 1010 (10,0)               | 0.100111 (39,0)              |

|---------------------------|---------------------------|------------------------------|

| $+0.0100(4_{10}^{10})$    | $\pm 1011 (11_{10})$      | $\pm 0.001101 (13_{10})$     |

| 0.0110 (6 <sub>10</sub> ) | 10101 (21 <sub>10</sub> ) | 0.110100 (52 <sub>10</sub> ) |

| (a)                       | (b)                       | (c)                          |

Notice that the first three rules result in a single bit and in the fourth rule the addition of two 1s yields a binary two (10). When binary numbers are added, the last condition creates 10 a sum of 0 in a given column and a carry of 1 over to the next column to the left, as illustrated in the following example:

|            | Decimal code | Binary code |

|------------|--------------|-------------|

| Carry bits | 166          | 1 111       |

|            | 47           | 10100110    |

|            |              | 00101111    |

| Result     | 213          | 11010101    |

B. Borowik et al., *Theory of Digital Automata*, Intelligent Systems, Control and Automation: Science and Engineering 63, DOI 10.1007/978-94-007-5228-3\_3, © Springer Science+Business Media Dordrecht 2013

| The four basic rules for<br>adding binary digits (bits)<br>are as follows: | The four basic rules<br>for subtracting bits are<br>as follows: | The four basic rules for<br>multiplying bits are as<br>follows: |

|----------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------|

| 0 + 0 = 0                                                                  | 0-0=0                                                           | $0 \times 0 = 0$                                                |

| 1 + 0 = 1                                                                  | 1 - 0 = 1                                                       | $1 \times 0 = 0$                                                |

| 0 + 1 = 1                                                                  | 1 - 1 = 0                                                       | $0 \times 1 = 0$                                                |

| 1 + 1 = 10                                                                 | 10 - 1 = 1                                                      | $1 \times 1 = 1$                                                |

Table 3.1 Binary arithmetic

#### 3.2 Binary Subtraction

Subtraction is generally simpler than addition since only two numbers are involved and the upper value representation is greater than the lower value representation. The problem of "borrow" is similar in binary subtraction to that in decimal. We can construct a subtraction table that has two parts – the three cases of subtracting without borrow, and the one case of the involvement of a borrow digit, no matter how far to the left is the next available binary digit.

| 10101 (21,0)     | 1000 (810)    |

|------------------|---------------|

| $-1010(10_{10})$ | $-11(3_{10})$ |

| $1011(11_{10})$  | $101(5_{10})$ |

| (a)              | (b)           |

|                  | . ,           |

When subtracting numbers, you sometimes have to borrow from the next column to the left. A borrow is required in binary only when you try to subtract a 1 from a 0. In this case, when a 1 is borrowed from the next column to the left, a 10 is created in the column being subtracted, and the last of the four basic rules just listed must be applied, Table 3.1.

For 10 minus 1, 1 is borrowed from the "tens" column for use in the "ones" column, leaving the "tens" column with only 2. The following examples show "borrowing" in binary subtraction.

| 0.0010 (210)                  | 100 (4,0)                       | 0.1010 (10,0)     |

|-------------------------------|---------------------------------|-------------------|

| $-\underline{0.0001}(1_{10})$ | $-\underline{010}(2_{10}^{10})$ | $-0.0110(6_{10})$ |

| $0.0001(1_{10})$              | $010(2_{10})$                   | $0.0100(4_{10})$  |

| (c)                           | (d)                             | (e)               |

#### **3.3 Binary Multiplication**

Binary multiplication of two bits is the same as multiplication of the decimal digits 0 and 1. Multiplication is performed with binary numbers in the same manner as with decimal numbers. It involves forming partial products, shifting

| <u>1101</u>   | <u>1101</u>                                        |

|---------------|----------------------------------------------------|

| 1101          | 0000                                               |

| + 0000        | + 1101                                             |

| 1101          | 1101                                               |

| × <u>1101</u> | × <u>1101</u>                                      |

| 1101          | 1101                                               |

|               | $ \times \ \frac{1101}{1101} \\ + \ 0000 \\ 1101 $ |

each successive partial product left one place, and then adding all the partial products.

## 3.4 Binary Division

Basically the reverse of the multiply by shift and add. Division in binary code follows the same procedure as division in decimal code.

| $A = 430_{10} = 110101110_2;$       | $A = 204_{10} = 11001100_{(2)},$ |

|-------------------------------------|----------------------------------|

| $B = 10_{10} = 1010; A/B = 43_{10}$ | $B = 12_{10} = 1100_{(2)},$      |

| 110101110  1010                     | $B = 204_{10}/12_{10} = 17_{10}$ |

| <u>-1010</u> 101011                 | 11001100   1100                  |

| _ 1101                              | <u>1100</u> 10001                |

| 1010                                | 00001                            |

| 1111                                | <u> </u>                         |

| 1010                                | 11                               |

| 1010                                | 0                                |

| 1010                                | 110                              |

| 0000                                | 0                                |

|                                     | 1100                             |

|                                     |                                  |

|                                     | 0000                             |

| (a)                                 | (b)                              |

Detailed study of digital arithmetic is beyond the scope of this book. For a more comprehensive discussion of computer arithmetic, the reader may consult [4, 5, 10, 11].

## 3.5 BCD Addition

The procedures followed in adding BCD are the same as those used in binary. For example, let's consider the addition of the two BCD digits 5 and 3:

| +0101 | $_{\rm BCD)}(5_{10})$ |

|-------|-----------------------|

| 0011  | $_{\rm BCD}(3_{10})$  |

| 1000  | $_{\rm BCD)}(8_{10})$ |

There is, however, the possibility that addition of BCD values will result in invalid totals. The following example shows this:

|                           | $+1001_{(BCD)}(9_{10})$<br><u>0110</u> <sub>(BCD)</sub> (6 <sub>10</sub> ) |

|---------------------------|----------------------------------------------------------------------------|

| Invalid BCD $\rightarrow$ | $1111 (15_{10}) (15_{10})$                                                 |

The sum  $1111_2$  is the binary equivalent of  $15_{10}$ ; however, 1111 is not a valid BCD number. You cannot exceed 1001 in BCD, so a correction factor must be made. To do this, you add  $6_{10} (0110_{BCD})$  to the sum of the two numbers. The "**add 6**" correction factor is added to any BCD group larger than  $1001_2$ .

Remember, there is no 1010, 1011, 1100, 1101, 1110, or 1111, in BCD:

| + 1111     | ← Invalid BCD  |

|------------|----------------|

| 0110 (BCD) | Add $(6_{10})$ |

| 0001 1111  | ← New BCD      |

The sum plus the add 6 correction factor can then be converted back to decimal to check the answer.

Add two numbers  $A = 279_{10} = 0010\ 0111\ 1001,\ B = 581_{10} = 0101\ 1000\ 0001.$

| 0010                                       | 0111 | 1001 |                |  |

|--------------------------------------------|------|------|----------------|--|

| +0101                                      | 1000 | 0001 |                |  |

| 0111                                       | 1111 | 1010 |                |  |

| +                                          | 0110 | 0110 | Add $(6_{10})$ |  |

| $C = 1000 \leftarrow 0110 \leftarrow 0000$ |      |      |                |  |

Result  $C = 100001100000 = 860_{10}$ .

#### **3.6** Arithmetic Operations with Signed Numbers

The one's and two's complements of a binary number are operations used by computers, to perform internal mathematical calculations. To complement a binary number means to change it to a negative number.

#### 3.6.1 1s and 2s Complements Forms

This allows the basic arithmetic operations of subtraction, multiplication, and division to be performed through successive addition. The intention of this section is to introduce the basic concepts of complementing.

#### 3.6.2 1s Complement

Let's assume that we have a 5-bit binary number that we wish to represent as a negative number. The number is decimal 19, or binary:

100112

There are two ways to represent this number as a negative number. The first method is to simply place a minus sign in front of the number, as we do with decimal numbers:

#### -(10011),

This method is suitable for us, but it is impossible for computers to interpret, since the only symbols they use are binary 1s and 0s. To represent negative numbers, then, some digital computing devices use what is known as the one's complement method. First, the one's complement method places an extra bit (sign bit) in the most significant (left-most) position and lets this bit determine whether the number is positive or negative. The number is positive if the sign bit is 0 and negative if the sign bit is 1. Using the one's complement method, +19 decimal is represented in binary as shown here with the sign bit (0) indicated in bold:

#### **0** 10011,

The negative representation of binary 10011 is obtained by placing a 1 in the most significant bit position and inverting each bit in the number (changing 1s to 0s and 0s to 1s). So, the one's complement of binary 10011 is:

#### 1 01100,

If a negative number is given in binary, its one's complement is obtained in the same fashion.

$$+15_{10} = 0 \ 1111_2$$

$-15_{10} = 1 \ 0000_2$

#### 3.6.3 2s Complement

The two's complement is similar to the one's complement in the sense that one extra digit is used to represent the sign. The two's complement computation, however, is slightly different. In the one's complement, all bits are inverted; but in the two's complement, each bit, from right to left, is inverted only after the first 1 is detected. Let's use the number +22 decimal as an example:

$$+22_{10}=0$$

10110,

Its two's complement would be:

$$-22_{10} = 1\ 01010_2$$

Note that in the negative representation of the number 22, starting from the right, the first digit is a 0, so it is not inverted; the second digit is a 1, so all digits after this one are inverted.

|         | 1s and 2s complements forms |                        |                        |         | 1s and 2s complements forms |                        |                        |

|---------|-----------------------------|------------------------|------------------------|---------|-----------------------------|------------------------|------------------------|

| Decimal | Binary                      | 4-bit 1s<br>complement | 4-bit 2s<br>complement | Decimal | Binary                      | 4-bit 1s<br>complement | 4-bit 2s<br>complement |

| +7      | 0.111                       | 0.111                  | 0.111                  | -0      | 1.000                       | 1.111                  | 0.000                  |

| +6      | 0.110                       | 0.110                  | 0.110                  | -1      | 1.001                       | 1.110                  | 1.111                  |

| +5      | 0.101                       | 0.101                  | 0.101                  | -2      | 1.010                       | 1.101                  | 1.110                  |

| +4      | 0.100                       | 0.100                  | 0.100                  | -3      | 1.011                       | 1.100                  | 1.101                  |

| +3      | 0.011                       | 0.011                  | 0.011                  | -4      | 1.100                       | 1.011                  | 1.100                  |

| +2      | 0.010                       | 0.010                  | 0.010                  | -5      | 1.101                       | 1.010                  | 1.011                  |

| +1      | 0.001                       | 0.001                  | 0.001                  | -6      | 1.110                       | 1.001                  | 1.010                  |

| +0      | 0.000                       | 0.000                  | 0.000                  | -7      | 1.111                       | 1.000                  | 1.001                  |

Table 3.2 4-bit 1s and 2s complements forms

Table 3.3

8-bit 1s and 2s complements forms

| Decimal | Binary                    | Inverse (1s complement) | 2s complement            |

|---------|---------------------------|-------------------------|--------------------------|

| -7      | $[-7]_{b} = 1.000111_{2}$ | $[-7]_i = 1.111000_2$   | $[-7]_{tc} = 1.111001_2$ |

If a negative number is given in two's complement, its complement (a positive number) is found in the same fashion:

$$-14_{10} = \mathbf{1} \ 10010_2$$

$+14_{10} = \mathbf{0} \ 01110_2$

Again, all bits from right to left are inverted after the first 1 is detected. Other examples of the 1s and 2s complement are shown here (Tables 3.2 and 3.3):

#### 3.6.4 Additional in the 1s Complement System

There are several options for adding: Case 1. A > 0, B > 0, A + B < 1.  $[A > 0]_i + [B > 0]_i = A + B$ . Case 2. A > 0, B < 0, A + B > 0.  $[A > 0]_i + [B < 0]_i = A + 2 + B - 2^{-n}$ Case 3. A > 0, B < 0, A + B < 0.  $[A > 0]_i + [B < 0]_i = A + 2 + B - 2^{-n}$ Case 4. A < 0, B < 0, |A + B| < 1.  $[A < 0]_i + [B < 0]_i = 2 + A - 2^{-n} + 2 + B - 2^{-n}$

Where the  $[A]_{i}$ ,  $[B0]_{i}$  – representation of numbers in a computer.

Examples

Case 2.

$$A = +0,1101$$

$[A]_{b} = 0,1101$   $[A]_{i} = 0,1101$

$B = -0,0011$   $[B]_{b} = 1,0011$   $[B]_{i} = 1,1100$

$1 \leftarrow 0,1001$

$C = 0,1010 <= [C]_{b} = 0,1010 <= \overline{[C]_{i} = 0,1010}$

Case 3. A = -0,1101 $[A]_{h} = 1,1101$ [A] = 1,0010[B] = 0.0011B = +0.0011[B] = 0,0011 $C = -0,1010 <= [C]_{b} = 1,1010 <= [C]_{c} = 1,0101$ Case 4. A = -0,0101 $[A]_{h} = 1,0101$  $[A]_{i} = 1,1010$ B = -0.0110 [B]<sub>b</sub> = 1.0110  $[B]_{i} = 1,1001$ **1** ← 1,0011 1  $C = -0,1011 < = [C]_{h} = 1,1011 < = [C]_{i} = 1,0100$ **Example.** Case |A| = |B|, A < 0, B > 0.A = -0.0101 $[A]_{db} = 1,0101$  $[A]_{=}=1,1010$  $[B]_{\rm h} = 0,0101$ B = +0.0101 $[B]_{i} = 0.0101$  $C = -0,0000 <= [C]_{b} = 1,0000 <= [C]_{c} = 1,1111$ **Example.** Case A > B, B > 0, |A + B| = 1.  $[A]_{h} = 0,0111$ [A] = 0,0111A = +0.0111B = +0,1001 $[B]_{=}=0,1001$ [B] = 0,1001 $C = +0,1111 \le [C]_{b} = 0,1111 \le [C]_{i} = 1,0000$ **Example.** Case A < 0, B < 0, |A + B| = 1.  $[A]_{h} = 1,0111$  $[A]_{i} = 1,1000$ A = -0,0111B = -0.1001 $[B]_{L} = 1,1001$  $[B]_{i} = 1,0110$  $1 \leftarrow 0.1110$ C = +0,1111 < = [C] = 0,1111 < = [C] = 0,1111

#### 3.6.5 Additional in the 2s Complement System

There are several options for adding:

Case 1. A > 0, B > 0, A + B < 1.  $[A > 0]_{tc} + [B > 0]_{tc} = A + B$ . Case 2. A > 0, B < 0, A + B > 0.  $[A > 0]_{tc} + [B < 0]_{tc} = A + 2 + B$ . Case 3. A > 0, B < 0, A + B < 0.  $[A > 0]_{tc} + [B < 0]_{tc} = A + 2 + B$ . Case 4. A < 0, B < 0, |A + B| < 1.  $[A < 0]_{tc} + [B < 0]_{tc} = 2 + A + 2 + B$ . Here the  $[A]_{tc}$ ,  $[B0]_{tc}$  – representation of numbers in a computer. Examples.

Case 3.  $A = -0,1101 [A]_{b} = 1,1101 [A]_{tc} = 1,0011$   $B = +0,0011 [B]_{b} = 0,0011 [B]_{tc} = 0,0011$  $C = -0,1010 < = [C]_{b} = 1,1010 < = [C]_{tc} = 1,0110$

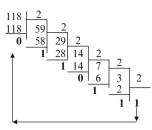

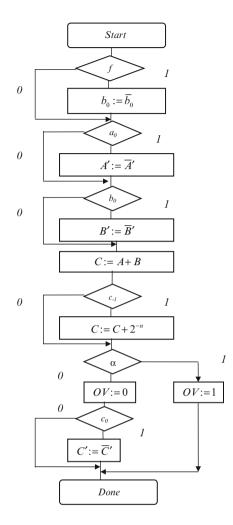

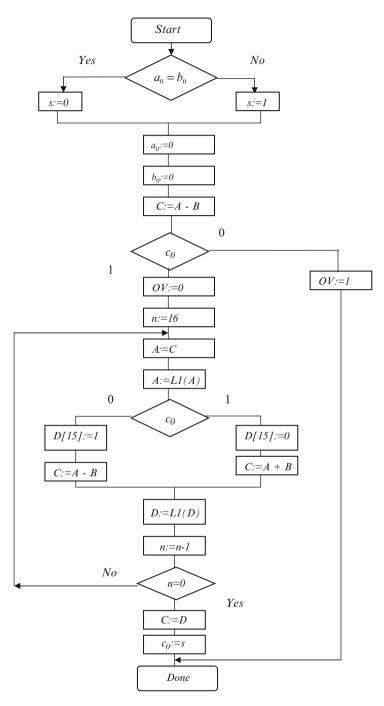

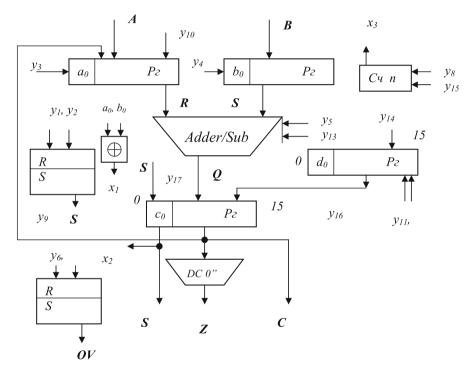

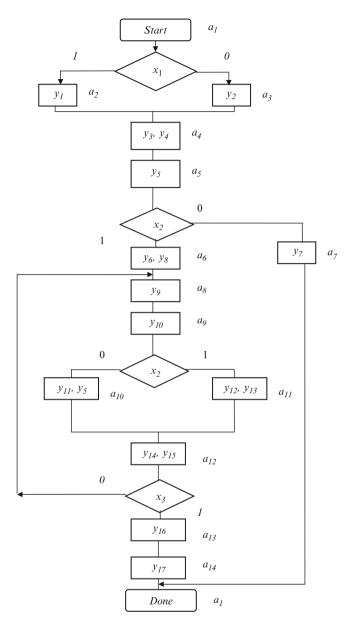

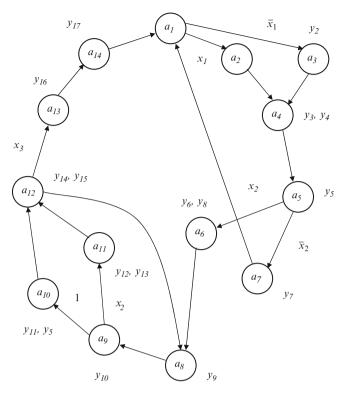

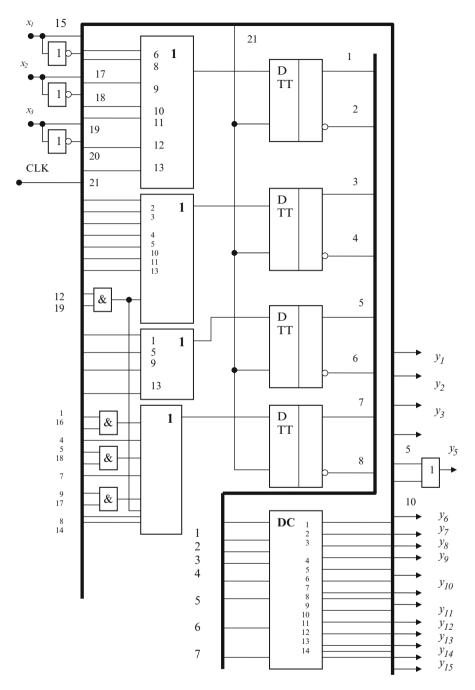

where  $a_o, b_0, c_o$  - sign bits; OV - value of overflow digit; f- The type of operation (f=0 - Addition, f=1 - Subtraction)

Fig. 3.1 The block diagram of the addition (subtraction) of binary numbers in the direct code

Case 4. A = -0,0101  $[A]_{b} = 1,0101$   $[A]_{tc} = 1,1011$  B = -0,0110  $[B]_{b} = 1,0110$   $[B]_{tc} = 1,1010$   $C = -0,1011 <= [C]_{b} = 1,1011 <= [C]_{tc} = 1,1010$ Example. Case |A| = |B|, A < 0, B > 0. A = -0,0101  $[A]_{b} = 1,0101$   $[A]_{tc} = 1,1011$  B = +0,0101  $[B]_{b} = 0,0101$   $[B]_{tc} = 0,0101$  $C = +0,0000 <= [C]_{b} = 0,0000 <= [C]_{tc} = 10,0000$

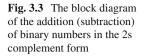

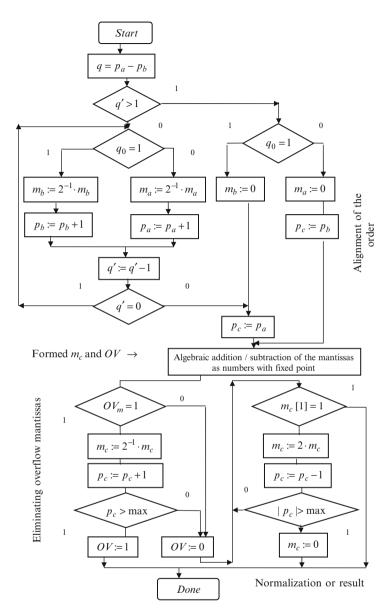

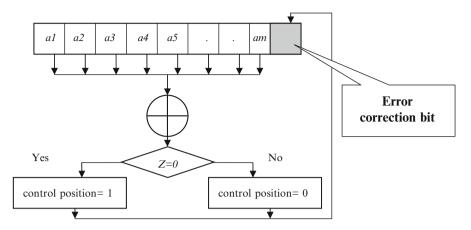

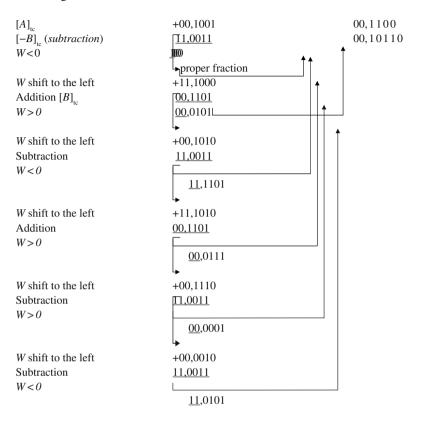

Figures 3.1, 3.2, 3.3 show a block diagram of the addition (subtraction) of binary numbers in the direct, inverse and complementary codes.

where a<sub>o</sub>,b<sub>0</sub>,c<sub>o</sub> - sign bits; OV - value of overflow digit; A',B',C' -modules of numbers; c<sub>-1</sub> - transfer from a sign bit; f- The type of operation (f=0 - Addition, f=1 - Subtraction)

Fig. 3.2 The block diagram of the addition (subtraction) of binary numbers in the inverse code (1s complement form)

# 3.7 BCD Subtraction

Either packed or unpacked BCD numbers can be subtracted. BCD subtraction follows the same rules as binary subtraction. However, if the subtraction causes a

where  $a_o, b_0, c_o$  - sign bits; OV - value of overflow digit;  $\alpha^*$  - value of overflow in an additional code; B' - module of number; f- The type of operation (f=0 - Addition, f=1 - Subtraction)

borrow and/or creates an invalid BCD number, an adjustment is required to correct the answer. The correction method is to subtract 6 from the difference in any digit position that has caused an error.

#### **Examples.**

Represent the number of  $A = -256_{10}$  in the inverse code for the BCD:

|        | 1.0010 0101 0110        |                             |

|--------|-------------------------|-----------------------------|

|        | <u>+ 0110 0110 0110</u> | Add (6 <sub>10</sub> ) 0110 |

|        | 1000 1011 1100          |                             |

| Result | $A_i = 1.011101000011.$ |                             |

Represent the number of  $A = -398_{10}$  in the two complement code for the BCD:

|                        | 1.001110011000        | Add (6 <sub>10</sub> ) 0110 |

|------------------------|-----------------------|-----------------------------|

| +                      | <u>0110 0110 0110</u> | 10                          |

|                        | 1. 1001 1111 1110     |                             |

|                        | 0110 0000 0001        |                             |

|                        | +1                    |                             |

| <b>Result</b> $A_{tc}$ | =1.0110 0000 0010     |                             |

$A = 37_{10} = 0011\ 0111_{(BCD)}$ .  $B = 12_{10} = 0000\ 0010_{(BCD)}$ . Result  $C = A - B = 15_{10} = BCD$ ?

|        | 0011 0111                          |

|--------|------------------------------------|

|        | + 0000 0010                        |

|        | 0011 0101                          |

| Result | $C = 0011  0101_{(BCD)} = 25_{10}$ |

$A = -1000\ 0010\ 0101_{(BCD)} = -825_{10}, B = 1001\ 0100\ 0110_{(BCD)} = 946_{10}.$ Result  $C = -A + B = (-825 + 946)_{10} = 121_{10} = BCD$ ?

| 1.0001    | 0111               | 0101                                         |

|-----------|--------------------|----------------------------------------------|

| 0.1001    | 0100               | 0110                                         |

| 1.1010    | 1011               | 1011                                         |

| <u> </u>  | 0110               | <u>0110</u> (adjustment Add $0110_{(BCD)}$ ) |

| Result C= | $0. \leftarrow 00$ | $01 \leftarrow 0010 \leftarrow 0001.$        |

## 3.8 BCD Multiplication and Division

Multiplication cannot be performed on packed BCD; the four most significant bits must be zeroed for the adjustment to work.

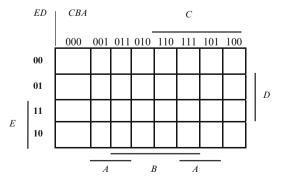

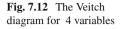

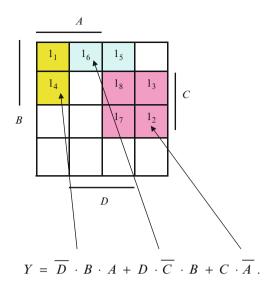

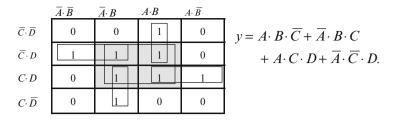

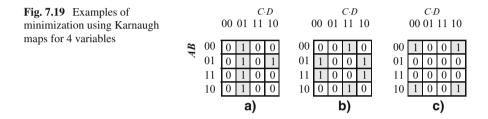

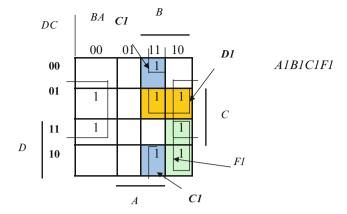

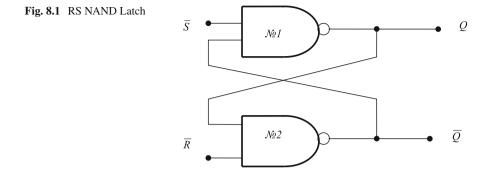

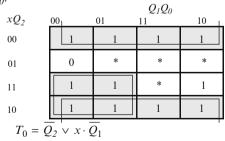

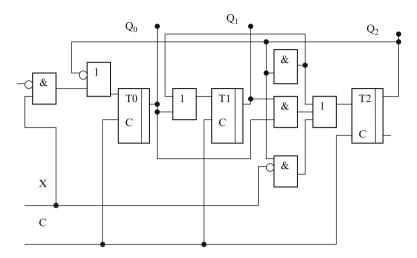

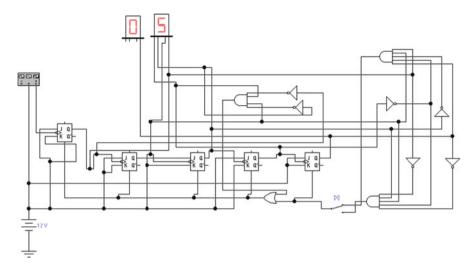

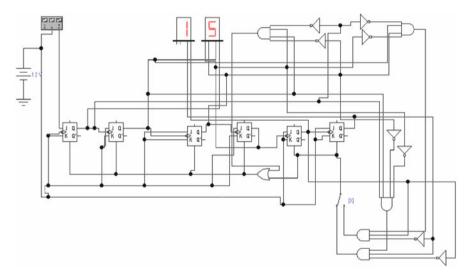

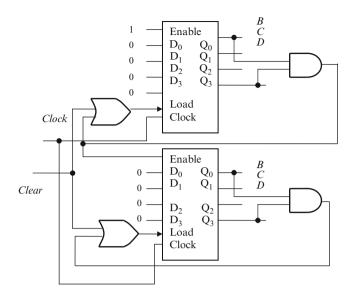

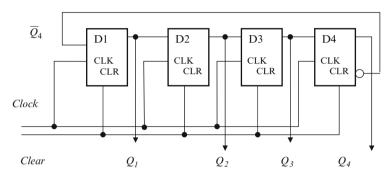

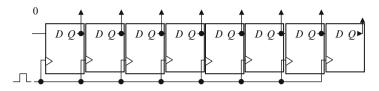

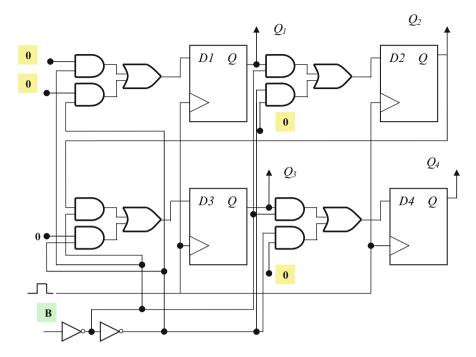

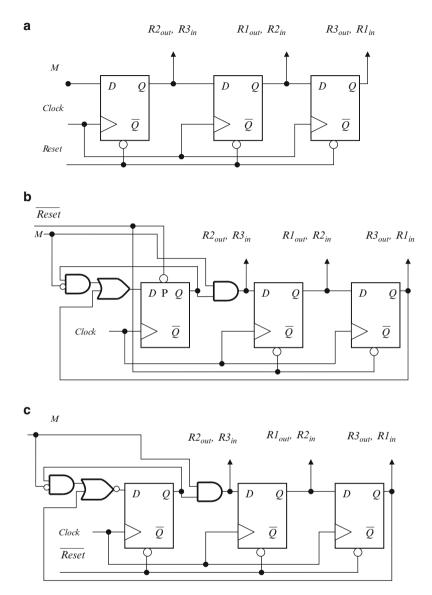

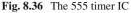

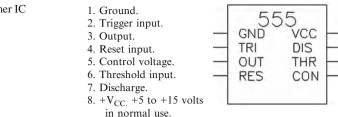

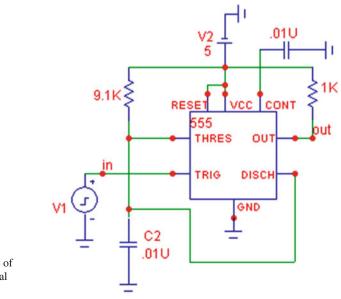

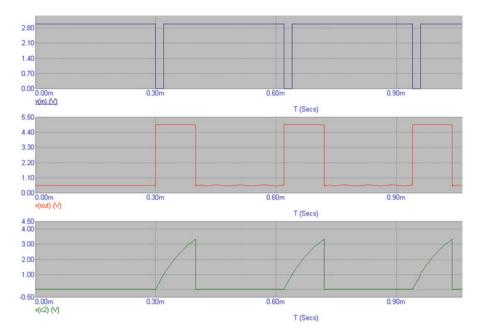

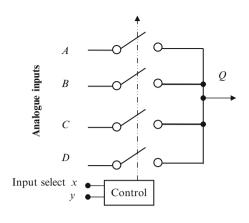

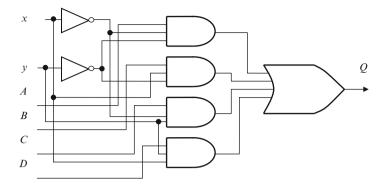

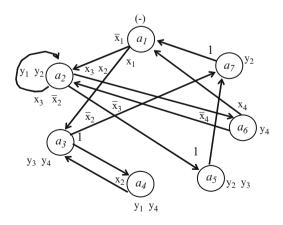

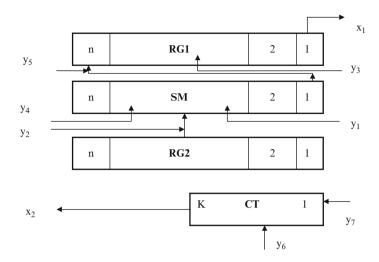

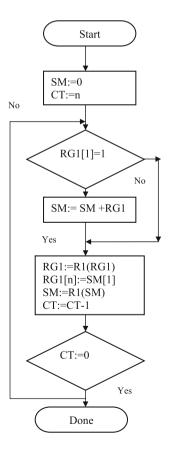

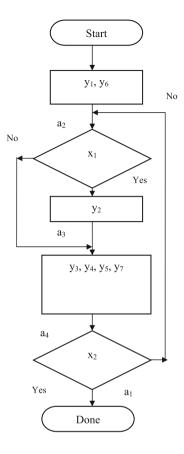

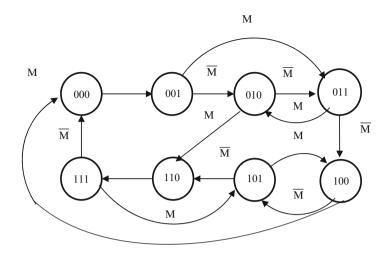

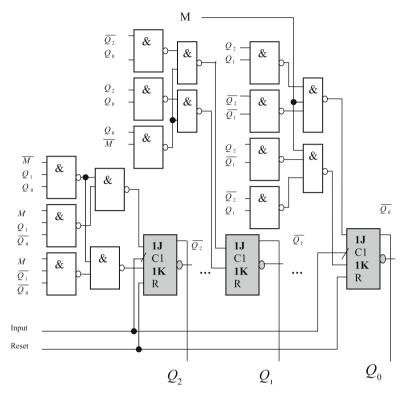

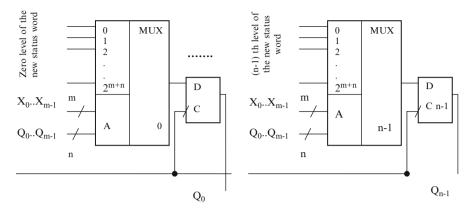

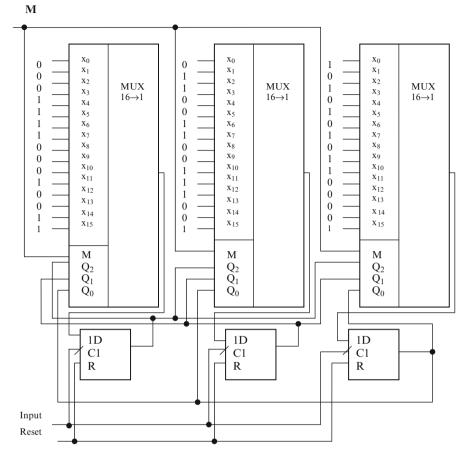

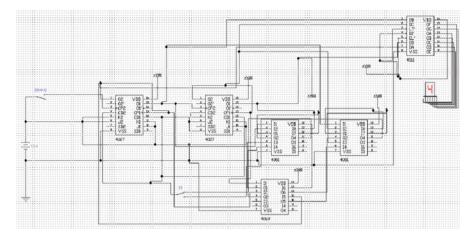

BCD division also cannot be performed on packed numbers. Before dividing an unpacked BCD number, the division adjustment is made by converting the BCD numbers to binary.