#### THE INSULATED GATE BIPOLAR TRANSISTOR

## IGBT

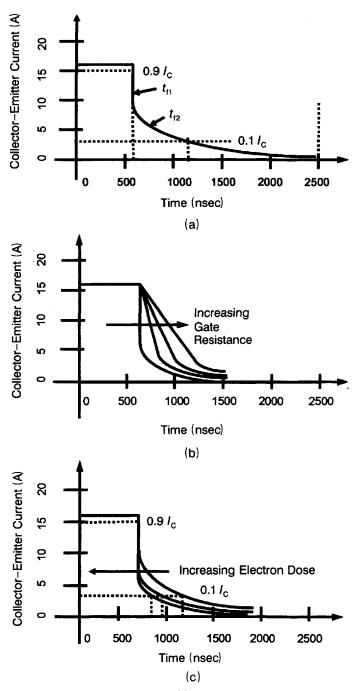

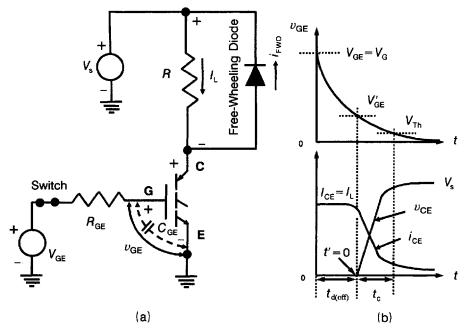

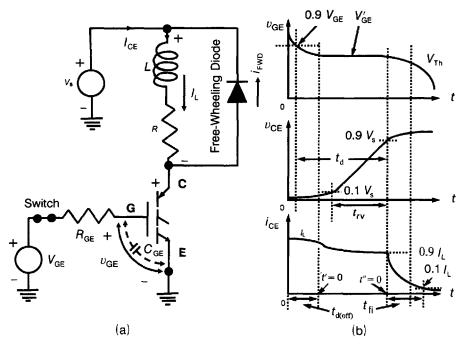

### THEORY AND DESIGN

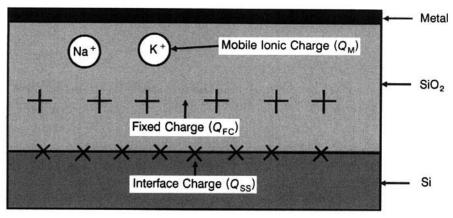

#### IEEE Press 445 Hoes Lane Piscataway, NJ 08854

#### IEEE Press Editorial Board Stamatios V. Kartalopoulos, *Editor in Chief*

M. Akay J. B. Anderson R. J. Baker J. E. Brewer M. E. El-Hawary R. J. Herrick D. Kirk R. Leonardi M. S. Newman M. Padgett W. D. Reeve S. Tewksbury G. Zobrist

Kenneth Moore, Director of IEEE Press Catherine Faduska, Senior Acquisitions Editor John Griffin, Acquisitions Editor Christina Kuhnen, Associate Acquisitions Editor

#### THE INSULATED GATE BIPOLAR TRANSISTOR

## IGBT

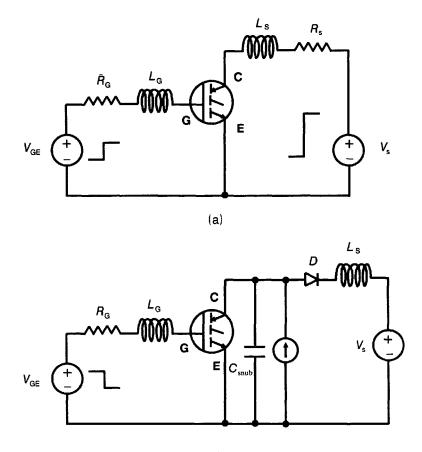

## THEORY AND DESIGN

Vinod Kumar Khanna

A JOHN WILEY & SONS, INC., PUBLICATION

Copyright © 2003 by the Institute of Electrical and Electronics Engineers, Inc. All rights reserved.

Published simultaneously in Canada.

No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, scanning or otherwise, except as permitted under Section 107 or 108 of the 1976 United States Copyright Act, without either the prior written permission of the Publisher, or authorization through payment of the appropriate per-copy fee to the Copyright Clearance Center, Inc., 222 Rosewood Drive, Danvers, MA 01923, 978-750-8400, fax 978-750-4470, or on the web at www.copyright.com. Requests to the Publisher for permission should be addressed to the Permissions Department, John Wiley & Sons, Inc., 111 River Street, Hoboken, NJ 07030, (201) 748-6011, fax (201) 748-6008, e-mail: permreq@wiley.com.

Limit of Liability/Disclaimer of Warranty: While the publisher and author have used their best efforts in preparing this book, they make no representations or warranties with respect to the accuracy or completeness of the contents of this book and specifically disclaim any implied warranties of merchantability or fitness for a particular purpose. No warranty may be created or extended by sales representatives or written sales materials. The advice and strategies contained herein may not be suitable for your situation. You should consult with a professional where appropriate. Neither the publisher nor author shall be liable for any loss of profit or any other commercial damages, including but not limited to special, incidental, consequential, or other damages.

For general information on our other products and services please contact our Customer Care Department within the U.S. at 877-762-2974, outside the U.S. at 317-572-3993 or fax 317-572-4002.

Wiley also publishes its books in a variety of electronic formats. Some content that appears in print, however, may not be available in electronic format.

#### Library of Congress Cataloging-in-Publication Data:

Khanna, Vinod Kumar, 1952-

The Insulated gate bipolar transistor (IGBT): theory and design / Vinod Kumar Khanna. p. cm

"A Wiley-Interscience publication." Includes bibliographical references and index. ISBN 0-471-23845-7 (cloth) 1. Insulated gate bipolar transistor. I. Title.

TK971.96.B55K49 2003 621.3815'282---dc21

2003043251

Printed in the United States of America

10 9 8 7 6 5 4 3 2 1

To my daughter, Aloka, and my wife, Amita My mother, Smt. Pushpa Khanna, and my father, Shri Amarnath Khanna

## CONTENTS

| Preface x |                                               |                                                             |    |

|-----------|-----------------------------------------------|-------------------------------------------------------------|----|

| 1         | Power Device Evolution and the Advent of IGBT |                                                             | 1  |

|           | 1.1                                           | Introductory Background / 1                                 |    |

|           | 1.2                                           | Insulated Gate Bipolar Transistor / 5                       |    |

|           | 1.3                                           | Advantages and Shortcomings of IGBT / 8                     |    |

|           | 1.4                                           | IGBT Structure and Fabrication / 12                         |    |

|           | 1.5                                           | Equivalent Circuit Representations / 14                     |    |

|           | 1.6                                           | Principle of Operation and Charge-Control<br>Phenomena / 16 |    |

|           | 1.7                                           | Circuit Modeling / 17                                       |    |

|           | 1.8                                           | Packaging Options for IGBTs / 22                            |    |

|           | 1.9                                           | Handling Precautions of IGBTs / 23                          |    |

|           | 1.10                                          | IGBT Gate Driving Circuits / 23                             |    |

|           | 1.11                                          | IGBT Protection / 26                                        |    |

|           | 1.12                                          | Summary and Trends / 27                                     |    |

|           | Revie                                         | ew Exercises / 28                                           |    |

|           | References / 29                               |                                                             |    |

| 2         | IGBT                                          | Fundamentals and Status Review                              | 35 |

|           | 2.1                                           | Device Structures / 35                                      |    |

|           | 2.2                                           | Device Operational Modes / 46                               |    |

|           | 2.3                                           | Static Characteristics of IGBT / 50                         |    |

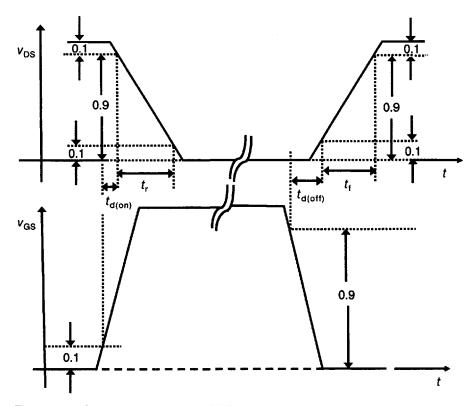

|           | 2.4                                           | Switching Behavior of IGBT / 55                             |    |

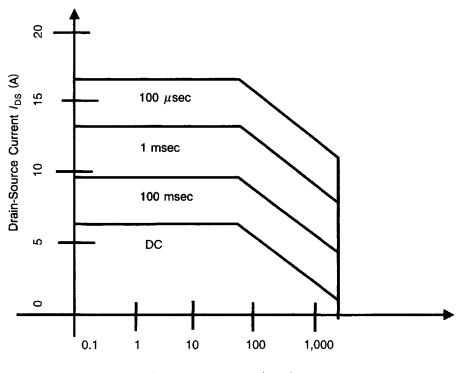

|           | 2.5                                           | Safe Operating Area (SOA) / 77                              |    |

- 2.5 Safe Operating Area (SOA) / //

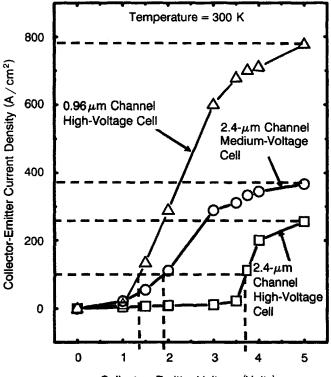

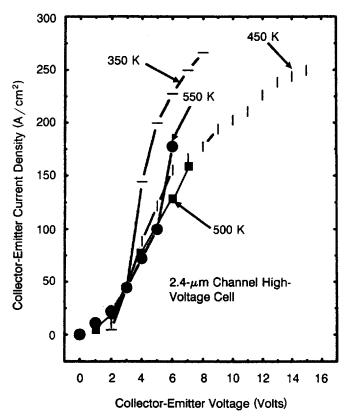

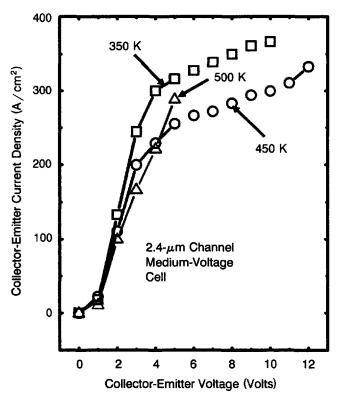

2.6 High-Temperature Operation / 83

- 2.7 Radiation Effects / 85

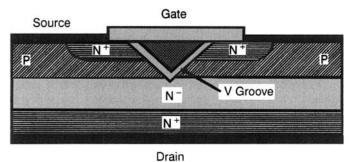

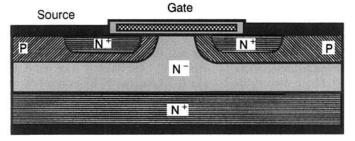

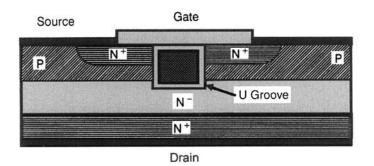

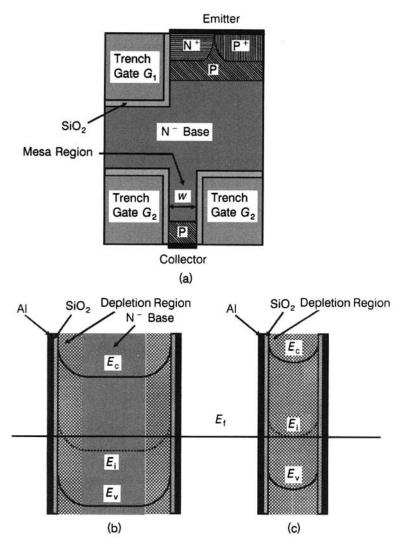

- 2.8 Trench-Gate IGBT and Injection-Enhanced IGBT (IEGT) / 86

- 2.9 Self-Clamped IGBT / 89

- 2.10 Ratings and Applications of IGBT / 90

- 2.11 Summary and Trends / 94

Review Exercises / 95

References / 97

#### 3 MOS Components of IGBT

- 3.1 General Considerations / 101

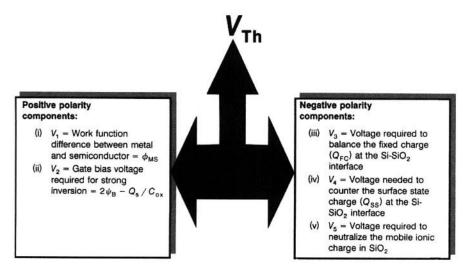

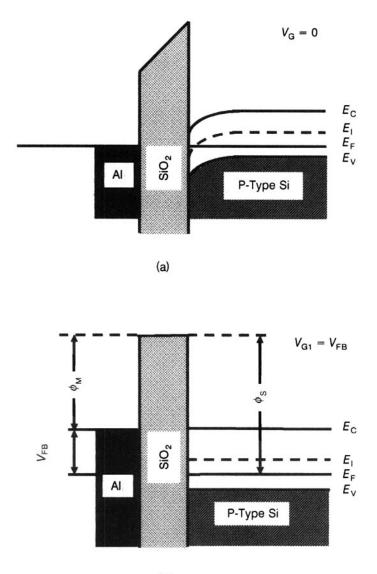

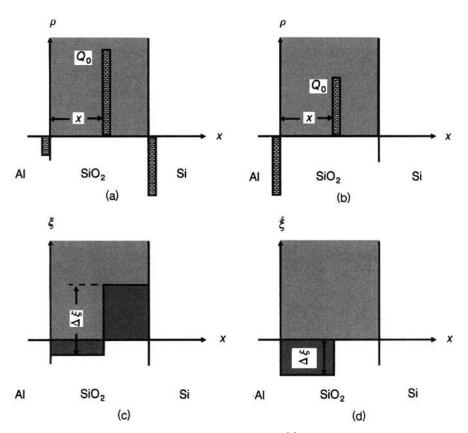

- 3.2 MOS Structure Analysis and Threshold Voltage / 107

- 3.3 Current-Voltage Characteristics of MOSFET; Transconductance and Drain Resistance / 119

- 3.4 ON-Resistance Model of DMOSFET and UMOSFET / 123

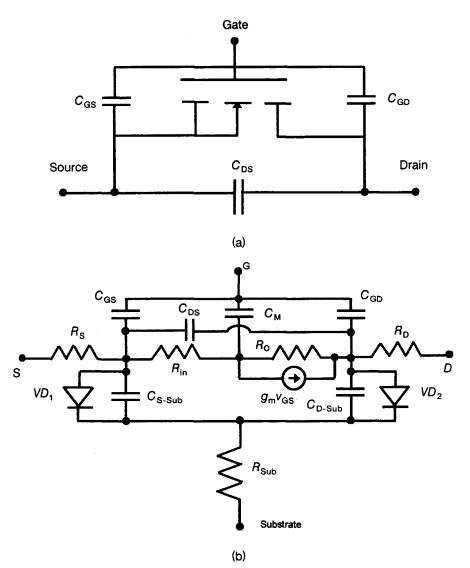

- 3.5 MOSFET Equivalent Circuit and Switching Times / 130

- 3.6 Safe Operating Area (SOA) / 134

- 3.7 Neutron and Gamma-Ray Damage Effects / 134

- 3.8 Thermal Behavior of MOSFET / 136

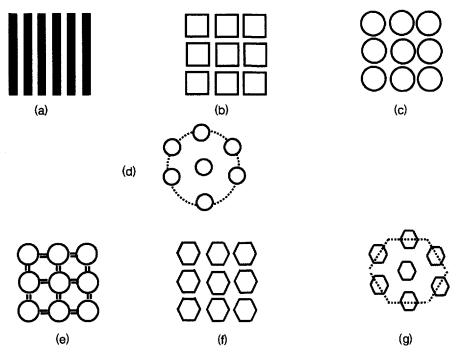

- 3.9 DMOSFET Cell Windows and Topological Designs / 138

- 3.10 Summary and Trends / 138

Review Exercises / 139

References / 140

- Appendix 3.1: Derivation of Eqs. (3.2a) and (3.2b) / 141

- Appendix 3.2: Derivation of Eq. (3.7) / 142

- Appendix 3.3: Derivation of the Equations for Bulk Semiconductor Potential  $\psi_B$  and the Surface Charge  $Q_s$  at the Point of Transition into Strong Inversion / 146

- Appendix 3.4: Derivation of Eqs. (3.33)-(3.36) / 147

- Appendix 3.5: Derivation of Eq. (3.39) / 150

- Appendix 3.6: Derivation of Eq. (3.49) / 152

#### 4 Bipolar Components of IGBT

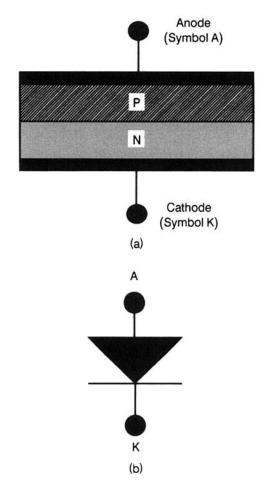

- 4.1 PN Junction Diode / 155

- 4.2 P-I-N Rectifier / 172

- 4.3 Bipolar Junction Transistor / 180

#### 101

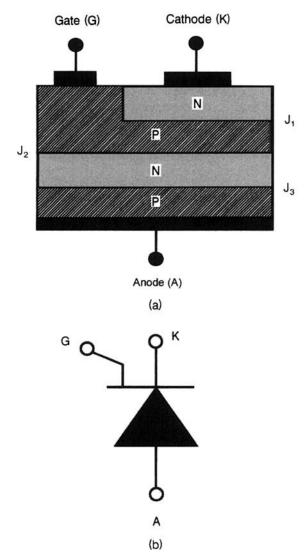

- 4.4 Thyristor / 189

- 4.5 Junction Field-Effect Transistor (JFET) / 198

- 4.6 Summarizing Remarks / 198

Review Exercises / 198

References / 200

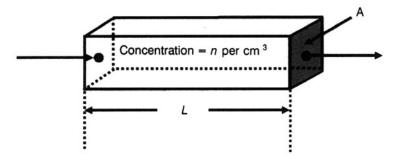

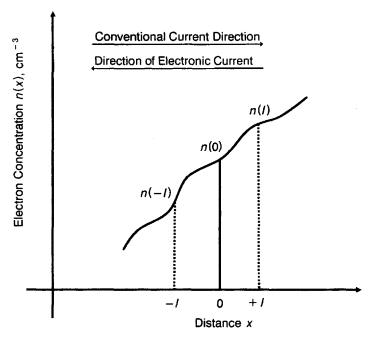

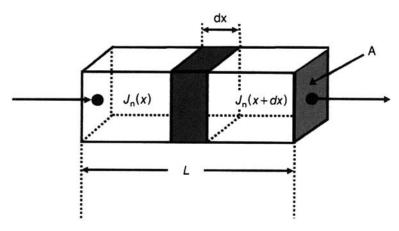

- Appendix 4.1 Drift and Diffusion Current Densities / 201

- Appendix 4.2 Einstein's Equation / 204

- Appendix 4.3 Continuity Equation and Its Solution / 206

- Appendix 4.4 Solution of the Continuity Equation (4.41) / 209

- Appendix 4.5 Derivation of Eq. (4.50) / 212

- Appendix 4.6 Derivation of Current Density Equations (4.55) and (4.56) / 217

- Appendix 4.7 Transistor Terminal Currents [Eqs. (4.57) and (4.58)] / 220

- Appendix 4.8 Common-Base Current Gain  $\alpha_T$ [Eq. (4.63)] / 225

#### 5 Physics and Modeling of IGBT

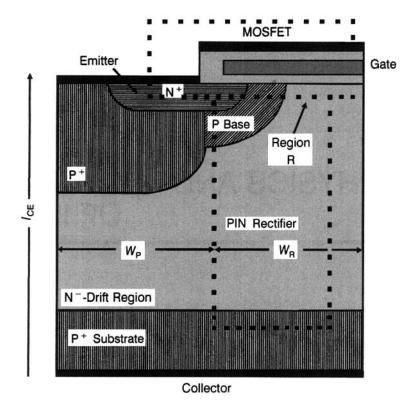

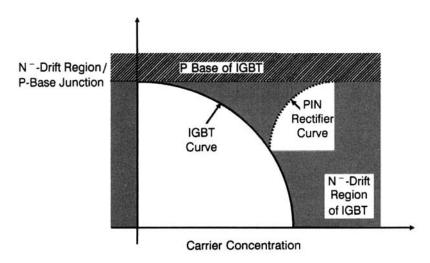

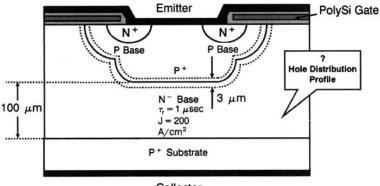

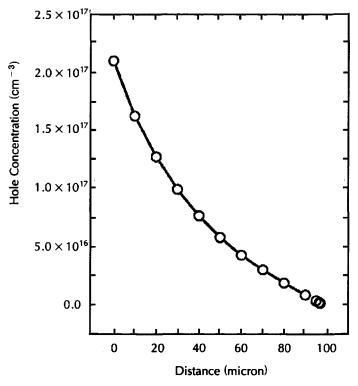

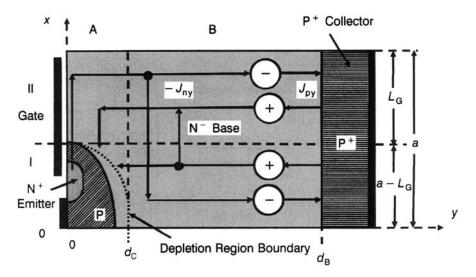

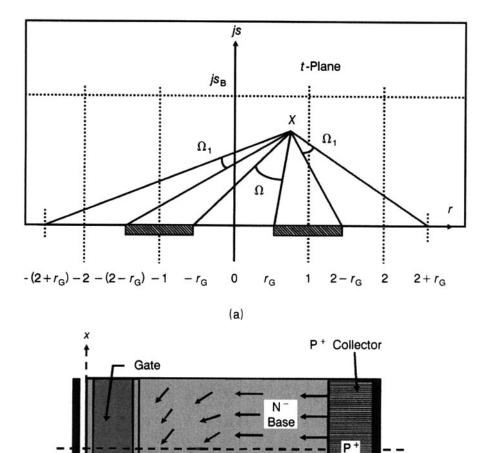

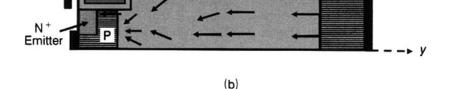

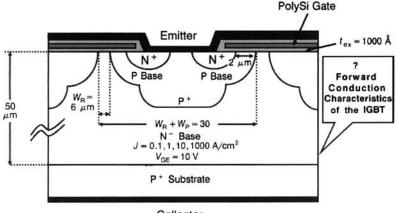

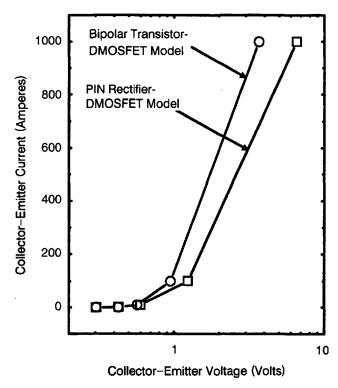

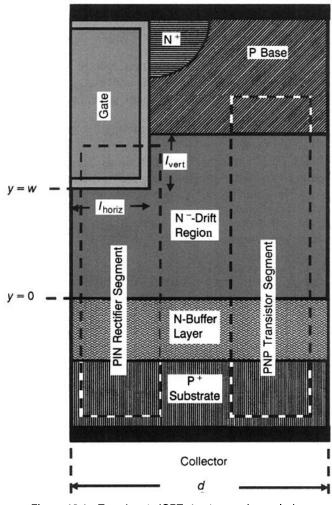

- 5.1 PIN Rectifier-DMOSFET Model of IGBT / 230

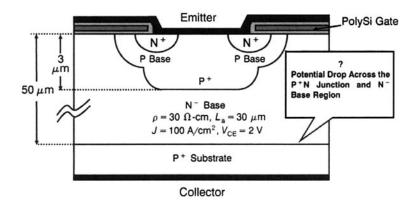

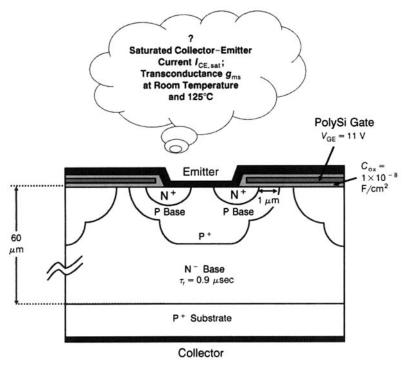

- 5.2 Bipolar Transistor-DMOSFET Model of IGBT by Extension of PIN Rectifier-DMOSFET Model / 241

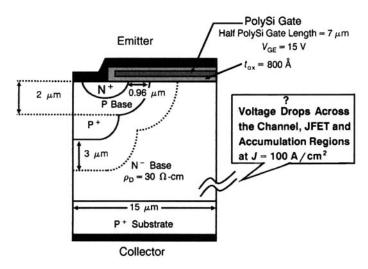

- 5.3 Bipolar Transistor-DMOSFET Model of IGBT with Device-Circuit Interactions / 251

- 5.4 Concluding Comments / 280

Review Exercises / 281

References / 283

- Appendix 5.1 Solution of Eq. (5.8) / 285

- Appendix 5.2 Derivation of Eqs. (5.33) and (5.34) / 286

- Appendix 5.3 Derivation of Eq. (5.35) / 288

- Appendix 5.4 Derivation of Eq. (5.38) [Solution of Eq. (5.35)] / 289

- Appendix 5.5 Derivation of Eqs. (5.40)–(5.42) / 290

- Appendix 5.6 Derivation of Eq. (5.44) / 293

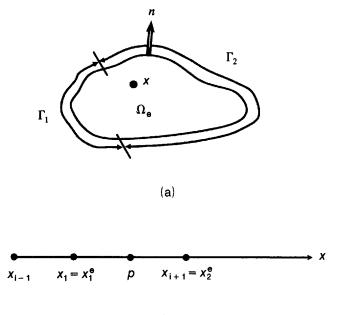

- Appendix 5.7 Derivation of Eqs. (5.81) and Construction of Equivalent Conductive Network for 1-D Linear Element / 297

#### X CONTENTS

#### 6 Latchup of Parasitic Thyristor in IGBT

- 6.1 Introduction / 303

- 6.2 Static Latching / 306

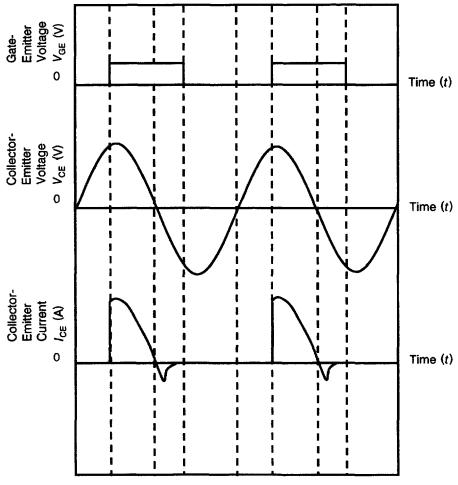

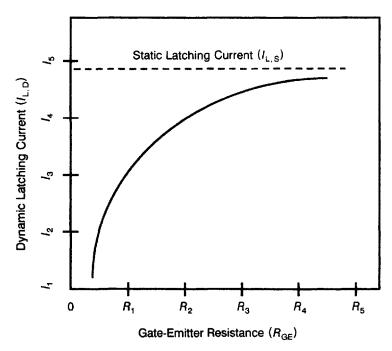

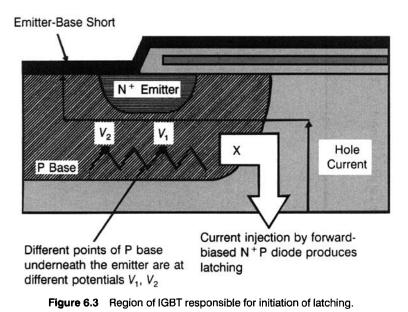

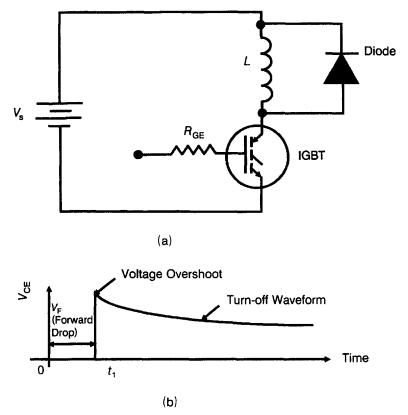

- 6.3 Dynamic Latching / 308

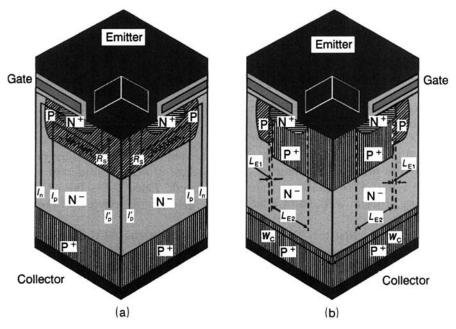

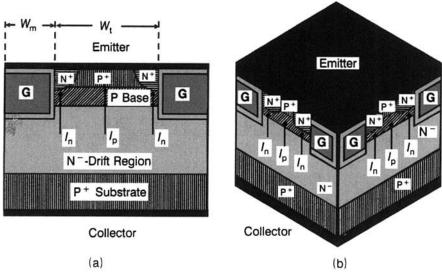

- 6.4 Latching Prevention Measures / 317

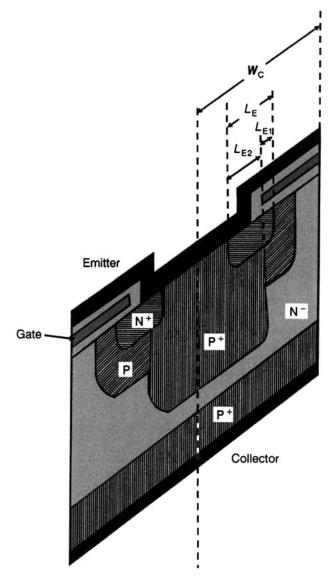

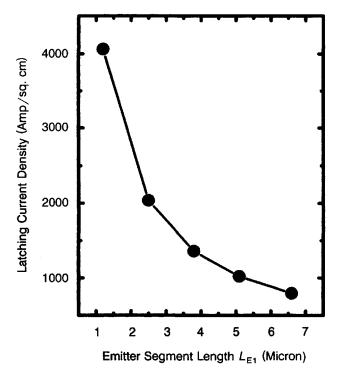

- 6.5 Latching Current Density of Trench-Gate IGBT / 340

6.6 Summarizing Remarks / 342

Review Exercises / 342

References / 344

Appendix 6.1 Equation (6.15) / 345

Appendix 6.2 Equation (6.20) / 347

#### 7 Design Considerations of IGBT Unit Cell

349

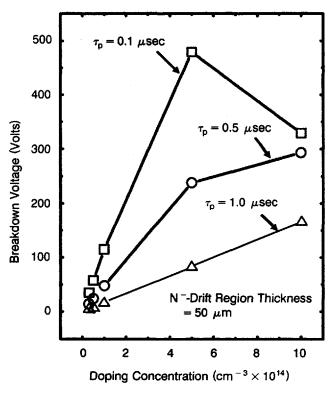

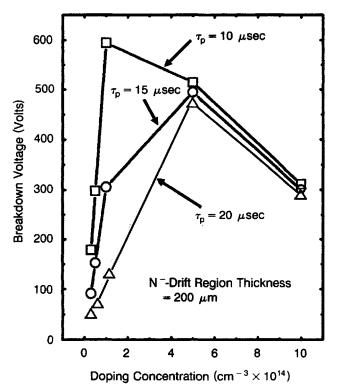

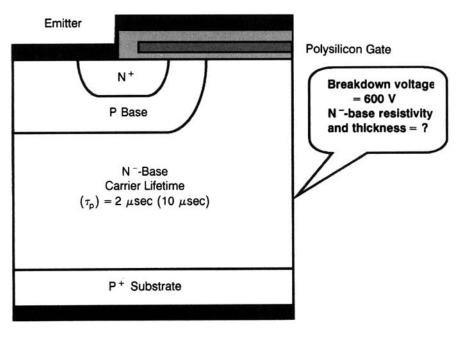

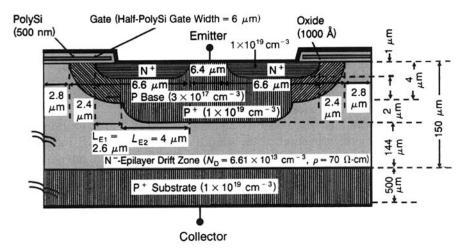

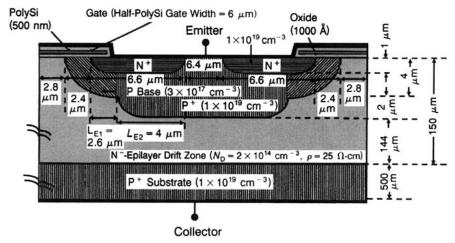

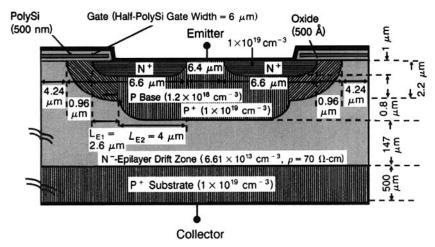

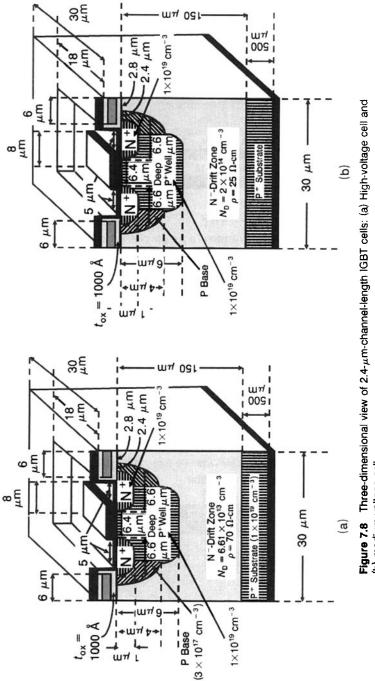

- 7.1 Semiconductor Selection and Vertical Structure Design / 349

- 7.2 IGBT Design by Analytical Calculations and Numerical Simulations / 362

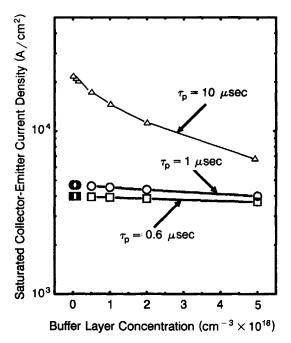

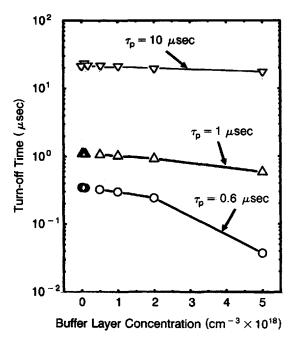

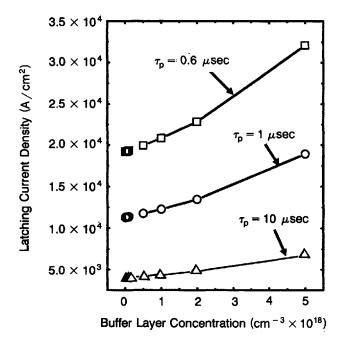

- 7.3 Optimization of N-Buffer Layer Structure / 381

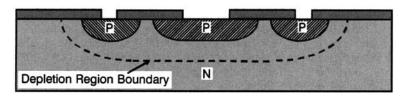

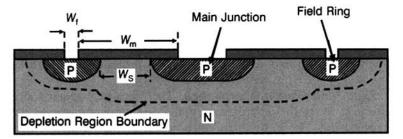

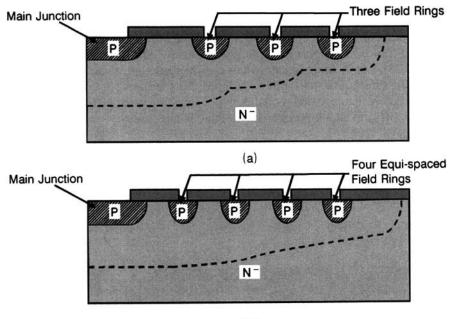

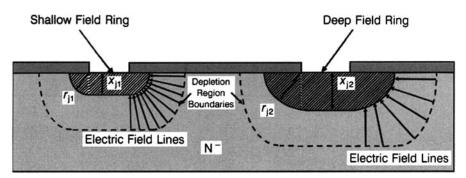

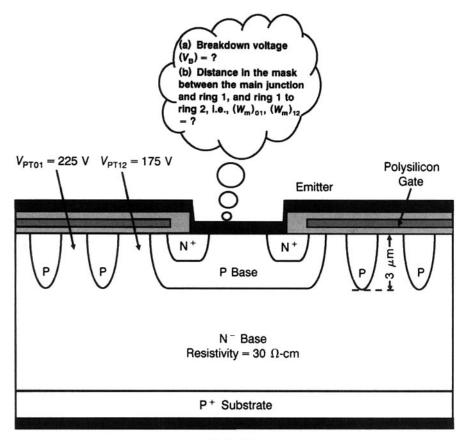

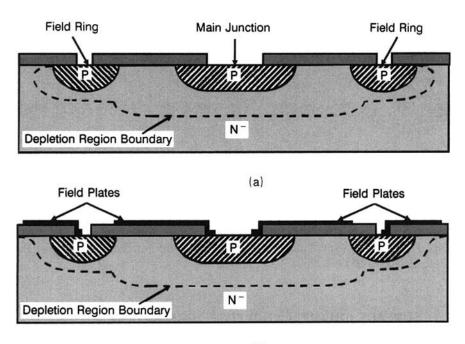

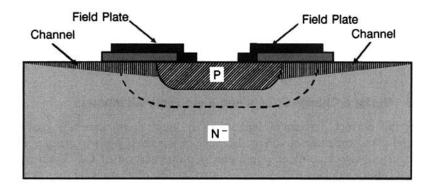

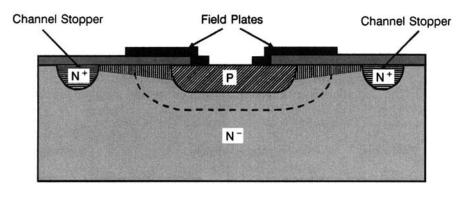

- 7.4 Field Ring and Field Plate Termination Design / 385

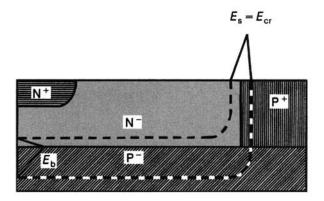

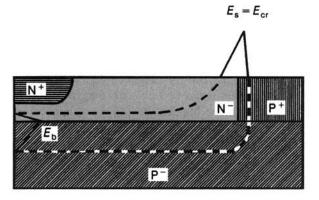

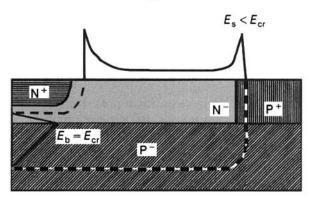

- 7.5 Surface Ion-Implanted Edge Termination / 394

- 7.6 Reduced Surface Electric Field (RESURF) Concept for Breakdown Voltage Enhancement in Lateral IGBT / 395

- 7.7 Concluding Comments / 398

Review Exercises / 399

References / 400

- Appendix 7.1 Multiplication Coefficient M / 402

- Appendix 7.2 V<sub>BR</sub> Equation / 403

- Appendix 7.3 Avalanche Breakdown Voltage  $(V_B)$  / 404

- Appendix 7.4 Punchthrough Voltage  $(V_{PT})$  / 406

- Appendix 7.5  $BV_{CYL}/BV_{PP}$  Equation / 406

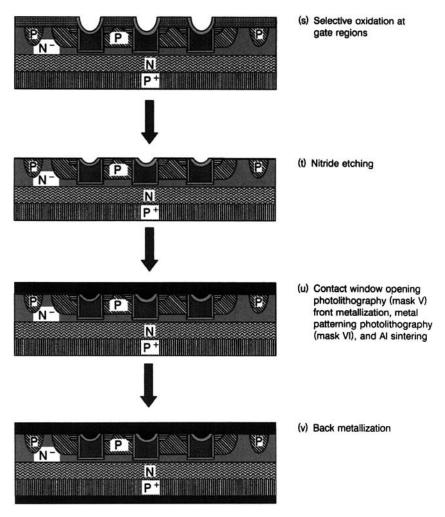

#### 8 IGBT Process Design and Fabrication Technology 411

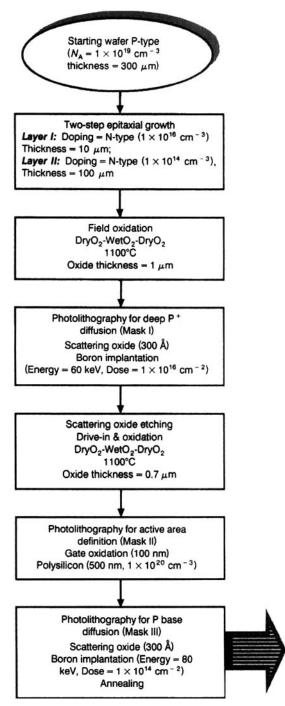

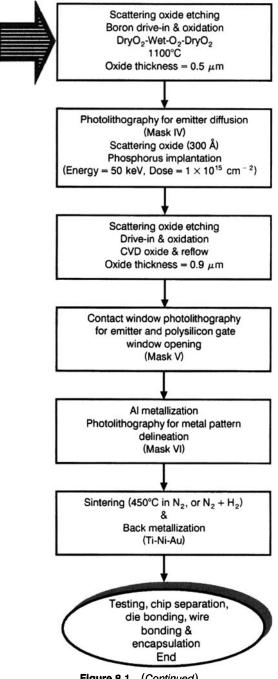

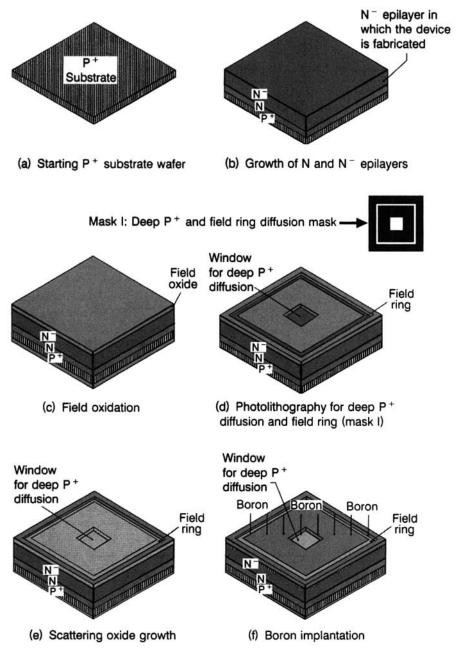

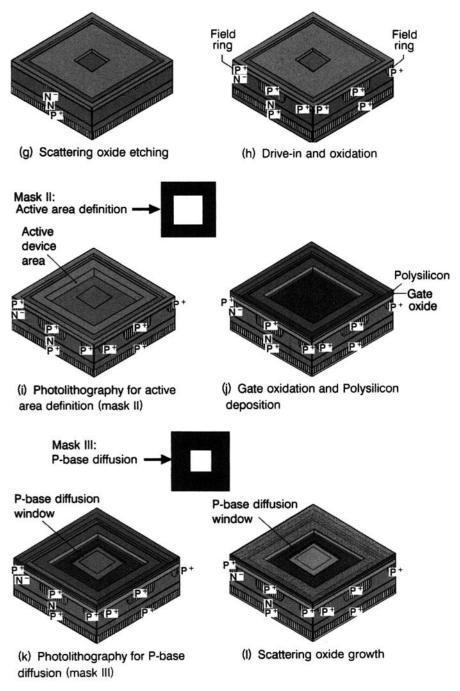

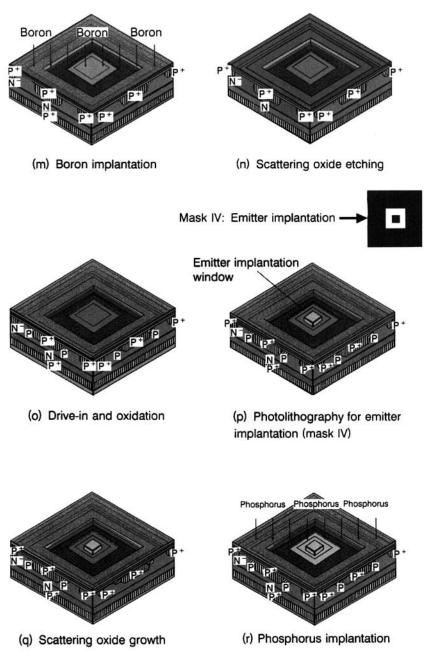

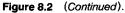

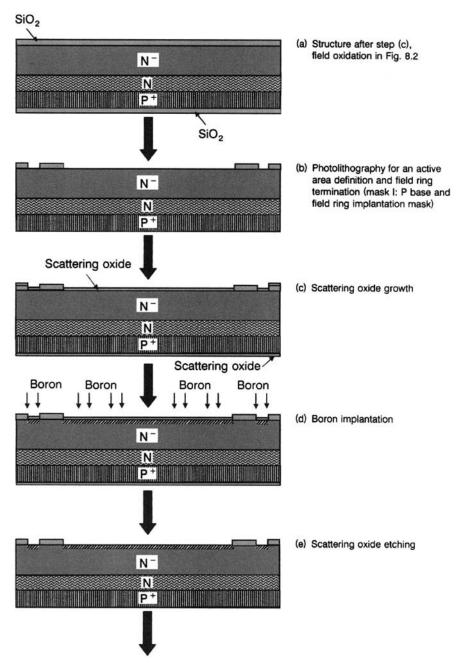

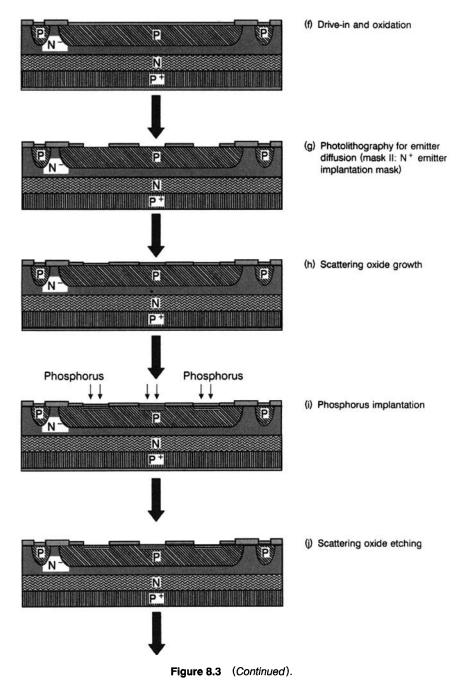

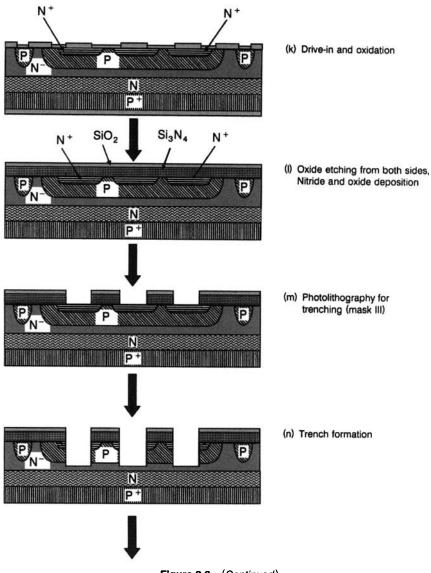

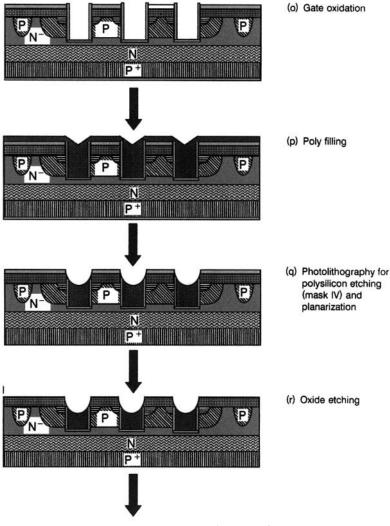

- 8.1 Process Sequence Definition / 412

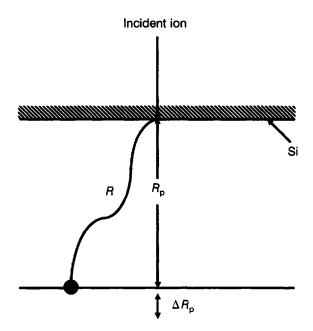

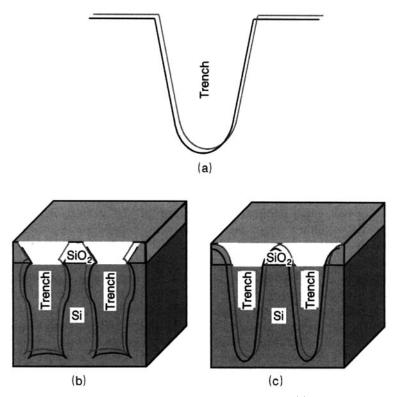

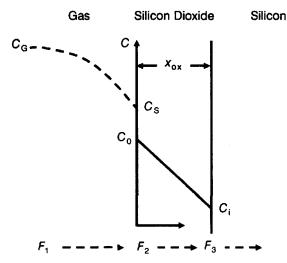

- 8.2 Unit Process Steps / 428

- 8.3 Process Integration and Simulation / 443

Review Exercises / 450 References / 452 Appendix 8.1 Thermal Oxidation of Silicon / 453 Appendix 8.2 Derivation of Eqs. (8.3)-(8.5) / 458

#### 9 Power IGBT Modules

- 9.1 Paralleling IGBTs, and Integration of Logic Circuits with Power Components / 465

- 9.2 Power Module Technologies / 470

- 9.3 Isolation Techniques / 475

- 9.4 Integrable Devices: Bipolar, CMOS, DMOS (BCD), and IGBT / 478

- 9.5 Power IGBT Driving, Temperature Sensing, and Protection / 479

- 9.6 Parasitic Components of IGBT Module Package / 482

- 9.7 Flat-Packaged IGBT Modules / 484

- 9.8 Desirable Features and Reliability of IGBT Modules / 486

- 9.9 Module Heat Sinks and Cooling / 489

- 9.10 Material Requirements for High-Power IGBT Modules / 490

- 9.11 State-of-the-Art and Trends / 491

Review Exercises / 495

References / 496

#### 10 Novel IGBT Design Concepts, Structural Innovations, and Emerging Technologies

- 10.1 Trade-Off Between ON-State Voltage Drop and Switching Losses / 499

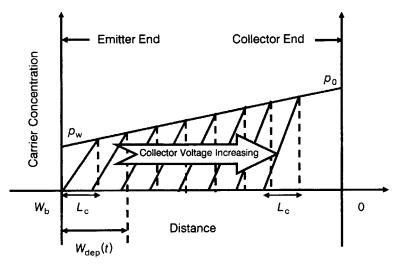

- 10.2 Parallel and Coupled PIN Diode-PNP Transistor Model of Carrier Distribution in the ON State of Trench IGBT / 502

- 10.3 Non-Self-Aligned Trench IGBT for Superior ON-State Performance / 505

- 10.4 Dynamic N-Buffer Insulated Gate Bipolar Transistor (DB-IGBT) / 505

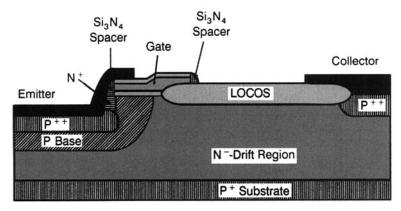

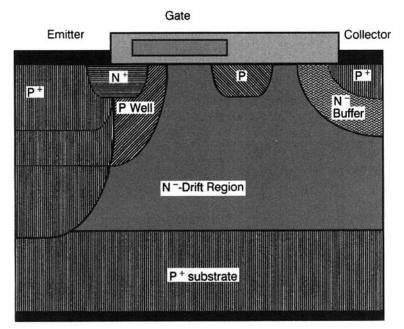

- 10.5 Lateral IGBT with Reverse Blocking Capability / 509

- 10.6 Lateral IGBT with High-Temperature Latchup Immunity / 511

- Self-Aligned Sidewall-Implanted N<sup>+</sup>-Emitter Lateral IGBT (Si-LIGBT) with High Latchup Current Capability / 512

- 10.8 Improved LIGBT Structure for Larger FBSOA / 513

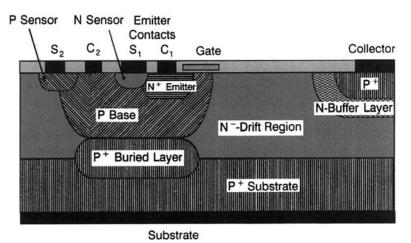

- 10.9 Lateral IGBT with Integrated Current Sensor / 514

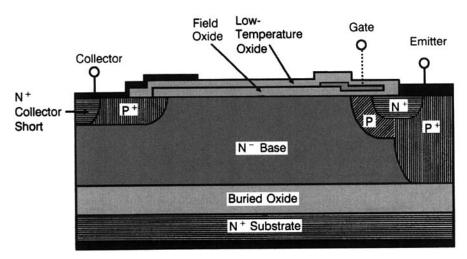

- 10.10 Dielectrically Isolated Fast LIGBTs / 515

- 10.11 Lateral IGBT in Thin Silicon-on-Insulator (SOI) Substrate / 516

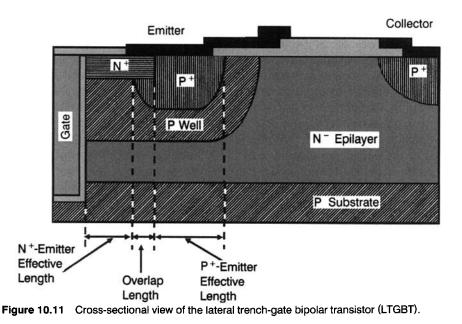

- 10.12 Lateral Trench-Gate Bipolar Transistor (LTGBT) for Improved Latchup Characteristics / 517

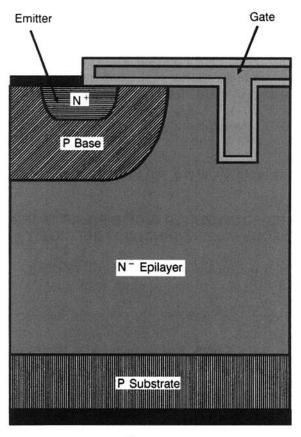

- 10.13 Trench Planar Insulated Gate Bipolar Transistor (TPIGBT) / 518

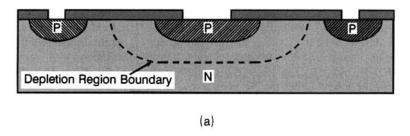

- 10.14 Clustered Insulated Gate Bipolar Transistor in Homogeneous Base Technology (HB-CIGBT) / 520

- 10.15 Trench Clustered Insulated Gate Bipolar Transistor (TCIGBT) / 522

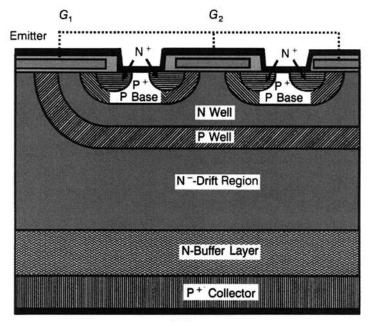

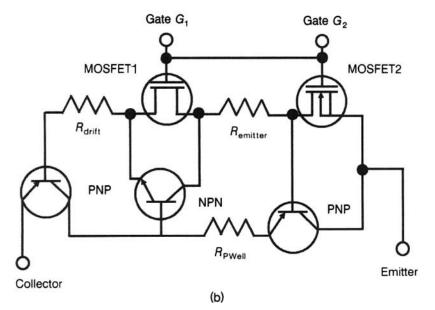

- 10.16 Double-Gate Injection-Enhanced Gate Transistor (DG-IEGT) / 523

- 10.17 SiC IGBTs / 525

- 10.18 Summary and Trends / 527

- Review Exercises / 527

- References / 529

- Appendix 10.1 Electron Current at the Collector Junction / 530

- Appendix 10.2 Transient Base Stored Charge  $Q_{base}(t) \neq 531$

- Appendix 10.3 Depletion Width in the Presence of Mobile Carrier Concentration / 532

- Appendix 10.4 Modulated Base Resistance  $(R_b)$  / 533

- Appendix 10.5 ON-State Voltage Drop Due to Recombination in the End Regions of the PIN Diode in the IGBT / 534

- Appendix 10.6 Energy Loss / 535

- Appendix 10.7 Excess Carrier Concentration  $p_w$  in the N<sup>-</sup> Base of TIGBT at the Emitter End / 536

- Appendix 10.8 ON-State Voltage Drop Across the N $^-$  Base of IGBT / 542

#### **11 IGBT Circuit Applications**

- 11.1 DC-to-DC Conversion / 545

- 11.2 DC-to-AC Inversion / 558

. •

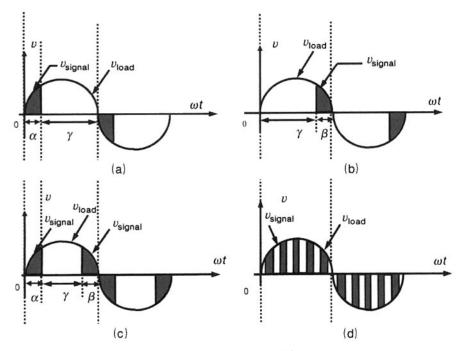

11.3 AC-to-DC Conversion / 570

11.4 Soft-Switching Converters / 575

11.5 IGBT Circuit Simulation / 587

11.6 Applications of IGBT Converters / 592

11.7 Summarizing Remarks / 604

Review Exercises / 605

References / 607

#### Index

609

About the Author

## PREFACE

The insulated gate bipolar transistor (IGBT) represents the most commercially advanced device of a new family of power semiconductor devices synergizing high-input impedance MOS-gate control with low forward-voltage drop bipolar current conduction. It reduces the size and complexity of controlling circuitry, thereby drastically reducing the system cost. Today, it is finding widespread applications in the medium-power and medium-frequency range in uninterruptible power supplies, industrial motor drives, and domestic and automotive electronics. During recent years, no other single device has been able to revolutionize the power device scenario and cast its impact on life of the common man as much as IGBT alone has done as a power conditioning device in domestic, consumer, and industrial sectors. Power is the *life blood* driving all electrical installations, machines, trains, computers, telecommunication networks, entertainment, and other household equipment, all over the world.

Despite the growing interest in this device since its conception, no book is currently available which is, to the best of my knowledge, completely devoted to the physics and technology of IGBT. There is a dearth of generalized treatises on physics and technology of semiconductor devices. Presently available books deal with semiconductor device physics, power semiconductor devices, thyristor physics, field-effect and bipolar transistor physics, MOS physics, and related device technologies. The overwhelming pervasion of IGBT in industrial and consumer electronics warranted publication of a new book that comprehensively treats the subject. The enormous interest in IGBT constituted my principal motivation in undertaking the project of writing this book.

As its title indicates, this book has a singularity of focus on IGBT. However, it goes without saying that IGBT represents an interesting combination of PIN diode, bipolar transistor, bipolar thyristor, and power DMOS-FET properties. So this text on IGBT prepares the reader not only with regard to IGBT but also with regard to the aforesaid devices that work in harmony resulting in IGBT characteristics. The expansive topical coverage of this book therefore incorporates useful material from both MOS and bipolar

aspects, greatly enhancing the utility of the book. To elaborate, the forward conduction characteristics of IGBT are controlled by conductivity modulation of the PIN diode as well as MOSFET channel length. The latching of the IGBT is governed by the current gain of the bipolar transistor and regenerative thyristor action. A smaller channel length yields low forward drop device but makes it vulnerable to latching of built-in parasitic bipolar thyristor. Controlling the forward blocking capability of the IGBT requires careful attention to planar floating field ring termination design. The reverse blocking voltage is dictated by beveling during chip dicing. Likewise, the turn-off time of IGBT is determined by the carrier lifetime and hence the reverse recovery waveform of the PIN diode. So, if we look with this broad perspective, learning about IGBT requires a good knowledge about these constituent devices. Thus although the focus is on a singular device, the remaining devices are automatically a part of the overall picture. The era of MOSbipolar combination devices has already dawned, and the book seeks to introduce the reader to this new era of intermixed technologies.

This book is written at the tutorial level to fulfill the needs of power device courses in electrical and electronics engineering and microelectronics engineering. The targeted audience of this book also includes practicing engineers and scientists. The students of today are the professionals of tomorrow. A careful blending of a tutorial design for students and specialist design for the practitioners has been made. By providing a large number of examples sprinkled throughout the text, as well as appending both questions and problems at the end of each chapter, it is hoped that classroom adaptation of the book will be easy with proper selection of course material. Up-to-date end-of-chapter references will provide the researcher a useful guide to the literature on IGBT. Thus the book caters to the requirements of a wide cross section of readership embracing students, professionals, and researchers.

A comprehensive, in-depth, and state-of-the-art treatment of the subject has been provided, encompassing a wide range of topics. Chapter 1 introduces the reader to the power semiconductor device scenario, the need for MOS-bipolar combination devices, and the birth of the IGBT. The working principle of IGBT is described in a simple way. The IGBT equivalent circuit is introduced, and the SPICE model is discussed. Packaging and handling precautions of IGBTs, gate driving circuits, and protection techniques are briefly presented.

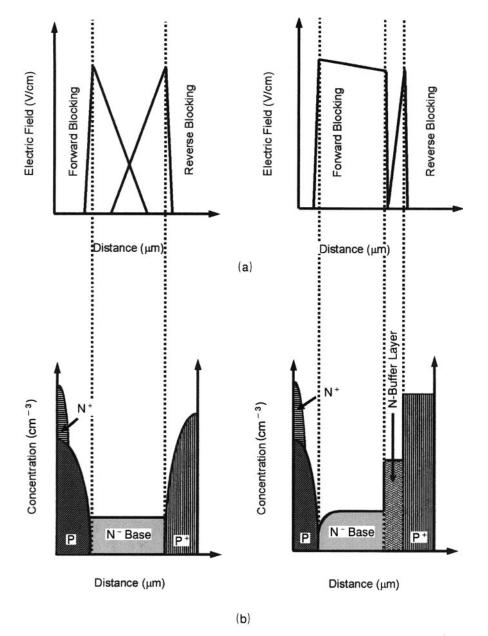

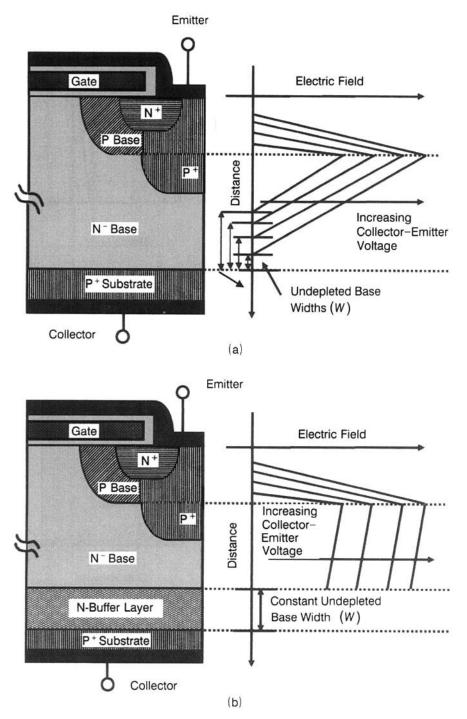

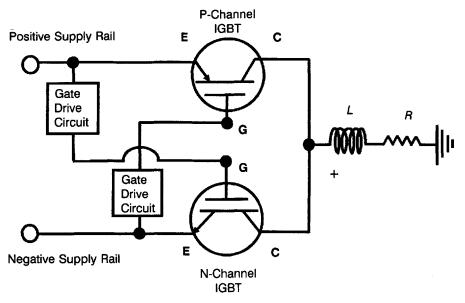

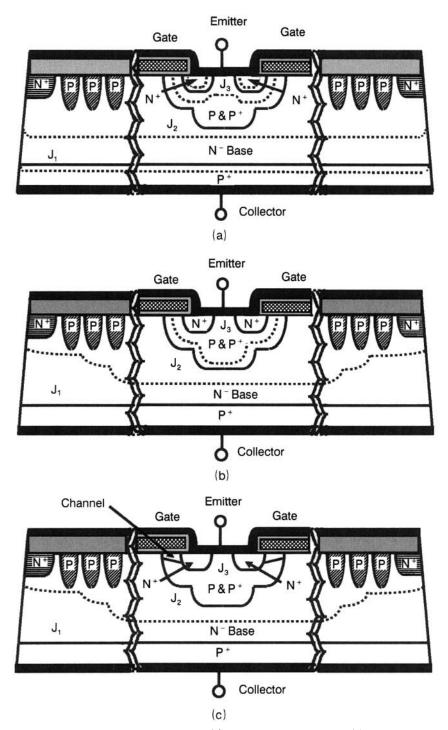

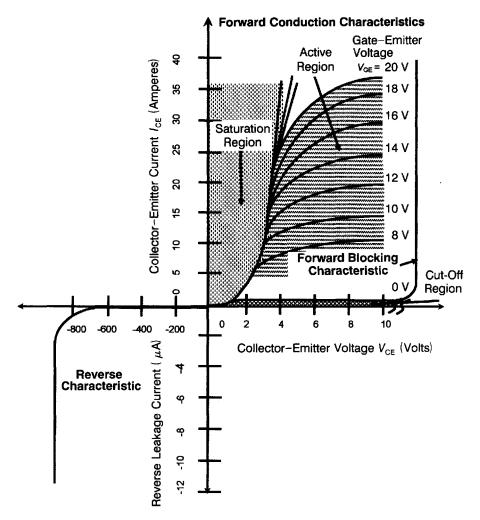

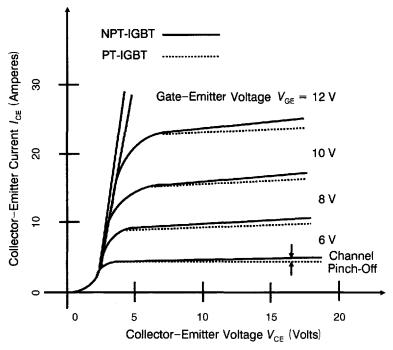

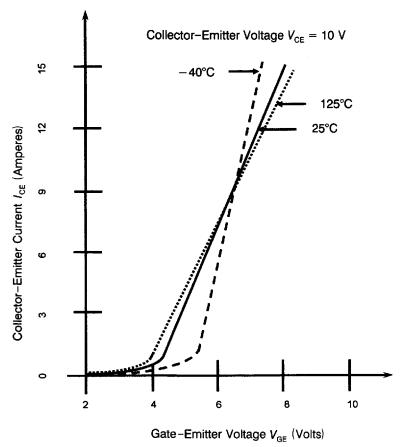

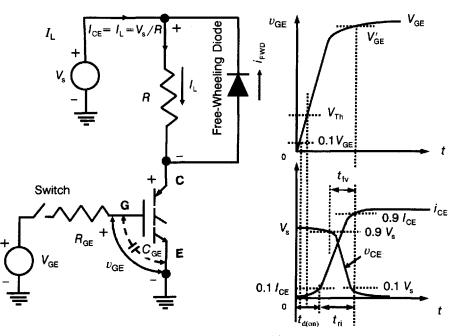

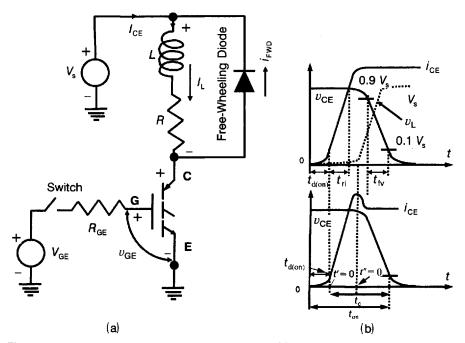

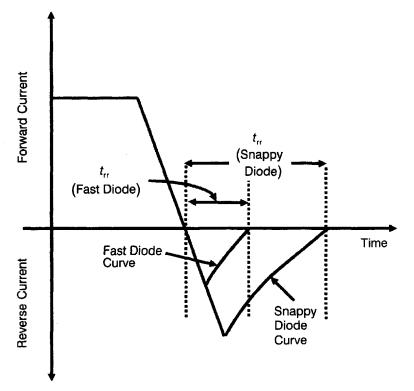

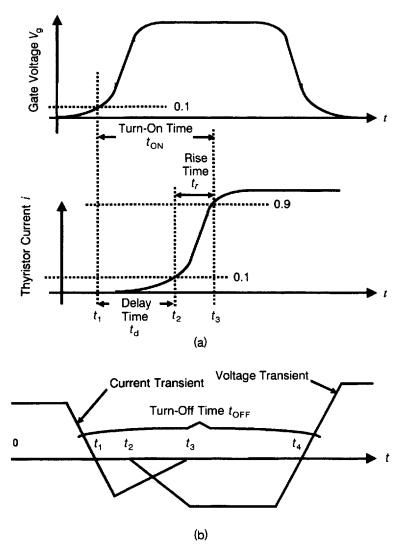

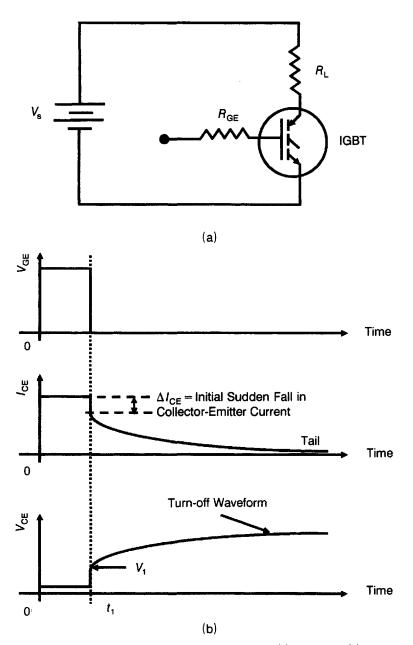

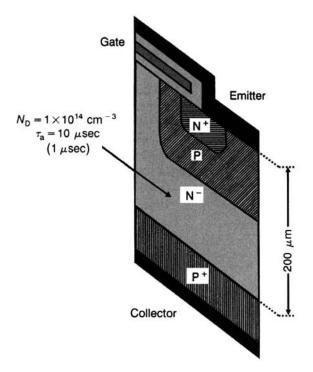

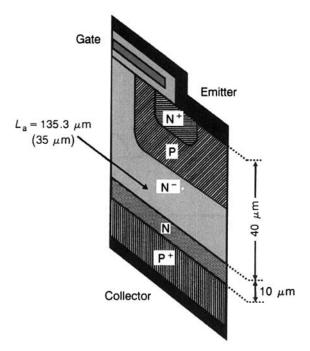

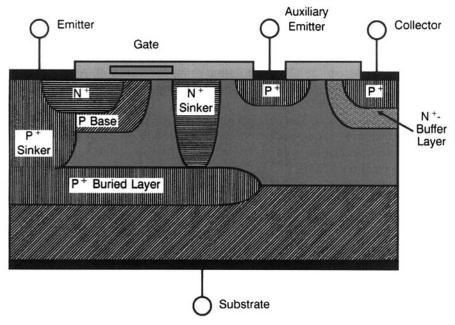

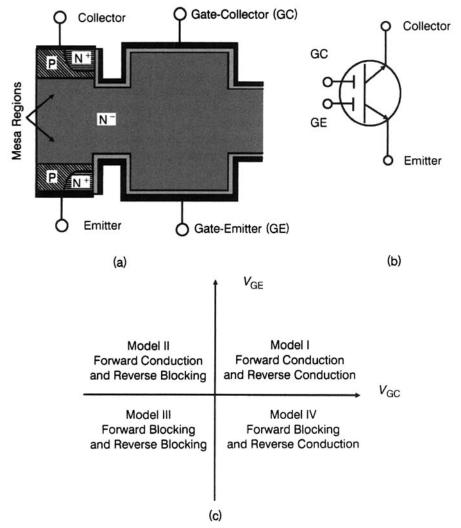

Chapter 2 summarizes the basic types of IGBTs, their operational features, performance characteristics, limitations, specifications, and applications. Lateral and vertical IGBT structures are discussed. Nonpunchthrough and punchthrough types of IGBTs are explained. Their doping profiles and operational differences are described. Different modes of operation of IG-BTs, such as forward conduction and blocking modes, are dealt with. IGBT turn-on and turn-off with resistive and inductive loads are analyzed. Softswitching concepts are outlined. Effects of temperature and nuclear irradiation on IGBT characteristics are pointed out. The working of trench-gate and self-clamped IGBTs is addressed.

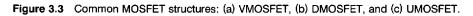

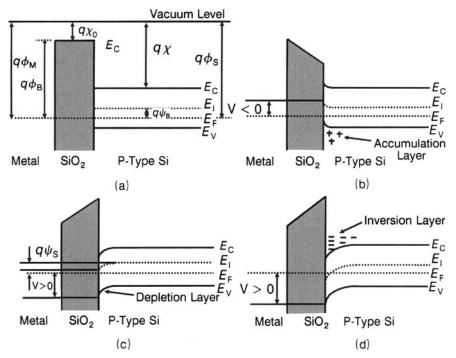

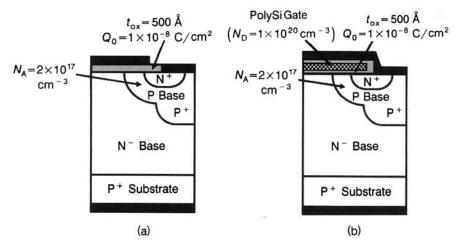

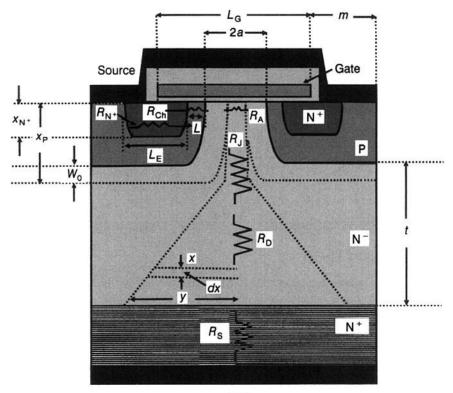

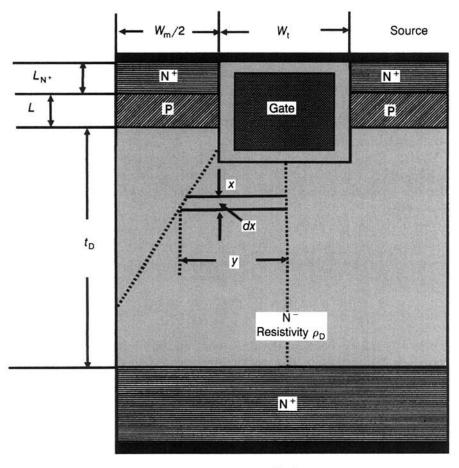

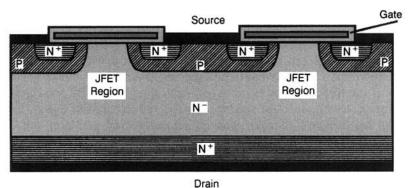

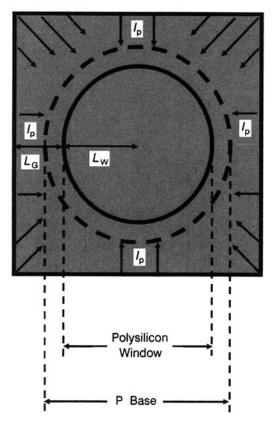

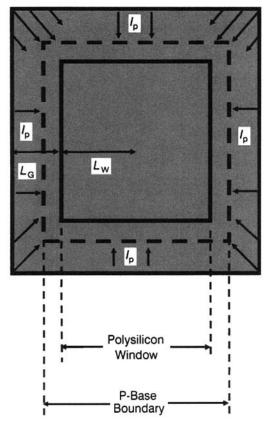

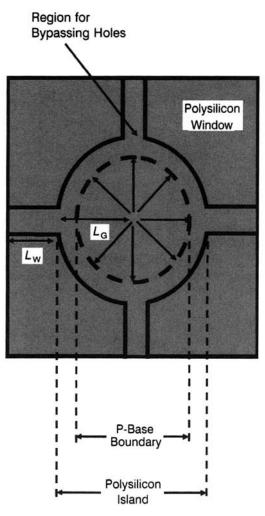

Chapter 3 covers the fundamentals of MOS structure including thermal equilibrium energy-band diagram, flat-band voltage, threshold voltage, capacitance effects, power DMOSFET structures, ON-resistance components, safe operating area, radiation and thermal effects on device characteristics, DMOSFET geometrical topologies, and so on, which are essential for understanding the physical principles of operation of IGBT.

Chapter 4 presents the theory of bipolar devices such as the PN-junction diode, the PIN rectifier, the bipolar junction transistor, the thyristor, and the junction field-effect transistor. After perusal of this chapter, the reader will be able to understand the essential principles of bipolar device operation.

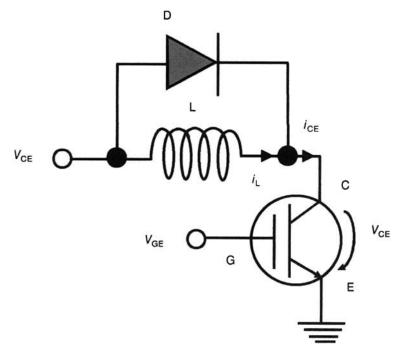

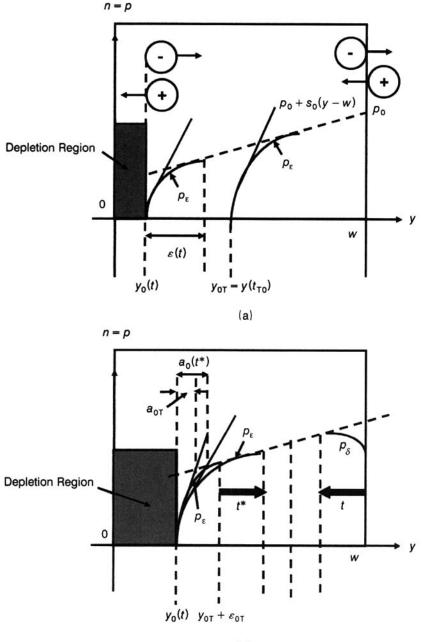

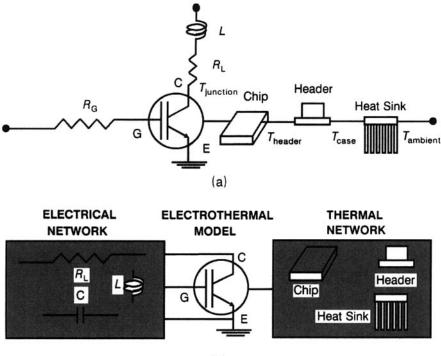

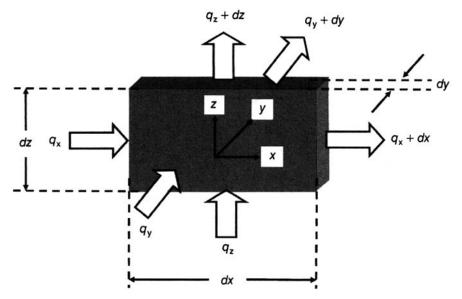

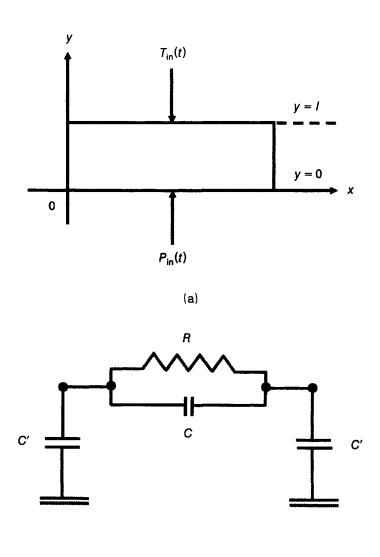

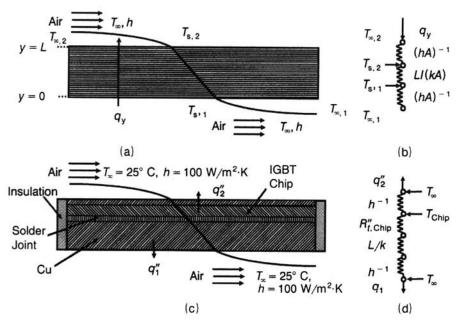

From Chapter 5 onwards, the study of IGBT models begins, including static, dynamic, and electrothermal behavior. Discussions of PIN rectifier–DMOSFET and bipolar transistor–DMOSFET models of IGBT are followed by analytical models of ON-state carrier distribution, two-dimensional effects, modeling of device–circuit interactions, transient analysis of IGBT circuits, and so forth.

Because latching is a serious problem with IGBTs, this issue is discussed in detail in Chapter 6, outlining the causes of latching and the techniques of providing latching immunization of IGBT structure. After explaining static and dynamic latchup, methods of latchup prevention are dealt with exhaustively.

Since the IGBT is a conglomeration of millions of elementary cells, Chapter 7 delves into the design techniques of IGBT unit cell using computer-aided design tools. The discussion begins with semiconductor selection and vertical structure design; followed by emitter and base doping profiles and channel length, transconductance and forward voltage drop, trade-off between conduction and switching losses, unit cell layout design, and intercell spacing; then N-buffer layer structural optimization; and concludes with field ring and field plate termination design, as well as other techniques of junction edge termination for surface electric field minimization and breakdown voltage enhancement.

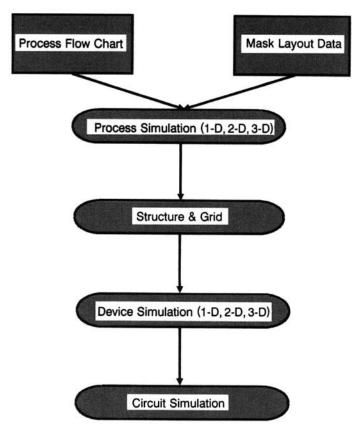

Chapter 8 describes the enabling technologies for power IGBT fabrication. Each unit process step is discussed, and the various steps are integrated for IGBT realization. Main steps are starting silicon preparation, epitaxial growth, polySi deposition, gate oxide fabrication, diffusion and ion implantation, mask making and microlithography, dry etching, and plasma processes, trench excavation, metallization, encapsulation, and electron irradiation for lifetime tailoring. Process simulation is also reviewed.

Chapter 9 addresses the subject of power IGBT modules and the associated technologies. Discussion of logic circuits and power device integration is followed by a summary of isolation techniques. Different types of protection and other accessories in the module are described. Flat-pack modules and materials technology for modules are also examined. Chapter 10 provides both a retrospective as well as a bird's-eye view of futuristic IGBT technologies. It surveys new design ideas and IGBT structures, giving projections on future trends in this rapidly expanding field. Structures considered include the non-self-aligned trench IGBT, dynamic N-buffer IGBT, lateral IGBTs with reverse blocking capability and high-temperature latch-up immunity, self-aligned sidewall-implanted  $N^+$  emitter lateral IGBT with high latchup current capability, LIGBT structure for larger FBSOA, lateral IGBT with integrated current sensor, dielectrically isolated fast LIGBT, lateral IGBT in thin (SOI) substrate, lateral trench-gate bipolar transistor, trench planar IGBT, clustered IGBT in homogeneous base technology, trench-clustered IGBT, double-gate injection-enhanced gate transistor, and many others.

Finally, Chapter 11 gives a perspective of the proliferating applications of IGBTs in circuits such as motor drives, automotive ignition, power supplies, welding, induction heating, and so on. Different types of converters such as DC-to-DC converters, DC-to-AC converters and AC-to-DC converters are mathematically analyzed. Soft-switching converters are touched upon. SABER and SPICE circuit models and design methods are also discussed.

It is earnestly hoped that the above topical coverage of this book will be useful for graduate/postgraduate students and researchers in this field. The book will serve as a textbook cum reference book on the subject. If the book serves the purpose of those for whom it is intended, I will deem my endeavors amply rewarded.

Although utmost care has been taken to ensure accuracy in presentation and content, no work can claim to be error-free and complete. Suggestions for improvement are cordially welcomed from our readers.

#### ACKNOWLEDGMENTS

It gives me immense pleasure to thank the director, senior scientists, and my colleagues at CEERI, Pilani, for encouragement in my efforts. I wish to thank the group leader and members of the erstwhile power device group, with whom I shared many insights into the power device physics and technology over our years of working together. I am obliged to Prof. Dr. Arnold Kostka and Mr. B. Maj, Technical University, Darmstadt, for guiding me into the simulation field.

It was a great opportunity working with my editor, Ms. Christina Kuhnen. I appreciate her prompt response and quick action on my problems, without which it would not have been possible to adhere to the schedule. I am grateful to the reviewers of the manuscript for their constructive criticism and for pointing out many errors and omissions, thereby bringing the book to its present form and contents. Any new book owes its origin to its predecessors as well as to research papers, reports, and review articles. I am indebted to the numerous authors of these works, many of whom are listed in the reference section at the end of each chapter. The interested reader is referred to the excellent works cited in the references to acquire an indepth knowledge of any specialized topic.

I am indebted to Dr. P. K. Khanna and Mr. Vijay Khanna for moral support.

Finally, I thank my daughter and wife for their love, patience, and understanding and for tolerating my long hours of work with grace, during the course of this project spanning over two years. Thanks from my heart to all of the above and also to anyone who may have directly or indirectly helped me in this work and whom I may have forgotten to mention.

VINOD KUMAR KHANNA

Pilani, India June 2003

## ABOUT THE AUTHOR

Vinod Kumar Khanna, was born in Lucknow, India in 1952. He is currently a senior scientist in the Solid-State Devices Division of Central Electronics Engineering Research Institute in Pilani, India. He received his Ph.D. in Physics in 1988 from Kurukshetra University and during the last 23 years has been involved extensively in device, process design, and fabrication of power semiconductor devices. His work has focused most notably on high-current and high-voltage rectifiers, high-voltage TV deflection transistors, the power Darlington transistor, inverter grade thyristor, and power DMOSFET and IGBT.

Dr. Khanna has published more than 30 research papers in international journals and conference proceedings and authored 2 books. He has presented papers at the IEEE-IAS Annual Meeting in Denver, Colorado in 1986 and worked as a guest scientist at Technical University, Darmstadt, Germany in 1999. He is a fellow of the IETE in India and is a life member of the Semiconductor Society and Indian Physics Association.

# 1

## POWER DEVICE EVOLUTION AND THE ADVENT OF IGBT

#### 1.1 INTRODUCTORY BACKGROUND

Power semiconductor devices are the essential components determining the efficiency, size, and cost of electronic systems for energy conditioning. The proliferating demand of controllable power electronic systems has promoted research on novel device materials, structures, and circuit topologies [1–7]. Present-day power devices are invariably fabricated using silicon as the base material. Among the upcoming semiconductor materials, silicon carbide has attracted the most attention [8–10]. The higher breakdown field of SiC ( $2.2 \times 10^6$  V/cm for 4H-SiC,  $2.5 \times 10^5$  V/cm for Si) enables it to offer a projected 200-fold reduction in specific ON resistance as compared to Si devices. SiC devices also promise superior high-temperature performance due to the large energy gap (4H-SiC: 3.26 eV; Si: 1.12 eV), high thermal conductivity (4H-SiC: 4.9 W/cm; Si: 1.5 W/cm), high chemical inertness, high pressure, and radiation resistance of this material.

Power device and process design engineers worldwide are relentlessly searching for the *perfect semiconductor switch* defined by the following characteristic features: (i) Very low driving losses: The switch has high input impedance so that the drive current is infinitesimally small. Furthermore, the drive circuit is simple and inexpensive. (ii) Insignificant ON state or forward conduction losses: The forward voltage drop at the operating current is zero. Additionally, the operational current density is large, making the chip small in size and cost-effective for a given current-carrying capability. (iii) Minimal

The Insulated Gate Bipolar Transistor (IGBT) Theory and Design, By Vinod Kumar Khanna. ISBN 0-471-23845-7 © 2003 Institute of Electrical and Electronics Engineers

OFF state or reverse blocking losses: Infinitely large reverse blocking voltage together with zero leakage current, even when exposed to elevated temperatures. (iv) *Extremely low switching losses*: Both the turn-on and turn-off times approach zero. In direct current (time period =  $\infty$ ) and low-frequency (large but finite time period) applications, these losses are very small because the switching times are much less than the respective periodic times.

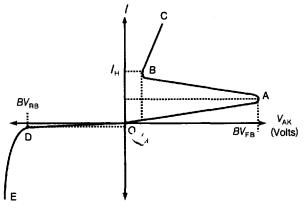

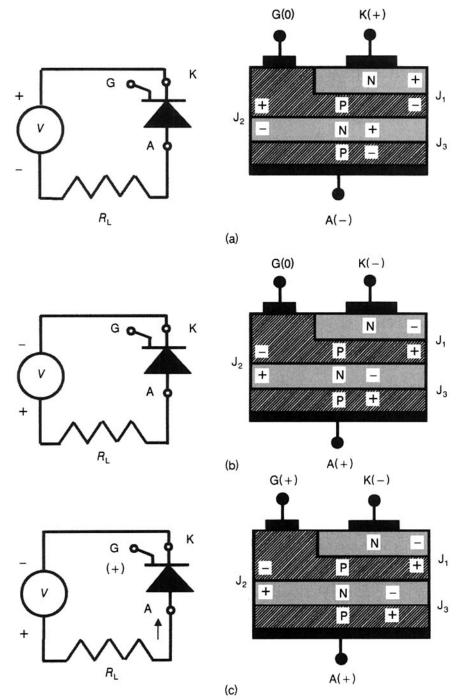

Advancements in power devices have revolutionized power electronics, and today's market offers a wide spectrum of devices intended for different applications. In applications where gate turn-off capability is not necessary, thyristors or silicon-controlled rectifiers (SCRs), the highest power density devices, have been the workhorse of power electronics [5–6], carrying high forward currents of ~ 3500 A with a forward drop < 2 V and withstanding  $\geq 6000$  V in the reverse direction. Thyristors have long been the solo devices catering to the megawatt power range, available in ratings like 12 kV/1.5 kA, 7.5 kV/1.65 kA, 6.5 kV/2.65 kA, and so on. They are classified as: phasecontrol thyristors used for a 50/60-Hz AC mains line and the inverter thyristors for higher frequencies of ~ 400 Hz. Typical turn-on and turn-off times are 1 and 200  $\mu$ sec. Thyristors are widely used in high-voltage DC (HVDC) conversion, static var compensators, solid-state circuit breakers, large power supplies for electrochemical plants, industrial heating, lighting and welding control, DC motor drives, and so on.

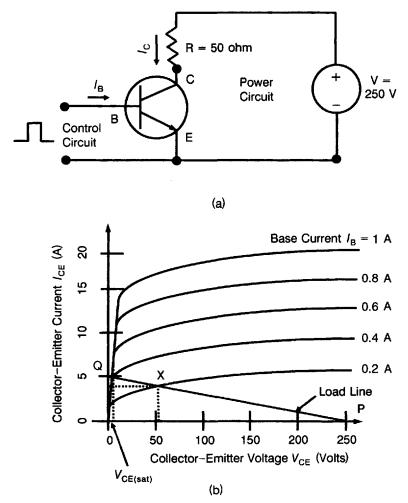

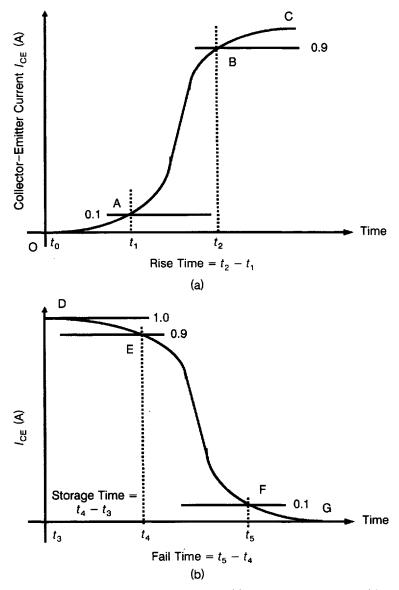

As turn-off is accomplished by collector-emitter voltage reversal in conventional thyristors, in applications where the load current is both turned on and turned off by the input signal, power bipolar junction transistors (BJTs) have been extensively used. Modular double or triple Darlington transistors (1200 V, 800 A) are used in converters with switching frequencies up to several kilohertz. Although bipolar transistors have turn-off time <1 µsec, they need very high base current drive both in the ON state and during turn-off. A competing device is the gate turn-off thyristor (GTO). It has forward current capability much higher than the BJT but requires excessively high gate drive current (750 A for 4000 V, 3000 A GTO). Its switching frequency is limited to 1-2 kHz with  $t_{on} = 4 \ \mu sec$  and  $t_{off} = 10 \ \mu sec$ . GTOs are used in DC and AC motor drives, uninterruptible power supply (UPS) systems, static var compensators, and photovoltaic and fuel cell converters from a few kilowatts to several megawatts of power. Improvements in the GTO structure, the gate drive, the packaging, and the inverse diode led to a new switching component, the integrated gate commutated thyristor (IGCT), a hard-switched GTO, which may be viewed as the hybridization of a modified GTO structure with very low inductive gate drive. Also, 4.5-kV and 5.5-kV IGCTs with currents up to 4 kA, as well as 6-kV/6-kA IGCTs [11-12], are commercially available, with further possibility of extension up to 10 kV, depending on market demand.

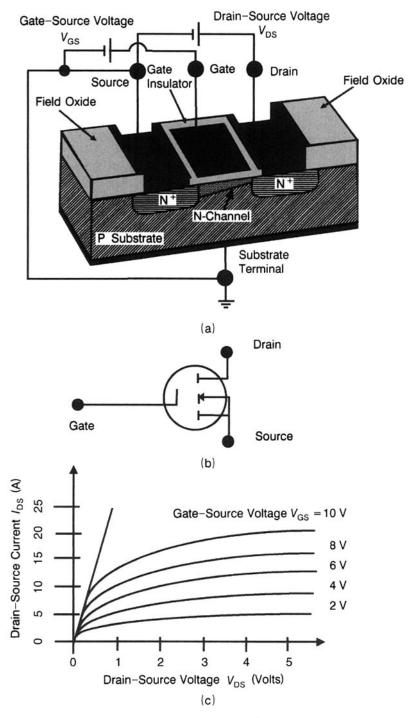

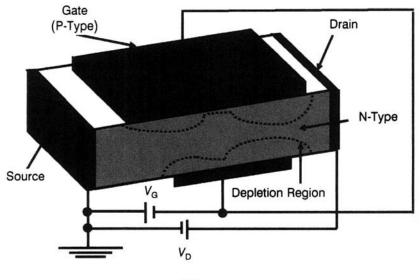

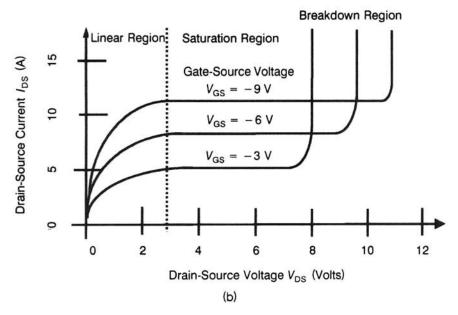

Another device accepted for gate turn-off applications is the vertical double-diffused MOSFET (VDMOSFET) [13]. Its gate drive current is very

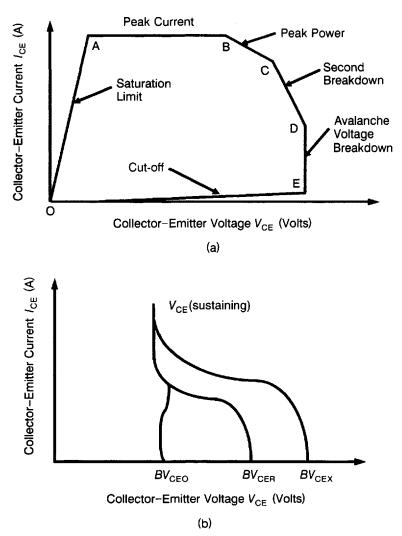

low, and 500-V/50-A VDMOSFET devices have switching frequencies of  $\sim 100$  kHz with turn-on and turn-off times below 100 nsec. Fast switching speed, ease of drive, wide safe operating area (SOA), and capability to withstand high rates of rise of ON-state voltage (dV/dt) have made VD-MOSFETs the logical choice in power circuit designs. However, VDMOS-FETs operate by unipolar conduction. So, their ON resistance drastically increases with drain-source voltage capability, restricting their exploitation to voltages less than a few hundred volts. Moreover, as the voltage rating increases, the inherent reverse diode shows increasing reverse recovery

Drain

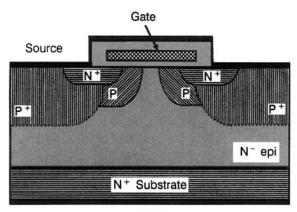

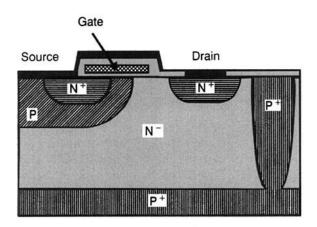

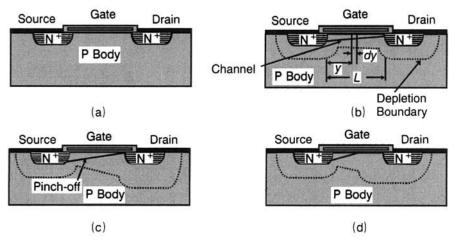

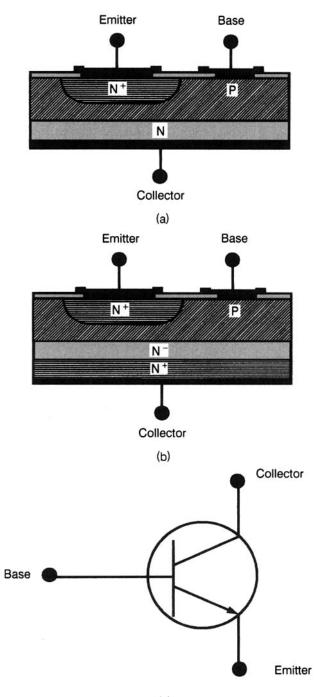

Figure 1.1 Structure of (a) conventional MOSFET and (b) Cool MOSFET.

charge  $(Q_{rr})$  and reverse recovery time  $(t_{rr})$ , causing more switching losses. Power VDMOSFETs have gained a strong foothold in low-voltage, low-power, and high-frequency applications such as switch-mode power supplies (SMPS), brushless DC motor (BLDM) drives, solid-state DC relays, automobile power systems, and so on. A new approach to reduce the high-voltage-sustaining drift zone resistance is offered by the Cool-MOS concept [14–15], allowing

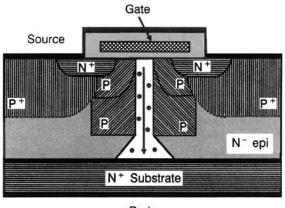

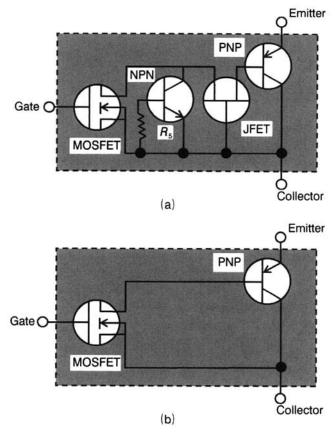

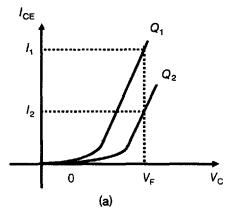

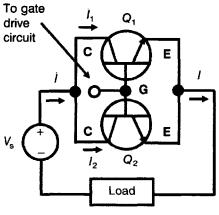

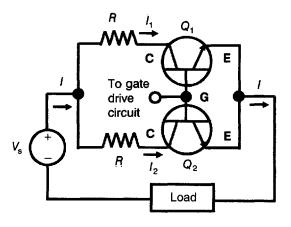

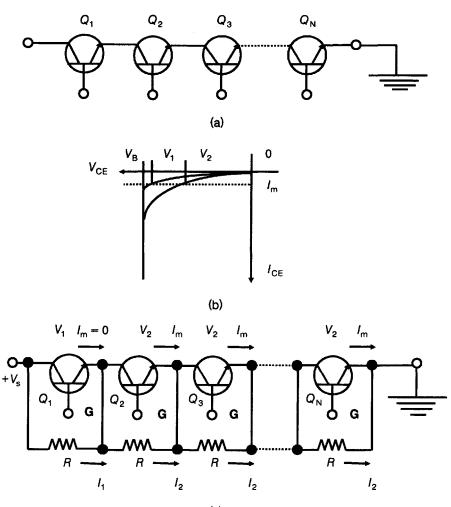

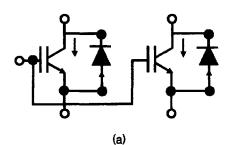

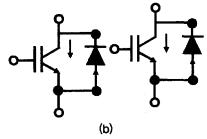

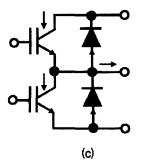

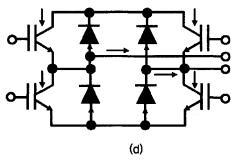

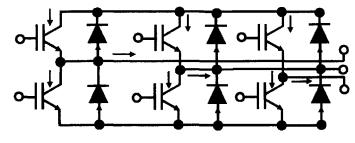

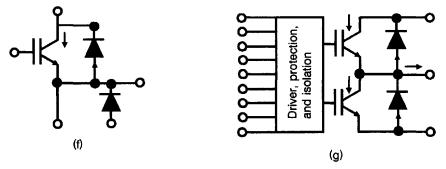

**Figure 1.2** MOS-bipolar combinations. (a) Darlington configuration. (b) Series or cascade configuration. (c) Parallel or cascode configuration.

reduction of ON resistance by a factor of 5-10 compared to conventional MOSFETs having equal area, in the breakdown voltage range 600-1000 V. Here vertical P stripes are inserted into the N-drift zone (Fig. 1.1). Due to the finely structured sequence of opposite polarity layers, a marked increase in doping occurs in this zone. In the blocking state, with increasing drain-source voltages, the space-charge region at the border between P and N stripes expands, eventually leading to the depletion of the epilayer. The OFF-state voltage therefore comprises both horizontal and vertical components. Due to horizontal extension of the depletion region, drift region thickness need not be large, leading to lower conduction and switching losses and also requiring less gate drive power. For withstanding higher voltages, the area with P stripes is made larger. Reduction in doping is not necessary, as in conventional MOSFETs. Thus in Cool MOSFET, an extra P-doped region is introduced in the N-drift region. This allows a much higher breakdown voltage to be achieved using a much higher doping concentration for the N-drift region than in a conventional MOSFET. The use of a high doping concentration for the N-drift region reduces the ON resistance of the device.

Thus we find that amongst the presently available power switches, each offers distinct advantages in certain applications but suffer from shortcomings in other areas. Thus, it was considered worthwhile to blend the properties of MOSFET and bipolar devices. Indeed, the amelioration of device parameters toward the ideal switch was considerably accelerated by the idea of MOS-bipolar combination. In the beginning, many MOS-bipolar merger alternatives were explored. The performance characteristics and limitations of the chief combinations are pointed out below. The Darlington configuration (Fig. 1.2a) provides a high current gain at high output currents but gives a larger forward voltage drop than a single transistor and longer turn-off time because negative base drive cannot be applied to the BJT base during turn-off. Consequently, it exhibits high switching losses. In the series or cascade configuration (Fig. 1.2b) the drawbacks include the increase of forward drop and the need to drive one gate along with one base. In the parallel or cascode Configuration (Fig. 1.2c), the BJT must be driven in harmony with the MOSFET for turn-off loss minimisation, thus restricting the useful cut-off frequency. The breakthrough overcoming the above limitations was achieved with the success of the insulated gate bipolar transistor (IGBT).

#### 1.2 INSULATED GATE BIPOLAR TRANSISTOR

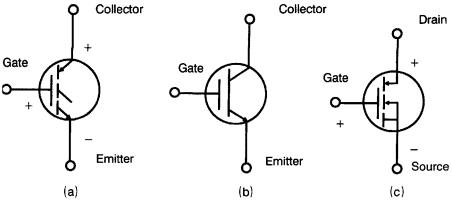

Other names of this device include the insulated gate rectifier (acronym IGR), conductivity-modulated FET (COMFET), gain-enhanced MOSFET (GEMFET), BiFET (bipolar FET), and injector FET. It is a prime member of the family of MOS-bipolar combination devices. Other members of this

family are the MOS-gated thyristor (MOS-SCR) and MOS-controlled thyristor (MCT).

The IGBT was first demonstrated by Baliga in 1979 [16] and then in 1980 by Plummer and Scharf [17], by Leipold et al. [18], and by Tihanyi [19]. Advantages of IGBT were comprehensively described by Becke and Wheatley [20] and by Baliga et al. in 1982 [21] and 1983 [22]. More work was carried out by Russell [23], Chang et al. [24], Goodman et al. [25], Baliga et al. [26], Yilmaz et al. [27] and Nikagawa et al. [28]. The IGBT was commercially introduced in the marketplace in 1983. Since then there has been a significant improvement in the device ratings and characteristics, from the initial 5 kW for discrete IGBTs to more than 200 kW for IGBT power modules. Presently, several large companies are manufacturing this device, notable among them being IXYS Corporation, International Rectifier, Powerex, Philips, Motorola, Fuji Electric, Mitshubishi Electric, Hitachi, Toshiba, Siemens, Eupec, and so on. Today, the IGBT is an established replacement of the power BJT, Darlington transistor, MOSFET, and GTO thyristor in the medium voltage (600-2500 V), medium power (10 kW), and medium frequency range up to 20 kHz. Also, 600-V/50-A IGBTs capable of hard switching at 150 kHz are commercially available. Just as the power MOSFET has replaced the BJT in low-voltage applications (< 200 V), the IGBT has replaced the BJT in the medium-voltage range 200-2000 V and is suitable for compact smart power modules. Modules with 6500-V blocking voltage capability and 200-, 400-, and 600-A current have been reported. High-voltage IGBTs are used for electric traction such as streetcars and locomotives. High-power IGBTs are challenging the dominance of GTOs in the megawatt range due to their high speed, large RBSOA, and easy controllability. However, the available power ratings of IGBTs are lower than those of GTOs, up to a rated switch power of 36 MVA (6 kV, 6 kA). MOS-SCR and MCT are alternative candidates for these applications. The injection-enhanced IGBT or IEGT [29] is a promising candidate as a next-generation high-power MOS-gated device, which can replace GTO. Basically, IGBTs operate like a bipolar transistor and have a smaller carrier accumulation in the N-type high resistance layer. So, IGBTs with forward blocking voltage > 1700 V suffer from a much larger ON-state voltage drop than do gate turn-off thyristors (GTOs). To reduce the ON-state voltage, a carrier profile similar to the GTO is adopted in the IEGT, retaining the easy gate drivability and turn-off capability of IGBT. The 4500-V IEGT has a forward drop  $V_{\rm F}$  of 2.5 V at 100 Å/cm<sup>2</sup>. Current density of IEGT at  $V_{\rm F} = 2.5$  V is 10 times that of UMOS-IGBT (U-groove metal-oxide semiconductor-IGBT).

Today, minimum feature sizes in IGBT chips are shrinking down to 1  $\mu$ m and submicron technologies using direct stepping on wafer. The IGBT is the most widely used power device in the medium power and medium frequency range, finding widespread applications in AC motor drives, traction control, inductive heating systems, radiological systems (X-ray tubes), uninterruptible power supplies (UPS), switch-mode power supplies (SMPS), static var and

| Sector<br>No. | Power Electronics Sector                     | Applications                                                                                                                                                                                                      |

|---------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | Low-power sector ( < 10 kW)                  | Switching power supplies for comput-<br>ers, printers, facsimile machines,<br>and consumer electronics; automo-<br>tive electronics, heating and light-<br>ing circuits, small motor drives,<br>and UPS.          |

| 2             | Mid-power sector (between 10<br>kW and 1 MW) | Solid-state drives for multi-horse-<br>power induction motors, UPS, and<br>machines for factory automation<br>(using smart power ICs and mod-<br>ules); heating, ventilation, and air-<br>conditioning equipment. |

| 3             | High-power or megawatt-<br>power sector      | Solid-state motor drives for heavy motors, HVDC, UPS, etc.                                                                                                                                                        |

Table 1.1 Applications of Different Power Electronic Sectors

harmonic compensators, and so on. Table 1.1 shows that major marketing opportunities for power electronics reside in the low- and medium-power sectors. As the IGBT pervades these sectors, the utility of this device escalates.

A close look at the power electronics scenario reveals that the area between 100 V and 1000 V has vastly benefited from IGBT development and modular packaging concepts. IGBTs have gained immense importance since their introduction in the market in 1983. The IGBT is readily interconnected with control circuitry in low-cost plastic modules that are used for driving small machines for factory automation. The high output impedance of IGBTs allows parallel connection of many IGBTs. No device draws more current than its neighbors, resulting in better current sharing. So for higher load current applications, current up-scaling is accomplished by paralleling several devices. Today, 600-V, 1200-V, 2500-V, and 3300-V IGBTs/IGBT modules are commercially available up to current ratings of 2400 A. Also, 4.5- and 6.5-kV IGBT modules have been reported.

High-current and high-voltage IGBTs (> 1700 V, 1000 A) are used for traction and industrial applications. Both IGBTs and IGCTs have the potential to decrease the cost and increase the power density of pulse-width modulation voltage-source converters (VSCs), because of snubberless operation. The high voltage requirement of electrical power transmission and distribution (HVDC) systems is handled by series stacking of IGBTs. As traction systems use parallel connection of devices and HVDC employs series connection, the nature of these applications differs [30]. Consequently, the failure modes of devices in these systems are of opposite nature: *open-circuit failure* for traction and *short-circuit failure* for HVDC. These counter require-

ments have led to two different packaging concepts: the die-soldered, nonhermetic, wire-bonded module, mounted by bolting to heat sink and single-side cooled; and the dry contact, hermetic, presspack, mounted by pressure stacks and double-side cooled, as adapted from thyristor technology.

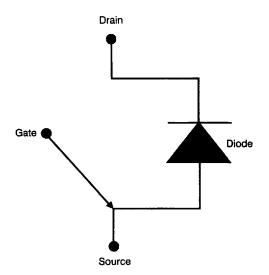

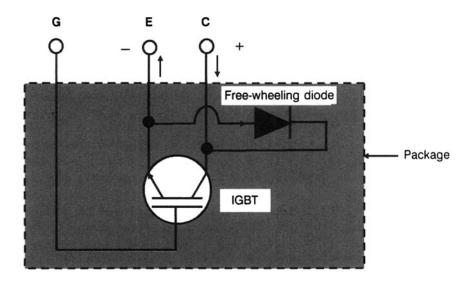

#### 1.3 ADVANTAGES AND SHORTCOMINGS OF IGBT

IGBT is created by the functional integration of MOS and bipolar device technologies in monolithic form. It combines the best attributes of the existing families of MOS and bipolar devices (Table 1.2) to achieve optimal device characteristics, approximately fulfilling the criteria of the ideal power switch. Moreover, it has no integral diode like the MOSFET. In an IGBT, absence of the diode provides the user an opportunity to choose an external fast recovery diode suitable for a particular application or to purchase a "co-pak" having the IGBT and the diode in the same package. So, problems associated with the integral diode across the P-base/N-drift region in the power MOSFET are absent in the IGBT.

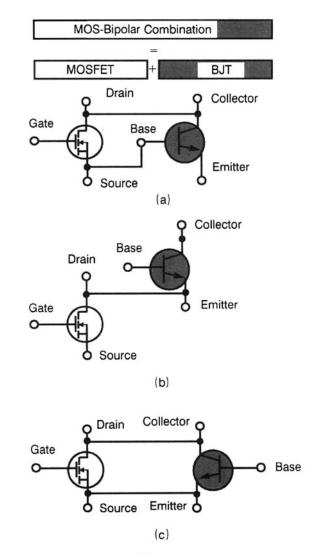

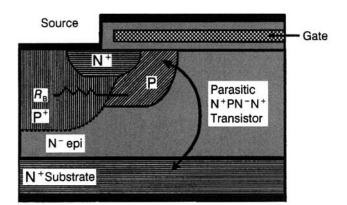

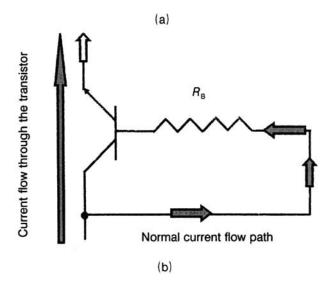

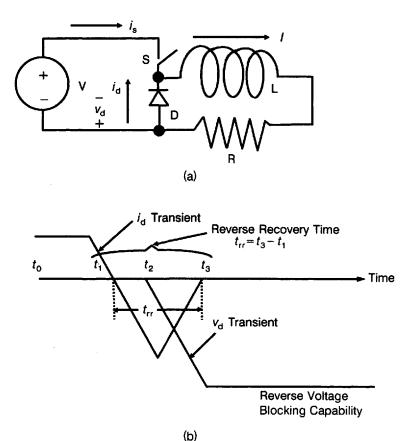

The major difficulty with the MOSFET is the reverse recovery characteristic of the diode. High carrier lifetime in the N-drift region of as-fabricated MOSFETs makes reverse recovery of diode slow accompanied by a large recovery charge. With increasing voltage ratings, the integral diode exhibits higher reverse recovery charge and reverse recovery time, and thereby high losses. Furthermore, this charge produces a high reverse recovery current, which increases with di/dt. The high current flowing through the transistors in the circuit causes excessive power dissipation and thermal stresses on them. To improve the reverse recovery characteristic, electron irradiation is performed with subsequent annealing of positive oxide charge around 200°C. But still the integral diode in the MOSFET creates problems due to the existence of a bipolar transistor in the structure (Fig.1.3). The voltage drop across the base resistance of this bipolar transistor due to current flowing during reverse recovery forward biases the emitter-base junction of the transistor. The high voltage developed across the transistor often leads to second breakdown. Thus actuation of the bipolar transistor during diode reverse recovery causes serious problems in power MOSFETs.

The IGBT provides high input impedance MOS gating, together with large bipolar current-carrying capability, while designed to support high voltages. A circuit designer views the IGBT as a device with MOS input characteristics and bipolar output characteristics—that is, a voltage-controlled BJT device. This feature simplifies, to a large extent, the driving circuit. This, combined with IGBT ruggedness, eliminates the complexity of protective snubber circuits, allowing simple, lightweight, and economic power electronic systems to be constructed with IGBTs. Over and above, integration of MOS control with bipolar conduction is a way of building intelligence in the chip because "electronic intelligence" is intimately related to the controlling strategy for

| Serial<br>No. | MOSFETs                                                                                        | Bipolars                                                                                                 |

|---------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

|               | Features:                                                                                      | Features:                                                                                                |

| 1             | Single-carrier device                                                                          | Two-carrier device                                                                                       |

| 2             | Works by majority carrier drift                                                                | Operates by minority-carrier diffusion                                                                   |

| 3             | Voltage driven                                                                                 | Current driven                                                                                           |

| 4             | Drain current $\alpha$ channel width                                                           | Collector current $\alpha$ emitter length and area                                                       |

| 5             | Higher breakdown voltage is achieved<br>using lightly doped drain region                       | Higher breakdown voltage requires lightly doped collector region                                         |

| 6             | Current density for given voltage drop<br>is high at low voltages and low at<br>high voltages  | Current density for given voltage drop<br>is medium, and severe trade-off exists<br>with switching speed |

| 7             | Square-law current-voltage characteristics<br>at low current and linear I-V at high<br>current |                                                                                                          |

| 8             | Negative temperature coefficient of drain current                                              | Positive temperature coefficient of collector current                                                    |

| 9             | No charge storage                                                                              | Charge stored in base and collector                                                                      |

|               | Pros:                                                                                          | Cons:                                                                                                    |

| 1             | High input impedance $Z \sim 10^9 - 10^{11} \Omega$                                            | Low input impedance $Z \sim 10^3 - 10^5 \Omega$                                                          |

| 2             | Minimal drive power. No DC current<br>required at gate                                         | Large drive power. DC current needed<br>at base continuously                                             |

| 3             | Simple drive circuit                                                                           | Complex drive circuit as large positive                                                                  |

| 9             | shiple drive chealt                                                                            | and negative currents are required                                                                       |

| 4             | More linear operation and less harmonics                                                       | More intermodulation and cross-<br>modulation products                                                   |

| 5             | Devices can be easily paralleled                                                               | Devices cannot be easily paralleled                                                                      |

| 6             | No thermal runaway                                                                             | Prone to thermal runaway                                                                                 |

| 7             | Less susceptible to second breakdown                                                           | Vulnerable to second breakdown                                                                           |

| 8             | Maximum operating temperature<br>= $200^{\circ}C$                                              | Maximum operating temperature $= 150^{\circ}C$                                                           |

| 9             | Very low switching losses                                                                      | Medium to high switching losses<br>depending on trade-off with<br>conduction losses                      |

| 10            | High switching speed, which is less temperature-sensitive                                      | Lower switching speed, which is more sensitive to temperature                                            |

|               | Cons:                                                                                          | Pros:                                                                                                    |

| 1             | High ON resistance                                                                             | Low ON resistance                                                                                        |

| 2             | Low transconductance                                                                           | High transconductance                                                                                    |

| Table 1.2 | Features, Pros and | Cons of MOSFETs and Bipolars |

|-----------|--------------------|------------------------------|

|-----------|--------------------|------------------------------|

**Figure 1.3** (a) Parasitic bipolar transistor in power MOSFET structure. (b) Equivalent circuit showing the parasitic bipolar transistor and the resistance  $R_{\rm B}$  of the P base underneath the N<sup>+</sup> source.

switching the power device on and off. Thus it represents a step toward "smart or intelligent power switching." It must not be forgotten here that besides the BJT and the MOSFET, features of P-N junction diodes, P-I-N rectifiers, and the thyristor are also visible in the IGBT.

Let us make a comparative assessment of current-carrying capacities of IGBT with MOSFET and BJT. We note that IGBTs are fabricated in a range of voltage ratings: for example 300-V IGBTs are used for applications based

| Property            | IGBT                | FET                  |  |

|---------------------|---------------------|----------------------|--|

| Junctions           | Two-junction device | Zero-junction device |  |

| Forward voltage     | > 0.7 V             | > 0 V                |  |

| Blocking voltage    | 1200 V              | 500 V                |  |

| Forward current     | 400 A               | 50 A                 |  |

| Turn-on time        | 0.9 µsec            | 90 nsec              |  |

| Turn-off time       | $1.5 \mu sec$       | 150 nsec             |  |

| Switching frequency | > 150 kHz           | > 1 MHz              |  |

Table 1.3 Features of IGBT and FET

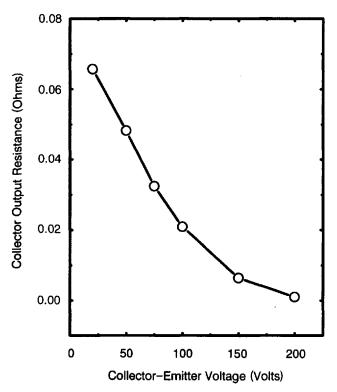

on rectified 110-V AC line, 600-V IGBTs for rectified 220-V AC line, and 1200-V IGBTs for rectified 440-V AC line. The example of IGBTs with 600-V blocking capability is cited. Its room-temperature current density is 200 A/cm<sup>2</sup>, which is 20 times that of the equivalent power MOSFET and 5 times that of the BJT having a current gain of 10 and forward drop of 2 V. At 200°C, the current density of IGBT becomes 60 times that of the MOSFET. To quote another illustrative case, the ON resistance of a 400-V IGBT is 0.1  $\Omega$  at 20 A, which is 0.1 that of the ON resistance of an equally rated MOSFET. Not only is the ON resistance of IGBT low, its temperature coefficient (TCR) is much smaller than MOSFET.

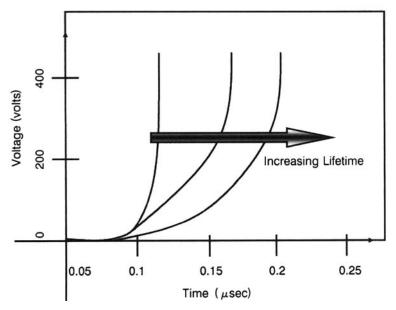

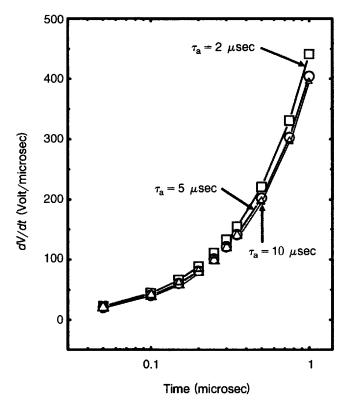

Now concerning the disadvantages of the IGBT, the major penalty paid by this hybridization of MOS and bipolar properties, is the slower switching of the IGBT compared to that of the power MOSFET (Table 1.3). Nevertheless, an interesting feature of IGBT is that its turn-off time can be decreased by electron or proton irradiation at the expenditure of an increase in forward drop. This unique capability endows the IGBT with the valuable opportunity of trading off between switching and conduction losses to cater to the power switching requirements of a broad application range. To elaborate, it is noted that for circuits operating at low frequencies with large duty cycles, such as the line-operated phase-control circuits, where conduction losses dominate over switching losses, turn-off times from 5 to 20  $\mu$ sec are sufficient. For high-frequency circuits with short duty cycles (e.g., AC motor drives working at 1-20 kHz switching frequencies), the necessary turn-off times cover the range 500 nsec to 2  $\mu$ sec. For still higher frequency circuits (e.g., switching power supplies operating at 20-100 kHz), the required turn-off times lie in the range from 100 to 500 nsec. Suitable IGBTs can be fabricated for all the above applications, compromising between the forward drop and turn-off time specifications.

It must be mentioned here that the IGBT requires a minimum forward voltage of at least 0.7 V before turning on, whereas the MOSFET can conduct with  $V_{\rm DS} > 0$  V. Therefore, in low supply voltage applications (e.g., 12-V automotive electronics), IGBT is not a good choice.

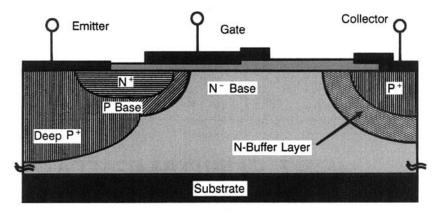

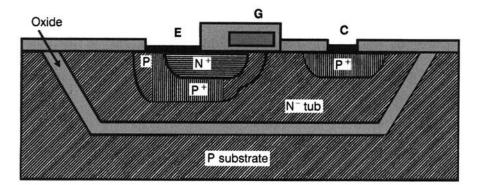

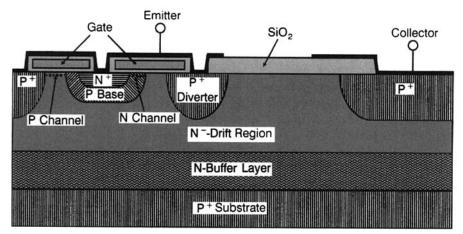

#### 1.4 IGBT STRUCTURE AND FABRICATION

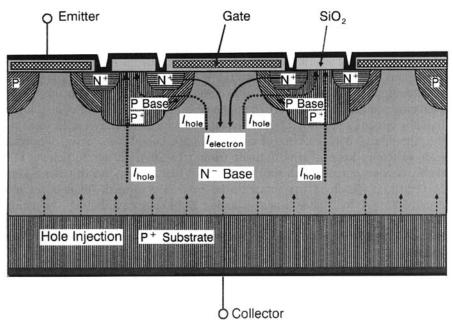

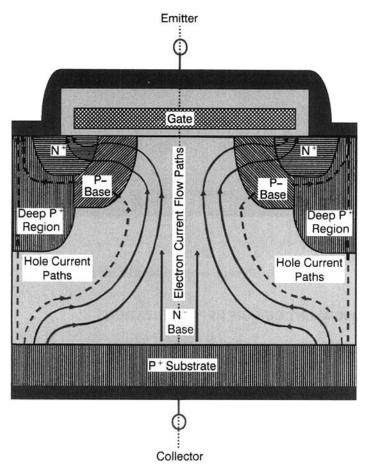

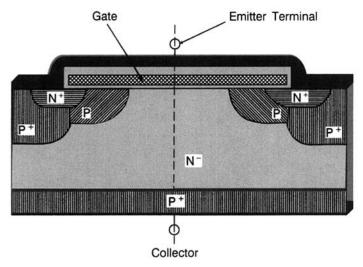

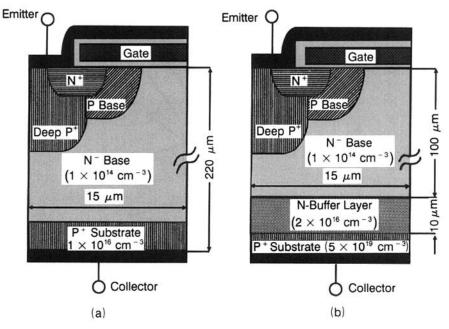

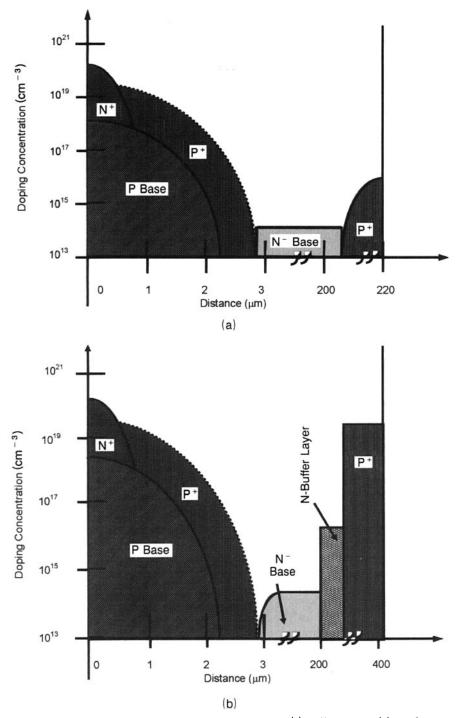

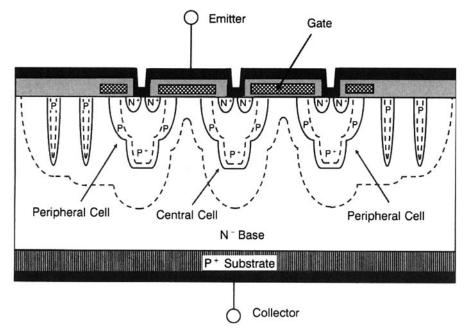

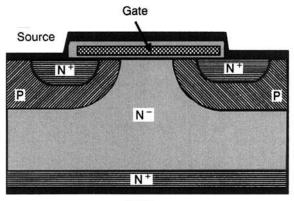

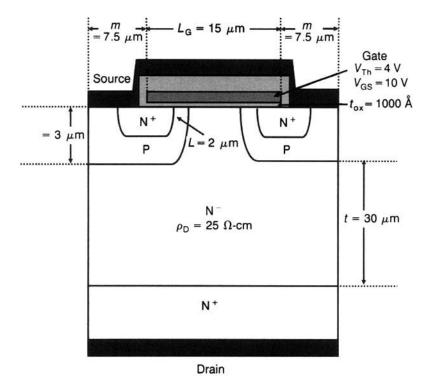

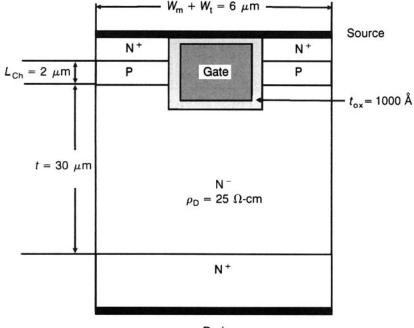

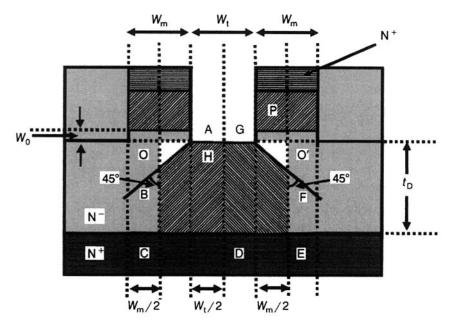

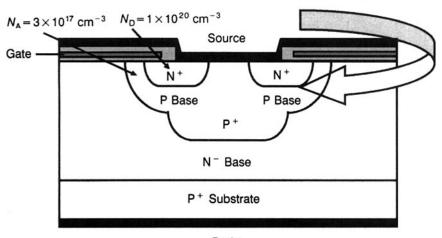

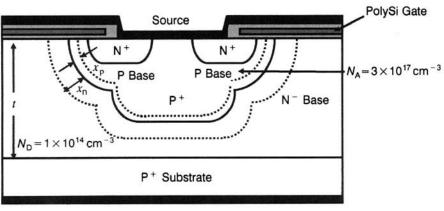

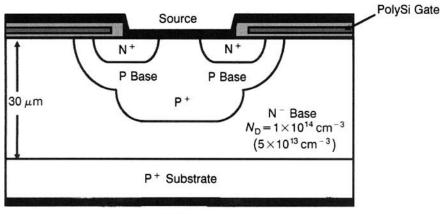

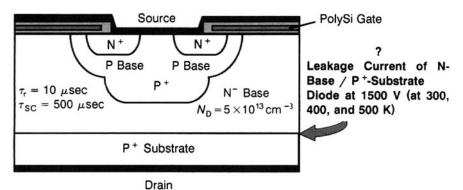

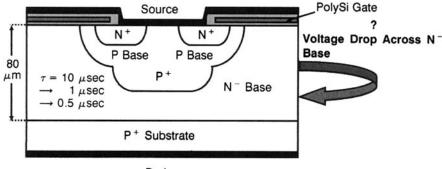

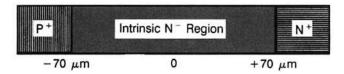

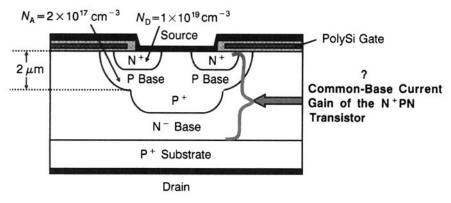

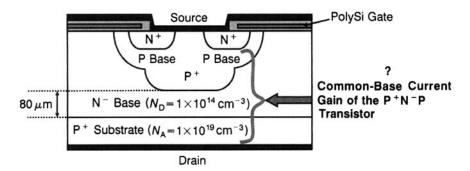

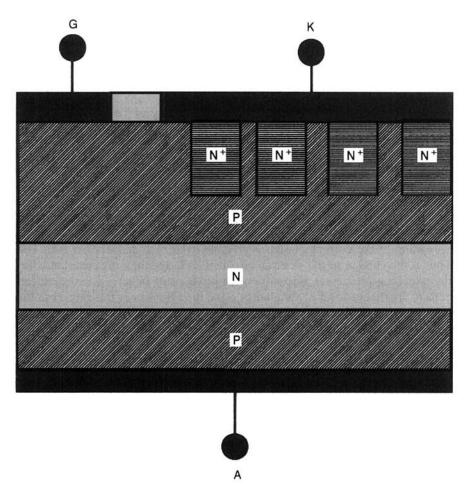

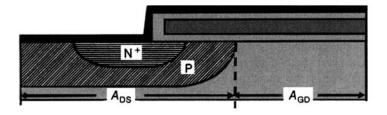

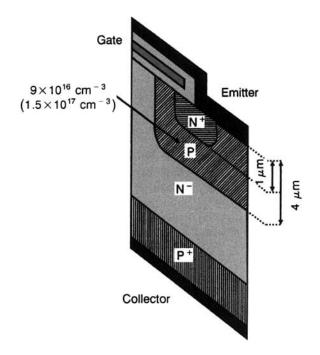

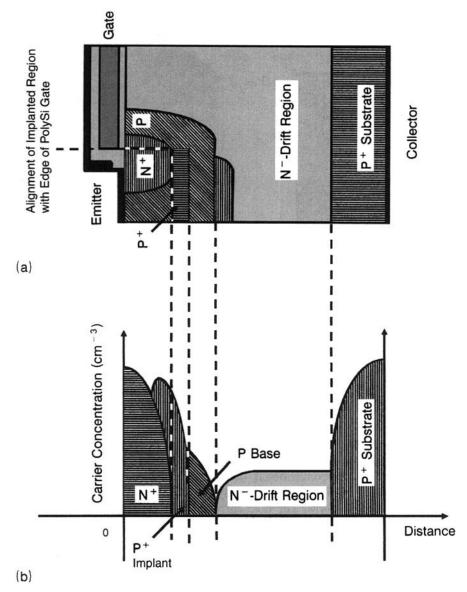

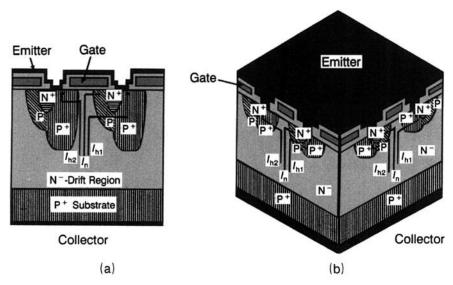

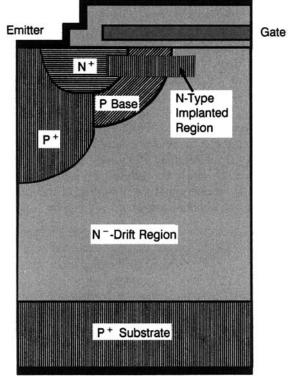

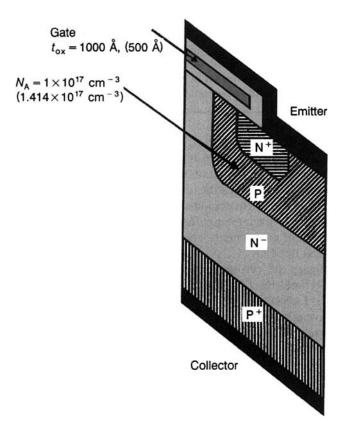

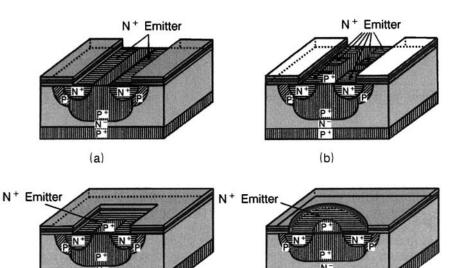

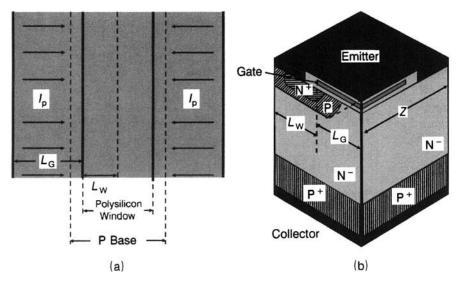

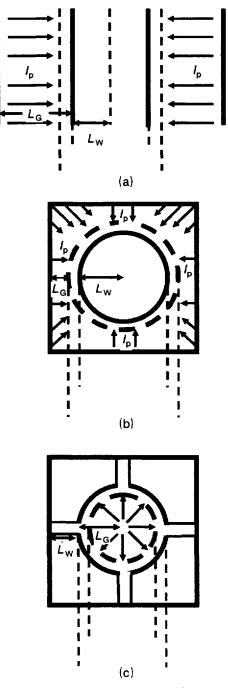

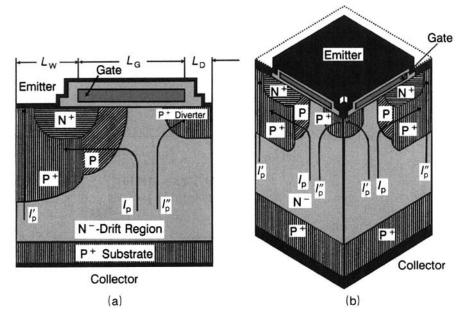

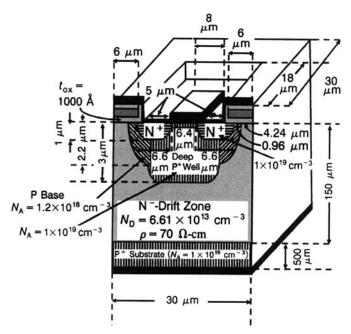

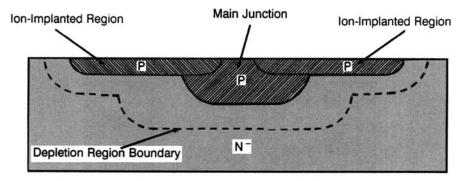

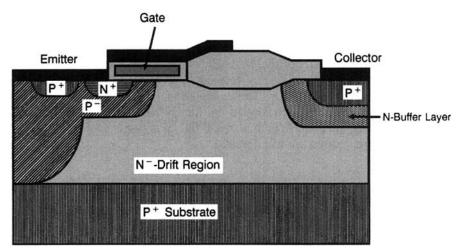

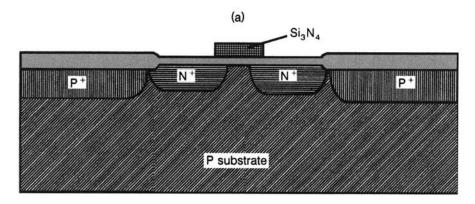

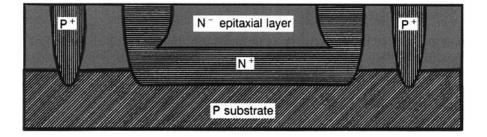

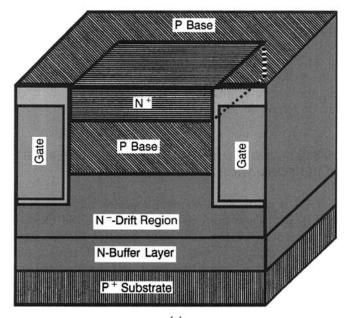

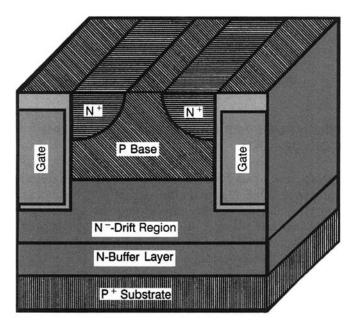

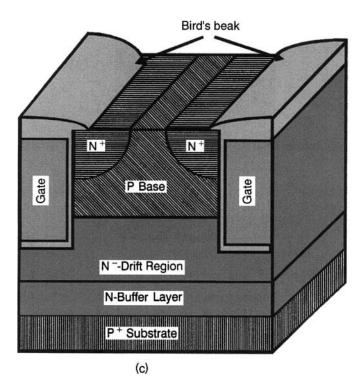

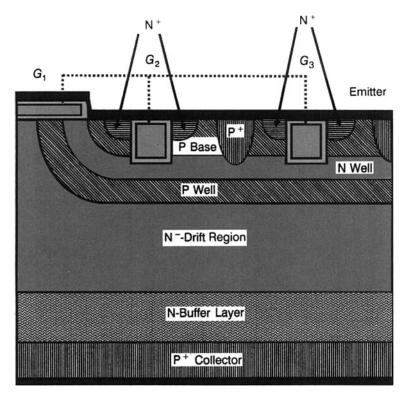

Figure 1.4 shows, schematically, the cross section of the basic IGBT structure. This is one of the several structures possible for this device. In practice, the power IGBT essentially comprises a repetitive array of millions of cells arranged, in a topological layout, providing a large aspect ratio: width versus length (W/L). Figure 1.5 represents an *elementary unit cell* of this multicellular power electronic component. The picture in Fig 1.6 shows the unit cell appearance in three dimensions. The different device regions of the structure must be clearly recognized. The N<sup>+</sup> layer at the top is the emitter. The P<sup>+</sup> layer at the bottom constitutes the collector. It is also called the *hole-injecting layer*. There are two base regions known as the P base and N base. Essentially, the IGBT comprises a four-layer N-P-N-P thyristor structure.

From Figs. 1.5 and 1.6, it is evident that the silicon cross section of the IGBT is virtually similar to the vertical DMOSFET (VDMOSFET) except for the  $P^+$  substrate in the IGBT. Also, both devices have a polysilicon gate structure and P wells with N<sup>+</sup> source regions. The thickness and resistivity of the N-type material between P wells controls the voltage rating of both the devices. Therefore, IGBT is fabricated by an N-channel polysilicon-gate self-aligned vertical DMOSFET (VDMOSFET) process. Because the IGBT

Figure 1.4 Schematic cross-sectional view of the IGBT.

Figure 1.5 IGBT unit cell. Half unit cell obtained by cutting across the dotted line represents the basic building block for analysis.

is essentially a VDMOSFET with an additional PN junction in the drain region, the process sequence of IGBT fabrication is the same as for the power VDMOSFET except that the starting N<sup>+</sup> substrate in VDMOSFET is replaced by P<sup>+</sup> substrate in IGBT. Like the SCR, an IGBT is fabricated with Si material due to its good thermal conductivity and high breakdown voltage. N<sup>-</sup> epitaxial layer is grown over the starting P<sup>+</sup> substrate followed by ion implantation, thermal diffusion, oxidation, chemical vapor deposition, and photolithographic steps as in poly-Si gate MOSFET processing. The details of fabrication technology will be described in Chapter 8.

Figure 1.6 Three-dimensional view of the IGBT unit cell.

#### 1.5 EQUIVALENT CIRCUIT REPRESENTATIONS

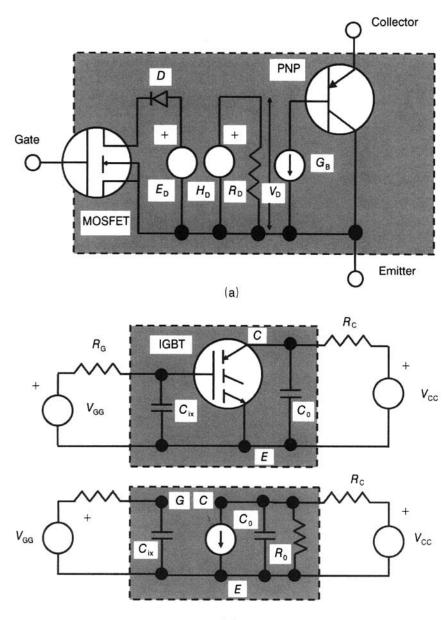

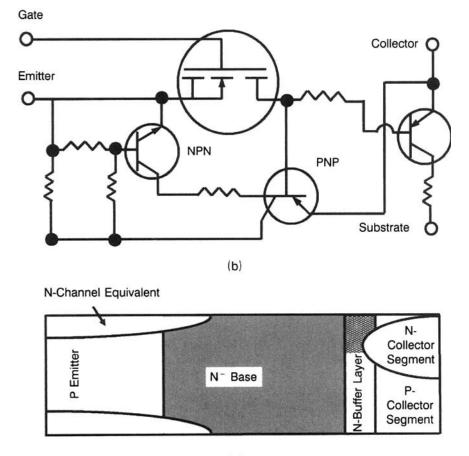

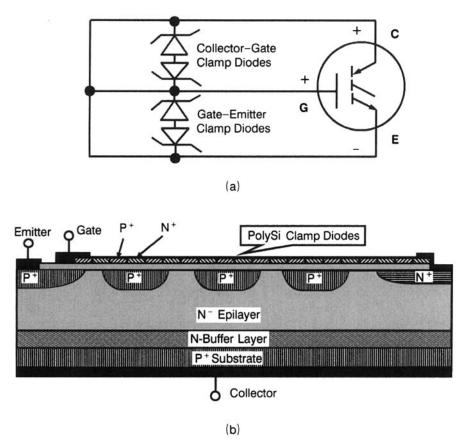

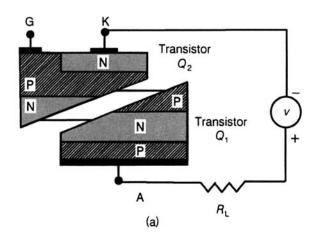

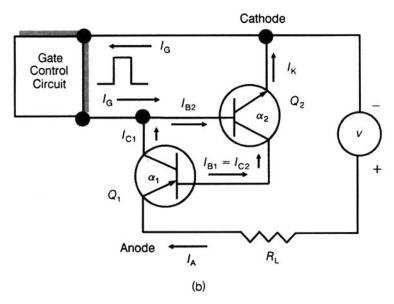

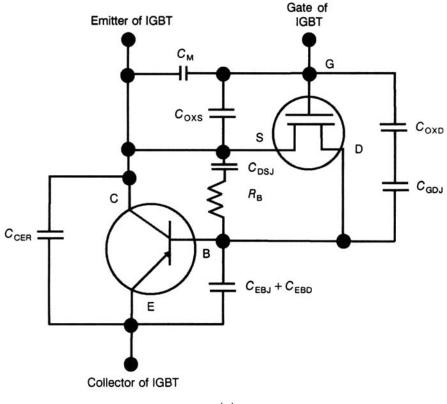

A clear perception of IGBT operation can be obtained by examining its equivalent circuit. From a close inspection of the IGBT cross-sectional diagram in Fig. 1.4, its equivalent circuit model is drawn in Fig. 1.7a. A pair of NPN and PNP transistors represents the thyristor. The collector of the NPN transistor is connected to the base of the PNP transistor, and likewise the collector of PNP transistor supplies the base current for the NPN transistor through the JFET. The NPN and PNP transistors thus constitute a regenerative feedback loop. It can also be seen from Fig. 1.7a, that sintered aluminum metallization as well as deep P<sup>+</sup> diffusion in the center of P base short-circuit the emitter and base of the NPN transistor. This is represented by the shorting resistance  $R_s$  connecting the emitter and base of NPN transistor in Fig. 1.7a. Emitter-base shorting is essential to ensure that the sum-total gain of NPN and PNP transistors  $(\alpha_{NPN} + \alpha_{PNP})$  does not exceed unity so that the thyristor does not latch up. Latching is avoided because it results in loss of gate control over output current. The latch-free IGBT, thus obtained, behaves as a single bipolar transistor in the form of its PNP component. Furthermore, the MOSFET channel is formed in the P base below the gate oxide. This channel joins the N<sup>+</sup> emitter and N<sup>-</sup> collector of the NPN transistor. So, this transistor is shunted by a MOSFET in the equivalent circuit. The JFET in the circuit represents the constriction of current between any two neighboring IGBT cells.

For proper IGBT functioning, it is obvious that the operation of the NPN transistor is deliberately avoided. Hence, the NPN transistor can be neglected. Then Fig. 1.7a is replaced by the simplified equivalent circuit

Figure 1.7 Electrical equivalent circuit models of IGBT. (a) Equivalent circuit of IGBT. (b) Simplified equivalent circuit of IGBT.

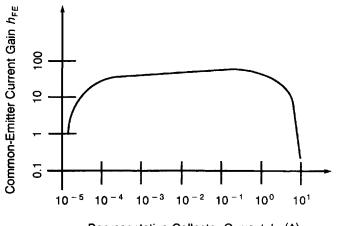

illustrated in Fig.1.7b. This circuit contains only two elements—for example the MOSFET and the PNP transistor. Therefore, the IGBT is viewed as an N-channel enhancement mode MOSFET driving a PNP bipolar transistor in a *pseudo-Darlington configuration*. Being the final stage of a pseudo-Darlington transistor, the PNP transistor is never in heavy saturation under normal operation so that its voltage drop is always higher than that of a saturated PNP transistor. The condition under which the PNP transistor will saturate is during latchup of the IGBT, which is an undesirable condition from which the device must be kept away. But the P<sup>+</sup> layer in an IGBT covers the full chip area. Hence its injection efficiency and conduction drop are superior to that of a BJT of equal size. The fact that PNP transistor does not operate under saturation gives the IGBT advantage during turn-off because it is easier to switch off an unsaturated transistor than a saturated one. Furthermore, because the base of PNP is not externally accessible, the turn-off time cannot be reduced by a drive circuit. Lifetime killing techniques and N-buffer layer are used for this purpose. But they decrease the current gain of PNP transistor and increase the forward drop of IGBT. The gain of PNP transistor therefore controls the conduction and switching losses. It also determines the latchup immunity of the built-in thyristor in IGBT as follows. The N-buffer layer and the wide epi N<sup>-</sup> base decrease the gain of the PNP transistor while the gain of the NPN transistor is reduced by decreasing its base resistance, thereby inhibiting dynamic latching during turn-off. During that period, a large hole current density flows through its P base, raising its gain to high values.

From these considerations, it is evident that the design of an IGBT involves the optimization of both the MOSFET and the bipolar parts. Naturally, there are two approaches to reduce the conduction drop of the IGBT: either (i) to decrease the ON resistance of the MOSFET by increasing the chip size and cell density, resulting in a "conductivity-modulated MOSFET" or (ii) to increase the current gain of the PNP transistor (with due attention to the latching and blocking voltage capabilities), producing a "MOSFET-driven bipolar transistor." Both approaches are applied in practice.

Considering the IGBT as a PIN rectifier whose output current flows through a MOSFET channel provides further simplification, but this is not an accurate representation of the equivalent circuit. Therefore, it is generally not used as IGBT equivalent circuit.

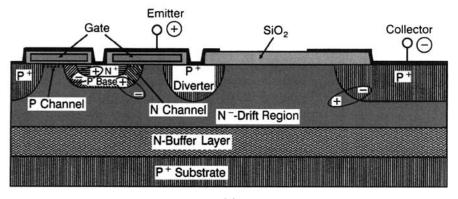

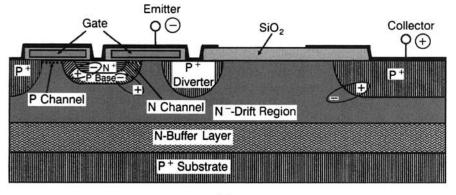

## 1.6 PRINCIPLE OF OPERATION AND CHARGE-CONTROL PHENOMENA

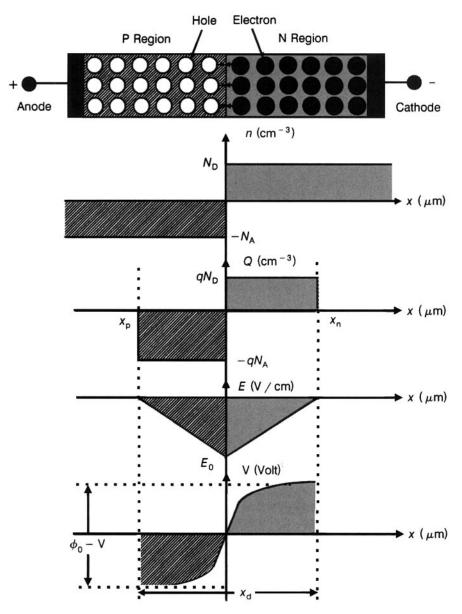

With reference to Figs. 1.4, 1.5, and 1.6, and with zero gate bias applied, the IGBT structure is equivalent to a PNPN break-over diode having a emitter short. The IGBT remains off when the collector is positively biased with respect to the emitter ( $V_{CE} > 0$ ). This is because the junction between the P-base and N<sup>-</sup>-type epitaxial layer is reverse-biased. Similarly, the IGBT remains in the off-state, when  $V_{CE} < 0$ , due to reverse bias across the junction between P<sup>+</sup> substrate and N<sup>-</sup> epitaxial layer. So, the collector-emitter current  $I_{CE}$  is minimal until breakdown in both polarities. For forward  $V_{CE}$  the breakdown is caused by avalanche of the N<sup>-</sup>P junction, while for reverse  $V_{CE}$  it is initiated by the same process at the N<sup>-</sup>P<sup>+</sup> junction.

Applying the  $V_{CE} > 0$  condition, the IGBT is turned on by applying a positive gate-emitter voltage ( $V_{GE}$ ) of sufficient magnitude to induce an N channel in the underlying P region, thereby connecting the N<sup>+</sup> emitter with N<sup>-</sup> base, forward biasing the base-emitter junction of the PNP transistor and making it conduct. The current flow across the junction between the N<sup>-</sup>-type epitaxial layer and the P-type substrate results in injection of minority-carrier

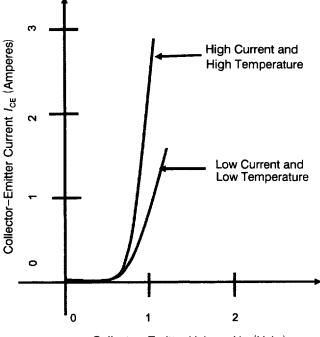

holes into the epitaxial layer. Consequently, conductivity modulation of this layer takes place, reducing its resistance and bringing about a large flow of collector-emitter current  $I_{CE}$ . To turn-off the IGBT, the gate-emitter voltage  $V_{GF}$  is made zero so that the channel in the P region is removed. Depending on the value of  $V_{CE}$ , three different regions of operation are observed in the IGBT. In the first regime, at a small value of  $V_{CE} \sim 0.7$  V, the IGBT is a VDMOSFET in parallel with a PNP transistor. Current transport takes place by recombination of excess electrons and holes in N<sup>-</sup>-region. The second regime commences from  $V_{CE} > 0.7$  V where the characteristics portray MOSFET behavior. At high  $V_{CE}$  values, the excess holes injected from the emitter of the PNP transistor are not absorbed by recombination in the N<sup>-</sup> base and spill over to the P base contributing to PNP bipolar current. The MOSFET current  $I_{MOS}$  is the base current of the bipolar transistor, and the collector-emitter current  $I_{CE}$  of IGBT duplicates the general shape of MOSFET characteristics except that it is the amplified version of  $I_{MOS}$ . In the third regime, when the current exceeds a critical level, the device latches up like the ON state of a thyristor. Consequently, gate control is lost.

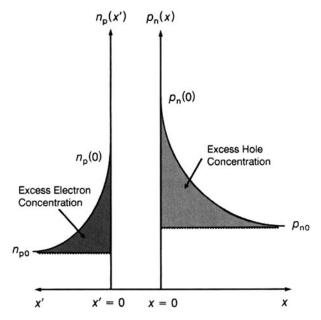

Device operation will be dealt with at length in Chapter 2. It may be remarked here that the MOS part of the IGBT controls its turn-on while the bipolar part determines the steady-state and turn-off behavior. Like the BJT and the MOSFET devices, the IGBT is also a charge-control device. In a PNP BJT operating in the active mode, the electron injection from the base terminal produces a negative charge in the N<sup>-</sup> base. This is balanced by an injection of holes from the P-emitter for maintaining charge neutrality. So the hole concentration in the base region is enhanced, allowing the holes to move from emitter to collector. Similarly, in an N-channel MOSFET, the conduction begins when its input capacitance has received adequate positive charge to raise the gate-source voltage to the level required to achieve inversion for channel formation. The main difference between bipolar and MOSFET conduction is that in the BJT a continuous supply of base current in the form of electrons is imperative to replenish the electrons lost by recombination. But in the MOSFET the gate dielectric (oxide) separating the electrons (in the channel) and positive charge on the oxide prevents their recombination so that current flow is necessary only for establishing charge density or during its withdrawal. Also, this charge requirement is very small. It follows that the IGBT that merges both bipolar and MOSFET properties is also a charge-control device.

#### 1.7 CIRCUIT MODELING

Device manufacturers and circuit designers require IGBT models to understand device internal mechanisms, optimize structures, and predict circuit behavior [31-53]. Various circuit simulation packages—notably, Saber and members of the Simulation Program with Integrated Circuit Emphasis (SPICE, PSPICE, HSPICE, IG-SPICE, etc.)—are available for IGBT modeling. Models are classified as mathematical (analytical models based on semiconductor physics), semimathematical (combining device physics with existing models in the simulator), behavioral or empirical (simulating IGBT characteristics without consideration of physical mechanisms), and seminumerical (using finite element methods to model the wide base and using analytical methods for other device parts). They are also categorized as microscopic (based on physical structure and equations) and macroscopic or composite (utilizing the available device models).

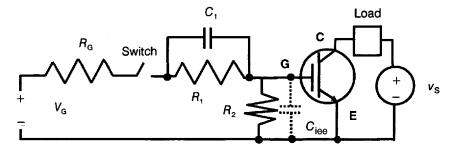

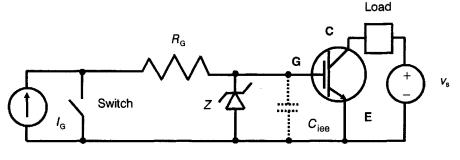

The macroscopic IGBT model, following the semimathematical approach, has been formulated in SPICE based on the existing models of MOSFET and BJT devices. This model is useful for circuit simulation, and it is less complicated and time-consuming than the microscopic model. Figure 1.8a presents the resistive or DC model of IGBT in SPICE. Three additional voltage- and current-controlled generators can be seen between the MOS-FET and BJT sections. These are included because the output characteristics of the IGBT are not exactly the same as those of the MOSFET, calling for modifications. Furthermore, since SPICE requires that the inputs of controlling variables must be of only one source type, either all voltage or all current, the controlling variables are converted into the same type.

Diode D and the two-dimensional voltage-controlled voltage source (VCVS)  $E_D$  represent the typical value of output voltage (0.7-1.0 V). The dimension of a source is understood from the definition of non-linear-dependent sources in SPICE which are characterized by any of the four equations i = f(v), v = f(v), i = f(i) and v = f(i), where the functions are polynomials and the arguments can be multidimensional. The diode prevents the collector current of the BJT from flowing on applying a reverse voltage across the output of IGBT.  $H_D$  is a current-controlled voltage source (CCVS), which transforms the drain current of the MOSFET into the driving voltage  $V_D$  across the resistor  $R_D$ .  $G_B$  is a two-dimensional nonlinear voltage-controlled current source, which drives the output transistor.

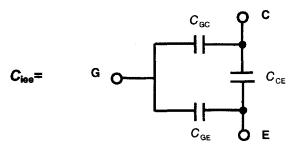

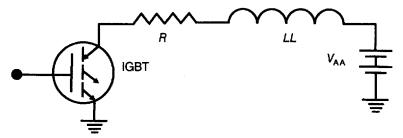

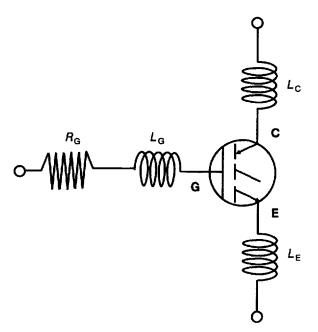

Figure 1.8b shows the dynamic SPICE model of IGBT, which is a combination of the DC model and the nonlinear input capacitance  $C_{ix}$ , modeled by a four-segment piecewise linear function. The reverse capacitance is very small while the output capacitance  $C_o$  is taken from the data sheets. The currentcontrolled input capacitance is synthesized with the nonlinear input resistive circuit to obtain the complete SPICE macromodel of the IGBT.

The accuracy of this model is lower than that of the mathematical IGBT models because the wide base in IGBT differs from the existing discrete power BJT models. IGBT switching behavior is primarily controlled by the distributed charge in this wide base. The behavior of the distributed charge is governed by the ambipolar transport equation, a second-order partial differential equation.

(b)

Figure 1.8 SPICE models of IGBT. (a) DC model of IGBT. (b) Switching circuit and dynamic model of the IGBT.

| Example 1.1 | Manufacturing | process | of | IGBTs | produces | two | different | types | as |

|-------------|---------------|---------|----|-------|----------|-----|-----------|-------|----|

| follows:    |               |         |    |       |          |     |           |       |    |

| IGBT Type | Forward Voltage Drop<br>at 80 A (in volts) | Turn-Off Loss<br>per Switching (in mJ) |

|-----------|--------------------------------------------|----------------------------------------|

| Slow IGBT | 1.2                                        | 10                                     |

| Fast IGBT | 2.1                                        | 5                                      |

Considering a duty ratio of 50% for a DC drive application, at what frequency will the two IGBTs give the same total power loss? Compare the power losses of the two IGBTs at 5 kHz and 10 kHz.

Neglecting the turn-on, driving, and nonconducting state losses, we can write

Power loss  $P_{\text{loss}}$  = Forward voltage  $V_{\text{F}} \times$  Forward curren  $I_{\text{F}} \times$  Duty Ratio

+ Switching frequency  $(f) \times$  Energy lost during turn-off

(E1.1.1)

For the slow IGBT

$$P_{\text{loss}} = 1.2 \times 80 \times 0.5 + f \times 10^3 \times 10 \times 10^{-3} = 48 + 10f$$

(E1.1.2)

For the fast IGBT,  $P_{\text{loss}} = 2.1 \times 80 \times 0.5 + f \times 10^3 \times 5 \times 10^{-3} = 84 + 5f$  (E1.1.3)

The power losses of the slow and fast IGBTs will be equal at a frequency f(kHz) obtained from the equality

$$48 + 10f = 84 + 5f \tag{E1.1.4}$$

from which f = 7.2 kHz.

| At $f = 5$ kHz,    |                                                              |          |

|--------------------|--------------------------------------------------------------|----------|

| For the slow IGBT, | $P_{\text{loss}} = 1.2 \times 80 \times 0.5$                 |          |

|                    | $+5 \times 10^{3} \times 10 \times 10^{-3} = 98 \text{ W}$   | (E1.1.5) |

| For the fast IGBT, | $P_{\text{loss}} = 2.1 \times 80 \times 0.5$                 |          |

|                    | $+5 \times 10^{3} \times 5 \times 10^{-3} = 109 \text{ W}$   | (E1.1.6) |

| At $f = 10$ kHz,   |                                                              |          |

| For the slow IGBT, | $P_{\rm loss} = 1.2 \times 80 \times 0.5$                    |          |

|                    | $+10 \times 10^{3} \times 10 \times 10^{-3} = 148 \text{ W}$ | (E1.1.7) |

| For the fast IGBT, | $P_{\text{loss}} = 2.1 \times 80 \times 0.5$                 |          |

or the fast IGBT,

$$P_{\text{loss}} = 2.1 \times 80 \times 0.5$$

$$+ 10 \times 10^3 \times 5 \times 10^{-3} = 134 \text{ W}$$

(E1.1.8)

Thus we conclude that at 5 kHz, the slow IGBT is superior, giving a lower power loss (98 W) than the fast IGBT (109W). At 10 kHz, the slow IGBT becomes inferior because it gives a higher power loss (148 W) than the fast IGBT (134 W).

*Example 1.2* Assuming a 50% duty cycle, calculate the power dissipation of 1000-V IGBT, BJT, and MOSFET chips of equal area, each carrying a current of 50 A, given

| Serial No. | Device | Forward Voltage Drop<br>at 50 A (volts) | Turn-Off Time<br>( µsec) |

|------------|--------|-----------------------------------------|--------------------------|

| 1          | IGBT   | 2                                       | 1                        |

| 2          | BJT    | 15                                      | 1                        |

| 3          | MOSFET | 40                                      | 0.1                      |

the following set of parameters for the devices:

Perform these calculations at two frequencies, 25 kHz and 100 kHz.

Neglecting turn-on, driving, and OFF-state losses, the power dissipation  $P_{\rm D}$  is the sum of power loss incurred during steady-state forward conduction ( $P_{\rm ss}$ ) and power loss during switching from ON state to OFF state ( $P_{\rm sw}$ ), that is

$$P_{\rm D} = P_{\rm ss} + P_{\rm sw} \tag{E1.2.1}$$

Let T be the periodic time of the gate pulse,  $\tau_1$  the time fraction of the time period T for which the device remains on,  $\tau_2$  the turn-off time,  $V_F$  the forward voltage drop at current  $I_F$ , and  $V_B$  the blocking voltage. Then the power dissipation is expressed as

$$P_{\rm D} = V_{\rm F} I_{\rm F} \tau_1 + (1/2) V_{\rm B} I_{\rm F} (\tau_2/T)$$

(E1.2.2)

The first term  $(P_{ss})$  in this expression is independent of frequency and depends only on the duty cycle so that we have the following:

For IGBT,

$$P_{\rm ss} = 2 \times 50 \times 0.5 = 50 \text{ W}$$

For BJT,

$$P_{\rm ss} = 15 \times 50 \times 0.5 = 375 \text{ W}$$

For MOSFET,

$$P_{\rm ss} = 40 \times 50 \times 0.5 = 1000 \,\,{\rm W}$$

Total power dissipation at 25 kHz is as follows: For IGBT,

$$P_{\rm D} = 50 + (1/2) \times 1000 \times 50 \times 1 \times 10^{-6} / \{1/(25 \times 10^3)\} = 675 \text{ W}$$

For BJT,

$$P_{\rm D} = 375 + (1/2) \times 1000 \times 50 \times 1 \times 10^{-6} / \{1/(25 \times 10^3)\} = 1000 \text{ W}$$

For MOSFET,

$$P_{\rm D} = 1000 + (1/2) \times 1000 \times 50 \times 0.1 \times 10^{-6} / \{1/(25 \times 10^3)\} = 1062.5 \text{ W}$$

Total power dissipation at 100 kHz is as follows: For IGBT,

$$P_{\rm D} = 50 + (1/2) \times 1000 \times 50 \times 1 \times 10^{-6} / \{1/(100 \times 10^3)\} = 2550 \text{ W}$$

For BJT,

$P_{\rm D} = 375 + (1/2) \times 1000 \times 50 \times 1 \times 10^{-6} / \{1/(100 \times 10^3)\} = 2875 \text{ W}$

For MOSFET,

$$P_{\rm D} = 1000 + (1/2) \times 1000 \times 50 \times 0.1 \times 10^{-6} / \{1/(100 \times 10^3)\} = 1250 \text{ W}$$

From the above, it is irresistible to conclude that at 5 kHz the IGBT is the least lossy of the three devices. At 10 kHz the IGBT still remains better than BJT but both IGBT and BJT become inferior to MOSFET due to increased power losses.

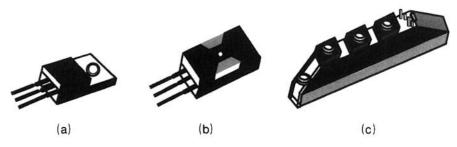

#### 1.8 PACKAGING OPTIONS FOR IGBTs

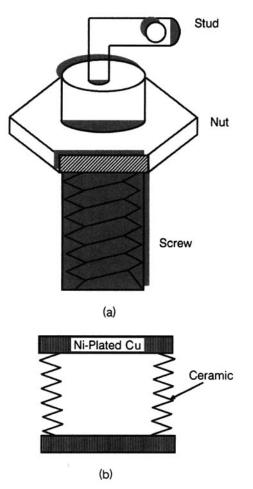

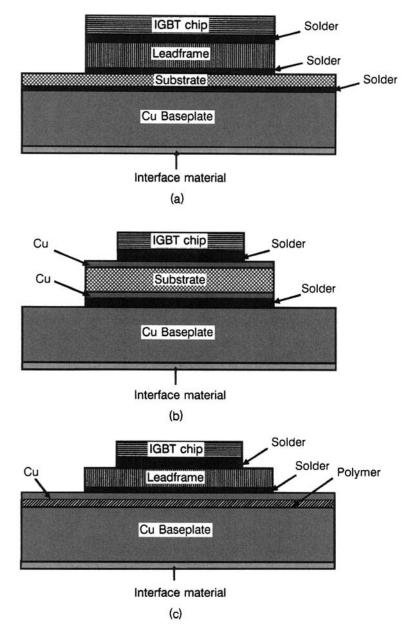

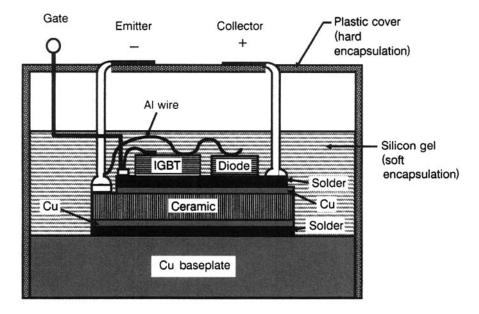

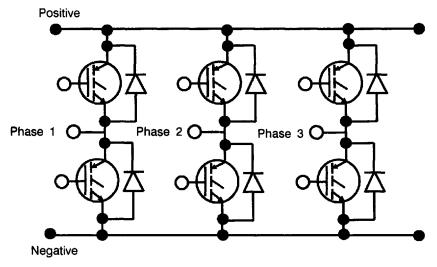

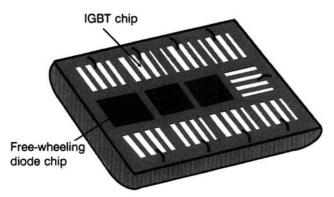

Desirable characteristics of a package include good electrical and thermal performance, long life, high reliability, and low cost. Additionally, for a module, electrical isolation of the base plate from the semiconductor die is necessary in order that both the halves of a phase leg are enclosed in one package. This is also required for convenience so that modules switching, different phases, can be mounted on the same heat sink, and also from safety considerations for grounding the heat sink. IGBTs are generally packaged in three types of commercially available packages (Fig. 1.9): (i) *Discrete packages* such as TO-220, TO-247, TO-264, and SOT-227B. These packages contain a single device and are used for low-power applications. (ii) *Power module package*: These package multiple dice and are available in several configurations such as half-bridge, full-bridge, and three-phase bridge. (iii) *Press pack*: This type has been recently introduced for modules (see Chapter 9, Section 9.7).

Figure 1.9 Common IGBT packages. (a) TO-220 AB. (b) TO-247 AD. (c) TO-240 AA.

#### 1.9 HANDLING PRECAUTIONS OF IGBTs

(i) Before assembly into a circuit, the IGBTs should be stored with their leads shorted together by metallic springs or kept in a conducting material.