# The Illustrated Guide to PSpice \_\_\_\_

# **Robert Lamey**

Cincinnati Technical College

I(T)P<sup>™</sup>

#### NOTICE TO THE READER

Publisher does not warrant or guarantee any of the products described herein or perform any independent analysis in connection with any of the product information contained herein. Publisher does not assume, and expressly disclaims, any obligation to obtain and include information other than that provided to it by the manufacturer.

The reader is expressly warned to consider and adopt all safety precautions that might be indicated by the activities described herein and to avoid all potential hazards. By following the instructions contained herein, the reader willingly assumes all risks in connection with such instructions.

The publisher makes no representations or warranties of any kind, including but not limited to, the warranties of fitness for particular purpose or merchantability, nor are any such representations implied with respect to the material set forth herein, and the publisher takes no responsibility with respect to such material. The publisher shall not be liable for any special, consequential or exemplary damages resulting, in whole or in part, from the readers' use of, or reliance upon, this material.

Cover design by Katie Hayden

#### **Delmar Staff:**

Administrative Editor: Wendy J. Welch Senior Project Editor: Christopher Chien Senior Production Supervisor: Larry Main Art and Design Coordinator: Lisa Bower Assistant Editor: Jenna Daniels

For information, address Delmar Publishers Inc. 3 Columbia Circle Box 15-015 Albany, New York 12212-5015

COPYRIGHT © 1995 BY DELMAR PUBLISHERS INC.

### The trademark ITP is used under license.

All rights reserved. No part of this work covered by the copyright hereon may be reproduced or used in any form or by any means—graphic, electronic, or mechanical, including photocopying, recording, taping, and information storage or retrieval systems—without written permission of the publisher.

Printed in the United States of America Published simultaneously in Canada by Nelson Canada, a division of The Thompson Corporation

### 2 3 4 5 6 7 8 9 10 XXX 00 99 98 97 96 95

### Library of Congress Cataloging-in-Publication Data

Lamey, Robert. The illustrated guide to PSPICE / Robert Lamey. p. cm. Includes index. ISBN 0-8273-6524-1

1. PSpice. 2. Electric circuit analysis-Data processing.

3. Electronic circuits-Data processing. I. Title. TK454.L35 1995 621.3815'0285'5369-dc20

94-2662 CIP

# Contents

#### Preface ix **Getting Started with PSpice** 1 1.1 **PSpice Software** 1 1.2 Installation 2 1.3 Working Directory 3 1.4 PSpice Hardware Requirements 3 1.5 PSpice Editor 4 1.6 PSpice Circuit Descriptions 5 1.7 Values and Units in PSpice 6 PSpice from the Command Line 1.8 8 2 **DC Circuits** 9 2.1 Circuit Description 9 2.2 **Circuit Analysis** 14 Command Line Circuit Description and Analysis 2.3 15 2.4 Errors 16 2.5 Variable-Source Circuits 16 20 2.6 Series-Parallel Circuits Multiple-Source-Multiple-Loop Circuits 2.7 21 23 2.8 Analysis at Circuit Nodes 2.9 Transient Analysis of Resistor-Capacitor Circuits 24 2.10 Transient Analysis of Resistor-Inductor Circuits 28 2.11 Ideal Components 29 30 2.12 Potentiometers

v

### vi / CONTENTS

### **3** AC Circuits 31

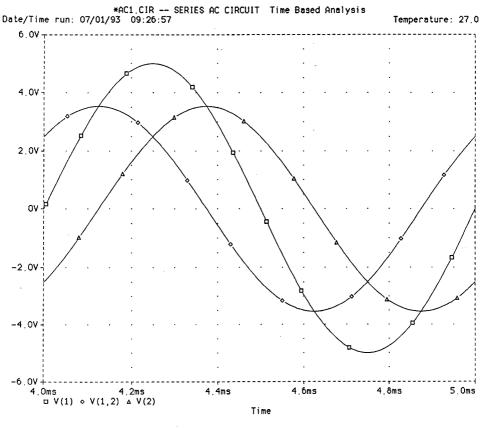

- 3.1 Series AC Circuit Time-Based Analysis 33

- 3.2 Series AC Circuit Frequency-Based Analysis 36

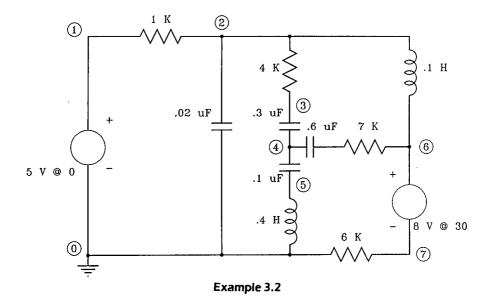

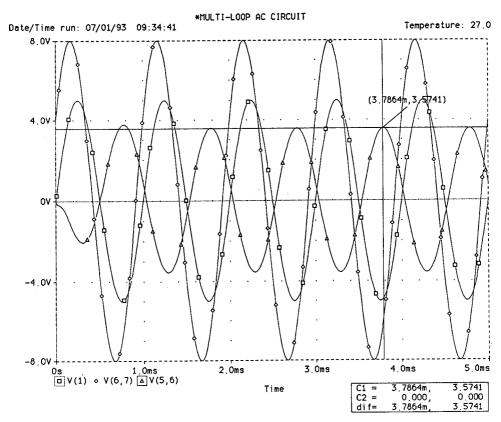

- 3.3 Multiple-Source-Multiple-Loop AC Circuits 37

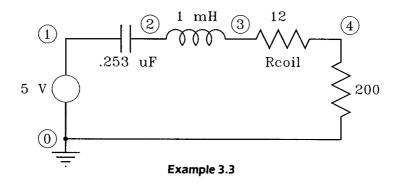

- 3.4 Series Resonant Circuits 41

- 3.5 Parallel Resonant Circuits 43

- 3.6 High-Pass and Low-Pass Filter Circuits 46

- 3.7 Transformer Circuits 49

### 4 Diode Circuits 57

- 4.1 Creating Diode.LIB 58

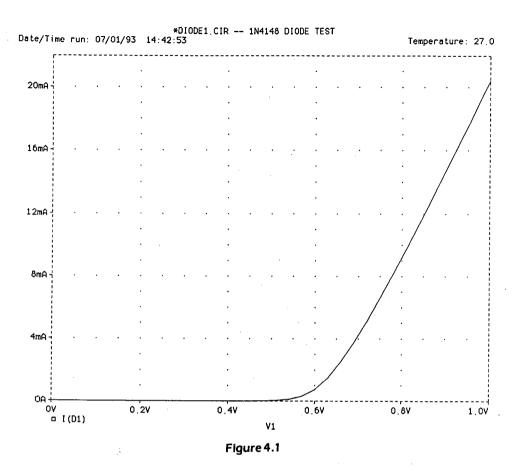

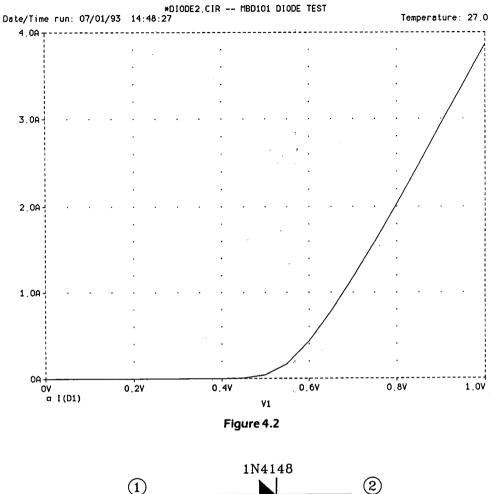

- 4.2 Diode Characteristics 59

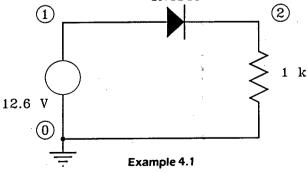

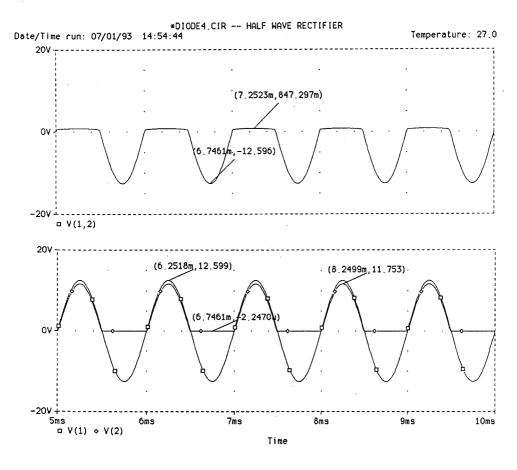

- 4.3 Half-Wave Rectifiers 60

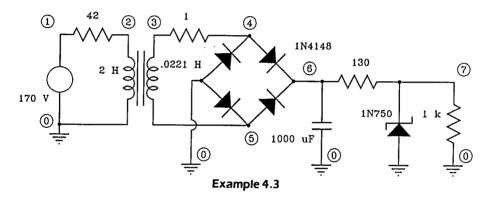

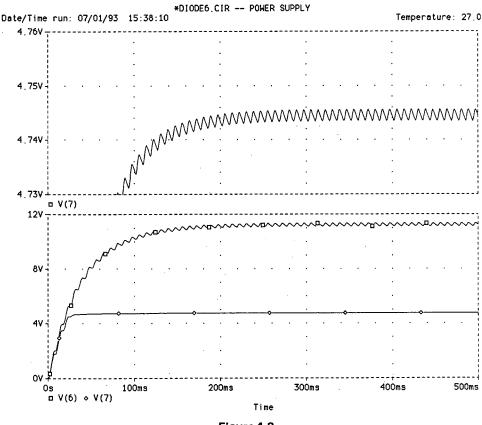

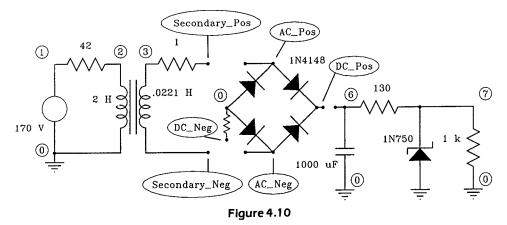

- 4.4 Bridge Rectifiers 63

- 4.5 Power Supplies 67

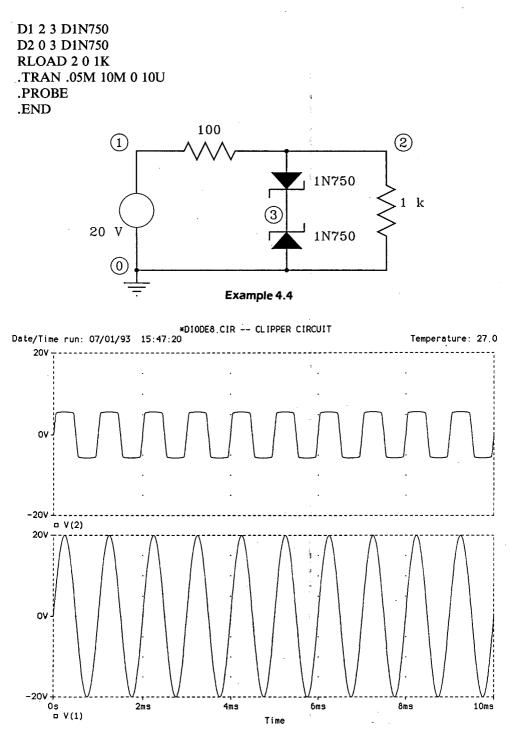

- 4.6 Clipper Circuits 67

- 4.7 Subcircuits 70

### 5 Operational Amplifier Circuits 73

- 5.1 Creating OpAmp.LIB 73

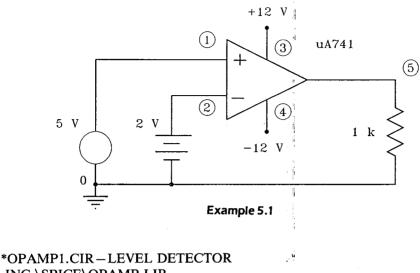

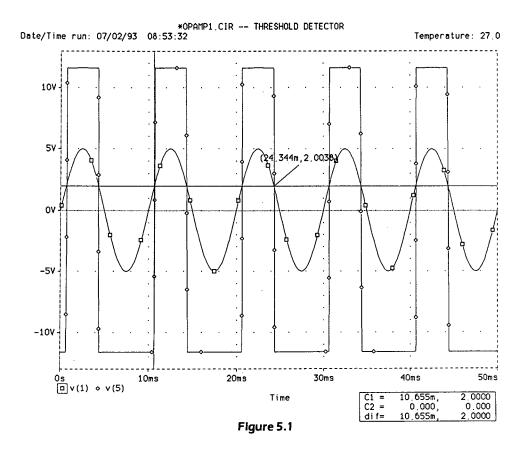

- 5.2 Level Detector Circuits 74

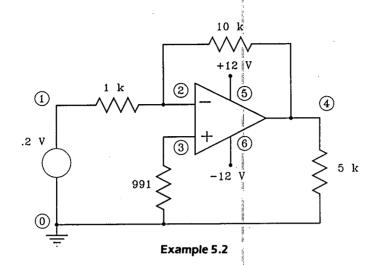

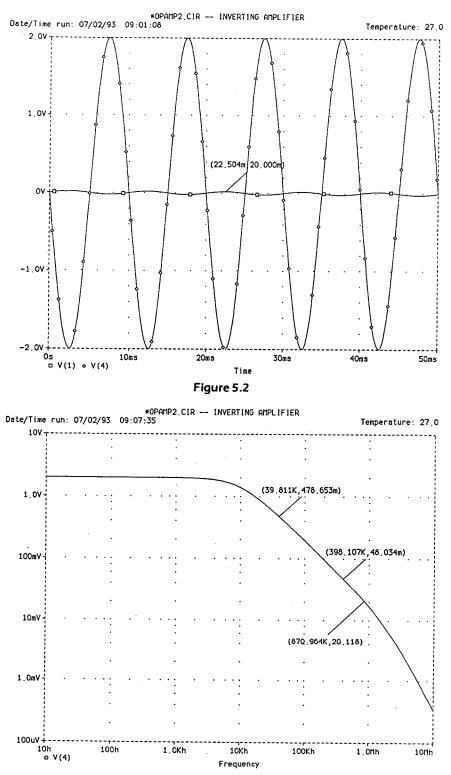

- 5.3 Inverting Amplifier 76

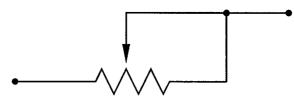

- 5.4 Variable Gain Amplifiers Modeling Variable Resistors 77

- 5.5 Potentiometer Subcircuit 80

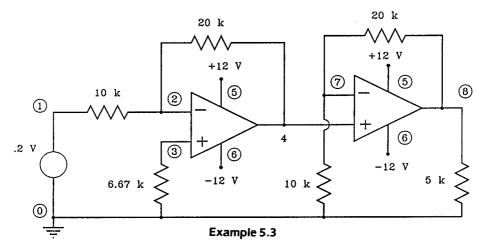

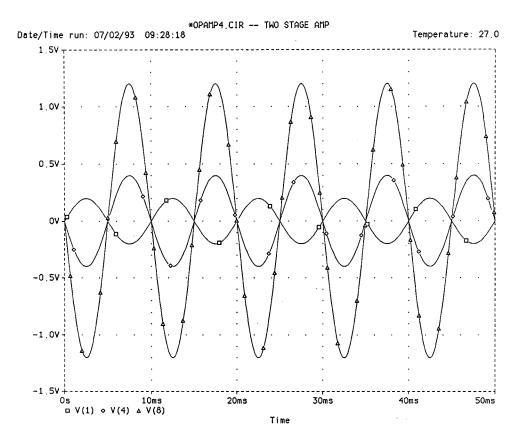

- 5.6 Multistage Amplifiers 81

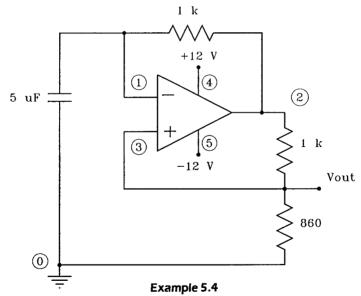

- 5.7 Op Amp Oscillators 83

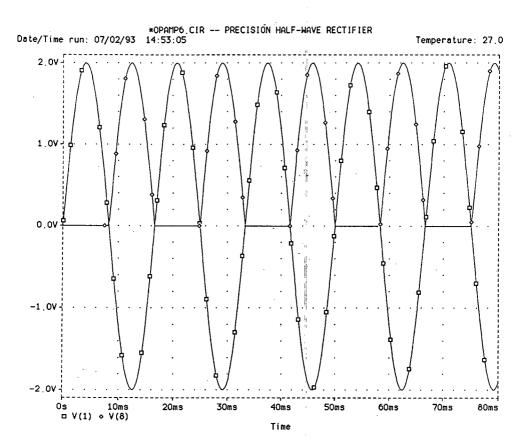

- 5.8 Precision Half-Wave Rectifier 85

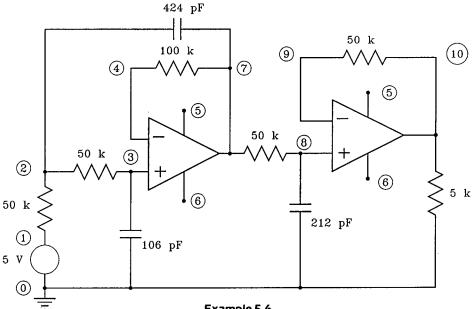

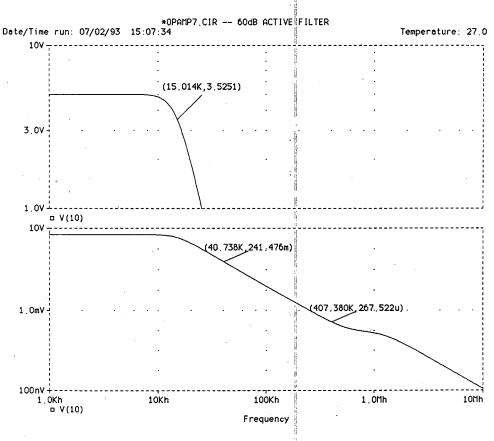

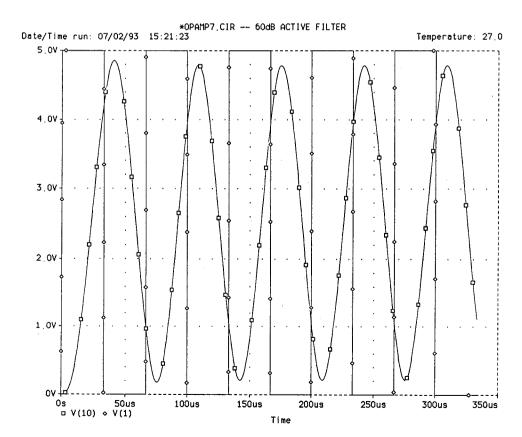

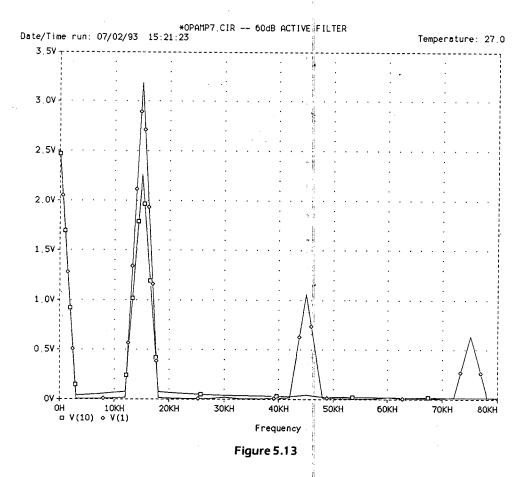

- 5.9 60 dB Active Filter 88

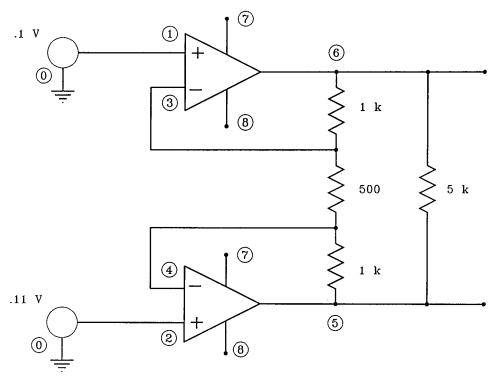

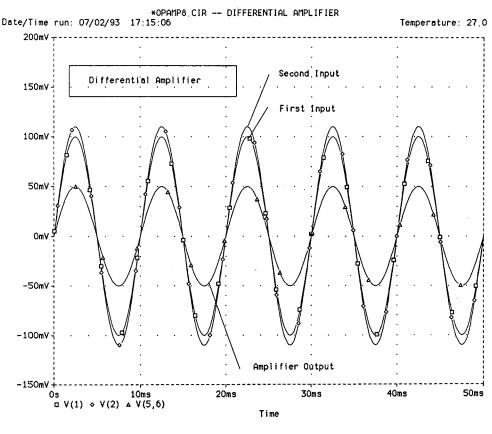

- 5.10 Differential Amplifier 91

### **6** Bipolar Junction Transistor Circuits 95

- 6.1 Transistor DC Load Lines 96

- 6.2 DC Load Line in Collector Feedback Biasing 100

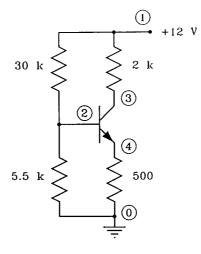

- 6.3 Small Signal Amplifiers 101

- 6.4 Transistor Modeling 108

|   | 6.5 | Cascaded Amplifiers 111            |                |

|---|-----|------------------------------------|----------------|

|   | 6.6 | Power Amplifiers 113               |                |

|   | 6.7 | Class B Amplifiers 116             |                |

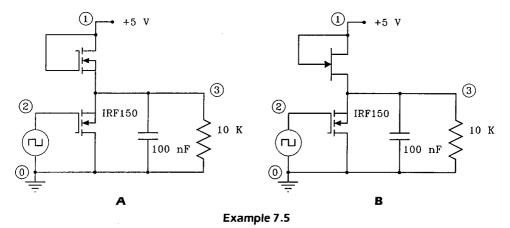

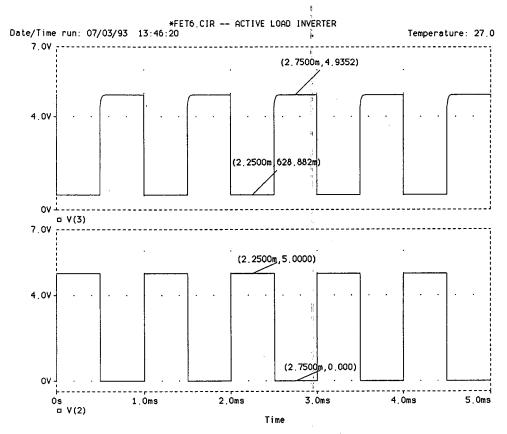

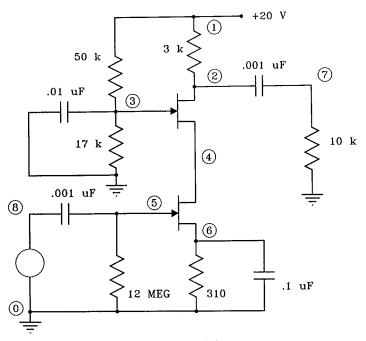

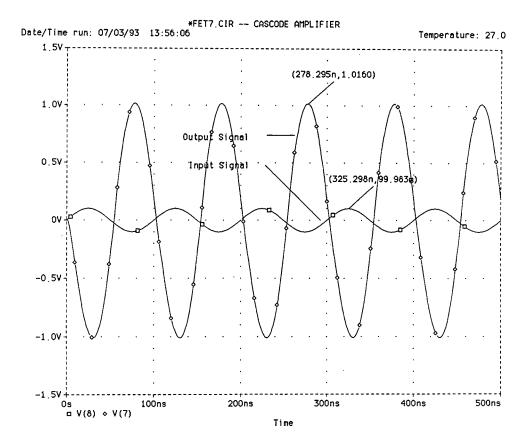

| 7 | Fie | eld-Effect Transistor Circuits     | 123            |

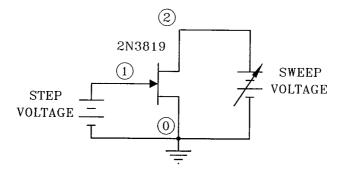

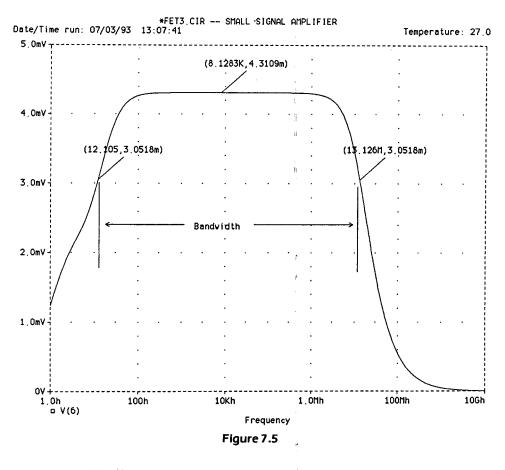

|   | 7.1 | Transconductance Curve 124         |                |

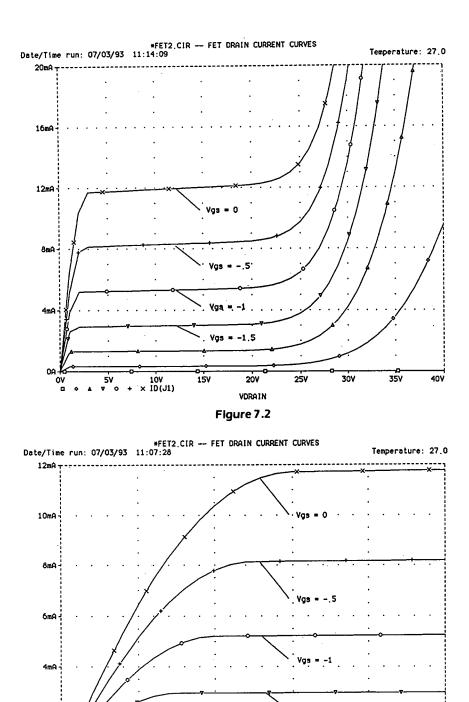

|   | 7.2 | Drain Current Curves 126           |                |

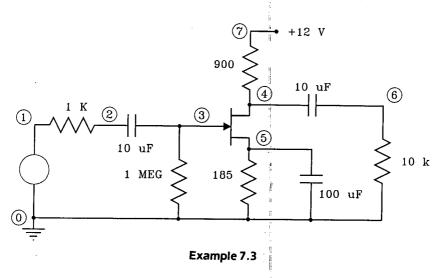

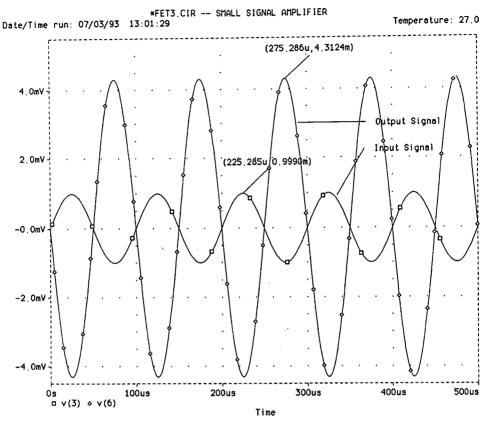

|   | 7.3 | Small-Signal Amplifiers 127        |                |

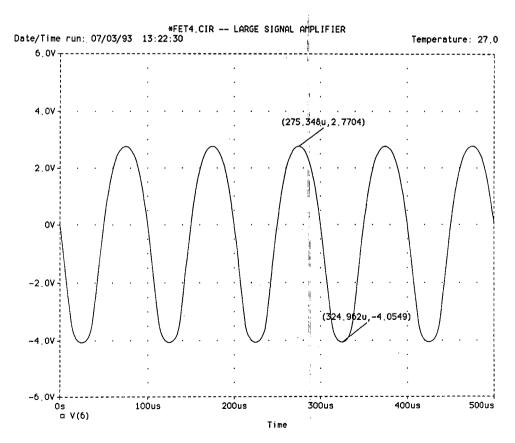

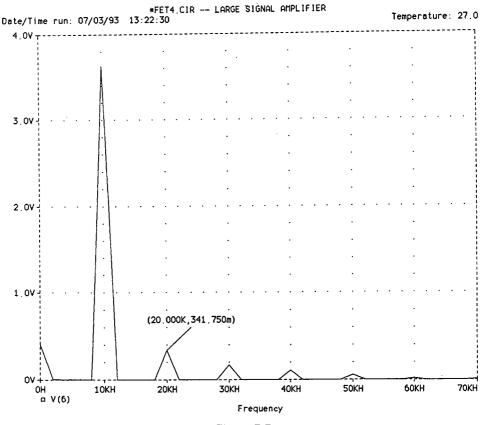

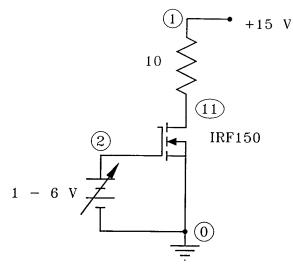

|   | 7.4 | Large-Signal Amplifiers 132        |                |

|   | 7.5 | MOSFET Transconductance Curve 13   | 4              |

|   | 7.6 | Active-Load Switching 135          |                |

|   | 7.7 | Cascode Amplifier 138              |                |

| 8 | An  | nalog Communications Circuits      | 141            |

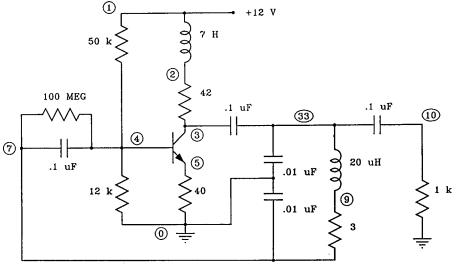

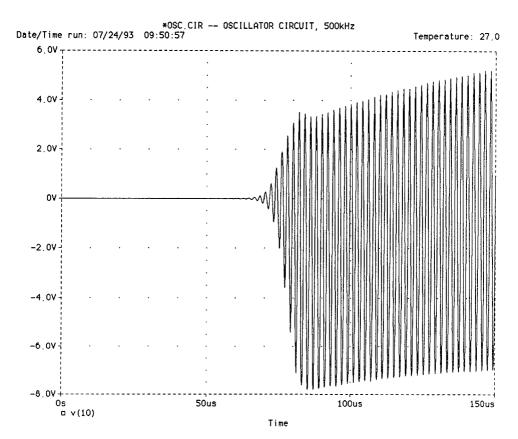

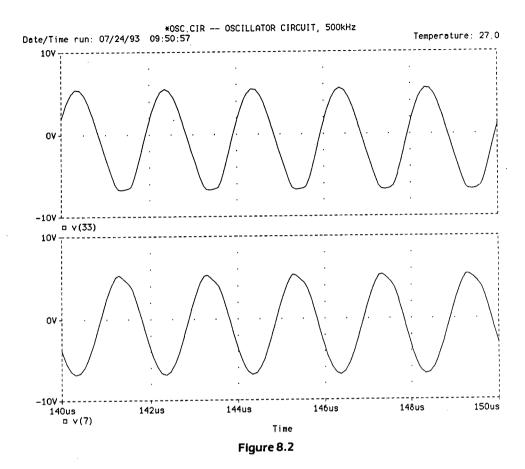

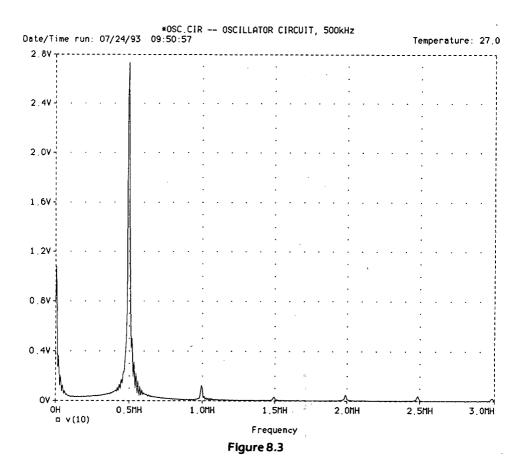

|   | 8.1 | Colpitts Oscillator 141            |                |

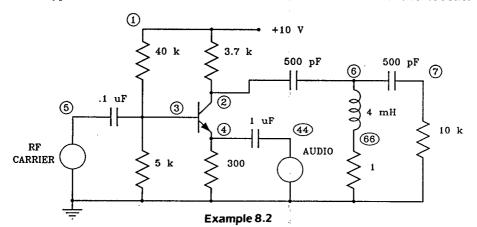

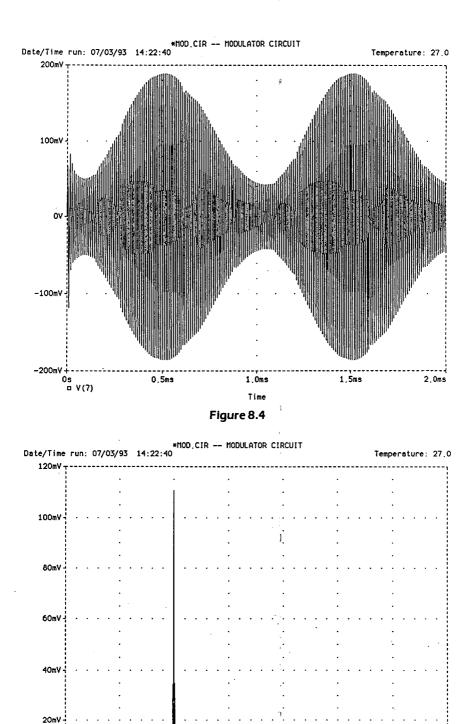

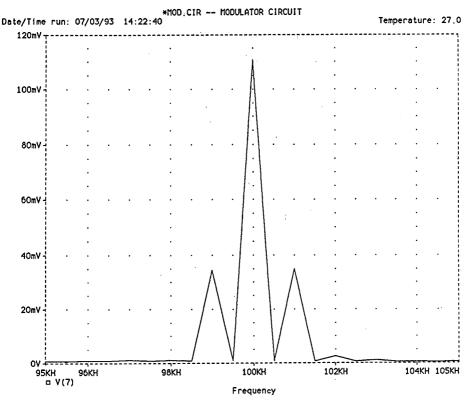

|   | 8.2 | Low-Level Amplitude Modulation 144 | l I            |

|   | 8.3 | High-Level Amplitude Modulation 15 | 0              |

|   | 8.4 | AM and FM Demodulation 152         |                |

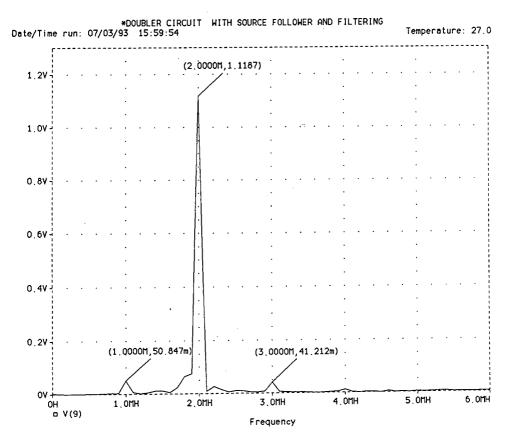

|   | 8.5 | Doubler Circuits 158               |                |

| A | Nu  | meric Value and Expression C       | onventions 164 |

| В | Ab  | bridged PSpice Command List        | 166            |

| С | At  | bridged List of Analog Devices     | and            |

| - |     | braries 186                        |                |

|   | in  | dex 217                            |                |

|   |     |                                    |                |

|   |     |                                    |                |

|   |     |                                    |                |

an anna an ann anna an

Ę

THE STREET

C. D. D. D. D.

# Trademarks

"PSpice" is a registered trademark of MicroSim Corporation.

"The Design Center," "Probe," "Schematics," "StmEd," and "Stimulus Editor" are trademarks of MicroSim Corporation.

"Microsoft," "MS," and "MS-DOS" are registered trademarks, and "Windows" is a trademark of Microsoft Corporation.

"IBM" is a registered trademark of International Business Machines Corporation.

# Preface

While SPICE software for computer simulation of analog circuitry has been used commercially for years, I was first introduced to PSpice (SPICE for personal computers) just two years ago. The impact on my teaching style and on my students was immediate and dramatic.

It also became clear that working technicians and electronics hobbyists could benefit greatly from PSpice. PSpice takes the tedium out of circuit analysis calculations, which can bog down a lecture and make discoveries in circuit performance boring rather than exciting. This is particularly true when recalculating the same circuit after making a change in the value of a single component or the frequency of a single source. PSpice, used as a demonstrator, added accuracy to the waveform phase shifts and frequency response curves that was marginal when graphed by hand on a blackboard.

For my students, the advantages were even greater. PSpice has become an integral part of every laboratory experiment. Simulation provides an accurate theoretical model that students use for comparison to the circuits in the lab exercise. Discrepancies are discussed in terms both of sources of experimental error and of necessary changes in the model to better explain the voltages and currents in the circuit under examination.

The introduction of PSpice into my analog circuit analysis classes prompted the search for an appropriate textbook. I quickly found that all the available books presume the reader is approaching PSpice with the background of an engineer, and is familiar with terms such as "transient analysis," "quadratic voltage coefficient," and "base-emitter zero bias p-n capacitance." The authors maintain a focus on the completeness that an engineer demands, at the expense of the directness and clarity that a student requires. The reference book that fills the engineer's needs is virtually unreadable to a technical student, or the amateur hobbyist, and sometimes even the experienced technician who is using a circuit simulator for the first time.

There seemed to be no textbook specifically written to explain how to use PSpice to model the circuits students typically encounter in a technical curriculum, or an amateur encounters in pursuit of his hobby. This book has been designed to fill the need of the student, the technician, the hobbyist, and the computer simulation novice.

### x / PREFACE

To achieve this end:

- 1. Features that a student or hobbyist will likely use in the course of his technical education, or in the pursuit of certifications and licenses, are included. All other features are either relegated to the appendixes or omitted.

- 2. Material is presented in the order it is usually encountered in an electronics engineering technology curriculum. This chronology provides order for the student and easy reference for the amateur electronics maven. Following an introductor chapter about PSpice itself, Chapter 2 explains how PSpice can be used to analyze circuitry found in a DC circuit analysis class. Chapter 3 uses PSpice for AC circuit analysis. This curriculum based, chapter-wise progression continues through the study of diodes, op-amps, transistors, and communication circuitry.

- 3. All features presented are also illustrated with examples. In each example, new features are explained in sufficient detail to allow the reader to use the new feature in an assignment, a lab exercise, or to apply to circuitry under test for trouble shooting purposes.

This book is not complete and makes no attempt to cover every option to every PSpice command. Completeness is left to other authors and other books. Here the focus is on clarity, relevance for electronics students, technicians, and hobbyists, and immediate applicability to topics covered in an electronics engineering technology curriculum.

Although the author of this text is singular, many contributed their time and effort before the final product was complete. I would like to acknowledge the contributions of Roberto Uribe, Kent State University; Innocent Usoh, Nashville State Technical University; Ian Davis, Miami Dade Community College; Adnan Al-Smadi, Tennessee State University; and Ronald Harris, Weber State University, Utah. These readers scrutinized several chapters, suggesting improvements and detecting errors. Gary Webster and Robert McLain, my colleagues at Cincinnati Technical College, provided the sounding board against which my ideas for material and presentation were tested. My special thanks are reserved for Andrea Feld-Brockett, who spent many tedious days editing the original manuscript.

I am particularly indebted to the people at MicroSim Corporation for not only generously allowing portions of their software documentation to be reproduced in the appendixes of this book, but also for their permission to package the evaluation version of PSpice with the text.

Recognition should also be given to the students of Cincinnati Technical College, who patiently made use of this text in manuscript while it was still being shaped and reshaped into its final form.

# Getting Started with PSpice

# 1.1 PSpice Software

In order to free engineers (and students) from the laborious, sometimes complex, and usually time-consuming work of circuit analysis, a team at the University of California at Berkeley developed SPICE (Simulation Program with Integrated Circuit Emphasis) software in the mid-1970s. SPICE consisted of a set of powerful algorithms for a wide range of circuit analysis methods. Unfortunately, SPICE was available only for mainframe and VAX-type computers.

In 1984 MicroSim Corporation made SPICE analysis available for personal computers under the name PSpice. Although PSpice is a commercial product costing thousands of dollars (depending on platform and analysis features), MicroSim has chosen to make an evaluation version available at no cost.

The evaluation version of PSpice has many, but not all, of the features of the commercial product. This version, while fully functional, has been designed with limitations that make it inadequate for commercial use. Businesses are expected to purchase the commercial PSpice package. For classroom and evaluation use, the limitations are not significant. The most relevant of these limitations are:

- 1. The evaluation version restricts circuits to a maximum of 10 transistors, compared to 200 transistors for the commercial package. This is not usually a problem in student designs. When necessary, the limitation can be circumvented by the creation of a subcircuit using a dependent current source to model the behavior of the transistor. There are similar limitations and solutions for the number of operational amplifiers that can be simulated.

- 2. The library for the evaluation version is much smaller than that of the commercial package. However, the reduced library does contain the more common components used in technical textbooks. For example, the 741 op amp, the 2N2222 transistor, and the 2N3906 and 2N3904 matched pair are included in the evaluation library.

There are other restrictions, such as the inability to perform distortion analysis; but this and similar restrictions are not important in a technical electronics program.

## **1.2 Installation**

PSpice must be run from a hard disk. Evaluation Version 6.0 is the current version of the PSpice software as of this publication date, and has been supplied with this text. The evaluation version may be copied and shared without violating copyright laws. Users can also contact MicroSim Corp. to obtain evaluation copies free of charge. Since Delmar has bundled PSpice with this text, contacting MicroSim would only be necessary if the hardware of the user's system required a different version. (See Section 1.4-PSpice Hardware Requirements.)

MicroSim will supply PSpice on 3.5- or 5.25-inch floppy disks for a DOS, Windows, or a Macintosh environment. The following installation description assumes that PSpice is being loaded onto the C: drive from 3.5-inch floppies in the B: drive and will run under DOS. Installation under other conditions is very similar.

To install PSpice, place disk one, which contains the INSTALL program, in drive B: and change to B: drive. At the B: prompt, type:

### B:\>install <return>

The INSTALL program is virtually transparent to the user. That is, with a minimum of user input, INSTALL will decompress the PSpice files, transfer the files into an appropriate subdirectory, and make changes to the user's AUTOEXEC.BAT and CONFIG.SYS files. The INSTALL interface to the user is a series of windows that open to explain the installation process, or to prompt the user for information. A detailed window-by-window explanation of the process is neither necessary or possible since INSTALL examines the user's computer and opens different windows depending on the system it finds. The process is well designed and painless; just answer questions, hit keys when prompted, and load the next disk when asked.

PSpice will be loaded into a subdirectory. The default name is \MSEVAL60. This is slightly cryptic (it stands for MicroSim Evaluation Version 6.0) and inconvenient, and the user is given the opportunity to use a different subdirectory name by back-spacing over the old name and entering a new one. The author prefers \SPICE, and so \SPICE will be used throughout this book.

After a subdirectory name is chosen, INSTALL will decompress and transfer the PSpice files. When this is complete, INSTALL may request permission to alter the user's AUTOEXEC.BAT and/or CONFIG.SYS files. If INSTALL asks if it may change a file, give it permission; the changes are necessary. The PSpice software requires a path into \SPICE and the setting of an environmental variable (SIMLIB-PATH = C:\SPICE) in AUTOEXEC.BAT. It also requires proper "file" and "buffer" sizes in the CONFIG.SYS. These details need not concern the user; INSTALL will set all parameters correctly.

The final messages to the user are to: (1) run the program SETUPDEV.EXE, which is necessary; (2) read the README.DOC file, which is not necessary; and (3) re-boot the system to use the new AUTOEXEC.BAT and CONFIG.SYS. Running SETUPDEV.EXE is important and cannot be skipped. PSpice needs to know a few facts about the user's system that INSTALL cannot determine; specifically, the type of display, the port to use for making hard copies, and the brand and model of the

hard copy device. SETUPDEV is a menu-driven program and allows the user to choose a video driver (probably IBMVGA), hard copy port (probably LPT1), and hard copy device from lists of options. Be sure to choose the SAVE option in the main menu before exiting.

Reading README.DOC can be skipped. The information is of little use to the new user of PSpice. README.DOC contains upgrade information and enhancement features that are only useful to the professional designer. Re-booting the system is important. While the AUTOEXEC.BAT can be rerun from the DOS prompt, changes made to the CONFIG.SYS file are unavailable to the system until a re-boot occurs.

# 1.3 Working Directory\_\_\_\_\_

Since INSTALL has created a path into C:\SPICE, the PSpice files can be run from the root directory, but this leads to the clutter of many circuit files stored in the root. PSpice can be used from the \SPICE directory, but this places user files among the PSpice files and creates more clutter. Another option is to work from the \SPICE directory but name every circuit file with A: (or B:) so it is saved on a floppy. This requires the user to always have a floppy. It also makes save and retrieve operations slow because of the slow access times for floppy drives.

The best solution to this problem is to create a new directory just for the user's circuit files. This method is used in this book. To create the new directory, change into the \SPICE directory and type:

C:\SPICE>mkdir circuits

This will make a new subdirectory under \SPICE. When using the PSpice program, first change into this directory using the change directory command. Type:

C:\>CD \SPICE\CIRCUITS <return>

The path into \SPICE created by the INSTALL program makes the PSpice programs available while in the \SPICE\CIRCUITS subdirectory, but files created by the user will be isolated in their own subdirectory.

# 1.4 PSpice Hardware Requirements\_

The hardware requirements for PSpice have grown over the last several versions as the software has been improved in its analysis abilities and its interface. Version 6.0 requires a hard disk, a co-processor and at least 2 Megabytes of extended memory. Users with systems that do not meet these requirements must either upgrade their systems or download earlier versions of the software from the MicroSim BBS (714-830-1550; no parity, 8 bits, 1 stop bit). Version 5.4 required a co-processor, but could operate in conventional memory, i.e. 640 kbytes of RAM. Version 5.1 worked in conventional memory and could operate with or without a co-processor; however operation without a co-processor was considerably slower.

### 4 / GETTING STARTED WITH PSPICE

A mouse is optional in all versions. Versions 5.1 and 5.4 used a text-based editor that was usually more convenient to operate from the keyboard. Version 6.0 gives the user a considerably improved graphic editor that can operate from the keyboard but makes much better use of the mouse by providing pull-down menus and hot buttons. While the monitor is obviously necessary, a printer (or plotter) is not. PSpice will still operate even if there is no means for making a hard copy of its results.

### 1.5 PSpice Editor

The most apparent improvement in version 6.0 of PSpice is the editor. The old, slow, text-based control shell and editor have been replaced by a graphic windowsstyle editor that is intuitive, convenient, and responds better to a mouse. Since the purpose of this text is to provide information about PSpice on an as-needed basis, a complete description of the editor operation is not given here. Editor features, like the PSpice analysis features, are introduced as they become relevant through the text. For now, an overview description of the editor will suffice.

The program PS.EXE is used to enter the PSpice editor. To begin using PSpice, change into the \SPICE\CIRCUITS subdirectory and type

### C:\SPICE\CIRCUITS>PS (filename)<return>

The user has the option to provide PSpice with the name of a file only if the file already exists. PSpice will not create a new file at the command line. When creating a new file, type PS with no argument. New files are named within the PSpice editor. When the return key is hit, PSpice displays the screen as shown in Figure 1.1.

Figure 1.1

The top line of the window contains a minus sign (-) on the left. A double click with the left mouse button on the minus sign is the signal to exit the PSpice editor and return to the DOS prompt. In the center is the filename of the current circuit description. This remains "untiled" until the first save of the circuit file. To the right are two squares containing small triangles. A single click with the left mouse button on the first square shrinks the editor window to an icon. A double click on the icon is required to return the editor window. A single click on the second square expands the window to fill the entire screen.

NOTE: In most programs the left mouse button is used far more than the right button. Consequently, it has become common to omit the reference to left or right, and to assume that "to click the mouse" always refers to the left button. When the right button is to be used, the word "right" is explicitly indicated. This convention will be used for the rest of this text.

The second line in the window lists menu titles for six pull-down menus. These are accessed by clicking with the mouse or by holding down the  $\langle Alt \rangle$  key and hitting the underscored letter in the menu title. Most of the menu items are obvious, making PSpice very intuitive to use. For example, most users would guess that pulling down the "File" menu and choosing "Save" would save the file to disk. Choosing "File" and then "Print" sends the file to the hard copy device (printer). Each menu option will be described as needed. Because saving files and opening already existing files are the primary interactions between PSpice and the operating system, a few items should be mentioned about naming files. DOS requires the root name of a file to be eight characters or less and PSpice requires a .CIR extension. When saving files, the extension can be included in the file name or omitted. The PSpice editor will automatically add the extension .CIR. Files should be named to indicate the type of circuit described in the file, but this is not mandatory. A filename of FOOLISH.CIR would be accepted, but this would be foolish. Files should be named to indicate a lab exercise or a problem number, or given names such as SERIES.CIR or RESO-NANT.CIR.

The third line in the window contains the hot buttons. Clicking a button is a shortcut to performing some of the most common operations. These are quite convenient and in most cases obvious. Clicking the question mark opens the help files. The second, third, and fourth buttons open, save, and print files respectively. The other buttons will be discussed as needed. The three rectangles to the right of the buttons contain the current cursor position, the editor mode (either insert or overwrite), and the amount of RAM memory in the computer.

Below these lines is the text area for writing the circuit description. To the right and below the text area are the scroll bars; these are accessed by the mouse, and allow the user to scroll through a long or wide document.

### 1.6 PSpice Circuit Descriptions

For PSpice to do its work, it needs information from the user about the circuit to be analyzed. This information consists of the following items.

### 6 / GETTING STARTED WITH PSPICE

1. THE TITLE LINE. The first line of every circuit description file is considered the title line and ignored by the analysis algorithms. It is not necessary to title a file, but it is necessary to provide a first line to be ignored. A typical title line might look like this:

\*Series circuit-Three resistors

The asterisk (\*) is recognized by PSpice as the beginning of a comment statement, and everything from the asterisk to the end of the line is ignored. Since the first line is always ignored, the asterisk is not strictly necessary; but it is generally used for clarity. If the user does not intend to title the circuit, a lone asterisk can be placed on line one.

One of the most common mistakes made by students learning PSpice is forgetting that line one will be ignored. If a voltage source or electrical component is placed on line one, it will be ignored when the circuit is analyzed.

- 2. SOURCES. PSpice accepts both voltage and current sources. Sources can be direct current or a variety of alternating current waveforms, and multiple sources can be included in a single circuit. The naming of sources and the proper syntax for use in a circuit description is left for Chapter 2, where DC circuits are described and analyzed.

- 3. COMPONENTS. PSpice accepts both passive and active components. Passive components include resistors, capacitors, and inductors. Diodes, bipolar transistors, op amps, and FETS are active components; that is, they perform amplification or switching functions, or they require their own source of power to perform their function. Again, procedures for naming and using these components are left to appropriate chapters.

- 4. ANALYSIS. PSpice can analyze circuits in many ways. It can determine component voltage drops and branch currents, but it can also sweep frequencies to determine bandwidth or perform Fourier analysis on complex waveforms.

- 5. OUTPUT. Once the circuit has been analyzed, the information requested by the user can be displayed as specific voltages and currents in an output file. The output file has the same root name as the circuit description file but has .OUT instead of .CIR for the extension. PSpice can also display the output information graphically on the monitor. By using PROBE to display output, the user can turn the computer screen into an oscilloscope and view waveforms as a function of time. PROBE can also display the results of a Fourier analysis effectively simulating a spectrum analyzer. If the circuit description file contains an error, the location of the error and the type of error are noted for the user in the output file.

# 1.7 Values and Units in PSpice\_

Values in electrical circuits vary greatly in magnitude. A circuit may have a 3 picoFarad capacitor and a 22 megohm resistor. PSpice allows users to enter component, source, and analysis values in standard floating-point notation, exponential

notation, or by using prefixes. For example, a 3 microHenry inductor can be expressed as

.000003 or 3e-6 or 3u

First notice that the unit Henry is not necessary. The user can include the proper unit for clarity, but PSpice ignores words such as Farads, Ohms, and Seconds. That is,

.000003Henry or 3e-6Henry or 3uH

are also valid inputs. PSpice knows the proper units for capacitors, resistors, inductors, time, and the like. Consequently the 22 megohm resistor can be expressed equivalently as

| 22000000 | 220000000hm | 22000000Ω | 22Meg   |

|----------|-------------|-----------|---------|

| 22Megohm | 22e6        | 22e6Ohm   | 2.2e7   |

| 22000K   | 22000Kilo   | 22000KQ   | 22000e3 |

Capacitor values deserve extra caution. If the word *Farad* is used following a capacitor value, the initial F in *Farad* is interpreted by PSpice as the prefix *femto*. The following two expressions do not represent the same capacitor value.

### 3e-6 3e-6Farad

The first expression indicates 3 microFarads. The second value is 3e-6 femtoFarads or 3e-21 Farads. To include the units and retain the value of 3 microFarads, the prefix for "micro" should be used instead of the exponential notation. The following two expressions are equivalent.

#### 3e-6

### 3uFarad

Valid prefixes recognized by PSpice are listed here:

| F   | (FEMTO) | 10e <sup>-15</sup> |

|-----|---------|--------------------|

| Р   | (PICO)  | 10e <sup>-12</sup> |

| Ν   | (NANO)  | 10e-9              |

| U   | (MICRO) | 10e <sup>-6</sup>  |

| Μ   | (MILLI) | 10e <sup>-3</sup>  |

| Κ   | (KILO)  | 10e+3              |

| MEG | (MEGA)  | 10e+6              |

| G   | (GIGA)  | 10e+9              |

| Т   | (TERA)  | 10e <sup>+12</sup> |

These prefixes can be used as upper- or lower-case letters. PSpice is not case-

sensitive, meaning upper- and lower-case letters are treated as identical characters. The use of most of these prefixes is obvious, but special note should be made that the symbols for micro, milli, and mega are U, M, and MEG.

# 1.8 PSpice from the Command Line

All PSpice operations such as printing, analysis, and graphical display can be accessed from within the PSpice editor, making the editor serve as the controller for the PSpice environment. This makes PSpice convenient and accessible to users who are only marginally familiar with DOS or perfer the convenience of a self-contained environment. The user does have the option to use PSpice from the command line, using his or her own preferred editor (any editor that will create an ASCII file), and calling the analysis and display programs directly from the DOS prompt. This was a useful feature in earlier versions of PSpice because the editor was slow and responded poorly to the mouse. In version 6.0, the editor has been greatly improved, making command line operation a matter of personal preference.

In this text, PSpice features will first be explained using the PSpice editor and afterward using command line entries. This is primarily for users who, because of hardware limitations, are using earlier versions of PSpice. DOS 5.0 and DOS 6.0 include a text editor called EDIT. Since this editor is as common to DOS users as any, EDIT will be used for examples of using PSpice from the command line.

# - 2

# **DC Circuits**

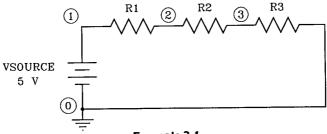

The focus of Chapter 2 is the description and analysis of circuits containing one or more direct-current power sources. The circuits to be analyzed are circuits that are likely to be encountered by students in a DC circuits analysis class or by novice electronics hobbyists. Circuit complexity increases through the chapter from a simple series circuit; through multiloop, multisource circuits; to DC circuits using capacitors and inductors. The description and analysis of Example 2.1 (a single-source, three-resistor series circuit) are explained in minute detail, including the use of the PSpice editor and the simulation software. For subsequent circuits, only new features are given this level of scrutiny.

# 2.1 Circuit Description

The circuit shown in Example 2.1 must be described in a manner understandable to PSpice, whether the PSpice editor or another editor is used. We use the PSpice editor first and discuss alternatives later.

For reasons described in Chapter 1, it is assumed that the PSpice files are in a subdirectory called \SPICE and the working directory is a subdirectory under \SPICE, namely \SPICE\CIRCUITS. At the appropriate prompt, type PS followed by <return>.

C:\SPICE\CIRCUITS>PS <return>

This command will call the PSpice environment. If this is the first time that PSpice has been used, or if a new blank text area was left in the editor when PSpice was last

### Example 2.1

exited, "untitled" appears in the center of the top line. If a circuit description was left in the editor, PSpice remembers the last circuit description and loads it. Figure 2.1 shows the menu options available in the "File" pull-down menu. Choosing "New" from the menu replaces an existing circuit description with a blank screen, ready for a new circuit.

In order to be both concise and clear about references to menu items and to actions requiring a mouse click, two typesetting conventions are adopted for the editor. First, references to menus, menu selections, or certain pop-up windows that appear in the editor are indicated by the use of *italics*. For example, the previous paragraph refers to the *New* selection in the *File* pull-down menu. Second, actions requiring a mouse click are indicated by **boldface** type. Sequences of actions are separated by backslashes. Saving a file to disk requires clicking the *File* menu and selecting *Save*. These actions are indicated by **\File**\Save. In fact, menu selections can be made in three ways:

- 1. From the keyboard, pull-down menus are chosen by hitting the <Alt> key and the underscored letter in the menu title. Menu items are chosen by hitting the underscored letter without the <Alt> key.

- 2. From the keyboard, pull-down menus can be chosen by hitting the <Alt> key, using the cursor keys to move the highlight left or right, and hitting <return>. When the menu opens, move up or down using the cursor keys to the required selection and hit <return> again.

- 3. Most commonly, menu selections are made using the mouse, clicking on each indicated **boldfaced** item.

|                                        | unffled                 |       |

|----------------------------------------|-------------------------|-------|

| Eile Edit Analysis [                   | un Options <u>H</u> elp |       |

| New                                    | 1.1 INS 7329 Pb         |       |

| New Edit Window                        |                         | *     |

| ©pen F2                                |                         |       |

| Save F3                                |                         | ŗ     |

| Save As.,.                             |                         | ····· |

| Page Setup                             |                         |       |

| Print F4                               |                         |       |

| DOS Shell                              |                         | Ì     |

| Close Window Alt+F4                    |                         |       |

| Exit All Alt+F3                        |                         |       |

|                                        | -                       |       |

| 7                                      |                         | *     |

| •••••••••••••••••••••••••••••••••••••• | *                       |       |

Figure 2.1

With the editor open and a blank text area (using Files New if necessary), the circuit description can be entered. The circuit description is a list, telling PSpice about the circuit to be analyzed. Since computers are notoriously poor at reading users' minds, care must be taken to describe the circuit in terms that PSpice can understand. The circuit description for Example 2.1 is given below with explanation for the proper syntax.

**Title Line** The first line of the circuit description—the title line—is ignored by the analysis program. Begin the title line with an asterisk. PSpice is not case-sensitive, meaning upper- and lower-case letters are treated identically. Throughout this book, upper-case letters are used for uniformity.

### \*DC1.CIR - SERIES CIRCUIT

**Source Description** PSpice allows the use of voltage and current sources. The general description of a DC voltage or current source is

### <source> <pos node> <neg node> <DC value>

where <pos node> and <neg node> are the positive and negative insertion points, respectively, for the DC supply. The circuit description becomes

\*DC1.CIR – SERIES CIRCUIT VSOURCE 1 0 5

There are several items to note in the description of a DC source.

- 1. A voltage source begins with a "V" plus the source name. A current source begins with an "I" plus the source name. The source name is any string of alphanumeric characters. Examples of acceptable source names are VSOURCE, VDC, V1, V38A, and IALPHA2. No space is permitted between the V (or I) and the rest of the source name. PSpice uses white space for delimiters; and entering V SOURCE would result in a double error because V would have no name and SOURCE would be considered the name of pos node>.

- 2. The order of the nodes is important. The positive node is written before the negative node. If the order is reversed, currents will travel through the circuit in an unexpected direction. Any alphanumeric string (up to 131 characters) can be used to name a node, but in practice nodes are usually named using non-negative integers.

- 3. PSpice uses conventional current flow. That is, positive current moves from positive to negative through a load. Since conventional current flows from negative to positive through a voltage source, this current is given a negative value by PSpice.

- 4. The circuit must have a ground reference named node "0" (node zero). Often it is convenient for the ground to be at the negative end of the source, but it can be at any point in the circuit.

### 12 / DC CIRCUITS

- 5. PSpice understands that the "5" means 5 Volts. The word "Volts" can be included to make the circuit description more readable for the user, but it is not necessary. If the word "Volts" is included, no space is permitted between the numeric value and the word "Volts," i.e., 5Volts.

- 6. The general description for any voltage or current source (DC or any of several AC waveforms) is given in Appendix C.

- 7. The delimiters between VSOURCE, the nodes, and the voltage value are spaces. PSpice also accepts multiple spaces, tabs, and commas. Throughout this text, spaces are used.

**Component Description** In this circuit, only resistors are used. In PSpice, resistors are indicated by an "R" plus a name. A complete list of component symbols is given in Appendix C. For the sake of simplicity, the resistors are called R1, R2, and R3. In more complicated circuits, components are usually given more descriptive names to make the description more readable. For example: RLOAD, REMITTER, RCOIL, or RSOURCE.

The general form for describing a resistor is

### R<name> <pos node> <neg node> <resistor value>

| *DC1 CIR | – SERIES CIRCUIT |

|----------|------------------|

| VSOURCE  | 105              |

| R1       | 1 2 1K           |

| R2       | 2 3 2K           |

| R3       | 3 0 3K           |

|          |                  |

Just as in the case of the source description, the nodes of components are listed positive node first.

**Analysis** In a resistive DC circuit, the user is generally interested in component voltages, voltages at nodes relative to ground, and branch currents. The general form of the command to perform .DC analysis is

### .DC <source> <starting voltage> <ending voltage> <increment>

Several items require further explanation in the .DC analysis command.

- 1. The dot (period) preceding the DC is required and indicates a directive for the PSpice software, as opposed to the previous component descriptions.

- 2. .DC analysis uses a "sweep" of voltage levels for a particular source. The first argument following the .DC command is the voltage source that is to be varied over the range set by the next two values. In this example VSOURCE is the source; but the circuit to be simulated does not have a variable source.

- 3. In order to indicate that a single voltage level is to be used, the starting and ending voltages are given the same value. An increment value must be provided,

even though the value is irrelevant, since the beginning and end of the sweep are the same voltage. PSpice requires an increment value greater than zero. For the example here, an increment of 1 is chosen arbitrarily.

The circuit description for Example 2.1 becomes

\*DC1.CIR – SERIES CIRCUIT

| VOORCE | 105           |

|--------|---------------|

| R1     | 1 2 1K        |

| R2     | 2 3 2K        |

| R3     | 3 0 3K        |

| .DC    | VSOURCE 5 5 1 |

**Output** PSpice can display the results of the analysis either graphically or as a printed list of values. In this example, because the values of concern are static and do not change over time, making a list is more appropriate. PSpice will deposit these values in a file with the same root name as the circuit description file, but with an .OUT extension, i.e., DC1.OUT. The output file will be examined in detail when the circuit description is complete and the PSpice analysis is finished. The general form for the output display command is

.PRINT DC <value one> <value two> . . .

The .PRINT DC command will print any number of circuit voltages and currents. Component voltages are indicated by using the nodes surrounding the component or by using the component name. The voltage dropped by R2 is written

V(R2) or V(2,3)

Voltages at nodes relative to ground are written

V(2) and V(3)

for the voltages at node 2 and node 3 respectively.

Currents must be written using component names. Using nodes will create a syntax error. In a series circuit there is only one value for current, but in the .PRINT DC statement it can be written using any of the following.

I(R1) I(R2) I(R3) I(VSOURCE)

PSpice uses conventional current, meaning current flowing from a positive node to a negative node through a load is considered positive. In the sample circuit, the current through R1, R2, and R3 travels from the positive end of each resistor to the negative end. The current through the source flows from the negative end to the positive end. Consequently, the value given by PSpice for I(SOURCE) will be the same magnitude as the current value for the resistors, but will have a negative sign.

Assuming the user is interested in the voltage dropped by R2, the voltage at node 2 relative to ground, and the current in the loop, the circuit description becomes

```

*DC1.CIR – SERIES CIRCUIT

VSOURCE 1 0 5

R1 1 2 1K

R2 2 3 2K

R3 3 0 3K

.DC VSOURCE 5 5 1

.PRINT DC V(2,3) V(2) I(R2)

.END

```

All circuit descriptions end with the .END statement.

This completes the circuit description. To save the circuit description to disk, either use **\File\Save** or click the third hot button from the left, i.e., the button with the picture of a floppy disk. If the file has not yet been named, a window will open providing the opportunity to name the file. Any name may be chosen, but in the context of this chapter, DC1.CIR is a logical choice. The user may include the .CIR extension or allow the editor to automatically add it. After the save operation, the word "untitled" at the top of the window is replaced by the new file name.

# 2.2 Circuit Analysis

Before running the analysis program, certain analysis options should be set. Open the Analysis Options window by executing \Analysis \Analysis Options. The options to automatically run PROBE after analysis and to browse the output file after the analysis should be turned off. These options are toggled on and off by clicking the box to the left of the option. PROBE is the graphics display program. Since the circuit description has requested two voltage values and one current value, there is no data to represent graphically. The browser allows the user to examine the analysis output, but does not allow any editing of the file. Usually the output file contains some unneeded information, a number of page breaks, and a great deal of white space, that can be deleted. *PSpice* should be chosen as the simulator and the window can be closed by clicking **OK**.

The analysis can be started in three ways. \**Run**\**Simulator**; hitting the F11 key; or clicking the analysis hot button (the 11th button from the left) begins the simulation. The simulator program begins by replacing the editor screen with a display containing information about the analysis. For a circuit as simple as DC1.CIR, the analysis only takes a second, and then the editor returns to the screen. The output file created by the simulator can be examined by using \**Analysis\Browse Output**.

If editing of the output file is necessary, it can be edited by using the PSpice editor. Use File we Edit Window and then File open to open DC1.OUT. Typically, there is a large amount of unneeded information, white space, and page breaks to be deleted. Because the PSpice editor scrolls rather slowly, it may not be the best choice for editing the output file. If the analysis is to be included in a larger file such as a

lab report, it is usually more convenient to load the entire DC1.OUT file into a word processor and then edit.

VSOURCE V(2,3) V(2) I(R2) 5.000E + 00 1.667E + 00 4.167E + 00 8.333E - 04

The requested voltages and currents are displayed in exponential notation and in standard units, i.e., Volts and Amperes. The voltage from node 2 to node 3 is 1.667 Volts. The voltage from node 2 to ground is 4.167 Volts, and the current through resistor R2 is .8333 milliamps.

# 2.3 Command Line Circuit Description and Analysis\_

The circuit description file can be created and the PSpice analysis completed without the use of the PSpice command shell. Any text editor or word processor that will create an ASCII file can be used to create the DC1.CIR file. Since EDIT.EXE supplied with DOS 5.0 is probably the most commonly available text editor, it is used as the example editor in this book. Most users choose to store the utility files supplied with DOS in a subdirectory called DOS. Consequently it is necessary to have a PATH into C:\DOS as part of the PATH command in the AUTOEXEC.BAT file. If the user prefers to use another editor, a PATH to the appropriate subdirectory is necessary. Assuming the user has installed the PSpice files in the \SPICE subdirectory and has created another subdirectory \SPICE\CIRCUITS as explained in Chapter 1, the circuit description file is created by typing

C:\SPICE\CIRCUITS>EDIT DC1.CIR <return>

Even though the PSpice editor has been greatly improved, the EDIT editor has several advantages. EDIT scrolls long documents better, responds better to the mouse, and is more convenient for deleting large amounts of text. Use of the editor is not explained here. It is left to the user to enter the circuit description, repeated here for convenience:

\*DC1.CIR – SERIES CIRCUIT VSOURCE 1 0 5 R1 1 2 1K R2 2 3 2K R3 3 0 3K .DC VSOURCE 5 5 1 .PRINT DC V(2,3) V(2) I(R2) .END

Save the file and return to the DOS prompt. To run the circuit analysis software, enter

### 16 / DC CIRCUITS

### C:\SPICE\CIRCUITS>PSPICE DC1.CIR <return>

The result of the analysis is stored in DC1.OUT. To view the output, to edit it, or to print a hard copy, use the editor with DC1.OUT as the argument.

C:\SPICE\CIRCUITS>EDIT DC1.OUT <return>

### 2.4 Errors\_

It is always possible that a circuit description contains an error. For example, R3 might be described as spanning nodes 3 and 4. This would indicate an open circuit that would be impossible for PSpice to analyze.

R3 3 4 3K

Omitting the final "1" from the .DC analysis line would be an error.

.DC VSOURCE 5 5

Of course, if the user incorrectly enters R3 as a 4K resistor instead of a 3K resistor, PSpice-having no way of knowing this was incorrect-would analyze the circuit using 4K as the value of R3.

The PSpice environment has two methods for detecting errors in a circuit description. The first method involves running the syntax checker before performing the simulation. This can be done in any one of three ways. \**Analysis\Syntax Check**; hitting the F10 key; or clicking the hot button containing the check mark (the 10th button from the left) all run the syntax checker. If there is no error in the circuit description, a pop-up window notifies the user. If an error is found, a different window opens explaining the location and the type of error. Clicking *Goto Error* returns the user to the editor on the line where the error was found.

Alternatively, the simulator can be used without checking for errors. If the analysis program detects an error, the analysis is stopped and a message appears in the analysis window telling the user to examine the .OUT file. The location and the type of error is noted in the circuit description in the output file. The error must be corrected in the .CIR file; corrections made in the .OUT file will not correct the problem.

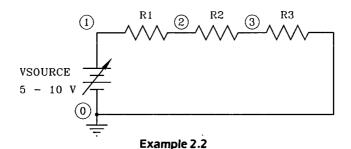

## 2.5 Variable-Source Circuits\_

The tedium of circuit calculations performed by hand doubles and triples when the same circuit must be analyzed a second and third time because a single component is changed. If the voltage source used in Example 2.1 is replaced by a variable supply, the component voltages and the current must be recalculated for each new source voltage value. In Example 2.2, the supply is changed from 5 Volts to 10 Volts in steps of .5 Volts. This means the circuit must be analyzed 11 times, a task better suited to computers than to humans.

To have PSpice sweep the voltages from 5 to 10 volts, the .DC analysis line is changed to read

.DC VSOURCE 5 10 .5

This instructs the software to analyze the circuit for all voltages from 5 to 10 Volts inclusively in .5 Volt increments. The output file will contain the following information:

| VSOURCE     | V(2,3)      | V(2)        | I(R2)       |

|-------------|-------------|-------------|-------------|

| 5.000E+00   | 1.667E + 00 | 4.167E+00   | 8.333E-04   |

| 5.500E + 00 | 1.833E + 00 | 4.583E + 00 | 9.167E-04   |

| 6.000E + 00 | 2.000E + 00 | 5.000E + 00 | 1.000E - 03 |

| 6.500E + 00 | 2.167E + 00 | 5.417E + 00 | 1.083E - 03 |

| 7.000E + 00 | 2.333E + 00 | 5.833E + 00 | 1.167E-03   |

| 7.500E + 00 | 2.500E + 00 | 6.250E + 00 | 1.250E-03   |

| 8.000E + 00 | 2.667E + 00 | 6.667E + 00 | 1.333E - 03 |

| 8.500E + 00 | 2.833E+00   | 7.083E + 00 | 1.417E - 03 |

| 9.000E + 00 | 3.000E + 00 | 7.500E + 00 | 1.500E - 03 |

| 9.500E + 00 | 3.167E + 00 | 7.917E+00   | 1.583E-03   |

| 1.000E + 01 | 3.333E + 00 | 8.333E + 00 | 1.667E - 03 |

The task of recalculation changes from tedious to ridiculous when the voltage increment is decreased to something very small and requires hundreds or thousands of calculations. Even if the calculations are made by a computer, the resulting tabled data are difficult to read. A better and faster solution is to calculate fewer points and then graph those points, allowing the user to extrapolate the values in between the calculated values. PSpice can very simply make the indicated graph using the range of source voltages as the independent variable (X-axis), and the calculated component voltages and currents as dependent variables (Y-axis). To indicate that a graph is needed, the .PROBE command must be added to the circuit description. The revised file becomes:

\*DC2.CIR VSOURCE 1 0 5

```

R1 1 2 1K

R2 2 3 2K

R3 3 0 3K

.DC VSOURCE 5 10 .5

* DC ANALYSIS FROM 5 TO 10 VOLTS - STEP .5 VOLTS

.PROBE

* PROBE – COMMAND TO USE GRAPHICS TOOLS

.PRINT DC V(2,3) V(2) I(R2)

.END

```

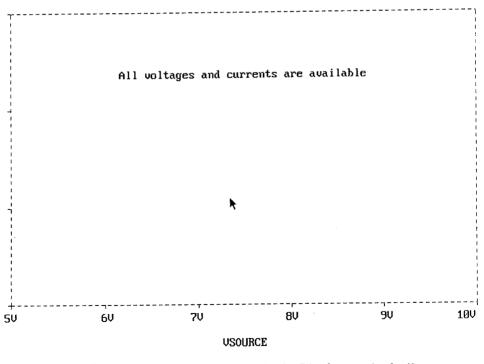

PSpice will still write the requested voltages and current to the .OUT file, but will also create a few new files that contain the information needed to graphically represent the results. PROBE.EXE is the PSpice program that accesses these files and displays the data on a coordinate plane. PROBE can be run automatically when the simulation is complete by clicking the *Auto-run Probe* box in the *Analysis Options* window (\**Analysis\Analysis Options**), or manually, using any one of three methods: \**Run\Probe**; hitting the F12 key; or clicking the PROBE hot button (the 12th button from the left).

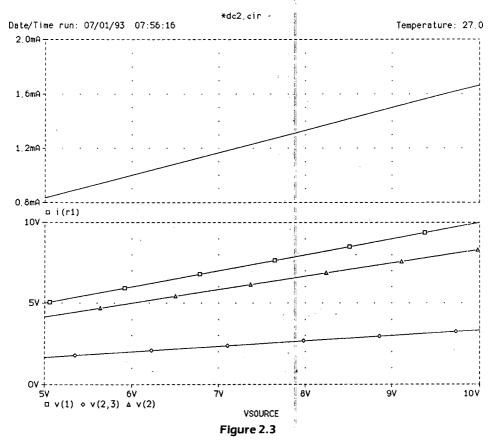

As shown in Figure 2.2, PSpice allows the user to graph many voltages and currents. Generally, the source voltage is graphed first as a reference. A second and

Exit <u>Add\_trace</u> X\_axis Y\_axis Plot\_control Display\_control Macros Hard\_copy Zoom Label conFig\_colors

third trace can be added to show V(2,3) and V(2) as these voltages change with the changing source voltage.

The current I(R2) could also be graphed, but the plotted line would merely be traced across the bottom of the graph. This occurs because the current magnitude is about 1000 times smaller than that of the graphed voltages. PSpice is willing to use the Y-axis for both voltage and current, but the scale must be the same for both. This means that as the voltage at node 1 is graphed at 5 (5 Volts) the current at that voltage is graphed at .8333e-3 (.0008333 Amps) or virtually zero. The solution is to graph the current on its own plot so that PSpice can give it an appropriate scale on the Y-axis. To do this, choose "Plot\_control" from the menu. This results in a new list of menu options. If you choose "Add\_plot" from the menu, a second plot appears on the screen above the first. When you choose "Exit" from the "Plot\_control" menu, the main menu reappears. The current can now be graphed with reasonable Y-axis scaling, as shown in Figure 2.3. Hitting "e" twice (or <esc> twice) returns the user to the PSpice editor. Working from the command line, the operation is virtually the same.

C:\SPICE\CIRCUITS>PSPICE DC2.CIR

### 20 / DC CIRCUITS

runs the analysis program. When the analysis is finished, PROBE can be run from the command line by typing

### C:\SPICE\CIRCUITS>PROBE DC2.CIR

This two-command sequence has been automated in a batch file called SIM.BAT. By typing SIM DC2.CIR at the C:\SPICE\CIRCUITS> prompt on the command line, the computer is instructed to run the PSpice simulation program, and if the circuit description contains the .PROBE instruction, then the PROBE program is run automatically when the analysis is complete.

In fact, PROBE is more commonly used to illustrate changes over time or frequency than a range of voltages. Consequently, it is more often used to display voltages and currents in circuits with alternating current sources. Used in this manner, PSpice can duplicate the operation of an oscilloscope or a spectrum analyzer, but these functions will be explained in later chapters.

# 2.6 Series-Parallel Circuits

As the number of branches and elements in a circuit becomes greater, analysis by hand calculation becomes more difficult, more time consuming, and more prone to error. Each of these problems is minimized by using PSpice. Additional branches and elements require more care in labeling nodes and writing the circuit description, but otherwise the procedure for complex circuits is the same as that for a simple series circuit. See Example 2.3.

\*DC3.CIR-SERIES - PARALLEL CIRCUIT V1 1 0 20 R1 1 2 100 R2 2 3 200 R3 3 4 300 R4 2 5 400 R5 3 6 500 R6 5 0 600 R2 R3 R1 3 (4) (2) 100 200 300 R4 R5 400 500 ٧ı R9 20 Volts (5) (6)900 R6 R7 R8 600 700 800  $\bigcirc$

### Example 2.3

R7 5 0 700 R8 6 0 800 R9 4 0 900 .DC V1 20 20 1 .PRINT DC I(R1) I(R4) I(R5) I(R9) .PRINT DC V(2,3) V(3,6) V(6,0) V(0,5) V(5,2) .END

The currents in the .PRINT DC statement in Example 2.3 were chosen to illustrate that the current provided by the source is equal to the sum of the branch currents. The current I(V1) is negative because the circuit current moving through the source is flowing from the negative end of the source to the positive end.

| V1        | I(V1)      | I(R4)     | I(R5)     | I(R9)     |

|-----------|------------|-----------|-----------|-----------|

| 2.000E+01 | -4.123E-02 | 2.196E-02 | 9.249E-03 | 1.002E-02 |

The voltages in the second .PRINT DC statement were chosen to illustrate that the voltage drops and rises around a loop must sum to zero. The polarity of the requested voltages is particularly important when summing a loop. As the loop is traced in the clockwise direction, the values are positive until V(0,5). The voltage from node 0 to node 5 is a rise in potential and is represented by PSpice as a negative drop.

V1V(2,3)V(3,6)V(6,0)V(0,5)V(5,2)2.000E + 013.854E + 004.624E + 007.399E + 00-7.094E + 00-8.783E + 00

# 2.7 Multiple-Source-Multiple-Loop Circuits

The next level of difficulty usually encountered in the study of DC networks is the analysis of multiple-source-multiple-loop circuits. This involves solving simultaneous equations that describe each loop in the circuit, a process that greatly increases both the amount of time involved and the opportunity for error. Further, if the circuit analysis does not match the student's experimental results, tracing the error can be quite difficult. As circuitry increases in complexity, the advantages of using PSpice become more dramatic.

As in the case of series-parallel circuits, there are no new features to learn for the analysis of multiple-source-multiple-loop circuits. Errors in these circuits usually occur because of problems in describing the polarity of the voltage sources. Obviously, if a source is accidentally described to PSpice with the polarity reversed, the voltages and currents in the circuit will be changed radically.

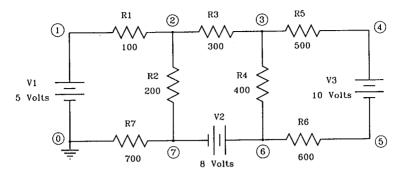

Consider the circuit shown in Example 2.4.

\*DC4.CIR MULTI-LOOP, MULTI-SOURCE CIRCUIT V1 1 0 5 V2 6 7 8

### 22 / DC CIRCUITS

Example 2.4

The analysis of this circuit results in an output file containing the requested information.

\*DC4.CIR MULTI-LOOP, MULTI-SOURCE CIRCUIT \*\*\*\* DC TRANSFER CURVES TEMPERATURE = 27.000 DEG C V1 I(R4) 5.000E+00 - 2.743E-03

In more simple circuits, it is usually easy to determine which end of a resistor is the positive node, and consequently should be placed first in the circuit description. In a circuit with multiple sources, the positive end of the component is less obvious. The current through resistor R4 was chosen for display in this example because it is not apparent in which direction current will flow through the resistor. In the circuit description, node 5 was placed first on the incorrect supposition that it was the positive node. PSpice is able to analyze the circuit, correctly giving the current through R4 a negative value to indicate that the current, in fact, travels backward compared to the polarity indicated by the user in the circuit description.

# 2.8 Analysis at Circuit Nodes\_

In all versions of PSpice prior to version 6.0, the .OUT for every circuit analyzed contained the voltages at each circuit node and the currents through each source. This served as the default analysis and required no special instruction in the circuit description. Version 6.0 does not provide node voltages unless specifically told to include them in the output file. The circuit description for the circuit in Example 2.4 has been rewritten with the .DC analysis and the .PRINT DC commands marked as comments by asterisks. .SAVEBIAS is the command to provide node voltages and source currents. The syntax for the command is

.SAVEBIAS < name of output file without .OUT extension >> voltage type>

\*DC4.CIR MULTI-LOOP, MULTI-SOURCE CIRCUIT V1 1 0 5 V2 6 7 8 V3 4 5 10 R1 1 2 100 R2 2 7 200 R3 2 3 300 R4 3 6 400 R5 3 4 500 R6 5 6 600 R7 7 0 700 \*.DC V1 5 5 1 \*.PRINT DC I(R4) .SAVEBIAS DC4 DC .END

When the simulation is complete, the .OUT file contains the following information.

| ****       | SM                  | ALL SIG | NAL BL | AS SOLUTI | ON | I TEN | <b>IPERATU</b> | RE | . = 27 | .000 DEG C |

|------------|---------------------|---------|--------|-----------|----|-------|----------------|----|--------|------------|

| NOI        | DE VO               | OLTAGE  | NODE   | VOLTAGE   | 3  | NODE  | VOLTAGI        | Ξ  | NODE   | VOLTAGE    |

| (          | 1)                  | 5.0000  | ( 2)   | 4.7566    | (  | 3)    | 8.6062         | (  | 4)     | 13.6500    |

| (          | 5)                  | 3.6504  | ( 6)   | 9.7035    | (  | 7)    | 1.7035         |    |        |            |

| VOI        | TAG                 | E SOUR  | CE CUR | RENTS     |    |       |                |    |        |            |

| NAN        | ИE                  |         | CUF    | RENT      |    |       |                |    |        |            |

| <b>V</b> 1 | V1 - 2.434E - 03    |         |        |           |    |       |                |    |        |            |

| V2         | $V_2 - 1.283E - 02$ |         |        |           |    |       |                |    |        |            |

| V3         | V3 -1.009E - 02     |         |        |           |    |       |                |    |        |            |

The node voltages are all referenced to node 0 (the ground point). The currents

through the voltage supplies are negative because the current travels through supplies from negative to positive and PSpice indicates positive current as flowing from positive to negative. PSpice also allows the user to request the original information about the current through the R4 resistor by removing the comment asterisks from the .DC and .PRINT DC lines. If both types of analysis are requested, however, PSpice places the .DC analysis in the .OUT file and the analysis at the circuit nodes in a file without extension (DC4).

# 2.9 Transient Analysis of Resistor-Capacitor Circuits\_

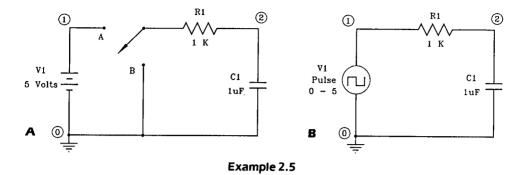

The last topic usually considered in a DC circuit analysis class is the response of reactive elements to a DC supply. These circuits differ from all the previous circuits in that the currents and voltages generated are time dependent. That is, the current through the circuit and the voltages dropped across each component are not constant until the electric and magnetic fields of the reactive components have reached steady-state conditions. Consider the resistor-capacitor circuit shown in Example 2.5.

Example 2.5A is a circuit typically found in a lab exercise for determining RC time constants. When the switch is thrown to position A, current flows and the capacitor begins to charge. After the capacitor has reached full charge, the circuit is singularly uninteresting. After this point, no current flows, and the capacitor drops the entire source voltage. Consequently, analysis generally focuses on the action of the circuit prior to the full charge time. Similarly, in the discharge phase when the switch is moved to position B, the circuit is interesting only during the capacitor discharge. Afterward no current flows, and no voltages are generated.

The closing and opening of the switch in Example 2.5A can easily be described to PSpice by the use of a square wave source that outputs 5 Volts for some length of time and then changes to 0 Volts, allowing the capacitor to discharge. The PSpice circuit description for this circuit (Example 2.5B) introduces a few new features, so the description is given, and then the new items are explained.

```

*DC5.CIR RESISTOR-CAPACITOR CIRCUIT

V1 1 0 PULSE( 0 5 0 1N 1N 5M 10M)

R1 1 2 1K

C1 2 0 1U

.TRAN 1M 10M

.PROBE

.PRINT TRAN V(2) V(1,2) I(R1)

.END

```

First, notice that the source is not described as a DC voltage source. The DC supply in PSpice is not time dependent. If the source were described as a DC supply, the output developed by PSpice would reflect the conditions after steady-state conditions had been reached. Besides this, the circuit requires a means of allowing the capacitor to discharge, simulating the switch being moved to position B.

Describing the source as a square wave that changes from 5 Volts to 0 Volts after

the capacitor reaches full charge gives a time-dependent source. Dropping the source to 0 Volts simulates the shorting discharge path. The PULSE voltage source supplies the required square wave defined by the string of arguments within the parentheses. The general form for the PULSE source is:

PULSE ( initial voltage pulse voltage delay time rise time fall time pulse width period )

Each of these arguments deserves a few words of explanation.

**initial Voltage = 0** This is the starting voltage and the low-level voltage of the square wave. In our example, the voltage applied to the circuit is 0 (zero) until the switch is moved to position A. At that time, the applied voltage jumps to 5 Volts.

**Pulse Voltage = 5** This is the high-level voltage of the square wave. In our example, it is 5 Volts corresponding to the applied 5 Volt DC source.

**Delay Time** = 0 This is the amount of time between the beginning of our observation of the circuit and the beginning of the first pulse. In our example, we begin to observe the circuit at the instant when the switch is thrown. Consequently the delay is zero seconds.

**Rise Time** = 1N The rise time is the amount of time required for a signal to change from its low-level voltage to its high level. This must be a value greater than zero. Every action requires a finite amount of time, although the amount may be vanishingly small. Here the rise time is given a value of one nanosecond. While PSpice has trouble with an ideal square wave (0 second rise time), PSpice will allow an arbitrarily small rise time that can very closely approximate an ideal square wave.

Fall Time = 1N The fall time is the amount of time required for a signal to

change from its high-level voltage to its low level. The fall time, like the rise time, must be greater than zero, but it can be arbitrarily small.

**Pulse Width** = 5M The pulse width is the length of time the signal will remain at the high voltage level. Five milliseconds was chosen in this example because the RC time constant for the circuit is one millisecond. This pulse width, in effect, leaves the switch in position A for exactly five time constants, just long enough to bring the capacitor to full charge.

**Period** = 10M The period is the time needed to complete one cycle of the square-wave signal. Since the pulse width is 5 milliseconds, a period of 10 milliseconds implies the signal is at the low-level voltage for the remaining 5 milliseconds. In this example, the discharge path of position B is equivalent to a zero voltage on the source, allowing the capacitor to discharge through V1. In either case the discharging time constant is the same. A 50% duty cycle was chosen because the charging and discharging time constants in this circuit are identical. PSpice does not require this and the analysis proceeds correctly for whatever duty cycle the user indicates by the pulse width and period values.

Line 4 describes the capacitor. Since the symbol "R" is used to indicate resistors, it is not surprising that PSpice uses "C" to indicate capacitors. As in the case of resistors, the next two numbers indicate the nodes for the position of the capacitor in the circuit. The value of the capacitor is one microfarad, which is written as 1U.

.TRAN tells PSpice that a time-based analysis is to be used. The general form for the .TRAN command is

### .TRAN <sample time> <analysis duration>

PSpice calculates circuit values as often as PSpice determines it is necessary in order to make an accurate graphical display of the analysis. This frees the user from making the determination. While .PROBE makes good use of this information, there would be an overwhelming amount, of difficult to interpret data, if it were all printed in the .OUT file. The sample time of one millisecond in the example circuit indicates that only information calculated at one millisecond intervals should be printed to the output file. In short, the .Print TRAN statement makes use of the sample time parameter to restrict the printed data to manageable amounts, but .PROBE ignores the sample time and displays all of the calculated data. Even if the .Print TRAN statement is not included in the circuit description, and the sample time parameter is not used, the sample time value could not be omitted. Some value, less than the analysis duration, must be included to avoid a syntax error.

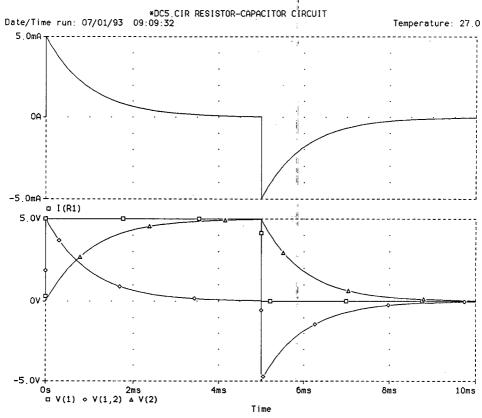

The .PRINT TRAN command tells PSpice to include values for the voltage across the capacitor V(2), the voltage across the resistor V(1,2), and the loop current I(R1), in the .OUT file. The data are given in the table at the top of page 27.

The PROBE program can be set to run automatically when the simulation is complete by setting the Auto-run box in the Analysis\Analysis Options window, or run manually by clicking the PROBE hot button. When examining a time-based signal, it is useful to begin by graphing the input waveform as a reference. Graphing V(2)

### CHAPTER TWO / 27

| TIME        | V(2)        | V(1,2)        | I(R1)        |

|-------------|-------------|---------------|--------------|

| 0.000E + 00 | 0.000E + 00 | 0.000E + 00   | 0.000E + 00  |

| 1.000E - 03 | 3.156E + 00 | 1.844E + 00   | 1.844E - 03  |

| 2.000E - 03 | 4.324E + 00 | 6.760E - 01   | 6.760E - 04  |

| 3.000E - 03 | 4.752E + 00 | 2.479E - 01   | 2.479E - 04  |

| 4.000E - 03 | 4.909E + 00 | 9.088E - 02   | 9.088E - 05  |

| 5.000E - 03 | 4.967E + 00 | 3.126E - 02   | 3.126E - 05  |

| 6.000E - 03 | 1.830E + 00 | - 1.830E + 00 | -1.830E - 03 |

| 7.000E - 03 | 6.710E - 01 | -6.710E - 01  | -6.710E - 04 |

| 8.000E - 03 | 2.460E - 01 | -2.460E - 01  | -2.460E - 04 |

| 9.000E - 03 | 9.020E - 02 | -9.020E-02    | -9.020E-05   |

| 1.000E - 02 | 3.300E - 02 | -3.100E-02    | -3.100E-05   |

and V(1,2) against the source illustrates the reversal in polarity of the resistor voltage. To see the change in the circuit current over time, a second plot should be generated using "Plot\_control" and adding the trace  $I(R_1)$ .

The final output generated by PROBE is shown in Figure 2.4.

Figure 2.4

# 2.10 Transient Analysis of Resistor-Inductor Circuits

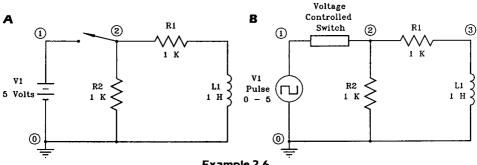

With a small modification, the same circuit can be used to test the transient response of a resistor-inductor circuit. By substitution of an inductor for the capacitor and introduction of a voltage-controlled switch, a circuit typically used as a lab exercise can be simulated. The symbol recognized by PSpice for an inductor is an "L," which is the standard symbol used in electronics.

Because an inductor's magnetic field must collapse as soon as the maintaining current is removed, circuits designed to measure an L/R time constant usually include a resistor such as R2 to provide a discharge path for the coil. Without this path, the current generated by the collapsing field will cause the switch to arc over. During the charging of the coil, R2 is in parallel with the source and does not affect the current through the coil or the voltages across R1 or the coil.

Modeling Example 2.6A requires a new element to effectively disconnect the source from the circuit. Merely reducing the voltage source to zero would indicate a short circuit across R2 and identical L/R time constants for the charging and discharging phases. To model Example 2.6A accurately, an open circuit must replace the source when the voltage drops to zero. The voltage-controlled switch in Example 2.6B will produce a virtual short when the source is at 5 Volts and an open when the source falls to zero.

Modeling the switch requires two lines in the circuit description.

### SI 2 1 1 0 V\_SWITCH

This tells PSpice that the switch (S1) is placed between nodes 2 and 1. The switch is controlled by the voltage between nodes 1 and 0 (i.e., the source). V\_SWITCH is the arbitrarily chosen name for the switch. The general form for the switch is:

#### S<name> <+ switch node> <- switch node> <+ control node> + <- control node> <switch name>

### .MODEL V\_SWITCH VSWITCH

Example 2.6

Because PSpice can model many kinds of switches, it is necessary to specify the type of switch to use in the analysis. The .MODEL tells PSpice that the switch that has been named V\_SWITCH is of type VSWITCH. The parameters of VSWITCH can be user specified, but in this example the default values are acceptable. The general form is

### .MODEL <switch name> <switch type>

By default a VSWITCH has a value of 1 ohm when the controlling voltage is at least 1 Volt, and 1 Megohm when the controlling voltage is 0 volts or less.

The resulting circuit description is

```

*DC6.CIR RESISTOR-INDUCTOR CIRCUIT

.MODEL V_SWITCH VSWITCH

V1 1 0 PULSE(0 5 0 1N 1N 5M 10M)

R1 2 3 1K

R2 2 0 1K

L1 3 0 1

S1 2 1 1 0 V_SWITCH

.TRAN .1M 10M

.PROBE

.END

```

Graphing the source voltage, the resistor voltage, the inductor voltage, and the circuit current yields textbook results.

## 2.11 Ideal Components

PSpice treats capacitors and inductors as ideal components. This means that capacitors have zero leakage current (infinite parallel resistance) and inductors have zero winding resistance. Since the parallel resistance of capacitors is usually very large (tens or hundreds of Megohms), omitting the parallel resistor in the modeled circuit creates an error between the model and reality that is insignificantly small. Omitting the winding resistance for a large inductor, on the other hand, can result in large errors. In the previous example, a one-Henry inductor might have a winding resistance of 200 ohms. Since this would represent 17% of the total circuit resistance, the charging and discharging times for the real circuit would not match the times generated by the PSpice model. The circuit description should be altered to include this resistance.

\*DC6.CIR RESISTOR-INDUCTOR CIRCUIT .MODEL V\_SWITCH VSWITCH V1 1 0 PULSE(0 5 0 1N 1N 5M 10M) R1 2 3 1K

R2 2 0 1K L1 3 4 1 RCOIL 4 0 200 S1 2 1 1 0 V\_SWITCH .TRAN .1M 10M .PROBE .END

Notice that the voltage across the inductor is still the voltage at node 3 and not V(3,4). In reality, it is impossible to take a voltage reading across the inductor without also measuring the voltage drop across the winding resistance.

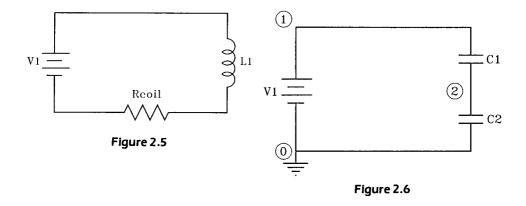

Two other problems are caused by the ideal capacitor and inductor models used by PSpice. Consider the circuit shown in Figure 2.5.

Modeling this circuit without a value for the winding resistance results in an error when the analysis is attempted because PSpice interprets the inductor as zero resistance and a short across the source. For a less obvious reason, the capacitor circuit shown in Figure 2.6 could not be modeled without a parallel leakage resistance.

Again the problem is the treatment of the capacitors as ideal elements. In this circuit, node 2 represents an open in the circuit. PSpice must be able to establish a DC bias voltage for every point in the circuit. Since node 2 is isolated by two infinite resistances, no DC bias voltage can be established, and PSpice indicates an error. This problem can be avoided by including a parallel resistance for at least one of the capacitors. Adding a 100 Megohm resistor in parallel with C1 would not change the circuit performance appreciably, but would allow PSpice to establish the needed DC bias, and would make the circuit description more accurately model the real circuit.

# 2.12 Potentiometers

The only topic generally covered in a DC circuits analysis class is the use of variable resistors. PSpice can model potentiometers, but the model requires the use of subcircuits and other complex PSpice features that are inappropriate for inclusion at this point. Potentiometers are modeled in Chapter 5. -3

# **AC Circuits**

The advantages of circuit analysis software increase dramatically when the voltage (or current) source changes in magnitude and polarity. Because capacitors and inductors cause phase shifts between the voltage and current in an AC circuit, the scalar algebra use to analyze DC circuits must be replaced by vector algebra. Not only do the calculations required to determine voltage levels and phase angles increase the difficulty of the analysis and the amount of time invested, but the repeated conversions between polar and rectangular coordinates greatly increase the opportunity for error.

PSpice not only eliminates the need for tedious calculation but can also display the results of the analysis in graphic form. It is generally true that numeric voltage and current levels in an AC circuit are less useful to a technician than the waveform those numbers describe. That is, technicians rely more on oscilloscopes when examining AC circuits than on volt meters. This is especially true at high frequencies.

In the previous chapter, PSpice is used to examine the voltage dropped across a capacitor charged by a DC supply. The table of time-dependent voltages was clearly less useful in understanding the behavior of the component than the same information in graphic form. Similarly, we rely on the ability of PSpice to graphically display circuit response in AC circuits.

For convenience, the syntax for descriptions of resistors, capacitors, and inductors is repeated here:

resistor

R<name> <pos node> <neg node> <value>

capacitor

C<name> <pos node> <neg node> <value>

inductor

L<name> <pos node> <neg node> <value>

### 32 / AC CIRCUITS

PSpice allows the user to simulate many AC waveforms. The PULSE waveform is introduced in Chapter 2. Because a sine wave is the only waveform not distorted by capacitors and inductors, it is of primary interest in the study of AC circuits. Descriptions of other available waveforms, such as exponentials and piecewise linear waves, are found in Appendix C.

A sine wave voltage source is described by the following:

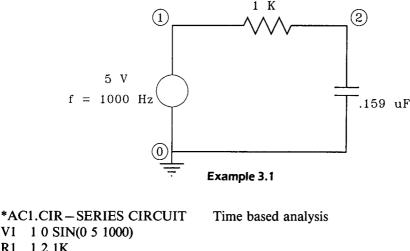

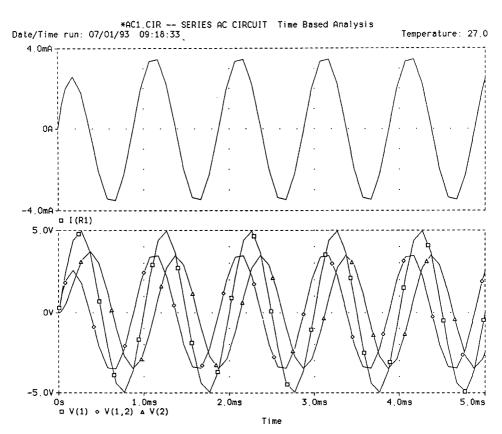

### V<name> <pos node> <neg node> SIN (sine wave parameters)