Lecture Notes in Electrical Engineering 294

Valery Sklyarov Iouliia Skliarova Alexander Barkalov Larysa Titarenko

# Synthesis and Optimization of FPGA-Based Systems

## **Lecture Notes in Electrical Engineering**

## Volume 294

#### Board of Series Editors

Leopoldo Angrisani, Napoli, Italy Marco Arteaga, Coyoacán, México Samarjit Chakraborty, München, Germany Jiming Chen, Hangzhou, P.R. China Tan Kay Chen, Singapore, Singapore Rüdiger Dillmann, Karlsruhe, Germany Gianluigi Ferrari, Parma, Italy Manuel Ferre, Madrid, Spain Sandra Hirche, München, Germany Faryar Jabbari, Irvine, USA Janusz Kacprzyk, Warsaw, Poland Alaa Khamis, New Cairo City, Egypt Torsten Kroeger, Stanford, USA Tan Cher Ming, Singapore, Singapore Wolfgang Minker, Ulm, Germany Pradeep Misra, Dayton, USA Sebastian Möller, Berlin, Germany Subhas Mukhopadyay, Palmerston, New Zealand Cun-Zheng Ning, Tempe, USA Toyoaki Nishida, Sakyo-ku, Japan Federica Pascucci, Roma, Italy Tariq Samad, Minneapolis, USA Gan Woon Seng, Nanyang Avenue, Singapore Germano Veiga, Porto, Portugal Junjie James Zhang, Charlotte, USA

For further volumes: http://www.springer.com/series/7818

#### About this Series

"Lecture Notes in Electrical Engineering (LNEE)" is a book series which reports the latest research and developments in Electrical Engineering, namely:

- Communication, Networks, and Information Theory

- Computer Engineering

- Signal, Image, Speech and Information Processing

- Circuits and Systems

- Bioengineering

LNEE publishes authored monographs and contributed volumes which present cutting edge research information as well as new perspectives on classical fields, while maintaining Springer's high standards of academic excellence. Also considered for publication are lecture materials, proceedings, and other related materials of exceptionally high quality and interest. The subject matter should be original and timely, reporting the latest research and developments in all areas of electrical engineering.

The audience for the books in LNEE consists of advanced level students, researchers, and industry professionals working at the forefront of their fields. Much like Springer's other Lecture Notes series, LNEE will be distributed through Springer's print and electronic publishing channels.

Valery Sklyarov · Iouliia Skliarova Alexander Barkalov · Larysa Titarenko

# Synthesis and Optimization of FPGA-Based Systems

Valery Sklyarov Iouliia Skliarova Department of Electronics, Telecommunications and Informatics University of Aveiro Aveiro Portugal Alexander Barkalov Larysa Titarenko Institute of Informatics and Electronics University of Zielona Góra Zielona Góra Poland

ISSN 1876-1100 ISSN 1876-1119 (electronic) ISBN 978-3-319-04707-2 ISBN 978-3-319-04708-9 (eBook) DOI 10.1007/978-3-319-04708-9 Springer Cham Heidelberg New York Dordrecht London

Library of Congress Control Number: 2013958443

© Springer International Publishing Switzerland 2014

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed. Exempted from this legal reservation are brief excerpts in connection with reviews or scholarly analysis or material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work. Duplication of this publication or parts thereof is permitted only under the provisions of the Copyright Law of the Publisher's location, in its current version, and permission for use must always be obtained from Springer. Permissions for use may be obtained through RightsLink at the Copyright Clearance Center. Violations are liable to prosecution under the respective Copyright Law.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

While the advice and information in this book are believed to be true and accurate at the date of publication, neither the authors nor the editors nor the publisher can accept any legal responsibility for any errors or omissions that may be made. The publisher makes no warranty, express or implied, with respect to the material contained herein.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

## Preface

Field-Programmable Gate Arrays (FPGAs) were invented by Xilinx in 1985, i.e., less than 30 years ago. The influence of FPGAs on many directions in engineering is growing continuously and rapidly. There are many reasons for such progress and the most important are the inherent configurability of FPGAs and their relatively cheap development cost. Forecasts suggest that the impact of FPGAs will continue to grow and the range of applications will increase considerably in the future. Recent field-configurable microchips incorporate multicore processors and reconfigurable logic appended with a number of frequently used devices such as digital signal processing slices and block memories. FPGA-based systems can be synthesized and implemented in general-purpose computers using integrated design environments. Experiments and explorations of such systems are commonly based on prototyping boards linked to the same environment.

It is widely known and proven that FPGAs can be applied efficiently in a vast variety of engineering applications. One reason for this is that growing system complexity makes it very difficult to ship designs without errors. Hence, it is essential to be able to fix errors after fabrication, which can be done significantly easier with customizable devices.

The complexity of contemporary chips is increasing exponentially with time and the number of available transistors grows faster than the ability to design meaningfully with them. This situation is a well-known design productivity gap, which is increasing continuously. Therefore, design productivity will be the real challenge for future systems. Although in unit production volumes and revenue, Application-Specific Integrated Circuits (ASICs) and Application-Specific Standard Products (ASSPs) surpass FPGAs, forecasts of FPGA design start numbers are currently ahead of ASIC/ASSP design starts. Thus, the high involvement of FPGAs in new designs of circuits and systems and the need for better design productivity undoubtedly require huge engineering resources, which are the major output of technical universities, and this book is intended to provide assistance for the relevant courses.

FPGAs still operate at lower clock frequencies than general-purpose computers and ASICs. The cost of the most advanced devices is high. Cheaper microchips operate at clock frequencies that are lower than in inexpensive computers that are widely used. One of the most important applications of FPGAs is improving the performance of implemented systems. To achieve acceleration with devices that are generally slower, parallelism needs to be applied extensively.

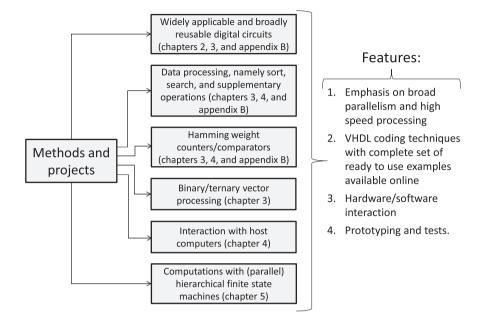

The book pursues two main objectives and is composed of two parts. The **first part** with appendices A and B (written by Valery Sklyarov and Iouliia Skliarova) introduces the concepts of the design of digital systems using contemporary Field-Programmable Gate Arrays and presents the recent results of the authors in FPGA-based high-performance accelerators. This part is composed of five chapters with the main objective of extending topics that are traditionally included within digital systems in a way that enables FPGA-based design to be discussed, illustrated by examples, and supported by experiments with relatively cheap prototyping boards that are widely available. The **second part** of the book (written by Alexander Barkalov and Larisa Titarenko) includes four chapters and covers more theoretical aspects of finite state machines (FSMs) with the main objective of reducing FPGA basic resources (slices or look-up tables), minimizing delays in the circuits, and achieving greater optimization of fundamental components in FPGAs.

The following features set the book apart from others in the field:

- It provides easily understandable introductory sections (appropriate even for the first-year students in the area) that are gradually extended to more advanced topics covering the novel techniques that are proposed and disseminated by the authors and demonstrated in numerous examples from practical applications.

- 2. Fully synthesizable hardware-description language specifications (VHDL, in particular) for the majority of the circuits and systems described are presented ready to be tested and incorporated in practical engineering designs, which is indispensable for both undergraduate and postgraduate university students.

- 3. A number of practical designs based on the proposed models and methods for complete applications are discussed from areas such as data processing, combinatorial search, and computations relying on the model of a hierarchical finite state machine.

- 4. Exploring models and methods that involve not only core reconfigurable logical elements but also a number of embedded blocks (e.g., memories and digital signal processing slices) and template-based circuits.

The book provides the following additional features:

- The design examples have been tested in three prototyping boards with Xilinx and Altera FPGAs. The latest Nexys-4 board from Digilent with the recent Artix-7 FPGA from the Xilinx 7 series and the well-known Digilent Atlys board with the Xilinx Spartan-6 FPGA were used for the majority of the examples. Many projects were also tested in the DE2-115 board with the Altera Cyclon-IVe FPGA that was developed especially for education and is popular in university courses.

- 2. All the VHDL examples from the book are available online at http://sweet.ua. pt/skl/Springer2014.html. The website also provides the latest updated projects. These projects can be downloaded and tested and evaluated immediately. Each example includes a brief description, the VHDL code, a user constraints file, and a bitstream for the selected FPGA.

The chapters in the book contain the following material:

Chapter 1 introduces FPGA architectures by presenting the general structure of modern devices and explaining the core elements and the most important embedded blocks, such as memory and digital signal processing slices. A few typical FPGA-based design scenarios are discussed that cover the phases of specification, supplying physical constraints, implementation, configuration, and finally, testing. In this introductory chapter, design specifications are presented at the schematic level, where a circuit is constructed either from components available in vendor-specific libraries, user-defined blocks, or from properly customized intellectual property cores. A number of simple examples are given that are ready to be tested in FPGA-based prototyping boards. The three prototyping boards used in the book are characterized briefly and the general ideas for interaction with circuits and systems implemented in FPGAs are introduced. All the processing steps are explained through numerous examples.

Chapter 2 presents a concise introduction to synthesizable VHDL that is sufficient for the design methods and examples given in subsequent chapters to be understood without much background knowledge. The main objective of this chapter is to explain the basis of VHDL modules and their specification capabilities without going into detail. There are many excellent books dedicated to VHDL that may be used to complement this book. Our primary target is the synthesis and optimization of FPGA-based circuits and systems and VHDL is just an instrument that is used in the book to describe the desired functionalities and structures. Thus this chapter only provides the minimum necessary to allow subsequent chapters to be read without additional material, and to enable all the proposed examples to be understood and tested with the FPGA-based prototyping boards.

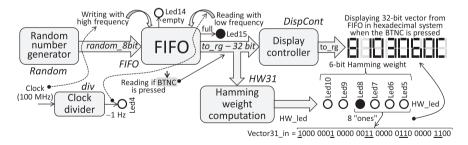

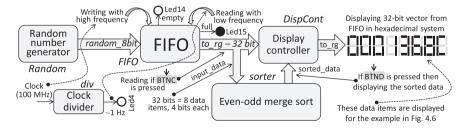

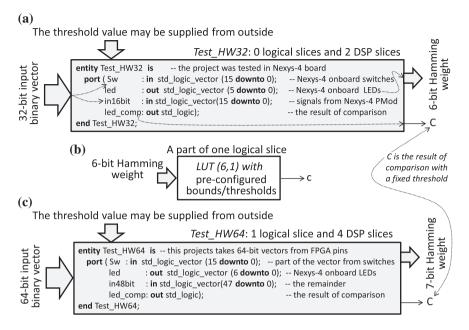

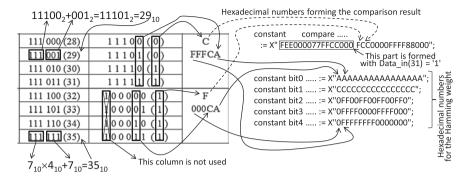

Chapter 3 begins with a brief description of widely used simple combinational and sequential circuits. Many examples are given with implementations of the circuits in FPGAs. Next, various optimization techniques are discussed with special emphasis on broad parallelism, which is very important for FPGA-based applications. More complicated digital circuits and systems are introduced, such as parallel networks for sorting and searching, hamming weight counters/comparators, concurrent vector processing units, and advanced finite state machines. The circuits are designed so that operations over multiple data items can be executed concurrently. Network-based solutions, such as sorting and counting networks in particular, and the efficient mapping of circuits to FPGA primitives (look-up tables) are examples. A number of alternative competing methods are discussed and evaluated. All the circuits and systems are described in VHDL, implemented and tested in FPGAs, and finally evaluated by applying various criteria. Many of the novel solutions proposed are parameterized, which permits very complex projects to be developed in FPGAs for solving advanced problems in several areas, such as data processing and combinatorial search.

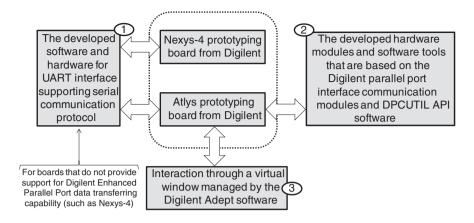

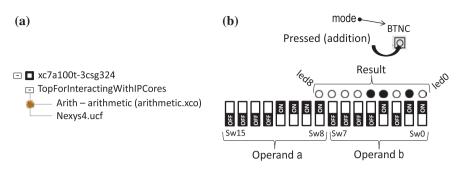

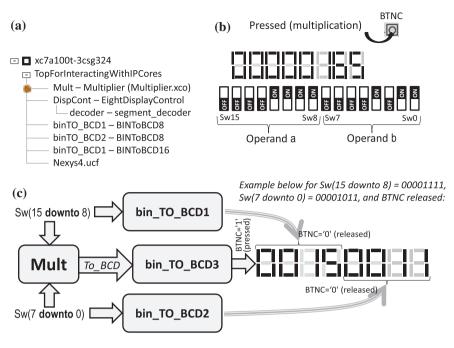

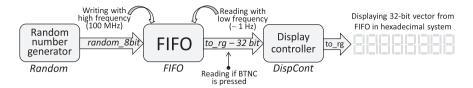

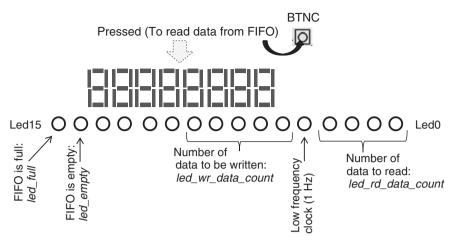

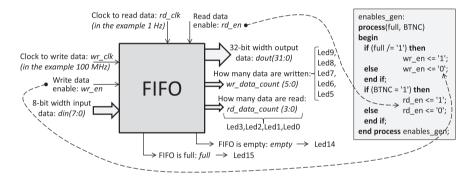

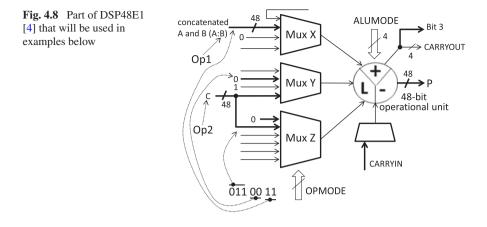

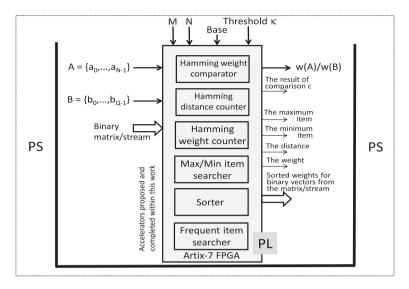

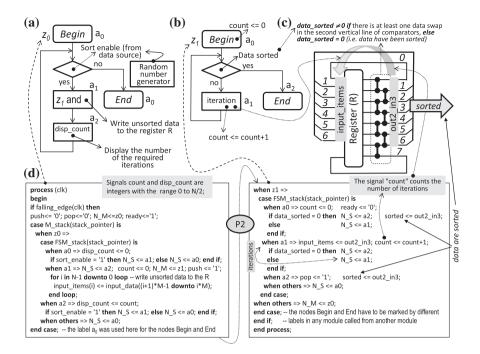

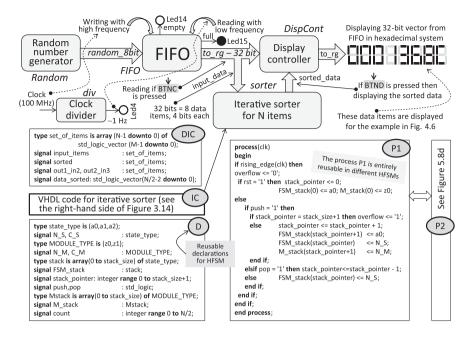

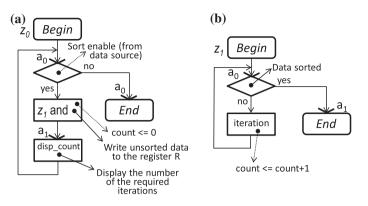

Chapter 4 begins with examples that demonstrate how commercially available intellectual property cores can be embedded in different designs. In particular, arithmetical circuits constructed from digital signal processing slices, and parameterized memory blocks that provide support for data buffering (such as FIFO—first input first output), are described. More details on digital signal processing slices are then given and it is shown how these may be used efficiently in practical circuits such as hamming weight counters/comparators. The major part of this chapter is dedicated to interactions between a host computer and FPGAbased prototyping boards through the Digilent enhanced parallel port and the UART (Universal Asynchronous Receiver and Transmitter) interfaces. Complete details of the communication modules are described, including both software for general-purpose computers that was developed in the C++ language, and hardware for FPGAs. The next section makes use of the designed modules for projects that involve such interactions for different purposes. A more complicated design for a network-based iterative data sorter from Chap. 3 is implemented and tested in this way as a complete fully functioning example. The chapter concludes with a brief description of programmable systems-on-chip (PSoC) that combine an embedded processing system with a reconfigurable logic, which can lead to more efficient implementations of the applications. Proposals for mapping the designs from Chap. 3 to the PSoC are given and discussed.

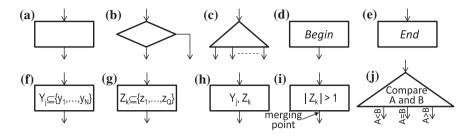

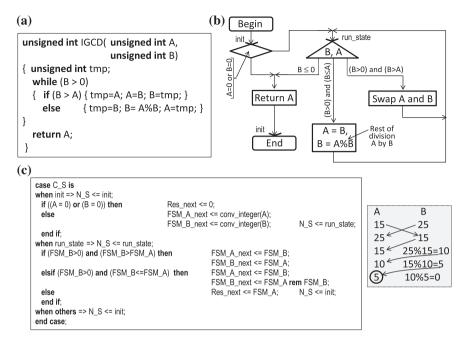

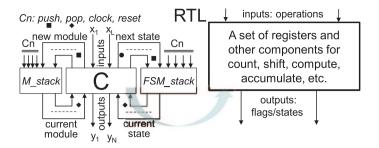

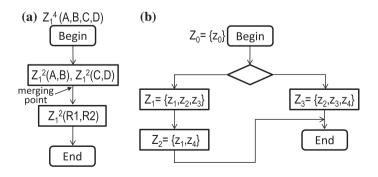

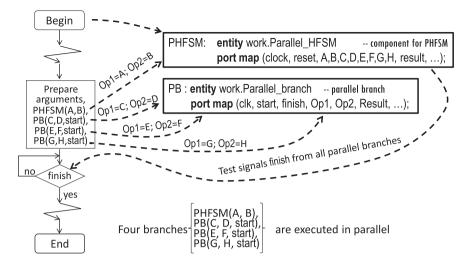

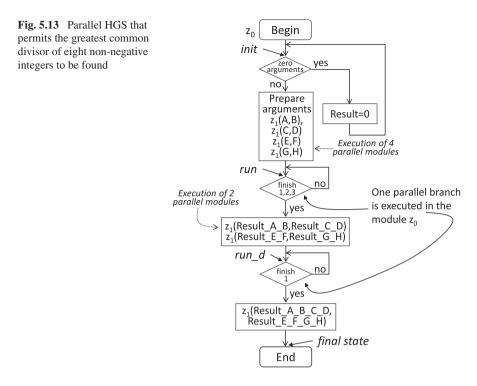

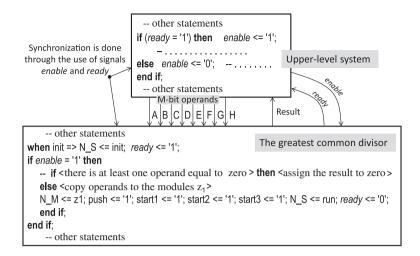

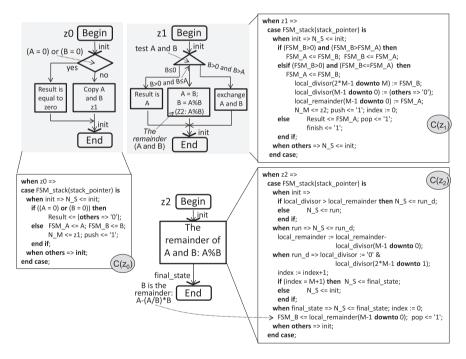

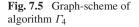

Chapter 5 gives an overview of the design techniques based on hierarchical and parallel specifications. First, hierarchical graph-schemes (HGSs) are introduced that enable complex digital control algorithms to be decomposed and described efficiently. A module, described by an HGS, is the fundamental entity that provides the basis for the technique, and is an autonomous, complete, and potentially reusable component. A module has to be designed such that: (1) it can be verified independently of other modules; (2) it possesses a well-defined external interface so it can be reused in different specifications. It is shown that a set of HGSs (modules) can be implemented in a hierarchical finite state machine (HFSM) with a stack memory. Many VHDL examples are given that demonstrate that HFSMs permit the execution of hierarchical algorithms and provide support for recursion if required. Various types of HFSMs are described and synthesizable VHDL templates for these are given that can be customized for particular problems. Parallel specifications and parallel HFSMs are also discussed. Many fully functioning VHDL examples for all the types of HFSMs above are presented and evaluated. It is also shown how software programs can be mapped to hardware with the aid of HFSM models. Finally, a variety of HFSM optimization techniques are proposed.

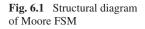

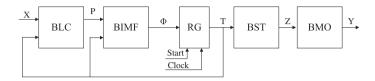

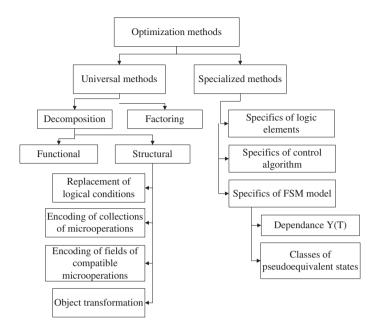

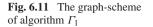

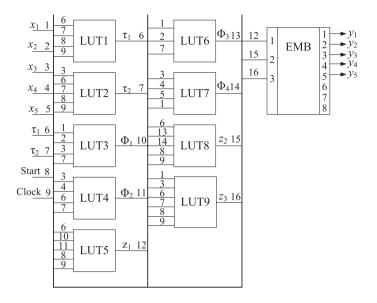

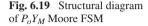

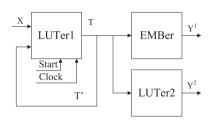

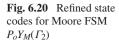

Chapter 6 is devoted to the problems of optimization of Moore FSM's logic circuits implemented with FPGAs. The general characteristic is given for methods of functional and structural decomposition. Distinctive features of FPGA are analyzed allowing the number of look-up table (LUT) elements in logic circuits of Moore FSMs to be decreased. The classification of optimization methods are given for Moore FSM including: (1) the transformation of state codes into codes of the classes of pseudo-equivalent states (PES); (2) presentation of state codes as concatenations of codes of PES and collections of microoperations; (3) replacement of logical conditions (input variables of FSM) with additional variables. All discussed methods are illustrated by examples.

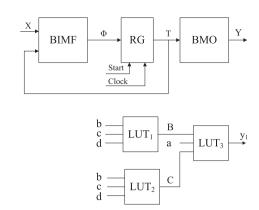

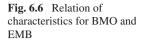

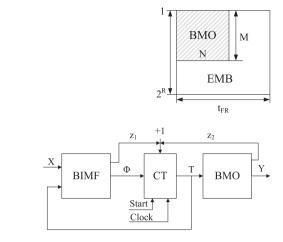

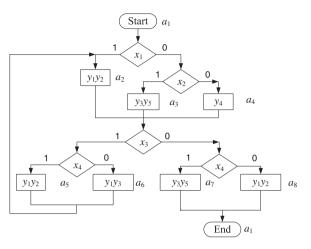

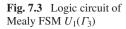

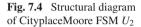

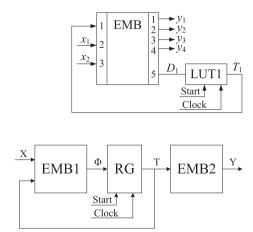

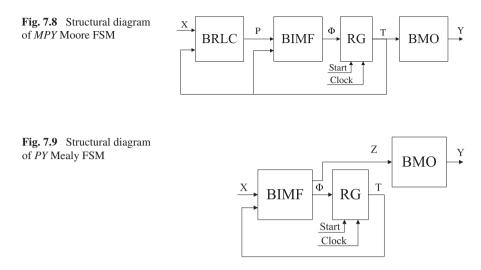

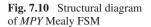

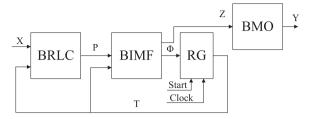

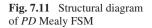

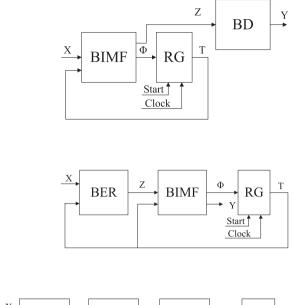

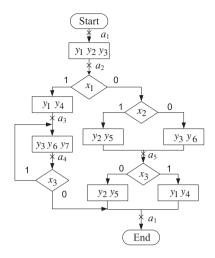

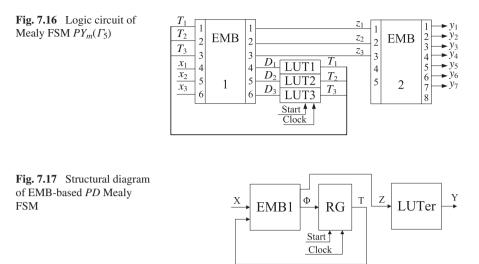

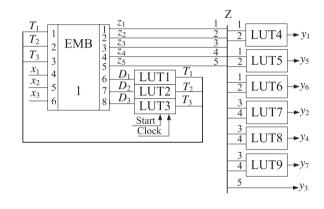

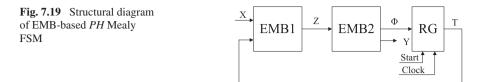

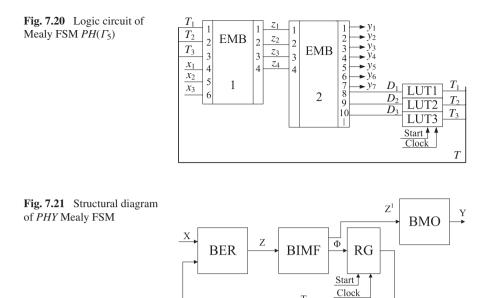

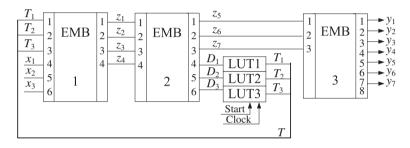

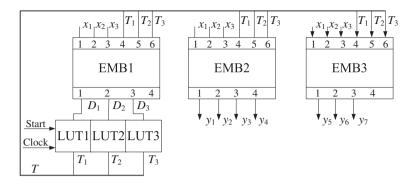

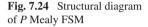

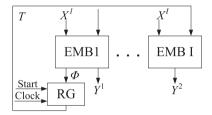

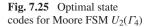

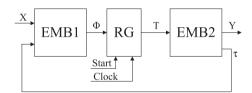

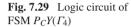

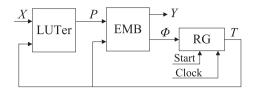

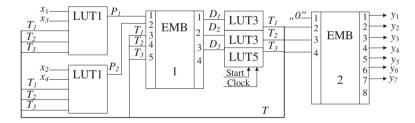

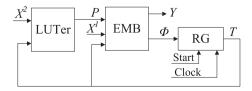

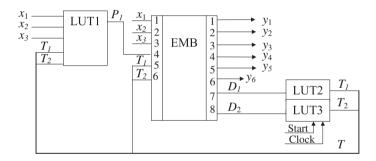

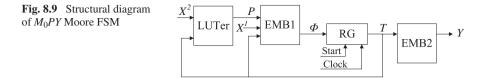

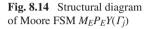

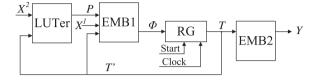

Chapter 7 deals with design of Moore FSMs based on using embedded memory blocks (EMB). The methods of trivial EMB-based implementation of logic circuits

of both Moore and Mealy FSMs are discussed. In this case, only one EMB is enough for implementing the circuit. Next, the optimization methods are discussed based on replacement of logical conditions as well as encoding of the collections of microoperations. The considered methods are based on encoding the rows of FSM's structure table. All these methods lead to two-level models of Mealy FSMs and to three-level models of Moore FSMs. Next, these methods are combined together for further optimization of hardware in FSM logic circuits. The last section considers applying PES-based methods in EMB-based Moore FSMs. All discussed methods are illustrated by examples.

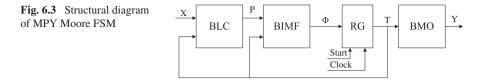

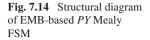

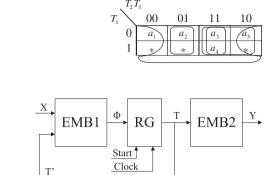

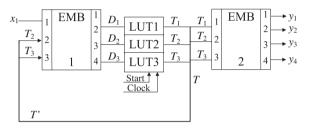

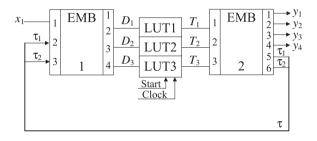

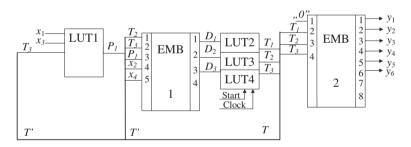

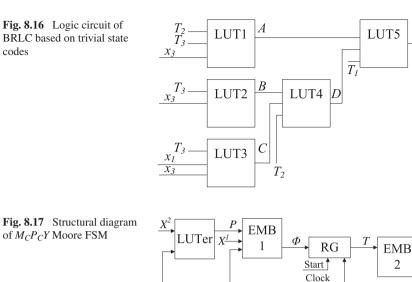

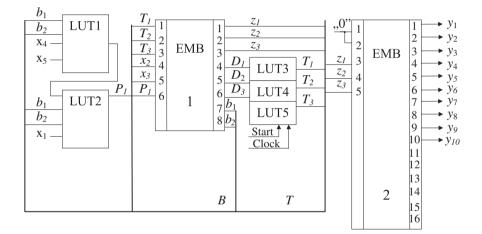

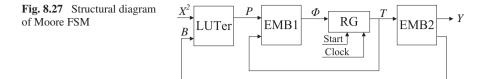

Chapter 8 is devoted to optimization of logic circuits of EMB-based FSMs. First of all, the design methods based on the replacement of logical conditions are discussed for both Moore and Mealy FSMs. Next, the proposed optimization methods are presented. These methods are based on splitting the set of logical conditions. This approach allows decreasing the number of LUTs in the circuit of the block of replacement of logical conditions. In the case of Moore FSM, the optimization methods are based on optimal state assignment, as well as the transformation of state codes into codes of the classes of PES. All discussed methods are illustrated by examples.

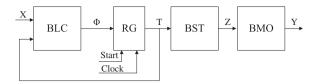

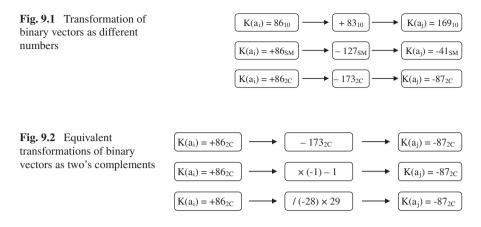

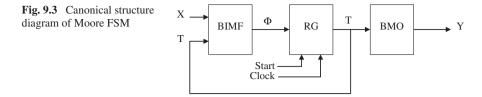

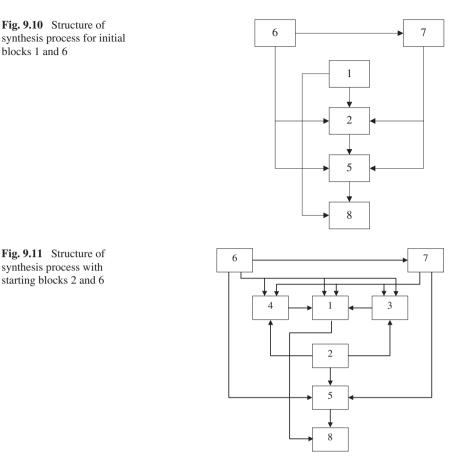

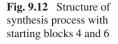

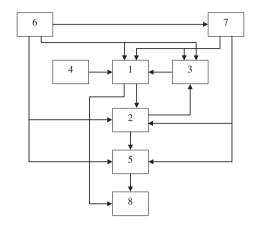

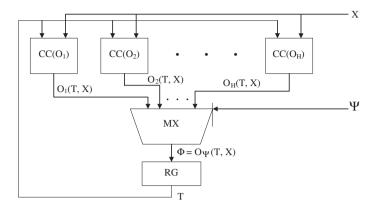

Chapter 9 is devoted to using the datapath for decreasing the number of LUTs in logic circuits of FPGA-based Moore FSMs. Firstly, the principle of operational implementation of interstate transitions is proposed. It is based on the usage of operational elements (adders, counters, shifters, and so on) for calculating codes the states of transitions. Next, the organization of FSM with operational implementation of interstate transitions is discussed. An example is given for application of the proposed method. Next, the base structure of synthesis process is proposed for Moore FSM with operational implementation of interstate transitions. The structure of the synthesis process depends on initial conditions such as set of operational automaton executing the transitions. Next, the method is shown based on mixture of traditional and proposed approaches for calculation of the codes of states of transitions. The last part of the chapter discusses the efficiency of the proposed solutions.

Appendix A contains a short description used in the book synthesizable VHDL constructions and reserved words in alphabetical order with examples.

Appendix B offers a number of synthesizable VHDL specifications that provide support for many projects in the part I of the book. All the examples are presented so that they can be tried out and examined directly.

The book can be used as supporting material for university courses that involve FPGA-based design, such as "Digital design," "Computer architecture," "Electronics," "Embedded systems," "Reconfigurable computing," "Communications," and "FPGA-based systems." It will also be helpful in engineering practice and research activity in areas where FPGA-based circuits and systems are planned to be designed and investigated. It is important to note that the presented fully functioning VHDL projects (that are also available online at http://sweet.ua.pt/skl/Springer2014.html) can be used directly in many research and engineering applications.

## Contents

## Part I Design of Digital Circuits and Systems on the Basis of FPGA

| 1 | FPC  | A Architectures, Reconfigurable Fabric, Embedded Blocks |    |

|---|------|---------------------------------------------------------|----|

|   | and  | Design Tools                                            | 3  |

|   | 1.1  | Introduction to FPGA                                    | 3  |

|   | 1.2  | The Basis of FPGA Devices.                              | 8  |

|   |      | 1.2.1 Configurable Logic Blocks of Xilinx FPGAs         | 8  |

|   |      | 1.2.2 Logic Elements of Altera FPGAs                    | 12 |

|   | 1.3  | Embedded Blocks                                         | 13 |

|   |      | 1.3.1 Embedded Memories                                 | 13 |

|   |      | 1.3.2 Embedded DSP Slices                               | 17 |

|   | 1.4  | Clock Distributions and Resets                          | 20 |

|   | 1.5  | Design Tools                                            | 21 |

|   | 1.6  | Implementation and Prototyping                          | 27 |

|   | 1.7  | Interaction with FPGA-Based Circuits and Systems        | 34 |

|   | Refe | prences                                                 | 40 |

| 2 | Svn  | thesizable VHDL for FPGA-Based Devices                  | 43 |

| - | 2.1  | Introduction to VHDL                                    | 43 |

|   | 2.2  | Data Types, Objects and Operators                       | 50 |

|   | 2.3  | Combinational and Sequential Processes                  | 55 |

|   | 2.0  | 2.3.1 Combinational Processes                           | 56 |

|   |      | 2.3.2       Sequential Processes                        | 59 |

|   | 2.4  | Functions, Procedures, and Blocks.                      | 63 |

|   | 2.5  | Generics and Generates                                  | 70 |

|   | 2.6  | Libraries, Packages, and Files                          | 76 |

|   | 2.7  | Behavioral Simulation                                   | 81 |

|   | 2.8  | Prototyping                                             | 85 |

|   |      | prences                                                 | 88 |

| 3 | Desi | gn Tec                                | hniques                                                  | 89  |  |  |  |  |

|---|------|---------------------------------------|----------------------------------------------------------|-----|--|--|--|--|

|   | 3.1  | Comb                                  | inational Circuits                                       | 89  |  |  |  |  |

|   |      | 3.1.1                                 | Encoders                                                 | 92  |  |  |  |  |

|   |      | 3.1.2                                 | Decoders                                                 | 93  |  |  |  |  |

|   |      | 3.1.3                                 | Multiplexers                                             | 94  |  |  |  |  |

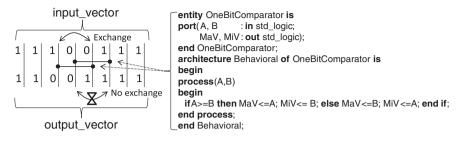

|   |      | 3.1.4                                 | Comparators                                              | 95  |  |  |  |  |

|   |      | 3.1.5                                 | Arithmetical Circuits                                    | 95  |  |  |  |  |

|   |      | 3.1.6                                 | Barrel Shifters.                                         | 96  |  |  |  |  |

|   | 3.2  | Seque                                 | ntial Circuits                                           | 97  |  |  |  |  |

|   |      | 3.2.1                                 | Registers                                                | 97  |  |  |  |  |

|   |      | 3.2.2                                 | Shift Registers                                          | 98  |  |  |  |  |

|   |      | 3.2.3                                 | •                                                        | 98  |  |  |  |  |

|   |      | 3.2.4                                 | Arithmetical Circuits with Accumulators                  | 99  |  |  |  |  |

|   | 3.3  | Finite                                | State Machines                                           | 100 |  |  |  |  |

|   | 3.4  |                                       | nization of FPGA-Based Circuits and Systems              | 104 |  |  |  |  |

|   |      | 3.4.1                                 | Highly Parallel Network-Based Solutions                  | 105 |  |  |  |  |

|   |      | 3.4.2                                 | Hardware Accelerators                                    | 110 |  |  |  |  |

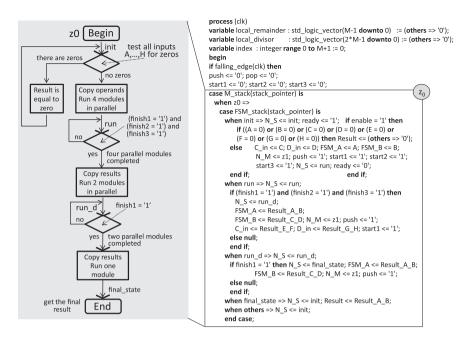

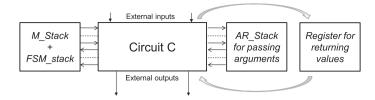

|   |      |                                       | Parallel Modular Algorithms Running                      |     |  |  |  |  |

|   |      |                                       | in Hierarchical FSMs                                     | 111 |  |  |  |  |

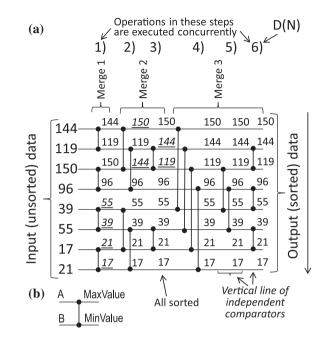

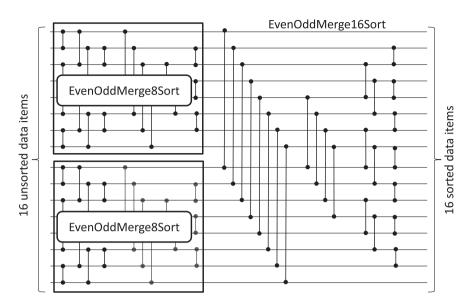

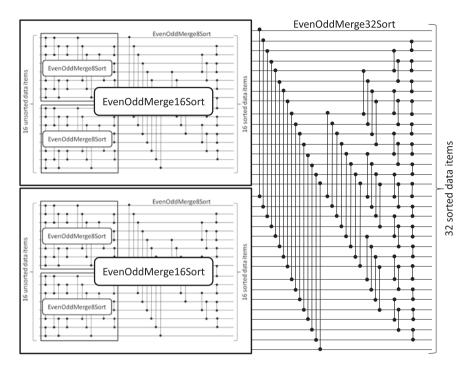

|   | 3.5  | Design                                | n Examples for Parallel Sort                             | 112 |  |  |  |  |

|   | 3.6  |                                       | n Examples for Parallel Search                           | 118 |  |  |  |  |

|   | 3.7  | Design Examples for Parallel Counters |                                                          |     |  |  |  |  |

|   | 3.8  | Design Examples for Counting Networks |                                                          |     |  |  |  |  |

|   | 3.9  |                                       | n Examples for LUT-Based Hamming Weight                  |     |  |  |  |  |

|   |      | -                                     | ers/Comparators                                          | 130 |  |  |  |  |

|   | 3.10 |                                       | gn Examples for Operations Over Vectors                  | 137 |  |  |  |  |

|   | Refe | rences                                |                                                          | 141 |  |  |  |  |

|   |      |                                       |                                                          |     |  |  |  |  |

| 4 | Emb  | oedded                                | Blocks and System-Level Design                           | 143 |  |  |  |  |

|   | 4.1  | Using                                 | IP Cores                                                 | 143 |  |  |  |  |

|   | 4.2  | Design                                | n with Embedded DSP Slices                               | 153 |  |  |  |  |

|   | 4.3  | Intera                                | ction with FPGA                                          | 158 |  |  |  |  |

|   |      | 4.3.1                                 | Digilent Parallel Port Interface                         | 159 |  |  |  |  |

|   |      | 4.3.2                                 | UART Interface                                           | 167 |  |  |  |  |

|   | 4.4  | Softw                                 | are/Hardware Co-design and Co-simulation                 | 179 |  |  |  |  |

|   |      | 4.4.1                                 | Software-Hardware Co-design with Digilent                |     |  |  |  |  |

|   |      |                                       | Parallel Port Interface                                  | 181 |  |  |  |  |

|   |      | 4.4.2                                 | Software-Hardware Co-design with UART Interface          | 188 |  |  |  |  |

|   | 4.5  | Progra                                | ammable Systems-on-Chip                                  | 197 |  |  |  |  |

|   | Refe | -                                     | · · · · · · · · · · · · · · · · · · ·                    | 202 |  |  |  |  |

|   |      |                                       |                                                          |     |  |  |  |  |

| 5 | Desi | gn Tecl                               | hnique Based on Hierarchical and Parallel Specifications | 205 |  |  |  |  |

|   | 5.1  |                                       | lar Hierarchical Specifications                          | 205 |  |  |  |  |

|   | 5.2  | Hierar                                | rchical Finite State Machines                            | 210 |  |  |  |  |

|   |      | 5.2.1                                 | HDL Template for HFSM with Explicit Modules              | 211 |  |  |  |  |

|   |      |                                       |                                                          |     |  |  |  |  |

|    |       | 5.2.2 HDL Template for HFSM with Implicit Modules      | 220 |

|----|-------|--------------------------------------------------------|-----|

|    | 5.3   | Synthesis of HFSMs                                     | 221 |

|    |       | 5.3.1 Synthesis of HFSMs with Explicit Modules         | 222 |

|    |       | 5.3.2 Synthesis of HFSMs with Implicit Modules         | 229 |

|    | 5.4   | Parallel Specifications and Parallel HFSMs             | 230 |

|    | 5.5   | Hardware Implementations of Software Programs          |     |

|    |       | Based on HFSM Models                                   | 239 |

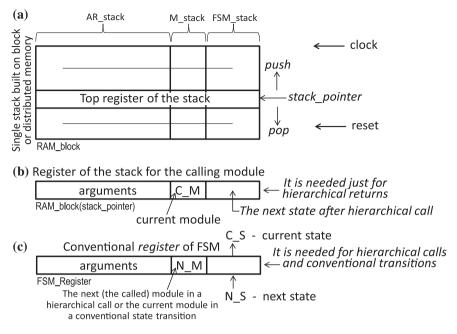

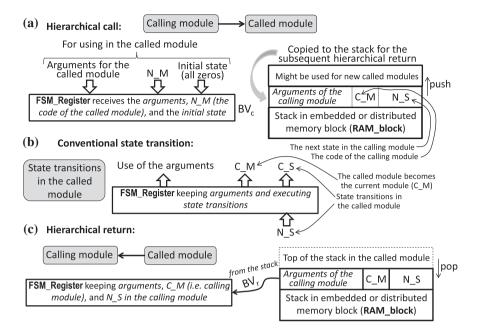

|    | 5.6   | Using Stacks Based on Embedded or Distributed Memories | 242 |

|    | 5.7   | Optimization Techniques                                | 245 |

|    | 017   | 5.7.1 Execution of Hierarchical Returns                | 245 |

|    |       | 5.7.2 Providing Multiple Entry Points to HGSs          | 246 |

|    |       | 5.7.3 Fast Stack Unwinding                             | 247 |

|    | 5.8   | Practical Applications.                                | 247 |

|    |       | rences                                                 | 254 |

|    | Kere  |                                                        | 234 |

| Pa | rt II | Methods for Optimization of Finite State Machines      |     |

|    |       | for FPGA-Based Circuits and Systems                    |     |

| 6  | Har   | dware Reduction in Logic Circuits of Moore FSM         | 259 |

|    | 6.1   | General Characteristic of Existing Methods             | 259 |

|    | 6.2   | Object Transformation in Moore FSM.                    | 266 |

|    | 6.3   | Expansion of State Codes for Moore FSM                 | 271 |

|    | 6.4   | Synthesis of Moore FSM with Replacement of             |     |

|    |       | Logical Conditions                                     | 279 |

|    | Refe  | rences                                                 | 283 |

| 7  | Desi  | gn of FSMs with Embedded Memory Blocks                 | 285 |

|    | 7.1   | Trivial Implementation of Mealy and Moore FSMs         | 285 |

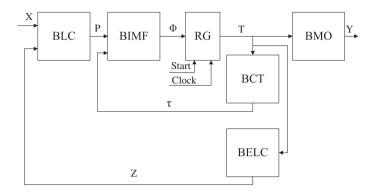

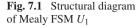

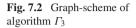

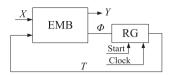

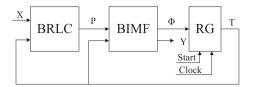

|    | 7.2   | Structural Decomposition of FSMs                       | 200 |

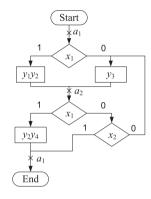

|    | 7.3   | Design of Mealy FSM with Encoding of the               | 271 |

|    | 1.5   | Collections of Microoperations                         | 295 |

|    | 7.4   | Design of Mealy FSM with Encoding of the               | 2)5 |

|    | 7.7   | Fields of Compatible Microoperations.                  | 298 |

|    | 7.5   | Design of Mealy FSM with Encoding of the Rows          | 290 |

|    | 1.5   | of Structure Table                                     | 300 |

|    | 7.6   | Optimization of BIMF Based on Pseudoequivalent         | 500 |

|    | 7.0   | States of Moore FSM                                    | 305 |

|    | Dafa  |                                                        |     |

|    | Kele  | rences                                                 | 310 |

| 8  | -     | imization of FSMs with Embedded Memory Blocks          | 313 |

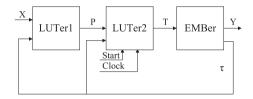

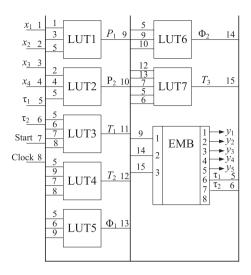

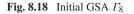

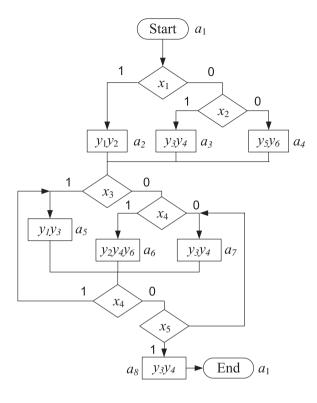

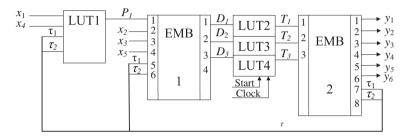

|    | 8.1   | Trivial Implementation of MP Mealy FSMs                | 313 |

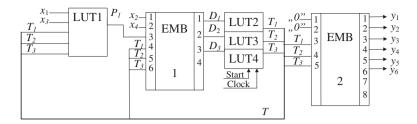

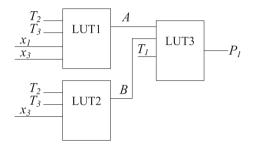

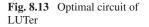

|    | 8.2   | Optimization of LUTer.                                 | 321 |

|    | 8.3   | Optimization of LUTer Based on Pseudoequivalent States | 325 |

|    | 8.4   | Optimization of LUTer Based on Encoding of             |     |

|    |       | Collections of Microoperations                         | 334 |

|    | Refe  | rences                                                 | 341 |

| 9                         | Fini  | te State Machines with Operational Implementation                 |     |  |  |  |  |

|---------------------------|-------|-------------------------------------------------------------------|-----|--|--|--|--|

|                           | of T  | ransitions                                                        | 343 |  |  |  |  |

|                           | 9.1   | Conception of Operational Implementation of Transitions           | 343 |  |  |  |  |

|                           | 9.2   | Organisation of FSM with Operational Generation of Transitions    | 346 |  |  |  |  |

| 9.3 Example of FSM Design |       |                                                                   |     |  |  |  |  |

|                           | 9.4   | Structural Representation of Synthesis Process for FSM with OAT . | 353 |  |  |  |  |

|                           |       | 9.4.1 Base Structure of Synthesis Process for FSM with OAT        | 354 |  |  |  |  |

|                           |       | 9.4.2 Refinement of Basic Structure of Synthesis Process          | 355 |  |  |  |  |

|                           | 9.5   | Organization of Operational Automaton of Transitions              | 359 |  |  |  |  |

|                           |       | 9.5.1 Typical Structure Models of Operational Automata            | 359 |  |  |  |  |

|                           |       | 9.5.2 Organizational Specifics of OAT                             | 360 |  |  |  |  |

|                           |       | 9.5.3 Organization of Combinational Part of OAT                   | 360 |  |  |  |  |

|                           | 9.6   | Synthesis Method for FSM with Supplemented Set of                 |     |  |  |  |  |

|                           |       | Operations of Transitions                                         | 363 |  |  |  |  |

|                           | 9.7   | Investigation of Efficiency of FSM with OAT                       | 367 |  |  |  |  |

|                           | Refe  | erences                                                           | 373 |  |  |  |  |

| Aj                        | opend | lix A: VHDL Constructions Used in the Book and                    |     |  |  |  |  |

|                           |       | Additional Support Materials                                      | 375 |  |  |  |  |

| Aj                        | opend | lix B: Coding Examples                                            | 403 |  |  |  |  |

| In                        | dex.  |                                                                   | 429 |  |  |  |  |

|                           |       |                                                                   |     |  |  |  |  |

# Abbreviations

| ACP   | Accelerator Coherency Port                         |

|-------|----------------------------------------------------|

| ALM   | Adaptive Logic Modules                             |

| API   | Application Programming Interface                  |

| APSoC | All Programmable System-on-Chip                    |

| ARM   | Advanced RISC Machine                              |

| ASCII | American Standard Code for Information Interchange |

| ASIC  | Application-Specific Integrated Circuit            |

| ASMBL | Advanced Silicon Modular Block                     |

| ASSP  | Application-Specific Standard Product              |

| AXI   | Advanced eXtensible Interface                      |

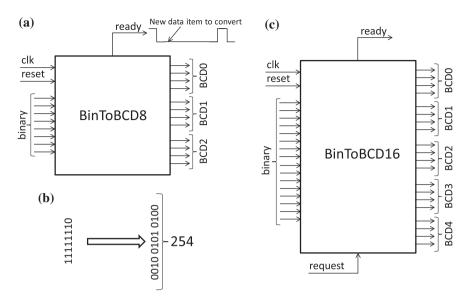

| BCD   | Binary-Coded Decimal                               |

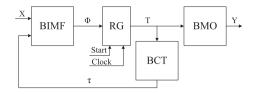

| BCT   | Block of Code Transformer                          |

| BIMF  | Block of Input Memory Functions                    |

| BMO   | Block of MicroOperations                           |

| BOT   | Block of Operations of Transitions                 |

| BRLC  | Block of Replacement of Logical Conditions         |

| BST   | Block of State Transformer                         |

| BV    | Binary Vector                                      |

| CAD   | Computer-Aided Design                              |

| CC    | Combinational Circuit                              |

| CLB   | Configurable Logic Block                           |

| СМО   | Collection of Microoperations                      |

| CMT   | Clock Management Tiles                             |

| CN    | Carry Network                                      |

| CNB   | Carry Network Block                                |

| CPLD  | Complex Programmable Logic Device                  |

| CT    | Counter                                            |

| DCM   | Digital Clock Manager                              |

| DDR   | Double Data Rate                                   |

| DSP   | Digital Signal Processing                          |

| EG    | Equivalent Gate                                    |

| EMB   | Embedded Memory Block                              |

| EMBer | Logic Circuit Consisting of EMBs                   |

|       |                                                    |

| EDD   |                                      |

|-------|--------------------------------------|

| EPP   | Enhanced Parallel Port               |

| FA    | Full Adder                           |

| FIFO  | First Input First Output             |

| FPGA  | Field-Programmable Gate Array        |

| FPLD  | Field-Programmable Logic Device      |

| FSM   | Finite State Machine                 |

| FSMD  | Finite State Machine with Data path  |

| GFT   | General Formula of Transitions       |

| GPI   | General-Purpose Interface            |

| GSA   | Graph-Scheme of Algorithm            |

| HA    | Half Adder                           |

| HDL   | Hardware Description Language        |

| HDMI  | High-Definition Multimedia Interface |

| HFSM  | Hierarchical Finite State Machine    |

| HGS   | Hierarchical Graph-Scheme            |

| HID   | Human Interface Device               |

| HW    | Hamming Weight                       |

| HWC   | Hamming Weight Comparator            |

| IGCD  | Iterative Greatest Common Divisor    |

| IP    | Intellectual Property                |

| ISE   | Integrated Software Environment      |

| JTAG  | Joint Test Action Group              |

| LAB   | Logic Array Block                    |

| LC    | Logical Condition                    |

| LCC   | Linear Chain of Classes of PES       |

| LCS   | Linear Chain of States               |

| LE    | Logic Element                        |

| LED   | Light Emitting Diode                 |

| LSB   | Least Significant Bit                |

| LUT   | Look-Up Table                        |

| LUTer | Logic Circuit Consisting of LUTs     |

| MI    | Microinstruction                     |

| MLAB  | Memory Logic Array Block             |

| MMCM  | Mixed-Mode Clock Manager             |

| МО    | Microoperation                       |

| MSB   | Most Significant Bit                 |

| OA    | Operational Automaton                |

| OAT   | Operational Automaton of Transitions |

| OLC   | Operational Linear Chain             |

| OP    | Operational Part                     |

| PAL   | Programmable Array Logic             |

| PB    | Parallel Branch                      |

| PC    | Personal Computer                    |

| PEO   | Pseudoequivalent Outputs             |

|       |                                      |

| PES   | Pseudoequivalent States                     |

|-------|---------------------------------------------|

| PHFSM | Parallel Hierarchical Finite State Machine  |

| PL    | Programmable Logic                          |

| PLA   | Programmable Logic Arrays                   |

| PLD   | Programmable Logic Device                   |

| PLL   | Phase-Locked Loop                           |

| PLR   | PipeLine Register                           |

| Pmod  | Peripheral Module                           |

| PROM  | Programmable Read-Only Memory               |

| PS    | Processing System                           |

| PSoC  | Programmable Systems-on-Chip                |

| RAM   | Random-Access Memory                        |

| RG    | Register                                    |

| RGCD  | Recursive Greatest Common Divisor           |

| RISC  | Reduced Instruction Set Computer            |

| ROM   | Read-Only Memory                            |

| RTL   | Register-Transfer Level                     |

| SBF   | System of Boolean Functions                 |

| SDC   | Sequential Digital Circuit                  |

| SDK   | Software Development Kit                    |

| SIMD  | Single Instruction Multiple Data            |

| SHWC  | Simplest Hamming Weight Counter             |

| SOP   | Sum-Of-Products                             |

| SPI   | Serial Peripheral Interface                 |

| ST    | Structure Table                             |

| STT   | Synthesizable Table of Transitions          |

| UART  | Universal Asynchronous Receiver/Transmitter |

| UCF   | User Constraints File                       |

| USB   | Universal Serial Bus                        |

| VHDL  | VHSIC Hardware Description Language         |

| VHSIC | Very High Speed Integrated Circuits         |

| XDC   | Xilinx Design Constraints                   |

| XST   | Xilinx Synthesis Technology                 |

## Conventions

- 1. VHDL keywords are shown in **bold font**.

- 2. VHDL comments are shown in the following font: -- this is a comment.

- 3. The most important concepts are shown in *italic font*.

- 4. VHDL is not case sensitive language and thus UPPERCASE and lowercase letters may be used interchangeably.

- 5. Many examples in the book need libraries which are not explicitly shown and have to be included (see details in Sect. 2.6 and *library* in appendix A).

Xilinx<sup>®</sup>, Artix<sup>®</sup>, ISE<sup>®</sup>, LogiCore<sup>®</sup>, Spartan<sup>®</sup>, Virtex<sup>®</sup>, Vivado<sup>®</sup>, Zynq<sup>®</sup> are registered trademarks of Xilinx Inc. Chipscope, CORE Generator are trademarks of Xilinx Inc. Adept, Atlys, and Nexys-4 are trademarks of Digilent, Inc. Altera<sup>®</sup>, Stratix<sup>®</sup> and Cyclone<sup>®</sup> are registered trademarks of Altera Corp. Other product and company names mentioned may be trademarks of their respective owners.

The research results reported in this book were supported by the European Union through the European Regional Development Fund, FEDER through the Operational Program Competitiveness Factors—COMPETE, and National Funds through FCT—Foundation for Science and Technology in the context of the projects FCOMP-01-0124-FEDER-022682 (FCT reference PEst-C/EEI/UI0127/2011) and Incentivo/EEI/UI0127/2013.

# Part I Design of Digital Circuits and Systems on the Basis of FPGA

## Chapter 1 FPGA Architectures, Reconfigurable Fabric, Embedded Blocks and Design Tools

**Abstract** This chapter introduces FPGA architectures by presenting the general structure of modern devices and explaining the core elements and the most important embedded blocks, such as memory and digital signal processing slices. A few typical FPGA-based design scenarios are discussed that cover the phases of specification, supplying physical constraints, implementation, configuration and finally, testing. In this introductory chapter, design specifications are presented at the schematic level, where a circuit is constructed either from components available in vendor-specific libraries, user-defined blocks, or from properly customized intellectual property cores. A number of simple examples are given that are ready to be tested in FPGA-based prototyping boards. The three prototyping boards used in the book are characterized briefly and the general ideas for interaction with circuits and systems implemented in FPGAs are introduced. All the processing steps are explained through numerous examples.

## **1.1 Introduction to FPGA**

Field-Programmable Gate Arrays (FPGAs) were invented less than 30 years ago and their influence on different directions in engineering is growing continuously and extremely fast. There are many reasons for such progress and the most important of them is an inherent configurability and relatively cheap development cost.

In accordance with forecasts, the impact of FPGAs on different development directions will continue to grow and the number of such directions will be extended in future. When FPGAs were first proposed, they were predominantly used for implementing simple random and glue logic [1]. Nowadays, even undergraduate students are capable of constructing complex digital devices on the basis of FPGAs.

The world's first FPGA XC2064<sup>™</sup> was introduced and shipped in 1985 by Xilinx. It offered 800 gates (85,000 transistors, 128 logic cells, 64 Configurable

© Springer International Publishing Switzerland 2014

Logic Blocks—CLBs with two 3-input look-up tables, max clock frequency 50 MHz). The chip was sold for \$55 and produced on a 2.0  $\mu$  process [2]. Recent field-configurable micro-chips can be seen as a mixture of traditional gate arrays and ASIC (Application-Specific Integrated Circuit) components (such as ARM dual-core Cortex-A9) where the development of software and hardware can be done relatively independent of each other (e.g. *Zynq* all programmable system-on-chip [3]). FPGA complexity has reached 6.8 billion transistors [4], clock frequency exceeds gigahertz, and the most advanced technology is 20 nm [5] (14 and 10 nm processes are expected to be announced in 2014 [5]).

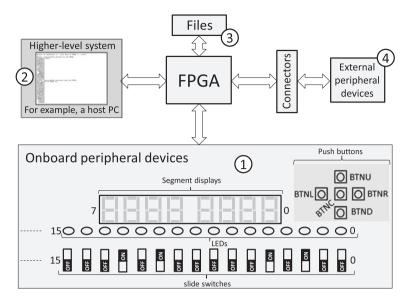

FPGA-targeted Computer-Aided Design (CAD) systems permit different specifications, tools, and components (such as hardware and system-level description languages, design templates, intellectual property (IP) cores, soft/hard build-in blocks) to be linked and combined within a single project. The relevant circuits can be synthesized, implemented, and tested in the same environment installed on a general-purpose computer with connected through standard interfaces (e.g. USB, PCI express, wireless) FPGA-based prototyping boards/systems.

Nowadays, the way to evolve higher performance systems from a generalpurpose computer, proposed more than 50 years ago [6], has been finally implemented in reality. Advances in FPGA technologies and architectures are clearly shown in [7]. From 1985 to 2013 FPGAs grew 100,000 times in capacity and became significantly faster. Two largest companies Altera and Xilinx continue to dominate on the market [8].

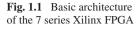

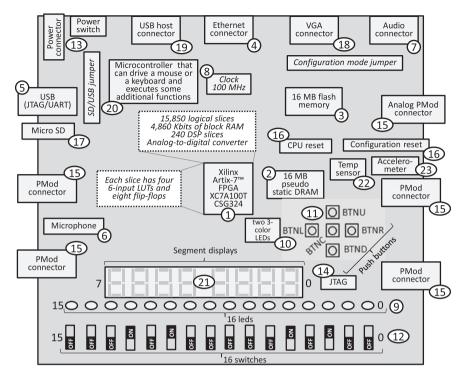

Figure 1.1 depicts the recent 7 series Xilinx FPGA column-based ASMBL (Advanced Silicon Modular Block) architecture [9]. The core configurable elements are slices that contain look-up tables (LUT), flip-flops and supplementary logic. A CLB consists of two slices and will be described in more detail in Sect. 1.2. DSP blocks are efficient for digital signal processing. They execute multiplication, addition, subtraction, logical and other operations over up to 48 bit operands. Some of FPGA columns contain block memories, hard intellectual property (IP) cores, input/output blocks, clock distributers and mixed signal managers. We will describe these blocks later on in this chapter.

Different FPGA elements can be:

- 1. Configured to implement the desired functionality.

- 2. Flexibly interconnected with each other.

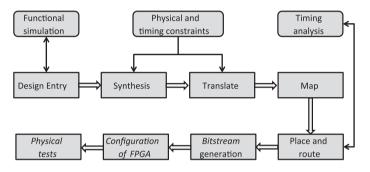

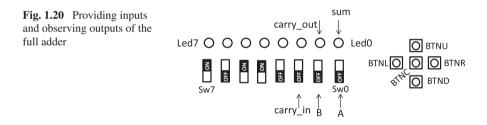

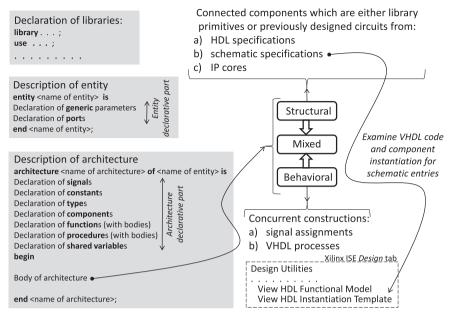

Fig. 1.2 One possible scenario of FPGA-based design

For example, an available 6-input/1-output slice LUT enables any Boolean function of 6 variables to be implemented. Configuration permits a particular function to be realized. A DSP block can be configured to implement a variety of arithmetic and logic operations. Besides it provides many additional useful features for digital signal and other types of processing that will be discussed later. Interconnections set up links between internal pins of different elements. Customization (configuring elements and interconnections) is done through reloading a bitstream to FPGA. The details will be given on examples below. Since the development of circuits and systems does not involve complex technological processes, FPGA are very appropriate for prototyping and verifying different design ideas.

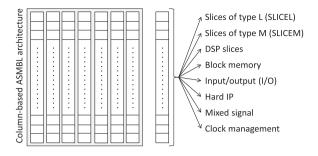

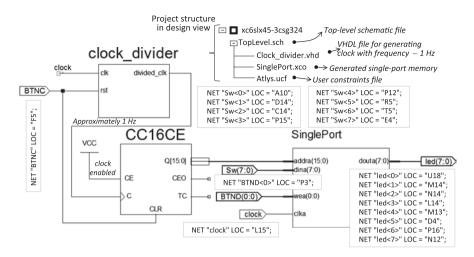

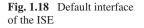

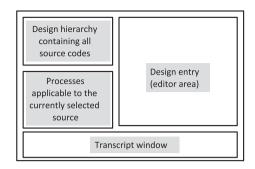

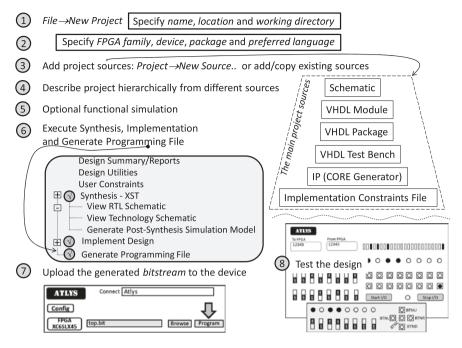

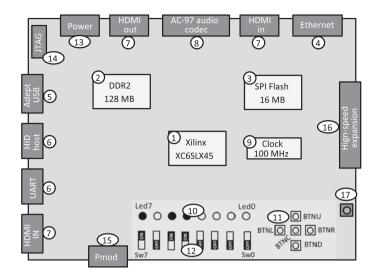

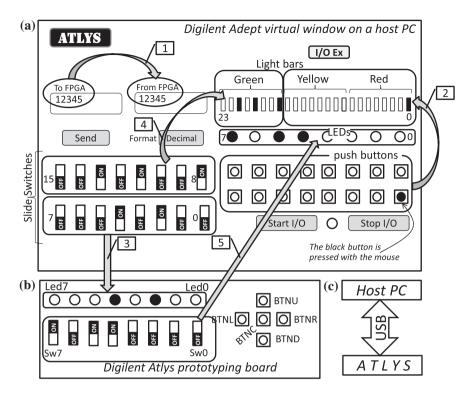

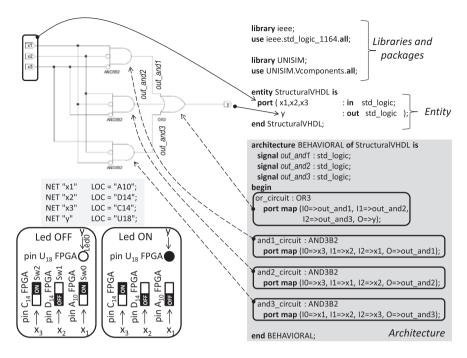

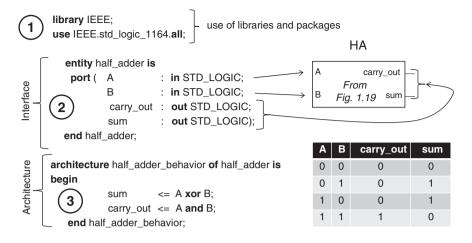

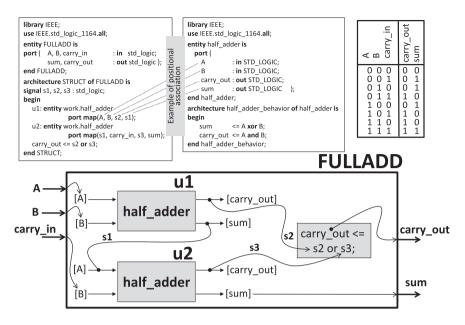

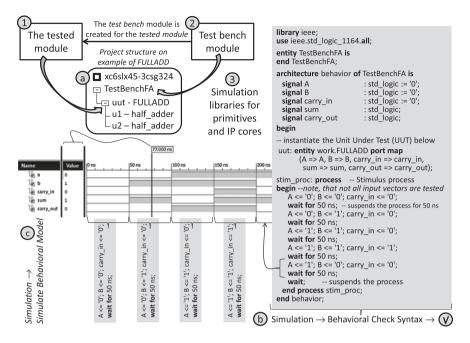

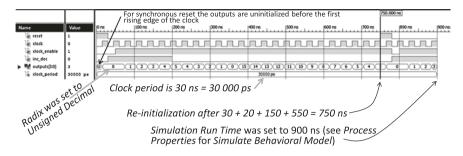

Figure 1.2 illustrates one possible scenario of FPGA-based design using Xilinx Integrated Software Environment (ISE release version 14.7), Digilent Adept software [10] and Atlys prototyping board [11] containing xc6slx45 FPGA of Xilinx Spartan-6 family.

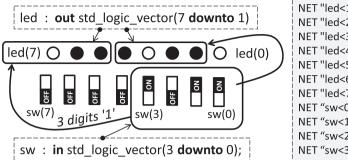

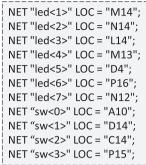

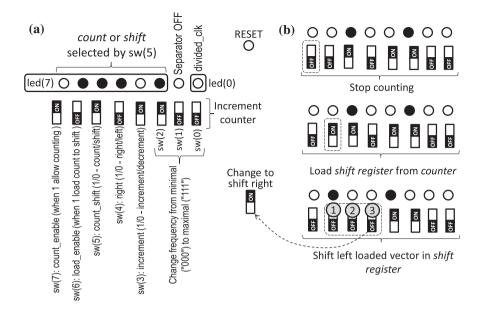

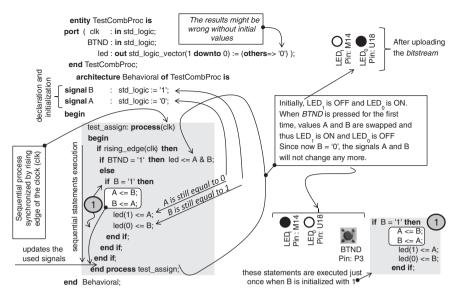

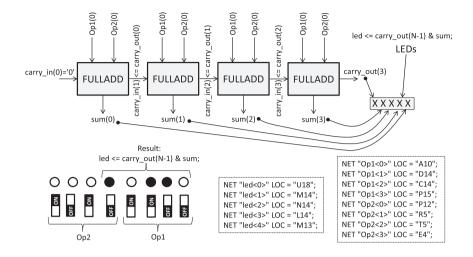

Different sources for the project are available in the ISE and we will use schematic editor (see point 1 in Fig. 1.2) and describe a circuit with 3 inputs  $(x_1, x_2, x_3)$  and 1 output (y) detecting exactly one value '1' in a 3-bit input vector (" $x_1x_2x_3$ "). Thus, y = '1' for any vector from the set {"001","010',"100"}, otherwise y = '0'. The circuit is saved in the file *SimpleSchematic.sch*. Let us connect three inputs ( $x_1, x_2, x_3$ ) and one output (y) of the circuit with external FPGA pins that are in turn connected with switches Sw0, Sw1, Sw2, and LED (Light-Emitting Diode) Led0 on the Atlys board. Such connections are indicated in a user constraints (implementation constraints) file (UCF) which is entitled *Atlys.ucf*  and shown in point 2 of Fig. 1.2, where A10, D14, C14, and U18 are names of FPGA external pins connected with the switches and the LED (see point 5 in Fig. 1.2). The NET keyword is used to apply constraints to specific signals (to the input and output signals in our case). The LOC keyword defines where a design element can be placed within the device. The detailed information about constraints can be found in [12]. Our ISE project (shown in between points 1 and 2 in Fig. 1.2) indicates the chosen FPGA (*xc6slx45-3csg324*), the top-level module (*SimpleSchematic.sch*) and the UCF (*Atlys.ucf*) which specifies pin assignment for the top-level module.

At the next phase synthesis, implementation and generate programming file steps are applied to our project (see point 3 in Fig. 1.2). The generated file *simple-schematic.bit* may now be used to configure the FPGA, which can be done either directly from the ISE or in board-targeted software, such as Digilent Adept [10] (see point 4 in Fig. 1.2). At the last step (see point 5 in Fig. 1.2) we verify the circuit functionality in FPGA using the onboard switches Sw0, Sw1, Sw2 to supply values of inputs  $x_1$ ,  $x_2$ ,  $x_3$  and the onboard Led0 to examine the result (i.e. the value of y). The circuit is so simple that it is implemented in just one slice LUT and there are totally 27,288 such LUTs available in the chosen FPGA.

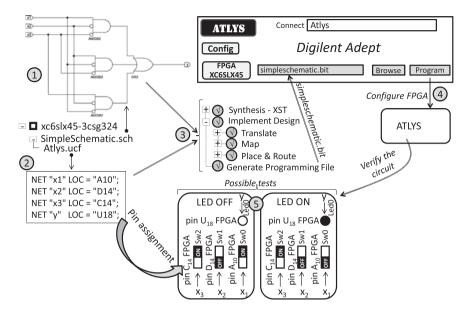

The designed circuit can be taken as a component for new projects and thus, a hierarchy will be involved. Suppose, we would like to analyze three groups of signals  $(x_1,x_2,x_3)$ ,  $(x_4,x_5,x_6)$ , and  $(x_7,x_8,x_9)$  and detect that exactly one group contains exactly one value '1'. The circuit that implements such functionality from the schematic editor of ISE is shown in Fig. 1.3.

At the beginning we create a component that contains the circuit shown in Fig. 1.2 (see point 1). This can be done in the ISE using the option *Create Schematic Symbol*. Since the name of the entity in point 1 of Fig. 1.2 is *SimpleSchematic*, the name of the component is the same (see Fig. 1.3). The component has to be connected within the new designed circuit much like it is done for library primitives (gates) in point 1 of Fig. 1.2. Thus, the desired functionality is described. The *Atlys.ucf* needs to be modified as follows:

| NET "x1" LOC = "A10"; | # Sw0                                          |

|-----------------------|------------------------------------------------|

| NET "x2" LOC = "D14"; | # Sw1                                          |

| NET "x3" LOC = "C14"; | # Sw2                                          |

| NET "x4" LOC = "P15"; | # Sw3                                          |

| NET "x5" LOC = "P12"; | # Sw4                                          |

| NET "x6" LOC = "R5";  | # Sw5                                          |

| NET "x7" LOC = "T5";  | # Sw6                                          |

| NET "x8" LOC = "E4";  | # Sw7                                          |

| NET "x9" LOC = "P3";  | # BTND – onboard button available on the Atlys |

| NET "y" LOC = "U18";  | # Led0                                         |

Here the symbol # permits comments to be provided and the comments shown above characterize links of the circuit pins with the FPGA external pins connected to the onboard switches and the button. The available onboard components and FPGA pins are connected in the printed circuit of the board and information about such connections is available from the Atlys board documentation [11].

Fig. 1.3 Hierarchical design and analysis of the results

Point 1 in Fig. 1.3 illustrates the project structure with the top-level module Top.sch. It is clearly seen that the structure is hierarchical in which the top-level module (Top.sch) is composed of four lower level modules (SimpleSchematic.sch). A dashed arrow line *a* points to the circuit *Top.sch* copied from the ISE schematic editor. Point 2 refers to the ISE design steps that have already been briefly discussed. In the Design Summary/Reports (see point b in Fig. 1.3) different characteristics of the circuit are summarized, particularly the used resources (now three LUTs are required in two FPGA slices), and delays (the maximum combinational path delay is 9.1 ns). We can use many other options, for example, View RTL Schematic (RTL is a Register Transfer Level). For our project schematic is taken as a design entry and it is the same as in the schematic editor (see the circuit indicated by dashed arrow line c). However, schematic can also be built by ISE tools from specifications in hardware description languages (HDL), which are generally considered to be more productive and efficient than schematic descriptions. Configuring (programming) the FPGA is provided in point 3. Verification of the designed circuit on the Atlys board is done in point 4.

Although the two projects in Figs. 1.2 and 1.3 are indeed trivial, they demonstrate the essential steps for FPGA-based design, which are also common for complex systems. A similar technique can be used for Altera Quartus environment (later on we will demonstrate some examples in Quartus 13 Web edition software for Altera FPGAs). For example, the *block editor* of Quartus enables schematic of the design to be created. Note, that although diagrams, such as in point 1 of Fig. 1.2, are illustrative for simple circuits, they become confused, difficult for verification and error prone for complex designs, for which HDL becomes more preferable. We will make an introduction to VHDL—Very-high speed integrated circuit HDL in Chap. 2. Now let us characterize basic FPGA components with more details.

## 1.2 The Basis of FPGA Devices

Configurable logic blocks (CLBs) are the main logic resources for implementing digital circuits. We will discuss such blocks that are used in recent FPGAs of the major two companies: Altera and Xilinx.

### 1.2.1 Configurable Logic Blocks of Xilinx FPGAs

We consider CLBs for the recent 7 series FPGAs that are also very similar to the popular Spartan-6 family of FPGAs. A CLB is composed of 2 *slices* that are connected to a switch matrix for access to the general routing matrix [9]. Every slice contains: (1) *four LUTs*; (2) *eight* edge-triggered D-type *flip-flops*, four of which can also be configured as level-sensitive latches; (3) *multiplexers*; and (4) *carry logic* for arithmetic circuits. Up to 16:1 multiplexer can be implemented in one slice using built in multiplexers and LUTs.

There are two types of slices: SLICEL and SLICEM. Each CLB has either two SLICELs or a SLICEL and a SLICEM. SLICEM provides support for two additional operations: storing data in the slice that in this case may be used to compose a distributed RAM; and shifting up to 32-bit data.

Each slice LUT has 6 independent inputs  $(x_0,...,x_5)$ , 2 independent outputs  $O_5$  and  $O_6$  and can be configured to implement: (1) any Boolean function of up to 6 variables  $x_0,...,x_5$ ; (2) any two Boolean functions of up to 5 shared variables  $x_0,...,x_4$  and  $x_5$  has to be set to high level; (3) any two Boolean functions of up to 3 and 2 separate variables. The propagation delay is independent of the function implemented in the LUT.

Let us consider an example of LUT(6,1) with 6 inputs  $x_5,x_4,x_3,x_2,x_1,x_0$ and 1 output y. The LUT will be used to implement a parity function for 6-bit binary vector  $x_5x_4x_3x_2x_1x_0$  in such a way that the Hamming weight of the vector  $x_5x_4x_3x_2x_1x_0y$  is odd (the Hamming weight of a binary vector is the number of values '1' in the vector). The truth table for the function y is given in Table 1.1.

The column *Hex* contains hexadecimal vector that is used for INIT attribute in the ISE environment (it is accessed through the *Object Properties* described below). The vector begins with the value marked with an asterisk in Table 1.1:

#### 1.2 The Basis of FPGA Devices

| x4x3x2x1x0 | y1y0 | Hex    | x5x4x3x2x1x0 | у | Hex | x5x4x3x2x1x0 | у | Hey |

|------------|------|--------|--------------|---|-----|--------------|---|-----|

| 00000      | 00   | ca     | 000000       | 1 | 9   | 100000       | 0 | 6   |

| 00001      | 01   |        | 000001       | 0 |     | 100001       | 1 |     |

| 00010      | 10   |        | 000010       | 0 |     | 100010       | 1 |     |

| 00011      | 11   |        | 000011       | 1 |     | 100011       | 0 |     |

| 00100      | 11   | 35     | 000100       | 0 | 6   | 100100       | 1 | 9   |

| 00101      | 10   |        | 000101       | 1 |     | 100101       | 0 |     |

| 00110      | 01   |        | 000110       | 1 |     | 100110       | 0 |     |

| 00111      | 00   |        | 000111       | 0 |     | 100111       | 1 |     |

| 01000      | 01   | a5     | 001000       | 0 | 6   | 101000       | 1 | 9   |

| 01001      | 10   |        | 001001       | 1 |     | 101001       | 0 |     |

| 01010      | 01   |        | 001010       | 1 |     | 101010       | 0 |     |

| 01011      | 10   |        | 001011       | 0 |     | 101011       | 1 |     |

| 01100      | 11   | 59     | 001100       | 1 | 9   | 101100       | 0 | 6   |

| 01101      | 00   |        | 001101       | 0 |     | 101101       | 1 |     |

| 01110      | 10   |        | 001110       | 0 |     | 101110       | 1 |     |

| 01111      | 01   |        | 001111       | 1 |     | 101111       | 0 |     |

| 10000      | 01   | a5     | 010000       | 0 | 6   | 110000       | 1 | 9   |

| 10001      | 10   |        | 010001       | 1 |     | 110001       | 0 |     |

| 10010      | 01   |        | 010010       | 1 |     | 110010       | 0 |     |

| 10011      | 10   |        | 010011       | 0 |     | 110011       | 1 |     |

| 10100      | 01   | ab     | 010100       | 1 | 9   | 110100       | 0 | 6   |

| 10101      | 11   |        | 010101       | 0 |     | 110101       | 1 |     |

| 10110      | 00   |        | 010110       | 0 |     | 110110       | 1 |     |

| 10111      | 11   |        | 010111       | 1 |     | 110111       | 0 |     |

| 11000      | 01   | 65     | 011000       | 1 | 9   | 111000       | 0 | 6   |

| 11001      | 10   |        | 011001       | 0 |     | 111001       | 1 |     |

| 11010      | 11   |        | 011010       | 0 |     | 111010       | 1 |     |

| 11011      | 00   |        | 011011       | 1 |     | 111011       | 0 |     |

| 11100      | 01   | ab* ** | 011100       | 0 | 6   | 111100       | 1 | 9*  |

| 11101      | 11   |        | 011101       | 1 |     | 111101       | 0 |     |

| 11110      | 00   |        | 011110       | 1 |     | 111110       | 0 |     |

| 11111      | 11   |        | 011111       | 0 |     | 111111       | 1 |     |

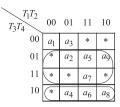

**Table 1.1** Truth tables for configuring LUT(5, 2) and LUT(6, 1)

(i.e. the first digit is  $9_{16}$ ): 9669699669966996699<sub>16</sub> and it represents the binary vector for the output y: 1001 0110 1001 0100 1001 1001 1001 0110 0110 1001 1001 0010 0110 1001 1001 0110 1001 (for easier comparison of hexadecimal and binary vectors, digits 9 are shown in **bold** and digits 6 are shown in a normal font).

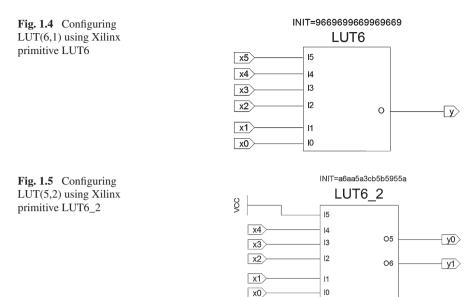

Figure 1.4 demonstrates configuring the LUT(6,1) in the schematic editor of the ISE. The vector **96696996699669**<sub>16</sub> is assigned to the INIT attribute accessed through the *Object Properties* (point mouse to the LUT in the schematic editor and right mouse button click to change *Object Properties*). Figure 1.5 demonstrates configuring LUT(5,2) to implement the functions  $y_0$  and  $y_1$  shown in Table 1.1.

Now hexadecimal vector composed of 16 hexadecimal digits is split in two 8-digit sub-vectors in such a way that the first sub-vector configures the first

function and the second sub-vector configures the second function. For our example in Table 1.1 the following vector is built:  $a6aa5a3cb5b5955a_{16}$ . The first sub-vector  $a6aa5a3c_{16}$  enables the function  $y_1$  to be configured. The second sub-vector  $b5b5955a_{16}$  enables the function  $y_0$  to be configured.

An asterisk (\*) in Table 1.1 indicates the beginning of the first sub-vector and two asterisks (\*\*) in Table 1.1 indicate the beginning of the second sub-vector. The circuits in Figs. 1.4 and 1.5 can easily be verified supplying inputs from switches and displaying values of the functions on LEDs. In Fig. 1.5 a 6-input LUT is taken but the most significant input is set to high ('1') by supplying VCC signal and configuring the LUT(5,2) to implement two different Boolean functions of 5 shared variables.

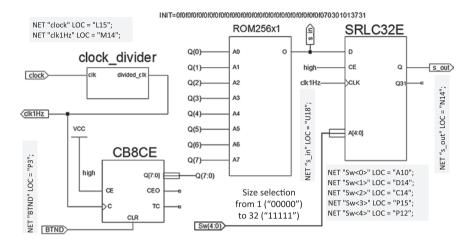

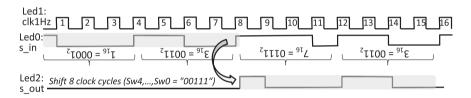

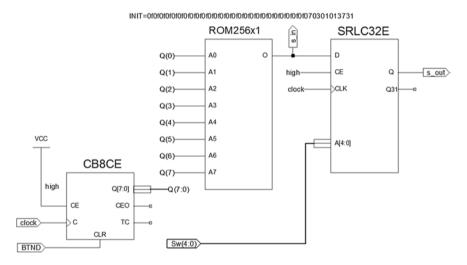

LUTs in SLICEMs can implement a synchronous (distributed) RAM/ROM with single, dual or quad ports. We can also configure SLICEM as up to 32-bit shift register not requiring slice flip-flops. The register enables serial data on its input to be delayed on its output from 1 to 32 clock cycles. The number of clocks for delay is controlled by a dedicated 5-bit input vector. Figure 1.6 gives an example of a circuit that contains a LUT-based  $256 \times 1$  ROM and a shift register with variable size (from 1 to 32).

**Fig. 1.6** Using LUT-based (distributed) memory (Xilinx primitive ROM256x1) and a shift register (Xilinx primitive SRLC32E)

**Fig. 1.7** Waveforms of signals displayed on the LEDs Led1 (clock with frequency 1 Hz), Led0 (data from the ROM), Led2 (data from the shift register)

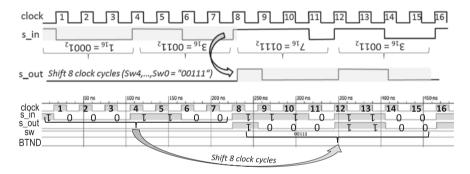

approximately every second. Connections between the bus Q(7:0) and the lines Q(7),...,Q(0) are provided by names much like it is done for the lines *clk1 Hz* and high (i.e. non-shown in Fig. 1.6 wires with equal names are, in fact, connected). The project has been tested in the Atlys board. Onboard switches Sw4,...,Sw0 are used to set the shift register size which can be defined from 1 ("00000") to 32 ("11111"). All necessary connections with FPGA pins (see grey rectangular areas) are shown in Fig. 1.6 in form of lines of the file Atlys.ucf. The onboard button BTND supplies the reset signal (just for the counter, because the shift register does not need to be cleared). Three onboard LEDs (Led2, Led1, and Led0) are used for verification of the project. Led1 gets the clk1Hz signal (clock with a frequency approximately equal to 1 Hz). Thus, all other signals can be verified sequentially relatively to the low-frequency clock (see waveforms in Fig. 1.7). Switches Sw4,...,Sw0 permit delay of the Led2 (shift register output s\_out) relatively to the Led0 (shift register input s\_in) to be set. For example, if Sw4,...,Sw0 are assigned to the value "00111" then the delay is 8 clock cycles and waveforms for such a case are shown in Fig. 1.7. The project is implemented on 12 slices from which one slice is used for the ROM and one slice is used for the shift register. A number of other useful LUT configurations are considered in [9]. It is important to note that LUT-based memories can be used as configurable combinational circuits enabling functionality to be changed during execution time.

The number of slices in Spartan-6 family FPGAs varies from 600 to 23,038. The number of slices in 7 series FPGAs varies from 10,250 to 305,400.

## 1.2.2 Logic Elements of Altera FPGAs

We consider logic elements for recent Stratix-V series FPGAs with core reconfigurable fabric called logic array block (LAB) [13] composed of adaptive logic modules (ALM), which can be configured to implement logic, arithmetic, and memory functions. Half of the available LABs may be used as memory LAB (MLAB).

Each ALM contains different LUT-based resources and can implement any Boolean function of up to six variables. Besides, a number of other types of Boolean functions F(n,m) describing circuits with n inputs and m outputs can be implemented such as F(4,3) and F(5,2).

ALMs operate in four possible modes [13]:

- 1. Normal mode enables two Boolean functions of up to 5 variables or one Boolean function of up to 6 variables to be implemented. Besides, 8 available data inputs allow certain Boolean functions with more than 6 variables to be realized.

- 2. Extended mode permits the result of the implemented Boolean function to be registered.

- 3. Arithmetic mode uses four 4-input LUTs for pre-adder logic connected with two dedicated full adders.

- 4. Shared arithmetic mode permits 3 input additions to be implemented. The details are given in [13].

Each ALM in an MLAB can be programmed as either a  $64 \times 1$  or a  $32 \times 2$  block. Since each MLAB supports a maximum of 640 bits it can be configured as either a  $64 \times 10$  or a  $32 \times 20$  simple dual-port static RAM.

For some examples of this book we will use the DE2-115 prototyping board with Altera Cyclone-IV FPGA [14]. LABs of this FPGA contain groups of logic elements (LE) and one LAB consists of 16 LEs. Each LE contains: 4-input LUT which can implement any Boolean function of 4 variables; a flip-flop, which in [14] is called a programmable register; a carry and a register (a flip-flop) chains connections.

LEs operate in normal and arithmetic modes. The first mode is efficient for general logic applications and combinational functions. The second mode is more appropriate for adders, counters, accumulators, and comparators.

Thus, the primary reconfigurable resources of Xilinx and Altera FPGAs are based on LUTs. The simplest element of Altera FPGAs is LE/ALM and it

contains fewer resources than a Xilinx FPGAs slice, which is the simplest element in Xilinx FPGAs. The most advanced recent devices of both companies include 6-input LUTs, which can be configured for implementing logic, memory, and arithmetic functions.

The number of LEs in Cyclone-IV FPGAs varies from 6,725 to 149,760. The number of LEs in Stratix-V FPGAs is from 236K to 952K. In this book we will mainly use Xilinx FPGA of Spartan-6 and Artix-7 families. The majority of examples can easily be converted to Altera FPGAs and we will consider some examples for Altera Cyclone-IVe devices.

## 1.3 Embedded Blocks

In addition to basic reconfigurable logic described in the previous section contemporary FPGAs contain numerous embedded blocks which can be observed in the basic architecture of the Xilinx 7 series FPGA in Fig. 1.1 (similar embedded blocks are available for Altera FPGAs [13]). We will discuss such blocks and their use in different projects on examples of embedded memories and DSP slices for Spartan-6 family and 7 series of Xilinx FPGAs.

### 1.3.1 Embedded Memories

Embedded memory blocks, or Block RAMs, are widely available in modern FPGAs and are used for efficient data storage and buffering. FPGAs of Spartan-6 family contain from 12 to 268 Block RAMs each of which stores up to 18 Kb of data and can be configured as either two independent 9 Kb RAMs or one 18 Kb RAM. Each RAM is addressable through two ports, but can also be configured as a single-port RAM. The width of the two ports of a 18 Kb RAM is configurable independently of each other as  $16K \times 1$ ,  $8K \times 2$ ,  $4K \times 4$ ,  $2K \times 8$ ,  $1K \times 16$ ,  $512 \times 32$  (when no parity bits are used) or  $16K \times 1$ ,  $8K \times 2$ ,  $4K \times 4$ ,  $2K \times 9$ ,  $1K \times 18,512 \times 36$  (when parity bits are used). Data can be written to either or both ports and can be read from either or both ports [15]. Each port has its own address, data in (input data), data out (output data), clock, clock enable, and write enable. The read and write operations are synchronous and require an active clock edge. Block RAMs are organized in columns within an FPGA device (see Fig. 1.1) and can be interconnected to create wider and deeper memory structures. It is possible to specify Block RAMs characteristics and to initialize memory content in VHDL code, which will be shown in the next chapter. Intellectual Property (IP) core generator and schematic library primitives can also be used (Chap. 4 gives some examples).

The 7 series FPGAs contain from 135 to 1,880 Block RAMs each of which stores up to 36 Kb of data. FPGAs provide support for 36 and 18 Kb block RAMs

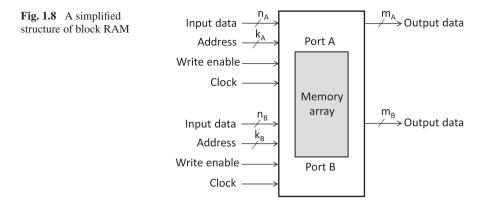

[16] with built-in FIFO (first input first output) logic. Each 36 Kb block RAM can be configured as  $32K \times 1$ ,  $16K \times 2$ ,  $8K \times 4$ ,  $4K \times 8$ ,  $2K \times 16$ ,  $1K \times 32$ , or  $512 \times 64$  (when no parity bits are used) or  $32K \times 1$ ,  $16K \times 2$ ,  $8K \times 4$ ,  $4K \times 9$ ,  $2K \times 18$ ,  $1K \times 36$ , or  $512 \times 72$  (when parity bits are used). An additional Block RAM features in the 7 series devices is an opportunity to use output registers. A simplified structure of block RAM is presented in Fig. 1.8, where  $n_A/n_B$  is the size of input data for the port A/B,  $m_A/m_B$  is the size of output data for the port A/B,  $k_A/k_B$  is the size of address for the port A/B.

Each block RAM contains two completely independent ports that share the same memory array for write and read operations (i.e. true dual-port memory can be built). Potential conflicts during write operations need to be avoided and this issue is addressed in [16].

We have already mentioned that Block RAM (36 Kb for the 7 series devices or 18 Kb for the Spartan-6 family devices) can be decomposed into two independent block RAMs (18 Kb for the 7 series devices or 9 Kb for the Spartan-6 family devices), each of which behaves similarly to the initial block. Several block RAMs can compose larger memory if required.

Each memory access (a read or a write) in the devices [15, 16] is controlled by a clock. All inputs, data, address, clock enables, and write enables are registered. Clocking the address means that data remain unchanged until the next clock cycle.

Let us consider now two simple examples of using single and dual-port embedded memories for Spartan-6 FPGA available on the Atlys prototyping board. Block RAMs will be created by the Xilinx *LogiCore* block memory generator [17]. First we add a new source in the Xilinx ISE (option  $Project \rightarrow New Source$ ) and then select IP and a name *SinglePort*. The core generator will be launched. Let us leave all the options (listed in 6 steps) unchanged except the following: *Memory type* (step 2) has to be defined as *Single Port RAM*, *Write Width* (step 3) is assigned to 8, *Write Depth* (step 3) is assigned to 65536 (i.e. we would like to create a memory from several block RAMs with the total size of 64 KB) and *Load Init File* option (step 4) is *checked* (i.e. we would like to upload an initialization file of type COE). A COE is a text file (created, for instance, in Notepad) indicating *memory\_initialization\_radix* (valid values are 2, 10, or 16) and

**Fig. 1.9** Simple example with memory built from a single port block RAMs (CC16CE is the Xilinx library primitive for a 16-bit binary counter)

*memory\_initialization\_vector* which contains values for each memory element (that in our case is an 8-bit word). Any value has to be written in radix defined by the *memory\_initialization\_radix*. The following example presents a valid COE file which will be used for our project (additional details can be found in [17]):

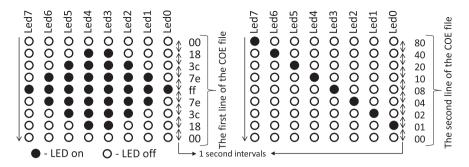

memory\_initialization\_radix = 16; memory\_initialization\_vector = 00, 18, 3c, 7e, ff, 7e, 3c, 18, 00, 80, 40, 20, 10, 08, 04, 02, 01, 00, 01, 02, 04, 08, 10, 20, 40, 80, 00, 80, c0, 60, 30, 18, 0c, 06, 03, 01, 00, 80, c0, e0, 70, 38, 1c, 0e, 07, 03, 01, 00;

Coefficients are separated by a space, a comma, or by placing one value in each line with a carriage return. A semicolon indicates the end of specification line such as memory\_initialization\_radix = 16;. In our example the first 48 bytes of memory will be filled in from the COE file above and the remaining bytes are assigned to  $FF_{16}$  (the option *Fill Remaining Memory Locations* available at step 4 is checked and the value FF is chosen). The button *Show* permits the contents of the COE file to be displayed and examined.

After generation a primitive for the single port memory can be used in the ISE schematic editor much like any other Xilinx library primitive. Figure 1.9 gives an example of a trivial circuit which permits to read from RAM and to display on the Atlys onboard LEDs the sequence partially shown in Fig. 1.10 (much like Fig. 1.6 the relevant constraints of the *Atlys.ucf* are given in Fig. 1.9).

The sequence in Fig. 1.10 was specified in the first (00, 18, 3c, 7e, ff, 7e, 3c, 18, 00) and in the second (80, 40, 20, 10, 08, 04, 02, 01, 00) lines of the COE file above. If the button *BTND* is pressed data from the onboard switches are written to the RAM

Fig. 1.10 Initialization (COE) file specifies visual sequence on the LEDs

and displayed on the LEDs. Thus, we can examine both write and read operations. From the ISE *Design Summary* we can see that 32 RAM blocks have been allocated. A similar memory can be defined as an HDL component.

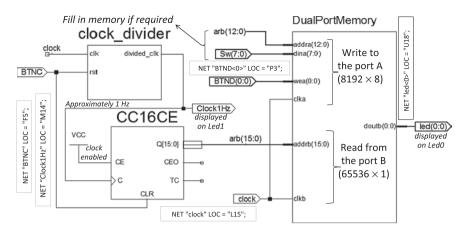

Let us build now a simple dual-port memory. The steps are similar to the steps for the single port memory. The majority of options of the *LogiCore* generator are unchanged except the following: *Memory type* (step 2) has to be defined as *Simple Dual Port RAM*, *Write Width* for the port A (step 3) is assigned to 8, *Write Depth* for the port A (step 3) is assigned to 8192 (i.e. we would like to create memory from several block RAMs with the total size 8 KB), *Write Width* for the port B (step 3) is assigned to 1, and *Load Init File* option (step 4) is *checked*. Thus, the first port A is configured as 8,192 × 8 and the second port B—as 65,536 × 1. The following COE file is used (note that now the radix is chosen to be 2):

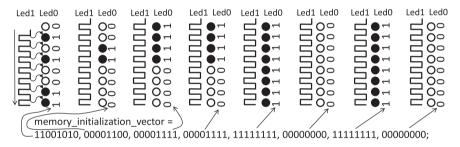

memory\_initialization\_radix = 2; memory\_initialization\_vector = 11001010, 00001100, 00001111, 00001111, 11111111, 00000000, 11111111, 00000000;

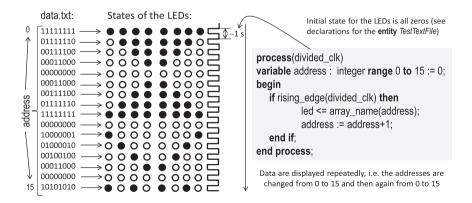

Figure 1.11 gives an example of a trivial circuit which permits to initialize  $8,192 \times 8$  RAM by byte values from the COE file above through the first port A and then to read from RAM and to display on the rightmost Atlys onboard LED Led0 signals from the single output of the second port B of 65,536  $\times$  1 RAM.

In our example the first 8 bytes of memory will be filled in from the COE file above and the remaining bytes are assigned to FF<sub>16</sub> (the option *Fill Remaining Memory Locations* available at step 4 is checked and the value FF is chosen). The clock signal with the reduced frequency (approximately 1 Hz) is displayed on Led1. Thus we can see changes of Led0 (i.e. the second port B output) relatively to Led1 (i.e. relatively to clock with the reduced frequency) and these changes are shown in Fig. 1.12. The desired sequence has been specified in the COE file above by binary 8-bit vectors. From the ISE *Design Summary* we can see that 4 RAM blocks have been allocated. The second example clearly demonstrates that two ports of the same block RAMs can have different aspect ratio (8,192 × 8 for the port A and 65,536 × 1 for the port B). Data are written to the memory by

**Fig. 1.11** Example with memory to be built from simple dual-port block RAMs (CC16CE is the Xilinx library primitive for a 16-bit binary counter)

Fig. 1.12 Initialization (COE) file specifies visual sequence on the LED Led0

bytes and read by bits. Thus, many useful converters can be created directly in memory without the need for additional logic. All necessary details can be found in [15-17].

## 1.3.2 Embedded DSP Slices

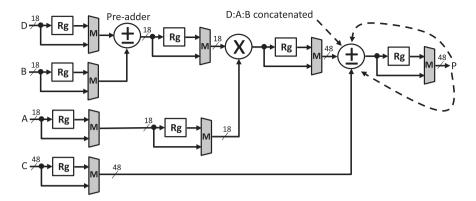

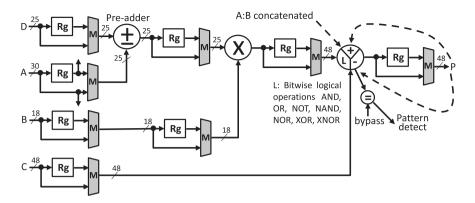

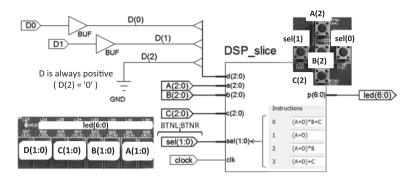

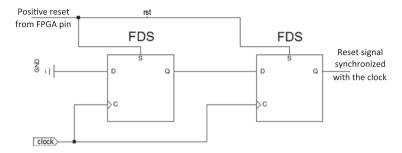

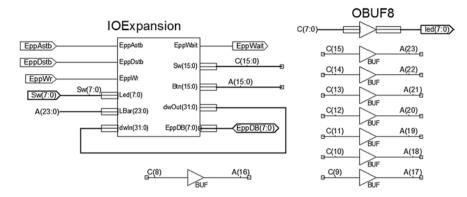

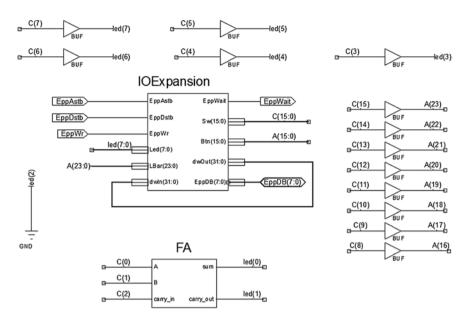

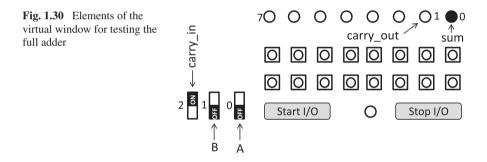

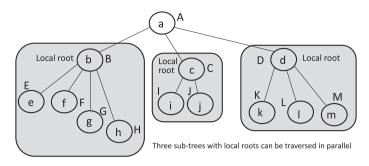

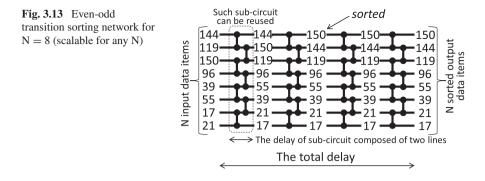

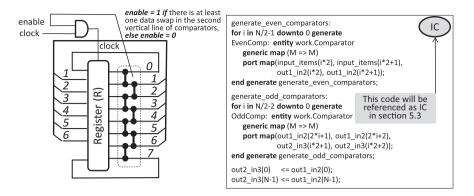

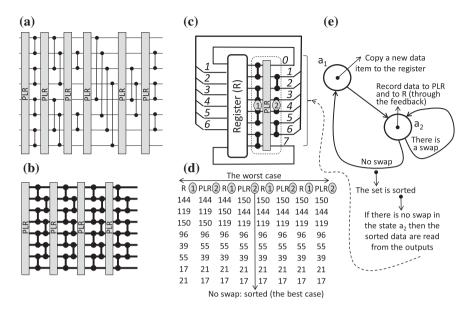

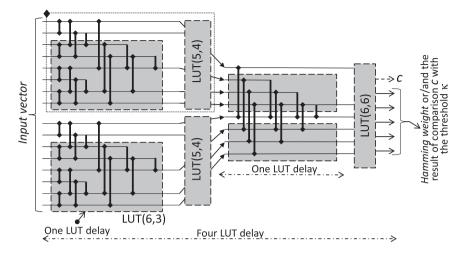

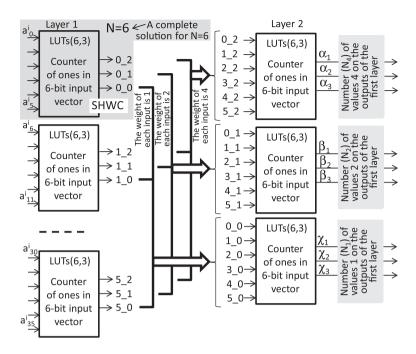

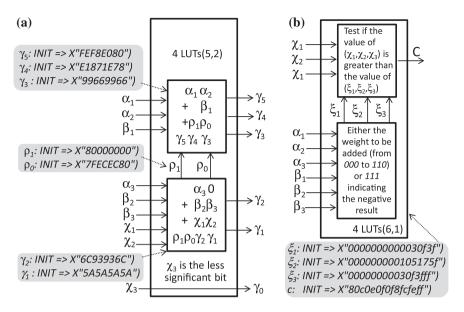

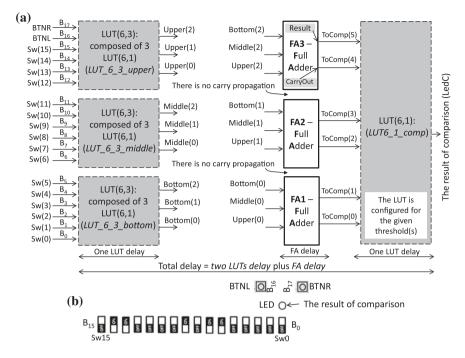

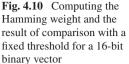

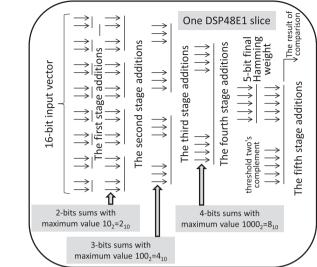

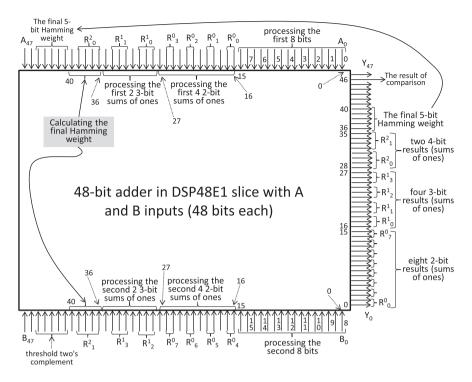

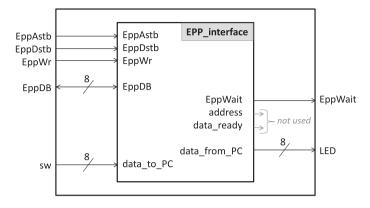

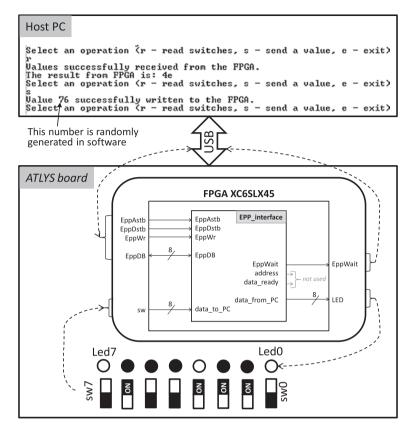

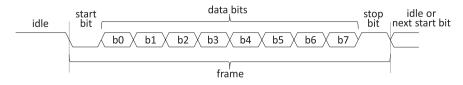

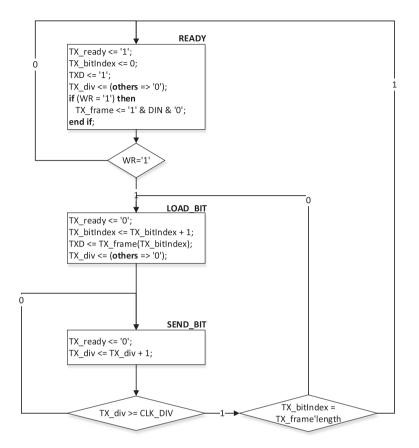

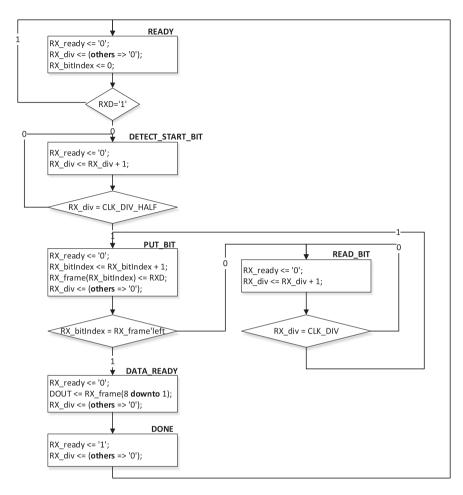

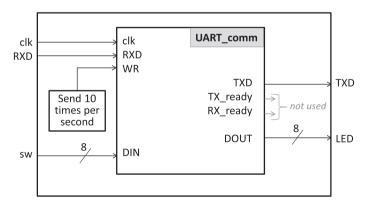

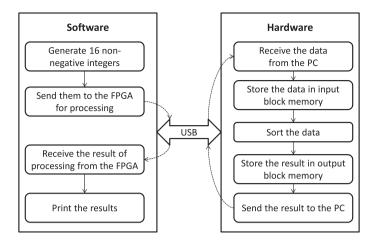

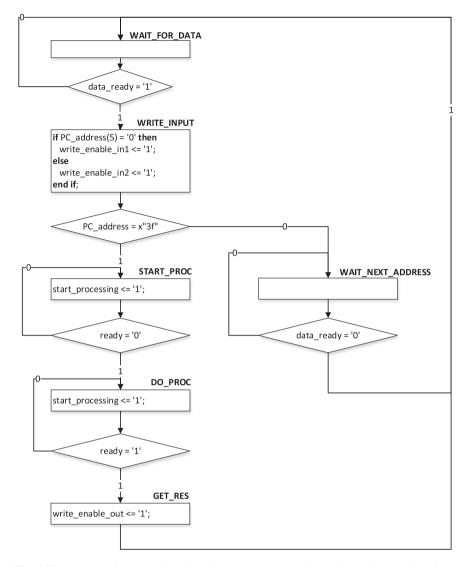

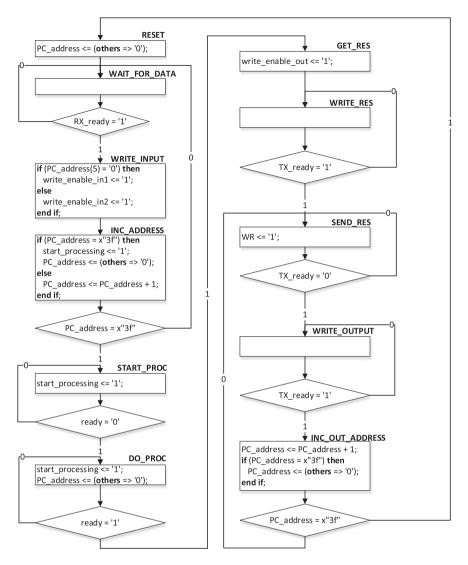

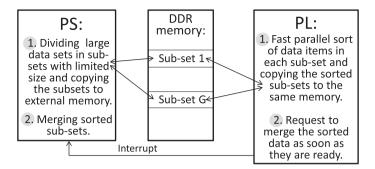

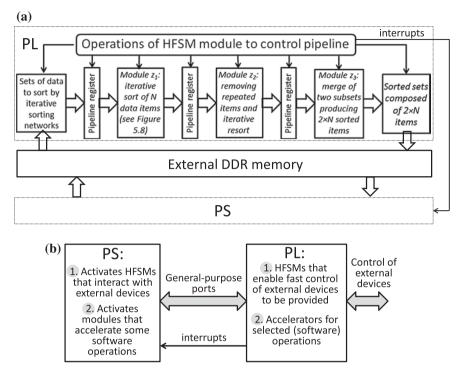

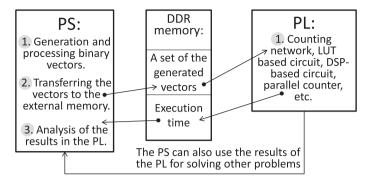

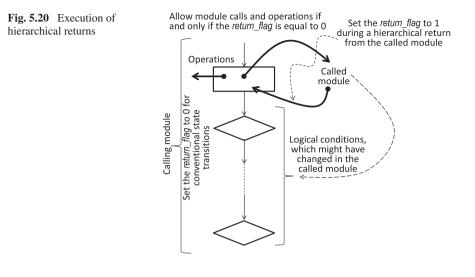

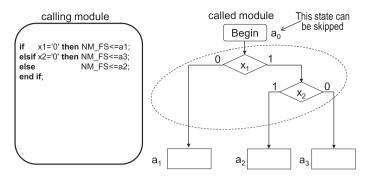

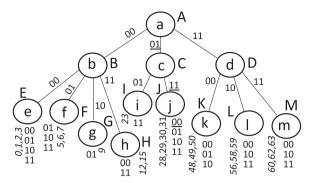

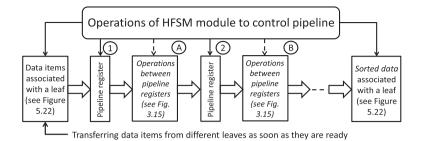

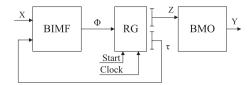

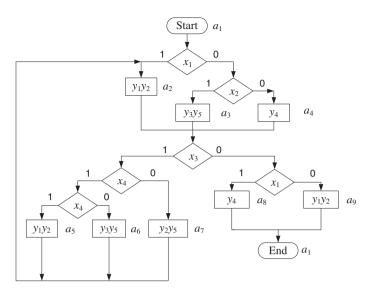

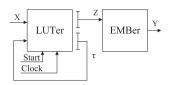

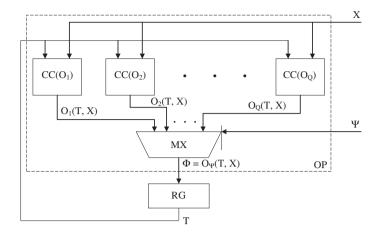

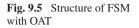

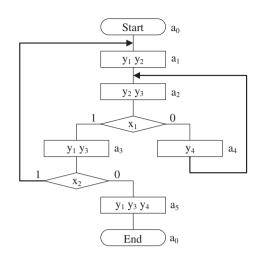

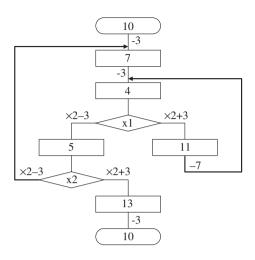

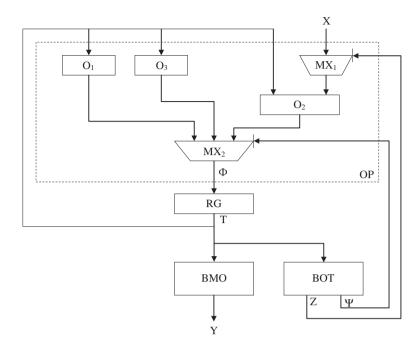

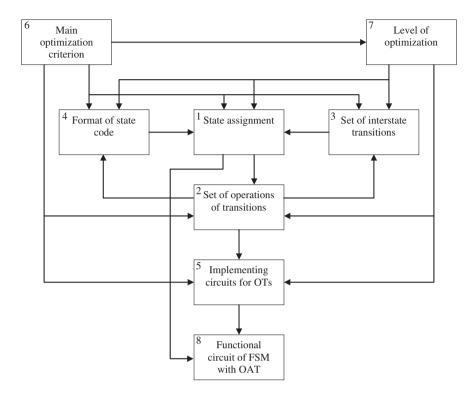

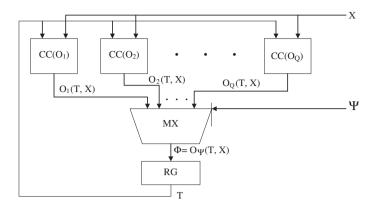

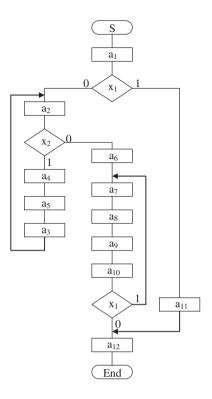

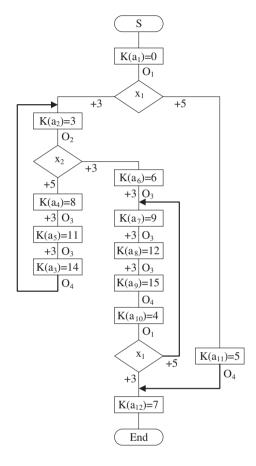

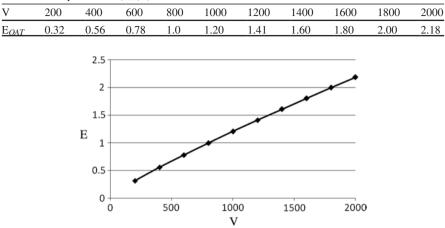

Devices of Spartan-6 family include from 8 to 180 digital signal processing slices DSP48A1 which support several functions, including multiplier, multiplieraccumulator, pre-adder/subtracter followed by a multiply accumulator, multiplier followed by an adder, wide bus multiplexers, magnitude comparator, and wide counter [18]. These types of functions are frequently required in DSP applications. It is also possible to connect multiple DSP48A1 slices to form wide math functions, DSP filters, and complex arithmetic without the use of general FPGA logic