## Vazgen Melikyan

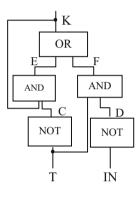

# Simulation and Optimization of Digital Circuits

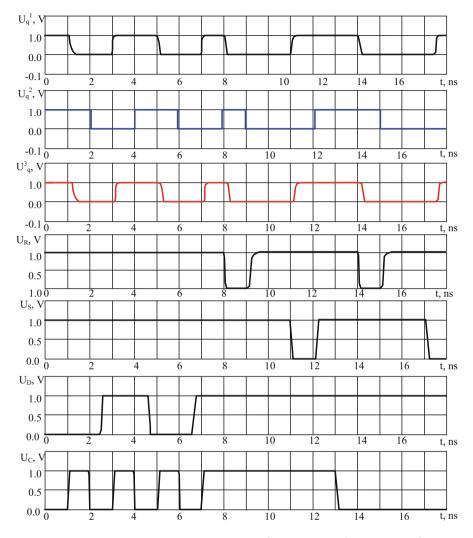

Considering and Mitigating Destabilizing Factors

Simulation and Optimization of Digital Circuits

Vazgen Melikyan

# Simulation and Optimization of Digital Circuits

Considering and Mitigating Destabilizing Factors

Vazgen Melikyan Director of Educational Department Synopsys Armenia CJSC Yerevan, Armenia

ISBN 978-3-319-71636-7 ISBN 978-3-319-71637-4 (eBook) https://doi.org/10.1007/978-3-319-71637-4

Library of Congress Control Number: 2018932032

© Springer International Publishing AG, part of Springer Nature 2018

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Printed on acid-free paper

This Springer imprint is published by the registered company Springer International Publishing AG part of Springer Nature.

The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

Dedicated to the bright memory of my parents. Shavarsh Melikyan and Siranush Hakobyan.

#### Preface

The book systematically expounds the main results obtained by the author in the field of gate-level simulation and optimization of digital ICs, with consideration of destabilizing factors (radiation exposure, ambient temperature, nonideality of the power source, input signals, interconnects, power rails, etc.).

The basis of most methods, models, and algorithms of gate-level simulation of digital ICs proposed in the monograph is to provide a practical compromise between the accuracy of the results obtained and the costs of the required computer resources.

The book is anticipated for scientists and engineers specializing in the field of IC simulation, as well as for students and postgraduate students studying the disciplines related to IC design.

Yerevan, Armenia

Melikyan V. Sh.

#### Introduction

Designing modern digital integrated circuits (IC) is impossible without the use of effective electronic design automation (EDA) tools. High rates of the development of IC fabrication technologies constantly lead to the necessity to update EDA tools, including systems of gate-level simulation and optimization of digital ICs.

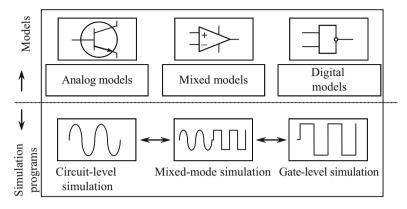

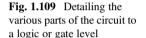

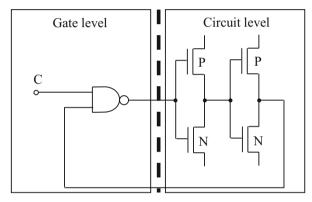

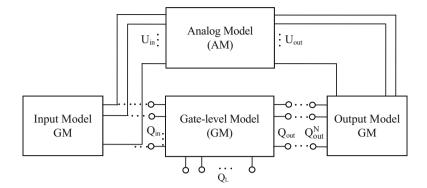

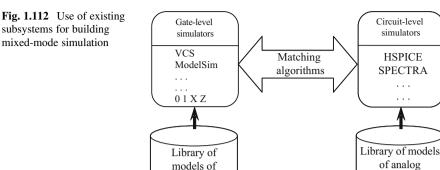

Owing to the success in microelectronics, leading companies-manufacturers such as Intel, Taiwan Semiconductor Manufacturing Company (TSMC), Samsung, and Global Foundries (GF) have already developed 16-, 14-, and even 7-nanometer technologies of IC fabrication. At present, already produced ICs contain tens of billions of active devices on a single die with an area up to hundreds of mm<sup>2</sup>. Taking into account the planned transition to 5-nanometer technology in the near future and increasing the crystal size to a thousand square millimeters, the number of circuit elements will soon increase another several times. Traditional systems of circuitlevel simulation based on models in the form of systems of ordinary differential equations are not suitable for an entire simulation of modern ICs due to unacceptably high costs of machine resources (computing time and memory size). The way out is the use of either pure gate-level simulation in case of digital ICs or a multilevel mixed-mode simulation that uses different models and algorithms of fundamentally different nature (circuit, logic, etc.) for different IC parts in case of digital and mixedsignal ICs. In case of mixed-mode analysis, the role of gate-level simulation is also extremely important, because it is just due to its application that the dimensionality of the problem is reduced.

Thus, gate-level simulation has become the main tool for the analysis of modern digital ICs and digital fragments of ICs. However, the tasks assigned to gate-level simulation tools have now changed radically. Traditional gate-level simulation was focused on the qualitative reflection of the processes occurring in digital circuits and was based on the apparatus of Boolean algebra, and high speed of simulation was achieved precisely due to the simplified representation of models of logic gates. For detailed simulation, circuit-level simulation tools were used. As a result of fundamental change of gate-level simulation role, a rather detailed imitation of signals just at the logical level of abstraction is required, and not at the expense of the main

advantage-the speed of simulation. Otherwise, the dimensionality issue of simulating circuits will be not solved.

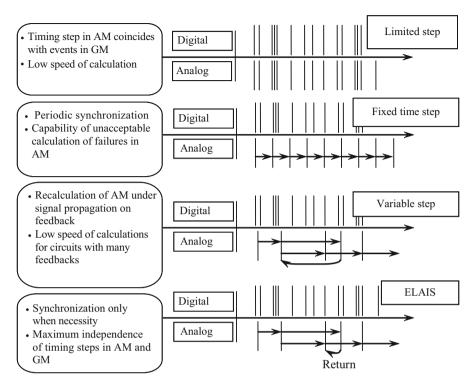

Thus, an extreme need arises for the development of digital circuit simulation systems that simultaneously possess the speed, inherent in gate-level simulation and accuracy, close to circuit-level simulation.

Existing gate-level simulation tools are not able to solve this problem, since at the time of their creation the ratios of various physical phenomena were fundamentally different. Because of the unjustifiably low accuracy of existing gate-level models, in most cases they do not even provide qualitatively accurate results of simulation of modern digital ICs.

A series of reasons exist that make it difficult to apply the available methods of gate-level simulation in the real IC design practice. For example, with the transition to 90-nanometer and newer technologies, the leakage currents of transistors, ignored by existing simulation programs, already have a dominant role. In the development of modern high-speed ICs, operating in the range of tens of gigahertz, the role of parasitic inductances changes radically. There are many other examples of this kind. However, among all reasons, nowadays the dominant is the absence of the possibility of considering the influence of various external (ambient temperature, radiation, etc.) and internal (delay and distortion of the waveform when passing through the interconnect, crosstalk, IR drop, etc.) destabilizing factors (DF) on IC operation in existing gate-level simulation tools. The fact is that due to the success in the development of microelectronics, the ratio of the parameters of useful and parasitic signals has changed qualitatively. If, for example, the amplitude of logic gate signals in recent years has decreased from a few to a part of volts, the magnitude of the changes in the output signals of logic gates due to fluctuations in ambient temperature or radiation exposure has not only not decreased but also increased. The latter is due to the gradual strengthening of requirements in relation to the ranges of external DF, under which the designed ICs should remain operational. As a result, the influence of external DF became commensurable, and sometimes exceeded their nominal values. If earlier it was possible to ignore the changes in the levels of logical signals due to the mentioned external DF, at present this in most cases simply leads to qualitatively inaccurate simulation results. A similar situation occurs with internal DFs. For example, the ratio of the delay on the logic gate and on the interconnect has changed from 100:1 sometimes to 1:100 over the last decade, and it's impossible to ignore this factor in simulating circuits. Approximately the same situation is with other external and internal DFs. Therefore, the existing means of gate-level simulation of digital circuits, created at times when the role of DF was insignificant, are not suitable for analysis of modern ICs and need either fundamental restructuring or replacement with tools built by new principles. This also refers to gate-level simulation subsystems, embedded in systems of mixed-mode multilevel simulation. Therefore, it is necessary to develop gate-level simulation means, used autonomously or as part of mixed-mode simulators, since they are not adapted to consider DF effects.

The development of gate-level simulation and optimization tools with consideration of DFs has now become a decisive part in the progress of design automation of electronic circuits. Therefore, intensive work is underway to create fundamentally new gate-level simulation approaches and optimize digital ICs, allowing with the inherent speed of gate-level simulation and accuracy close to circuit-level simulation to reproduce the operation of digital ICs taking DFs into account.

However, despite the small progress, the successes in this direction are more than modest. There is no general theoretical approach to solve different aspects of the problem, which significantly reduces the effectiveness of the developed methods. Attempts are being made to solve the problem by partially using simpler but having nonlogical (often circuit-level) nature of models, which leads to disadvantages that are unacceptable from the viewpoint of design practice. There is no clear classification of DFs and their parameters. The main causes (e.g., the discrete nature of variables) of the inapplicability of existing gate-level simulation systems to consider DF effects are not eliminated.

There are a number of unresolved problems in both parametric and structural optimization of DCs, and there are simply no means of considering DFs in them.

Gate-level simulation and optimization of DCs with consideration of DFs requires a fundamentally new approach to develop such class of EDA tools.

This monograph is devoted to the description of the developed new principles for constructing such systems.

The author expresses deep gratitude to his teachers in science:

- Archangelsky Alexei Yakovlevich,

- Agakhanyan Tatevos Mamikonovich,

- Norenkov Igor Petrovich,

- Rusakov Sergey Grigorievich.

The author would also like to thank his colleague Ruzanna Goroyan who assisted in the preparation of this monograph.

### Contents

| 1                   | General Issues of Gate-Level Simulation and Optimization<br>of Digital Circuits with Consideration of Destabilizing Factors |                                                               |     |  |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----|--|--|

|                     | 1.1                                                                                                                         | Significance of DF Influence on Functioning of Modern Digital |     |  |  |

|                     | 1.1                                                                                                                         | Circuits                                                      | 1   |  |  |

|                     |                                                                                                                             | 1.1.1   External DF.                                          | 1   |  |  |

|                     |                                                                                                                             | 1.1.2 Internal DF.                                            | 32  |  |  |

|                     | 1.2                                                                                                                         | Analysis of the Current State of Simulation and Optimization  |     |  |  |

|                     |                                                                                                                             | of Digital Circuits in Terms of DF Consideration              | 53  |  |  |

|                     | 1.3                                                                                                                         | Requirements for Gate-Level Simulation Tools and Optimization |     |  |  |

|                     |                                                                                                                             | of Digital Circuits, Focused on DF Consideration              | 64  |  |  |

|                     | 1.4                                                                                                                         | Principles of Gate-Level Simulation and Optimization          |     |  |  |

|                     |                                                                                                                             | of Digital Circuits with Consideration of DF                  | 68  |  |  |

| 2                   | Mod                                                                                                                         | lels of Logical Elements for DF Consideration                 | 77  |  |  |

|                     | 2.1                                                                                                                         | Capabilities of MCE to Define Functional Failures             | 77  |  |  |

|                     | 2.2                                                                                                                         | Structure of the Model of Considering DF Effects (MCE)        | 83  |  |  |

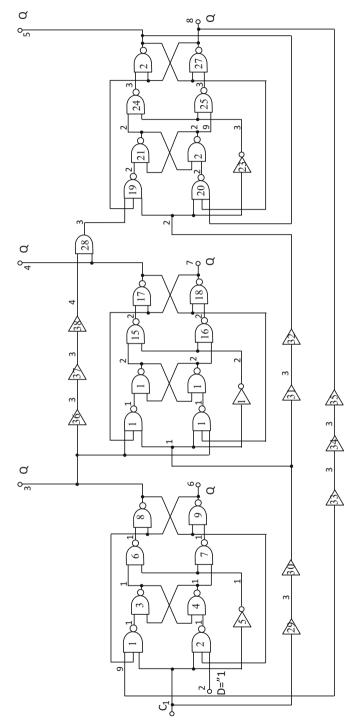

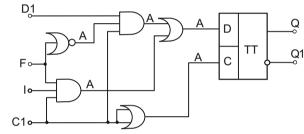

|                     |                                                                                                                             | 2.2.1 Logic Block of MGE                                      | 85  |  |  |

|                     |                                                                                                                             | 2.2.2 Inertia block of MGE                                    | 90  |  |  |

|                     | 2.3                                                                                                                         | Determination of Timing Parameters of the MCE                 | 117 |  |  |

|                     | 2.4                                                                                                                         | Research of Properties of the MCE                             | 124 |  |  |

| 3                   | Mod                                                                                                                         | lels for Determining the Influence of DF                      | 137 |  |  |

|                     | 3.1                                                                                                                         | Methodology for Constructing Models for Determining           |     |  |  |

| the Influence of DF |                                                                                                                             |                                                               |     |  |  |

|                     |                                                                                                                             | 3.1.1 The Basic Logic Cell TTL                                | 144 |  |  |

|                     |                                                                                                                             | 3.1.2 Basic Logical Cell ECL                                  | 148 |  |  |

|                     |                                                                                                                             | 3.1.3 Basic Logical Cell CMOS                                 | 150 |  |  |

|                     |                                                                                                                             | 3.1.4 Models of Interconnects                                 | 174 |  |  |

|                     |                                                                                                                             | 3.1.5 MDE Noise in Power Rails                                | 177 |  |  |

|                     | 3.2                                                                                                                         | Models of Noise in Power Lines                                | 184 |  |  |

|    | 3.3  | Calculation and Optimization of the Parameters of Models     |     |

|----|------|--------------------------------------------------------------|-----|

|    |      | for Determining the Influence of DF                          | 189 |

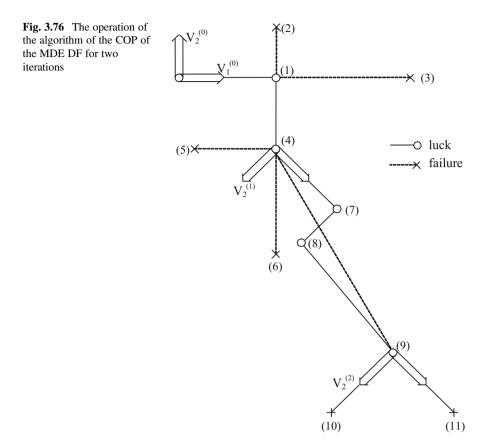

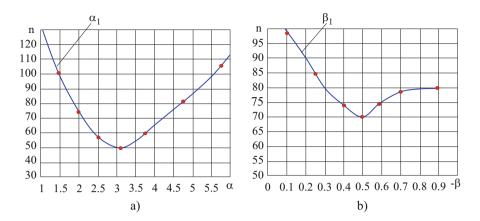

|    |      | 3.3.1 Description of the COP Algorithm of the MDE DF         | 194 |

|    |      | 3.3.2 An Example of the COP Algorithm of MDE DF              | 194 |

|    | 3.4  | Models of Circuits with Switched Capacitors                  | 200 |

|    |      | 3.4.1 Examples of the Use of Integrated Circuit Models       |     |

|    |      | on a SC                                                      | 206 |

|    |      | 3.4.2 Improving the Accuracy of Integrated Circuit Models    |     |

|    |      | on a SC                                                      | 210 |

| 4  |      | orithmic Implementation of the Automated System              |     |

|    | of G | ate-Level Simulation of Digital Circuits with Consideration  |     |

|    |      | <b>F</b>                                                     | 213 |

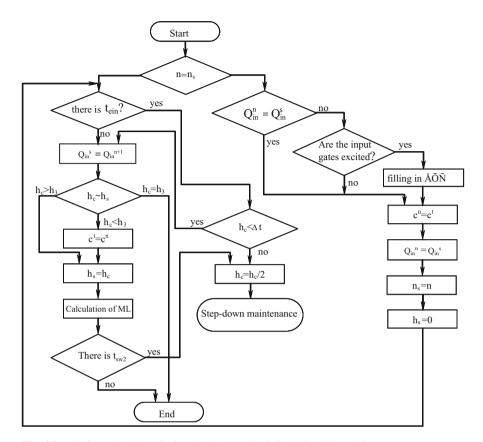

|    | 4.1  | Algorithm of Gate-Level Simulation of Digital Circuits       |     |

|    |      | with Consideration of DF                                     | 213 |

|    | 4.2  | Description of the Algorithm                                 | 226 |

|    | 4.3  | Simulation Example                                           | 230 |

|    | 4.4  | Mixed-Mode Simulation Algorithms with Consideration          |     |

|    |      | of DF                                                        | 230 |

| 5  |      | imization of Digital Circuits with Consideration of DF       | 247 |

|    | 5.1  | Optimization of Critical Timing Paths of Digital Circuits    |     |

|    |      | with Consideration of DF                                     | 247 |

|    | 5.2  | Algorithm for Optimization of Critical Timing Paths          |     |

|    |      | of Digital Circuits with Consideration of DF                 | 262 |

|    | 5.3  | An example of Optimization of Critical Timing Paths          |     |

|    |      | of Digital Circuits with Consideration of DF                 | 263 |

|    | 5.4  | Optimization of Power Consumption of Digital Circuits        |     |

|    |      | with Consideration of DF                                     | 289 |

| 6  | Ling | guistic and Software Development of the Automated System     |     |

|    | of G | ate-Level Simulation of Digital Circuits with Consideration  |     |

|    | of D | <b>F</b>                                                     | 301 |

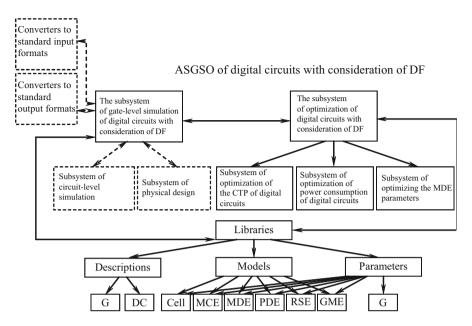

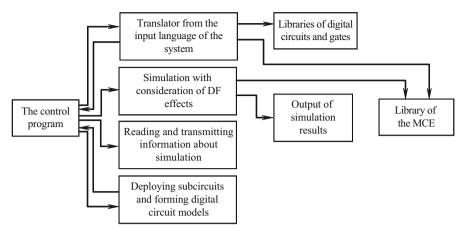

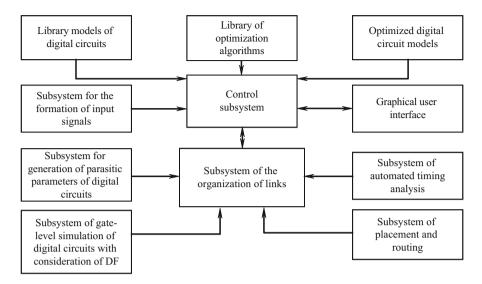

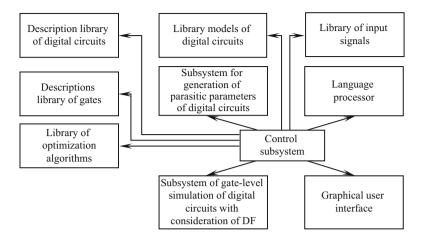

|    | 6.1  | Software Structure                                           | 301 |

|    | 6.2  | Linguistic Development                                       | 306 |

|    | 6.3  | System of Programs of Gate-Level Simulation and Optimization |     |

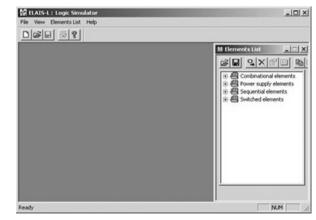

|    |      | of Digital Circuits with Consideration of DF of ELAIS-L      | 312 |

|    | 6.4  | Description of the Input Language of ELAIS-L                 | 317 |

|    |      | 6.4.1 Description According to the Backus-Naur Form          | 317 |

|    |      | 6.4.2 Informal Description                                   | 326 |

| In | dev  |                                                              | 343 |

|    | uun. |                                                              | 575 |

### **Chapter 1 General Issues of Gate-Level Simulation and Optimization of Digital Circuits with Consideration of Destabilizing Factors**

#### 1.1 Significance of DF Influence on Functioning of Modern Digital Circuits

Digital circuits (digital ICs, digital fragments of mixed-signal ICs and systems based on them) [1, 2] operate in the environment of different destabilizing factors (DFs) [3–15], which significantly influence their behavior and often disrupt the normal operation [16–19].

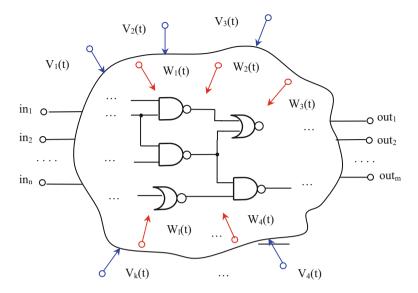

According to the place of application, DFs can be classified into external and internal. Modern digital circuits function in the environment shown in Fig. 1.1 where  $V_i(t)$ , i = 1, 2, ..., k-external, and  $W_j(t)$ , j = 1, 2, ..., l-internal DFs, and k and l are the numbers of different types of DFs.

The degree of influence of different DFs on the functioning of digital circuits is different. Studies [2, 4, 20–40] show that at the present stage of the development of circuitry and the technology of fabricating digital circuits, the most significant effect is the influence of DF, given in Table 1.1.

Features of the presented DF types from the point of view of their significance on the distortion of circuit signals are shown below.

#### 1.1.1 External DF

In this section the significance, mechanisms of the influence of radiation  $(V_1)$  on the operation of digital circuits, and the methods used to reduce the effect of DF of this type are relatively presented in detail. For the other types of external DFs, only the issue of their significance on the operation of digital ICs is considered, since the mechanisms and methods of combating them are well known.

The issue of the influence of radiation on the behavior of digital circuits has been studied by many groups of authors, among which the works of [3, 4, 16, 17, 20, 21,

<sup>©</sup> Springer International Publishing AG, part of Springer Nature 2018

V. Melikyan, *Simulation and Optimization of Digital Circuits*, https://doi.org/10.1007/978-3-319-71637-4\_1

Fig. 1.1 Environment of functioning of a digital circuit

| According to the place of application of DF | According to the nature of DF                        | Symbol                |

|---------------------------------------------|------------------------------------------------------|-----------------------|

| External                                    |                                                      |                       |

| External                                    | Radiation exposure                                   | $V_1$                 |

|                                             | Ambient temperature                                  | V <sub>2</sub>        |

|                                             | Non-ideality of power source                         | $V_3$                 |

|                                             | Non-ideality of input signal source                  | $V_4$                 |

|                                             | Non-ideality of load                                 | $V_5$                 |

|                                             | Electromagnetic field                                | $V_6$                 |

|                                             | Mechanical impacts (vibration, strike, acceleration, | V7                    |

|                                             | etc.)                                                |                       |

|                                             | Climatic conditions (humidity, atmospheric pres-     | $V_8$                 |

|                                             | sure, etc.)                                          |                       |

| Internal                                    | Non-ideality of interconnects                        | $W_1$                 |

|                                             | Non-ideality of power rails                          | $W_2$                 |

|                                             | Features of the internal structure of the circuit    | <i>W</i> <sub>3</sub> |

|                                             | (number of loads, etc.)                              |                       |

|                                             | Distorted input signal form of the element           | $W_4$                 |

Table 1.1 Classification of DF

41–58] are particularly distinguished by the depth of the study of the significance of the effect of this type of DF on the operation of digital ICs.

Digital circuits function in the radiation environment and are subject to its influence [3, 17, 20, 21, 41, 42, 46, 48, 49, 59, 60], which occurs as follows: the charged particle passes through the substance of digital IC, loses energy in the interaction with an atomic lattice, the energy lost by the charged particle is

transferred to the bound electrons, as a result of which ionization occurs, new electron-hole pairs are formed [61, 62].

Thus, particles of ionizing radiation passing through the components of digital IC interact with the atoms of IC substance and transmit their energy to them. The further propagation of this energy in the volume of IC leads to different radiation effects.

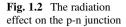

These effects are manifested [41, 43, 48] in the form of changes in the parameters and characteristics of separate semiconductor devices of digital circuits (transistors, diodes, passive components, etc.) (Fig. 1.2) [61]. As a result, the integrated parameters and characteristics of entire digital circuits change. The behavior of digital circuits in processing the same input signals depends on the parameters of surrounding radiation environment. With the development of IC manufacturing technology, the role of the influence of radiation on the behavior of digital circuits is continuously increasing [3, 20, 41, 47]. This is due to the fact that over time, the geometric sizes of semiconductor devices of digital ICs and, as a result, capacities decrease [1, 2, 31, 63–66]. At the same time, the values of the supply voltage of digital circuits and the power consumption are also reduced [67-70]. Due to the noted reasons for storing useful information, less charge or current is required. However, in this case, the digital circuit becomes more sensitive to radiation, since the ratio of the induced charge of the ionizing particle to the charge necessary for storing useful information increases [21, 41, 48]. Thus, ionizing particles with lower energy, which could previously be ignored by digital circuits, can cause radiation damage and failures in modern digital ICs.

Table 1.2 shows the classification of the most significant radiative effects for digital circuits, based on generalization of research results [3, 16, 20, 41, 42, 48–50, 52, 55, 58, 61].

According to [41, 47, 48, 62], during radiation of digital IC, the characteristics of their active and passive devices change, which, in turn, leads to failures of ICs of two types:

- Long-term (residual)

- Short-term (transitional)

These two groups differ from each other in the nature of the processes occurring in the circuit, in terms of their duration, as well as in parameters characterizing the size of their influence on digital circuits.

Long-term radiation damage in digital ICs is caused by displacement and ionization effects [3, 41, 48, 52]. Due to displacement effects, the lifetime, mobility and carrier concentrations change, leading to a change in the parameters of electronic

| Classification 1                                          | Kind of radiation effect                                                                                                                               | Classification 2                     | Kind of<br>radiation<br>effect |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------|

| By the nature of physical processes                       | Displacement (displacement<br>of atoms in the crystal lattice,<br>leading to radiation defects)                                                        |                                      |                                |

|                                                           | Ionization (ionization of sub-<br>strate by radiation,<br>i.e. formation of free charge<br>carriers)                                                   |                                      |                                |

| By the nature of power flux                               | Uniform                                                                                                                                                |                                      |                                |

|                                                           | Heterogeneous                                                                                                                                          |                                      |                                |

|                                                           | Equilibrium                                                                                                                                            |                                      |                                |

|                                                           | Nonequilibrium                                                                                                                                         | -                                    |                                |

| Due to occurrence                                         | Primary, caused directly by<br>radiation energy that is<br>absorbed by a digital circuit<br>(displacement defects, con-<br>ductivity modulation, etc.) |                                      |                                |

|                                                           | Secondary, caused by the<br>auxiliary radiation, redistribu-<br>tion of energy (radiative<br>latching, secondary photocur-<br>rent, breakdown, etc.)   |                                      |                                |

| By the ratio between the                                  | Residual, long-term                                                                                                                                    |                                      |                                |

| duration of the exposure to                               | Transitional, short-term                                                                                                                               | On the conse-                        | Recoverable                    |

| radiation $T_{\rm i}$ and the relaxation time $T_{\rm p}$ |                                                                                                                                                        | quences of tran-<br>sient ionization | Non-<br>recoverable            |

|                                                           |                                                                                                                                                        | currents                             | Destructive                    |

Table 1.2 Classification of radiation effects, important for digital circuits

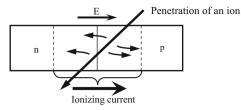

components of digital ICs. Because of ionization, charges in dielectric layers accumulate (Fig. 1.3) [61], which also lead to a change in the parameters of components of digital circuits.

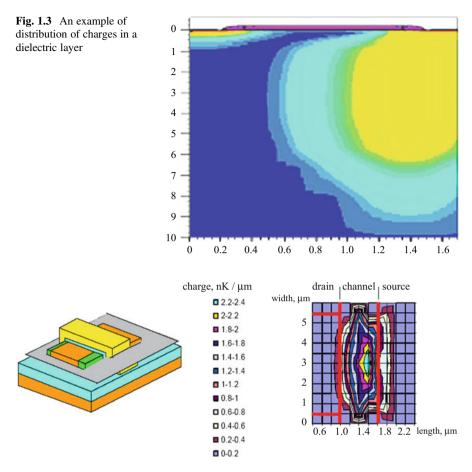

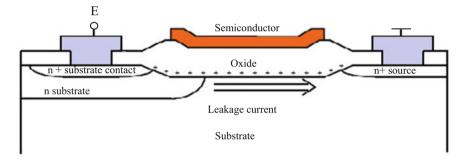

For example, the accumulation of a positive charge in a dielectric can lead to the formation of inverse channels in p regions of bipolar transistors that cause the occurrence of uncontrolled current components [3, 41, 48], and the change in the parameters of CMOS transistors is mainly associated with the formation of a positive charge in the layer of the gate dielectric (Fig. 1.4) [62], modeling the channel conductivity of a given type of transistor [20].

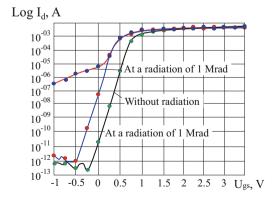

This, in turn, causes a change in the threshold voltage of the transistor, occurrence of parasitic channels, changes in carrier mobility, etc. These phenomena lead to a change in the parameters of the device, which, in turn, can cause its functional damage. As seen from Fig. 1.5 [56], which shows the dependence of the drain current of the n-MOS transistor on the gate-source voltage in the presence and absence of radiation, the increase of the pre-threshold currents is obvious. As a result of irradiation, the leakage currents of the transistor can become commensurate

Fig. 1.4 An example of the distribution of charges in a layer of a gate dielectric of an MOS transistor

**Fig. 1.5** Dependence of the drain current of the n-MOS transistor on the gate-source voltage in the presence and absence of radiation (technology— $0.7 \mu m$ , *W*/L = 2000/1.5)

with the operating currents. In the study and calculation of residual radiation effects, all components of the radiation environment (heavy ions, protons, etc.) are represented by unit dose (rad), and the summary dose is used as the key calculation parameter [41].

Short-term radiation effects are caused by the appearance of ionization currents in the volume of digital ICs, causing a change in the state of digital circuits with a short duration, and sometimes causing damage to it [47, 53]. At the same time, the minimum power of the absorbed radiation dose is several orders of magnitude lower than that required for digital IC failures due to thermodynamic effects [41, 47, 48]. The environment that generates transient radiative effects can consist of particles of various types (protons, heavy ions, etc.). Since the forms of interaction of these particles with the IC substance have different character, the models for describing the transient radiative effects for them are also different. Heavy ions, penetrating the sensitive areas of digital ICs, lead to direct ionization.

Generation of one electron-hole pair in a semiconductor requires about 3.6 eV of energy, while an ionizing particle can have energy up to 4 ... 9 MeV [61].

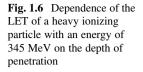

For this reason, the linear energy transfer (LET), measured in MeV-cm<sup>2</sup>/mg [41, 62] and decreasing as a function of penetration depth (Fig. 1.6) [61], is used as the characterizing parameter of the radiation environment with heavy ions.

In case of protons, ionization in sensitive regions is mainly formed indirectly. As a result of the collision of a proton with high energy, with the substance of digital IC, a secondary ion is formed leading to ionization. In this case, the proton energy, which characterizes the excitation of the secondary ion, is used as the main parameter of the radiation environment. In rare cases, when the LET threshold for the electronic component of a digital IC is too low (LET <1 MeV-cm<sup>2</sup>/mg), protons can form a direct ionization [41, 42, 61].

In such cases, it is convenient to use the proton LET as the determining parameter of the size of the influence of the radiation environment. Depending on the type of particle, its energy, and the type of semiconductor device exposed, transient radiation effects can lead to various disruptions in the operation of the digital IC. These violations by nature are divided into three groups [4, 41, 48, 62]:

- 1. Recoverable (light) failures. Radiation induces a fault in one bit of a digital circuit. Failures of this type can be fixed by resetting the system or by overwriting the data in digital circuits. This category includes:

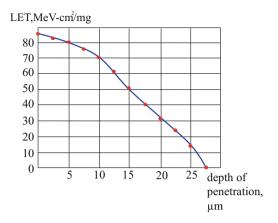

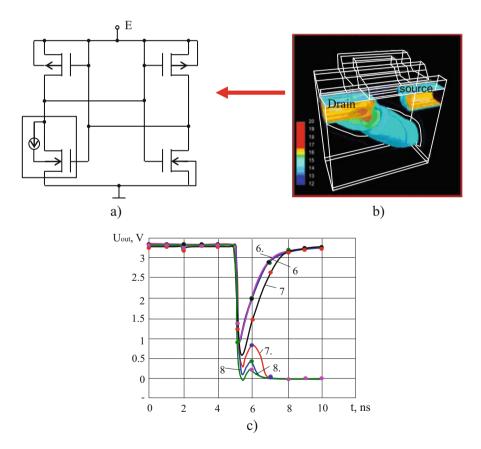

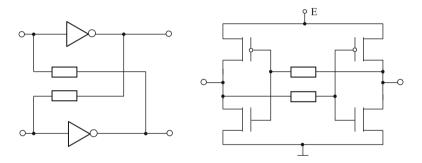

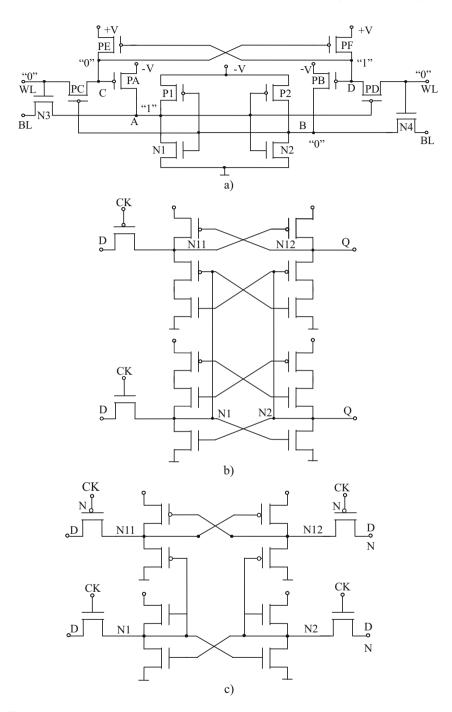

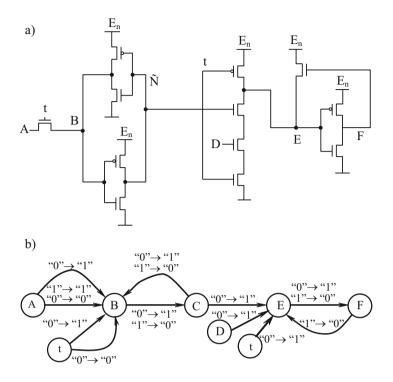

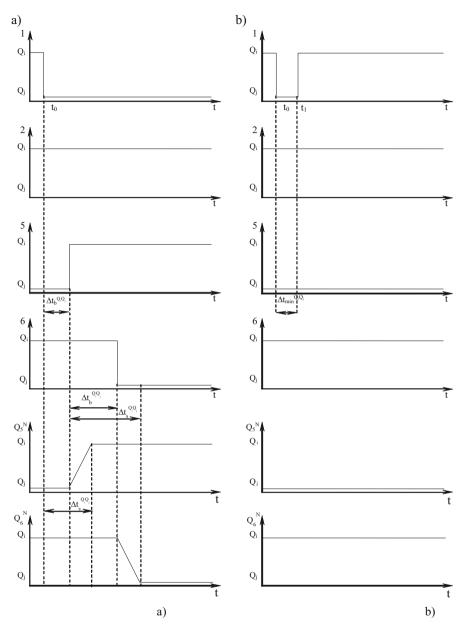

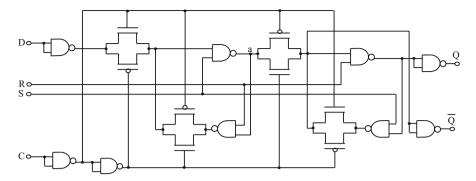

- Single switching, when particle with high energy, passing through the sensitive area of the cell (for example, memory cells), forms accumulation of charges, leading to switching of the state of the cell (memory cell). In the static CMOS memory cells, which are two inverters covered by feedbacks (Fig. 1.7a), the sensing nodes are the drains of transistors (Fig. 1.7b). If the LET of the penetrating particle exceeds the critical value for this cell, this results in a single switching in the device (Fig. 1.7c).

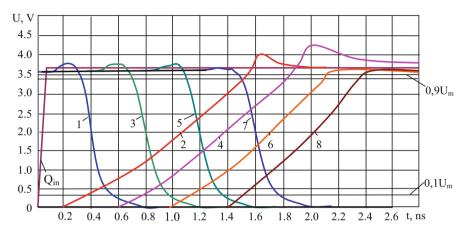

**Fig. 1.7** Single switching of the static CMOS cell (a) the scheme of the affected static CMOS cell; (b) accumulated charge in the drain area of CMOS transistor; (c) the output voltage of the static CMOS cell at different energy values of ionizing particle  $(6 \dots 8.5 \text{ MeV})$

| Device type         | Sensitive area                                                  | Type of recoverable failure                                                          |  |

|---------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------|--|

| Memory              | Memory cells                                                    | A bit switch                                                                         |  |

|                     | Control device                                                  | Switching the bit into sequential and false short-term pulses in combinational parts |  |

| Combinational logic | Combinational logic                                             | False short-time pulses                                                              |  |

| Sequential logic    | Sequential logic                                                | A bit switch                                                                         |  |

| Microprocessors     | Registers, cache memory,<br>sequential logic, control<br>device | A bit switch                                                                         |  |

|                     | Combinational logic                                             | False short-time pulses                                                              |  |

Table 1.3 Classification of single recoverable errors by device types and their sensitive areas

- Multi-bit switching, having a similar mechanism, but leading to simultaneous switching of several bits of the device. Charge accumulation in various nodes of digital ICs can be formed by means of one or several particles simultaneously.

- A single functional failure, which is a special case of a single switching. In complex memory devices, memory cells and external circuits are connected to other devices, designed to perform additional functions, for example, to detect and fix errors. If an ionizing particle affects the circuit of this type, then the normal functioning of the entire cell is disrupted.

Table 1.3 shows the classification of single recoverable errors by device types and their sensitive areas.

2. Non-recoverable failures. This category includes permanent errors. An example of an error of this type is the non-recoverable failure of one digital circuits bit.

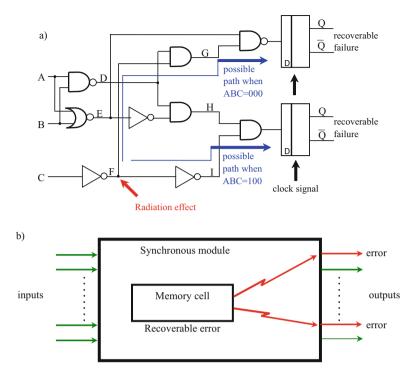

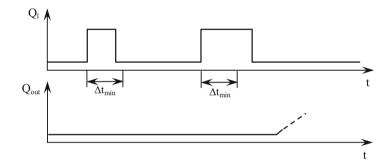

It should be noted that for the same radiation exposure of the same digital circuit, both recoverable (Fig. 1.8a) and non-recoverable (Fig. 1.8b) failures can occur [62]. The reason is that the accumulation of charges as a result of transferring the ionizing particle generates a transient noise impulse, competing with normal synchronized signals in digital circuits.

The resulting effect depends on: the vulnerability of the affected node of a digital circuit, the activity of combinational logical paths of signal propagation in a digital circuit, the propagation delay in the signal path, the dynamic parameters of latches and flip-flops in a digital circuit, and many other circuit-level and technological features of implementing a digital circuit.

If a false signal disappears with time, then a recoverable error is obtained; if a single switch results in a permanent error at the output of the circuit, a non-recoverable error is obtained.

- 3. Destructive failures (DR). This category includes:

- Single "latching." This phenomenon is specific for CMOS circuits. It is associated with the opening of a parasitic pnpn thyristor under certain

Fig. 1.8 Recoverable (a) and non-recoverable (b) failures of digital circuits

conditions. This leads to a short circuit of the power source, which generates large currents, capable of disabling digital circuits. The cause of this phenomenon, in addition to electrical overloads [71, 72], can also be the penetration of an ionizing particle.

- Single "unwinding." This phenomenon is also based on parasitic feedback. However, in this case, the presence of a parasitic pnpn thyristor is not mandatory. It occurs when a parasitic npn transistor is opened in an n-MOS transistor with a large drain current, and a feedback is formed under the influence of the penetrating particle. This phenomenon occurs mainly at high values of the supply voltage.

- Single breakdown of the gate. In this case, the penetrating ionizing particle leads to a breakdown of the gate oxide of a CMOS transistor. This phenomenon is typical for electronic components in which a large electric field is formed in the oxide layer.

- A single heavy error. In this case, the high-energy particle passes through the gate oxide and leads to displacements of the threshold voltage.

- Single burning. This phenomenon occurs in power MOS transistors, where

parasitic bipolar transistors are present. Under the influence of the ionizing

particle, the parasitic transistor opens. The resulting high currents and power

can lead to the melting of the transistor.

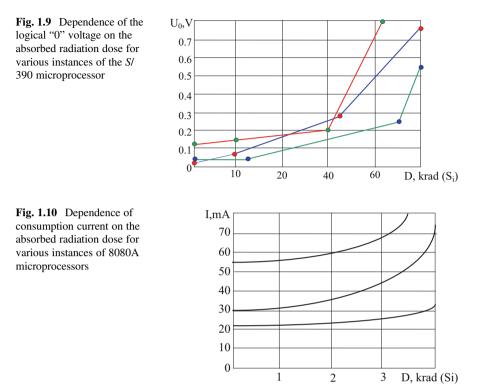

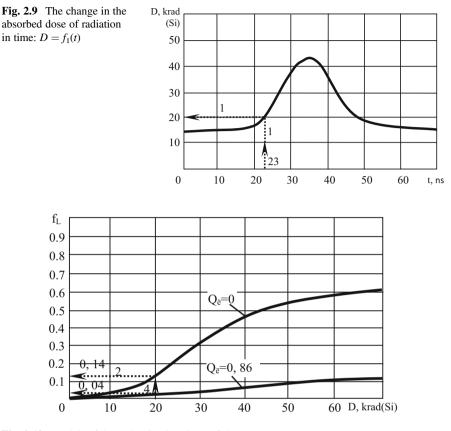

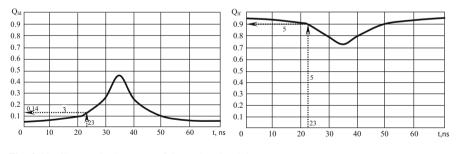

According to [48], radiation affects the static, dynamic, and functional parameters of digital ICs. The static parameters of digital circuits are mainly influenced by the particle fluence  $\varphi$  or the absorbed radiation dose D, and the dynamic parameters— power of absorbed dose P. The functional parameters of the digital IC depend on all of the above written characteristics of irradiation. The most sensitive to radiation exposure, the static parameters of digital circuits are the levels of logical signals "0" and "1." For example, according to [48], the logical "0" level at the internal nodes of the *S*/390 microprocessor, depending on the absorbed dose of radiation, changes as shown in Fig. 1.9.

It is not difficult to see that even for small values of radiation, the level of  $U_{\rm o}$  can vary by more than an order of magnitude. The level of radiation, according to [41, 48], greatly affects the amount of current consumed from the power source, which, in turn, determines all modes of operation of the digital IC. As an example, Fig. 1.10 shows the dependencies of the current consumed by the microprocessor 8080A (manufactured by n-MOS technology by different companies) on the absorbed radiation dose [44]. As seen from the charts, depending on the absorbed dose of radiation, the power consumption varies several times, which, undoubtedly, leads to various failures in the circuit operation.

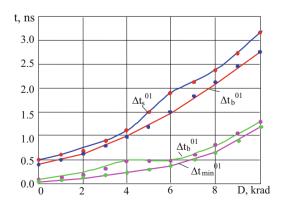

The effect of radiation exposure on the inertia (in particular, on signal propagation delay) of the logic gates of digital ICs is due to a change in the parameters of active

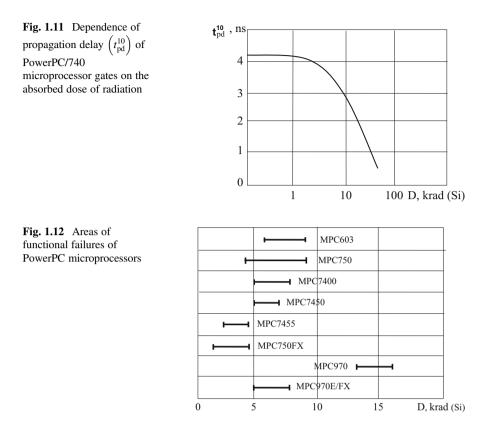

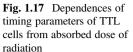

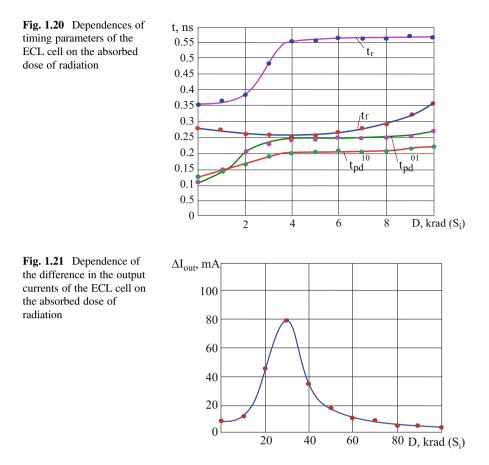

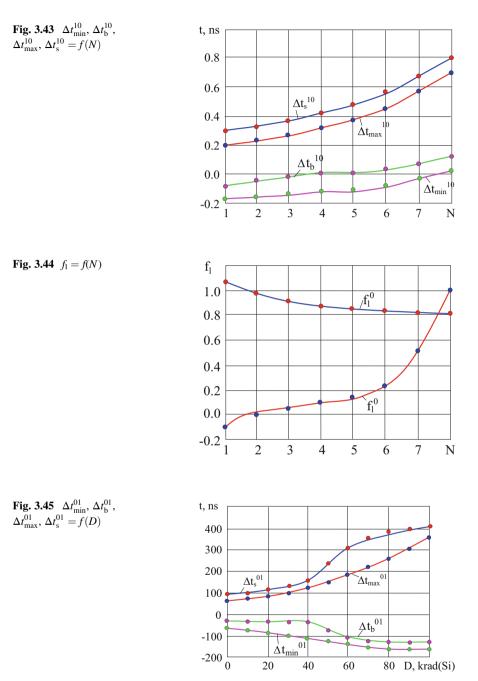

elements and passive regions of semiconductor structures, as well as an increase in leakage current. According to the data of [3], changes in timing parameters can sometimes reach up to several orders, and, depending on IC fabrication technology, the gate delay can both increase and vice versa. For example, Fig. 1.11 shows the time dependence of propagation delay  $\left(t_{\rm pd}^{10}\right)$  of the PowerPC/740 microprocessor gates from the absorbed radiation dose (*D*). As seen from the chart, the dependence is significant.

To represent the significance of radiation effect on functional parameters of digital ICs, as an example, a diagram of functional failures of some PowerPC microprocessors [73] is illustrated on Fig. 1.12.

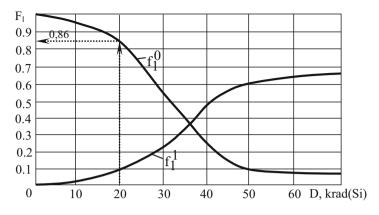

It can be seen from the diagrams that functional failures, which are a consequence of changes in the static and dynamic parameters of IC gates, appear even in case of insignificant values of radiation exposure (Figs. 1.13, 1.14, and 1.15).

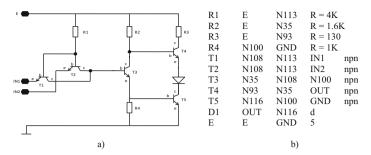

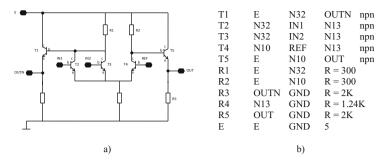

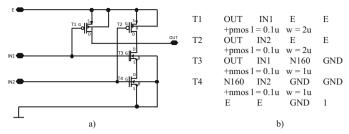

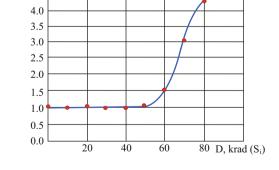

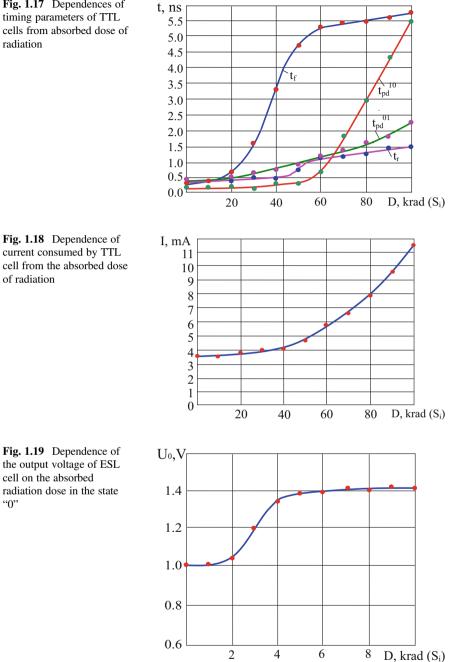

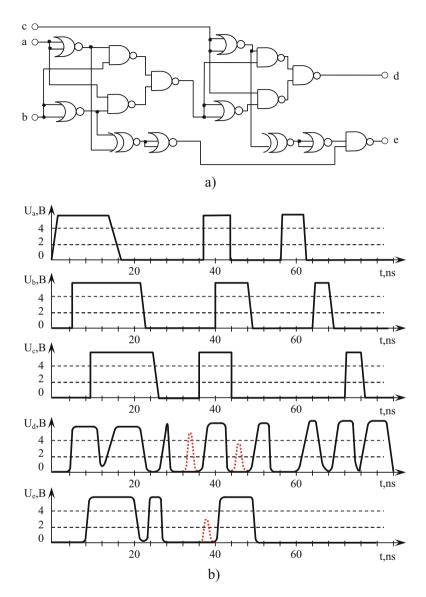

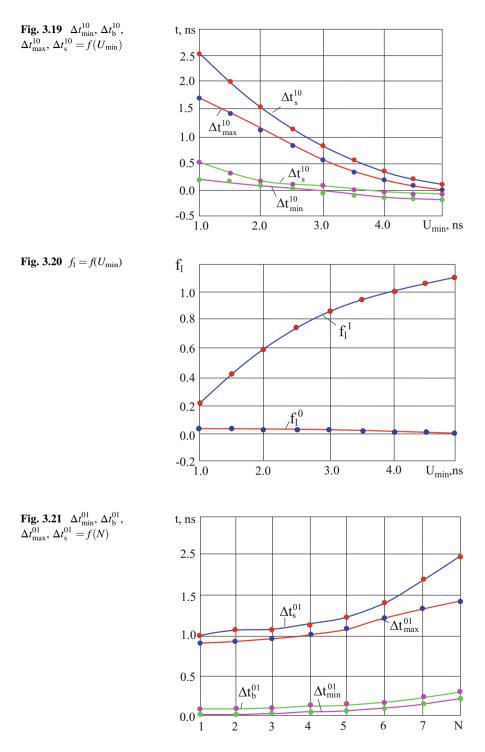

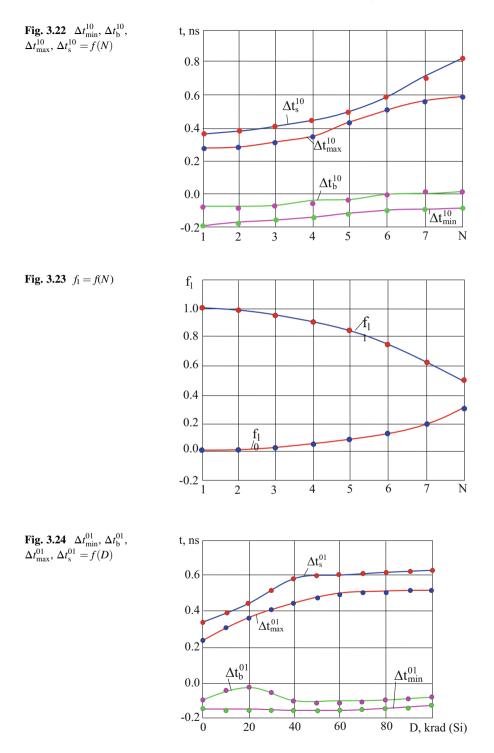

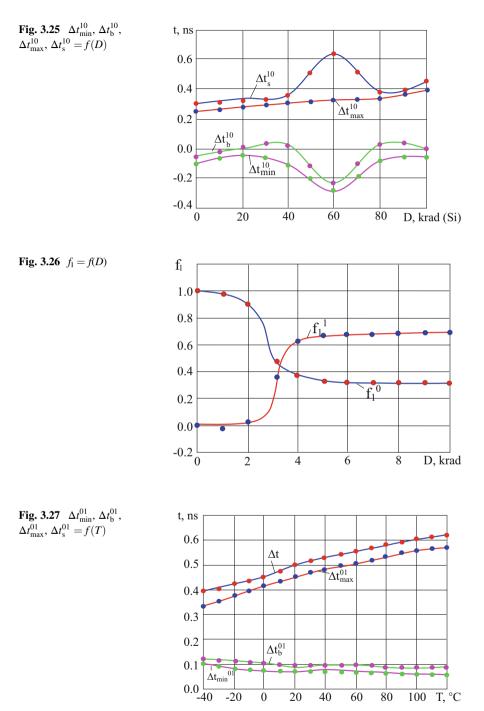

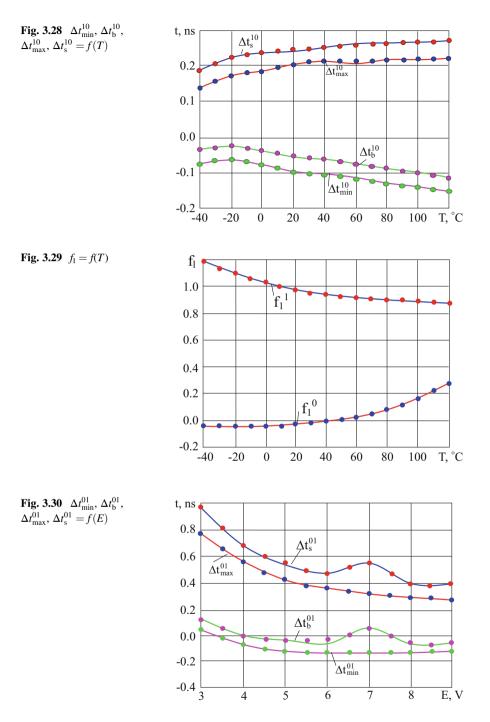

Figures 1.16, 1.17, and 1.18 show different dependencies for the standard TTL cell (Fig. 1.13), and Figs. 1.19, 1.20, and 1.21—for the ECL cell (Fig. 1.14) obtained by simulating these circuits using the SPICE circuit simulator [74, 75]. These charts also confirm the strong dependence of digital circuit parameters on radiation.

MODEL NPN NPN (LEVEL=1 BF=42 NF=0.995 IS=2.2E-17 ISC=2.2E-17 ISE=2.2E-17 +NE=1.45 RB=151.4797694 IRB=1.791514E-4 RBM=1.3776E-3 RE=1.16 IKF=1.257515E-3 +NKF=0.59 VAF=210.8833929 BR=0.0108 NR=1 NC=1.0645678 RC=20.2 IKR=8.978E-3 +VAR=9.95 TBF1=5.5E-3 TBF2=-2E-6 TNE1=-2.88029E-4 TNE2=8.875512E-5 +TNF1=-1.534813E-4 TNF2=1.449935E-6 TRB1=1E-4 TIRB1=4.485779E-7 +TRM1=9.44068E-6 TRE1=2.130384E-5 TIKF1=-5.73196E-3 TIKF2=2.523403E-5 +TVAF1=-6.950157E-5 TBR1=1E-4 TBR2=5E-6 TNR1=1E-5 TNR2=-1E-6 TNC1=1E-4 +TNC2=-1.1E-6 XTB=0 XTI=3 TRC1=1E-3 TIKR1=-8.9251E-3 EG=1.18 + CJE=1.353304E-13 VJE=0.941157 MJE=0.4592962 FC=0 CJC=9.430542E-14 +VJC=0.5445709 MJC=0.2932769 TLEVC=1 CTE=8.658836E-4 CTC=1.571976E-3 +TVJE=1.189865E-3 TVJC=3.303052E-3 TREF=25 SUBS=1 TLEV=0) \* .ENDL BIP

c)

The frequency of input pulses is 100 MHz, the duration of rise and fall times of input signal is 0.5 ns, the ambient temperature is  $25^{\circ}$  C, the number of loads is 4.

d)

Fig. 1.13 Standard TTL cell. (a) circuit, (b) SPICE description, (c) parameters of the transistor model, (d) nominal operating conditions

Due to the importance of the effect of radiation on the functioning of modern digital IC, various methods are used to increase their resistance to this type of DF. The classification of digital circuits on radiation hardness is also known [46] (Table 1.4).

There are three ways to increase the hardness of CMOS digital circuits to radiation:

- 1. Improvement of technological process. By changing some technological parameters (for example, by improving the quality of the gate oxide of a CMOS transistor) and steps, it is possible to increase the radiation hardness of digital ICs [54].

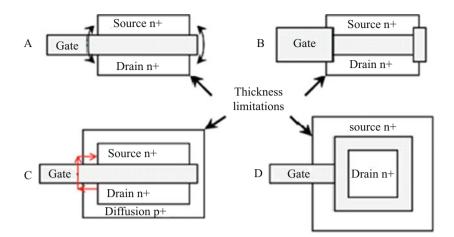

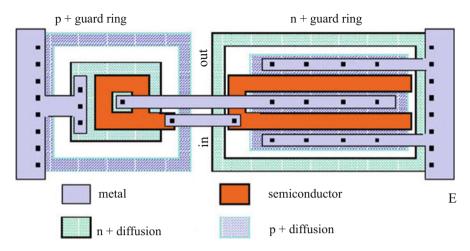

- 2. The use of special topological solutions that allow to some extent solve the problems of increasing static currents and eliminating a single "latching," and also reducing the sensitivity to single switching. Figure 1.22 [56] shows various topological implementations of an n-MOS transistor, which to some extent prevent the increase of parasitic leakage currents. From this point of view, the most acceptable variant is *D*, known as the "Transistor with Protected Topology" (TPT).

However, in this case, there are some difficulties associated with large transistor sizes, with large values of drain and source capacitance, and also with the choice of the W/L ratio. Despite the mentioned shortcomings, TPT has wide practical

.MODEL NPN NPN (LEVEL=1 BF=42 NF=0.995 IS=2.2H7 ISC=2.2E17 ISC=2.2E17 +NE=1.45 RB=151.4797694 IRB=1.791514E-4 RBM=1.3776E-3 RE=1.16 IKF=1.257515E-3 +NKF=0.59 VAF=210.8833929 BR=0.0108 NR=1 NC=1.0645678 RC=20.2 IKR=8.978E -3 +VAR=9.95 TBF1=5.5E -3 TBF2=-2E-6 TNE1=-2.88029E-4 TNE2=8.875512E-5 +TNF1=-1.534813E-4 TNF2=1.449935E-6 TRB1=1E-4 TIRB1=4.485779E-7 +TRM1=9.44068E-6 TRE1=2.130384E-5 TIKF1=-5.73196E-3 TIKF2=2.523403E-5 +TVAF1=-6.950157E-5 TBR1=1E-4 TBR2=5E-6 TNR1=1E-5 TNR2=-1E-6 TNC1=1E-4 +TNC2=-1.1E-6 XTB=0 XTI=3 TRC1=1E-3 TIKR1=-8.9251E-3 EG=1.18 +CJE=1.353304E-13 VJE=0.941157 MJE=0.4592962 FC=0 CJC=9.430542E -14 +VJC=0.5445709 MJC=0.2932769 TLEVC=1 CTE=8.658836E-4 CTC=1.571976E-3 +TVJE=1.189865E-3 TVJC=3.303052E-3 TREF=25 SUBS=1 TLEV=0) \* .ENDL BIP

The frequency of the input pulses is 100 MHz, the duration of rise and fall times of input signal is 0.3 ns, the ambient temperature is  $25^{\circ}$  C, the number of loads is 3.

Fig. 1.14 Standard ESL cell. (a) circuit, (b) SPICE description, (c) parameters of the transistor model, (d) nominal operating conditions

application. Figure 1.5 shows the advantage of TPT in relation to the usual topology of an MOS transistor. With the help of topological solutions, it is also possible to reduce leakage currents between separate semiconductor devices (Fig. 1.23 [56]). Figure 1.24 [56] illustrates an example of the topology of a rad-hard CMOS inverter, which allows reducing the mentioned currents.

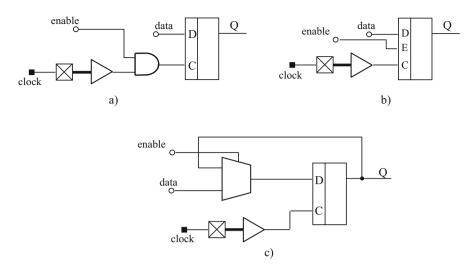

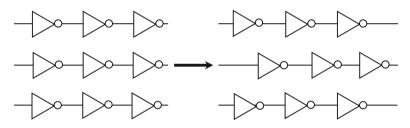

3. Selection of special circuit architectures, less sensitive to changes in the parameters of circuit components as a result of radiation exposure. For a digital circuit to become more resistant to long-term radiation effects, various means can be used. One of such means is simulation of changes in some parameters (threshold voltage, conductivity, etc.) of transistors and obtaining their dependencies on the total radiation dose. Such simulation allows predicting the impact of general dose on the behavior of digital circuits and, based on this, design a digital circuit. There are several ways to increase the hardness to short-term radiation effects [17, 45–48, 53, 54, 56]. For example, a single switching can be prevented by changing the critical value of the charge or by filtering the transition signals resulting from exposure to a high-energy particle. Such an example is shown in Fig. 1.25 [56]. Figures 1.26 and 1.27, respectively, illustrate examples of rad-hard memory cells [56], and also circuit-level solutions for synchronizing circuits to increase radiation hardness [46].

.MODEL nmos NMOS (LMIN=1.0E-07 LMAX='2.4000E-07-dxl' WMIN='1.0000E-06-dxw' +WMAX='1.0000E-05-dxw' LEVEL=54 VERSION=4.2 BINUNIT=2 PARAMCHK=1 +MOBMOD=0 CAPMOD=2 IGCMOD=1 IGBMOD=1 DIOMOD=1 RDSMOD=0 +RBODYMOD=0 RGATEMOD=0 PERMOD=1 ACNOSMOD=0 TRNOSMOD=0 +TNOM=25 TOXE='toxn' TOXM='toxn' DTOX=3e -010 EPSROX=3.9 WINT=6e-009 +LINT=2.5e-009 LL=0 WL=0 LLN=1 WLN=1 LW=0 WW=0 LWN=1 WWN=1 LWL=0 +WWL=0 LLC=0 WLC=0+LWC=0 WWC=0 LWLC=0 WWLC=0 DLC=1.172e -008 DWC=0 +XPART=1 TOXREF=3e -009 DLCIG=2.5e-009 XL='-3.5E-08+dxl' XW='1.5e-8+dxw +VTH0='0.22744278+dvthn' WVTH0='5.5738939e -009+dwvthn' LVTH0 = '0+dlvthn' +PVTH0='0+dpvthn' K1=0.32433703 LK1=-2.4740667e-010 WK1=-1.2374044e-008 +PK1=2.4748089e-015 K2=-0.011014366 LK2=1.2028732e-009 WK2 = 3.4532661e-009 +PK2=-6.9065323e-016 K3=-2.9571429 LK3=1.5428571e-008 K3B=1.2 W0=-5e-008 +DVT0=13.9 DVT1=1.25 DVT2=0 DVT0W=0 DVT1W=0 DVT2W=0 DSUB=0.5 MINV=0+VOFFL=0 DVTP0=4e-007 DVTP1=1.5714286 LDVTP1=8.5714286e-008 LPE0=4.45e-008 +LPEB=0 XJ=1.5e-007 NGATE=4e020 NDEP=8.3687e017 NSD=1e020 PHIN=0 CDSC=0 +CDSCB=0 CDSCD=0 CIT=-0.00012285714 LCIT=2.2457143e-010 VOFF=-0.11586017 +LVOFF=-2.4718229e-009 WVOFF=-1.6403173e-008 PVOFF=1.318624e-015 +NFACTOR=0.5 ETA0=0.22133733 WETA0= -1.3377345e-008ETAB=-0.1 +U0=0.045463996 LU0=-5.1444e-010 WU0=-1.2300788e-008 PU0=5.1598332e-016 +UA=-6.284e-010 UB=2.2915951e-018 LUB=-9.1553714e-027 WUB=-1.0877056e-024 +PUB=4.185198e-032 UC=2.4114338e-010 LUC=-4.1075238e-019 WUC=-1.3447417e-016 +PUC=4.1087561e-024 VSAT=114000 A0=2.375 AGS=0.95 A1=0 A2=1 B0=0 B1=0 +KETA=-0.044142857 LKETA=3.4285714e -009 DWG=0 DWB=0 PCLM=0.84 PDIBLC1=0 +PDIBLC2=1,4285714e-005 LPDIBLC2=1,7142857e-011 PDIBLCB=0 DROUT=0 +PVAG=1.5 DELTA=0.0075 PSCBE1=9.264e008 PSCBE2=1e-020 FPROUT=200 PDITS=0 +PDITSD=0 PDITSL=0 RSH=10.5 RDSW=140 PRWG=0 PRWB=0 WR=1 ALPHA0=0 +ALPHA1=0.03 BETA0=8.7 AGIDL=9e -008 BGIDL=2.3e009 CGIDL=0.5 EGIDL=0.53 +AIGBACC=0.01134 BIGBACC=0.003249 CIGBACC=0.1416 NIGBACC=4.05 +AIGBINV=0.35 BIGBINV=0.03 CIGBINV=0.006 EIGBINV=1.1 NIGBINV=1 +AIGC=0.010347143 LAIGC= -9.4285714e-012 +BIGC=0.001525 CIGC=0 +AIGSD=0.0083547333 LAIGSD=5.716e-012 WAIGSD=9.5552467e-011 +PAIGSD=-5.733148e-018 BIGSD=0.0004021 CIGSD=0.001463 NIGC=1 POXEDGE=1 +PIGCD=2.3 NTOX='ntoxn' XRCRG1=12 XRCRG2=1 CGSO='cgon' CGDO='cgon' +CGBO=0 CGDL='cgln' CGSL='cgln' CLC=1e-007 CLE=0.6 CF='cfn' CKAPPAS=0.6 +ACDE=1.2 +MOIN=12.6 NOFF=1.686 VOFFCV= -0.05472 KT1=-0.2624 LKT1=-1.62e-009 +KT1L=0 KT2=-0.04464 UTE=-1.5502921 LUTE=1.1143371e-008 WUTE=7.437167e-008 +PUTE=-1.7199444e-015 UA1=2.684e-009 UB1=-3.673e-018 UC1=-6.421e-011 PRT=0 +AT=35357.143 LAT=0.0019285714 JSS=1.77E -07 JSWS=4.23E-13 JSWGS=9E-12 NJS=1 +IJTHSFWD=0.01 IJTHSREV=0.01 BVS=10 XJBVS=1 PBS=0.5 CJS='cjn' MJS=0.25 +PBSWS=0.8 CJSWS='cjswn' MJSWS=0.01 PBSWGS=0.78 CJSWGS='cjswgn' +MJSWGS=0.52 +TPB=1.00E -03 TCJ=7.32E-04 TPBSW=1.90E-03 TCJSW=3.57E-04 +TPBSWG=1.90E-03 +TCJSWG=3.57E-04 XTIS=3 DMCG=9.25e-008 DMCI=9.25e-008 +DMDG=0 DMCGT=0 DWJ=0 XGW=0 XGL=0 RSHG=0.1 GBMIN=1e -012 RBPB=50 +RBPD=50 RBPS=50 RBDB=50 RBSB=50 NGCON=1 STIMOD=2 SA0=0.63E-6

+SB0=0.63E-6 KVSAT=0.20 WLOD =0.8E-6 TKU0=0.01 KU0=-7.36E-8 LLODKU0=1 +WLODKU0=1 LKU0=4.027E-7 WKU0=8E-7 PKU0=-2.0E-13 KVTH0=3.5E-9 +STK2=1.35E-9 STETA0=0 LKVTH0=-2.68E-11 WKVTH0=1.5E-6 PKVTH0=0 +LLODVTH=1 WLODVTH=1 LODK2=0.5 LODETA0=1 FNOIMOD=1 NOIA=4.2926E+41 +NOIB=1.612E+24 NOIC=8.75 EM=1.192E+07 EF=0.8841 TNOIMOD=0)

.MODEL pmos PMOS (LMIN='1.0000E-05-dxl' LMAX=2.001E-05 WMIN='1.0000E-06-+dxw' +WMAX='1.0000E-05-dxw' LEVEL=54 VERSION=4.2 BINUNIT=2 PARAMCHK=1 +MOBMOD=0 CAPMOD=1 IGBMOD=1 DIOMOD=1 RDSMOD=0 +RBODYMOD=0 RGATEMOD =0 PERMOD=1 ACNQSMOD=0 TRNQSMOD=0 +TNOM=25 TOXE='toxp' TOXM='toxp' DTOX=5.25e -010 EPSROX=3.9 WINT=5e-009 +LINT=2.5e-009 LL=0 WL=0 LLN=1 WLN=1 LW=0 WW=0 LWN=1 WWN=1 LWL=0 +WWL=0 LLC=0 WLC=0 LWC=0 WWLC=0 WWLC=0 DLC=1.525e -008 DWC=0 +XPART=1 TOXREF=3e-009 DLCIG=2.5e-009 XL='-3.5E-8+dxl' XW='1.5E-8+dxw' +VTH0='-0.16574717+dvthp' WVTH0='5.4744025e-009+dwvthp' LVTH0='0+dlvthp' +PVTH0='0+dpvthp'

Fig. 1.15 Standard CMOS cell. (a) circuit, (b) SPICE description, (c) parameters of the transistor model, (d) nominal operating conditions

K1=0.1623 K2=0.012789333 WK2=-8.9378e-010 K3=-0.58 K3B=0.8 +W0=0 DVT0=10 DVT1=1.71 DVT2=0.0928 DVT0W=0 DVT1W=0 DVT2W=0 DSUB=0.5 +MINV=0 VOFFL=0 DVTP0=0 DVTP1=0 LPE0=2.805e-007 LPEB=1e-007 +XJ=1.7000001e-007 NGATE=8e019 NDEP=1.7200001e017 NSD=1e020 PHIN=0 CDSC=0 +CDSCB=0 CDSCD=0 LCDSCD='0+dlcdscdp' CIT=0.00011166667 WCIT= -1.117225e-009 +VOFF=-0.09669 NFACTOR=0.5 ETA0=0.085 ETAB=-0.02 U0=0.0085405017 +WU0=-7.8540918e-010 UA=-2.77941e-010 WUA=1.5417705e-017 UB=2.0172933e-018 +WUB=-1.430048e-025 UC=8.136e-011 VSAT=120000 A0=3.62 AGS=1.096 A1=0 A2=1 +B0=0 B1=0 KETA= -0.04058 DWG=0 DWB=0 PCLM=0.2 PDIBLC1=0 PDIBLC2=0.005 +PDIBLCB=0 DROUT=0 PVAG=0 DELTA=0.02 PSCBE1=9.264e008 PSCBE2=1e-020 +FPROUT=1000 PDITS=0 PDITSD=0 PDITSL=0 RSH=9.68 RDSW='210+drdswp'+PRWG=0 PRWB=0 WR=1 ALPHA0=0 ALPHA1=0.06 BETA0=12 AGIDL=9e -008 +BGIDL=2.3e009 CGIDL=0.5 EGIDL=0.53 AIGBACC=0.01069 BIGBACC=0.003132 +CIGBACC=0.1498 NIGBACC=4.049 AIGBINV=0.35 BIGBINV=0.03 CIGBINV=0.006 +EIGBINV=1.1 NIGBINV=1 AIGC=0.00606 BIGC=0.0007625 CIGC=1e-010 +AIGSD=0.0045821833 WAIGSD=7.820575e -011 BIGSD=0 CIGSD=0.002267 NIGC=1 +POXEDGE=1 PIGCD=2.3 NTOX='ntoxp' XRCRG1=12 XRCRG2=1 CGSO='cgop' +CGDO='cgop' CGBO=0 CGDL='cglp' CGSL='cglp' CLC=1e-007 CLE=0.6 CF='cfp' +CKAPPAS=0.6 ACDE=1.2 MOIN=11.09 NOFF=2.175 VOFFCV=-0.03885 KT1=-0.29497017 +WKT1=5.1727518e-008 KT1L=0 KT2=-0.027639233 WKT2=-1.9417371e-008 +UTE=-1.193365 WUTE=6.3681825e-008 UA1=4.1822917e-009 WUA1=-1.0334331e-015 +UB1=-7.7915117e-018 WUB1=1.4758542e-024 UC1=-6.421e-011 PRT=0 AT=280000 +JSS=1.245E -07 JSWS=3.77E-13 JSWGS=3.00E-12 NJS=1 IJTHSFWD=0.01 +IJTHSREV=0.01 BVS=10 XJBVS=1 PBS=0.8 CJS='cjp' MJS=0.36 PBSWS=0.8 +CJSWS='cjswp' MJSWS=0.01 PBSWGS=1 CJSWGS='cjswgp' MJSWGS=0.99 TPB=1.9E-03 +TCJ=8.54E-04 TPBSW=1.9E-03 TCJSW=3.57E-04 TPBSWG=1.9E-03 TCJSWG=3.12E-03 +XTIS=3 DMCG=9.25e-008 DMCI=9.25e-008 DMDG=0 DMCGT=0 DWJ=0 XGW=0 +XGL=0 RSHG=0.1 GBMIN=1e -012 RBPB=50 RBPD=50 RBPS=50 RBDB=50 RBSB=50 +NGCON=1 STIMOD=2 SA0=0.63E -6 SB0=0.63E-6 KVSAT=-0.9 WLOD=0.8E-6 +TKU0=0.1 KU0=1.3249E-7 LLODKU0=1 WLODKU0=1 LKU0=1.33E-7 WKU0=6.5E-7 +PKU0=0 KVTH0=-1.5E-9 STK2=4E-10 STETA0=0 LKVTH0=-1.68E-15 WKVTH0=0.5E-6

+PKVTH0=0 LLODVTH=2 WLODVTH=1 LODK2=2 LODETA0=1 FNOIMOD=1 +NOIA=1.635E+42 +NOIB=7.241E+26 NOIC=8.75 EM=1.50E+08 EF=1.19 TNOIMOD=0)

c)

d)

The frequency of the input pulses is 400 MHz, the duration of rise and fall times of input signal is 0.1 ns, the ambient temperature is  $25^{\circ}$  C, and the capacitive load is  $20\phi$ F.

$U_0, V$

45

Fig. 1.15 (continued)

**Fig. 1.16** Dependence of the TTL cell output voltage on the absorbed dose of radiation in "0"

4. Use of special packages (Fig. 1.28). Note that methods to increase the radiation hardness of digital ICs only slightly reduce the effect of radiation on the behavior of digital circuits.

Fig. 1.18 Dependence of current consumed by TTL cell from the absorbed dose of radiation

Table 1.4 Classification of digital ICs as per radiation hardness

|                                                    | Commercial       | Rad-hard       | Radiation-Protected |

|----------------------------------------------------|------------------|----------------|---------------------|

| Long-term (krad) $(S_i)$                           | <20              | 20100          | 1001000             |

| Short-term (rad) (S <sub>i</sub> )/s               | <10 <sup>7</sup> | $10^{7}10^{9}$ | >109                |

| Non-recoverable failures (MeV-cm <sup>2</sup> /mg) | <20              | 2080           | >80                 |

Summarizing the above, it can be said that radiation has a significant and decisive influence on the behavior of digital circuits: reduces the switching speed of digital cells, increases the static and dynamic power consumption of digital circuits, leads to various failures in digital circuits (Fig. 1.29).

Thus, the parameters of digital circuits, functioning in the environment of radiation exposure are strongly dependent on the level of exposure. The dimensions of the changes in the parameters of digital IC cells due to radiation exposure can reach from one to several orders and are capable of qualitatively changing the behavior of the circuit in case of the same input signals. For confirmation, Fig. 1.30 shows the

Fig. 1.22 Various topological implementations of an n-MOS transistor

Fig. 1.23 Leakage current between separate transistors, induced by radiation exposure

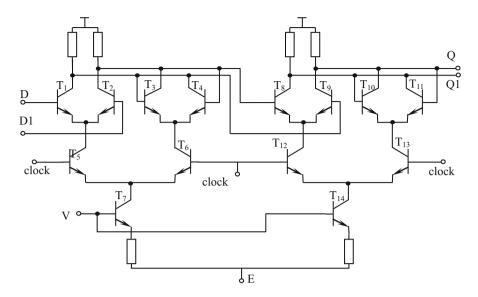

results of circuit-level simulation [76] of a D flip-flop (Fig. 1.29), with (Fig. 1.30a) and without consideration (Fig. 1.30b) of radiation. As seen from the diagrams, the difference is qualitative.

An important circumstance is the significant dependence of the values of changes of parameters of the same circuit, noted by many researchers, in case of the same radiation exposure from the processed signal transformations [3, 20, 41, 48, 53, 57, 59].

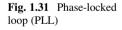

The situation is similar with respect to the significance of the influence of other types of external DFs (Table 1.1) (Fig. 1.31).

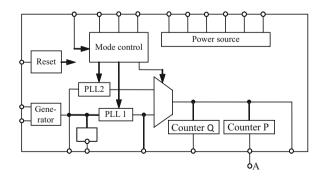

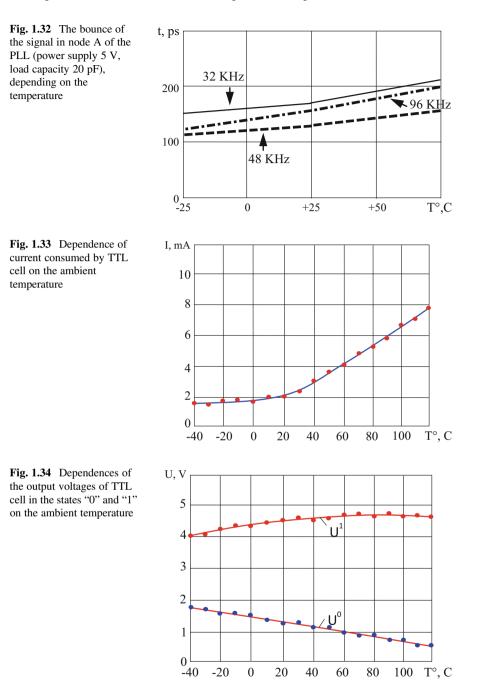

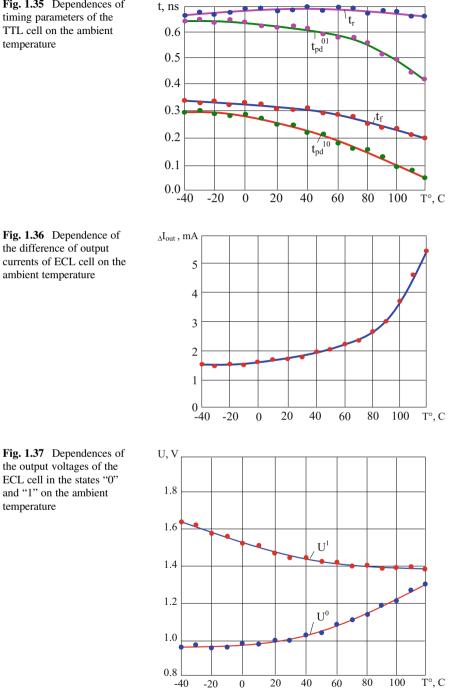

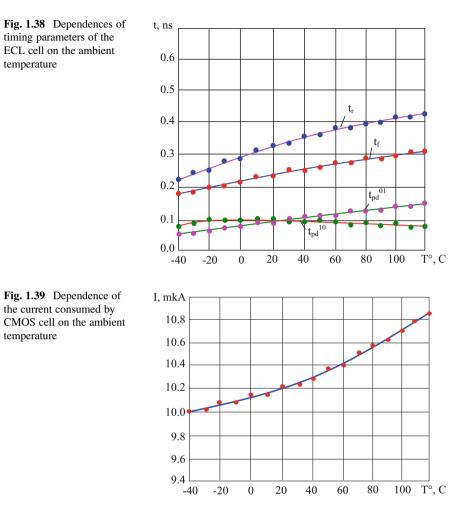

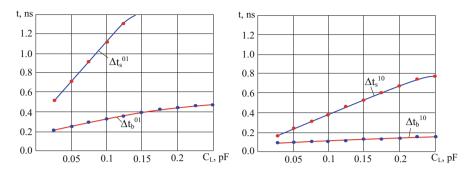

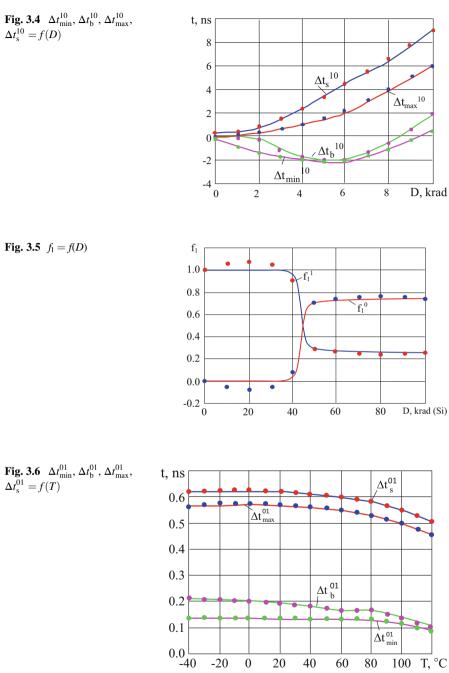

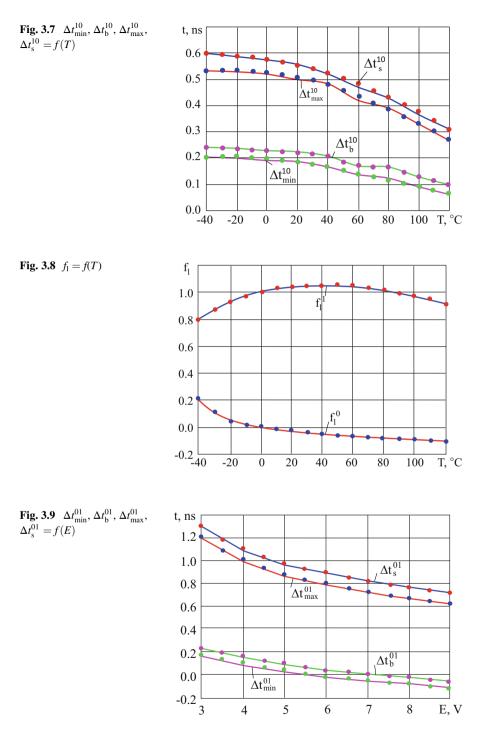

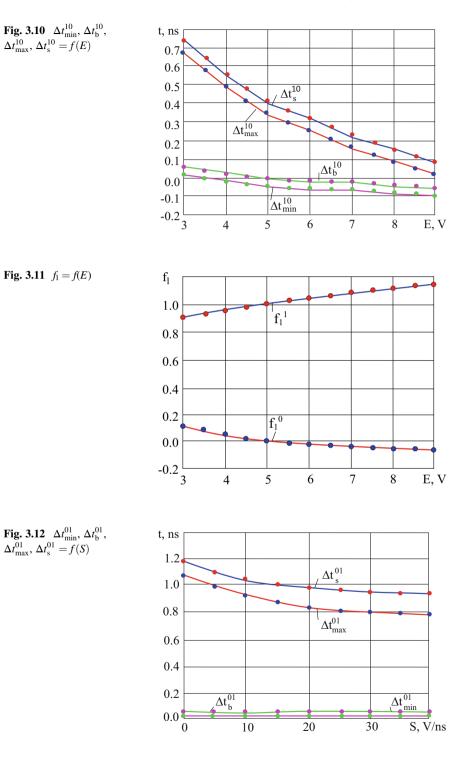

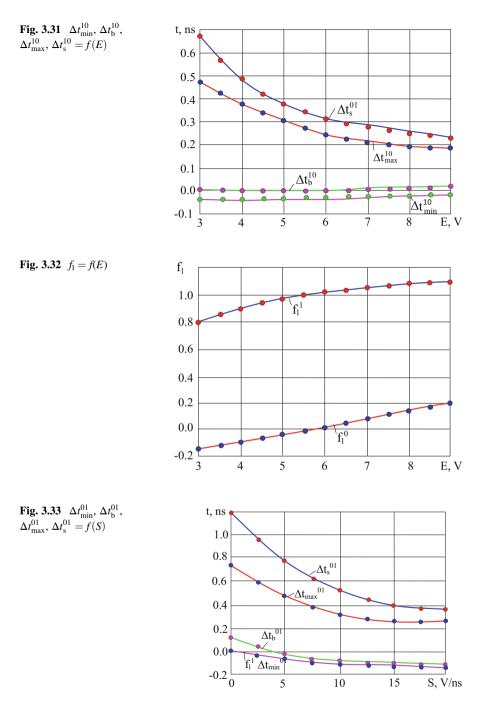

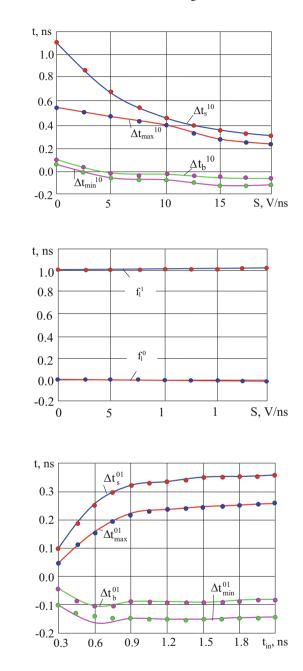

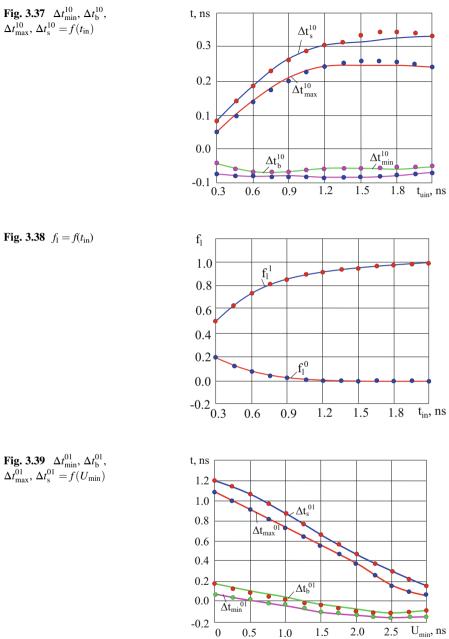

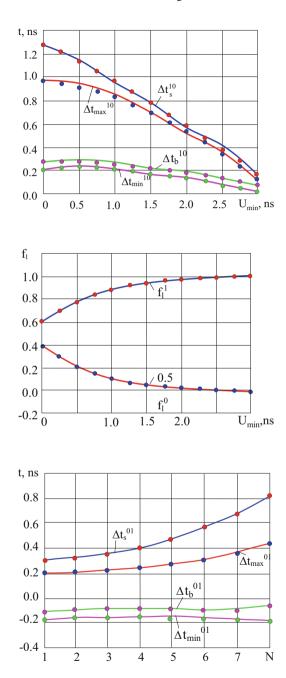

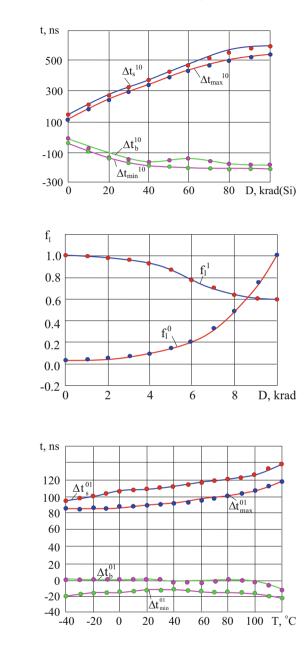

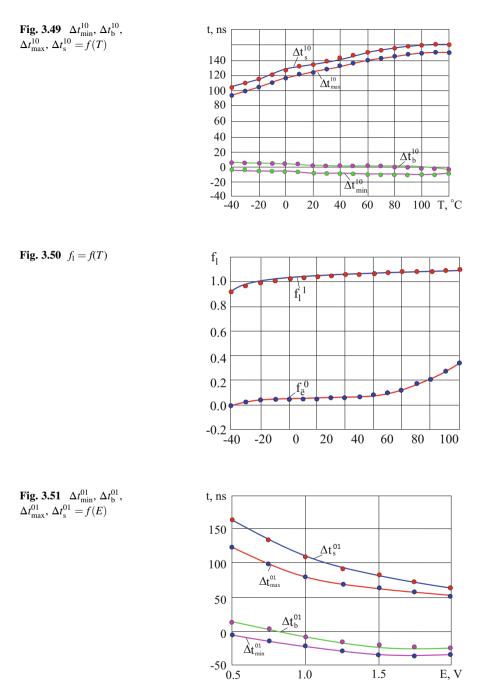

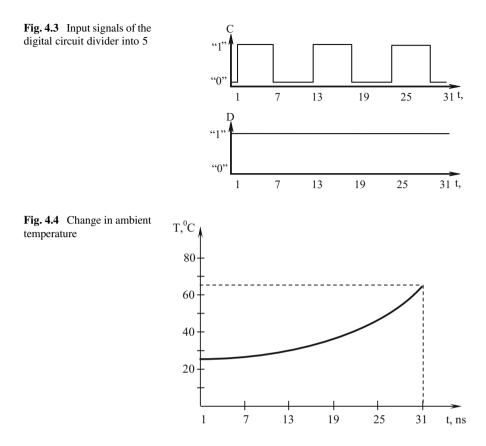

It is known that the parameters of both passive and active components of digital ICs are strongly dependent on the ambient temperature  $(V_2)$  [1, 2, 6, 32–35, 38, 67–70, 77–81]. Therefore, the integrated parameters of logic gates are also significantly changed in the operating range of the ambient temperature, which is confirmed by the dependencies, shown in Fig. 1.32 for the PLL (Fig. 1.31) [82], as well as in Figs. 1.33, 1.34, and 1.35—for the standard TTL cell (Fig. 1.13), in Figs. 1.36, 1.37,

Fig. 1.24 An example of topology of a rad-hard CMOS inverter

Fig. 1.25 Increase of radiation hardness of static CMOS memory cell by adding resistances in feedback circuits

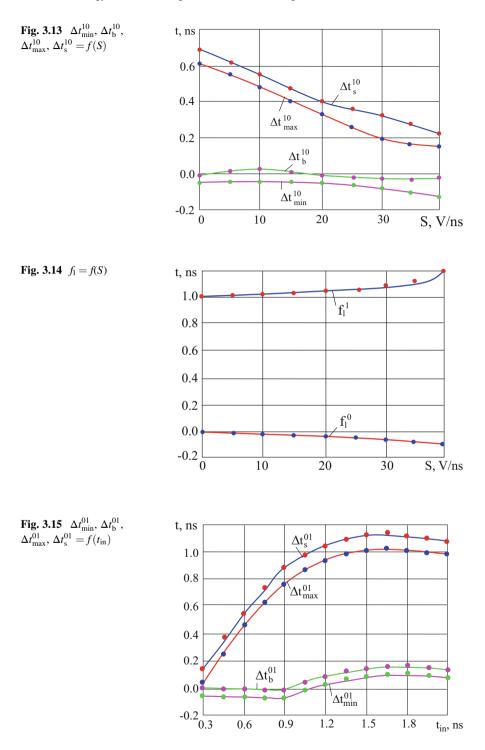

and 1.38 for the standard ECL cell (Fig. 1.14) and in Figs. 1.39 and 1.40—for the standard CMOS cell (Fig. 1.15), obtained by simulating with SPICE [59]. The situation is similar with a change in the supply voltage ( $V_3$ ).

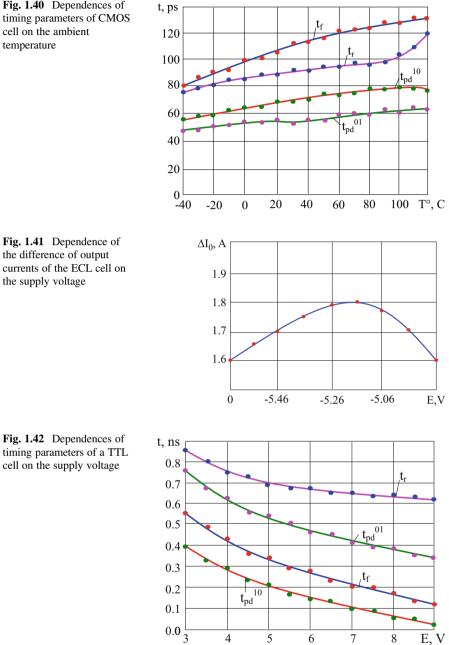

The dependence, illustrated in Fig. 1.41 [79], indicates significant displacements of circuit parameters even in insignificant limits of the change in the supply voltage  $(E_n)$ . Several times, and often even by orders of magnitude, the values of other parameters of digital circuits change even with small shifts of  $E_n$  from the nominal value.

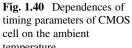

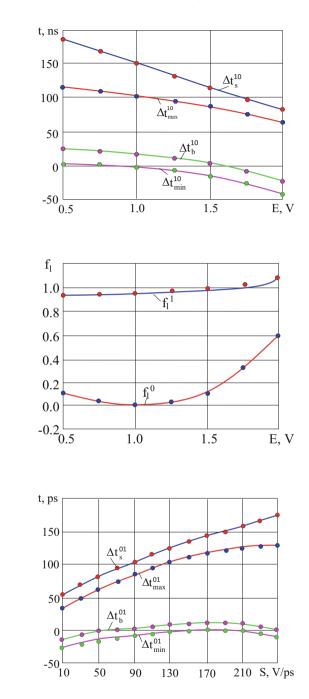

The same is confirmed by the dependencies in Fig. 1.42 for the standard TTL cell (Fig. 1.13), in Fig. 1.43 for the standard ECL cell (Fig. 1.14), obtained by simulating with SPICE [59].

The non-ideality of the sources of input signals ( $V_4$ , Table 1.1) are not only the real parameters (output impedance, capacitance, etc.) of the pulse generators of the entire circuit, but also formation of signals with distorted shapes (amplitude,

Fig. 1.26 Examples of rad-hard memory cells

Fig. 1.27 Examples of circuit-level solutions of circuit synchronization to increase radiation hardness (a-standard circuit, b-rad-hard solutions of the company Actel)

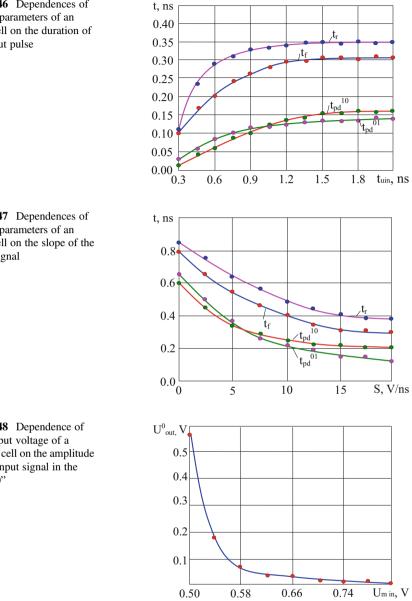

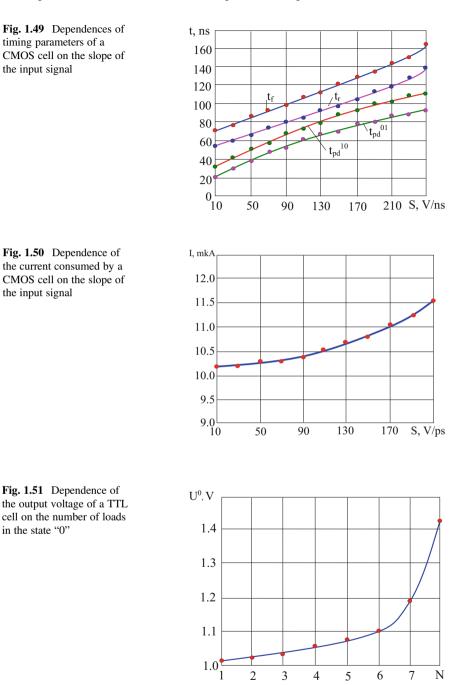

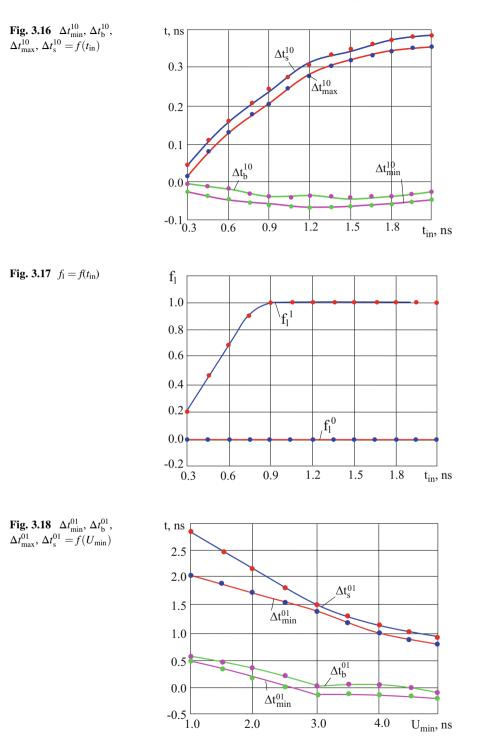

duration, etc.) in the internal nodes of the circuit. The latter is more often found in mixed-signal ICs, when signals are received on logic gates from analog blocks. In both cases, the operating modes of the loading cells are violated, since experimental studies show the existing strong dependence of digital cell parameters on the shape of input signals. As an example, Figs. 1.44, 1.45, 1.46, 1.47, 1.48, 1.49, and 1.50 shows the dependences of timing parameters of standard TTLs (Fig. 1.13), ECL (Fig. 1.14), and CMOS (Fig. 1.15) cells obtained by simulation using SPICE simulator [59].

The curves indicate the existing strong dependence of the shape of the output pulse of digital gates from the parameters of input signals, and this phenomenon cannot be ignored.

Fig. 1.29 D flip-flop

Fig. 1.30 Results of circuit-level simulation of a D flip-flop

Fig. 1.35 Dependences of timing parameters of the TTL cell on the ambient

The non-ideality of the loads of digital circuits ( $V_5$ , Table 1.1) is also considerable, especially in case of simulation of mixed-signal ICs, since in the internal nodes of the circuit the load is often an analog element whose input *I*–*V* characteristic can significantly differ from the same curves of the standard logic cells (TTL, ECL, I<sup>2</sup>L, CMOS, etc.). For this reason, the characteristics of the gate itself are shifted.

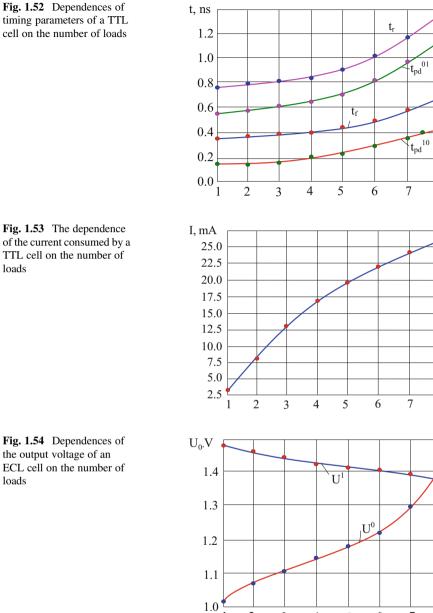

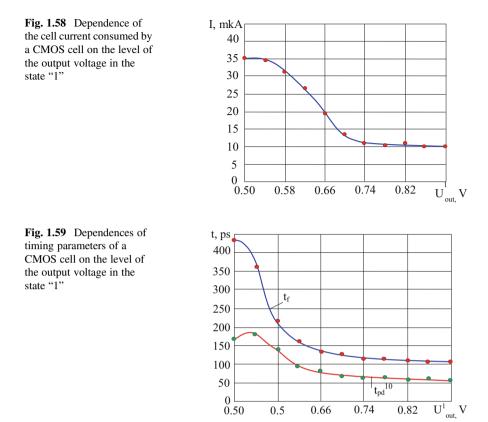

Similar experiments using SPICE make it easy to witness that the nonstandard I-V characteristic of the inputs of the gate load significantly affects the parameters of the gate source (this is also confirmed by the dependences in Figures 1.51, 1.52, 1.53, 1.54, 1.55, 1.56, 1.57, 1.58, and 1.59, obtained by simulating with SPICE [59]), and this factor should also be taken into account while simulating digital circuits.

As electromagnetic noise ( $V_6$ ) is widely covered in the literature [15, 40, 83], and the DF influence  $V_7$  and  $V_8$  is less significant, they are not discussed here.

0.4

0.2

0.0

10

$t_{pd}^{10}$

20

tf

S, V/ns

30

Fig. 1.46 Dependences of timing parameters of an ECL cell on the duration of the input pulse

Fig. 1.47 Dependences of timing parameters of an ECL cell on the slope of the input signal

Fig. 1.48 Dependence of the output voltage of a CMOS cell on the amplitude of the input signal in the state "0"

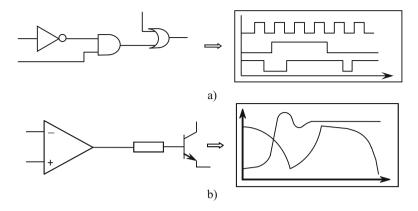

The dependencies presented in this section from literature sources, as well as the results of circuit simulation, indicate the considerable significance of the influence of external DFs (Table 1.1) on the behavior of digital circuits. The neglect of the noted DFs during their simulation can lead to significant, and often even to qualitative, errors of simulation of digital circuits.

Ν

Ν

2

3

4

5

6

7

Ν

Fig. 1.53 The dependence of the current consumed by a TTL cell on the number of loads

Fig. 1.54 Dependences of the output voltage of an ECL cell on the number of loads

## 1.1.2 Internal DF

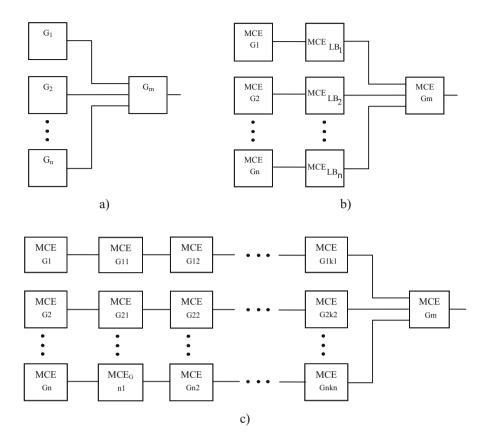

Non-ideality of interconnects ( $W_1$ ) has a dominant role in the characteristics of modern digital circuits [22, 25, 84, 85]. The influence of interconnects on the behavior of digital circuits has been studied by many groups of authors, among which the works of [7–9, 19, 22–27, 86–117] are particularly notable for the depth of the study of the significance of the effect of this type of DF on the operation of digital ICs.

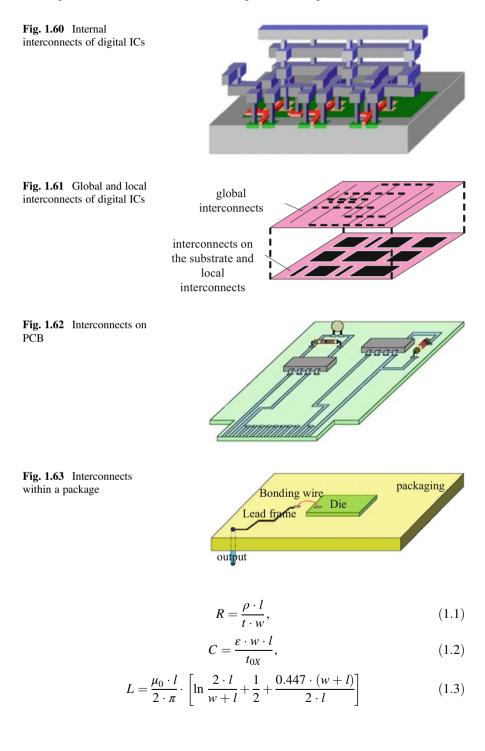

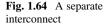

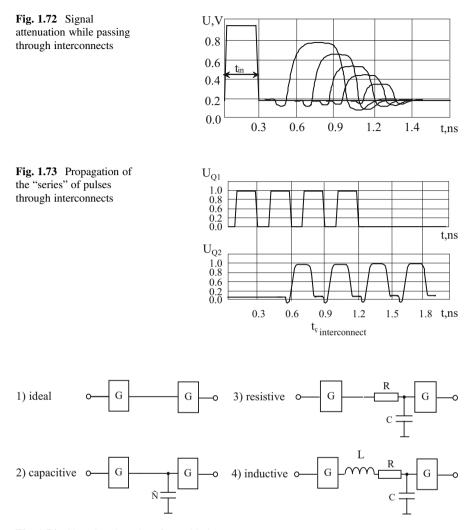

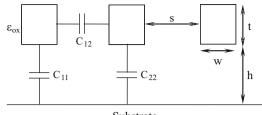

The behavior of a digital circuit is affected both by internal interconnects of digital ICs (Fig. 1.60) [117], which are divided into global and local (Fig. 1.61) [22], and interconnects on the PCB (Fig. 1.62) [118] and within the package of a digital circuit (Fig. 1.63) [119].

The behavior of a digital circuit significantly depends on:

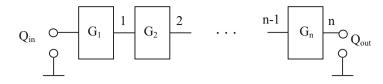

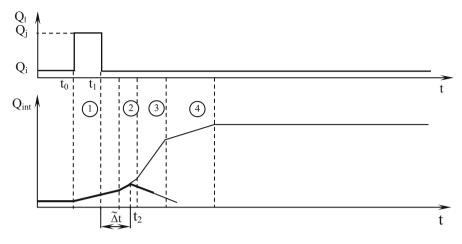

1. The intrinsic parasitic parameters *R*, *C*, *L*(1.1–1.3) [22] of a separate interconnect (Fig. 1.64) [25, 99], leading to distortion of the information signals passing through them, i.e.  $Q_1(t) \neq Q_2(t)$  (Fig. 1.65);

**Fig. 1.65** Distortion of information signal by interconnect

Fig. 1.67 Crosstalk of neighboring intradie interconnects

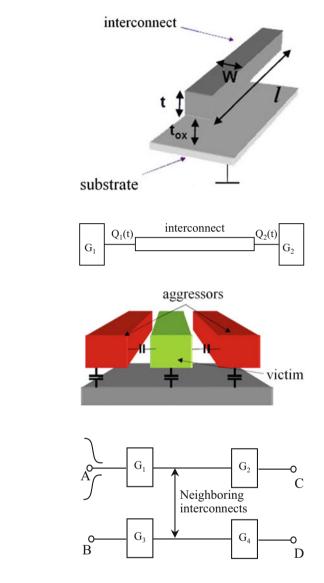

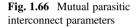

2. Mutual parasitic parameters between interconnects, as well as between interconnects and the IC substrate (Fig. 1.66) [110], leading to mutual influences of nearby intradic connections (Fig. 1.67).

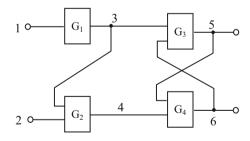

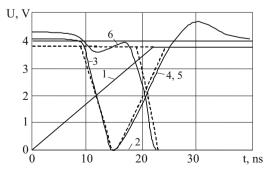

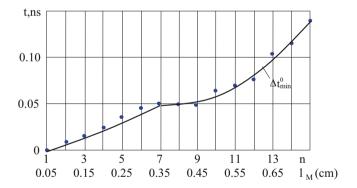

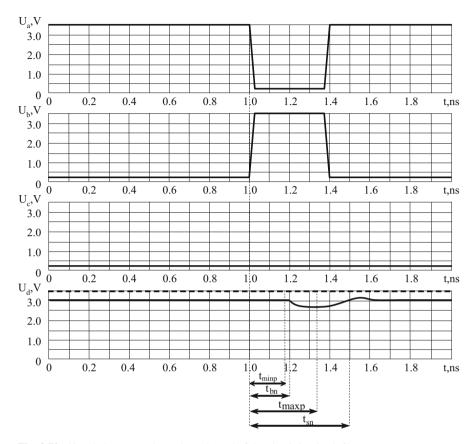

The influence of the intrinsic parasitic parameters of a single interconnect has a greater effect on timing parameters of the information signal [5, 7, 26, 100–103]. Figure 1.68 illustrates graphs of the change in timing parameters at the output of gate ( $G_1$ ) (Fig. 1.65), depending on the length of the interconnect, obtained using

SPICE. A standard CMOS cell was used as  $G_1$  and  $G_2$  (Fig. 1.15), the technology-45 nm, the interconnect parameters- $w = 0.14 \ \mu m$ ,  $t = 0.31 \ \mu m$ .

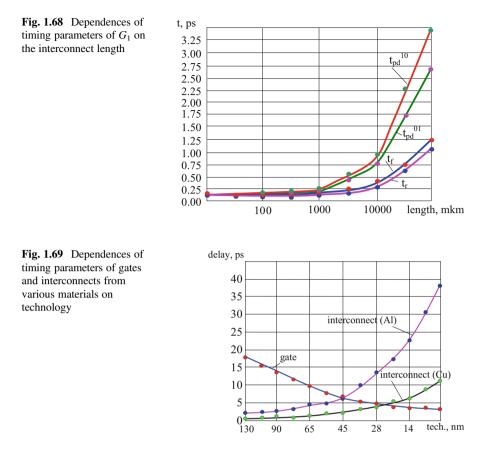

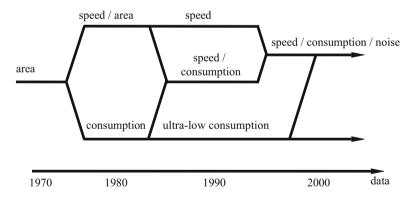

With the advance of the technology of manufacturing integrated circuits [64, 120, 121], the role of intradie interconnects in the operation of digital ICs became more and more tangible, and now the interconnects are already crucial in the formation of useful signals [8, 22, 121–124]. This is witnessed by the dependences (Fig. 1.69 [125] and Fig. 1.70 [126]) of delays of gate and interconnects from technology. As seen from the above graphs, the role of interconnect delays has now changed radically and often exceeds the intrinsic gate delay by several orders.

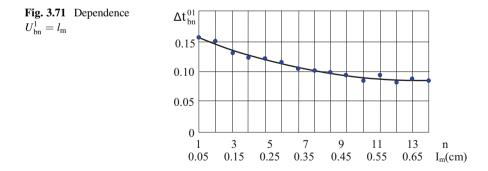

The explanation of this fact is as follows. The successes of microelectronics allow constantly the increase in the performance of logic gates [2, 35]. Ways to reduce the specific interconnect delays have almost exhausted themselves [92, 126]. The die area due to the success of the technology of their fabrication with time increases [126, 127]. Because of this, inter-cell distances increase (Fig. 1.71) [106], which leads to an increase in interconnect delays. Since a digital circuit is too sensitive to signal delays on its paths [15, 31, 128], there is a situation when the logic of the functioning of a digital circuit is largely determined by interconnect delays.

Fig. 1.71 Distribution of interconnect lengths in various microprocessor ICs

This circumstance forces digital circuit designers to look for radically new principles for their synthesis [31, 63, 128–132].

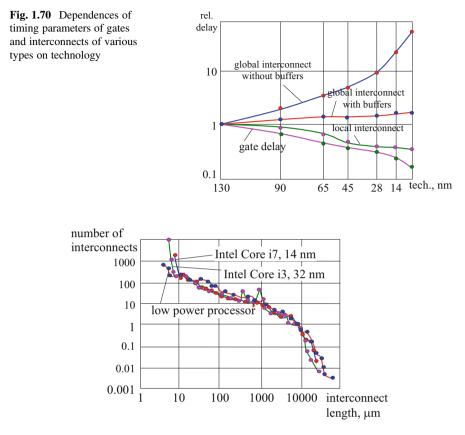

However, the intrinsic parasitic parameters of a single interconnect for nonstandard signal amplitudes (which, as already noted, often occurs during simulation of digital parts of mixed-signal ICs) may lead not only to signal delay during transition through the interconnects (Fig. 1.65) but also to the occurrence of such phenomena as gradual loss of the signal amplitude when passing through the interconnect (Fig. 1.72 shows signals in equidistant interconnection points with the parameters: l = 125 mm, w = 0.14 µm, t = 0.31 µm, the length of each segment-25 mm, the technology-28 nm) or the propagation of the "series" of pulses (Fig. 1.73 shows the signals at the inputs of  $G_1$  and  $G_2$  with the following interconnect parametersl = 30 mm, w = 0.14 µm, t = 0.31 µm, technology-28 nm). The diagrams in Figs. 1.72 and 1.73 were obtained by SPICE simulation of the circuit in Fig. 1.65 [100].

As the technology of manufacturing digital ICIs [64, 120, 121] has advanced, the roles of various parasitic parameters of interconnects have also changed (Fig. 1.74).

Fig. 1.74 Changing the roles of parasitic interconnect parameters

In particular, recently the role of the parasitic inductance of interconnects has increased dramatically [7, 91, 95, 96, 104, 107, 108]. It is known that the complex resistance of interconnects is defined in this form:

$$Z = R + j \cdot \omega \cdot L + \frac{1}{j \cdot \omega \cdot C}.$$

(1.4)

Increasing the frequency leads to an increase in the role of the inductive component. This, in turn, depending on the ratio between the parameters of gates and

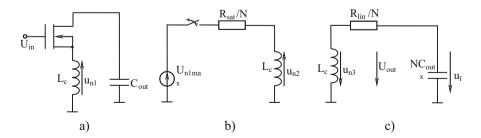

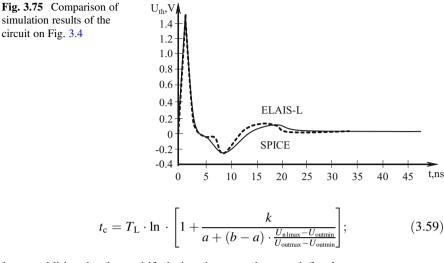

Fig. 1.75 Signal source with interconnects

Fig. 1.76 Critical consequences of interference noise: (a) glitch; (b) delay change

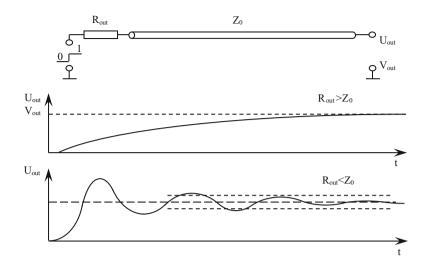

interconnects, can lead to new phenomena, in particular, to oscillation of the signal (Fig. 1.75 [95]).

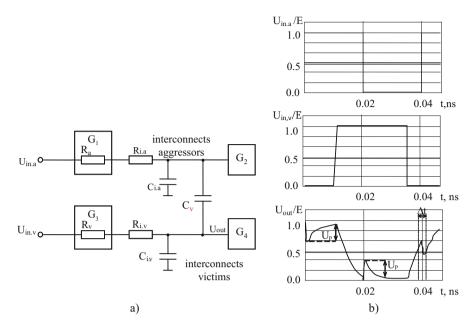

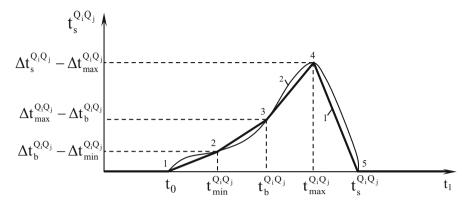

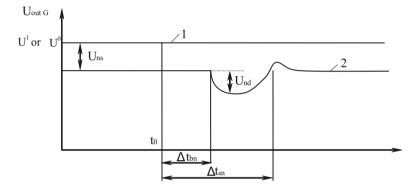

As seen from Fig. 1.75, the output resistance of most logic gates is loaded into an interconnect with a complex resistance  $Z_0$ . Depending on the ratio  $R_{out}$  and  $Z_0$ , different waveforms are possible. In particular, when  $R_{out}$  is smaller than  $Z_0$ , signal oscillations appear. As for the mutual parasitic parameters between interconnects (Fig. 1.66), their significance for the functioning of modern digital circuits is too large [114, 115]. They lead to crosstalk, which has two critical consequences for the victim when switching aggressors: glitches ( $U_P$ , Fig. 1.76a) in the static state of the victim and delay changes ( $\Delta t$ , Fig. 1.76b) in the state of switching the victim. Figure 1.77 shows  $U_P$  and  $\Delta t$  (Fig. 1.77b) for fragment of a digital circuit, the equivalent circuit of which is shown in Fig. 1.77a [22].

Fig. 1.77 Glitches and delay changes: (a) an equivalent circuit; (b) timing diagrams

The effect of the crosstalk signal on the functioning of a digital circuit depends on:

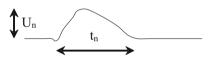

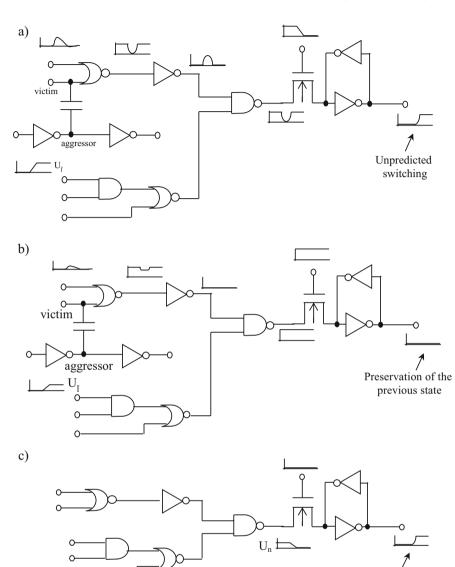

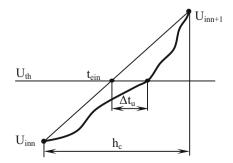

- The ratios of parameters of noise signal (Fig. 1.78) and the gate victims. Figure 1.79 shows an example where, depending on the  $U_n$  ratio and the threshold voltage of the victim, the output of a digital circuit can switch to an unintended error state (Fig. 1.79a) or remain in the same state (Fig. 1.79b).

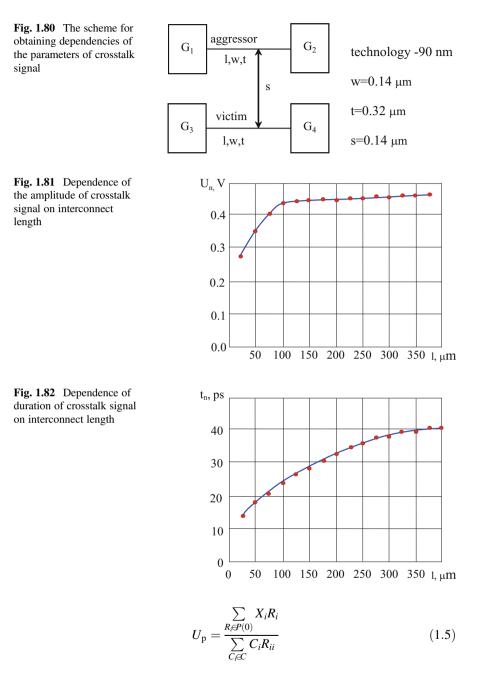

- From the location of noise signal. If the noise with a small  $U_n$  can be extinguished during propagation in the combinational part of a digital circuit (Fig. 1.79b), then the noise signal with the same  $U_n$  on arrival directly to the sequence fragments can switch the digital circuit to the wrong state (Fig. 1.79c) (Fig. 1.80).

Figures 1.81 and 1.82 show the dependences of  $U_n$  and  $t_n$  on the interconnect length for the circuit in Fig. 1.80, where a standard CMOS cell was used as a gate (Fig. 1.15).

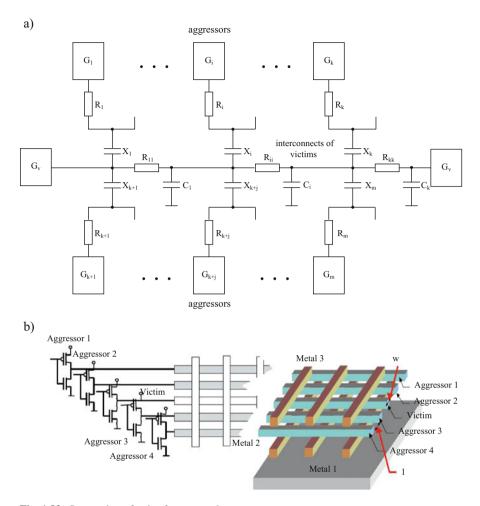

As seen from the graphs given by SPICE, the crosstalk is commensurate with useful signals even with small interconnect length. If the presence of a large number of interconnects with a much longer length (Fig. 1.71), as well as the summation factor of crosstalk (1.5 [110], where  $X_i$  is the capacity of interference between the victim and *i*th aggressor) in the presence of several aggressors (Fig. 1.83) is taken into account in digital circuits,

Fig. 1.79 Example of the effect of crosstalk on a digital circuit: (a) noise with a large  $U_n$ ; (b) noise with a small  $U_n$ ; (c) arrival of noise directly to sequential fragments

Unpredicted

switching

0

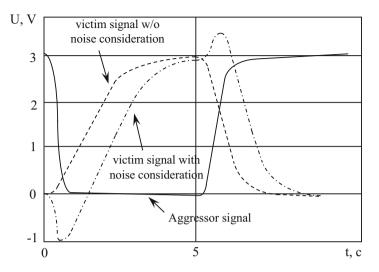

then it is not difficult to see that crosstalk plays a huge role in the functioning of digital circuits, and their consideration in the simulation of digital ICs is mandatory. Otherwise, this can lead to both quantitative (Fig. 1.84 [19]) and qualitative errors (Fig. 1.85 [133])).

Fig. 1.83 Summation of noise from several aggressors

It is also important that the crosstalk can propagate in digital circuits on different paths, depending on its current state. As an example, Fig. 1.86b illustrates a graph of propagation of the interference in the circuit of Fig. 1.86a. This circumstance complicates the predictability of the behavior of a digital circuit in the conditions of crosstalk.

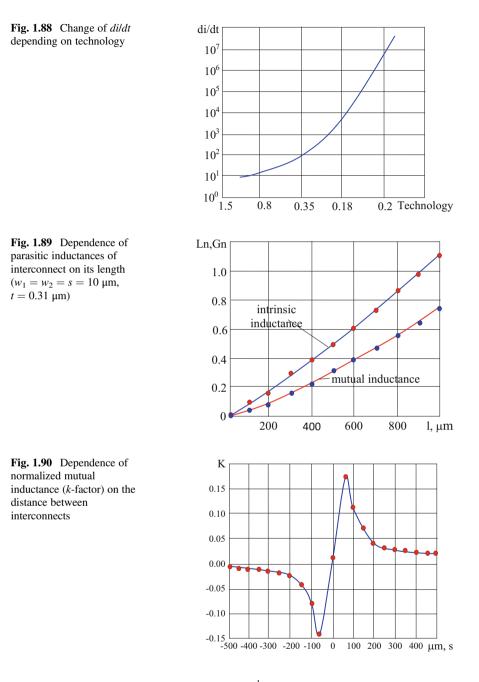

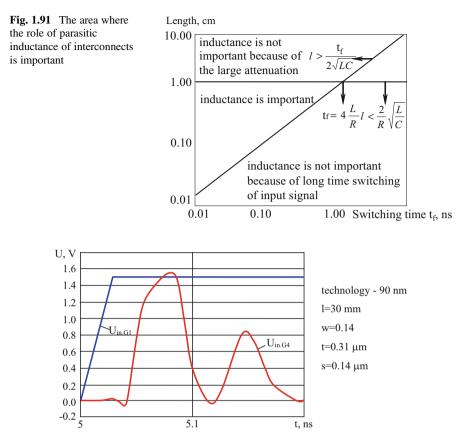

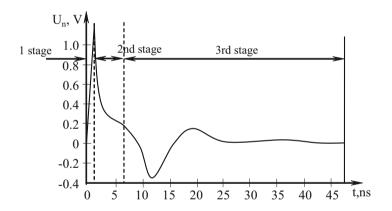

The role of the influence of crosstalk due to parasitic interconnection parameters on the functioning of digital circuits is so important that it is considered one of the main indicators of the quality of the design of modern digital circuits (Fig. 1.87) [111]. It becomes even more because of the increasing role of the inductive component [11, 124] ( $L \cdot di/dt$ ) of crosstalk (Figs. 1.88 [9], 1.89, 1.90), although it is important mainly for global interconnects (Fig. 1.91 [26]). Figure 1.92 shows the results of the simulation of the circuit of Fig. 1.80 using SPICE. A standard CMOS

Fig. 1.84 Example of a quantitative error in simulation results with and without crosstalk

cell (Fig. 1.15) was used as a gate, taking into account the parasitic inductances  $(L_c = 0.5 \text{ pG/}\mu\text{m}, L_B = 0.3 \text{ pH/}\mu\text{m})$ , capacitances  $(C_c = 36 \text{ aF/}\mu\text{m}, C_s = 62 \text{ aF/}M\text{m})$  and resistance  $(R = 0.4 \text{ m}\Omega/\mu\text{m})$  of interconnects. The results clearly demonstrate the importance of crosstalk on the behavior of digital circuits, including the inductive component, which generates signal oscillations.

Because of the significance of the effect of crosstalk due to the parasitic parameters of interconnects on the functioning of modern digital circuits, various methods are used to increase the resistance to this type of DF [22, 24, 25, 89, 111, 132, 134, 135]:

- 1. Logical methods (coding of polarity of signals, etc.)

- 2. Shielding of interconnects and increasing distances between interconnects

- 3. Rerouting of critical paths

- 4. Selection of transistor sizes in gates which serve as a source of the signal

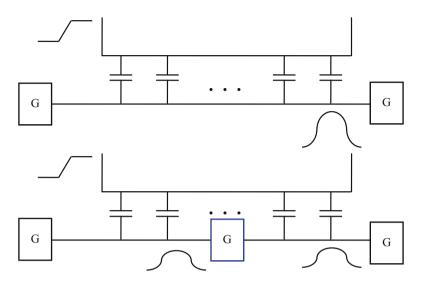

- 5. Addition of buffers on long interconnects (Fig. 1.93)

- 6. Other strategies for setting up interconnects (Fig. 1.94)

- 7. Some new approaches to the synthesis of digital circuits

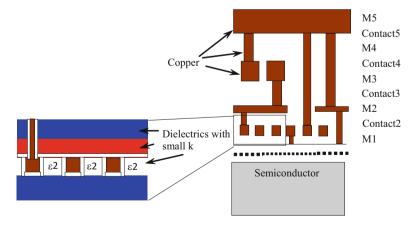

One way to reduce crosstalk is to improve technology. In particular, Cu ( $\rho_{Cu} \approx 1/3\rho_{Al}$ ) is used as an interconnect material instead of Al (Fig. 1.95 [24]), the metal layer and contacts are made simultaneously, reduce the *k* factor from 3.9 to 2, etc.

However, all the mentioned methods of increasing the noise immunity of a digital circuit only slightly reduce the influence of parasitic parameters of interconnects on the behavior of IC, and they must be taken into account while simulating modern digital circuits.

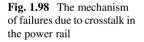

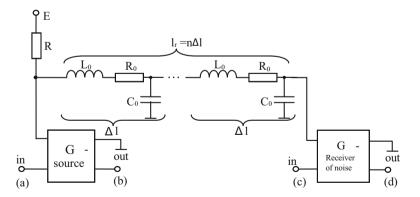

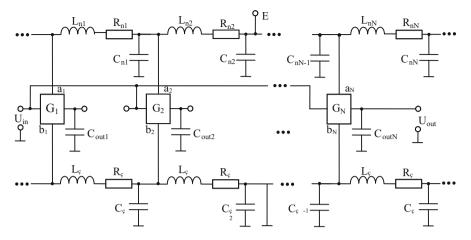

The non-ideality of power supply chains  $(W_2)$ , which are also distributed chains of parasitic *R*, *L*, *C* parameters (Fig. 1.96), causes mutual interference of gates,

Fig. 1.85 An example of a qualitative error in simulation results with and without consideration of crosstalk

functionally unrelated with each other, through the power rail (Fig. 1.97). The situation with the common bus is similar.

The issue of influence of parasitic parameters of power rails on the behavior of digital circuits has been studied by many groups of authors, among which the works of [12, 14, 19, 30, 124, 136–146] are particularly distinguished by the depth of the

Fig. 1.86 Noise propagation graph (a) an example of a scheme; (b) graph of propagation

Fig. 1.87 Dynamics of the importance of the design parameters of a digital circuit

study of the significance of the effect of this type of DF on the functioning of digital circuits.

It is known that, depending on the logical state of the  $G_1$ , especially during its switching, the value of the current  $I_{cons}^1$  consumed by this power supply from the power circuit varies. Therefore, the supply voltage of  $G_2$  changes:

$$E_{G_2} = E_{ideal} + L \cdot \frac{dI^1}{dt} + R \cdot dI^1, \qquad (1.6)$$

i.e., the noise through the power circuit has two main components:

Fig. 1.92 Results of simulating the circuit in Fig. 1.80 with parasitic parameters of interconnects

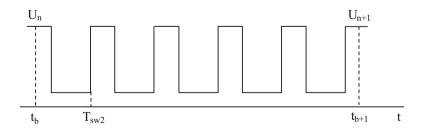

- 1. Noise due to switching of signal  $L \cdot di/dt$  [11]

- 2. Noise due to voltage drop in the power circuit IR [14]

As a result, the  $I_{cons}^2$  changes. This, in turn, due to parasitic parameters of  $G_2$  (Fig. 1.98) affects all parameters of the signal  $Q_{out2}$  and can lead to various kinds of errors and failures.

Thus, the function  $Q_{out2} = f_1(Q_{in2})$  is actually replaced by  $Q_{out2} = f_2(Q_{in2}, Q_{in1})$ . If one takes into account that on  $G_2$ , except  $G_1$ , all other gates of the circuit can affect, which appear through the power supply circuit of noise, even with consideration of difference in the signs of separate components, can become significant.

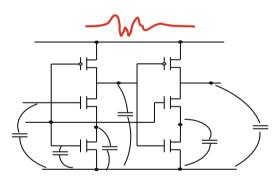

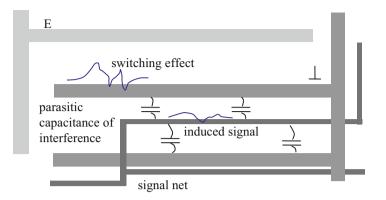

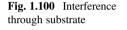

Noise in the power supply can also lead to indirect effects:

- 1. Crosstalk between the power supply and the signal nets of digital circuits (Fig. 1.99 [19])

- 2. Interference through the substrate (Fig. 1.100 [145]).

Fig. 1.93 Adding buffers on long interconnects

Fig. 1.94 Example of setting up interconnects

Fig. 1.95 Technological ways to reduce crosstalk

Fig. 1.97 Interaction of functionally unrelated gates through the power rail

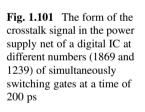

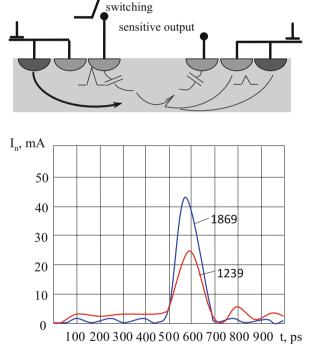

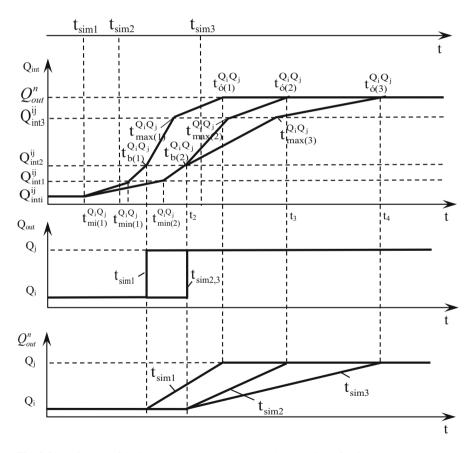

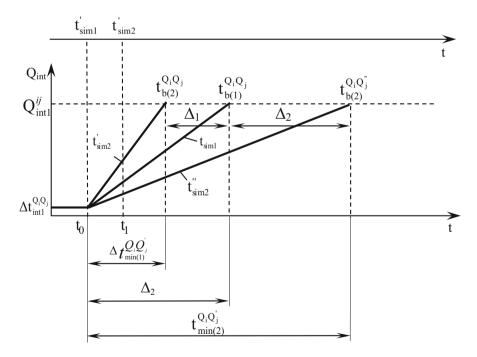

The level of crosstalk through the power supply circuit depends on the number of simultaneously switching gates (Fig. 1.101 [138]), as well as the distance l between the *G* aggressor and the *G* victim (Fig. 1.97). Figure 1.102 shows the dependence of the amplitude of the noise on l for the circuit in Fig. 1.97, obtained with the help of SPICE, when a standard CMOS cell was used as *G* (Fig. 1.15).

In modern digital circuits, the number of simultaneously switching gates and their distances to the *G*-victims are such [115] that noise of this type is significant and can influence the behavior of digital circuits. Figure 1.103 illustrates examples of measuring crosstalk through a substrate in a real digital IC [145].

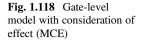

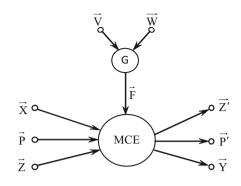

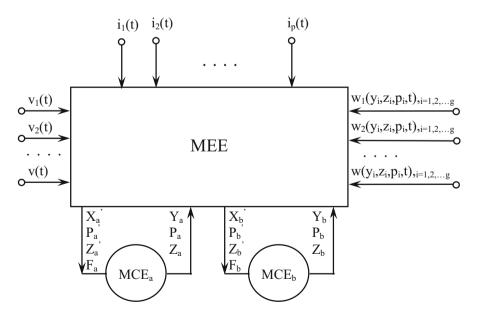

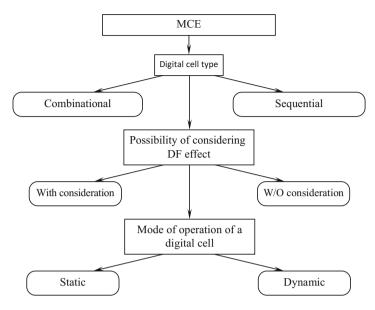

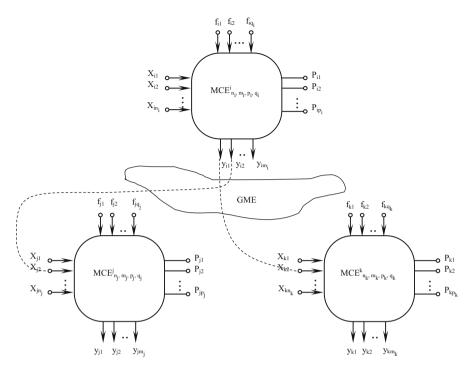

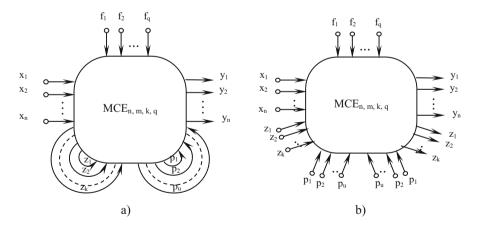

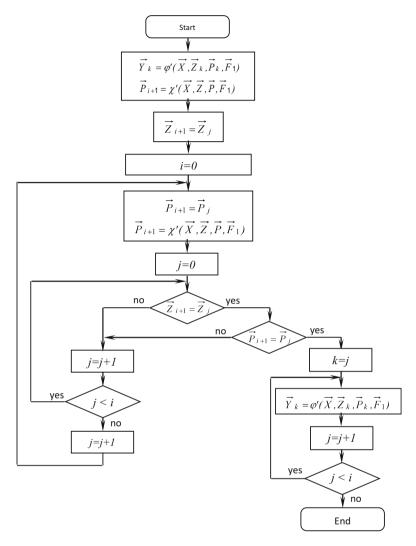

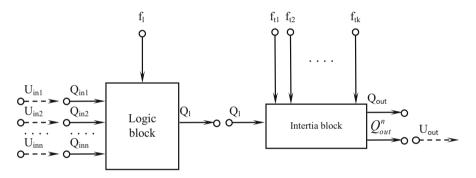

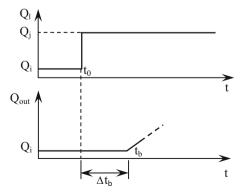

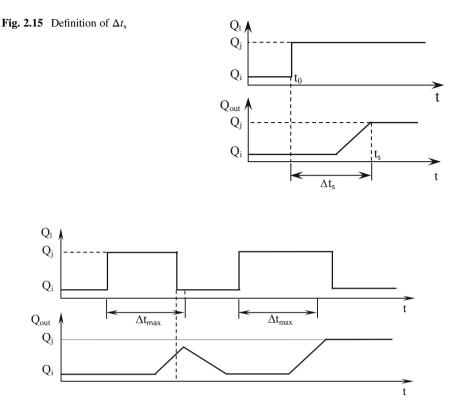

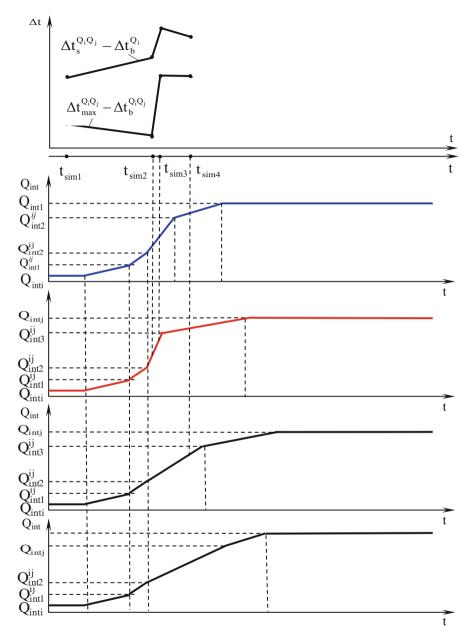

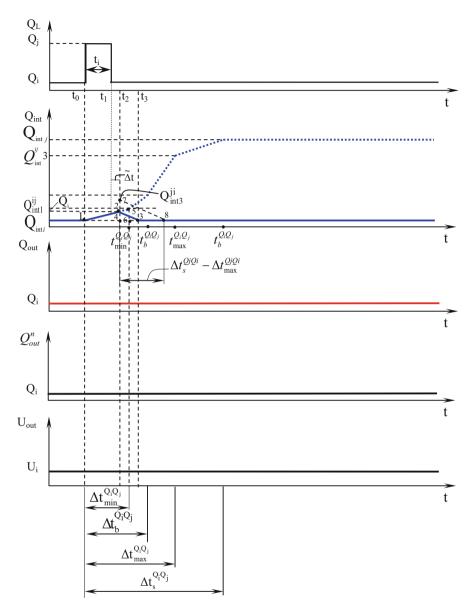

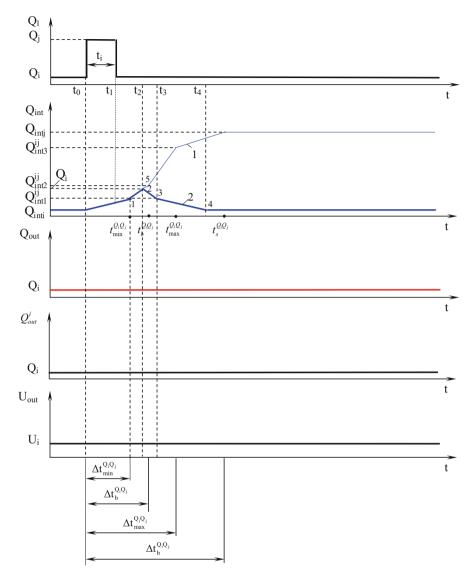

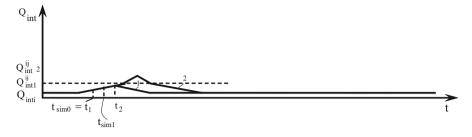

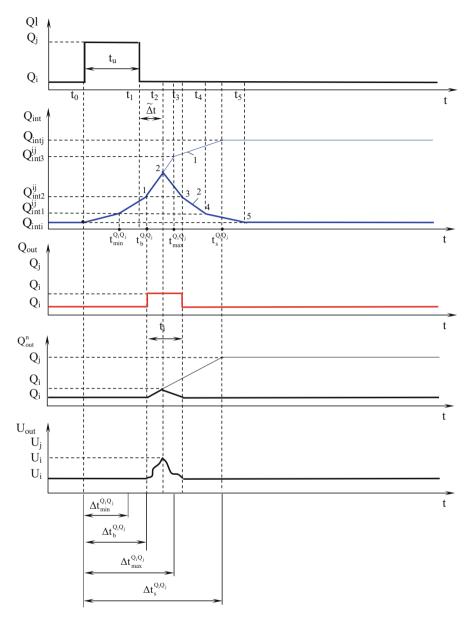

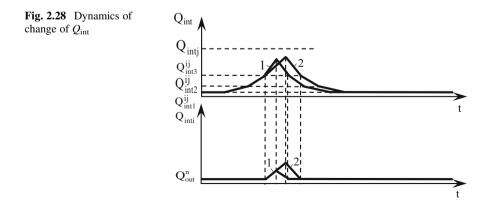

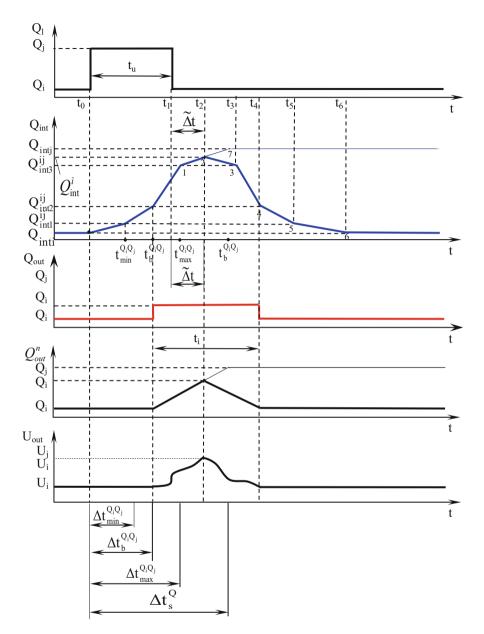

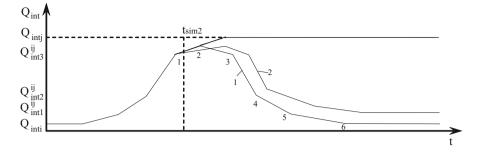

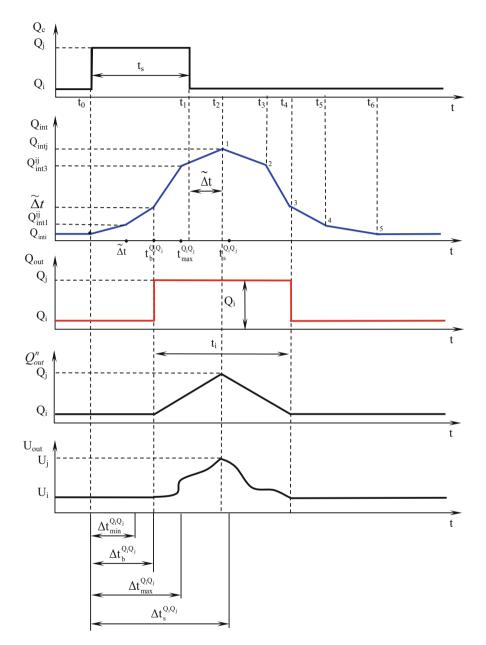

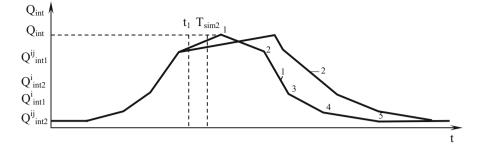

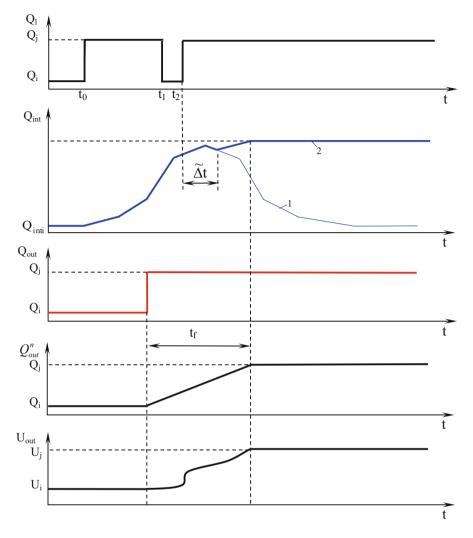

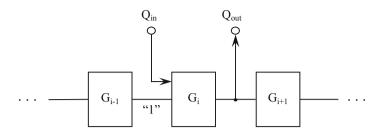

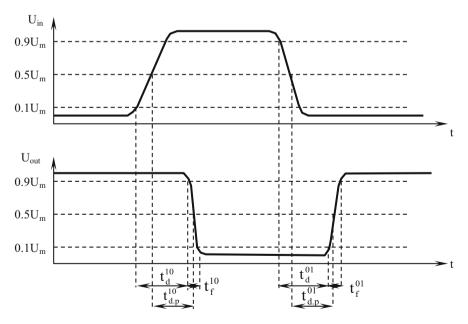

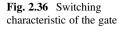

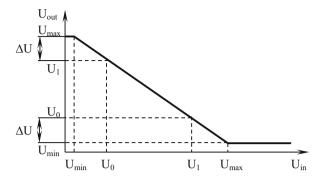

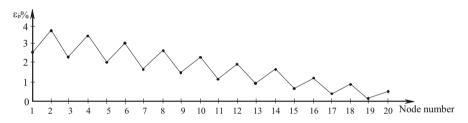

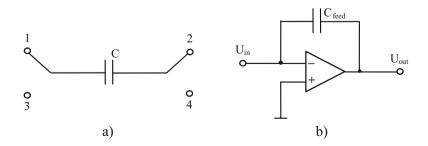

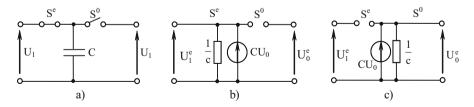

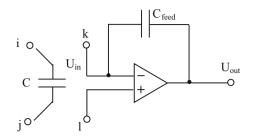

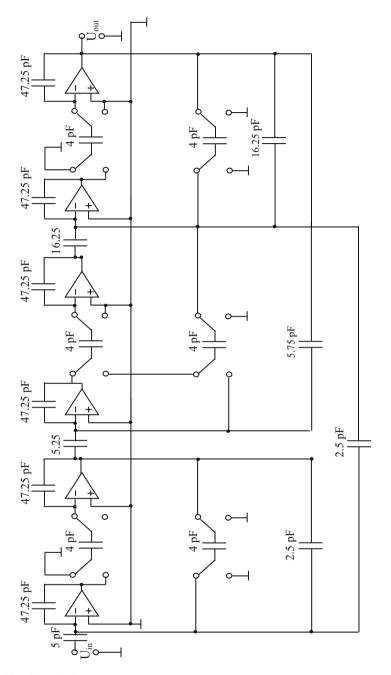

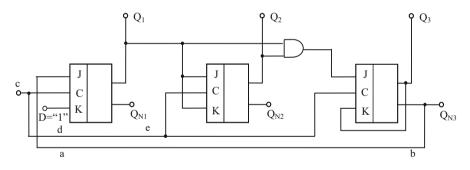

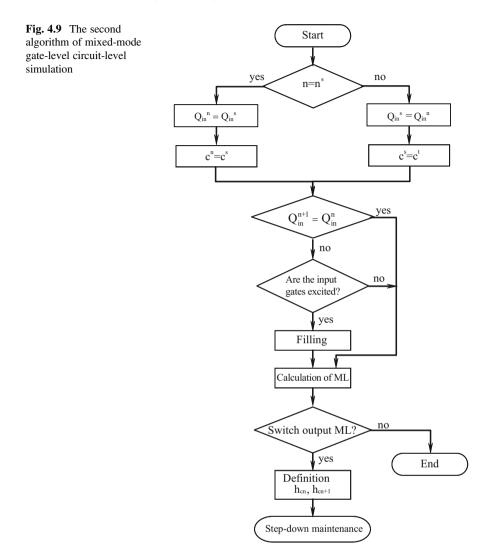

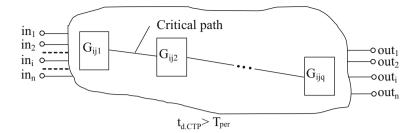

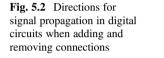

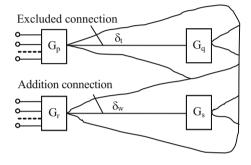

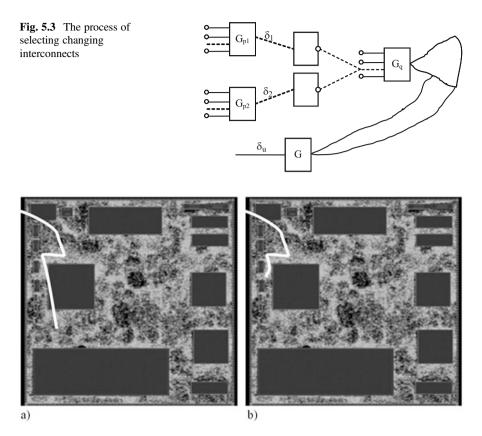

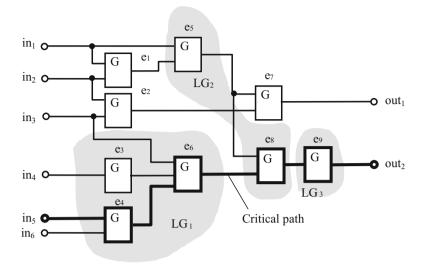

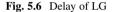

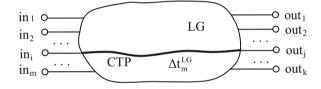

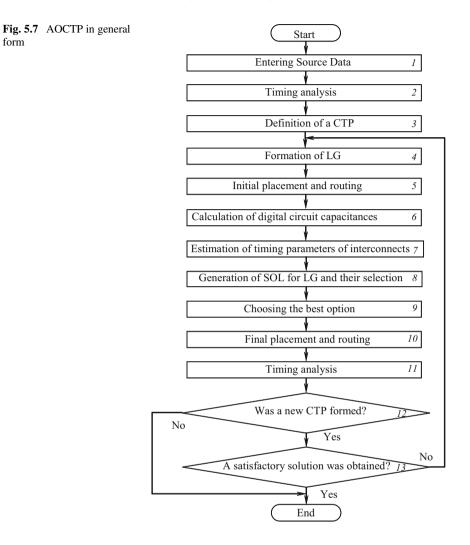

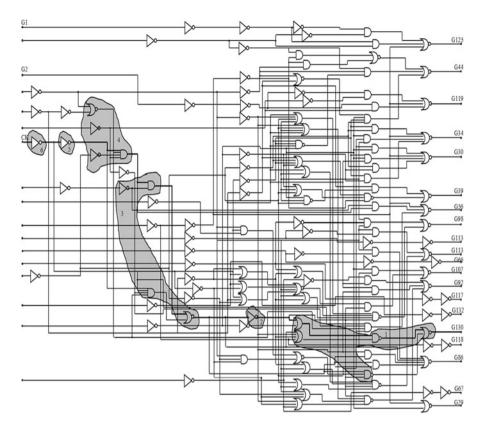

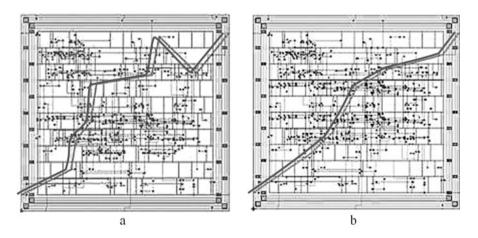

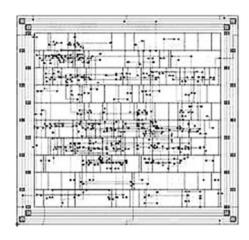

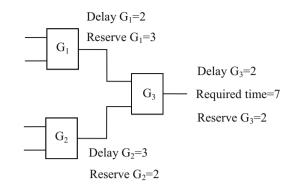

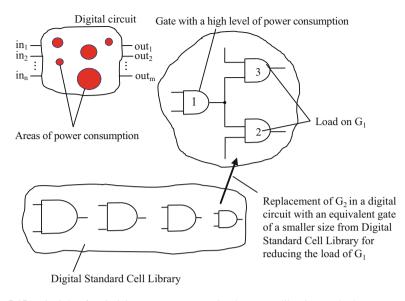

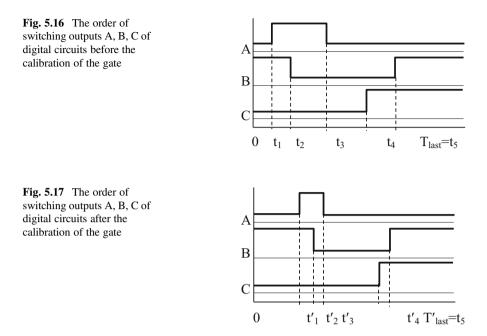

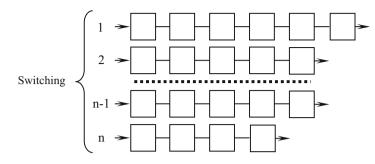

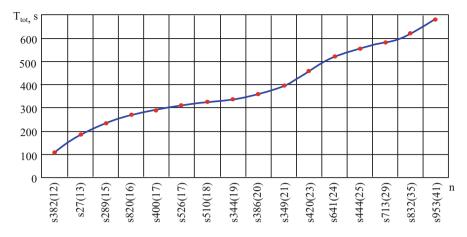

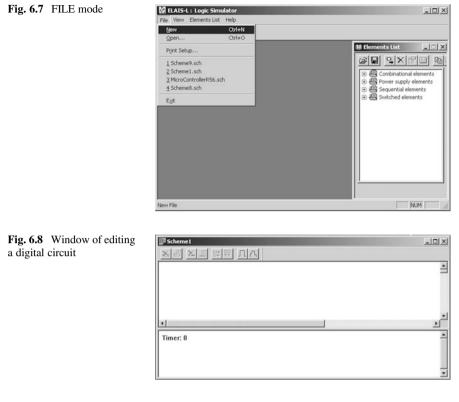

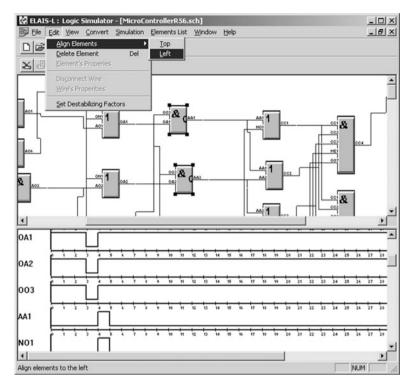

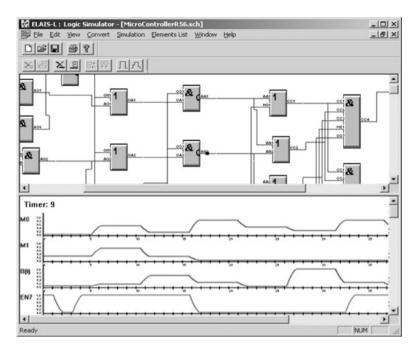

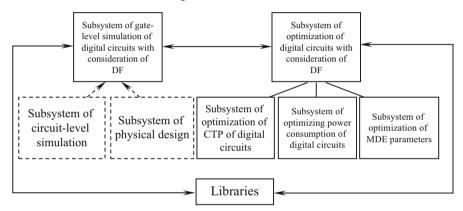

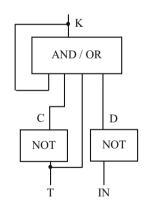

Fig. 1.99 Crosstalk between power supply and signal nets of digital circuits