### SPICE FOR POWER Electronics and Electric Power

SECOND EDITION

#### ELECTRICAL AND COMPUTER ENGINEERING

A Series of Reference Books and Textbooks

#### FOUNDING EDITOR

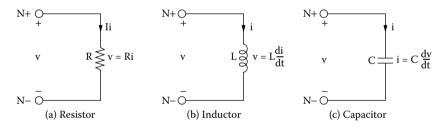

#### Marlin O. Thurston

Department of Electrical Engineering The Ohio State University Columbus, Ohio

- 1. Rational Fault Analysis, *edited by Richard Saeks and S. R. Liberty*

- 2. Nonparametric Methods in Communications, *edited by P. Papantoni-Kazakos and Dimitri Kazakos*

- 3. Interactive Pattern Recognition, Yi-tzuu Chien

- 4. Solid-State Electronics, *Lawrence E. Murr*

- 5. Electronic, Magnetic, and Thermal Properties of Solid Materials, *Klaus Schröder*

- 6. Magnetic-Bubble Memory Technology, Hsu Chang

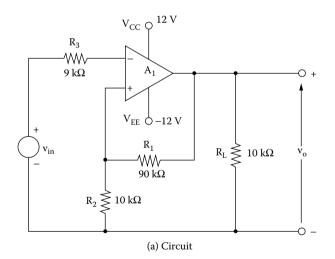

- 7. Transformer and Inductor Design Handbook, Colonel Wm. T. McLyman

- 8. Electromagnetics: Classical and Modern Theory and Applications, *Samuel Seely and Alexander D. Poularikas*

- 9. One-Dimensional Digital Signal Processing, Chi-Tsong Chen

- 10. Interconnected Dynamical Systems, *Raymond A. DeCarlo and Richard Saeks*

- 11. Modern Digital Control Systems, Raymond G. Jacquot

- 12. Hybrid Circuit Design and Manufacture, Roydn D. Jones

- Magnetic Core Selection for Transformers and Inductors: A User's Guide to Practice and Specification, Colonel Wm. T. McLyman

- 14. Static and Rotating Electromagnetic Devices, *Richard H. Engelmann*

- 15. Energy-Efficient Electric Motors: Selection and Application, *John C. Andreas*

- 16. Electromagnetic Compossibility, Heinz M. Schlicke

- 17. Electronics: Models, Analysis, and Systems, *James G. Gottling*

- 18. Digital Filter Design Handbook, Fred J. Taylor

- 19. Multivariable Control: An Introduction, P. K. Sinha

- 20. Flexible Circuits: Design and Applications, *Steve Gurley,* with contributions by Carl A. Edstrom, Jr., Ray D. Greenway, and William P. Kelly

- 21. Circuit Interruption: Theory and Techniques, *Thomas E. Browne, Jr.*

- 22. Switch Mode Power Conversion: Basic Theory and Design, *K. Kit Sum*

- 23. Pattern Recognition: Applications to Large Data-Set Problems, *Sing-Tze Bow*

- 24. Custom-Specific Integrated Circuits: Design and Fabrication, Stanley L. Hurst

- 25. Digital Circuits: Logic and Design, Ronald C. Emery

- 26. Large-Scale Control Systems: Theories and Techniques, Magdi S. Mahmoud, Mohamed F. Hassan, and Mohamed G. Darwish

- 27. Microprocessor Software Project Management, Eli T. Fathi and Cedric V. W. Armstrong (Sponsored by Ontario Centre for Microelectronics)

- 28. Low Frequency Electromagnetic Design, Michael P. Perry

- 29. Multidimensional Systems: Techniques and Applications, *edited by Spyros G. Tzafestas*

- 30. AC Motors for High-Performance Applications: Analysis and Control, *Sakae Yamamura*

- 31. Ceramic Motors for Electronics: Processing, Properties, and Applications, *edited by Relva C. Buchanan*

- 32. Microcomputer Bus Structures and Bus Interface Design, *Arthur L. Dexter*

- 33. End User's Guide to Innovative Flexible Circuit Packaging, *Jay J. Miniet*

- 34. Reliability Engineering for Electronic Design, Norman B. Fuqua

- 35. Design Fundamentals for Low-Voltage Distribution and Control, *Frank W. Kussy and Jack L. Warren*

- 36. Encapsulation of Electronic Devices and Components, *Edward R. Salmon*

- 37. Protective Relaying: Principles and Applications, *J. Lewis Blackburn*

- 38. Testing Active and Passive Electronic Components, *Richard F. Powell*

- Adaptive Control Systems: Techniques and Applications, V. V. Chalam

- 40. Computer-Aided Analysis of Power Electronic Systems, Venkatachari Rajagopalan

- 41. Integrated Circuit Quality and Reliability, Eugene R. Hnatek

- 42. Systolic Signal Processing Systems, *edited by Earl E. Swartzlander, Jr.*

- 43. Adaptive Digital Filters and Signal Analysis, Maurice G. Bellanger

- 44. Electronic Ceramics: Properties, Configuration, and Applications, *edited by Lionel M. Levinson*

- 45. Computer Systems Engineering Management, Robert S. Alford

- 46. Systems Modeling and Computer Simulation, *edited by Naim A. Kheir*

- 47. Rigid-Flex Printed Wiring Design for Production Readiness, *Walter S. Rigling*

- 48. Analog Methods for Computer-Aided Circuit Analysis and Diagnosis, *edited by Takao Ozawa*

- 49. Transformer and Inductor Design Handbook: Second Edition, Revised and Expanded, *Colonel Wm. T. McLyman*

- 50. Power System Grounding and Transients: An Introduction, *A. P. Sakis Meliopoulos*

- 51. Signal Processing Handbook, edited by C. H. Chen

- 52. Electronic Product Design for Automated Manufacturing, *H. Richard Stillwell*

- 53. Dynamic Models and Discrete Event Simulation, William Delaney and Erminia Vaccari

- 54. FET Technology and Application: An Introduction, *Edwin S. Oxner*

- 55. Digital Speech Processing, Synthesis, and Recognition, *Sadaoki Furui*

- 56. VLSI RISC Architecture and Organization, Stephen B. Furber

- 57. Surface Mount and Related Technologies, Gerald Ginsberg

- 58. Uninterruptible Power Supplies: Power Conditioners for Critical Equipment, *David C. Griffith*

- 59. Polyphase Induction Motors: Analysis, Design, and Application, *Paul L. Cochran*

- 60. Battery Technology Handbook, edited by H. A. Kiehne

- 61. Network Modeling, Simulation, and Analysis, *edited by Ricardo F. Garzia and Mario R. Garzia*

- 62. Linear Circuits, Systems, and Signal Processing: Advanced Theory and Applications, *edited by Nobuo Nagai*

- 63. High-Voltage Engineering: Theory and Practice, *edited by M. Khalifa*

- 64. Large-Scale Systems Control and Decision Making, edited by Hiroyuki Tamura and Tsuneo Yoshikawa

- 65. Industrial Power Distribution and Illuminating Systems, *Kao Chen*

- 66. Distributed Computer Control for Industrial Automation, Dobrivoje Popovic and Vijay P. Bhatkar

- 67. Computer-Aided Analysis of Active Circuits, Adrian Ioinovici

- 68. Designing with Analog Switches, *Steve Moore*

- 69. Contamination Effects on Electronic Products, *Carl J. Tautscher*

- 70. Computer-Operated Systems Control, Magdi S. Mahmoud

- 71. Integrated Microwave Circuits, edited by Yoshihiro Konishi

- 72. Ceramic Materials for Electronics: Processing, Properties, and Applications, Second Edition, Revised and Expanded, edited by Relva C. Buchanan

- 73. Electromagnetic Compatibility: Principles and Applications, *David A. Weston*

- 74. Intelligent Robotic Systems, edited by Spyros G. Tzafestas

- 75. Switching Phenomena in High-Voltage Circuit Breakers, edited by Kunio Nakanishi

- 76. Advances in Speech Signal Processing, edited by Sadaoki Furui and M. Mohan Sondhi

- 77. Pattern Recognition and Image Preprocessing, Sing-Tze Bow

- 78. Energy-Efficient Electric Motors: Selection and Application, Second Edition, *John C. Andreas*

- 79. Stochastic Large-Scale Engineering Systems, *edited by Spyros G. Tzafestas and Keigo Watanabe*

- 80. Two-Dimensional Digital Filters, *Wu-Sheng Lu* and Andreas Antoniou

- 81. Computer-Aided Analysis and Design of Switch-Mode Power Supplies, *Yim-Shu Lee*

- 82. Placement and Routing of Electronic Modules, edited by Michael Pecht

- 83. Applied Control: Current Trends and Modern Methodologies, edited by Spyros G. Tzafestas

- 84. Algorithms for Computer-Aided Design of Multivariable Control Systems, *Stanoje Bingulac and Hugh F. VanLandingham*

- 85. Symmetrical Components for Power Systems Engineering, *J. Lewis Blackburn*

- 86. Advanced Digital Signal Processing: Theory and Applications, *Glenn Zelniker and Fred J. Taylor*

- 87. Neural Networks and Simulation Methods, Jian-Kang Wu

- 88. Power Distribution Engineering: Fundamentals and Applications, *James J. Burke*

- 89. Modern Digital Control Systems: Second Edition, *Raymond G. Jacquot*

- 90. Adaptive IIR Filtering in Signal Processing and Control, *Phillip A. Regalia*

- 91. Integrated Circuit Quality and Reliability: Second Edition, Revised and Expanded, *Eugene R. Hnatek*

- 92. Handbook of Electric Motors, edited by Richard H. Engelmann and William H. Middendorf

- 93. Power-Switching Converters, Simon S. Ang

- 94. Systems Modeling and Computer Simulation: Second Edition, *Naim A. Kheir*

- 95. EMI Filter Design, Richard Lee Ozenbaugh

- 96. Power Hybrid Circuit Design and Manufacture, *Haim Taraseiskey*

- 97. Robust Control System Design: Advanced State Space Techniques, *Chia-Chi Tsui*

- 98. Spatial Electric Load Forecasting, H. Lee Willis

- 99. Permanent Magnet Motor Technology: Design and Applications, *Jacek F. Gieras and Mitchell Wing*

- 100. High Voltage Circuit Breakers: Design and Applications, *Ruben D. Garzon*

- 101. Integrating Electrical Heating Elements in Appliance Design, Thor Hegbom

- 102. Magnetic Core Selection for Transformers and Inductors: A User's Guide to Practice and Specification, Second Edition, *Colonel Wm. T. McLyman*

- 103. Statistical Methods in Control and Signal Processing, edited by Tohru Katayama and Sueo Sugimoto

- 104. Radio Receiver Design, Robert C. Dixon

- 105. Electrical Contacts: Principles and Applications, edited by Paul G. Slade

- 106. Handbook of Electrical Engineering Calculations, *edited by Arun G. Phadke*

- 107. Reliability Control for Electronic Systems, Donald J. LaCombe

- 108. Embedded Systems Design with 8051 Microcontrollers: Hardware and Software, *Zdravko Karakehayov*, *Knud Smed Christensen, and Ole Winther*

- 109. Pilot Protective Relaying, edited by Walter A. Elmore

- 110. High-Voltage Engineering: Theory and Practice, Second Edition, Revised and Expanded, *Mazen Abdel-Salam, Hussein Anis, Ahdab El-Morshedy, and Roshdy Radwan*

- 111. EMI Filter Design: Second Edition, Revised and Expanded, Richard Lee Ozenbaugh

- 112. Electromagnetic Compatibility: Principles and Applications, Second Edition, Revised and Expanded, *David Weston*

- 113. Permanent Magnet Motor Technology: Design and Applications, Second Edition, Revised and Expanded, Jacek F. Gieras and Mitchell Wing

- 114. High Voltage Circuit Breakers: Design and Applications, Second Edition, Revised and Expanded, *Ruben D. Garzon*

- 115. High Reliability Magnetic Devices: Design and Fabrication, Colonel Wm. T. McLyman

- 116. Practical Reliability of Electronic Equipment and Products, Eugene R. Hnatek

- 117. Electromagnetic Modeling by Finite Element Methods, João Pedro A. Bastos and Nelson Sadowski

- 118. Battery Technology Handbook, Second Edition, *edited by H. A. Kiehne*

- 119. Power Converter Circuits, William Shepherd and Li Zhang

- 120. Handbook of Electric Motors: Second Edition, Revised and Expanded, *edited by Hamid A. Toliyat and Gerald B. Kliman*

- 121. Transformer and Inductor Design Handbook, Colonel Wm T. McLyman

- 122. Energy Efficient Electric Motors: Selection and Application, Third Edition, Revised and Expanded, *Ali Emadi*

- 123. Power-Switching Converters, Second Edition, *Simon Ang* and Alejandro Oliva

- 124. Process Imaging For Automatic Control, edited by David M. Scott and Hugh McCann

- 125. Handbook of Automotive Power Electronics and Motor Drives, Ali Emadi

- 126. Adaptive Antennas and Receivers, *edited by* Melvin M. Weiner

- 127. SPICE for Power Electronics and Electric Power, Second Edition, *Muhammad H. Rashid and Hasan M. Rashid*

# SPICE FOR POWER Electronics and Electric Power

### SECOND EDITION

### MUHAMMAD H. RASHID

University of West Florida Pensacola, Florida, U.S.A.

### HASAN M. RASHID

University of Florida Gainesville, Florida, U.S.A.

A CRC title, part of the Taylor & Francis imprint, a member of the Taylor & Francis Group, the academic division of T&F Informa plc.

Published in 2006 by CRC Press Taylor & Francis Group 6000 Broken Sound Parkway NW, Suite 300 Boca Raton, FL 33487-2742

© 2006 by Taylor & Francis Group, LLC CRC Press is an imprint of Taylor & Francis Group

No claim to original U.S. Government works Printed in the United States of America on acid-free paper 10 9 8 7 6 5 4 3 2 1

International Standard Book Number-10: 0-8493-3418-7 (Hardcover) International Standard Book Number-13: 978-0-8493-3418-4 (Hardcover) Library of Congress Card Number 2005049658

This book contains information obtained from authentic and highly regarded sources. Reprinted material is quoted with permission, and sources are indicated. A wide variety of references are listed. Reasonable efforts have been made to publish reliable data and information, but the author and the publisher cannot assume responsibility for the validity of all materials or for the consequences of their use.

No part of this book may be reprinted, reproduced, transmitted, or utilized in any form by any electronic, mechanical, or other means, now known or hereafter invented, including photocopying, microfilming, and recording, or in any information storage or retrieval system, without written permission from the publishers.

For permission to photocopy or use material electronically from this work, please access www.copyright.com (http://www.copyright.com/) or contact the Copyright Clearance Center, Inc. (CCC) 222 Rosewood Drive, Danvers, MA 01923, 978-750-8400. CCC is a not-for-profit organization that provides licenses and registration for a variety of users. For organizations that have been granted a photocopy license by the CCC, a separate system of payment has been arranged.

Trademark Notice: Product or corporate names may be trademarks or registered trademarks, and are used only for identification and explanation without intent to infringe.

#### Library of Congress Cataloging-in-Publication Data

Rashid, M. H.

SPICE for power electronics and electric power / Muhammad H. Rashid, Hasan M. Rashid.-- 2nd ed.

p. cm. -- (Electrical and computer engineering ; 126) ISBN 0-8493-3418-7 (alk. paper)

1. Power electronics--Data processing, 2. Electronic circuit design--Data processing, 3. Electric

circuit analysis--Data processing. 4. SPICE (Computer file) I. Rashid, Hasan M. II. Title. III. Series.

TK7881.15.R38 2005 621.31'7'0285--dc22

2005049658

Visit the Taylor & Francis Web site at http://www.taylorandfrancis.com

Taylor & Francis Group is the Academic Division of T&F Informa plc.

and the CRC Press Web site at http://www.crcpress.com

To our family: Fa-eza, Farzana, and Hussain

## Preface

Power electronics is normally offered as a technical elective. It is an applicationoriented and interdisciplinary course that requires a background in mathematics, electrical circuits, control systems, analog and digital electronics, microprocessors, electric power, and electrical machines.

The understanding of the operation of a power electronics circuit requires a clear knowledge of the transient behavior of current and voltage waveforms for each and every circuit element at every instant of time.

These features make power electronics a difficult course for students to understand and for professors to teach. A laboratory helps in understanding power electronics and its control interfacing circuits. Development of a power electronics laboratory is relatively expensive compared to other courses in power electronics– electronic power (EE) curriculum. Power electronics is playing a key role in industrial power control.

The Engineering Accreditation Commission of the Accreditation Board for Engineering and Technology (EAC/ABET) requirements specify the computer integration and design content in the EE curriculum. To be competitive, a power electronics course should integrate a design content of approximately 50% and an extensive use of computer-aided analysis.

The student version of PSpice, which is available free to students, is ideal for classroom use and for assignments requiring computer-aided simulation and analysis. Without any additional resources and lecture time, PSpice can also be integrated into power electronics.

Probe is a graphics postprocessor in PSpice and is very useful in plotting the results of simulation. Especially with the capability of arithmetic operation, it can be used to plot impedance, power, etc. Once the students get experience in simulating on PSpice, they really appreciate the advantages of the .PROBE command. Probe is an option of PSpice, but it comes with the student version. Running Probe does not require a math coprocessor. Students can also opt for the normal printer output or printer plotting. The prints and plots are very helpful in relating students' theoretical understanding and making judgments on the merits of a circuit and its characteristics.

Probe is like a theoretical oscilloscope with the special features to perform arithmetic operations. It can be used as a laboratory bench to view the waveforms of currents, voltages, power, power factor, etc., with Fourier analysis giving the total harmonic distortion (THD) of any waveform.

The capability of Probe, along with other data representation features such as Table, Value, Function, Polynomial, Laplace, Param, and Step, makes PSpice

a versatile simulation tool for EE courses. Students can design power electronics circuits, use the PSpice simulator to verify the design, and make necessary design modifications. In the absence of a dedicated power electronics laboratory, the laboratory assignments could be design problems to be simulated and verified by PSpice.

This book is based on the author's experience in integrating 50% design content and SPICE on a power electronics course of 3 credit hours. The students were assigned design problems and asked to use PSpice to verify their designs by plotting or printing the output waveforms and to confirm the ratings of devices and components by plotting the instantaneous voltage, current, and power. The objective of this book is to integrate the SPICE simulator with a power electronics course at the junior level or senior level with a minimum amount of time and effort. This book assumes no prior knowledge about the SPICE simulator and introduces the applications of various SPICE commands through numerous examples of power electronics circuits.

This book can be divided into nine parts: (1) introduction to SPICE simulation — Chapter 1 to Chapter 3; (2) source and element modeling — Chapter 4 and Chapter 5; (3) SPICE commands — Chapter 6; (4) rectifiers — Chapter 7 and Chapter 11; (5) DC–DC converters — Chapter 8; (6) inverters — Chapter 9 and Chapter 10; (7) AC voltage controllers — Chapter 12; (8) control applications — Chapter 13 and Chapter 14; and (9) difficulties — Chapter 15. Chapter 7 to Chapter 12 use simple models for power semiconductor switches, leaving the complex models for special projects and assignments. Chapter 14 uses the simple circuit models of DC motors and AC inductor motors to predict their control characteristics. Two reference tables are included to aid in choosing a device, component, or command.

This book is intended to demonstrate the techniques for power conversions and the quality of the output waveforms, rather than the accurate modeling of power semiconductor devices. This approach has the advantage that the students can compare the results with those obtained in a classroom environment with simple switch models of devices.

This book can be used as a textbook on SPICE for students specializing in power electronics and power systems. It can also be a supplement to any standard textbook on power electronics and power systems. The following sequence is recommended:

- 1. Supplement to a basic power systems (or electrical machine) course with three hours of lectures (or equivalent lab hours) and self-study assignments from Chapter 1 to Chapter 6. Starting from Chapter 2, the students should work with PCs.

- 2. Continue as a supplement to a power electronics course with two hours of lectures (or equivalent lab hours) and self-study assignments from Chapter 7 to Chapter 14.

Without any prior experience on SPICE and integrating SPICE at the power electronics level, two hours of lectures (or equivalent lab hours) are recommended on Chapter 1 to Chapter 6. Chapter 7 to Chapter 14 could be left for self-study assignments. From the author's experience in the class, it has been observed that after two lectures of 50 min duration, all students could solve assignments independently without any difficulty. The class could progress in a normal manner with one assignment per week on power electronics circuits simulation and analysis with SPICE.

The book has sections on suggested laboratory experiments and design problems on power electronics. The complete laboratory guidelines for each experiment are presented. Thus, the book can also be used as a laboratory manual for power electronics. The design problems can be used as assignments for a designoriented simulation laboratory.

Although the materials on this book have been developed for engineering students, the book is also strongly recommended for EET students specializing in power electronics, and power systems.

Any comments and suggestions regarding this book are welcomed and should be sent to the author.

Dr. Muhammad H. Rashid Professor and Director Electrical and Computer Engineering University of West Florida 11000 University Parkway Pensacola, Florida 32514–5754,USA E-mail: mrashid@uwf.edu

> Muhammad H. Rashid Hasan M. Rashid Pensacola, Florida

## The Authors

Muhammad H. Rashid is employed by the University of Florida as Professor of Electrical and Computer Engineering and Director of the UF/UWF Joint Program in Electrical and Computer Engineering. Dr. Rashid received a B.Sc. degree in Electrical Engineering from the Bangladesh University of Engineering and Technology, and M.Sc. and Ph.D. degrees from the University of Birmingham in the UK. Previously, he worked as Professor of Electrical Engineering and Chair of the Engineering Department at Indiana University-Purdue University Fort Wayne. He also worked as Visiting Assistant Professor of Electrical Engineering at the University of Connecticut, Associate Professor of Electrical Engineering at Concordia University (Montreal, Canada), Professor of Electrical Engineering at Purdue University Calumet, and Visiting Professor of Electrical Engineering at King Fahd University of Petroleum and Minerals (Saudi Arabia), as a design and development engineer with Brush Electrical Machines Ltd. (England, UK), a Research Engineer with Lucas Group Research Centre (England, UK), and a Lecturer and Head of Control Engineering Department at the Higher Institute of Electronics (Malta).

Dr. Rashid is actively involved in teaching, researching, and lecturing in power electronics. He has published 16 books and more than 130 technical papers. His books are adopted as textbooks all over the world. One of his books, titled *Power Electronics*, has translations in Spanish, Portuguese, Indonesian, Korean, and Persian. Another of his works, Microelectronics, has translations in Spanish in Mexico and Spain. He has had many invitations from foreign governments and agencies to be keynote lecturer and consultant, from foreign universities to serve as an external Ph.D. examiner, and from funding agencies to review research proposals. His contributions in education are recognized by foreign governments and agencies to lecture and consult (NATO for Turkey in 1994, UNDP for Bangladesh in 1989 and 1994, Saudi Arabia in 1993, Pakistan in 1993, Malaysia in 1995 and 2002, Bangkok in 2002), by foreign universities (in Australia, Canada, Hong Kong, India, Malaysia, Singapore) to serve as an external examiner (for undergraduate, master's and Ph.D. examinations), by funding agencies (in Australia, Canada, USA, Hong Kong) to review research proposals, and by U.S. and foreign universities to evaluate promotion cases for professorship.

Dr. Rashid has authored nine Prentice Hall books: *Power Electronics* — *Circuits, Devices and Applications* (1988, 2/e 1993, 2003, 3/e), *SPICE for Power Electronics* (1993), *SPICE for Circuits and Electronics Using PSpice* (1990, 2/e 1995, 2003, 3/e), *Electromechanical and Electrical Machinery* (1986), and

Engineering Design for Electrical Engineers (1990). He has also authored five IEEE self-study guides, Self-Study Guide on Fundamentals of Power Electronics, Power Electronics Laboratory Using PSpice, Selected Readings on SPICE Simulation of Power Electronics, and Selected Readings on Power Electronics (IEEE Press, 1996) and Microelectronics Laboratory Using Electronics Workbench (IEEE Press, 2000). In addition, he has authored two books, Electronic Circuit Design using Electronics Workbench (January 1998) and Microelectronic Circuits — Analysis and Design (April 1999) by PWS Publishing, and has edited Power Electronics Handbook published by Academic Press (2001).

Dr. Rashid is a registered Professional Engineer in the Province of Ontario (Canada), a registered Chartered Engineer (UK), a Fellow of the Institution of Electrical Engineers (IEE, UK) and a Fellow of the Institute of Electrical and Electronics Engineers (IEEE, USA). He was elected as an IEEE Fellow with the citation "Leadership in power electronics education and contributions to the analysis and design methodologies of solid-state power converters." Dr. Rashid is the recipient of the 1991 Outstanding Engineer Award from The Institute of Electrical and Electronics Engineers (IEEE). He received the 2002 IEEE Educational Activity Award (EAB) Meritorious Achievement Award in Continuing Education with the citation "for contributions to the design and delivery of continuing education in power electronics and computer-aided-simulation." Dr. Rashid was an ABET program evaluator for electrical engineering from 1995 to 2000 and he is currently an engineering evaluator for the Southern Association of Colleges and Schools (SACS, USA). He has been elected as an IEEE-Industry Applications Society (IAS) a Distinguished Lecturer and Speaker. He is the Series Editor for Power Electronics and Applications, and Nanotechnology and Applications with CRC Press. He is also Editor-in-Chief of the Electric Power and Energy Series with Elsevier Publishing.

**Hasan M. Rashid** is a graduate student and Teaching Assistant since 2003 in the Department of Electrical and Computer Engineering, University of Florida. He received his BS degree in electrical engineering with Highest Honors from the University of Florida. He was designated as a University Scholar for the UF Undergraduate Research Initiative and completed a research project titled "Synthetic Ripple Design for Buck Converter." He designed, built, and tested a feedback converter (with higher than 80% efficiency) and reported his research in a paper titled "Design of an Efficient Half-Bridge Converter." He also completed a group project titled "Electronic Nose Based on Micro Mechanical Cantilever Arrays."

Mr. Rashid was on the Dean's List every Fall and Spring semester in the College of Engineering. He is a Member of Tau Beta Pi Engineering Honors Society and an Anderson Scholar. He was a Florida Bright Futures Scholar, Top Florida Scholar, and Valedictorian of his high school class in 2000.

# Acknowledgments

We would like to thank the following reviewers for their comments and suggestions:

Frederick C. Brockhurst, Rose–Hulman Institute of Technology A. P. Saki Meliopoulos, Georgia Institute of Technology Peter Lauritzen, University of Washington Saburo Matsusaki, TDK Corporation, Japan

It has been a great pleasure working with the editorial staff: Nora Konopka, Helena Redshaw, and B. J. Clark. Finally, we would like to thank our family for their love, patience, and understanding.

# PSpice Software and Program Files

The enclosed CD contains (a) the user-defined model library file Rashid\_SP2\_MODEL.LIB and (b) all PSpice circuit files (with an extension .CIR) in the folder Rashid\_SP2\_AD Circuits, PSpice Schematics (with an extension .SCH) in the folder Rashid\_SP2\_PSpice\_Schematics, and OrCAD Capture files (with extensions .OPJ and .DSN) in the folder Rashid\_SP2\_Orcad\_Capture for use with the book. PSpice Schematics and OrCAD Capture software can be obtained or downloaded from

Cadence Design Systems, Inc. 2655 Seely Avenue San Jose, CA 95134 Websites: http://www.cadence.com http://www.orcad.com http://www.pspice.com http://www.ema-eda.com

#### **IMPORTANT NOTES**

The PSpice circuit files (with an extension .CIR) are self-contained, and each file contains the necessary devices or component models. However, the PSpice Schematics files (with an extension .SCH) need the user-defined model library file Rashid\_SP23\_MODEL.LIB, which is included with the PSpice Schematic files and must be included from the Analysis menu of PSpice Schematics. Similarly, the OrCAD Capture files (with extensions .OPJ and .DSN) also need the user-defined model library file Rashid\_SP2\_MODEL.LIB, which is included with the Orcad Schematic files and must be included from the PSpice Simulation settings menu of the OrCAD Capture. If these files are not included, the simulation will not run and errors will occur.

For importing PSpice Schematics files to OrCAD Capture files, OrCAD Capture will require specifying the location of the msim\_evl.ini file. OrCAD Capture folder may not have the msim\_evl.ini file, and you must find the location of that file in your computer. If you cannot locate the file, you can copy the msim\_evl.ini file from the enclosed CD to your window folder C:\WINNT so that its location becomes C:\WINNT\msim\_evl.ini.

# Table of Contents

|                                                                                                       | pter 1 Introduction                                                                                                                                                                                                                                                                                            | 1                                      |

|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 1.1                                                                                                   | Introduction                                                                                                                                                                                                                                                                                                   | 1                                      |

| 1.2                                                                                                   | Descriptions of SPICE                                                                                                                                                                                                                                                                                          | 2                                      |

| 1.3                                                                                                   | Types of Spice                                                                                                                                                                                                                                                                                                 | 2                                      |

| 1.4                                                                                                   | Types of Analysis                                                                                                                                                                                                                                                                                              |                                        |

| 1.5                                                                                                   | Limitations of PSpice                                                                                                                                                                                                                                                                                          |                                        |

| 1.6                                                                                                   | Descriptions of Simulation Software Tools                                                                                                                                                                                                                                                                      |                                        |

| 1.7                                                                                                   | PSpice Platform                                                                                                                                                                                                                                                                                                |                                        |

|                                                                                                       | 1.7.1 PSpice A/D                                                                                                                                                                                                                                                                                               |                                        |

|                                                                                                       | 1.7.2 PSpice Schematics                                                                                                                                                                                                                                                                                        |                                        |

|                                                                                                       | 1.7.3 OrCAD Capture                                                                                                                                                                                                                                                                                            |                                        |

| 1.8                                                                                                   | PSpice Schematics vs. OrCAD Capture                                                                                                                                                                                                                                                                            |                                        |

| 1.9                                                                                                   | SPICE Resources                                                                                                                                                                                                                                                                                                |                                        |

|                                                                                                       | 1.9.1 Web Sites with Free SPICE Models                                                                                                                                                                                                                                                                         |                                        |

|                                                                                                       | 1.9.2 Web Sites with SPICE Models                                                                                                                                                                                                                                                                              |                                        |

|                                                                                                       | 1.9.3 SPICE and Circuit Simulation Information Sites                                                                                                                                                                                                                                                           |                                        |

|                                                                                                       | 1.9.4 Engineering Magazines with SPICE Articles                                                                                                                                                                                                                                                                |                                        |

| Sugg                                                                                                  | ested Reading                                                                                                                                                                                                                                                                                                  | 12                                     |

| Char                                                                                                  | pter 2 Circuit Descriptions                                                                                                                                                                                                                                                                                    | 15                                     |

| Chap                                                                                                  |                                                                                                                                                                                                                                                                                                                |                                        |

| 2.1                                                                                                   | Introduction                                                                                                                                                                                                                                                                                                   |                                        |

|                                                                                                       |                                                                                                                                                                                                                                                                                                                |                                        |

| 2.2                                                                                                   | Input Files                                                                                                                                                                                                                                                                                                    | 15                                     |

| 2.3                                                                                                   | Input Files<br>Nodes                                                                                                                                                                                                                                                                                           | 15<br>17                               |

| 2.3<br>2.4                                                                                            | Input Files<br>Nodes<br>Element Values                                                                                                                                                                                                                                                                         | 15<br>17<br>17                         |

| 2.3<br>2.4<br>2.5                                                                                     | Input Files<br>Nodes<br>Element Values<br>Circuit Elements                                                                                                                                                                                                                                                     | 15<br>17<br>17<br>17<br>19             |

| <ol> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>2.6</li> </ol>                                        | Input Files<br>Nodes<br>Element Values<br>Circuit Elements<br>Element Models                                                                                                                                                                                                                                   | 15<br>17<br>17<br>17<br>19<br>20       |

| <ol> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>2.6</li> <li>2.7</li> </ol>                           | Input Files<br>Nodes<br>Element Values<br>Circuit Elements<br>Element Models<br>Sources                                                                                                                                                                                                                        | 15<br>17<br>17<br>17<br>19<br>20<br>21 |

| <ol> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>2.6</li> <li>2.7</li> <li>2.8</li> </ol>              | Input Files<br>Nodes<br>Element Values<br>Circuit Elements<br>Element Models<br>Sources<br>Output Variables                                                                                                                                                                                                    |                                        |

| <ol> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>2.6</li> <li>2.7</li> <li>2.8</li> <li>2.9</li> </ol> | Input Files<br>Nodes<br>Element Values<br>Circuit Elements<br>Element Models<br>Sources<br>Output Variables<br>Types of Analysis                                                                                                                                                                               |                                        |

| 2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10                                                 | Input Files<br>Nodes<br>Element Values<br>Circuit Elements<br>Element Models<br>Sources<br>Output Variables<br>Types of Analysis<br>PSpice Output Commands                                                                                                                                                     |                                        |

| 2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10<br>2.11                                         | Input Files<br>Nodes<br>Element Values<br>Circuit Elements<br>Element Models<br>Sources<br>Output Variables<br>Types of Analysis<br>PSpice Output Commands<br>Format of Circuit Files                                                                                                                          |                                        |

| 2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10<br>2.11<br>2.12                                 | Input FilesNodes<br>Nodes<br>Element Values<br>Circuit Elements<br>Element Models<br>Sources<br>Output Variables<br>Types of Analysis<br>PSpice Output Commands<br>Format of Circuit Files.<br>Format of Output Files.                                                                                         |                                        |

| 2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10<br>2.11<br>2.12<br>2.13                         | Input Files<br>Nodes<br>Element Values<br>Circuit Elements<br>Element Models<br>Sources<br>Output Variables<br>Types of Analysis<br>PSpice Output Commands<br>Format of Circuit Files<br>Format of Output Files<br>Examples of PSpice Simulations                                                              |                                        |

| 2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10<br>2.11<br>2.12                                 | Input Files<br>Nodes<br>Element Values<br>Circuit Elements<br>Element Models<br>Sources<br>Output Variables<br>Types of Analysis<br>PSpice Output Commands<br>Format of Circuit Files<br>Format of Output Files<br>Examples of PSpice Simulations<br>PSpice Schematics                                         |                                        |

| 2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10<br>2.11<br>2.12<br>2.13                         | Input FilesNodes<br>Nodes<br>Element Values<br>Circuit Elements<br>Element Models<br>Sources<br>Output Variables<br>Types of Analysis<br>PSpice Output Commands<br>Format of Circuit Files<br>Format of Output Files<br>Examples of PSpice Simulations<br>PSpice Schematics<br>2.13.1 PSpice Schematics Layout |                                        |

| 2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10<br>2.11<br>2.12<br>2.13                         | Input Files<br>Nodes<br>Element Values<br>Circuit Elements<br>Element Models<br>Sources<br>Output Variables<br>Types of Analysis<br>PSpice Output Commands<br>Format of Circuit Files<br>Format of Output Files<br>Examples of PSpice Simulations<br>PSpice Schematics                                         |                                        |

| 2.14 1 | Importing Microsim Schematics in OrCAD Capture | 45 |

|--------|------------------------------------------------|----|

|        | sted Reading                                   |    |

| 00     | ems                                            |    |

| Cha | pter 3 | Defining Output Variables                    | 53 |

|-----|--------|----------------------------------------------|----|

| 3.1 | Introd | uction                                       | 53 |

| 3.2 | DC S   | weep and Transient Analysis                  | 53 |

|     | 3.2.1  | Voltage Output                               |    |

|     | 3.2.2  | Current Output                               |    |

|     | 3.2.3  | Power Output                                 | 56 |

| 3.3 | AC A   | nalysis                                      | 59 |

|     | 3.3.1  | Voltage Output                               | 59 |

|     | 3.3.2  | Current Output                               | 59 |

| 3.4 | Outpu  | It Markers                                   | 61 |

| 3.5 | Noise  | Analysis                                     | 61 |

| 3.6 | Summ   | nary                                         | 62 |

| Cha | pter 4 | Voltage and Current Sources                  | 65 |

| 4.1 | _      | uction                                       |    |

| 4.2 |        | es Modeling                                  |    |

| 7.2 | 4.2.1  | Pulse Source                                 |    |

|     | 7.2.1  | 4.2.1.1 Typical Statements                   |    |

|     | 4.2.2  | Piecewise Linear Source                      |    |

|     |        | 4.2.2.1 Typical Statement                    |    |

|     | 4.2.3  | Sinusoidal Source                            |    |

|     |        | 4.2.3.1 Typical Statements                   |    |

|     | 4.2.4  | Exponential Source                           |    |

|     |        | 4.2.4.1 Typical Statements                   |    |

|     | 4.2.5  | Single-Frequency Frequency Modulation Source |    |

|     |        | 4.2.5.1 Typical Statements                   |    |

| 4.3 | Indepe | endent Sources                               |    |

|     | 4.3.1  | Independent Voltage Source                   |    |

|     |        | 4.3.1.1 Typical Statements                   |    |

|     | 4.3.2  | Independent Current Source                   |    |

|     |        | 4.3.2.1 Typical Statements                   |    |

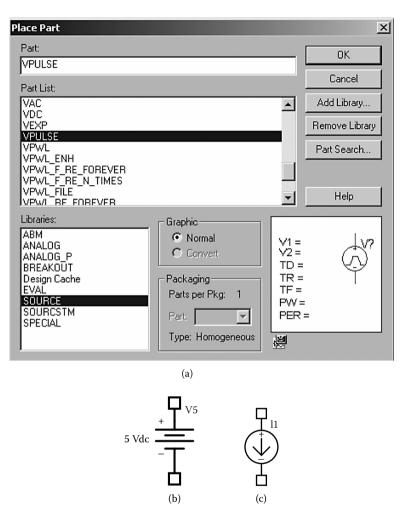

|     | 4.3.3  | Schematic Independent Sources                |    |

| 4.4 | Deper  | ident Sources                                |    |

|     | 4.4.1  | Polynomial Source                            |    |

|     |        | 4.4.1.1 Typical Model Statements             |    |

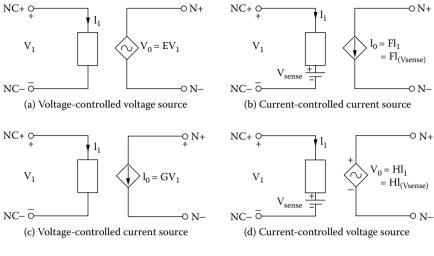

|     | 4.4.2  | Voltage-Controlled Voltage Source            |    |

|     |        | 4.4.2.1 Typical Statements                   |    |

|     | 4.4.3  | Current-Controlled Current Source            |    |

|       | 4.4.4   | Voltage-Controlled Current Source | 80 |

|-------|---------|-----------------------------------|----|

|       |         | 4.4.4.1 Typical Statements        | 80 |

|       | 4.4.5   | Current-Controlled Voltage Source | 81 |

|       |         | 4.4.5.1 Typical Statements        | 82 |

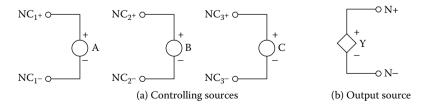

|       | 4.4.6   | Schematic Dependent Sources       | 82 |

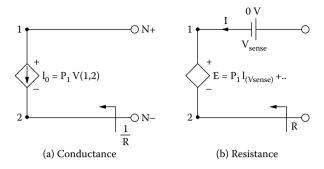

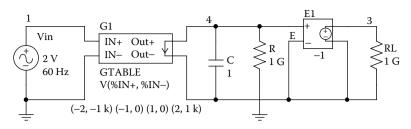

| 4.5   | Behav   | ioral Device Modeling             | 82 |

|       | 4.5.1   | VALUE                             | 84 |

|       |         | 4.5.1.1 Typical Statements        | 85 |

|       | 4.5.2   | TABLE                             | 86 |

|       |         | 4.5.2.1 Typical Statements        | 86 |

|       | 4.5.3   | LAPLACE                           | 87 |

|       |         | 4.5.3.1 Typical Statements        | 87 |

|       | 4.5.4   | FREQ                              |    |

|       |         | 4.5.4.1 Typical Statements        |    |

| Sumn  | nary    | ••                                |    |

| Sugge | ested R | leading                           | 89 |

|       |         | ~                                 |    |

| Chap | oter 5  | Passive Elements                    | 95  |

|------|---------|-------------------------------------|-----|

| 5.1  | Introdu | uction                              | 95  |

| 5.2  | Model   | ing of Elements                     | 95  |

|      | 5.2.1   | Some Model Statements               | 97  |

| 5.3  | Operat  | ting Temperature                    | 98  |

|      | 5.3.1   | Some Temperature Statements         | 98  |

| 5.4  | RLC E   | Elements                            |     |

|      | 5.4.1   | Resistor                            | 98  |

|      |         | 5.4.1.1 Some Resistor Statements    | 101 |

|      | 5.4.2   | Capacitor                           | 101 |

|      |         | 5.4.2.1 Some Capacitor Statements   | 102 |

|      | 5.4.3   | Inductor                            | 102 |

|      |         | 5.4.3.1 Some Inductor Statements    | 104 |

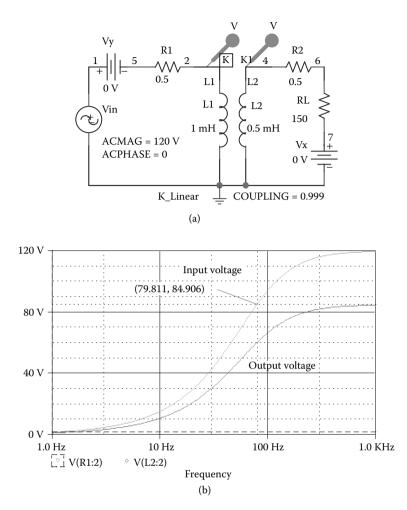

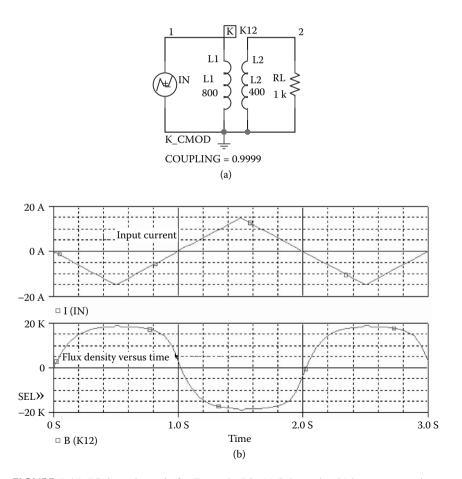

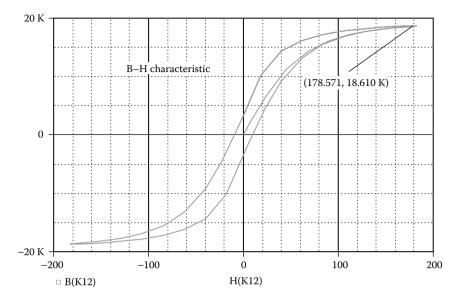

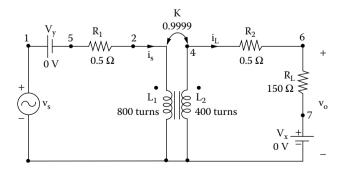

| 5.5  | Magne   | etic Elements and Transformers      | 106 |

|      | 5.5.1   | Linear Magnetic Circuits            | 107 |

|      | 5.5.2   | Nonlinear Magnetic Circuits         | 111 |

| 5.6  | Lossle  | ss Transmission Lines               |     |

| 5.7  | Switch  | nes                                 | 119 |

|      | 5.7.1   | Voltage-Controlled Switch           | 121 |

|      | 5.7.2   | Current-Controlled Switch           | 124 |

|      | 5.7.3   | Time-Dependent Switches             | 127 |

|      |         | 5.7.3.1 Time-Dependent Close Switch | 128 |

|      |         | 5.7.3.2 Time-Dependent Open Switch  | 128 |

| Sum  | nary    |                                     | 128 |

| Sugg | ested R | eading                              | 131 |

|      |         | -                                   |     |

| Chap  | oter 6            | Dot Commands                         | 137 |  |  |

|-------|-------------------|--------------------------------------|-----|--|--|

| 6.1   | Introdu           | uction                               | 137 |  |  |

| 6.2   | Model             | S                                    | 137 |  |  |

|       | 6.2.1             | .MODEL (Model)                       | 138 |  |  |

|       | 6.2.2             | .SUBCKT (Subcircuit)                 | 138 |  |  |

|       | 6.2.3             | .ENDS (End of Subcircuit)            | 139 |  |  |

|       | 6.2.4             | .FUNC (Function)                     | 140 |  |  |

|       | 6.2.5             | .GLOBAL (Global)                     | 141 |  |  |

|       | 6.2.6             | .LIB (Library File)                  | 142 |  |  |

|       | 6.2.7             | .INC (Include File)                  | 143 |  |  |

|       | 6.2.8             | .PARAM (Parameter)                   | 144 |  |  |

|       | 6.2.9             | .STEP (Parametric Analysis)          | 145 |  |  |

| 6.3   | Types             | of Output                            | 147 |  |  |

|       | 6.3.1             | .PRINT (Print)                       | 148 |  |  |

|       | 6.3.2             | .PLOT (Plot)                         | 148 |  |  |

|       | 6.3.3             | .PROBE (Probe)                       | 149 |  |  |

|       |                   | Probe Statements                     | 150 |  |  |

|       | 6.3.4             | Probe Output                         | 150 |  |  |

|       | 6.3.5             | .WIDTH (Width)                       | 154 |  |  |

| 6.4   | Operat            | ting Temperature and End of Circuit  | 154 |  |  |

| 6.5   | Option            | 18                                   | 155 |  |  |

| 6.6   | DC Ar             | nalysis                              | 156 |  |  |

|       | 6.6.1             | .OP (Operating Point)                |     |  |  |

|       | 6.6.2             | .NODESET (Nodeset)                   | 158 |  |  |

|       | 6.6.3             | .SENS (Sensitivity Analysis)         | 159 |  |  |

|       | 6.6.4             | .TF (Small-Signal Transfer Function) |     |  |  |

|       | 6.6.5             | .DC (DC Sweep)                       |     |  |  |

| 6.7   |                   | nalysis                              |     |  |  |

| 6.8   |                   | Analysis                             |     |  |  |

| 6.9   | Transi            | ent Analysis                         |     |  |  |

|       | 6.9.1             | .IC (Initial Transient Conditions)   |     |  |  |

|       | 6.9.2             | .TRAN (Transient Analysis)           |     |  |  |

| 6.10  |                   | r Analysis                           |     |  |  |

| 6.11  |                   | Carlo Analysis                       |     |  |  |

|       |                   | ivity and Worst-Case Analysis        |     |  |  |

|       |                   |                                      |     |  |  |

| 00    | Suggested Reading |                                      |     |  |  |

| Probl | ems               |                                      | 196 |  |  |

|       |                   |                                      |     |  |  |

| Cha | pter 7 | Diode Rectifiers |     |

|-----|--------|------------------|-----|

| 7.1 | Introd | uction           | 201 |

| 7.2 | Diode  | Model            |     |

| 7.3 | Diode  | Statement        |     |

| 7.4  | Diode | Characteristics                                | 204 |

|------|-------|------------------------------------------------|-----|

| 7.5  | Diode | Parameters                                     |     |

|      | 7.5.1 | Modeling Zener Diodes                          | 210 |

|      | 7.5.2 | Tabular Data                                   | 211 |

| 7.6  | Diode | Rectifiers                                     | 214 |

| 7.7  | Labor | atory Experiments                              | 234 |

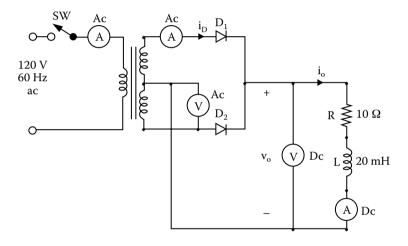

|      | 7.7.1 | Experiment DR.1                                |     |

|      |       | Single-Phase Full-Wave Center-Tapped Rectifier |     |

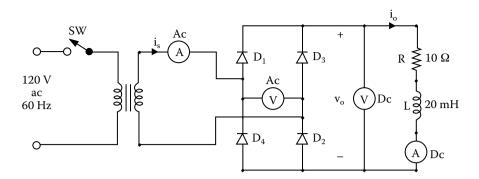

|      | 7.7.2 | Experiment DR.2                                |     |

|      |       | Single-Phase Bridge Rectifier                  |     |

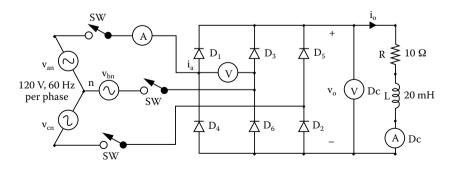

|      | 7.7.3 | Experiment DR.3                                |     |

|      |       | Three-Phase Bridge Rectifier                   |     |

| 7.8  | Sumn  | nary                                           |     |

| Sugg |       | Reading                                        |     |

|      |       | olems                                          |     |

| Chap | oter 8 DC–DC Converters     |  |

|------|-----------------------------|--|

| 8.1  | Introduction                |  |

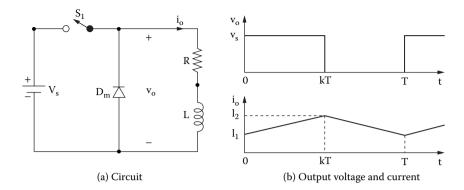

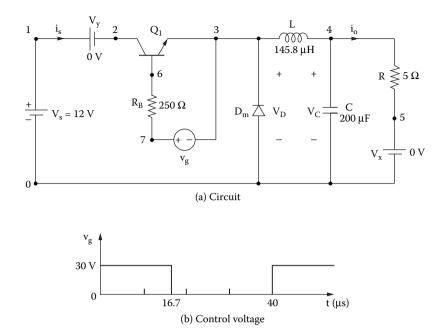

| 8.2  | DC Switch Chopper           |  |

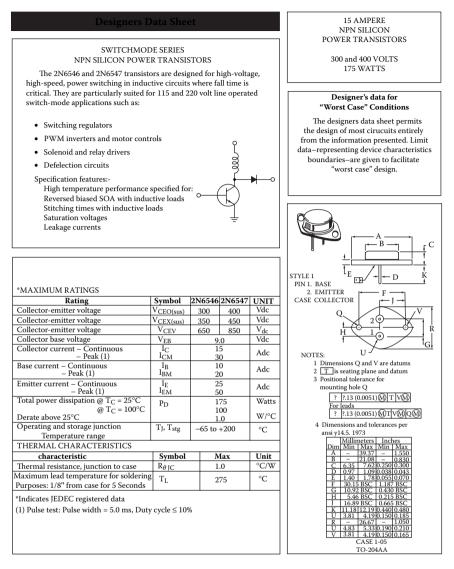

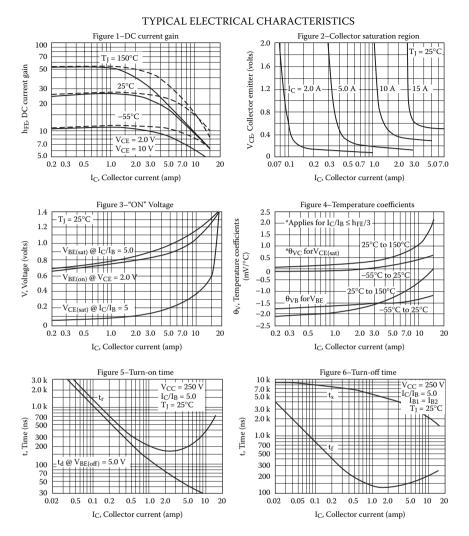

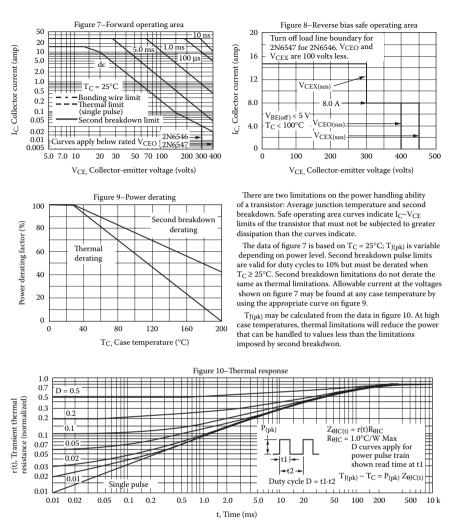

| 8.3  | BJT SPICE Model             |  |

| 8.4  | BJT Parameters              |  |

| 8.5  | Examples of BJT Choppers    |  |

| 8.6  | MOSFET Choppers             |  |

| 8.7  | MOSFET Parameters           |  |

| 8.8  | Examples of MOSFET Choppers |  |

| 8.9  | IGBT Model                  |  |

| 8.10 | Laboratory Experiment       |  |

|      | 8.10.1 Experiment TP.1      |  |

|      | DC Buck Chopper             |  |

|      | 8.10.2 Experimental TP-2    |  |

|      | DC Boost Chopper            |  |

| 8.11 | Summary                     |  |

|      | ested Reading               |  |

|      | gn Problems                 |  |

| Cha | pter 9 | Pulse-Width-Modulated Inverters   |  |

|-----|--------|-----------------------------------|--|

| 9.1 | Introd | luction                           |  |

| 9.2 | Volta  | ge-Source Inverters               |  |

|     |        | ent-Source Inverters              |  |

|     | Labor  | ratory Experiments                |  |

|     | 9.4.1  | Experiment PW.1                   |  |

|     |        | Single-Phase Half-Bridge Inverter |  |

|     |        |                                   |  |

|      | 9.4.2   | Experiment PW.2                                     | 319 |

|------|---------|-----------------------------------------------------|-----|

|      |         | Single-Phase Full-Bridge Inverter                   | 319 |

|      | 9.4.3   | Experiment PW.3                                     |     |

|      |         | Single-Phase Full-Bridge Inverter with PWM Control  | 319 |

|      | 9.4.4   | Experiment PW.4                                     |     |

|      |         | Single-Phase Full-Bridge Inverter with SPWM Control | 320 |

|      | 9.4.5   | Experiment PW.5                                     | 320 |

|      |         | Three-Phase Bridge Inverter                         | 320 |

|      | 9.4.6   | Experiment PW.6                                     | 321 |

|      |         | Single-Phase Current-Source Inverter                | 321 |

|      | 9.4.7   | Experiment PW.7                                     | 322 |

|      |         | Three-Phase Current-Source Inverter                 |     |

| Sum  | mary    |                                                     | 324 |

| Sugg | ested R | leading                                             | 324 |

|      |         | lems                                                |     |

|      | -       |                                                     |     |

| Cha  | oter 10 | Resonant-Pulse Inverters                            |     |

|      |         |                                                     |     |

|      |         | uction                                              |     |

|      |         | ant-Pulse Inverters                                 |     |

|      |         | Current Switching Converters (ZCSC)                 |     |

|      |         | Voltage Switching Converter (ZVSC)                  |     |

| 10.5 |         | atory Experiments                                   |     |

|      | 10.5.1  | Experiment RI.1                                     |     |

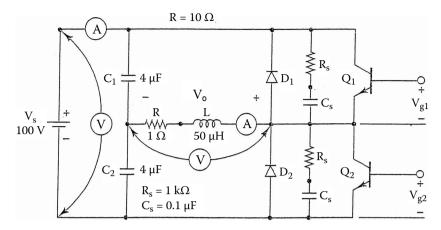

|      | 10.5.0  | Single-Phase Half-Bridge Resonant Inverter          |     |

|      | 10.5.2  | Experiment RI.2                                     |     |

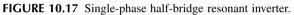

|      | 10 5 3  | Single-Phase Full-Bridge Resonant Inverter          |     |

|      | 10.5.3  | Experiment RI.3                                     |     |

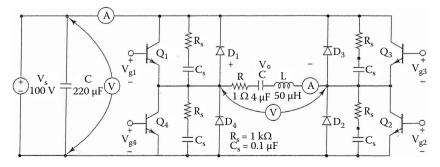

|      |         | Push–Pull Inverter                                  |     |

|      | 10.5.4  | Experiment RI.4                                     |     |

|      |         | Parallel Resonant Inverter                          |     |

|      | 10.5.5  | Experiment RI.5                                     |     |

|      |         | ZCSC                                                |     |

|      | 10.5.6  | Experiment RI.6                                     |     |

|      | _       | ZVSC                                                |     |

|      |         | ary                                                 |     |

| 00   |         | Leading                                             |     |

| Desi | gn Prot | lems                                                | 350 |

| ~    |         |                                                     |     |

| Chaj | pter 11 | Controlled Rectifiers                               | 355 |

| 11.1 | Introd  | uction                                              | 355 |

| 11.2 |         | nyristor Model                                      |     |

| 11.3 |         | bled Rectifiers                                     |     |

| 11.4 |         | oles of Controlled Rectifiers                       |     |

|      |         | ned Thyristor DC Model                              |     |

|      |         |                                                     |     |

| 11.6  | GTO Thyristor Model                         |     |

|-------|---------------------------------------------|-----|

| 11.7  | Example of Forced-Commutated Rectifiers     |     |

| 11.8  | Laboratory Experiments                      |     |

|       | 11.8.1 Experiment TC.1                      |     |

|       | Single-Phase Half-Wave Controlled Rectifier |     |

|       | 11.8.2 Experiment TC.2                      |     |

|       | Single-Phase Full-Wave Controlled Rectifier |     |

|       | 11.8.3 Experiment TC.3                      |     |

|       | Three-Phase Full-Wave Controlled Rectifier  |     |

| Sumn  | nary                                        |     |

| Sugge | ested Reading                               |     |

| Desig | n Problems                                  |     |

| Chan  | ter 12 AC Voltage Controllers               |     |

| _     | Introduction                                |     |

|       |                                             |     |

|       | AC Thyristor Model                          |     |

|       | AC Voltage Controllers                      |     |

|       | Examples of AC Voltage Controllers          |     |

| 12.5  | Laboratory Experiments                      |     |

|       | 12.5.1 Experiment AC.1                      |     |

|       | Single-Phase AC Voltage Controller          |     |

|       | 12.5.2 Experiment AC.2                      |     |

| 10.0  | Three-Phase AC Voltage Controller           |     |

|       | Summary                                     |     |

|       | ested Reading                               |     |

| Desig | n Problems                                  |     |

| Chap  | ter 13 Control Applications                 |     |

| 13.1  | Introduction                                |     |

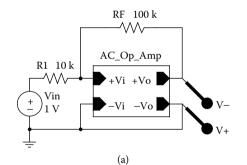

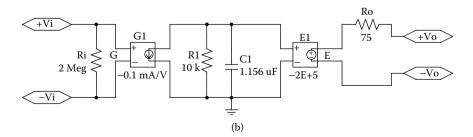

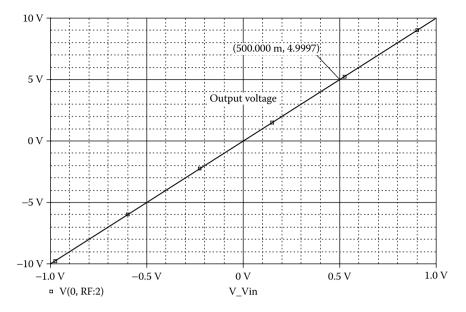

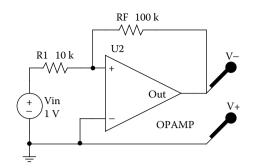

| 13.2  | Op-Amp Circuits                             |     |

|       | 13.2.1 DC Linear Models                     |     |

|       | 13.2.2 AC Linear Models                     |     |

|       | 13.2.3 Nonlinear Macromodels                |     |

| 13.3  | Control Systems                             |     |

| 13.4  | Signal Conditioning                         |     |

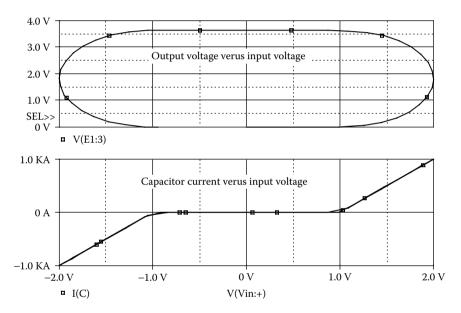

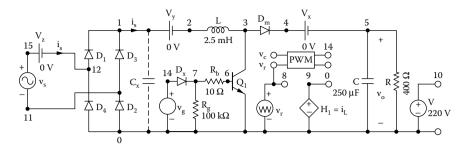

| 13.5  | Closed-Loop Current Control                 |     |

|       | ested Reading                               |     |

|       | ems                                         |     |

| Chap  | ter 14 Characteristics of Electrical Motors |     |

| 14.1  | Introduction                                | 183 |

|       | DC Motor Characteristics                    |     |

| 14.4  |                                             |     |

| Suggested Reading | 494 |

|-------------------|-----|

| Problems          |     |

### Chapter 15 Simulation Errors, Convergence Problems, and Other Difficulties

| Difficulties                                      |     |

|---------------------------------------------------|-----|

| 15.1 Introduction                                 |     |

| 15.2 Large Circuits                               |     |

| 15.3 Running Multiple Circuits                    |     |

| 15.4 Large Outputs                                |     |

| 15.5 Long Transient Runs                          |     |

| 15.6 Convergence                                  |     |

| 15.6.1 DC Sweep                                   |     |

| 15.6.2 Bias-Point Calculation                     |     |

| 15.6.3 Transient Analysis                         | 504 |

| 15.7 Analysis Accuracy                            | 505 |

| 15.8 Negative Component Values                    | 506 |

| 15.9 Power Switching Circuits                     | 507 |

| 15.9.1 Model Parameters of Diodes and Transistors | 507 |

| 15.9.2 Error Tolerances                           | 508 |

| 15.9.3 Snubbing Resistor                          | 508 |

| 15.9.4 Quasi-Steady-State Condition               | 508 |

| 15.10 Floating Nodes                              | 512 |

| 15.11 Nodes with Fewer than Two Connections       | 516 |

| 15.12 Voltage Source and Inductor Loops           | 517 |

| 15.13 Running PSpice Files on Spice               | 518 |

| 15.14 Running Spice Files on PSpice               | 518 |

| 15.15 Using Earlier Version of Schematics         | 519 |

| Suggested Reading                                 |     |

| Problems                                          |     |

| App | endix A Running PSpice on PCs     |  |

|-----|-----------------------------------|--|

| A.1 | Installing PSpice Software in PCs |  |

|     | Creating Input Circuit Files      |  |

|     | Running DOS Commands              |  |

| A.4 | PSpice Default Symbol Libraries   |  |

|     |                                   |  |

| bliography531 |

|---------------|

|---------------|

# 1 Introduction

The learning objectives of this chapter are to develop an understanding of the following:

- · General description and the types of SPICE software

- Types of analysis that can be performed on electronic and electrical circuits

- Limitations of PSpice software

- Online resources on SPICE

#### 1.1 INTRODUCTION

Electronic circuit design requires accurate methods of evaluating circuit performance. Because of the enormous complexity of modern integrated circuits, computer-aided circuit analysis is essential and can provide information about circuit performance that is almost impossible to obtain with laboratory prototype measurements. Computer-aided analysis makes possible the following procedures:

- 1. Evaluation of the effects of variations in such elements as resistors, transistors, and transformers

- 2. Assessment of performance improvements or degradations

- 3. Evaluation of the effects of noise and signal distortion without the need for expensive measuring instruments

- 4. Sensitivity analysis to determine the permissible bounds determined by the tolerances of all element values or parameters of active elements

- 5. Fourier analysis without expensive wave analyzers

- 6. Evaluation of the effects of nonlinear elements on circuit performance

- 7. Optimization of the design of electronic circuits in terms of circuit parameters

SPICE (simulation program with integrated circuit emphasis) is a general-purpose circuit program that simulates electronic circuits. It can perform analyses on various aspects of electronic circuits, such as the operating (or quiescent) points of transistors, time-domain response, small-signal frequency response, and so on. SPICE contains models for common circuit elements, active as well as passive, and it is capable of simulating most electronic circuits. It is a versatile program and is widely used in both industry and academic institutions.

Until recently, SPICE was available only on mainframe computers. In addition to the cost of the computer system, such a machine can be inconvenient for classroom use. In 1984, MicroSim introduced the PSpice simulator, which is similar to the Berkeley version of SPICE and runs on an IBM-PC or compatible, and is available free of cost to students for classroom use. PSpice<sup>®</sup> thus widens the scope for the integration of computer-aided circuit analysis into electronic circuits courses at the undergraduate level. Other versions of PSpice, which will run on the Macintosh II, 486-based processor, VAX, SUN, NEC, and other computers, are also available.

#### **1.2 DESCRIPTIONS OF SPICE**

PSpice is a member of the SPICE family of circuit simulators, all of which originate from the SPICE2 circuit simulator, whose development spans a period of about 30 yr. During the mid-1960s, the program ECAP was developed at IBM [1]. In the late 1960s, ECAP served as the starting point for the development of the program CANCER at the University of California (UC) at Berkeley. Using CANCER as the basis, SPICE was developed at Berkeley in the early 1970s. During the mid-1970s, SPICE2, which is an improved version of SPICE, was developed at UC–Berkeley. The algorithms of SPICE2 are robust, powerful, and general in nature, and SPICE2 has become an industry-standard tool for circuit simulation. SPICE3, a variation of SPICE2, is designed especially to support computer-aided design (CAD) research programs at UC–Berkeley. As the development of SPICE2 was supported using public funds, this software is in the public domain, which means that it may be used freely by all U.S. citizens.

SPICE2, referred to simply as SPICE, has become an industry standard. The input syntax for SPICE is a free-format style that does not require data to be entered in fixed column locations. SPICE assumes reasonable default values for unspecified circuit parameters. In addition, it performs a considerable amount of error checking to ensure that a circuit has been entered correctly.

PSpice, which uses the same algorithms as SPICE2, is equally useful for simulating all types of circuits in a wide range of applications. A circuit is described by statements stored in a file called the *circuit file*. The circuit file is read by the SPICE simulator. Each statement is self-contained and independent of every other statement, and does not interact with other statements. SPICE (or PSpice) statements are easy to learn and use.

A schematic editor can be used to draw the circuit and create a Schematics file, which can then be read by PSpice for running the simulation.

#### 1.3 TYPES OF SPICE

The commercially supported versions of SPICE2 can be classified into two types: mainframe versions and PC-based versions. Their methods of computation may differ, but their features are almost identical. However, some may include such additions as a preprocessor or shell program to manage input and provide interactive control, as well as a postprocessor to refine the normal SPICE output. A person used to one SPICE version (e.g., PSpice) should be able to work with other versions. Mainframe versions are:

| HSPICE (from Meta-Software), which is for integrated-circuit design with |

|--------------------------------------------------------------------------|

| special device models                                                    |

| RAD-SPICE (from Meta-Software), which simulates circuits subjected to    |

| ionizing radiation                                                       |

| IG-SPICE (from A.B. Associates), which is designed for "interactive"     |

| circuit simulation with graphics output                                  |

| I-SPICE (from NCSS Time Sharing), which is designed for "interactive"    |

| circuit simulation with graphics output                                  |

| Precise (from Electronic Engineering Software)                           |

| PSpice (from MicroSim)                                                   |

| AccuSim (from Mentor Graphics)                                           |

| Spectre (from Cadence Design)                                            |

| SPICE-Plus (from Valid Logic)                                            |

|                                                                          |

The PC versions include the following:

AllSpice (from Acotech) Is-Spice (from Intusoft) Z-SPICE (from Z-Tech) SPICE-Plus (from Analog Design Tools) DSPICE (from Daisy Systems) PSpice (from MicroSim) OrCAD (from Cadence) Spice (from KEMET) B2 Spice A/D (from Beige Bag Software) AIM-Spice (from AIM-Software) VisualSpice (from AIM-Software) VisualSpice (from Island Logix) Spice3f4 (from Kiva Design) OrCAD SPICE (from OrCAD) MDSPICE (from Zeland Software, Inc.) Ivex Spice (from Ivex Design)

#### 1.4 TYPES OF ANALYSIS

PSpice allows various types of analysis. Each analysis is invoked by including its command statement. For example, a statement beginning with the .DC command invokes the DC sweep. The types of analysis and their corresponding . dot commands are described in the following text.

DC analysis is used for circuits with time-invariant sources (e.g., steady-state DC sources). It calculates all node voltages and branch currents for a range of values, and their quiescent (DC) values are the outputs. The dot commands and their functions are:

- DC sweep of an input voltage or current source, a model parameter, or temperature over a range of values (.DC)

- Determination of the linearized model parameters of nonlinear devices (.OP)

- DC operating point to obtain all node voltages

- Small-signal transfer function with small-signal gain, input resistance, and output resistance (Thevenin's equivalent; .TF)

- DC small-signal sensitivities (.SENS)

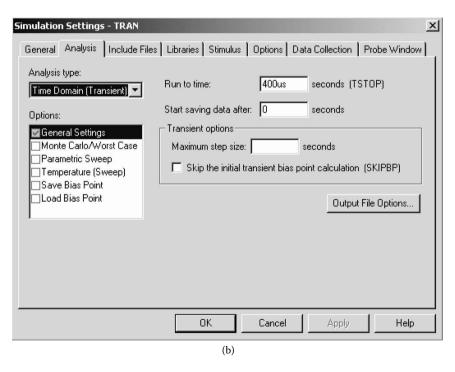

Transient analysis is used for circuits with time-variant sources (e.g., AC sources and switched DC sources). It calculates all node voltages and branch currents over a time interval, and their instantaneous values are the outputs. The dot commands and their functions are:

- Circuit behavior in response to time-varying sources (.TRAN)

- DC and Fourier components of the transient analysis results (.FOUR)

AC analysis is used for small-signal analysis of circuits with sources of variable frequencies. It calculates all node voltages and branch currents over a range of frequencies, and their magnitudes and phase angles are the outputs. The dot commands and their functions are:

- Circuit response over a range of source frequencies (.AC)

- Noise generation at an output node for every frequency (.NOISE)

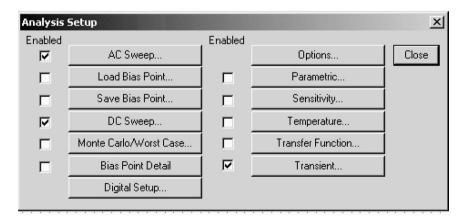

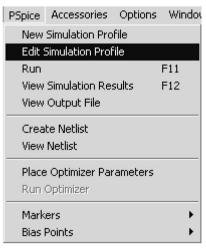

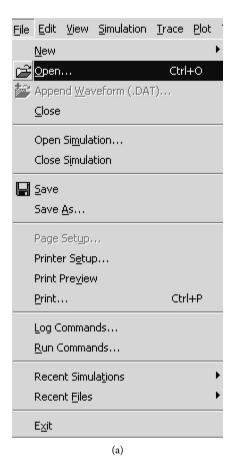

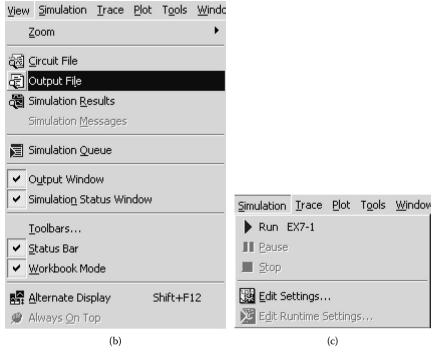

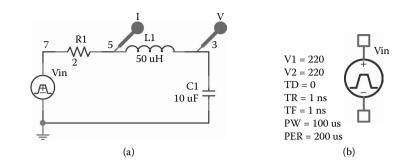

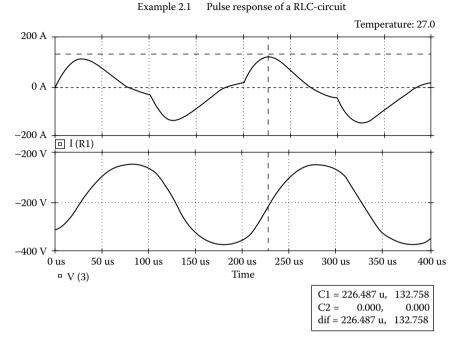

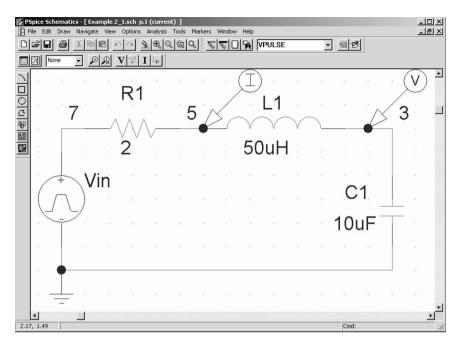

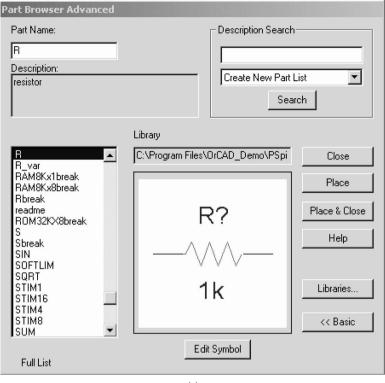

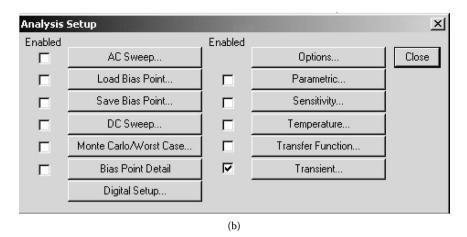

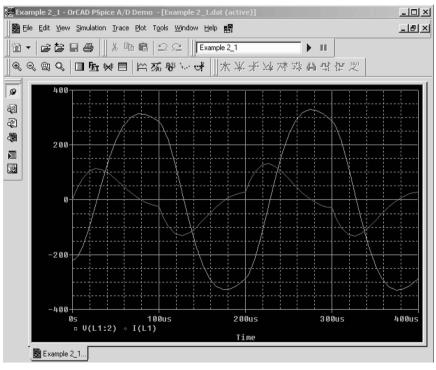

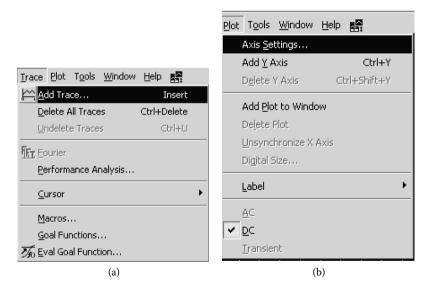

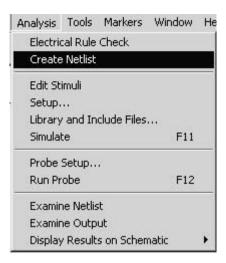

In Schematics versions, the commands are invoked from the setup menu, as shown in Figure 1.1.

FIGURE 1.1 Analysis setup in PSpice Schematics versions.

#### **1.5 LIMITATIONS OF PSPICE**

As a circuit simulator, PSpice has the following limitations:

- 1. The PC-based student version of PSpice is restricted to circuits with 10 transistors only. However, the professional (or production) version can simulate a circuit with up to 200 bipolar transistors (or 150 MOSFETs).

- 2. The program is not interactive; that is, the circuit cannot be analyzed for various component values without editing the program statements.

- 3. PSpice does not support an iterative method of solution. If the elements of a circuit are specified, the output can be predicted. On the other hand, if the output is specified, PSpice cannot be used to synthesize the circuit elements.

- 4. The input impedance cannot be determined directly without running the graphic postprocessor, Probe. Although the student version does not require a floating-point coprocessor for running Probe, the professional version does.

- 5. To run the PC version requires 512 kilobytes of memory (RAM).

- 6. Distortion analysis is not available.

- 7. The output impedance of a circuit cannot be printed or plotted directly.

- 8. The student version can run with or without a floating-point coprocessor. If a coprocessor is present, the program will run at full speed. Otherwise, it will run 5 to 15 times slower. The professional version requires a coprocessor.

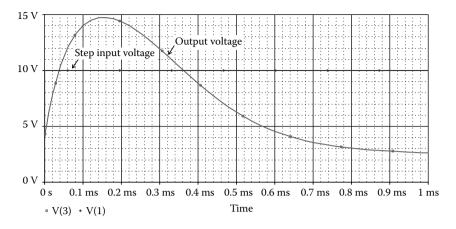

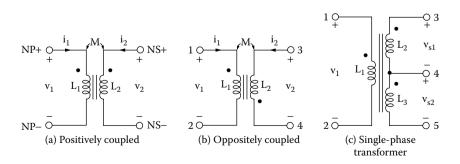

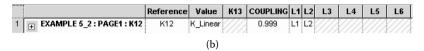

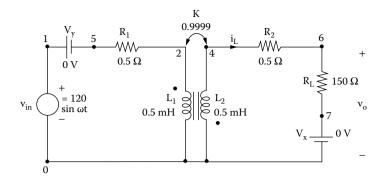

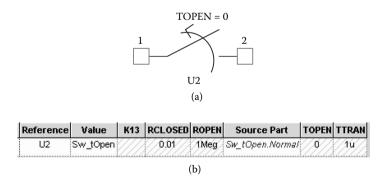

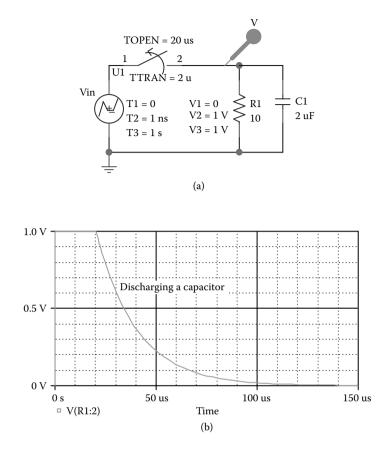

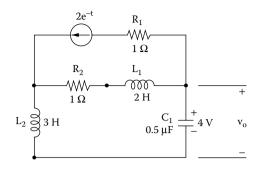

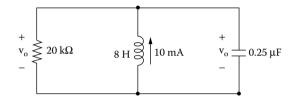

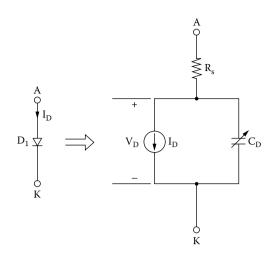

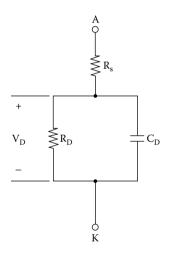

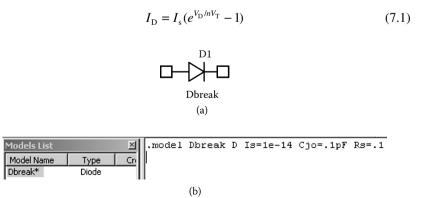

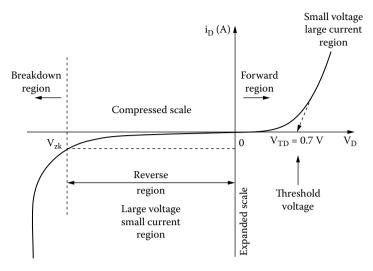

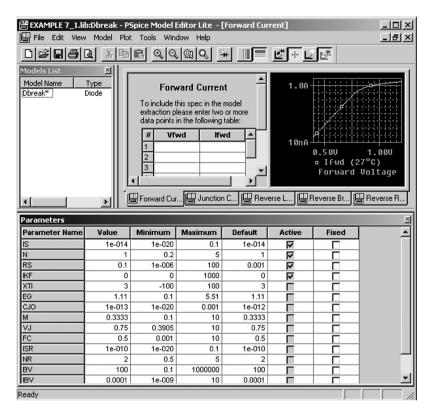

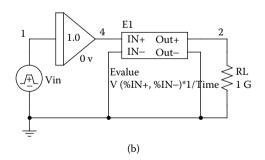

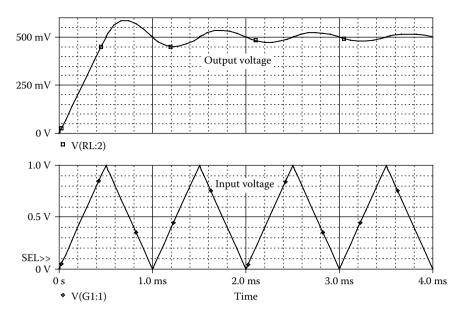

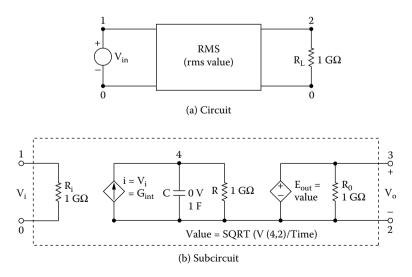

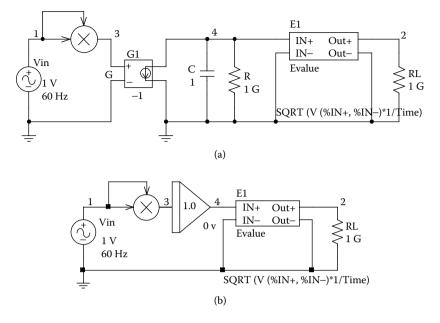

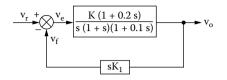

#### 1.6 DESCRIPTIONS OF SIMULATION SOFTWARE TOOLS