# PRACTICAL RELIABILITY of Electronic Equipment and Products

EUGENE R. HNATEK

Qualcomm Incorporated San Diego, California

New York • Basel

Copyright 2003 by Marcel Dekker, Inc. All Rights Reserved.

#### ISBN: 0-8247-0832-6

This book is printed on acid-free paper.

#### Headquarters

Marcel Dekker, Inc. 270 Madison Avenue, New York, NY 10016 tel: 212-696-9000; fax: 212-685-4540

#### **Eastern Hemisphere Distribution**

Marcel Dekker AG Hutgasse 4, Postfach 812, CH-4001 Basel, Switzerland tel: 41-61-260-6300; fax: 41-61-260-6333

#### World Wide Web

http://www.dekker.com

The publisher offers discounts on this book when ordered in bulk quantities. For more information, write to Special Sales/Professional Marketing at the headquarters address above.

#### Copyright © 2003 by Marcel Dekker, Inc. All Rights Reserved.

Neither this book nor any part may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying, microfilming, and recording, or by any information storage and retrieval system, without permission in writing from the publisher.

Current printing (last digit): 10 9 8 7 6 5 4 3 2 1

#### PRINTED IN THE UNITED STATES OF AMERICA

Copyright 2003 by Marcel Dekker, Inc. All Rights Reserved.

#### ELECTRICAL AND COMPUTER ENGINEERING

A Series of Reference Books and Textbooks

#### FOUNDING EDITOR

Marlin O. Thurston Department of Electrical Engineering The Ohio State University Columbus, Ohio

- 1. Rational Fault Analysis, edited by Richard Saeks and S. R. Liberty

- 2. Nonparametric Methods in Communications, *edited by P. Papantoni-Kazakos and Dimitri Kazakos*

- 3. Interactive Pattern Recognition, Yi-tzuu Chien

- 4. Solid-State Electronics, Lawrence E. Murr

- 5. Electronic, Magnetic, and Thermal Properties of Solid Materials, Klaus Schröder

- 6. Magnetic-Bubble Memory Technology, Hsu Chang

- 7. Transformer and Inductor Design Handbook, Colonel Wm. T. McLyman

- 8. Electromagnetics: Classical and Modern Theory and Applications, Samuel Seely and Alexander D. Poularikas

- 9. One-Dimensional Digital Signal Processing, Chi-Tsong Chen

- 10. Interconnected Dynamical Systems, Raymond A. DeCarlo and Richard Saeks

- 11. Modern Digital Control Systems, Raymond G. Jacquot

- 12. Hybrid Circuit Design and Manufacture, Roydn D. Jones

- 13. Magnetic Core Selection for Transformers and Inductors: A User's Guide to Practice and Specification, *Colonel Wm. T. McLyman*

- 14. Static and Rotating Electromagnetic Devices, Richard H. Engelmann

- 15. Energy-Efficient Electric Motors: Selection and Application, John C. Andreas

- 16. Electromagnetic Compossibility, Heinz M. Schlicke

- 17. Electronics: Models, Analysis, and Systems, James G. Gottling

- 18. Digital Filter Design Handbook, Fred J. Taylor

- 19. Multivariable Control: An Introduction, P. K. Sinha

- 20. Flexible Circuits: Design and Applications, Steve Gurley, with contributions by Carl A. Edstrom, Jr., Ray D. Greenway, and William P. Kelly

- 21. Circuit Interruption: Theory and Techniques, Thomas E. Browne, Jr.

- 22. Switch Mode Power Conversion: Basic Theory and Design, K. Kit Sum

- 23. Pattern Recognition: Applications to Large Data-Set Problems, Sing-Tze Bow

- 24. Custom-Specific Integrated Circuits: Design and Fabrication, Stanley L. Hurst

- 25. Digital Circuits: Logic and Design, Ronald C. Emery

- 26. Large-Scale Control Systems: Theories and Techniques, Magdi S. Mahmoud, Mohamed F. Hassan, and Mohamed G. Darwish

- 27. Microprocessor Software Project Management, Eli T. Fathi and Cedric V. W. Armstrong (Sponsored by Ontario Centre for Microelectronics)

- 28. Low Frequency Electromagnetic Design, Michael P. Perry

- 29. Multidimensional Systems: Techniques and Applications, *edited by Spyros G. Tzafestas*

- 30. AC Motors for High-Performance Applications: Analysis and Control, Sakae Yamamura

- 31. Ceramic Motors for Electronics: Processing, Properties, and Applications, *edited by Relva C. Buchanan*

- 32. Microcomputer Bus Structures and Bus Interface Design, Arthur L. Dexter

- 33. End User's Guide to Innovative Flexible Circuit Packaging, Jay J. Miniet

- 34. Reliability Engineering for Electronic Design, Norman B. Fuqua

- 35. Design Fundamentals for Low-Voltage Distribution and Control, Frank W. Kussy and Jack L. Warren

- 36. Encapsulation of Electronic Devices and Components, Edward R. Salmon

- 37. Protective Relaying: Principles and Applications, J. Lewis Blackburn

- 38. Testing Active and Passive Electronic Components, Richard F. Powell

- 39. Adaptive Control Systems: Techniques and Applications, V. V. Chalam

- 40. Computer-Aided Analysis of Power Electronic Systems, Venkatachari Rajagopalan

- 41. Integrated Circuit Quality and Reliability, Eugene R. Hnatek

- 42. Systolic Signal Processing Systems, edited by Earl E. Swartzlander, Jr.

- 43. Adaptive Digital Filters and Signal Analysis, Maurice G. Bellanger

- 44. Electronic Ceramics: Properties, Configuration, and Applications, *edited by Lionel M. Levinson*

- 45. Computer Systems Engineering Management, Robert S. Alford

- 46. Systems Modeling and Computer Simulation, edited by Naim A. Kheir

- 47. Rigid-Flex Printed Wiring Design for Production Readiness, Walter S. Rigling

- 48. Analog Methods for Computer-Aided Circuit Analysis and Diagnosis, *edited by Takao Ozawa*

- 49. Transformer and Inductor Design Handbook: Second Edition, Revised and Expanded, *Colonel Wm. T. McLyman*

- 50. Power System Grounding and Transients: An Introduction, A. P. Sakis Meliopoulos

- 51. Signal Processing Handbook, edited by C. H. Chen

- 52. Electronic Product Design for Automated Manufacturing, H. Richard Stillwell

- 53. Dynamic Models and Discrete Event Simulation, William Delaney and Erminia Vaccari

- 54. FET Technology and Application: An Introduction, Edwin S. Oxner

- 55. Digital Speech Processing, Synthesis, and Recognition, Sadaoki Furui

- 56. VLSI RISC Architecture and Organization, Stephen B. Furber

- 57. Surface Mount and Related Technologies, Gerald Ginsberg

- 58. Uninterruptible Power Supplies: Power Conditioners for Critical Equipment, David C. Griffith

- 59. Polyphase Induction Motors: Analysis, Design, and Application, Paul L. Cochran

- 60. Battery Technology Handbook, edited by H. A. Kiehne

- 61. Network Modeling, Simulation, and Analysis, *edited by Ricardo F. Garzia and Mario R. Garzia*

- 62. Linear Circuits, Systems, and Signal Processing: Advanced Theory and Applications, *edited by Nobuo Nagai*

- 63. High-Voltage Engineering: Theory and Practice, edited by M. Khalifa

- 64. Large-Scale Systems Control and Decision Making, edited by Hiroyuki Tamura and Tsuneo Yoshikawa

- 65. Industrial Power Distribution and Illuminating Systems, Kao Chen

- 66. Distributed Computer Control for Industrial Automation, *Dobrivoje Popovic and Vijay P. Bhatkar*

- 67. Computer-Aided Analysis of Active Circuits, Adrian Ioinovici

- 68. Designing with Analog Switches, Steve Moore

- 69. Contamination Effects on Electronic Products, Carl J. Tautscher

- 70. Computer-Operated Systems Control, Magdi S. Mahmoud

- 71. Integrated Microwave Circuits, edited by Yoshihiro Konishi

- 72. Ceramic Materials for Electronics: Processing, Properties, and Applications, Second Edition, Revised and Expanded, *edited by Relva C. Buchanan*

- 73. Electromagnetic Compatibility: Principles and Applications, David A. Weston

- 74. Intelligent Robotic Systems, edited by Spyros G. Tzafestas

- 75. Switching Phenomena in High-Voltage Circuit Breakers, edited by Kunio Nakanishi

- 76. Advances in Speech Signal Processing, edited by Sadaoki Furui and M. Mohan Sondhi

- 77. Pattern Recognition and Image Preprocessing, Sing-Tze Bow

- 78. Energy-Efficient Electric Motors: Selection and Application, Second Edition, *John C. Andreas*

- 79. Stochastic Large-Scale Engineering Systems, *edited by Spyros G. Tzafestas and Keigo Watanabe*

- 80. Two-Dimensional Digital Filters, Wu-Sheng Lu and Andreas Antoniou

- 81. Computer-Aided Analysis and Design of Switch-Mode Power Supplies, Yim-Shu Lee

- 82. Placement and Routing of Electronic Modules, edited by Michael Pecht

- 83. Applied Control: Current Trends and Modern Methodologies, *edited by Spyros G. Tzafestas*

- 84. Algorithms for Computer-Aided Design of Multivariable Control Systems, *Stanoje Bingulac and Hugh F. VanLandingham*

- 85. Symmetrical Components for Power Systems Engineering, J. Lewis Blackburn

- 86. Advanced Digital Signal Processing: Theory and Applications, *Glenn Zelniker* and Fred J. Taylor

- 87. Neural Networks and Simulation Methods, Jian-Kang Wu

- 88. Power Distribution Engineering: Fundamentals and Applications, James J. Burke

- 89. Modern Digital Control Systems: Second Edition, Raymond G. Jacquot

- 90. Adaptive IIR Filtering in Signal Processing and Control, Phillip A. Regalia

- 91. Integrated Circuit Quality and Reliability: Second Edition, Revised and Expanded, Eugene R. Hnatek

- 92. Handbook of Electric Motors, edited by Richard H. Engelmann and William H. Middendorf

- 93. Power-Switching Converters, Simon S. Ang

- 94. Systems Modeling and Computer Simulation: Second Edition, Naim A. Kheir

- 95. EMI Filter Design, Richard Lee Ozenbaugh

- 96. Power Hybrid Circuit Design and Manufacture, Haim Taraseiskey

- 97. Robust Control System Design: Advanced State Space Techniques, Chia-Chi Tsui

- 98. Spatial Electric Load Forecasting, H. Lee Willis

- 99. Permanent Magnet Motor Technology: Design and Applications, Jacek F. Gieras and Mitchell Wing

- 100. High Voltage Circuit Breakers: Design and Applications, Ruben D. Garzon

- 101. Integrating Electrical Heating Elements in Appliance Design, Thor Hegbom

- 102. Magnetic Core Selection for Transformers and Inductors: A User's Guide to Practice and Specification, Second Edition, *Colonel Wm. T. McLyman*

- 103. Statistical Methods in Control and Signal Processing, edited by Tohru Katayama and Sueo Sugimoto

- 104. Radio Receiver Design, Robert C. Dixon

- 105. Electrical Contacts: Principles and Applications, edited by Paul G. Slade

- 106. Handbook of Electrical Engineering Calculations, edited by Arun G. Phadke

- 107. Reliability Control for Electronic Systems, Donald J. LaCombe

- 108. Embedded Systems Design with 8051 Microcontrollers: Hardware and Software, Zdravko Karakehayov, Knud Smed Christensen, and Ole Winther

- 109. Pilot Protective Relaying, edited by Walter A. Elmore

- 110. High-Voltage Engineering: Theory and Practice, Second Edition, Revised and Expanded, *Mazen Abdel-Salam, Hussein Anis, Ahdab El-Morshedy, and Roshdy Radwan*

- 111. EMI Filter Design: Second Edition, Revised and Expanded, Richard Lee Ozenbaugh

- 112. Electromagnetic Compatibility: Principles and Applications, Second Edition, Revised and Expanded, *David Weston*

- 113. Permanent Magnet Motor Technology: Design and Applications, Second Edition, Revised and Expanded, *Jacek F. Gieras and Mitchell Wing*

- 114. High Voltage Circuit Breakers: Design and Applications, Second Edition, Revised and Expanded, Ruben D. Garzon

- 115. High Reliability Magnetic Devices: Design and Fabrication, Colonel Wm. T. McLyman

#### Additional Volumes in Preparation

Practical Reliability of Electronic Equipment and Products, Eugene R. Hnatek

To my mother Val, my wife Susan, and my Lord and Savior Jesus Christ for their caring ways, encouragement, and unconditional love. Words cannot adequately express my gratitude and feelings for them. To my brother Richard for his loving care of our mother.

### Preface

Reliability is important. Most organizations are concerned with fast time to market, competitive advantage, and improving costs. Customers want to be sure that the products and equipment they buy work as intended for the time specified. That's what reliability is: performance against requirements over time.

A number of excellent books have been written dealing with the topic of reliability—most from a theoretical and what I call a "rel math" perspective. This book is about electronic product and equipment reliability. It presents a practical "hands-on perspective" based on my personal experience in fielding a myriad of different systems, including military/aerospace systems, semiconductor devices (integrated circuits), measuring instruments, and computers.

The book is organized according to end-to-end reliability: from the customer to the customer. At the beginning customers set the overall product parameters and needs and in the end they determine whether the resultant product meets those needs. They basically do this with their wallets. Thus, it is imperative that manufacturers truly listen to what the customer is saying. In between these two bounds the hard work of reliability takes place: design practices and testing; selection and qualification of components, technology and suppliers; printed wiring assembly and systems manufacturing; and testing practices, including regulatory testing and failure analysis.

To meet any reliability objective requires a comprehensive knowledge of the interactions of the design, the components used, the manufacturing techniques employed, and the environmental stresses under which the product will operate. A reliable product is one that balances design-it-right and manufacture-it-correctly techniques with just the right amount of testing. For example, design verification testing is best accomplished using a logical method such as a Shewhart or Deming cycle (plan-do-check-act-repeat) in conjunction with accelerated stress and failure analysis. Only when used in this closed-feedback loop manner will testing help make a product more robust. Testing by itself adds nothing to the reliability of a product.

The purpose of this book is to give electronic circuit design engineers, system design engineers, product engineers, reliability engineers, and their managers this end-to-end view of reliability by sharing what is currently being done in each of the areas presented as well as what the future holds based on lessons-learned. It is important that lessons and methods learned be shared. This is the major goal of this book. If we are ignorant of the lessons of the past, we usually end up making the same mistakes as those before us did. The key is to never stop learning. The topics contained in this book are meant to foster and stimulate thinking and help readers extrapolate the methods and techniques to specific work situations.

The material is presented from a large-company, large-system/product perspective (in this text the words *product, equipment*, and *system* are interchangeable). My systems work experiences have been with large companies with the infrastructure and capital equipment resources to produce high-end products that demand the highest levels of reliability: satellites, measuring instruments (automatic test equipment for semiconductors), and high-end computers/servers for financial transaction processing. This book provides food for thought in that the methods and techniques used to produce highly reliable and robust products for these very complex electronic systems can be "cherry-picked" for use by smaller, resource-limited companies. The methods and techniques given can be tailored to a company's specific needs and corporate boundary conditions for an appropriate reliability plan.

My hope is that within this book readers will find some methods or ideas that they can take away and use to make their products more reliable. The methods and techniques are not applicable in total for everyone. Yet there are some ingredients for success provided here that can be applied regardless of the product being designed and manufactured. I have tried to provide some things to think about. There is no single step-by-step process that will ensure the production of a high-reliability product. Rather, there are a number of sound principles that have been found to work. What the reader ultimately decides to do depends on the product(s) being produced, the markets served, and the fundamental precepts under which the company is run. I hope that the material presented is of value.

#### ACKNOWLEDGMENTS

I want to acknowledge the professional contributions of my peers in their areas of expertise and technical disciplines to the electronics industry and to this book. This book would not have been possible without the technical contributions to the state of the art by the people listed below. I thank them for allowing me to use their material. I consider it an honor to have both known and worked with all of them. I deeply respect them personally and their abilities.

David Christiansen, Compaq Computer Corporation, Tandem Division

Noel Donlin, U.S. Army, retired

Jon Elerath, Compaq Computer Corporation, Tandem Division; now with Network Appliance Inc.

Charles Hawkins, University of New Mexico

Michael Hursthopf, Compaq Computer Corporation, Tandem Division

Andrew Kostic, IBM

Edmond Kyser, Compaq Computer Corporation, Tandem Division; now with Cisco Systems

Ken Long, Celestica

Chan Moore, Compaq Computer Corporation, Tandem Division

Joel Russeau, Compaq Computer Corporation, Tandem Division

Richard Sevcik, Xilinx Inc.

Ken Stork, Ken Stork and Associates

Alan Wood, Compaq Computer Corporation, Tandem Division

David Christiansen, Michael Hursthopf, Chan Moore, Joel Russeau, and Alan Wood are now with Hewlett Packard Company. Thanks to Rich Sevcik for reviewing Chapter 8. His expert comments and suggestions were most helpful. Thanks to Joel Russeau and Ed Kyser for coauthoring many articles with me. Their contributions to these works were significant in the value that was provided to the readers. To my dear friend G. Laross Coggan, thanks for your untiring assistance in getting the artwork together; I couldn't have put this all together without you. To my production editor, Moraima Suarez, thanks for your editorial contribution. I appreciate your diligence in doing a professional job of editing the manuscript and your patience in dealing with the issues that came up during the production process.

Eugene R. Hnatek

## Contents

#### Preface

#### 1. Introduction to Reliability

- 1.1 What Is Reliability?

- 1.2 Discipline and Tasks Involved with Product Reliability

- 1.3 The Bathtub Failure Rate Curve

- 1.4 Reliability Goals and Metrics

- 1.5 Reliability Prediction

- 1.6 Reliability Risk

- 1.7 Reliability Growth

- 1.8 Reliability Degradation

- 1.9 Reliability Challenges

- 1.10 Reliability Trends References

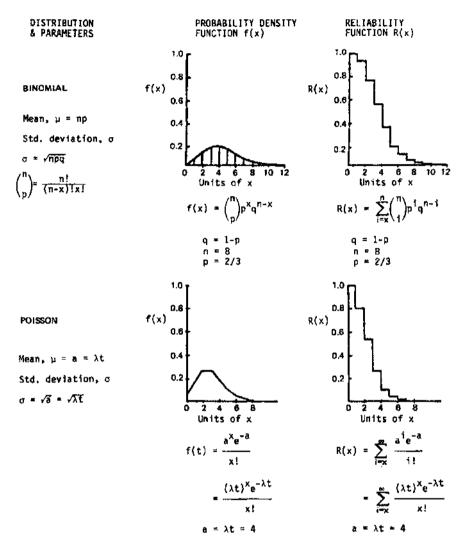

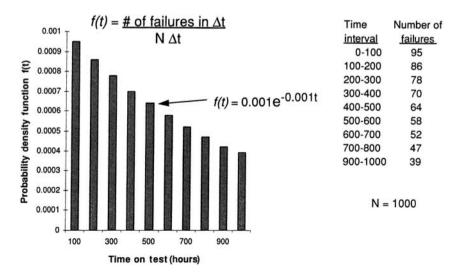

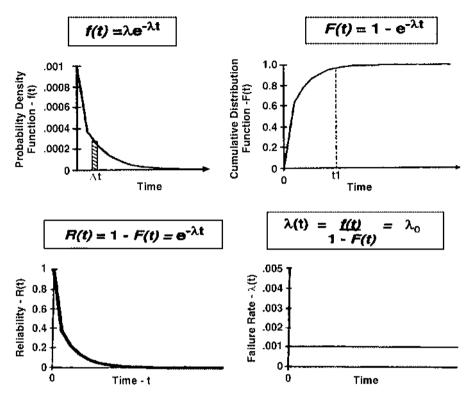

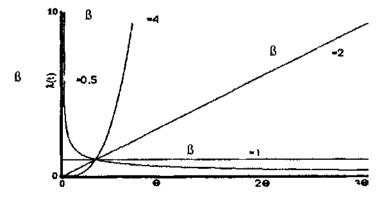

#### 2. Basic Reliability Mathematics

- 2.1 Statistical Terms

- 2.2 Statistical Distributions

- 2.3 Plotting and Linearization of Data

- 2.4 Confidence Limit and Intervals

- 2.5 Failure Free Operation

- 2.6 Reliability Modeling

Copyright 2003 by Marcel Dekker, Inc. All Rights Reserved.

2.7 Practical MTBF and Warranty Cost Calculations Reference Appendix A

#### 3. Robust Design Practices

- 3.1 Introduction

- 3.2 Concurrent Engineering/Design Teams

- 3.3 Product Design Process

- 3.4 Translate Customer Requirements to Design Requirements

- 3.5 Technology Assessment

- 3.6 Circuit Design

- 3.7 Power Supply Considerations

- 3.8 Redundancy

- 3.9 Component/Supplier Selection and Management

- 3.10 Reliability Prediction

- 3.11 Support Cost and Reliability Tradeoff Model

- 3.12 Stress Analysis and Part Derating

- 3.13 PCB Design, PWA Layout, and Design for Manufacture

- 3.14 Thermal Management

- 3.15 Signal Integrity and Design for Electromagnetic Compatibility

- 3.16 Design for Test

- 3.17 Sneak Circuit Analysis

- 3.18 Bill of Material Reviews

- 3.19 Design Reviews

- 3.20 The Supply Chain and the Design Engineer

- 3.21 Failure Modes and Effects Analysis

- 3.22 Design for Environment

- 3.23 Environmental Analysis

- 3.24 Development and Design Testing

- 3.25 Transportation and Shipping Testing

- 3.26 Regulatory Testing

- 3.27 Design Errors References Further Reading

- 4. Component and Supplier Selection, Qualification, Testing, and Management

- 4.1 Introduction

- 4.2 The Physical Supply Chain

- 4.3 Supplier Management in the Electronics Industry

- 4.4 The Role of the Component Engineer

- 4.5 Component Selection

- 4.6 Integrated Circuit Reliability

- 4.7 Component Qualification References Further Reading Appendix A: Supplier Scorecard Process Overview Appendix B: Self-Qualification Form for Programmable Logic ICs

#### 5. Thermal Management

- 5.1 Introduction

- 5.2 Thermal Analysis Models and Tools

- 5.3 Impact of High-Performance Integrated Circuits

- 5.4 Material Considerations

- 5.5 Effect of Heat on Components, Printed Circuit Boards, and Solder

- 5.6 Cooling Solutions

- 5.7 Other Considerations References Further Reading

#### 6. Electrostatic Discharge and Electromagnetic Compatibility

- 6.1 Electrostatic Discharge

- 6.2 Electromagnetic Compatibility Further Reading

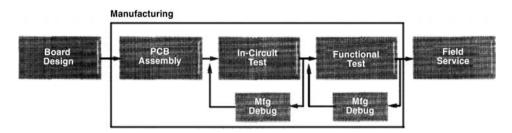

#### 7. Manufacturing/Production Practices

- 7.1 Printed Wiring Assembly Manufacturing

- 7.2 Printed Wiring Assembly Testing

- 7.3 Environmental Stress Testing

- 7.4 System Testing

- 7.5 Field Data Collection and Analysis

- 7.6 Failure Analysis References Further Reading

#### 8. Software

- 8.1 Introduction

- 8.2 Hardware/Software Development Comparison

- 8.3 Software Availability

8.4 Software Quality Reference

Appendix A: An Example of Part Derating Guidelines Appendix B: FMEA Example for a Memory Module Epilogue

# Introduction to Reliability

#### 1.1 WHAT IS RELIABILITY?

To set the stage, this book deals with the topic of electronic product hardware reliability. Electronic products consist of individual components (such as integrated circuits, resistors, capacitors, transistors, diodes, crystals, and connectors) assembled on a printed circuit board; third party–provided hardware such as disk drives, power supplies, and various printed circuit card assemblies; and various mechanical fixtures, robotics, shielding, cables, etc., all integrated into an enclosure or case of some sort.

The term *reliability* is at the same time ambiguous in the general sense but very exacting in the practical and application sense when consideration is given to the techniques and methods used to ensure the production of reliable products. Reliability differs/varies based on the intended application, the product category, the product price, customer expectations, and the level of discomfort or repercussion caused by product malfunction. For example, products destined for consumer use have different reliability requirements and associated risk levels than do products destined for use in industrial, automotive, telecommunication, medical, military, or space applications.

Customer expectations and threshold of pain are important as well. What do I mean by this? Customers have an expectation and threshold of pain for the product they purchase based on the price paid and type of product. The designedin reliability level should be just sufficient enough to meet that expectation and threshold of pain. Thus, reliability and customer expectations are closely tied to price. For example if a four- to five-function electronic calculator fails, the customer's level of irritation and dissatisfaction is low. This is so because both the purchase price and the original customer expectation for purchase are both low. The customer merely disposes of it and gets another one. However, if your Lexus engine ceases to function while you are driving on a busy freeway, your level of anxiety, irritation, frustration, and dissatisfaction are extremely high. This is because both the customer expectation upon purchase and the purchase price are high. A Lexus is not a disposable item.

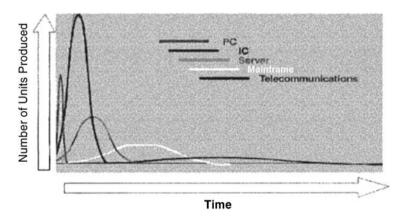

Also, for a given product, reliability is a moving target. It varies with the maturity of the technology and from one product generation to the next. For example, when the electronic calculator and digital watch first appeared in the marketplace, they were state-of-the-art products and were extremely costly as well. The people who bought these products were early adopters of the technology and expected them to work. Each product cost in the neighborhood of several hundred dollars (on the order of \$800-\$900 for the first electronic calculator and \$200-\$400 for the first digital watches). As the technology was perfected (going from LED to LCD displays and lower-power CMOS integrated circuits) and matured and competition entered the marketplace, the price fell over the years to such a level that these products have both become disposable commodity items (except for high-end products). When these products were new, unique, and high priced, the customer's reliability expectations were high as well. As the products became mass-produced disposable commodity items, the reliability expectations became less and less important; so that today reliability is almost a "don't care" situation for these two products. The designed-in reliability has likewise decreased in response to market conditions.

Thus companies design in just enough reliability to meet the customer's expectations, i.e., consumer acceptance of the product price and level of discomfort that a malfunction would bring about. You don't want to design in more reliability than the application warrants or that the customer is willing to pay for. Table 1 lists the variables of price, customer discomfort, designed-in reliability, and customer expectations relative to product/application environment, from the simple to the complex.

Then, too, a particular product category may have a variety of reliability requirements. Take computers as an example. Personal computers for consumer and general business office use have one set of reliability requirements; computers destined for use in high-end server applications (CAD tool sets and the like) have another set of requirements. Computers serving the telecommunication industry must operate for 20-plus years; applications that require nonstop availability and 100% data integrity (for stock markets and other financial transaction applications, for example) have an even higher set of requirements. Each of these

|                                                   | Calculators | Personal computers | Pacemaker | Computers<br>for banking<br>applications | Auto | Airline           | Satellite      |

|---------------------------------------------------|-------------|--------------------|-----------|------------------------------------------|------|-------------------|----------------|

| Price                                             | Low         |                    |           |                                          |      | >                 | Extremely high |

| Discomfort and repercussion caused by malfunction | Low         |                    |           |                                          |      | >                 | Extremely high |

| Designed-in reliability                           | Low         |                    |           |                                          |      | $\longrightarrow$ | Extremely high |

| Customer expectations                             | Low         |                    |           |                                          |      | $\longrightarrow$ | Extremely high |

TABLE 1

Key Customer Variables Versus Product Categories/Applications Environment

markets has different reliability requirements that must be addressed individually during the product concept and design phase and during the manufacturing and production phase.

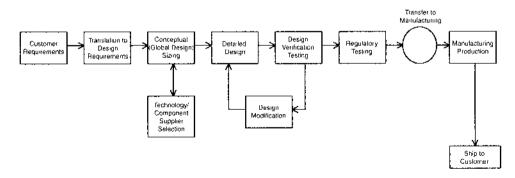

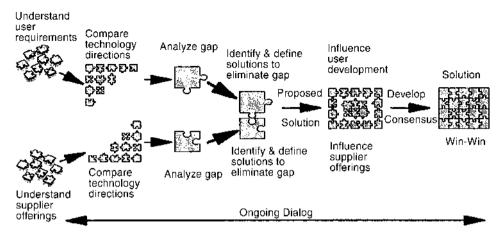

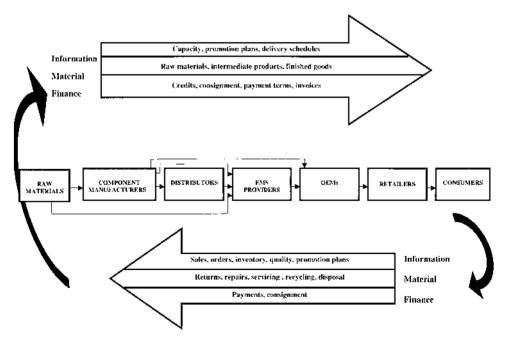

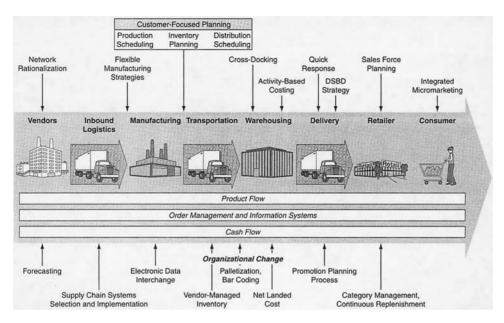

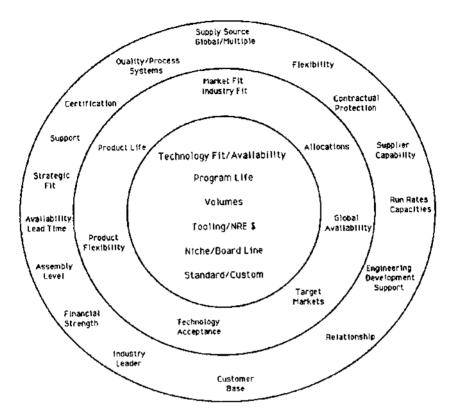

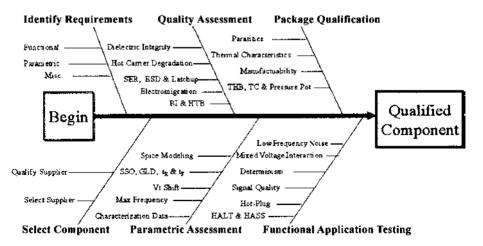

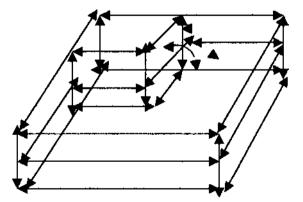

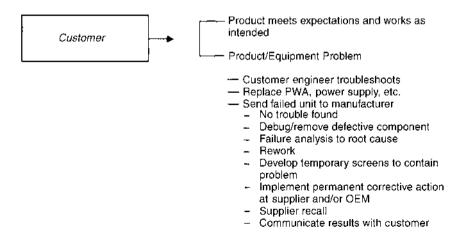

Reliability cannot be an afterthought apart from the design phase, i.e., something that is considered only when manufacturing yield is low or when field failure rate and customer returns are experienced. Reliability must be designed and built (manufactured) in from the start, commensurate with market and customer needs. It requires a complete understanding of the customer requirements and an accurate translation of those requirements to the language of the system designer. This results in a design/manufacturing methodology that produces a reliable delivered product that meets customer needs. Electronic hardware reliability includes both circuit and system design reliability, manufacturing process reliability, and product reliability. It is strongly dependent on the reliability of the individual components that comprise the product design. Thus, reliability begins and ends with the customer. Figure 1 shows this end-to-end product reliability methodology diagrammatically.

Stated very simply, reliability is not about technology. It's about customer service and satisfaction and financial return. If a consumer product is reliable, customers will buy it and tell their friends about it, and repeat business will ensue. The same holds true for industrial products. The net result is less rework and low field return rate and thus increased revenue and gross margin. Everything done to improve a product's reliability is done with these thoughts in mind.

Now that I've danced around it, just what is this nebulous concept we are talking about? *Quality* and *reliability* are very similar terms, but they are not interchangeable. Both quality and reliability are related to variability in the electronic product manufacturing process and are interrelated, as will be shown by the bathtub failure rate curve that will be discussed in the next section.

**FIGURE 1** End-to-end product reliability.

*Quality* is defined as product performance against requirements at an instant in time. The metrics used to measure quality include

PPM: parts per million defective AQL: acceptable quality level LTPD: lot tolerance percent defective

*Reliability* is the performance against requirements over a period of time. Reliability measurements always have a time factor. IPC-SM-785 defines reliability as the ability of a product to function under given conditions and for a specified period of time without exceeding acceptable failure levels.

According to IPC standard J-STD-001B, which deals with solder joint reliability, electronic assemblies are categorized in three classes of products, with increasing reliability requirements.

*Class 1*, or general, electronic products, including consumer products. Reliability is desirable, but there is little physical threat if solder joints fail. *Class 2*, or dedicated service, electronics products, including industrial and commercial products (computers, telecommunications, etc.). Reliability is important, and solder joint failures may impede operations and increase service costs.

*Class 3*, or high-performance, electronics products, including automotive, avionics, space, medical, military, or any other applications where reliability is critical and solder joint failures can be life/mission threatening.

Class 1 products typically have a short design life, e.g., 3 to 5 years, and may not experience a large number of stress cycles. Class 2 and 3 products have longer design lives and may experience larger temperature swings. For example, commercial aircraft may have to sustain over 20,000 takeoffs and landings over a 20-year life, with cargo bay electronics undergoing thermal cycles from ground level temperatures (perhaps as high as 50°C under desert conditions) to very low temperatures at high altitude (about -55°C at 35,000 feet). The metrics used to measure reliability include

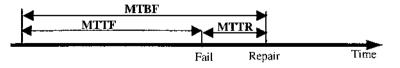

Percent failure per thousand hours MTBF: mean time between failure MTTF: mean time to failure FIT: failures in time, typically failures per billion hours of operation

Reliability is a hierarchical consideration at all levels of electronics, from materials to operating systems because

Materials are used to make components. Components compose subassemblies. Subassemblies compose assemblies.

Assemblies are combined into systems of ever-increasing complexity and sophistication.

#### 1.2 DISCIPLINE AND TASKS INVOLVED WITH PRODUCT RELIABILITY

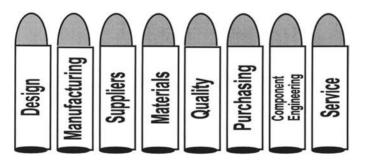

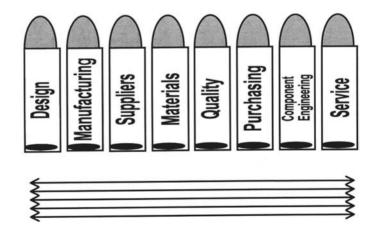

Electronic product reliability encompasses many disciplines, including component engineering, electrical engineering, mechanical engineering, materials science, manufacturing and process engineering, test engineering, reliability engineering, and failure analysis. Each of these brings a unique perspective and skill set to the task. All of these need to work together as a single unit (a team) to accomplish the desired product objectives based on customer requirements.

These disciplines are used to accomplish the myriad tasks required to develop a reliable product. A study of 72 nondefense corporations revealed that the product reliability techniques they preferred and felt to be important were the following (listed in ranked order) (1):

| Supplier control                                 | 76% |

|--------------------------------------------------|-----|

| Parts control                                    | 72% |

| Failure analysis and corrective action           | 65% |

| Environmental stress screening                   | 55% |

| Test, analyze, fix                               | 50% |

| Reliability qualification test                   | 32% |

| Design reviews                                   | 24% |

| Failure modes, effects, and criticality analysis | 20% |

Each of these companies used several techniques to improve reliability. Most will be discussed in this book.

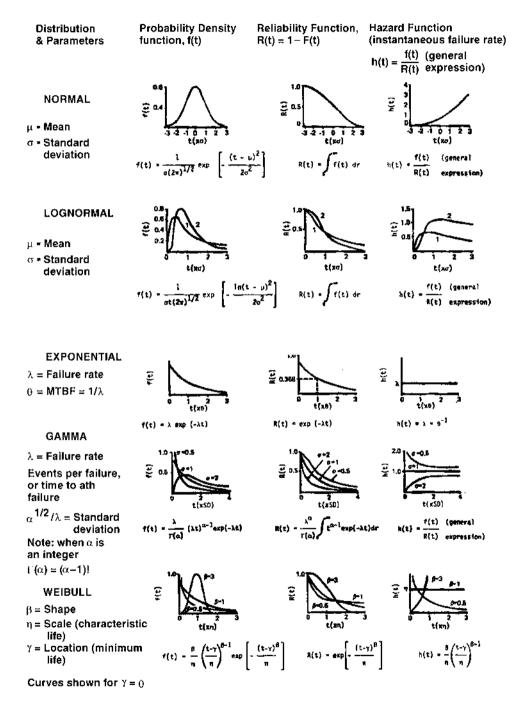

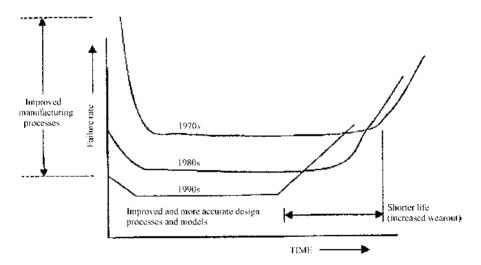

#### **1.3 THE BATHTUB FAILURE RATE CURVE**

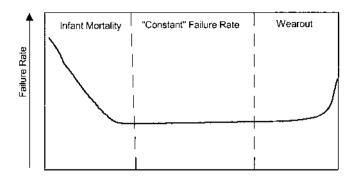

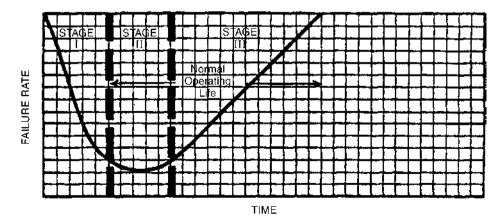

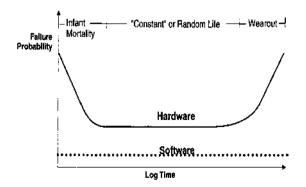

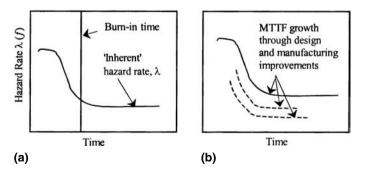

Historically, the bathtub failure rate curve has been used to discuss electronic equipment (product) reliability. Some practitioners have questioned its accuracy and applicability as a model for reliability. Nonetheless, I use it for "talking purposes" to present and clarify various concepts. The bathtub curve, as shown in Figure 2, represents the instantaneous failure rate of a population of identical items at identical constant stress. The bathtub curve is a composite diagram that provides a framework for identifying and dealing with all phases of the lives of parts and equipment.

Observations and studies have shown that failures for a given part or piece of equipment consist of a composite of the following:

FIGURE 2 The bathtub curve.

| Quality     | Unrelated to stress         | Eliminated by inspection process and       |

|-------------|-----------------------------|--------------------------------------------|

|             | Not time-dependent          | process improvements                       |

| Reliability | Stress-dependent            | Eliminated by screening                    |

| Wearout     | Time-dependent              | Eliminated by replacement, part design, or |

|             |                             | new source                                 |

| Design      | May be stress- and/or time- | Eliminated by proper application and       |

| _           | dependent                   | derating                                   |

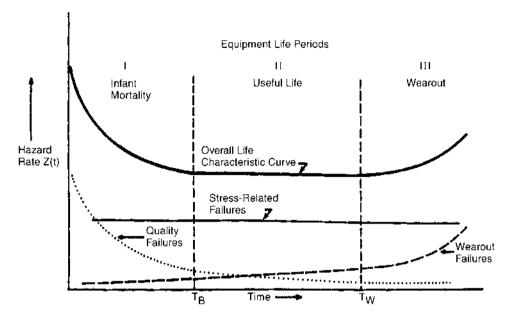

The bathtub curve is the sum of infant mortality, random failure, and wearout curves, as shown in Figure 3. Each of the regions is now discussed.

#### 1.3.1 Region I—Infant Mortality/Early Life Failures

This region of the curve is depicted by a high failure rate and subsequent flattening (for some product types). Failures in this region are due to quality problems and are typically related to gross variations in processing and assembly. Stress screening has been shown to be very effective in reducing the failure (hazard) rate in this region.

#### 1.3.2 Region II—Useful Life or Random Failures

Useful life failures are those that occur during the prolonged operating period of the product (equipment). For electronic products it can be much greater than 10 years but depends on the product and the stress level. Failures in this region are related to minor processing or assembly variations. The defects track with the defects found in Region I, but with less severity. Most products have acceptable

**FIGURE 3** The bathtub curve showing how various failures combine to form the composite curve.

failure rates in this region. Field problems are due to "freak" or maverick lots. Stress screening cannot reduce this inherent failure rate, but a reduction in operating stresses and/or increase in design robustness (design margins) can reduce the inherent failure rate.

#### 1.3.3 Region III—Aging and Wearout Failures

Failures in this region are due to aging (longevity exhausted) or wearout. All products will eventually fail. The failure mechanisms are different than those in regions I and II. It has been stated that electronic components typically wear out after 40 years. With the move to deep submicron ICs, this is dramatically reduced. Electronic equipment/products enter wearout in 20 years or so, and mechanical parts reach wearout during their operating life. Screening cannot improve reliability in this region, but may cause wearout to occur during the expected operating life. Wearout can perhaps be delayed through the implementation of stress-reducing designs.

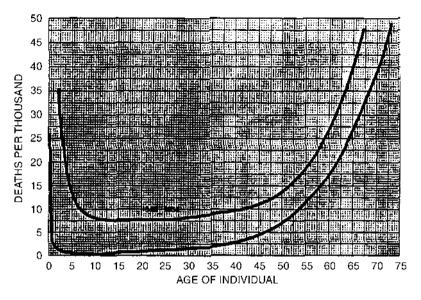

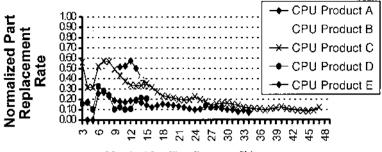

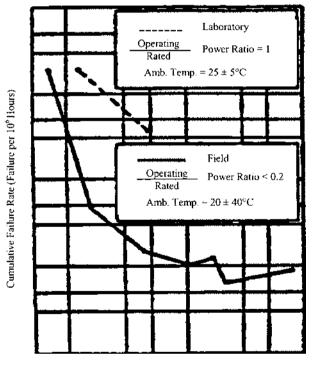

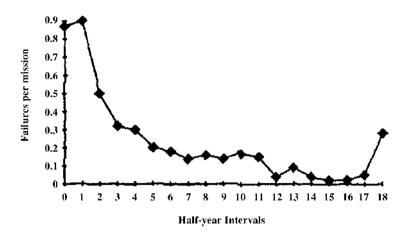

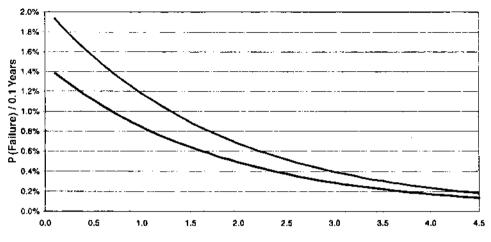

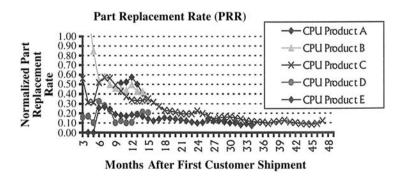

Figures 4–8 depict the bathtub failure rate curves for human aging, a mechanical component, computers, transistors, and spacecraft, respectively. Note that since mechanical products physically wear out, their life cycle failure rate

FIGURE 4 Human life cycle curve.

is very different from the electronic product life curve in the following ways: significantly shorter total life; steeper infant mortality; very small useful operating life; fast wearout.

Figure 9 shows that the life curve for software is essentially a flat straight line with no early life or wearout regions because all copies of a software program

FIGURE 5 Mechanical component life cycle curve.

Months After First Customer Shipment

FIGURE 6 Computer failure rate curve.

Calendar Operating Time (103 Hours)

FIGURE 7 Failure rates for NPN silicon transistors (1 W or less) versus calendar operating time.

FIGURE 8 Failure rate for spacecraft in orbit.

are identical and software reliability is time-independent. Software has errors or defects just like hardware. Major errors show up quickly and frequently, while minor errors occur less frequently and take longer to occur and detect. There is no such thing as stress screening of software.

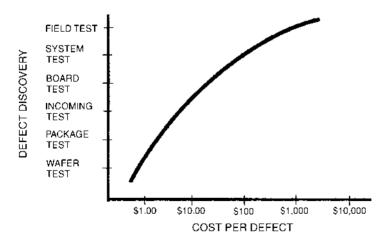

The goal is to identify and remove failures (infant mortalities, latent defects) at the earliest possible place (lowest cost point) before the product gets in the customer's hands. Historically, this has been at the individual component level but is moving to the printed wiring assembly (PWA) level. These points are covered in greater detail in Chapters 4 and 7.

**FIGURE 9** Typical software–hardware comparison life curve.

Let me express a note of caution. The bathtub failure rate curve is useful to explain the basic concepts, but for complete electronic products (equipment), the time-to-failure patterns are much more complex than the single graphical representation shown by this curve.

#### 1.4 RELIABILITY GOALS AND METRICS

Most hardware manufacturers establish reliability goals for their products. Reliability goals constrain the design and prevent the fielding of products that cannot compete on a reliability basis. Reliability goals are based on customer expectations and demand, competitive analysis, comparisons with previous products, and an analysis of the technology capability. A combined top-down and bottom-up approach is used for goal setting and allocation. The top-down approach is based on market demand and competitive analysis. Market demand is measured by customer satisfaction surveys, feedback from specific customers, and the business impact of lost or gained sales in which hardware reliability was a factor. The topdown analysis provides reliability goals at a system level, which is the customer's perspective.

The bottom-up approach is based on comparing the current product to previous products in terms of complexity, technology capability, and design/manufacturing processes. Reliability predictions are created using those factors and discussions with component suppliers. These predictions are performed at the unit or board level, then rolled up to the system level to be compared with the topdown goals. If they do not meet the top-down goals, an improvement allocation is made to each of the bottom-up goals, and the process is iterated.

However, there is a wide gap between what is considered a failure by a customer and what is considered a failure by hardware engineering. Again, using computers as an example, the customer perceives any unscheduled corrective maintenance (CM) activity on a system, including component replacement, adjustment, alignment, and reboot as a failure. Hardware engineering, however, considers only returned components for which the failure can be replicated as a failure. The customer-perceived failure rate is significantly higher than engineering-perceived failure rate because customers consider no-trouble-found (NTF) component replacements and maintenance activity without component replacement as failures. This dichotomy makes it possible to have low customer satisfaction with regard to product reliability even though the design has met its failure rate goals. To accommodate these different viewpoints, multiple reliability metrics are specified and measured. The reliability goals are also translated based on customer expectations into hardware engineering goals such that meeting the hardware engineering goals allows the customer expectations to be met.

Typical reliability metrics for a high-reliability, high-availability, fault-

| Metric                              | Definition                                                                                                                                                                                                                                                            |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Corrective maintenance<br>(CM) rate | A corrective maintenance activity such as a part replace-<br>ment, adjustment, or reboot. CMs are maintenance activi-<br>ties done in a reactive mode and exclude proactive activ-<br>ity such as preventive maintenance.                                             |

| Part replacement (PR)<br>rate       | A part replacement is any (possibly multiple) part replaced<br>during a corrective maintenance activity. For almost all<br>the parts we track, the parts are returned to the factory, so<br>part replacement rate is equivalent to part return rate.                  |

| Failure rate                        | A returned part that fails a manufacturing or engineering<br>test. Any parts that pass all tests are called no trouble<br>found (NTF). NTFs are important because they indicate a<br>problem with our test capabilities, diagnostics, or support<br>process/training. |

**TABLE 2** Metric Definitions for a High-Reliability, High-Availability,Fault-Tolerant Computer

Note: All rates are annualized and based on installed part population.

tolerant computer are shown in Table 2. The CM rate is what customers see. The part (component) replacement (PR) rate is observed by the factory and logistics organization. The failure rate is the engineers' design objective. The difference between the failure rate and the PR rate is the NTF rate, based on returned components that pass all the manufacturing tests. The difference between the CM rate and PR rate is more complex.

If no components are replaced on a service call, the CM rate will be higher than the PR rate. However, if multiple components are replaced on a single service call, the CM rate will be lower than the PR rate. From the author's experience, the CM rate is higher than the PR rate early in the life of a product when inadequate diagnostics or training may lead to service calls for which no problem can be diagnosed. For mature products these problems have been solved, and the CM and PR rates are very similar.

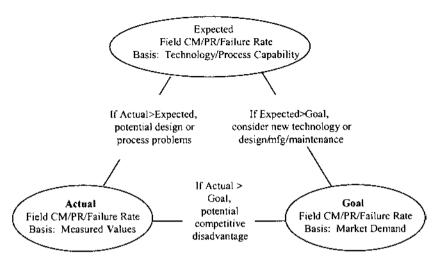

Each of the stated reliability metrics takes one of three forms:

CM/PR/failure rate goal, based on market demand Expected CM/PR/failure rate, based on predictions Actual CM/PR/failure rate, based on measurement

The relationships among the various forms of the metrics are shown in Figure 10.

FIGURE 10 Reliability metric forms.

#### **1.5 RELIABILITY PREDICTION**

Customers specify a product's reliability requirements. The marketing/product development groups want an accurate quantitative ability to trade off reliability for performance and density. They also may require application-specific qualifications to meet the needs of different market segments. The designers want design for reliability requirements that will not impede their time to market. Manufacturing wants stable qualified processes and the ability to prevent reliability problems. And there is the continuous pressure to reduce the cost of operations.

Reliability modeling assists in calculating system-level reliability from subsystem data and depicts the interrelationship of the components used. Using reliability models, a designer can develop a system that will meet the reliability and system level requirements and can perform tradeoff studies to optimize performance, cost, or specific parameters.

Reliability prediction is performed to determine if the product design will meet its goals. If not, a set of quality initiatives or process improvements are identified and defined such that the goals will be met. Reliability process improvements are justified by relating them directly to improved field reliability predictions.

Reliability prediction is nothing more than a tool for getting a gross baseline understanding of what a product's potential reliability (failure rate) is. The number derived from the calculations is not to be an end-all panacea to the reliability issue. Rather it is the beginning, a call to understand what constitutes reliability for that product and what the factors are that detract from achieving higher reliability. This results in an action plan.

Initial reliability predictions are usually based on component failure rate models using either MIL-HDBK-217 or Bellcore Procedure TR-332. Typically one analyzes the product's bill of materials (BOM) for the part types used and plugs the appropriate numbers into a computer program that crunches the numbers. This gives a first "cut" prediction. However, the failure rates predicted are usually much higher than those observed in the field and are considered to be worst-case scenarios.

One of the criticisms of the probabilistic approach to reliability (such as that of MIL-HDBK-217) is that it does not account for interactions among components, materials, and processes. The failure rate for a component is considered to be the same for a given component regardless of the process used to assemble it into the final product. Even if the same process is used by two different assemblies, their methods of implementation can cause differences.

Furthermore, since reliability goals are based on competitive analysis and customer experience with field usage, handbook-based reliability predictions are unlikely to meet the product goals. In addition, these predictions do not take into account design or manufacturing process improvements possibly resulting from the use of highly accelerated life test (HALT) or environmental stress screening (ESS), respectively. Table 3 presents some of the limitations of reliability prediction.

Thus, reliability prediction is an iterative process that is performed throughout the design cycle. It is not a "once done, forever done" task. The initial reliability prediction is continually refined throughout the design cycle as the bill of materials gets solidified by factoring in test data, failure analysis results, and

#### **TABLE 3** Limitations of Reliability Prediction

- Simple techniques omit a great deal of distinguishing detail, and the very prediction suffers inaccuracy.

- Detailed prediction techniques can become bogged down in detail and become very costly. The prediction will also lag far behind and may hinder timely hardware development.

- Considerable effort is required to generate sufficient data on a part class/level to report statistically valid reliability figures for that class/level.

- Component reliability in fielded equipment is very difficult to obtain due to lack of suitable and useful data acquisition.

- Other variants that can affect the stated failure rate of a given system are uses, operator procedures, maintenance and rework practices, measurement techniques or definitions of failure, operating environments, and excess handling differing from those addressed by modeling techniques.

the degree to which planned reliability improvement activities are completed. Subsequent predictions take into account usage history with the component technology, suppliers, and specific component type (part number) as well as field data from previous products and the planned design and manufacturing activities. Field data at the Tandem Division of Compaq Computer Corporation has validated that the reliability projections are more accurate than handbook failure rate predictions.

#### 1.5.1 Example of Bellcore Reliability Prediction

A calculated reliability prediction for a 56K modem printed wiring assembly was made using Bellcore Reliability Prediction procedure for Electronic Equipment, TR-332 Issue 5, December 1995. (Currently, Issue 6, December 1997, is the latest revision of Bellcore TR-332. The device quality level has been increased to four levels: 0, I, II, and III, with 0 being the new level. Table 4 describes these four levels.) Inherent in this calculation are the assumptions listed in Table 5.

Assuming component Quality Level I, the calculated reliability for the PWA is 3295 FITS (fails per  $10^9$  hr), which is equivalent to an MTBF of 303,481 hr. This failure rate is equivalent to an annual failure rate of 0.029 per unit, or 2.9 failures per hundred units per year. The assumption is made that

**TABLE 4** Device Quality Level Description from Bellcore TR-332(Issue 6, December 1997)

- The device failure rates contained in this document reflect the expected field reliability performance of generic device types. The actual reliability of a specific device will vary as a function of the degree of effort and attention paid by an equipment manufacturer to factors such as device selection/application, supplier selection/ control, electrical/mechanical design margins, equipment manufacturing process controls, and quality program requirements.

- *Quality Level 0* Commercial-grade, reengineered, remanufactured, reworked, salvaged, or gray-market components that are procured and used without device qualification, lot-to-lot controls, or an effective feedback and corrective action program by the equipment manufacturer.

- *Quality Level I* Commercial-grade components that are procured and used without thorough device qualification or lot-to-lot controls by the equipment manufacturer.

- *Quality Level II* Components that meet requirements of Quality Level I plus purchase specifications that explicitly identify important characteristics (electrical, mechanical, thermal, and environmental), lot control, and devices qualified and listed on approved parts/manufacturer's lists.

- *Quality Level III* Components that meet requirements of Quality Levels I and II plus periodic device qualification and early life reliability control of 100% screening. Also an ongoing continuous reliability improvement program must be implemented.

TABLE 5

56K Modem Analysis Assumptions

| An ambient air temperature of 40°C around the components (measured 0.5 in. above the component) is assumed.                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Component Quality Level I is used in the prediction procedure. This assumes standard commercial, nonhermetic devices, without special screening or preconditioning. The exception is the Opto-couplers, which per Bellcore recommendation are assumed to be Level III. |

| Electrical stresses are assumed to be 50% of device ratings for all components.                                                                                                                                                                                        |

| Mechanical stress environment is assumed to be ground benign (GB).                                                                                                                                                                                                     |

| Duty cycle is 100% (continuous operation).                                                                                                                                                                                                                             |

| A mature manufacturing and test process is assumed in the predicted failure rate (i.e., all processes under control).                                                                                                                                                  |

| The predicted failure rate assumes that there are no systemic design defects in the product.                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                        |

| there are no manufacturing test, or design problems that significantly affect field                                                                                                                                                                                    |

reliability. The results fall well within the normal range for similar hardware items used in similar applications. If quality Level II components are used the MTBF improves by a factor of about 2.5. One has to ask the following question: is the improved failure rate worth the added component cost? Only through a risk analysis and an understanding of customer requirements will one be able to answer this question.

|                  | Failure rate (FITS) | MTBF (hr) | Annualized failure rate |

|------------------|---------------------|-----------|-------------------------|

| Quality Level I  | 3295                | 303,481   | 0.029                   |

| Quality Level II | 1170                | 854,433   | 0.010                   |

The detailed bill-of-material failure rates for Quality Levels I and II are presented in Tables 6 and 7, respectively.

#### 1.6 RELIABILITY RISK

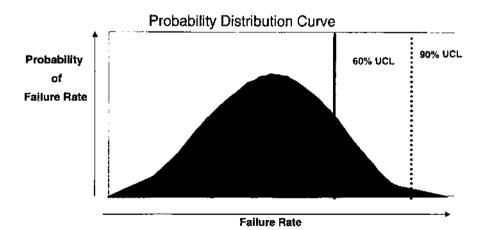

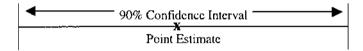

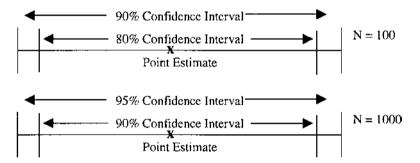

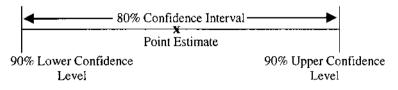

It is important that the person or group of people who take action based on reliability prediction understand risk. Reliability predictions vary. Some of the source of risks include correct statistical distribution, statistical error (confidence limits), and uncertainty in models and parameters.

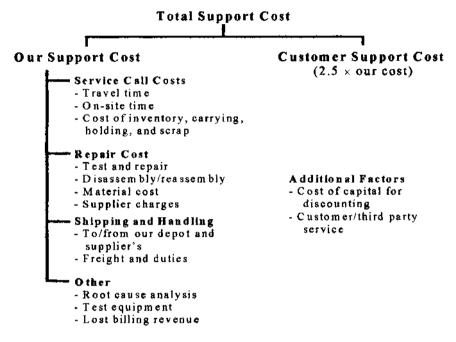

Reliability metrics revolve around minimizing costs and risks. Four cost elements to incorporate in metrics are

| ID     | Generic name          | Item code                             | Part name                        | QTY     | FR    |

|--------|-----------------------|---------------------------------------|----------------------------------|---------|-------|

| 1.1.54 | <b>v</b> <sup>1</sup> | IC-Memory                             | IC, SRAM, 32Kx8,15ns,3.3V,SOJ-2  | 2       | 438.8 |

|        | 322078-001            | IC-Memory                             | IC, FEPROM,256Kx8,3.3V,50ns,TSO  | 1       | 251.3 |

| 1.1.72 | 194774-001            | IC-Meriory                            | IC, \$M,V/REG,3.3V,500MA,MAX604  |         | 155.3 |

|        |                       | · · · · · · · · · · · · · · · · · · · | IC, ANALOG, CODEC, MQFP44, LUCE  |         | 285.8 |

| 1.1.96 | 009000-000            | IC-Analog                             |                                  | I       | 198.2 |

| 1.1.71 | 191952-001            | IC-Digital                            | IC, EEPROM,512x8,24CO4,SOIC      |         | 81.8  |

| 1.1.80 | 322062-001            | IC-Digital                            | IC, USB JCNTRLR, USS820, 48TQFP  |         | 81.8  |

| 1.1.91 | 322081-001            | IC-Digital                            | IC, DAT PMP,DSP1675T28,128TQFP   |         | 1.5   |

| 1.1.5  | 106146-099            | Resistor                              | RES, SM,2.4K OHM,1/8W,5%         | <br>  i | -     |

| 1.1.6  | 106146-118            | Resistor                              | RES, SM,15K OHM,1/8W,5%          | 1       | 1.5   |

| 1.1.9  | 107263-100            | Resistor                              | RES, SM,2.7K OHM,1/4W,5%         | -       |       |

| 1.1.10 | 107263-111            | Resistor                              | RES, SM,7.5K OHM,1/4W,5%         | 1 2     | 1.5   |

| 1.1.20 | 114740-238            | Resistor                              | RES, SM,24.3 OHM,1%,1/10W,0805   |         | 3.0   |

| 1.1.23 | 119200-530            | Resistor                              | RES, SM,20.0k OHM, 1/4W, 1%      | 2       | 3.0   |

| 1.1.29 | 119919-001            | Resistor                              | RES, SM,0 OHM,1/16W,5%,0603      | 4       | 6.0   |

| 1.1.30 | 119919-034            | Resistor                              | RES, SM 4.7 OHM, 1/16W, 5%, 0603 | 1       | 1.5   |

| 1.1.31 | 119919-054            | Resistor                              | RES, SM,33 OHM,1/16W,5%,0603     | 1       | 1.5   |

| t.1.32 | 119919-070            | Resistor                              | RES, SM,150 OHM,1/16W,5%,0603    | 4       | 6.0   |

| 1.1.34 | 119919-082            | Resistor                              | RES, SM,470 OHM,1/16W,5%,0603    | 5       | 7.5   |

| 1.1.35 | 119919-086            | Resistor                              | RES, SM,680 OHM,1/16W,5%,0603    | 1       | 1.5   |

| 1.1.36 | 119919-090            | Resistor                              | RES, SM,1K OH,1/16W,5%,0603      | 1       | 1.5   |

| 1.1.37 | 119919-094            | Resistor                              | RES, SM,1.5K OHM,1/16W,5%,0603   | 1       | 1.5   |

| 1.1.38 | 119919-097            | Resistor                              | RES, SM,2K OHM,1/16W,5%,0603     | 1       | 1.5   |

| 1.1.39 | 119919-102            | Resistor                              | RES, SM,3.3K OHM,1/16W,5%,0603   | 1       | 1.5   |

| 1.1.40 | 119919-112            | Resistor                              | RES, SM,8.2K OHM,1/16W,5%,0603   | 1       | 1.5   |

| 1.1.41 | 119919-114            | Resistor                              | RES, SM,10K OHM,1/16W,5%,0603    | 2       | 3.0   |

| 1.1.42 | 119919-134            | Resistor                              | RES, SM,68KOHM,1/16W,5%,0603     | 1       | 1.5   |

| 1.1.43 | 119919-138            | Resistor                              | RES, SM,100K OHM,1/16W,5%,0603   | 4       | 6.0   |

| 1.1.48 | 124637-013            | Resistor                              | RES, SM,39 OHM,1W,5%             | 1       | 1.5   |

| 1.1.55 | 139708-001            | Resistor                              | RES, SM,100 OHM,1%,1/16W,603     | 1       | 1.5   |

| 1.1.56 | 139708-006            | Resistor                              | RES, SM,10K,1%,1/16W,603         | 18      | 27.0  |

| 1.1.57 | 139708-015            | Resistor                              | RES, SM,191 OHM,1%,1/16W,603     | 2       | 3.0   |

|        | 139708-045            | Resistor                              | RES, SM,34.0K,1%,1/16W,603       | 2       | 3.0   |

| 1.1.59 | 139708-096            | Resistor                              | RES, SM,475 OHM,1%,1/16W,603     | 2       | 3.0   |

| 1.1.60 | 139708-133            | Resistor                              | RES, SM,33.2k,1%,1/16W,603       | 2       | 3.0   |

| 1.1.61 | 139708-135            | Resistor                              | RES, SM,16.2k,1%,1/16W,603       | 2       | 3.0   |

| 1.1.62 | 139708-170            | Resistor                              | RES, SM,1.30K,1%,1/16W,0603      | 1       | 1.5   |

| 1.1.63 | 139708-194            | Resistor                              | RES, SM,26.1K,1%,1/16W,0603      | 2       | 3.0   |

| 1.1.1  | 105077-157            | Capacitor                             | CAP, SM, 047MFD, 50V, 5%, X7R    | L       | 3.0   |

| 1.1.2  | 105077-163            | Capacitor                             | CAP, SM,50V,X7R,5%,15uF,1812     | 2       | 6.0   |

| 1.1.3  | 105079-236            | Capacitor                             | CAP, SM,820PF,50V,10%,NPO        | 2       | 6.0   |

| 1.1.14 | 109764-013            | Capacitor                             | CAP, SM,1MFD,20V,20%,TANT        | 1       | 3.0   |

| 1.1.15 | 109764-017            | Capacitor                             | CAP, SM,4.7MFD,20V,20%,TANT      | l       | 3.0   |

| 1.1.22 | 117467-726            | Capacitor                             | CAP, 22MFD,35V ALEL              | 2       | 246.0 |

| 1.1.25 | 119917-115            | Capacitor                             | CAP, SM,15pF,5%,50V,COG,603      | 2       | 6.0   |

| 1.1.26 | 119917-118            | Capacitor                             | CAP, SM,27pF,5%,50V,COG,603      | 4       | 12.0  |

| 1.1.27 | 119917-121            | Capacitor                             | CAP, SM,47pF,5%,50V,COG,603      | 2       | 6.0   |

| 1.1.45 | 119949-001            | Capacitor                             | CAP, SM,22uf,35V,20%             | 3       | 9.0   |

|        |                       |                                       |                                  | · · · · |       |

TABLE 6

Reliability Calculation Assuming Quality Level I

| ID     | Generic name | Item code           | Part name                          | QTY | FR    |

|--------|--------------|---------------------|------------------------------------|-----|-------|

| 1.1.46 | 119949-003   | Capacitor           | CAP, SM,10uF,16V,20%,ALEL          | 5   | 225.0 |

| 1.1.50 | 129621-012   | Capacitor           | CAP, SM,CER,Y5V,0.1uF,16v,0603     | 32  | 96.0  |

| 1.1.51 | 129621-021   | Capacitor           | CAP, SM,CER,Y5V,10uF,35V,1210      | 1   | 3.0   |

| 1.1.52 | 129633-201   | Capacitor           | CAP, SM,25V,10%,0.015,0603         | 1   | 3.0   |

| 1.1.73 | 198183-002   | Capacitor           | CAP, SM, 47UF, X7R, 250V, 1825     | 1   | 3.0   |

| 1.1.83 | 322066-001   | Switch              | SWITCH, PUSH-PUSH, PB, THRU/HOLE   | 1   | 45.0  |

| 1.1.85 | 322068-001   | Relay               | IC, SM,SLD ST RLY,2FORMA,400V      | 1   | 75.0  |

| 1.1.86 | 322070-001   | Relay               | IC, SM, PWR SW, 1.2A, TPS2041D, SO | 1   | 75.0  |

| 1.1.8  | 106899-016   | Connector           | CONN, PCB, T/JK, 6P, LOW PRO       | 2   | 7.2   |

| 1.1.82 | 322065-001   | Connector           | CONN, USB,4P,T/H,TYPE-B            | 1   | 2.4   |

| 1.1.4  | 106125-001   | LF Diode            | DIODE, SM,GNL PRPPIN2NC            | 3   | 54.0  |

| 1.1.17 | 110118-001   | LF Diode            | DIODE, SM,ZENER, 10V               | 2   | 36.0  |

| 1.1.18 | 110118-012   | LF Diode            | DIODE, SM,ZENER, 18V               | 2   | 36.0  |

| 1.1.24 | 119606-001   | LF Diode            | DIODE, SM, DUAL, SWITCHING         | 2   | 72.0  |

| 1.1.67 | 187108-002   | LF Diode            | VSTR, SM,275V,250A,2215            | 1   | 30.0  |

| 1.1.68 | 187108-005   | LF Diode            | VSTR, SM,100V,250A,2215            | 1   | 30.0  |

| 1.1.93 | 353914-001   | LF Diode            | DIODE, SM, TVSARRAY, LOWCAP, 500W  | 1   | 18.0  |

| 1.1.11 | 107269-002   | LF Transistor       | XSTR, SM,NPNMMBTA42                | 1   | 18.0  |

| 1.1.16 | 110098-001   | LF Transistor       | XSTR, SM, PNP, MED PWR2907         | 1   | 18.0  |

| 1.1.49 | 128920-001   | LF Transistor       | XSTR, SM,NPN,HGH GAIN,MMBT6429     | 1   | 18.0  |

| 1.1.74 | 204109-002   | LF Transistor       | XSTR, SM,DGTL FET,N-CH,25V, 2A     | 1   | 60.0  |

| 1.1.90 | 322080-001   | LF Transistor       | XSTR, NPN, PWR, 80V, 1.5A, BD139   | 1   | 18.0  |

| 1.1.92 | 342615-001   | LF Transistor       | IC, SM,LD SW,8V.6323L,SSOT-6       | 1   | 120.0 |

| 1.1.19 |              |                     | DIODE, SM,LED,PURE GREEN,XPRNT     | 4   | 36.0  |

|        |              | tronic              |                                    |     |       |

| 1.1.77 |              | Optoelec-<br>tronic | IC, SM,OPTOCPI.R,300% CTR          | 2   | 54.0  |

| 1.1.78 |              |                     | IC, SM,OPTOCPLR,DUAL,300% CTR      | i   | 54.0  |

|        |              | tronic              |                                    |     |       |

|        |              |                     | FB, SM,80 OHM,500mA,1806           | 4   | 6.0   |

|        |              |                     | FB, SM,600 OHM,200mA,805           | 2   | 3.0   |

|        |              |                     | SPKR, XDCR,MINI PCB MMT            | 1   | 21.0  |

|        |              |                     | XFMR, MINI,V.32bis                 | 1   | 12.0  |

|        |              |                     | XTAL, 12.00MHZ,20PF,30PPM          | 1   | 75.0  |

| 1.1.69 | 187131-008   | Crystai             | XTAL, SM,29.4912MHz,20PF,20PPM     | 1   | 75.0  |

TABLE 6

Continued

- 1. The cost of a failure in the field

- 2. The cost of lost business due to unacceptable field failures

- 3. Loss of revenue due to reliability qualification delaying time to market

- 4. The cost of the lost opportunity to trade off "excess" reliability safety margins for increased performance/density

Note that the first two items represent a cost associated with failures that occur in a *small subpopulation* of the devices produced. In contrast the last two terms represent an opportunity to increase the profits on *every part* produced. Economic

| 1D     | Generic name | Item code  | Part name                          | QTY      | FR    |

|--------|--------------|------------|------------------------------------|----------|-------|

| 1.1.54 | 137240-007   | IC-Memory  | IC, SRAM,32Kx8,15ns,3.3V,SOJ-2     | 2        | 146.3 |

| 1.1.89 | 322078-001   | IC Memory  | IC, FEPROM,256Kx8,3.3V,50ns,TSO    |          | 83.8  |

| 1.1.72 | 194774-001   | IC-Analog  | IC, SM, V/REG, 3.3V, 500MA, MAX604 | 1        | 51.8  |

| 1.1.96 | 009000-000   | IC-Analog  | IC, ANALOG, CODEC, MQFP44, LUCE    | 1        | 95.3  |

| 1.1.71 | 191952-001   | IC-Digital | IC, EEPROM,512x8,24CO4,SOIC        | i        | 66.1  |

| 1.1.80 | 322062-001   | IC-Digital | IC, USB uCNTRLR, USS820, 48TQFP    |          | 27.3  |

| 1.1.91 | 322081-001   | IC-Digital | IC, DAT PMP, DSP1675T28, 128TOFP   | 1        | 27.3  |

| 1.1.5  | 106146-099   | Resistor   | RES, SM,2.4K OHM,1/8W,5%           |          | 0.5   |

| 1.1.6  | 106146-118   | Resistor   | RES, SM,15K OHM,1/8W,5%            | 1        | 0.5   |

| 1.1.9  | 107263-100   | Resistor   | RES, SM,2.7K OHM,1/4W,5%           | 1        | 0.5   |

| 1.1.10 | 107263-111   | Resistor   | RES, SM,7.5K OHM,1/4W,5%           | 1        | 0.5   |

| 1.1.20 | 114740-238   | Resistor   | RES, SM,24.3 OHM,1%,1/10W,0805     | 2        | 1.0   |

| 1.1.23 | 119200-530   | Resistor   | RES, SM,20.0k OHM, 1/4W, 1%        | 2        | 1.0   |

| 1.1.29 | 119919-001   | Resistor   | RES, SM,0 OHM,1/16W,5%,0603        | 4        | 2.0   |

| 1.1.30 | 119919-034   | Resistor   | RES, SM 4.7 OHM,1/16W,5%,0603      | 1        | 0.5   |

| 1.1.31 | 119919-054   | Resistor   | RES, SM,33 OHM,1/16W,5%,0603       | 1        | 0.5   |

| 1.1.32 | 119919-070   | Resistor   | RES, SM,150 OHM,1/16W,5%,0603      | 4        | 2.0   |

| 1.1.34 | 119919-082   | Resistor   | RES, SM,470 OHM,1/16W,5%,0603      | 5        | 2.5   |

| 1.1.35 | 119919-086   | Resistor   | RES, SM,680 OHM,1/16W,5%,0603      | 1        | 0.5   |

| 1.1.36 | 119919-090   | Resistor   | RES, SM,1K OH,1/16W,5%,0603        | 1        | 0.5   |

| 1.1.37 | 119919-094   | Resistor   | RES, SM,1.5K OHM,1/16W,5%,0603     | 1        | 0.5   |

| 1.1.38 | 119919-097   | Resistor   | RES, SM,2K OHM,1/16W,5%,0603       | <b>I</b> | 0.5   |

| 1.1.39 | 119919-102   | Resistor   | RES, SM,3.3K OHM,1/16W,5%,0603     | 1        | 0.5   |

| 1.1.40 | 119919-112   | Resistor   | RES, SM,8.2K OHM,1/16W,5%,0603     | 1        | 0.5   |

| 1.1.41 | 119919-114   | Resistor   | RES, SM,10K OHM,1/16W,5%,0603      | 2        | 1.0   |

| 1.1.42 | 119919-134   | Resistor   | RES, SM,68KOHM,1/16W,5%,0603       | 1        | 0.5   |

| 1.1.43 | 119919-138   | Resistor   | RES, SM,100K OHM,1/16W,5%,0603     | 4        | 2.0   |

| 1.1.48 | 124637-013   | Resistor   | RES, SM,39 OHM,1W,5%               | 1        | 0.5   |

| 1.1.55 | 139708-001   | Resistor   | RES, SM,100 OHM,1%,1/16W,603       | 1        | 0.5   |

| 1.1.56 | 139708-006   | Resistor   | RES, SM,10K,1%,1/16W,603           | 18       | 9.0   |

| 1.1.57 | 139708-015   | Resistor   | RES, SM,191 OHM,1%,1/16W,603       | 2        | 1.0   |

| 1.1.58 | 139708-045   | Resistor   | RES, SM,34.0K,1%,1/16W,603         | 2        | 1.0   |

| 1.1.59 | 139708-096   | Resistor   | RES, SM,475 OHM,1%,1/16W,603       | . 2      | 1.0   |

| 1.1.60 | 139708-133   | Resistor   | RES, SM,33.2k,1%,1/16W,603         | 2        | 1.0   |

| 1.1.61 | 139708-135   | Resistor   | RES, SM,16.2k,1%,1/16W,603         | 2        | 1.0   |

| 1.1.62 | 139708-170   | Resistor   | RES, SM,1.30K,1%,1/16W,0603        | 1        | 0.5   |

| 1.1.63 | 139708-194   | Resistor   | RES, SM,26.1K,1%,1/16W,0603        | 2        | 1.0   |

| 1.1.1  | 105077-157   | Capacitor  | CAP, SM, 047MFD, 50V, 5%, X7R      | l        | 1.0   |

| 1.1.2  | 105077-163   | Capacitor  | CAP, SM,50V,X7R,5%,.15uF,1812      | 2        | 2.0   |

| 1.1.3  | 105079-236   | Capacitor  | CAP, SM,820PF,50V,10%,NPO          | 2        | 2.0   |

| 1.1.14 | 109764-013   | Capacitor  | CAP, SM,1MFD,20V,20%,TANT          | 1        | 1.0   |

| 1.1.15 | 109764-017   | Capacitor  | CAP, SM,4.7MFD,20V,20%,TANT        | 1        | 1.0   |

| 1.1.22 | 117467-726   | Capacitor  | CAP, 22MFD,35V ALEL                | 2        | 82.0  |

| 1.1.25 | 119917-115   | Capacitor  | CAP, SM,15pF,5%,50V,COG,603        | 2        | 2.0   |

| 1.1.26 | 119917-118   | Capacitor  | CAP, SM,27pF,5%,50V,COG,603        | 4        | 4.0   |

| 1.1.27 | 119917-121   | Capacitor  | CAP, SM,47pF,5%,50V,COG,603        | 2        | 2.0   |

| 1.1.45 | 119949-001   | Capacitor  | CAP, SM,22uf,35V,20%               | 3        | 3.0   |

TABLE 7

Reliability Calculation Assuming Quality Level II

| 1.1.46   | 119949-003 | Capacitor     | CAP, SM,10uF,16V,20%,ALEL          | 5  | 75.0 |

|----------|------------|---------------|------------------------------------|----|------|

| 1.1.50   | 129621-012 | Capacitor     | CAP, SM,CER,Y5V,0.1uF,16v,0603     | 32 | 32.0 |

| 1.1.51   | 129621-021 | Capacitor     | CAP, SM,CER,Y5V,10uF,35V,1210      | 1  | 1.0  |

| 1.1.52   | 129633-201 | Capacitor     | CAP, SM,25V,10%,0.015,0603         | 1  | 1.0  |

| 1.1.73   | 198183-002 | Capacitor     | CAP, SM, 47UF, X7R, 250V, 1825     | 1  | 1.0  |

| 1.1.83   | 322066-001 | Switch        | SWITCH, PUSH-PUSH, PB, THRU/HOLE   | 1  | 15.0 |

| 1.1.85   | 322068-001 | Relay         | IC, SM,SLD ST RLY,2FORMA,400V      | 1  | 25.0 |

| 1.1.86   | 322070-001 | Relay         | IC, SM, PWR SW, 1.2A, TPS2041D, SO | 1  | 25.0 |

| 1.1.8    | 106899-016 | Connector     | CONN, PCB,T/JK,6P,LOW PRO          | 2  | 2.4  |

| 1.1.82   | 322065-001 | Connector     | CONN, USB, 4P, T/H, TYPE-B         | 1  | 0.8  |

| 1.1.4    | 106125-001 | LF Diode      | DIODE, SM, GNL PRPPIN2NC           | 3  | 18.0 |

| 1.1.17   | 110118-001 | LF Diode      | DIODE, SM,ZENER,10V                | 2  | 12.0 |

| 1.1.18   | 110118-012 | LF Diode      | DIODE, SM,ZENER, 18V               | 2  | 12.0 |

| 1.1.24   | 119606-001 | LF Diode      | DIODE, SM, DUAL, SWITCHING         | 2  | 24.0 |

| 1.1.67   | 187108-002 | LF Diode      | VSTR, SM,275V,250A,2215            | 1  | 10.0 |

| 1.1.68   | 187108-005 | 1.F Diode     | VSTR, SM,100V,250A,2215            | 1  | 10.0 |

| 1.1.93   | 353914-001 | LF Diode      | DIODE, SM, TVSARRAY, LOWCAP, 500W  | 1  | 6.0  |

| 1.1.11   | 107269-002 | LF Transistor | XSTR, SM,NPNMMBTA42                | 1  | 6.0  |

| 1.1.16   | 110098-001 | LF Transistor | XSTR, SM, PNP, MED PWR2907         | 1  | 6.0  |

| 1.1.49   | 128920-001 | LF Transistor | XSTR, SM,NPN,HGH GAIN,MMB16429     | l  | 6.0  |

| [1.1.74] | 204109-002 | LF Transistor | XSTR, SM, DGTL FET, N-CH, 25V, 2A  | 1  | 20.0 |

| 1.1.90   | 322080-001 | LF Transistor | XSTR, NPN, PWR, 80V, 1.5A, BD139   | 1  | 6.0  |

| 1.1.92   | 342615-001 | LF Transistor | IC, SM,LD SW,8V,6323L,SSOT-6       | 1  | 40.0 |

| 1.1.19   | 110204-005 | Optoclec-     | DIODE, SM,LED,PURE GREEN,XPRNT     | 4  | 12.0 |

|          |            | tronic        |                                    |    |      |

| 1.1.77   | 298956-001 | Optoelec-     | IC, SM,OPTOCPLR,300% CTR           | 2  | 54.0 |

|          |            | tronic        |                                    |    |      |

| 1.1.78   | 298957-001 | Optoelec-     | IC, SM,OPTOCPLR,DUAL,300% CTR      | 1  | 54.0 |

| <u> </u> |            | tronic        |                                    |    | * *  |

| 1.1.12   | 107352-009 | Inductive     | FB, SM,80 OHM,500mA,1806           | 4  | 2.0  |

| 1.1.13   | 107352-013 | Inductive     | FB, SM,600 OHM,200mA,805           | 2  | 1.0  |

| 1.1.64   | 141639-001 | Inductive     | SPKR, XDCR, MINI PCB MMT           | 1  | 7.0  |

| 1.1.66   | 176560-001 | Inductive     | XFMR, MINI,V.32bis                 | 1  | 4.0  |

| 1.1.65   | 160642-011 | Crystal       | XTAL, 12.00MHZ,20PF,30PPM          | 1  | 25.0 |

| 1.1.69   | 187131-008 | Crystal       | XTAL, \$M,29.4912MHz,20PF,20PPM    | 1  | 25.0 |

TABLE 7

Continued

pressures are going to force increased attention on reliability's role in improving time to market and enhancing performance.

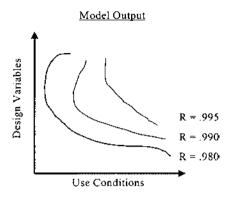

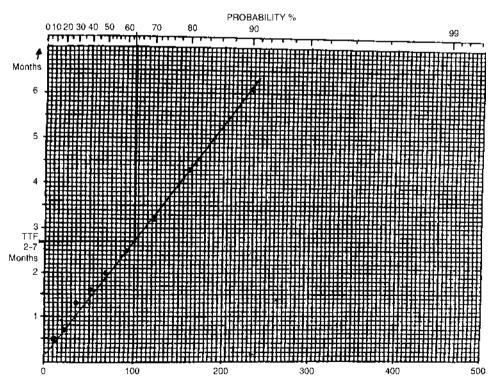

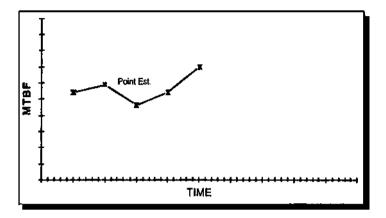

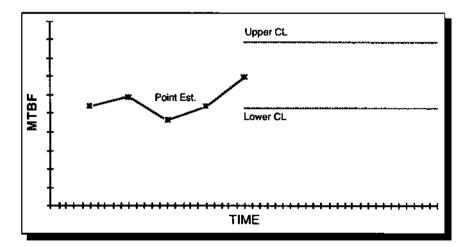

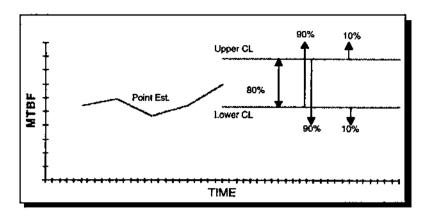

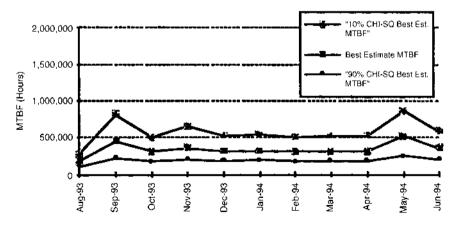

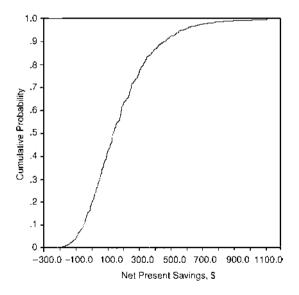

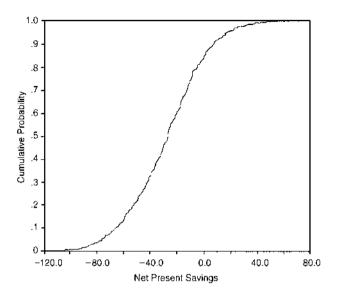

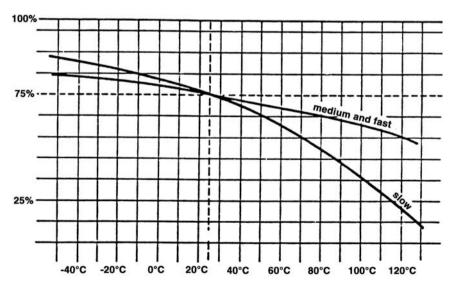

There are two ways to increase the value of reliability predictions. First, rather than a point prediction, the capability is needed to develop curves of reliability levels versus design, manufacturing, and end use variables (Fig. 11). This will allow optimization of the reliability given the economics of a particular marketplace. Second, risk needs to be quantified so it can be factored into technology decisions.

Let's use the bathtub curve to try to answer this question. As mentioned before, the bathtub curve depicts a product's reliability (i.e., failure rate) through-

FIGURE 11 Curves of reliability levels as a function of design and use conditions.

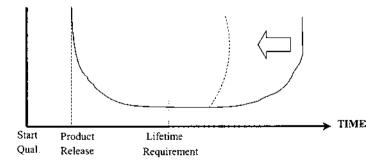

out its life. Figure 12 shows the bathtub curve with a vertical line placed at the product's design life requirements. If a high margin exists between the lifetime requirement and the wearout time, a high cost is incurred for having this design margin (overdesign for customer requirements), but there is a low reliability risk. If the wearout portion of the curve is moved closer to the lifetime requirement (less design margin), then a lower cost is incurred but a greater reliability risk presents itself. Thus, moving the onset of wearout closer to the lifetime expected by the customer increases the ability to enhance the performance of all products, is riskier, and is strongly dependent on the accuracy of reliability wearout models. Thus, one must trade off (balance) the high design margin versus cost. Several prerequisite questions are (1) why do we need this design margin and (2) if I

**FIGURE 12** Bathtub curve depicting impact of short versus long time duration between product lifetime requirement specifications and wearout.

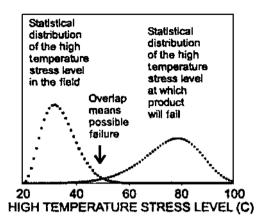

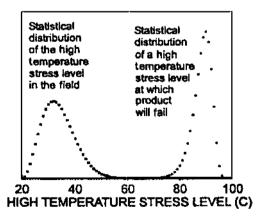

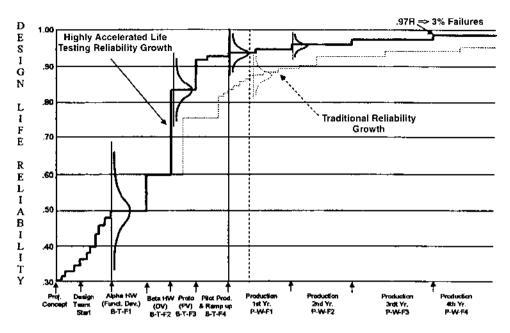

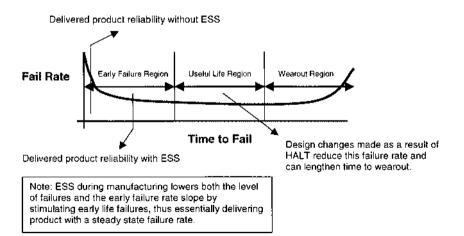

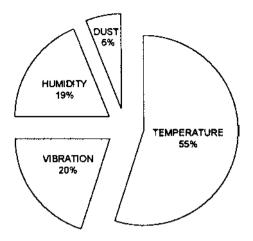

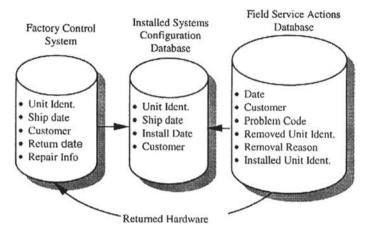

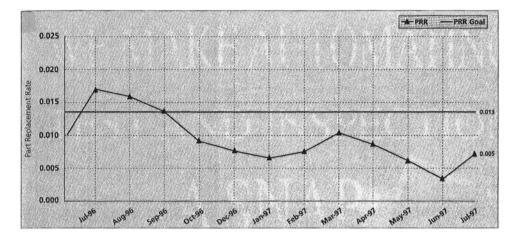

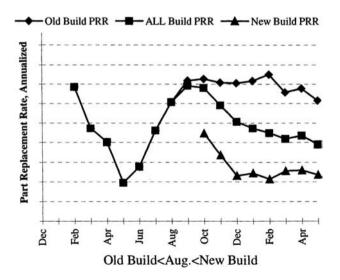

didn't need to design my product with a larger margin, could I get my product to market faster?