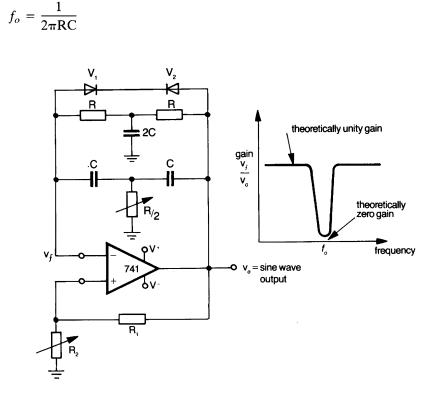

# Brian Moore and John Donaghy

# OPERATIONAL AMPLIFIER CIRCUITS

Brian Moore John Donaghy

William Heinemann Ltd 10 Upper Grosvenor Street, London W1X 9PA

#### LONDON MELBOURNE JOHANNESBURG AUCKLAND

First published by Pitman Publishing Pty Ltd 1986 First published in Great Britain by William Heinemann Ltd 1987

© Brian Moore and John Donaghy 1986

#### British Library Cataloguing in Publication Data Moore, Brian

Operational amplifier circuits.

1. Operational amplifiers 2. Integrated circuits 1. Title II. Donaghy, John 621.381'735 TK7871.58.06

ISBN 0 434 91263 8

Printed in Great Britain by Thomson Litho Ltd, East Kilbride, Scotland For Angela and Judy For TK This page intentionally left blank

# CONTENTS

|                                                     | PREFACE                                                                       |    |

|-----------------------------------------------------|-------------------------------------------------------------------------------|----|

| Chapter 1<br>INVERTING AND NON-INVERTING AMPLIFIERS |                                                                               |    |

| 1.1                                                 | Characteristics of an ideal operational amplifier                             | 1  |

| 1.2                                                 | Definitions                                                                   | 2  |

| 1.3                                                 | Circuit symbols for differential operational amplifiers                       | 4  |

| 1.4                                                 | Basic practical operational amplifier configurations: the inverting amplifier | 5  |

| 1.5                                                 | Review of ideal inverting operational amplifier characteristics               | 6  |

| 1.6                                                 | Ideal non-inverting amplifier                                                 | 7  |

| 1.7                                                 | Summary of some practical operational amplifier parameters                    | 11 |

| 1.8                                                 | Differential amplifier circuits using operational amplifiers                  | 11 |

| 1.9                                                 | Summing inverter                                                              | 12 |

| 1.10                                                | The real operational amplifier (introduction)                                 | 14 |

| 1.11                                                | Additional operational amplifier configurations                               | 14 |

| 1.12                                                | Worked examples on multi-input configurations                                 | 16 |

| 1.13                                                | Practical operational amplifier packages                                      | 20 |

| 1.14                                                | Important review points                                                       | 21 |

| 1.15                                                | Superposition theorem                                                         | 26 |

| 1.16                                                | Nodal analysis                                                                | 28 |

| 1.17                                                | Additional examples                                                           | 31 |

## Chapter 2 FREQUENCY RESPONSE, SLEW RATE AND BAND WIDTH

| 2.1 | Frequency response of the operational amplifier (introduction) | 33 |

|-----|----------------------------------------------------------------|----|

| 2.2 | Operational amplifier: input signal variations (introduction)  | 35 |

| 2.3  | Bode approximations (introduction)                             | 36 |

|------|----------------------------------------------------------------|----|

| 2.4  | Bode approximation: multistage amplifier                       | 38 |

| 2.5  | Rise time                                                      | 38 |

| 2.6  | Small signal bandwidth                                         | 39 |

| 2.7  | Open loop/closed loop relationship for non-inverting amplifier |    |

|      | circuits                                                       | 40 |

| 2.8  | Slew rate                                                      | 42 |

| 2.9  | Slew rate limiting of sine waves                               | 43 |

| 2.10 | Full power bandwidth (large signal bandwidth)                  | 44 |

| 2.11 | Slew rate limiting of square wave input                        | 45 |

| 2.12 | Slew rate limiting of triangular wave input                    | 45 |

| 2.13 | Worked examples                                                | 46 |

| 2.14 | Important review points                                        | 47 |

| 2.15 | Problems for readers                                           | 49 |

## Chapter 3 WAVEFORM GENERATORS

| 3.1  | Introduction                                                      | 51 |

|------|-------------------------------------------------------------------|----|

| 3.2  | Square wave generator                                             | 51 |

| 3.3  | Basic principles of a bistable npn transistor multivibrator       | 51 |

| 3.4  | Operational amplifier as a free-running symmetrical multivibrator | 53 |

| 3.5  | Ramp-generator theory                                             | 58 |

| 3.6  | Basic triangular wave generator circuit                           | 59 |

| 3.7  | Triangular wave generator circuit                                 | 59 |

| 3.8  | Sawtooth wave generator                                           | 61 |

| 3.9  | Introduction to sine wave generators (oscillators)                | 62 |

| 3.10 | Oscillators                                                       | 63 |

| 3.11 | Wien bridge oscillator                                            | 65 |

| 3.12 | Additional worked examples                                        | 65 |

| 3.13 | Important review points                                           | 71 |

| 3.14 | Problems for readers                                              | 73 |

## Chapter 4 POWER AMPLIFIERS AND POWER SUPPLIES

| 4.1  | Amplifier classification (introduction)                              | 76 |

|------|----------------------------------------------------------------------|----|

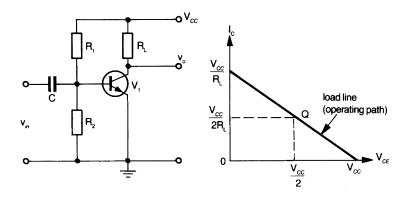

| 4.2  | Ideal Class A direct-coupled stage                                   | 76 |

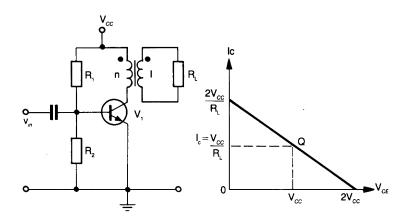

| 4.3  | Ideal Class A transformer-coupled output stage                       | 78 |

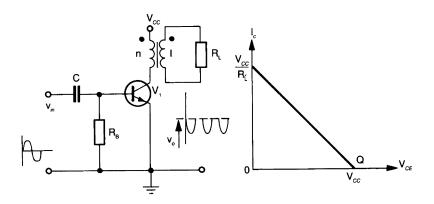

| 4.4  | Ideal Class B transformer-coupled output stage                       | 79 |

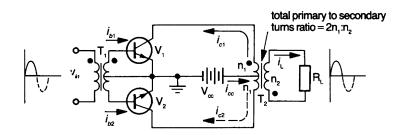

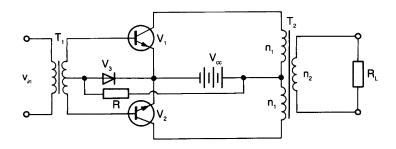

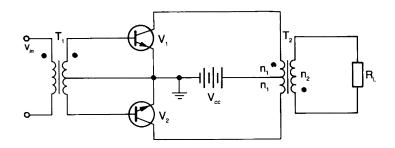

| 4.5  | Push-pull Class B power amplifier                                    | 79 |

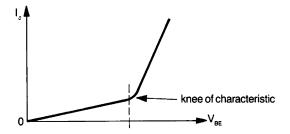

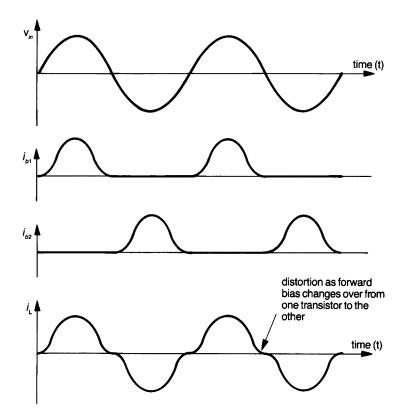

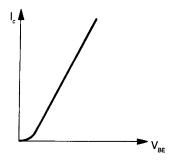

| 4.6  | Crossover distortion                                                 | 81 |

| 4.7  | Transistor power relationships for ideal push-pull amplifier circuit | 84 |

| 4.8  | Disadvantages of a transformer as a phase splitter                   | 84 |

| 4.9  | Complementary symmetry amplifier                                     | 84 |

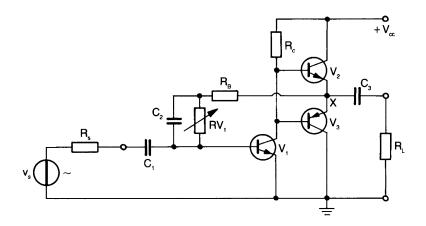

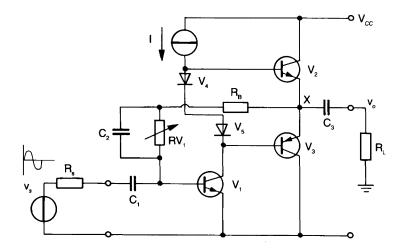

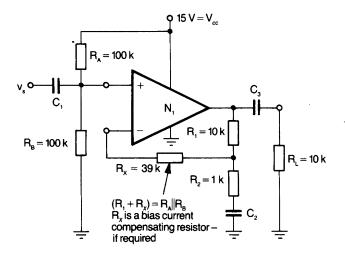

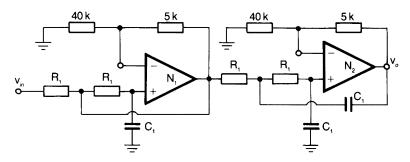

| 4.10 | Development of a power amplifier using an operational amplifier      | 85 |

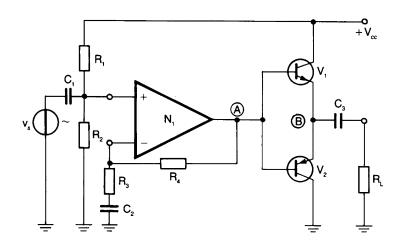

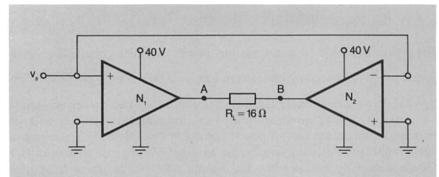

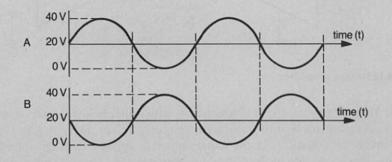

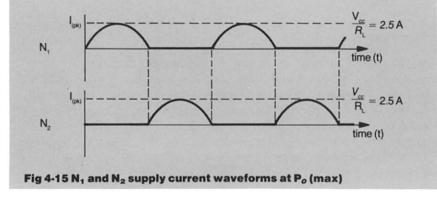

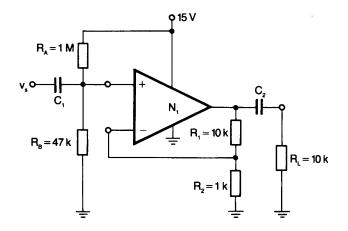

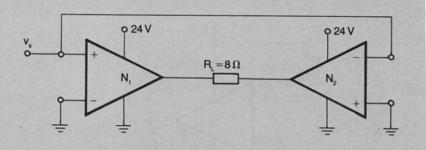

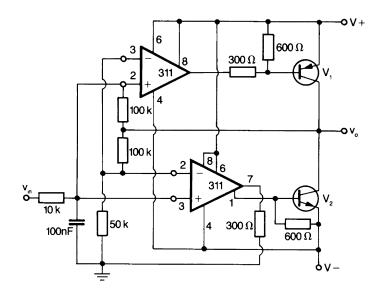

| 4.11 | Bridge amplifiers                                                    | 87 |

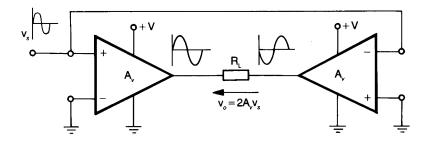

| 4.12 | Integrated circuit power amplifiers                                  | 90 |

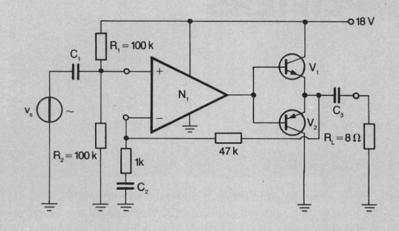

| 4.13 | Discrete power output stage                                  | 91  |

|------|--------------------------------------------------------------|-----|

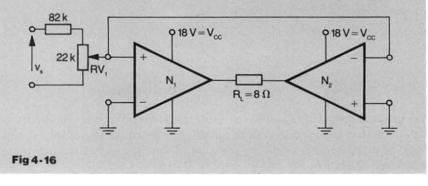

| 4.14 | Bridge amplifier circuit incorporating IC power amplifiers   | 92  |

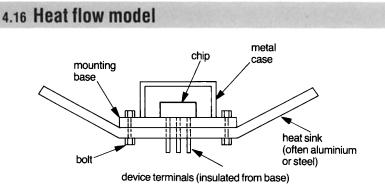

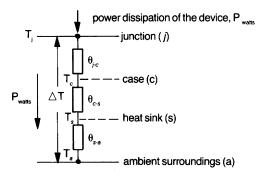

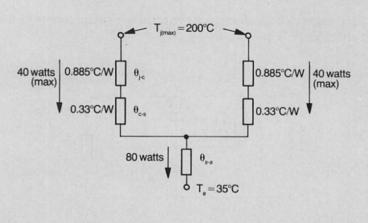

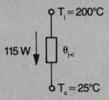

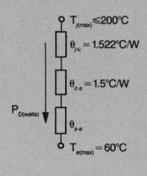

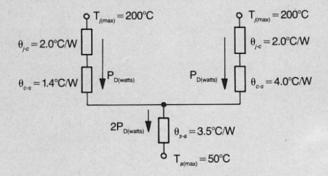

| 4.15 | Basic heat sink theory                                       | 93  |

| 4.16 | Heat flow model                                              | 94  |

| 4.17 | Introduction to regulators                                   | 96  |

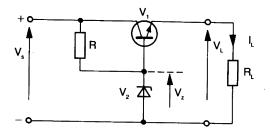

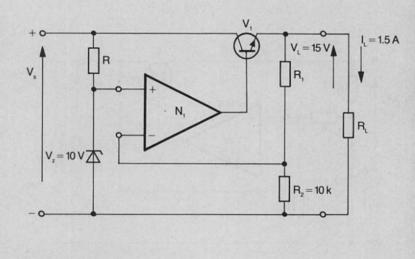

| 4.18 | Basic discrete series regulator circuit                      | 96  |

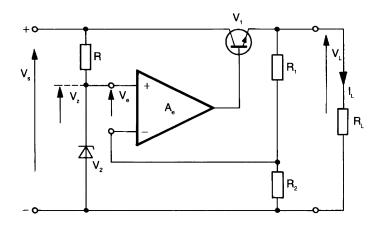

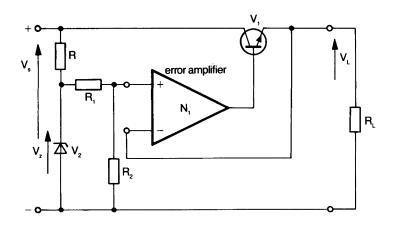

| 4.19 | Basic regulator with increased loop gain                     | 97  |

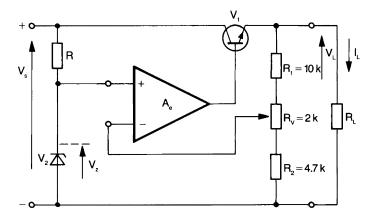

| 4.20 | Regulators producing output voltages lower than the internal |     |

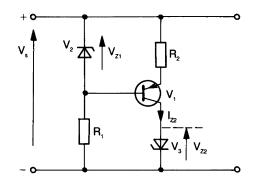

|      | reference element                                            | 99  |

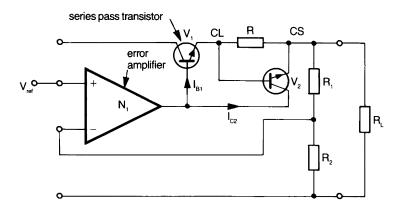

| 4.21 | Pre-regulation                                               | 100 |

| 4.22 | Current limiting circuit                                     | 102 |

| 4.23 | Integrated circuit regulators                                | 102 |

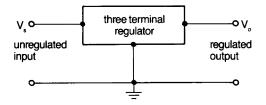

| 4.24 | Three terminal regulators                                    | 103 |

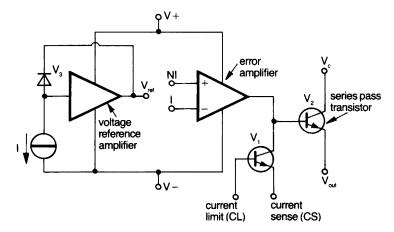

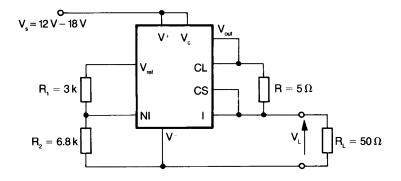

| 4.25 | Integrated circuit series voltage regulator                  | 103 |

| 4.26 | Important review points                                      | 105 |

| 4.27 | Problems for readers                                         | 108 |

## Chapter 5 SELECTED APPLICATIONS OF OPERATIONAL AMPLIFIERS

| 5.1   | Introduction                                              | 110 |

|-------|-----------------------------------------------------------|-----|

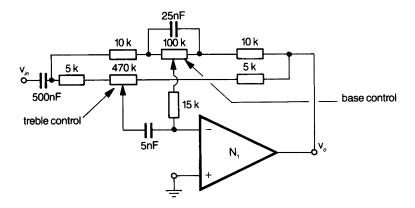

| 5.2   | Audio circuits                                            | 111 |

| 5.3   | Precision rectifiers                                      | 111 |

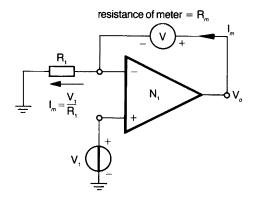

| 5.4   | High impedance DC voltmeter                               | 112 |

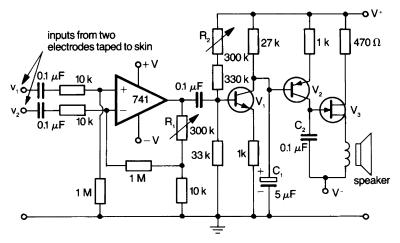

| 5.5   | Application in medical electronic monitoring systems      | 113 |

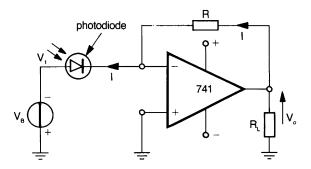

| 5.6   | Measurement of incident radiation using a photodiode      | 114 |

| 5.7   | Full wave ideal rectifier                                 | 115 |

| 5.8   | Peak detector                                             | 116 |

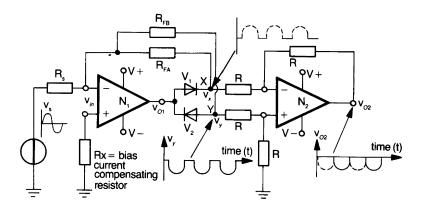

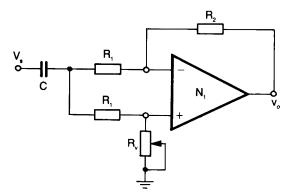

| 5.9   | Variable gain AC amplifier                                | 117 |

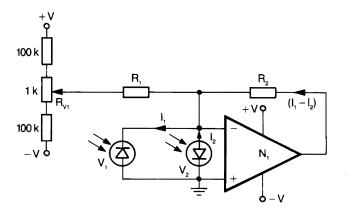

| 5.10  | Differential light intensity circuit                      | 118 |

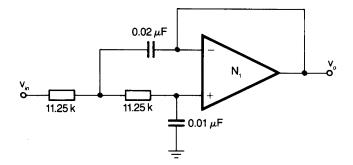

| 5.11  | Filter applications                                       | 119 |

| 5.12  | Linear read-out amplifier for resistive bridge circuit    | 120 |

| 5.13  | Miscellaneous circuit functions of operational amplifiers | 121 |

| 5.14  | Additional worked examples                                | 124 |

| INDEX |                                                           | 133 |

## PREFACE

This handbook provides a single source of information covering the basic principles of operational amplifier circuits. It will interest both the new and the experienced user of operational amplifiers.

We assume that readers possess a basic knowledge of simple electrical networks and of how transistors operate, but that they have no particular knowledge of operational amplifiers.

In some cases, circuit diagrams and symbol allocations are slightly unconventional. This is a deliberate attempt to simplify the information for the reader. In order to make some circuit diagrams clearer, supply connections have not always been shown.

Acknowledgment is made to Hans Heuer for his constructive critical comments.

Brian Moore John Donaghy September 1985

# INTRODUCTION

The initial concept of the operational amplifier comes from the field of analogue computers. The term *operational amplifier* now applies to a very high gain, differential input, direct coupled amplifier whose operating characteristics are determined by external feedback elements. By altering the nature of the feedback elements, different analogue operations can be achieved. The important point is that the overall circuit characteristics are, for the majority of practical purposes, determined only by these feedback elements.

Widespread use of integrated circuit operational amplifiers did not really commence until the 1960s. However, within a few years, they have become a standard design tool for applications far beyond the original scope of analogue computer circuits. This page intentionally left blank

## Chapter 1 INVERTING AND NON-INVERTING AMPLIFIERS

## 1.1 Characteristics of an ideal operational amplifier

The best approach to understanding the ideal operational amplifier is to consider the terminal characteristics of the amplifier in 'black box' form. The operational amplifier will be treated in this sense and, in general, what is inside the box will be disregarded.

It is convenient to assume that the amplifier has certain ideal characteristics. The effects of departures from the ideal exhibited by real operational amplifiers may then be expressed in terms of the errors to which they give rise. The ideal amplifier is assumed to have the following characteristics:

- **a** The differential voltage gain is infinite  $(A_{V0} = \infty)$ . This will, in general, make the performance entirely dependent on input and feedback networks.

- **b** The input resistance is infinite  $(r_{in} = \infty)$ . This will ensure that no current flows into the amplifier input terminals and the source network is not loaded.

- **c** The output resistance is zero  $(r_o = 0)$ . Ensures that the amplifier performance is not affected by the load.

- **d** The bandwidth is infinite  $(BW = \infty)$ . This is a bandwidth extending from zero to infinity, ensuring a response to DC signals and no phase change with frequency.

- **e** When the input signal is zero the output signal will also be zero, ie  $V_o = 0$  if  $V_{in} = 0$ .

## **Operational Amplifier Circuits**

Since the input impedance is infinite, there will be no current flowing into the amplifier input terminals. In addition, when negative feedback is employed, the differential input voltage reduces to zero. Proof of this is shown in Section 1.14A. These two statements are used as starting points for the analysis of negative feedback type amplifier circuits and will be explored in detail later on.

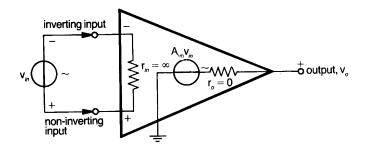

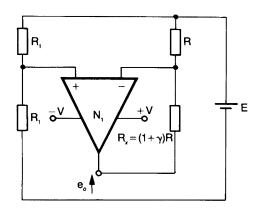

The equivalent circuit for an ideal operational amplifier (with  $r_{in} = \infty$  and  $r_o = 0$ ) is shown in Fig 1.1.

#### Fig. 1-1 Equivalent circuit for ideal operational amplifier

The amplifier responds only to the difference in voltage between the two input terminals. A positive-going signal at the inverting (-) input produces a negative-going signal component at the output, whereas the same signal at the non-inverting (+) input produces a positive-going output signal component. Essentially, the output signal is the combined response to such input signals. With an input voltage  $V_{in}$  the output voltage  $V_0$  will be  $A_{V0} V_{in}$ , where  $A_{V0}$  is the differential gain of the amplifier.

## **1.2 Definitions**

The following definitions should be referred to when appropriate.

## Differential amplifier

A differential amplifier is an amplifier designed to amplify the difference between two signals. Ideally:

$V_o = (+A_d)V_1 + (-A_d)V_2$  hence  $V_o = A_d(V_1 - V_2)$  where  $A_d =$  differential gain.

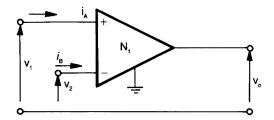

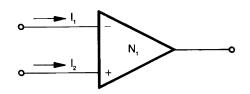

#### Fig. 1-2 Differential input, single ended output

## • Differential input signal (V<sub>d</sub>)

Referring to Fig 1.2,  $|V_d = V_1 - V_2|$  or  $|V_d = (V^+) - (V^-)|$  where  $(V^+)$  is the signal at the non-inverting input, relative to ground potential, and  $(V^-)$  is that at the inverting input.

## • Common-mode input signal (V<sub>c</sub>)

$V_c = \frac{1}{2}(V_1 + V_2)$ , the average of the two input signals.

## Differential gain

This is the ratio:  $\frac{\text{output voltage}}{\text{differential input voltage}}$ when the common-mode input signal is zero.

Hence,  $A_d = \frac{V_o}{V_d}$  when  $V_c = 0$ , ie when  $(V_1 = -V_2)$

## • Common-mode gain (A<sub>c</sub>)

$$A_c = \frac{V_o}{V}$$

when  $V_d = 0$ , ie when  $(V_1 = V_2)$

## • Common-mode rejection ratio (CMRR)

A real differential amplifier responds not only to the difference between the input signals, but also to their average. The CMRR indicates how much better the differential amplifier is at amplifying differential signals than common-mode signals. That is, the CMRR is a figure of merit for the differential amplifier. The CMRR should be high, so that:

$V_o = A_d V_d + A_c V_c \approx A_d V_d$  for many practical applications.

**Operational Amplifier Circuits**

$$CMRR = \left| \frac{A_d}{A_c} \right|$$

$$CMRR (dB) = 20 \log_{10} \left| \frac{A_d}{A_c} \right|$$

$$= A_d(dB) - A_c(dB)$$

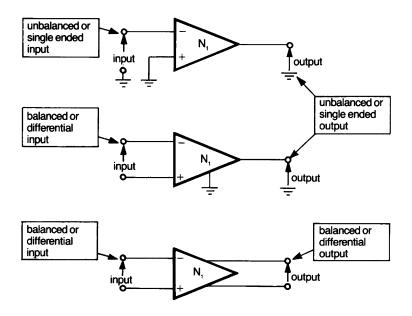

## 1.3 Circuit symbols for differential operational amplifiers

There are three main varieties of single-ended and differential connections, as shown in Fig 1.3.

#### Fig. 1-3 Circuit symbols for operational amplifiers

## 1.4 Basic practical operational amplifier configurations: the inverting amplifier

Operational amplifiers can be connected in two basic amplifying configurations:

- Inverting

- Non-inverting

The circuit of Fig 1.4 is one of the most widely used operational amplifier circuits. It is an amplifier whose closed-loop gain (gain of amplifier with feedback) from  $V_{in}$  to  $V_o$  is set by  $R_1$  and  $R_2$ . It can amplify AC or DC signals. To understand how this circuit operates under ideal conditions, we use the two assumptions referred to in Section 1.1:

- **a** The voltage  $V_d$  between (+) and (-) inputs tends to 0, as  $A_d \rightarrow \infty$  (from definition 1.2(a)).

- **b** The current drawn by both the (+) and the (-) input terminals is zero.

#### Fig 1-4 Ideal inverting operational amplifier configuration

It is worth pointing out that this circuit only functions properly when the junction of the two resistors  $R_1$  and  $R_2$  goes to the (-) or inverting input of the amplifier. This provides negative feedback, and only negative feedback gives a 'stable amplifier'.

## 1.5 Review of ideal inverting operational amplifier characteristics

- **a** Since the ideal operational amplifier has infinite gain, it can develop a finite output voltage,  $V_o$ , with zero differential input voltage,  $V_d$  (Fig 1.4).

- **b** The summing point is a virtual ground at the same potential as the (+) input.  $(V_d = 0, V^+ = 0, hence V^- = 0)$ .

- **c** The differential input to  $N_1$  is  $V_d = 0$ . If  $V_d$  is zero, then the full input voltage,  $V_{in}$ , must appear across  $R_2$ , because  $V^- = 0$ , making the current in  $R_2$ :

$$i_{in} = \frac{V_{in}}{R_2}$$

- **d** Since  $i_s = 0$  due to infinite input impedance, the input current  $i_{in}$  must also flow in  $R_1$  (*Kirchhoff's Current Law*), thus  $i_f = i_{in}$ .

- The voltage across  $\mathbf{R}_1$  is  $i_f \mathbf{R}_1$ , and since  $\mathbf{V}^- = 0$  this implies that  $\mathbf{V}_o = \mathbf{R}_1$

$$-i_f \mathbf{R}_1 = -i_{in} \mathbf{R}_1 = -\frac{\mathbf{R}_1}{\mathbf{R}_2} \cdot \mathbf{V}_{in}$$

The minus sign implies a 180° phase relationship with the input signal, ie inversion.

This is the characteristic voltage gain transfer function of the ideal inverting amplifier.

f The closed loop voltage gain of the amplifier

$$A_{CL} = \frac{V_o}{V_{in}} = -\frac{R_1}{R_2} \left( \text{Note the gain is strictly } \frac{R_1}{R_2} \right)$$

- **g** The load current,  $i_{\rm L}$ , flows through  $R_{\rm L}$ .

- Thus  $i_{\rm L} = -\frac{{\rm V}_o}{{\rm R}_{\rm L}}$

The operational amplifier output current,  $i_o$ , is:  $i_o = i_{in} + i_L$

**h** The input resistance seen by the input signal  $V_{in}$  is  $R_2$  since  $(V^-)$  is at zero potential.

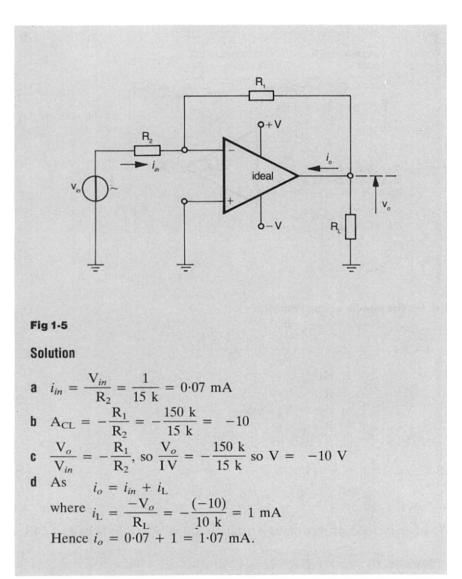

Example 1 Given that:  $R_2 = 15 \text{ k}$   $R_1 = 150 \text{ k}$   $V_{in} = 1 \text{ V}$   $R_L = 10 \text{ k}$ Refer to Fig 1.5 and determine: **a**  $i_{in}$  **b**  $A_{CL}$  **c**  $V_o$ **d**  $i_o$

## 1.6 Ideal non-inverting amplifier

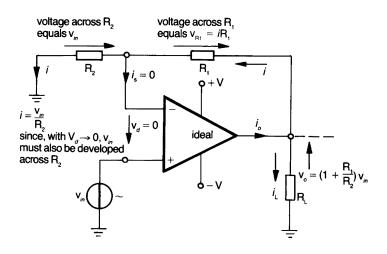

The second basic amplifying configuration of the operational amplifier is the non-inverting amplifier. Fig 1.6 shows a non-inverting amplifier circuit. The output voltage,  $V_o$ , has the same phase (or polarity, in the case of DC signals) as the input voltage.

The input resistance of the practical non-inverting amplifier is very large, often over 100 M, and depends on the actual closed loop gain. This very high input resistance, compared to the inverting circuit, is often a reason for choosing this arrangement. An analysis follows:

#### Fig. 1-6 The non-inverting amplifier

$$V^{-} = V^{+} = V_{in}, \text{ so } i = \frac{V_{in}}{R_2}$$

$$V_{R_1} = iR_1 = \frac{R_1}{R_2} \cdot V_{in}$$

$$V_o = V^{-} + V_{R_1} = V_m + V_{R_1}$$

$$\therefore \quad V_o = V_{in} + \frac{R_1}{R_2} \cdot V_{in}$$

so

$$V_o = \left\{1 + \frac{R_1}{R_2}\right\} V_{in}$$

and

$$A_{CL} = \frac{V_o}{V_{in}} = 1 + \frac{R_1}{R_2}.$$

Another method of proving this relationship is shown in Section 1.14B.

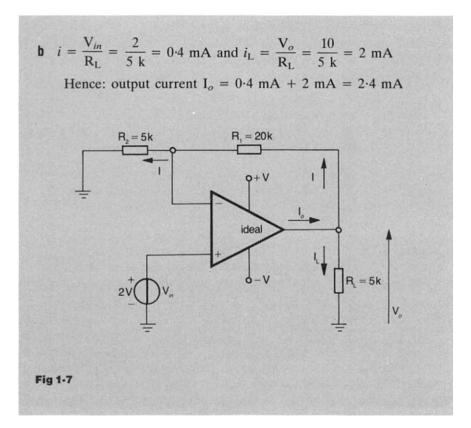

Example 2Determine, for the non-inverting amplifier shown in Fig 1.7,a the output voltageb the output current

Solution

**a** Output voltage

$$V_o = \left\{1 + \frac{R_1}{R_2}\right\} V_{in} = \left\{1 + \frac{20 \text{ k}}{5 \text{ k}}\right\} 2$$

Hence: output voltage = +10 V

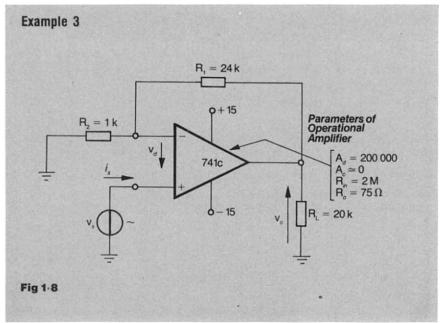

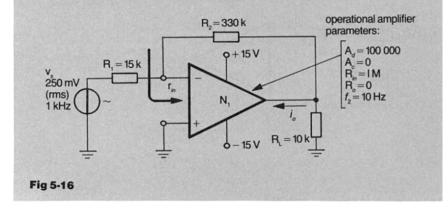

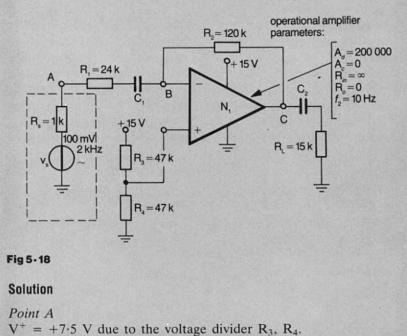

For the circuit shown in Fig 1.8, containing a real operational amplifier whose characteristics are given, determine the approximate value of the input signal current if  $v_o$  is 4 volts (rms).

## Solution

$$v_d = \frac{v_o}{A_d} = \frac{4}{200\,000}$$

volts (rms) = 20  $\mu$ V (rms)

$i_s = \frac{v_d}{R_{in}} = \frac{20 \ \mu V}{2M} = -10 \text{ pA}$  (rms)

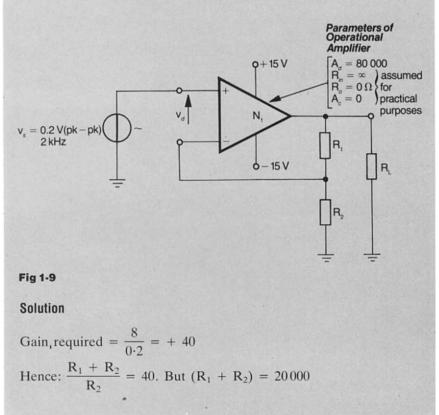

#### Example 4

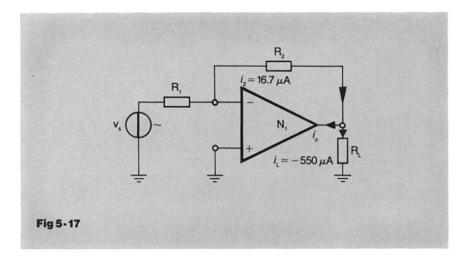

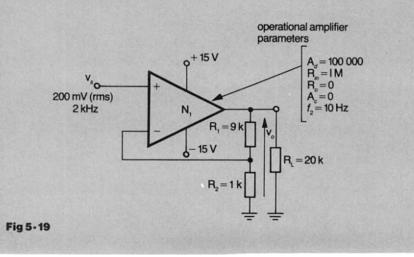

If  $v_o$  is 8 V (pk-pk) at 2 kHz for the 0.2 V input shown in Fig 1.9, determine  $R_1$ ,  $R_2$ ,  $v_d$  and the voltage across  $R_2$ ,  $v_{R_2}$ , given that the total load placed on the operational amplifier by the feedback resistors is to be 20 k.

so  $\frac{20\,000}{R_2} = 40 \text{ or } = R_2 = 500 \ \Omega$ Hence:  $R_1 = 20\,000 - 500 = 19\,500 \ \Omega$   $v_d = \frac{v_o}{A_d} = \frac{8}{80\,000} \text{ volts (pk-pk)} = 100 \ \mu\text{V (pk-pk)}$   $v_{R_2} = \text{ inverting input voltage } \Rightarrow \text{ non-inverting voltage since}$   $v_d \text{ is negligible at 100 } \mu\text{V by comparison with } v_s$ , which is 200 mV Hence:  $v_{R_2} = 0.2 \text{ V or } 200 \text{ mV (pk-pk)}$

## 1.7 Summary of some practical operational amplifier parameters

**a** The open loop voltage gain,  $A_{OL}$ , is the circuit's differential gain without feedback, ie as if the feedback path was made an open circuit. It follows then that  $A_{OL} = A_d$  and  $V_o = A_{OL}V_d$ .

$V_o$  can never exceed positive or negative saturation voltages. For a  $\pm 15$  V supply, the saturation voltages would be about  $\pm 13$  volts. Because output voltages,  $V_o$ , equals the differential input voltage,  $V_d$ , multiplied by open loop gain,  $A_{OL}$ , it can be seen that to produce saturation

$$V_d = \pm \frac{13}{200\,000} = \pm 65 \ \mu V \ (approx).$$

$V_d$  should, however, be neglected only if it is very small compared to  $V_s$ , the input signal voltage.

**b** Some typical parameters of a 741C operational amplifier are as follows:

- **i** Input resistance = 2 M

- ii Output resistance = 75 ohm

- iii CMRR = 90 dB

- iv Large signal voltage gain =  $200\,000$ .

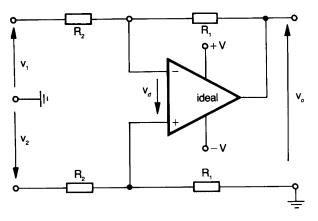

## 1.8 Differential amplifier circuits using operational amplifiers

Refer to Fig 1.10. It can be shown that:

Differential mode gain,  $V_1 \neq V_2$ :  $\frac{V_o}{V_2 - V_1} = \frac{R_1}{R_2}$ .

Note that the differential gain is defined solely by resistors  $R_1$  and  $R_2$ . Proof of this is left for the reader. (The analysis is simplified if  $R_1$  is assumed to be equal to  $nR_2$ .)

#### Fig. 1-10 Differential amplifier

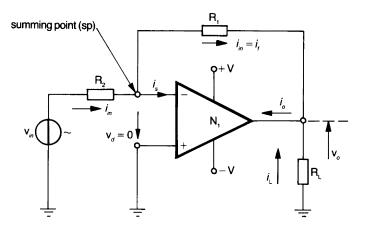

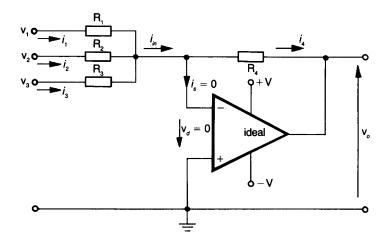

## 1.9 Summing inverter

A summing inverter circuit is used for adding signals, eg as in an audiomixing circuit. An example of a basic summing inverter circuit is shown in Fig 1.11. This circuit  $i_{in}$  is the algebraic sum of the input currents.

## Fig. 1-11 Summing inverter circuit

The (-) input is a virtual earth since (+) input is grounded and  $v_d$  is approximately zero.

so  $i_1 = \frac{v_1}{R_1}, i_2 = \frac{v_2}{R_2}, i_3 = \frac{v_3}{R_3}$

Hence:  $i_{in} = i_1 + i_2 + i_3 = i_4$ , since  $i_s$  is relatively small enough to be

neglected.

$$v_o = \nabla^- - i_4 R_4$$

=  $-i_4 R_4$  (since  $\nabla^- = 0$ )

=  $-(i_1 + i_2 + i_3) R_4$

$v_o = -\left(v_1 \frac{R_4}{R_1} + v_2 \frac{R_4}{R_2} + v_3 \frac{R_4}{R_3}\right)$

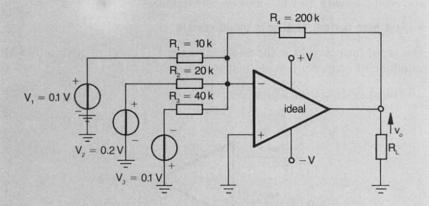

## Example 5

- Refer to Fig 1.12.

- a Determine the voltage gain applied to each input voltage.b Calculate the output voltage using Fig 1.12.

### Fig 1-12

Solution

**a i**

$$A_{CL1} = -\frac{R_4}{R_1} = -\frac{200 \text{ k}}{10 \text{ k}} = -20$$

**ii**  $A_{CL2} = -\frac{R_4}{R_2} = -\frac{200 \text{ k}}{20 \text{ k}} = -10$

**iii**  $A_{CL3} = -\frac{R_4}{R_3} = -\frac{200 \text{ k}}{40 \text{ k}} = -5$

**b**  $V_o = -\left\{V_1\frac{R_4}{R_1} + V_2\frac{R_4}{R_2} + V_3\frac{R_4}{R_3}\right\}$

$V_o = -[(0.1 \times 20) + (0.2 \times 10) + ((-0.1) \times 5)]$

$= -(2 + 2 - 0.5)$

Hence:  $V_o = -3.5 \text{ V}$

## 1.10 The real operational amplifier (introduction)

## • Input offset voltage

Ideal amplifiers produce 0 volts out for 0 volts in. However, in the practical case there may be a small DC voltage at the output even though no differential input voltage is applied.

The 'input offset voltage' may be considered as the DC input voltage which would produce the equivalent DC output voltage. The output voltage is actually caused by differences in the base-emitter junction voltages of the operational amplifier's input differential amplifier.

A related parameter to offset voltage is input offset voltage drift, ie variation in output voltage with temperature. Typical amplifiers usually possess drift levels in the range 5  $\mu$ V to 40  $\mu$ V per °C. Low drift amplifiers are available with 10 times better performance.

## · Input bias current and input offset current

The input bias current is the average of the DC currents required by the amplifier to properly bias its first stage.

I (bias) is defined as:  $I_B = \frac{I_1 + I_2}{2}$

## Fig. 1-13 Input bias current

Input offset current is the small difference in bias currents from one input to the other of the operational amplifier. For many applications, input offset current may be ignored. It is only of significance when the output DC level must be accurately related to the input DC level.

## • AC parameters

Parameter definitions have previously been mainly concerned with magnitudes of DC voltages and currents. Several important AC or frequency dependent parameters will be discussed in chapter 2.

## 1.11 Additional operational amplifier configurations

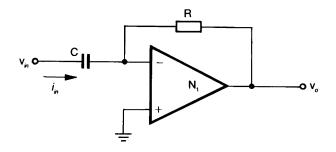

## • The integrator

If a constant current is applied to the input of the integrator it causes the

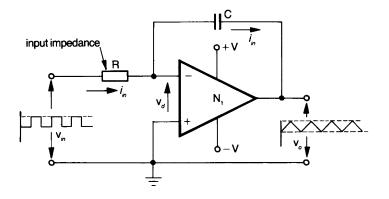

#### Fig. 1-14 Basic integrator circuit

output voltage of the circuit to decrease linearly with time. The square wave input shown causes the direction of the input current to change sense regularly, resulting in an output voltage which increases, then decreases, linearly with time, ie a triangular waveform.

The output voltage is proportioned to the integral of the input voltage.

$$\mathbf{v}_o = -\frac{1}{\mathrm{CR}} \int \mathbf{v}_{in} \,\mathrm{dt}.$$

See Proof in Section 1.14C.

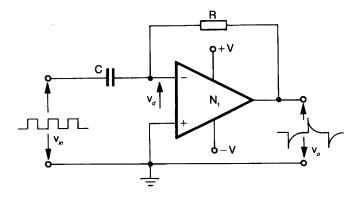

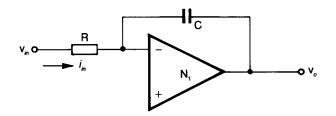

• The differentiator

#### Fig. 1-15 Basic differentiator circuit

The input current is proportional to the rate of change of input voltage with respect to time.

$$\mathbf{v}_o = -\mathbf{R}\mathbf{C}\left(\frac{\mathbf{d}}{\mathbf{d}\mathbf{t}}\cdot\mathbf{v}_{in}\right).$$

See Proof in Section 1.14D.

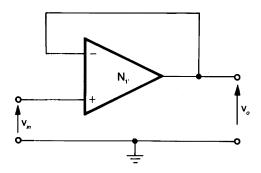

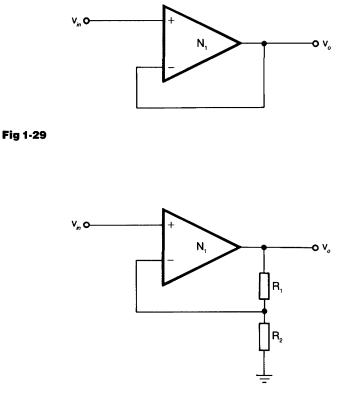

• The voltage follower

## Fig. 1-16 Basic voltage follower circuit

Ideally: Gain = 1 Input Resistance =  $\infty$  $v_o = v_{in}$ See Proof in Section 1.14E.

## 1.12 Worked examples on multi-input configurations

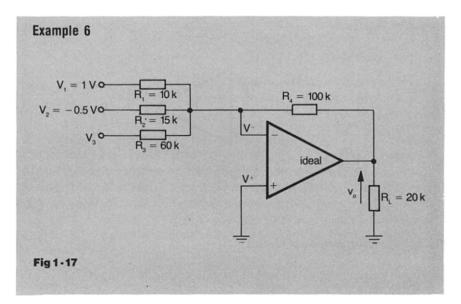

Determine the input,  $V_3$ , if the output voltage,  $V_o$ , is zero for the circuit diagram shown in Fig 1.17.

## Solution

Current in

$$R_4 = \left(\frac{V_1 - V^-}{R_1}\right) + \left(\frac{V_2 - V^-}{R_2}\right) + \left(\frac{V_3 - V^-}{R_3}\right)$$

If  $V_o$  is zero, then current in  $R_4$  must also be zero, since  $V^- = V^+ = 0$

Hence:  $\left(\frac{1 - 0}{10 \text{ k}}\right) + \left(\frac{-0.5 - 0}{15 \text{ k}}\right) + \left(\frac{V_3 - 0}{60 \text{ k}}\right) = 0$

$= \frac{1}{10 \text{ k}} - \frac{0.5}{15 \text{ k}} + \frac{V_3}{60 \text{ k}} = 0$

Multiplying throughout by 60 k:  $6 - 2 + V_3 = 0$

Hence:  $V_3 = -4 \text{ V}$

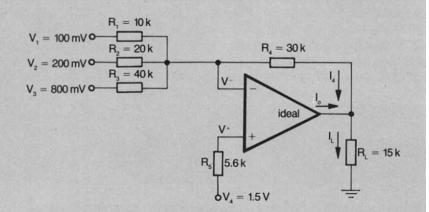

**Example 7** Determine  $I_4$ ,  $I_0$  and  $I_L$  for the circuit shown in Fig 1.18.

#### Fig 1 - 18

Solution

**a**

$$I_4 = \text{sum of currents in } R_1, R_2 \text{ and } R_3.$$

$$= \left(\frac{V_1 - V^-}{R_1}\right) + \left(\frac{V_2 - V^-}{R_2}\right) + \left(\frac{V_3 - V^-}{R_3}\right)$$

But  $V^- = V^+ = V_4$  since negligible current will flow in R

5

so

$$I_4 = \left(\frac{0 \cdot 1 - 1 \cdot 5}{10 \text{ k}}\right) + \left(\frac{0 \cdot 2 - 1 \cdot 5}{20 \text{ k}}\right) + \left(\frac{0 \cdot 8 - 1 \cdot 5}{40 \text{ k}}\right)$$

$= \left[\left(\frac{-1 \cdot 4}{10 \text{ k}}\right) + \left(\frac{-1 \cdot 3}{20 \text{ k}}\right) + \left(\frac{-0 \cdot 7}{40 \text{ k}}\right)\right]$

$= (-0 \cdot 14 - 0 \cdot 065 - 0 \cdot 0175)$

Hence:  $I_4 = -0 \cdot 22 \text{ mA}$

**b**  $V_o = V^- - I_4 R_4 = 1 \cdot 5 - (-0 \cdot 2225 \times 30 \text{ k})$

$= 1 \cdot 5 + 6 \cdot 675 = 8 \cdot 175 \text{ V}.$

$I_L = \frac{V_o}{R_L} = \frac{8 \cdot 175}{15 \text{ k}}$

Hence:  $I_L = 0 \cdot 545 \text{ mA}$

**c**  $I_o = I_L - I_4 = 0 \cdot 545 \text{ mA} - (-0 \cdot 2225 \text{ mA})$

Hence:  $I_o = 0 \cdot 77 \text{ mA}$ .

Check

$$\begin{array}{c|c} R_{4} = 30 \text{ k} & R_{L} = 15 \text{ k} \\ \hline \bullet & \bullet & I_{4} \\ -0.2225 \text{ mA} & \bullet & I_{L} \\ I_{0} = 0.7675 \text{ mA} \end{array}$$

## Fig 1-19

From Fig 1.19:  $V^- = (I_L R_L) + (I_4 R_4)$ =  $(0.545 \text{ mA} \times 15 \text{ k}) + (-0.2225 \text{ mA} \times 30 \text{ k})$ = 8.175 - 6.675. Hence:  $V^- = 1.5$  volts, which is correct.

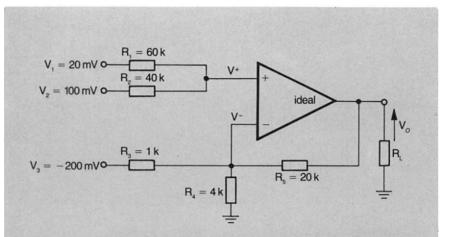

# **Example 8** Calculate $V_o$ , the output voltage of the circuit shown in Fig 1.20.

See Section 1.15 (Superposition theorem).

## Solution

Using superposition theorem:  $V^+ = \frac{V_1 \cdot R_2}{R_1 + R_2} + \frac{V_2 \cdot R_1}{R_1 + R_2}$ , ie the sum of the inputs from each source considered separately,

Fig 1-20

$$= \frac{(0.02 \times 40 \text{ k})}{100 \text{ k}} + \frac{(0.1 \times 60 \text{ k})}{100 \text{ k}}$$

= 0.008 + 0.06

V<sup>+</sup> = 0.068 volt

Hence: V<sup>-</sup> = 0.068 volt

$\left(\frac{V_3 - V^-}{R_3}\right) + \left(\frac{0 - V^-}{R_4}\right) + \left(\frac{V_o - V^-}{R_5}\right) = 0$

=  $\left(\frac{-0.2 - 0.068}{1 \text{ k}}\right) + \left(\frac{0 - 0.068}{4 \text{ k}}\right) + \left(\frac{V_o - 0.068}{20 \text{ k}}\right) = 0$

Multiplying by 1000 gives:

$-0.268 - 0.017 + \frac{V_o}{20} - 0.0034 = 0$

$\frac{V_o}{20} = 0.0034 + 0.017 + 0.268 = 0.2884.$

Hence:  $V_o = 20 \times 0.2884 = 5.768 V$

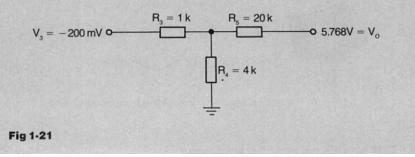

Check

From Fig 1.21:

$$V^- \cdot \left(\frac{1}{R_3} + \frac{1}{R_4} + \frac{1}{R_5}\right) = \left(\frac{V_3}{R_3} + \frac{0}{R_4} + \frac{V_o}{R_5}\right)$$

so  $V^- \cdot \left(\frac{1}{1\ k} + \frac{1}{4\ k} + \frac{1}{20\ k}\right) = \left(\frac{-0.2}{1\ k} + \frac{5.768}{20\ k}\right)$ .

Multiplying by 1000 gives:  $V^- \cdot (1 + 0.25 + 0.05) = -0.2 + 0.2884$

$V^- = \frac{0.0884}{1.3}$ .

Hence:  $V^- = 0.068\ V$  which is correct.

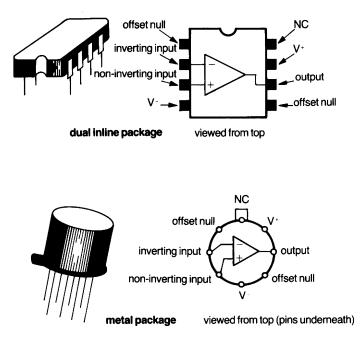

## 1.13 Practical operational amplifier packages

The LM741 series is a typical general purpose operational amplifier. Details of pin connections for two of its typical packages are shown in Fig 1.22. The exact meaning of some terminal connection applications will be explained in chapter 3. Fig 1.23 indicates the pin connections for a practical inverting amplifier circuit based on the LM741C Operational Amplifier.

Fig. 1-22 IC operational amplifier packages

#### Fig. 1-23 Connections for practical inverting amplifier circuit

The user of operational amplifiers does not require a detailed knowledge of their internal circuitry, but is mainly concerned with the external pin connections.

There is a degree of standardisation in the pin connections with some general purpose operational amplifiers.

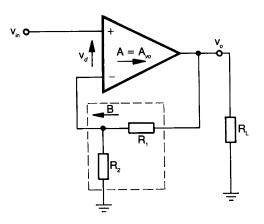

## A Proof of conditions for $v_d$ to be effectively zero in negative feedback non-inverting amplifier circuits

From Section 1.1.

With an ideal operational amplifier and negative feedback  $v_d$  is zero, whereas with a practical operational amplifier and negative feedback, it is normally very close to zero.

Refer to Fig 1.24. Assume the operational amplifier has finite  $A_{\nu o}$  and  $R_{in}$ , and zero  $R_o$ .

Note that the feedback is negative because the signal at the inverting input substracts from that at non-inverting input, as far as its effect on the output is concerned, and is derived from  $v_o$ , which is in phase with  $v_{in}$ .

$v_d = v_{in} - Bv_o$  where B is the transfer function of the feedback network.

That is,

$$v_d = v_{in} - \left(\frac{R_2}{R_1 + R_2}\right)v_o$$

.

But  $v_o = A_{Vo}v_d$ .

Hence:  $v_d = v_{in} - \left(\frac{R_2}{R_1 + R_2}\right)A_{Vo}v_d$ .

$$v_{d} + \left(\frac{R_{2}}{R_{1} + R_{2}}\right)A_{Vo}v_{d} = v_{in}$$

$$v_{d}\left(1 + \frac{R_{2}}{R_{1} + R_{2}}\right)A_{Vo} = v_{in}$$

Hence:  $v_{d} = \frac{v_{in}}{1 + \left(\frac{R_{2}}{R_{1} + R_{2}}\right)A_{Vo}}$

So  $v_{d} \rightarrow 0$  as  $\left(\frac{R_{2}}{R_{1} + R_{2}}\right)A_{Vo} \rightarrow \infty$ .

But  $\frac{R_{1} + R_{2}}{R_{2}}$  = closed loop gain. So we need:  $\frac{\text{open loop gain}}{\text{closed loop gain}} \rightarrow \infty$ , that

is, open gain  $\gg$  closed loop gain.

The small size of  $v_{d}$  is of no significance unless it can be shown that it

The small size of  $v_d$  is of no significance unless it can be shown that it may be neglected by comparison with related signal levels, mainly the input,  $v_{in}$  or  $v_s$  (Fig 1.25).

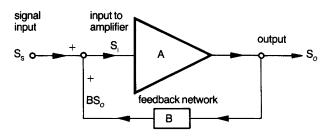

Fig. 1-25 Block diagram of feedback system

To make a more general analysis 'S' is used to represent a signal level which may either be a voltage, or a current level. 'A' is the amplifier gain and 'B' the 'gain' of the feedback network.  $S_i = S_s + BS_o$

Hence

$$S_{o} = AS_{i}$$

$$S_{i} = S_{s} + ABS_{i}$$

$$S_{i} - ABS_{i} = S_{s}$$

$$S_{i}(1 - AB) = S_{s}$$

$$S_{i} = \frac{S_{s}}{(1 - AB)}$$

Hence:  $S_i \rightarrow 0$  as  $-AB \rightarrow \infty$

Thus loop gain, AB, needs to have an associated phase shift of  $180^\circ$ , (ie negative feedback) and be very large in comparison with unity, for S<sub>i</sub> to approach zero. Under such circumstances, S<sub>i</sub> becomes very much smaller than S<sub>s</sub> and may be neglected in comparison with it.

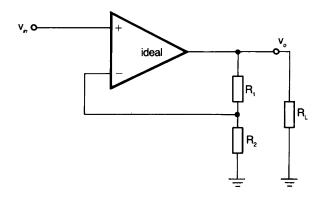

## **B** Proof of A<sub>CL</sub> for non-inverting amplifier (alternate method)

From Section 1.6. Refer to Fig 1.26.

#### Fig 1 - 26

$V^{-} = V^{+} = v_{in}$   $V^{-} = v_o \left(\frac{R_2}{R_1 + R_2}\right)$  by potential divider formula (amplifier input current being zero)  $v_{in} = v_o \left(\frac{R_2}{R_1 + R_2}\right)$

so Hence:

$$\mathbf{v}_{o} = \left(\frac{\mathbf{R}_{1} + \mathbf{R}_{2}}{\mathbf{R}_{2}}\right) \mathbf{v}_{in}$$

$$\mathbf{v}_{o} = \left(1 + \frac{\mathbf{R}_{1}}{\mathbf{R}_{2}}\right) \mathbf{v}_{in}$$

so,

and  $A_{CL} = \left(1 + \frac{R_1}{R_2}\right)$ , where  $A_{CL} = \frac{v_o}{v_{in}}$

C Proof of the integrator relationship:  $v_o = -\frac{1}{CR} \int v_{in} dt$

From Section 1.11. Refer to Fig 1.27.

#### Fig 1 - 27

The inverting input of the operational amplifier will remain close to ground potential due to the high open loop gain of the amplifier.

The voltage across the capacitor,  $v_c$ , is given by:

$v_{c} = \frac{1}{C}.$  Q where Q is the instantaneous value of the charge on the capacitor Now Q =  $\int_{t_{1}}^{t_{2}} i \, dt$ so  $v_{c} = \frac{1}{C} \int_{t_{1}}^{t_{2}} i \, dt$ Now  $i = \frac{v_{in}}{R}$  if inverting input is near ground potential so  $v_{c} = \frac{1}{CR} \int_{t_{1}}^{t_{2}} v_{in} \, dt$ now  $v_{o} = 0 - V_{c}$ so  $v_{o} = -\frac{1}{CR} \int_{t_{1}}^{t_{2}} v_{in} \, dt$ That is the output voltage of the circuit is the integral of  $v_{c}$  over the

That is, the output voltage of the circuit is the integral of  $v_{in}$  over the time interval  $t_1$  to  $t_2$  seconds, with a constant of proportionality equal to  $-\frac{1}{CR}$ .

## • The differentiator relationship

D Proof

$$\mathbf{v}_o = -\mathbf{RC}\left(\frac{\mathbf{d}}{\mathbf{dt}} \cdot \mathbf{v}_{in}\right)$$

Refer to Section 1.11. Refer to Fig 1.28.

#### Fig 1-28

$$Q = Cv_{in}, \text{ so } \Delta Q = C\Delta v_{in},$$

ie

$$\int i_{in} dt = Cdv_{in}$$

$$dv_{in}$$

or

$$i_{in} = C \frac{dv_{in}}{dt}$$

and since  $i_{in}$  also equals current through R and V<sup>-</sup> will stay close to ground potential due to the high value of  $A_{Vo}$ , it follows that:  $v_o = -i_{in}R$  since V<sup>-</sup> is approximately zero.

Hence:

$$-\frac{\mathbf{v}_o}{\mathbf{R}} = i_{in} = \mathbf{C}\left(\frac{\mathbf{d}}{\mathbf{dt}} \cdot \mathbf{v}_{in}\right)$$

so

$\mathbf{v}_o = -\mathbf{RC}\left(\frac{\mathbf{d}}{\mathbf{dt}}\cdot\mathbf{v}_{in}\right) \,.$

That is,  $v_o$  is proportional to the time derivative of  $v_{in}$  with a proportionality constant equal to -RC.

## E Proof that the voltage follower circuit has a gain of unity

From Section 1.11. Refer to Fig 1.29.

$V^- = V^+ = v_{in}$ But  $V^-$  also =  $v_o$ , hence  $v_o = v_{in}$ .

An alternative method would be as follows (from Fig 1.30):

Considering the non-inverting amplifier circuit, the voltage gain

$$\frac{\mathbf{v}_o}{\mathbf{v}_{in}} = 1 + \frac{\mathbf{R}_1}{\mathbf{R}_2}$$

In the voltage follower circuit  $R_1 = 0$  and  $R_2 = \infty$ .

Hence: gain = 1,

ie the voltage follower circuit is a special case of the non-inverting amplifier circuit.

## 1.15 Superposition theorem

- **a** In any network containing more than one source (voltage and/or current) the current in, or the potential difference across any branch can be found by considering the effect of each source separately at the appropriate point, and adding the effects.

- **b** Sources of emf not under consideration are replaced by short circuits, while current sources are replaced by open circuits; any internal resistances being left in circuit.

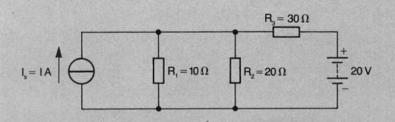

#### Example 9

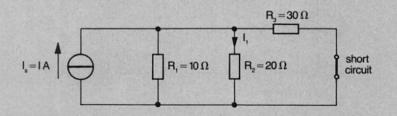

Determine the current in  $R_2$  of the circuit shown in Fig 1.31 by using the Superposition Theorem.

#### Fig 1-31

#### Solution

Consider the effect of the current source alone as shown in Fig 1.32.

#### Fig 1-32

R<sub>1</sub> is in parallel with R<sub>3</sub> = 10  $\Omega \parallel 30 \Omega = 7.5 \Omega$ Hence: I<sub>1</sub> =  $\left(\frac{7.5}{7.5 + 20}\right)$ IA = 0.273 A

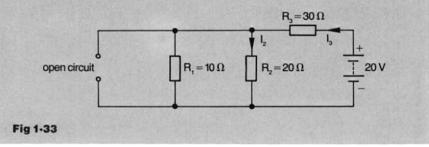

Considering the effect of the voltage source alone, as shown in Fig 1.33:

R<sub>1</sub> is in parallel with R<sub>2</sub> = 10  $\Omega \| 20 \ \Omega = 6.67 \ \Omega$ Hence: I<sub>3</sub> =  $\frac{20}{6.67 + 30} = 0.545 \ A$ Hence: I<sub>2</sub> =  $\left(\frac{10}{10 + 20}\right)0.545 = 0.182 \ A$ . The current in R<sub>2</sub> is the combined value of the currents produced by the current and the voltage source, ie the current in R<sub>2</sub> = I<sub>1</sub> (from current source) + I<sub>2</sub> (from voltage source) = 0.273 \ A + 0.182 \ A = 0.455 \ A.

## 1.16 Nodal analysis

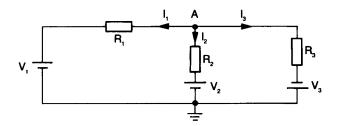

**a** Nodal analysis is a direct application of Kirchhoff's current law and is used to determine the voltage at nodes. Consider the circuit shown in Fig 1.34.

#### Fig 1. 34

- **b** Kirchhoff's current law indicates that  $I_1 + I_2 + I_3 = 0$ . Now if the voltage at node A is assumed to be V volts, then the currents may be expressed in terms of the voltage drops across the resistors, giving:  $\frac{V - V_1}{R_1} + \frac{V - V_2}{R_2} + \frac{V + V_3}{R_3} = 0$

- **c** The currents do not have to be shown all proceeding away from the node. However, the advantage of this arrangement is that V always appears on the left hand side of the equation, making sign changes unnecessary. If the currents are shown going towards the node, V has a negative sign in the equation format.

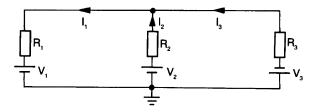

- **d** If the currents are as shown in Fig 1.35, then:  $I_2 + I_3 = I_1$ from Fig 1.35 it can be seen that:  $\frac{V_2 - V}{R_2} + \frac{-V_3 - V}{R_3} = \frac{V - V_1}{R_1}$

**Note:** This form of equation is disorderly, and so such a choice of current direction is inviting errors to be made.

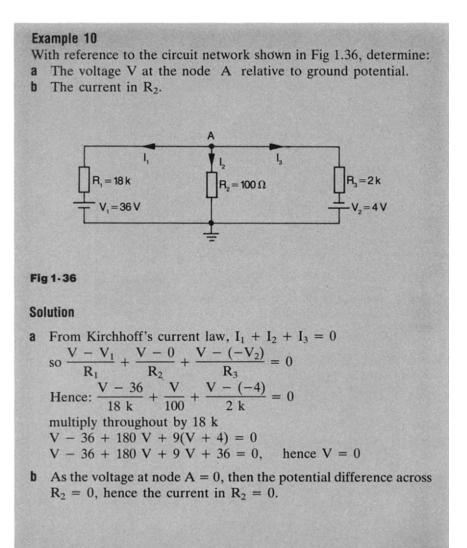

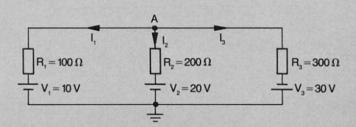

**Example 11** With reference to the circuit shown in Fig 1.37, determine the voltage V at node A relative to ground potential.

#### Fig 1-37

#### Solution

From Kirchhoff's current law,  $I_1 + I_2 + I_3 = 0$ thus  $\frac{V - 10}{100} + \frac{V - 20}{200} + \frac{V - (-30)}{300} = 0$ multiply throughout by 600 6 V - 60 + 3 V - 60 + 2 V + 60 = 0

Hence: V = 5.45 volts

Note: The equations shown in Example 11 may also be expressed in the form:

$$V\left[\frac{1}{R_1} + \frac{1}{R_2} + \frac{1}{R_3}\right] = \frac{V_1}{R_1} + \frac{V_2}{R_2} + \frac{V_3}{R_3}$$

thus

$$V = \frac{V_1G_1 + V_2G_2 + V_3G_3}{G_1 + G_2 + G_3}$$

where  $G = \frac{1}{R}$  = the conductance, measured in siemens.

## 1.17 Additional examples

## Example 12

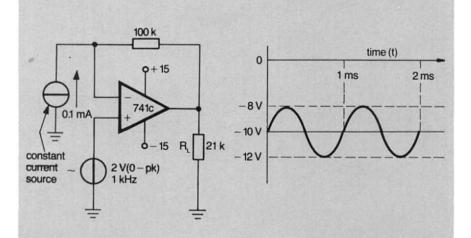

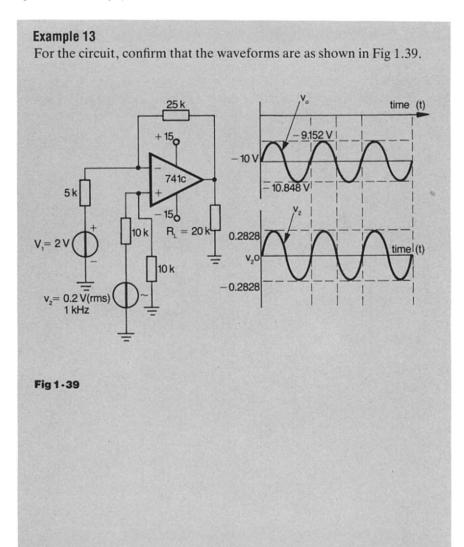

For the circuit, confirm that the output waveform is as shown in Fig 1.38.

Fig 1-38

## Chapter 2 FREQUENCY RESPONSE, SLEW RATE AND BANDWIDTH

# 2.1 Frequency response of the operational amplifier (introduction)

Many types of operational amplifiers are internally compensated by a small capacitor, eg about 30 pF (for a 741). The internal frequency compensation capacitor prevents the operational amplifier from oscillating with resistive feedback.

Oscillation is prevented by causing the gain of the operational amplifier to decrease at high frequencies. Otherwise there would be sufficient gain and phase shift to cause oscillations. (At a particular high frequency some in-phase signal is fed back to the input, from the output, through the ordinary feedback network.) This particular point is reviewed in more detail in Section 2.14A.

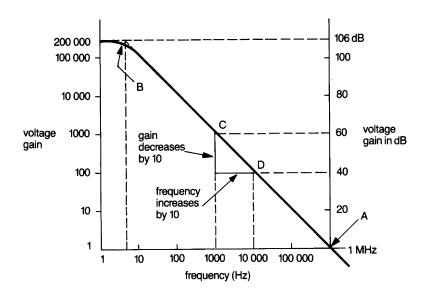

A typical frequency response curve is as shown in Fig 2.1. At low frequencies, the open loop voltage gain is very high, eg a 741 has a gain of about  $200\,000$  times or 106 dB.

Fig 2-1 Open-loop voltage gain versus frequency

Point B in Fig 2.1 indicates the upper break, or cut-off, frequency. At this point the voltage gain is 0.707 times the gain value at very low frequencies, and corresponds to a halving of power output to a constant load, for constant amplitude input signal.

Points C and D indicate how the gain decreases by a factor of 10 as frequency increases by a factor of 10, for frequencies greater than about ten times, or one decade, above the breakpoint. Also, from Fig 2.1 it can be seen that the voltage gain decreases by 20 dB, ie ten times, for an increase in frequency of ten times (one decade). Hence, the frequency response from B to A is often described as rolling off at a rate approaching 20 dB/decade.

This is equivalent to saying that the gain falls at a rate inversely proportional to the increase in frequency: due to the decreasing reactance of the compensating capacitor referred to earlier.

Point A is the unity gain frequency, and the product of the frequency and gain there is known as the gain-bandwidth product of the amplifier, being  $(1 \text{ MHz} \times 1) = 1 \text{ MHz}$  for the operational amplifier shown.

| Example  | e 1               |                                                                                                             |

|----------|-------------------|-------------------------------------------------------------------------------------------------------------|

|          |                   | open-loop gain of an operational amplifier at a fre-<br>kHz, if it has a unity gain bandwidth of $1.4$ MHz. |

| Solution | ı                 |                                                                                                             |

| From:    | A <sub>OL</sub> = | $= \frac{\text{Bandwidth at unity gain}}{\text{frequency}}$ $= \frac{1.4 \text{ MHz}}{20 \text{ kHz}}$      |

| Hence    | A <sub>OL</sub> = | = 70                                                                                                        |

When an operational amplifier is used as the basis of a negative feedback amplifier, then:

closed loop gain  $\times$  bandwidth of amplifier = open loop gain  $\times$  bandwidth of operational amplifier ie gain bandwidth product remains constant.

## 2.2 Operational amplifier: input signal variations (introduction)

The operational amplifier's response depends on the rate of change of the input signals applied to it. It is usual to consider the effect of *sinusoidal signals*, which have no abrupt discontinuity in their waveform, and *square wave signals* which consist of a succession of abrupt changes in slope. It is also usual to distinguish between *low amplitude output signals* (below about 1V peak) and *large signals* (above 1V peak). For small input, and hence output, signals noise is often the limiting factor for undistorted output; for large output signals, slewing rate is frequently the limiting factor.

The gain/frequency response for sinusoidal input signals is represented graphically by a plot of gain in decibels against a logarithmic frequency scale.

Strictly speaking,

gain in dB = 10  $\log_{10}\left(\frac{P_o}{P_{in}}\right)$

where  $P_o$  = output power and  $P_{in}$  = input power. From the above definition, dB gain = 10  $\log_{10} \left( \frac{V_o^2 / R_L}{V_{in}^2 / R_{in}} \right)$ = 20  $\log_{10} \left( \frac{V_o}{V_{in}} \cdot \frac{R_{in}}{R_L} \right)$

#### **Operational Amplifier Circuits**

Accepted usage is only strictly correct if  $R_{in} = R_L$ . It is nevertheless a convenient method of expressing and comparing voltage gains, eg a gain of 1000000 is equivalent to 120 dB, whereas one of 500000 is 114 dB, ie 6 dB less.

Example 2

Determine the voltage gain in dB:

a if  $\frac{V_o}{V_{in}} = 10$ , voltage gain in dB = 20 log<sub>10</sub> 10 = 20 dB

- **b** if  $\frac{V_o}{V_{in}} = 100$ , voltage gain in dB = 20 log<sub>10</sub> 100 = 40 dB

- **c** if  $\frac{V_o}{V_{in}} = \frac{1}{\sqrt{2}}$ , voltage gain in dB = 20 log<sub>10</sub>  $\frac{1}{\sqrt{2}} = -3$  dB.

Note, since power is proportional to  $V^2$ , a decrease in gain of 3 dB represents a halving of the output power, whereas a decrease of 6 dB corresponds to a halving of the voltage gain and the reduction of output power to a quarter of its original value.

## 2.3 Bode approximations (introduction)

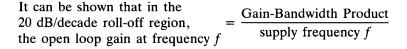

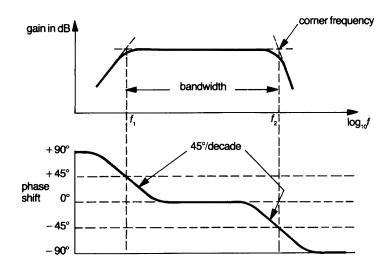

Gain/frequency plots are often approximated by a set of straight lines known as *Bode plots*. The significance of Bode plots can be determined by an analysis of Fig 2.2.

Fig 2-2 Bode approximation (gain/frequency)

In Fig 2.2 it is seen that the two straight Bode approximation lines intersect at  $f_c$ , and at this frequency the response is 3 dB down. The two straight lines are tangential to the true response at frequencies remote from the cut-off frequency, assuming the absence of other nearby breakpoints.

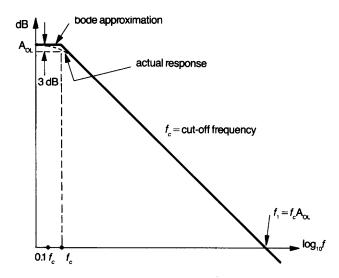

The corresponding phase/frequency characteristic is as shown in Fig 2.3. It can be seen that the Bode phase plot approximates the phase shift with limits of 0° and -90° for frequencies a decade below and above  $f_c$  respectively.

A single reactive component will introduce a slope approximating to a magnitude of 20 dB/decade into a frequency response. The slope will be positive or negative, depending upon whether the reactive component is capacitive or inductive and its location in the circuit.

#### Fig 2-3 Bode approximation (phase/frequency)

It can be shown that:  $\theta = -\tan^{-1} \frac{f}{f_c}$

for the type of frequency roll-off under discussion.

The Bode frequency plot is useful because, with practice, it enables a good theoretical approximation to the frequency response to be produced quite rapidly.

As far as the response under discussion is concerned:

- **a** when  $f \leq 0.1 f_c$ , the phase shift due to the breakpoint is effectively zero;

- **b** when  $f = f_c$ , the phase shift is  $-45^\circ$ ;

- **c** when  $f \ge 10 f_c$ , the phase shift is approximately  $-90^\circ$ .

The reader should consult a suitable text for further details.

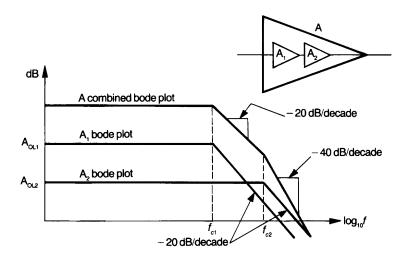

## 2.4 Bode approximation: multistage amplifier

Bode diagrams are most useful in determining the frequency response characteristics of cascaded gain stages.

The gain of a multistage amplifier is the product of the gains of individual stages. However, since gain is shown logarithmically in Bode plots, the overall Bode response is obtained by adding the responses of the separate stages.

Fig 2.4 illustrates the basic concepts of the production of a Bode plot for cascaded gain stages. The method is applicable to operational amplifier stages having responses similar in their general nature to that of compensated 741 type amplifiers.

#### Fig 2-4 Frequency response of cascaded gain stages

Bode diagrams are particularly useful in determining the stability and frequency response of feedback circuits. A frequency dependent response automatically implies that the amplifiers' gain and phase response will both change with frequency. Bode plots are further reviewed in Section 2.14B.

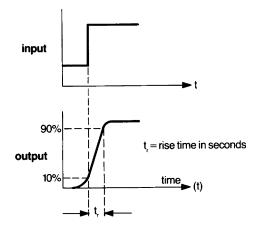

### 2.5 Rise time

Rise time is defined as the time required for the output voltage to rise from 10% of its final value to 90% of its final value in response to a step input.

This is illustrated in Fig 2.5, and proved in Section 2.14C.

#### Fig 2-5 Rise time illustration

For a 741 operational amplifier, or any circuit that has a simple -20 dB/decade roll-off above its upper cut-off frequency, it may be shown that upper cut-off frequency =  $\frac{0.35}{\text{rise time.}}$

This relationship is very useful as the basis of a practical method of determining the upper cut-off frequency of amplifier circuits. It is thus only necessary to examine the output response to a square wave input to be able to determine the upper cut-off frequency with adequate accuracy.

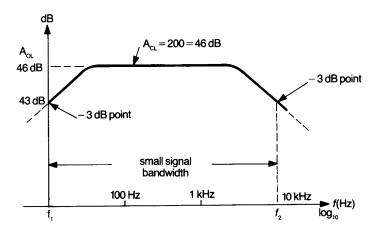

## 2.6 Small signal bandwidth

The useful frequency range or bandwidth of an amplifier is defined by an upper frequency limit,  $f_2$ , and a lower frequency limit,  $f_1$  (or zero hertz where amplifier is DC coupled).

At  $f_1$  and  $f_2$  the voltage gain is 0.707 its maximum value in the middle of the useful frequency range. This concept is represented in Fig 2.6.

Fig 2-6 Small signal bandwidth

## 2.7 Open loop/closed loop relationship for non-inverting amplifier circuits

Let  $f_2$  = upper cut-off frequency.

$f_{2(OL)}$  = upper cut-off frequency of open loop circuit, ie without negative feedback.

$f_{2(CL)}$  = upper cut-off frequency with negative feedback. It can be shown that:

closed loop Bandwidth,  $f_{2(CL)} = f_{2(OL)} \times \left(\frac{A_{OL}}{A_{CL}}\right)$ .

Let  $R_{o(OL)}$  = output resistance, under open loop conditions, and  $R_{o(CL)}$  = output resistance, under closed loop conditions. It can be shown that:

$$R_{o(CL)} = \frac{R_{o(OL)}}{\left(\frac{A_{OL}}{A_{CL}}\right)} \text{ and } R_{in(CL)} = R_{in(OL)}\left(\frac{A_{OL}}{A_{CL}}\right).$$

The useful relationships above are valid under conditions where the feedback is derived from the output voltage and fed back to the input as a voltage to be added antiphase to the input signal, ie a negative feedback voltage amplifier.

The inverting amplifier obeys the relationship  $f_{2(CL)} = f_{2(OL)} \times \left(\frac{A_{OL}}{A_{CL}}\right)$ approximately, providing  $A_{OL}$  and  $A_{CL}$  are gain magnitudes and provided that  $A_{CL}$  is > about 10. Strictly speaking  $f_{2(CL)} = f_{2(OL)} \left(\frac{A_{OL}}{A_{CL}+1}\right)$ .  $R_o$  is reduced to a low value and  $R_{in} = R_i$ .

#### Example 3

A non-inverting amplifier circuit has an open loop  $R_o$  of 75  $\Omega$  and a -3 dB cut-off frequency at 12 Hz. With feedback, R<sub>o</sub> decreases to 25 m $\Omega$ ; determine the amplifier's -3 dB bandwidth.

#### Solution

$R_{o(CL)} = \frac{R_{o(OL)}}{\frac{A_{OL}}{A_{CL}}}$ ie  $\frac{A_{OL}}{A_{CL}} = \frac{R_{o(OL)}}{R_{o(CL)}} = \frac{75 \ \Omega}{25 \ m\Omega} = 3000$

Closed loop bandwidth =  $f_{2(OL)} \times \left(\frac{A_{OL}}{A_{OL}}\right)$

$$= 12 \times 3000 = 36$$

kHz.

Hence: -3 dB bandwidth = 36 kHz.

#### Example 4

An inverting amplifier at constant amplitude input signal delivers a constant output power to its load over the frequency range 10 Hz to 30 kHz. Above 30 kHz the output power gradually decreases until at 350 kHz, for the same input power, the output power is halved, relative to that obtained at 20 kHz. If a 250 mV (rms) input signal at 20 kHz produces a 4 V (pk-pk) output waveform, determine the operational amplifier's upper cut-off frequency, if its open loop gain is approximately 106 dB.

#### Solution

The implication is that the upper cut-off frequency of the closed loop amplifier must be 350 kHz if the power output is halved.

The closed loop gain of the operational amplifier is given by:  $\frac{4 \text{ V (pk-pk)}}{250 \text{ mV (rms)}} = \frac{\sqrt{2} \text{ V (rms)}}{250 \text{ mV (rms)}} = 5.656 = A_{\text{CL}}.$ Given that  $A_{OL} = 106 \text{ dB}$  $106 \text{ dB} = 20 \log_{10} \frac{V_o}{V_{in}}$  $5.3 = \log_{10} |A_{OL}|$ Hence:  $A_{OL} = 199526$ , say 200000.

Now

$$f_{2(CL)} = f_{2(OL)} \times \frac{A_{OL}}{(A_{CL} + 1)}$$

∴  $f_{2(OL)} = f_{2(CL)} \times \frac{6.656}{200\,000}$  (neglecting the '1' since  $A_C \ge 1$ )

$= 350 \text{ kHz} \times \frac{6.656}{200\,000}$ .

Hence:  $f_{2(OL)} = 11.6 \text{ Hz}$ .

## 2.8 Slew rate

The slew rate of an operational amplifier indicates how fast its output voltages can change with respect to time. The general purpose operational amplifiers of the 741 series have a maximum slew rate of about  $0.5 \text{ V/}\mu\text{s}$ , whereas special purpose operational amplifiers may have slew rates of 100 V/ $\mu$ s or more. The lowest slew rate usually occurs at unity gain (unity gain as a result of negative feedback). The limited slew rate capabilities occur because internal compensation circuitry can only change its voltage at a rate limited by associated current sources.

For a capacitor

$$V = \frac{Q}{C} = \frac{I \times t}{C}$$

for a constant current, I

so  $\frac{\Delta V}{\Delta t} = \frac{I}{C}$

Hence, maximum slew rate =  $\frac{\text{change in output voltage}}{\text{change in time}} = \frac{I}{C}$ Where I = maximum current able to be supplied to the compensating capacitor C.

The essential point is that the capacitor has a maximum charging current associated with it in the operational amplifier, and its maximum voltage change with respect to time occurs when this current is being fully utilised. If capacitor voltage is required to change at a faster rate, there will be distortion of the output signal.

#### Example 5

A 741 operational amplifier, being used as a voltage follower, has an instantaneous input change of 5 volts. Determine how long it will take for the output voltage to change by 5 volts.

Solution From slew rate =  $\frac{\text{change in output voltage}}{\text{time}} = \frac{0.5 \text{ V}}{1 \times 10^{-6} \text{s}} = \frac{5 \text{ V}}{\text{time}}$ since a voltage follower has unity gain. So a change of 5 V at output will take 10 µs

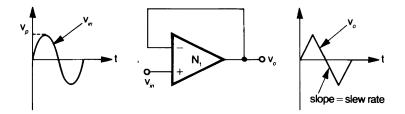

## 2.9 Slew rate limiting of sine waves

Consider the voltage follower in Fig 2.7 where  $v_{in}$  is a sine wave of peak amplitude  $v_p$ . The maximum rate of change of  $v_{in}$ , with respect to time, can be shown to be  $2\pi f v_p$  volts/sec where:

- **a** f is the frequency in Hz,

- **b** the peak amplitude is  $v_p$ .

shown in Fig 2.7.

The maximum rate of change of voltage with time occurs at the zero crossing points of a sinusoidal waveform; ie the waveform is at its steepest at these points. It should be apparent that increasing amplitude and increasing frequency will cause an increase in steepness at these points. This is because  $\frac{dv_o}{dt} \max = 2\pi f v_p$ , that is it is proportional to both f and  $v_p$ .

If the required rate of change is larger than the slew rate of the operational amplifier, the output,  $v_o$ , will be distorted. If the slew rate is grossly exceeded, then the output waveform will become triangular in nature, as

## Fig 2-7 Extreme slew rate limiting of sinusoidal output voltage Vo (when $2\pi f V p \rangle$ s)

The maximum frequency,  $f_{\text{max}}$ , at which slew rate will not distort the output voltage is:

$f_{\text{max}} = \frac{\text{slew rate}}{2\pi V_{op}}$  where  $V_{op}$  = maximum undistorted output voltage.

#### Example 6

The typical slew rate of a 741 is  $0.5 \text{ V/}\mu\text{s}$ . Determine the typical maximum frequency that an output signal may have, at an amplitude of 5 volts peak, without slew rate distortion occurring.

#### Solution

Since  $f_{\text{max}} = \frac{\text{slew rate}}{2\pi V_{op}}$ , ie  $f_{\text{max}} = \frac{0.5 \times 10^6}{2\pi \times 5}$ then  $f_{\text{max}} = 16 \text{ kHz}$ .

## 2.10 Full power bandwidth (large signal bandwidth)

This is the range of frequencies, from zero, over which a specific type of operational amplifier should produce no slew rate distortion of a maximum amplitude sinusoidal output signal.

A 741C amplifier should be capable of producing about 14 V (0-pk) sinusoidal for loads greater than, or equal to, 10 k and has a typical maximum slew rate of 0.5 V/ $\mu$ s. It can be shown that the full power bandwidth

(FPB, or large signal bandwidth) is given by:  $f = \frac{s}{2\pi V_p}$ .

Since  $2\pi f V_p \le s$  to avoid slew rate distortion, it follows that  $f \le \frac{s}{2\pi V_p}$  is

the range of frequencies over which an output signal of amplitude  $V_p$  can be obtained without slew rate distortion.

So full power bandwidth for the 741C will be about

$f \leq \frac{0.5 \times 10^6}{2\pi \times 14} \text{ Hz},$ FPB = 5.684 kHz.

#### Example 7

Calculate the full power bandwidth (FPB) of an operational amplifier operating from  $\pm 15$  V supply rails, if it saturates within 2 volts of these rails and has a maximum slew rate of 0.8 V/µs.

$$FPB = \frac{\text{slew rate}}{2\pi V_{op}} = \frac{0.8 \times 10^6}{6.28 \times (15 - 2)}$$

Hence: FPB = 9.8 kHz

## 2.11 Slew rate limiting of square wave input

In essence, slew rate limiting is the result of a limit in the ability of the internal circuitry of an operational amplifier to drive capacitive loads, either internal or external. The capacitance that limits the slewing ability is generally the compensation capacitance, although in some instances, it is the load capacitance.

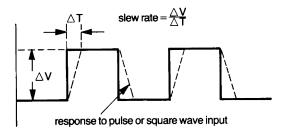

Fig 2.8 shows that at high required rates of signal change the current available to charge or discharge the capacitance is insufficient, and slew rate limiting of the actual output signal occurs.

#### Fig 2-8 The effect of slew rate on a square wave input

## 2.12 Slew rate limiting of triangular wave input

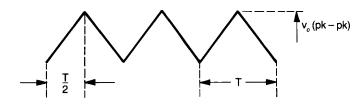

A triangular wave input will be correctly reproduced, in amplified form, at the output until the repetition rate of the signal is such that the rate of change of voltage inherent in the sloping edge waveform exceeds the slew rate capabilities of the operational amplifier.

Fig 2-9 Waveform diagram for 2.12

It can be shown that to avoid slew rate distortion: slew rate  $> \frac{V_o \text{ (pk-pk)}}{(T/2)}$  is necessary (Fig 2.9), ie slew rate >  $2V_o$  (pk-pk)  $f_r$  where  $f_r$  = repetition rate.

Hence:  $f_r \leq \frac{\text{slew rate}}{2V_o \text{ (pk-pk)}}$ , to avoid slew rate distortion.

In practice, two effects distort the output waveform. One is the maximum slew rate and the other is the frequency response limitations of the amplifier. The former tends to make triangular type waveforms, whereas frequency response limit tends to introduce an exponential component. At any instant it is the slower of these two effects that determines the actual waveform shape.

## 2.13 Worked examples

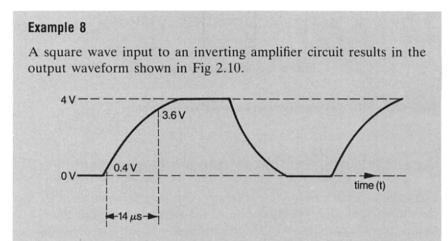

#### Fig 2-10

The time taken for each positive going output pulse to increase from 0.4 V to 3.6 V is 14  $\mu$ s. Determine the closed loop upper cut-off frequency (bandwidth).

#### Solution

The 0.4 V and 3.6 V represent 10% and 90% respectively of the maximum amplitude.

Since the closed loop upper cut-off frequency (see Section 2.5) 0.25

$=\frac{0.35}{\text{rise time}}$  then  $f_{\text{CL}}=\frac{0.35}{14\times 10^{-6}}$ .

Hence: bandwidth or closed loop upper cut-off frequency = 25 kHz.

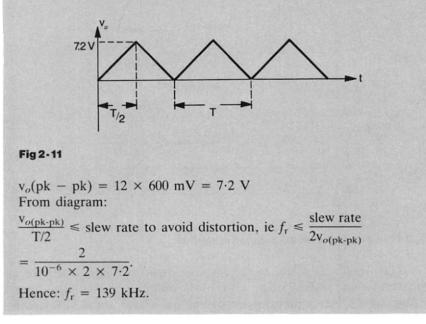

#### Example 9

Determine the highest repetition rate of a symmetrical triangular waveform input to an operational amplifier circuit before it suffers from slew-rate distortion.

#### Date given

Maximum slew rate =  $2 \text{ V/}\mu\text{s}$ pk-pk input amplitude = 600 mVAmplifier gain = 12

#### Solution

Output waveform is as shown in Fig 2.11.

## 2.14 Important review points

#### A Prevention of oscillation

Refer to Section 2.1.

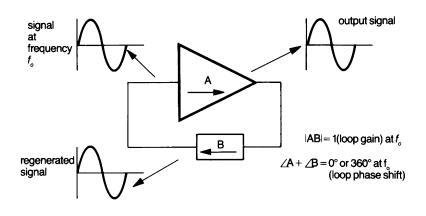

One method of preventing unwanted oscillation is to cause the gain to roll off at high frequencies so that there is insufficient gain available for oscillation to take place at the frequencies where there is the necessary loop phase shift of zero degrees.

Whereas negative feedback reduces the effective input signal to the operational amplifier, positive feedback increases it to a point where the

operational amplifier circuit may produce a sinusoidal output signal independent of any external input signal.

#### **B** Bode plot

Refer to Section 2.4.

A Bode plot is a graphical method for showing how the gain and phase shift of an amplifier vary with frequency.

A typical plot for an arbitrary RC coupled amplifier is shown in Fig 2.12.

#### Fig 2-12 Bode plot for an RC coupled amplifier

At low frequencies, due to the coupling capacitors' high reactance, the gain is very low, and the phase angle of the output, relative to the input, is leading by 90°. At frequency  $f_1$  the magnitude of the gain is 3 dB less than its mid-frequency value, and the phase lead is now 45°.

Over the bandwidth the gain and phase shift are reasonably constant. However, at  $f_2$ , the gain has again fallen to 3 dB below its mid-frequency value and the phase lag is  $45^{\circ}$ .

For this amplifier, the phase angle between output and input increases to a maximum of  $-90^{\circ}$ . The fall in gain at high frequencies is due to internal active device capacity tending to short the signal to ground, whilst the phase lag is due to the input, output and interstage coupling capacitors.

**C** Proof of:

$$f_2 = \frac{0.35}{\text{rise time}}$$

Refer to Section 2.5.

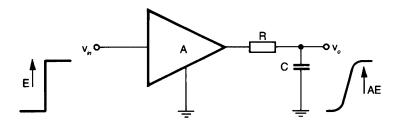

#### Fig 2-13

An amplifier with a single upper cut-off frequency,  $f_2$ , may be represented by the circuit shown in Fig 2.13.

If  $v_{in}$  in a step function of amplitude E, the output voltage,  $v_o$ , will be:  $v_o = AE(1 - e^{-t/CR}).$

The times  $t_1$  and  $t_2$  taken to reach 10% and 90% respectively of full amplitude will be:  $t_1 = CR \ln 0.9$  and  $t_2 = CR \ln 0.1$  so 10% to 90% rise time is  $t_2 = CR(\ln 0.9 - \ln 0.1)$

Now

$$f_2 = \frac{1}{2\pi CR}$$

=  $\frac{(\ln 0.9 - \ln 0.1)}{2\pi t_2}$

Hence:  $f_2 = \frac{0.35}{t_2}$ .

## 2.15 Problems for readers

#### Example 10

An operational amplifier, with open loop cut-off frequency equal to 10 Hz, is used in a non-inverting circuit with closed loop voltage gain of 12. With a square wave input signal, the output rise time is measured as 7  $\mu$ s. Determine the open loop gain of the operational amplifier, in dB.

#### Solution

95.6 dB

#### Example 11

A standard non-inverting amplifier circuit has an output resistance of 30 m $\Omega$ . The operational amplifier has an open loop output resistance of 120  $\Omega$ , an upper -3 dB cut-off frequency of 10 Hz and an open loop gain of 102 dB. Determine the amplifier's -3 dB bandwidth.

#### Solution

40 kHz

## Chapter 3 WAVEFORM GENERATORS

## 3.1 Introduction

This chapter deals with operational amplifier circuits which generate signals.

The four common circuits are:

- Square wave

- Triangular wave

- Sawtooth wave

- Sine wave

## 3.2 Square wave generator

A multivibrator is a circuit which essentially generates square waves. There are three types of multivibrator:

Astable (free running) — The two states of the circuit are momentarily stable, and the circuit switches repetitively between these states.

**Monostable** (one shot) — Has only one stable state, but it can be made to change to another state by the application of a suitable trigger pulse. It then returns to the stable state after a time interval determined by circuit component values.

**Bistable** (flip-flop) — Has two stable states and remains in one until suitably triggered to the other, in which it remains until again triggered to the first state, and so on.

## 3.3 Basic principles of a bistable npn transistor multivibrator

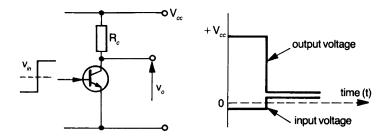

It is useful to note the basic principles of a bistable npn transistor multivibrator before considering the operational amplifier configurations. First consider the transistor as a switch, as shown in Fig 3.1, as the base voltage is changed from reverse bias to forward bias. The resulting voltage waveforms are also shown in Fig 3.1.

#### Fig 3-1 Basic principles of a transistor as a switch

**Reverse bias** Leakage current only in the collector circuit. The voltage drop across  $R_c$  is very small. The collector voltage is effectively  $_c + V_{cc}$ . Forward bias Collector current flows. The collector voltage falls until it saturates, in this case, at just about the base voltage.

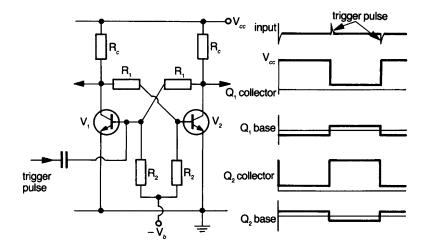

The principle of the above action is now applied to a bistable npn transistor multivibrator circuit as shown in Fig 3.2.

#### Fig 3-2 Bistable npn transistor multivibrator

52

- **a** Initially assume that the base-emitter junction of  $V_1$  is reverse biased. The collector of  $V_1$  will be at  $V_{cc}$ . A positive trigger pulse raises  $V_1$  base above zero.  $V_1$  collector voltage falls, causing  $V_2$  base voltage to fall, cutting off  $V_2$ . The collector voltage of  $V_2$  rises to  $V_{cc}$ .

- **b** A negative trigger pulse lowers collector current of  $V_1$ , causing  $V_1$  collector voltage to rise, which raises  $V_2$  base above zero.  $V_2$  collector voltage falls, assisting the fall of  $V_1$  base voltage and resulting in the cut-off of  $V_1$ . The collector voltage of  $V_1$  rises to  $V_{cc}$ , the initial condition.

## 3.4 Operational amplifier as a free-running symmetrical multivibrator

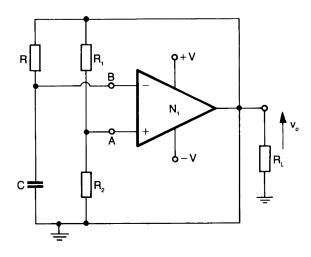

#### Fig 3-3 Free running symmetrical multivibrator

- **a** Refer to Fig 3.3. The two states of the circuit, between which it switches are:

- positive saturation

- negative saturation

- **b** The output is a square wave of frequency:

$$f = \frac{1}{T} = \frac{1}{2RC \ln\left(\frac{1+\beta}{1-\beta}\right)}$$

- **c** The feedback ratio ( $\beta$ ) is established by the potential divider made up of R<sub>1</sub> and R<sub>2</sub>, ie  $\beta = \frac{R_2}{R_1 + R_2}$

- **d** The amplitude of the exponential triangular waveform is  $\beta V_o$

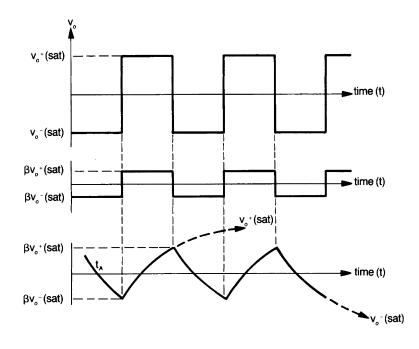

#### Fig 3-4 Waveforms of free running multivibrator

- **a** Assume that at time  $t_A$  the amplifier output is at  $V_o^-$  (sat). The voltage at terminal A (Fig 3.3) is  $\beta V_o^-$  (sat).

- **b** Simultaneously, at time  $t_A$ , terminal B is positive with respect to terminal A and its potential decreases as C discharges through R towards  $V_o^-$  (sat).

- **c** When  $V_B = V_A$  (since  $V_B$  is changing in potential, whereas  $V_A$  is static), the amplifier will start to come out of saturation. The positive feedback to terminal A will then assist in driving the output towards the positive saturation level.

- **d** The voltage across C cannot change instantaneously. C will now charge up through R towards  $V_o^+$  (sat) and the potential at B will rise exponentially to  $\beta V_o^+$  (sat).

- **e** The circuit will start to switch back to the initial state of negative saturation when  $V_B$  again equals  $V_A$ .

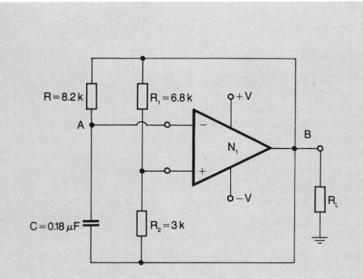

#### Example 1

Assume that the output of the circuit in Fig 3.5 saturates at some level between +12 V and +14 V.

#### Fig 3-5

- **a** Determine the frequency and amplitude of the waveforms at A and B.

- **b** Determine the possible variation in frequency and amplitude that would be caused by using resistors with tolerance of  $\pm 5\%$  and a capacitor with a tolerance of  $\pm 10\%$ .

#### Solution

a

$$\beta = \frac{R_2}{R_1 + R_2} = \frac{3 k}{6 \cdot 8 k + 3 k} = \frac{3 k}{9 \cdot 8 k} = 0.306$$

$$T = 2RC \ln \frac{(1 + \beta)}{(1 - \beta)}$$

Hence:  $T = 2 \times 8 \cdot 2 k \times 0.18 \times 10^{-6} \ln \left(\frac{1 + 0.306}{1 - 0.306}\right)$

$$= 2.952 \times 10^{-3} \ln \left(\frac{1 \cdot 306}{0.694}\right)$$

$$= 0.002952 \times 0.633$$

Hence:  $T = 0.001867$  seconds and, since  $T = \frac{1}{f}$ ,

f = 535.6 Hz = frequency at A, and B

The amplitude of the square wave output will be between +12 volts and +14 volts, so the exponential triangular waveform will be  $\beta$  times these values, ie between 12 × 0.306 and 14 × 0.306.

Hence, range is: 3·67 V and 4·29 V (0-pk) Amplitude of waveform at A between 3·67 and 4·29 V Amplitude of waveform at B between 12 and 14 V **b**  $\beta_{(max)} = \frac{3k \times 1 \cdot 05}{(3k \times 1 \cdot 05) + (6 \cdot 8k \times 0 \cdot 95)} = \frac{3 \cdot 15 k}{3 \cdot 15 k + 6 \cdot 46 k} = \frac{3 \cdot 15 k}{9 \cdot 61 k}$   $\beta_{(max)} = 0 \cdot 328$   $\beta_{(min)} = \frac{3k \times 0 \cdot 95}{(3k \times 0 \cdot 95) + (6 \cdot 8k \times 1 \cdot 05)} = \frac{2 \cdot 85 k}{2 \cdot 85 k + 7 \cdot 14 k} = \frac{2 \cdot 85 k}{9 \cdot 99 k}$   $\beta_{(min)} = 0 \cdot 285$ so  $T_{(max)} = 2 \times 1 \cdot 05 \times 8 \cdot 2 k \times 1 \cdot 1 \times 0 \cdot 18 \times 10^{-6} \ln \left(\frac{1 + 0 \cdot 328}{1 - 0 \cdot 328}\right)$   $= 3 \cdot 41 \times 10^{-3} \ln \left(\frac{1 \cdot 328}{0 \cdot 672}\right)$   $= 0 \cdot 00341 \times 0 \cdot 681 = 0 \cdot 00232 \text{ seconds}$ so  $f_{(min)} = \frac{1}{0 \cdot 00232} = 430 \cdot 9 \text{ Hz}$   $T_{(min)} = 2 \times 0 \cdot 95 \times 8 \cdot 2 k \times 0 \cdot 9 \times 0 \cdot 18 \times 10^{-6} \ln \left(\frac{1 + 0 \cdot 2853}{1 - 0 \cdot 2853}\right)$   $= 2 \cdot 52 \times 10^{-3} \ln \left(\frac{1 \cdot 2853}{0 \cdot 7147}\right)$   $= 0 \cdot 00252 \times 0 \cdot 587 = 0 \cdot 00148 \text{ seconds}$ so  $f_{(max)} = \frac{1}{0 \cdot 00148} = 675 \cdot 1 \text{ Hz}$ .

The frequency is not affected by the square wave amplitude. The square wave amplitude will still be between 12 and 14 volts.

The exponential triangular waveform will be between:

$\begin{array}{l} \beta_{(min)} \,\times\, 12 \,\, and \,\, \beta_{(max)} \,\times\, 14 \\ = \,\, 0{\cdot}285 \,\,\times\, 12 \,\, and \,\, 0{\cdot}328 \,\,\times\, 14 \\ = \,\, 3{\cdot}42 \,\, V \,\, and \,\, 4{\cdot}59 \,\, V \,\, (0{\text{-pk}}) \,\,. \end{array}$

#### Example 2

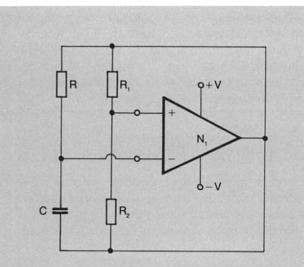

The basic square wave generator (astable or free running multivibrator) shown in Fig 3.6 is to be constructed so that the 'triangular' waveform is to be half the amplitude of the square wave output. The frequency of the oscillation is to be 200 Hz. Determine the constraints that these requirements place on the component values.

#### Fig 3-6

Solution

$T = 2RC \ln \left(\frac{1+\beta}{1-\beta}\right) \text{ and the required value of } T = \frac{1}{200} \text{ s} = 5 \text{ ms}$ so:  $0.005 = 2RC \ln \left(\frac{1+\beta}{1-\beta}\right) \dots (1)$ The amplitude relationship requires that  $\beta = 0.5 \dots (2)$ Substituting (2) in (1) gives:  $0.005 = 2RC \ln \left(\frac{1.5}{0.5}\right)$ Hence:  $0.005 = 2RC \ln 3$ 0.005 = 2.197 RCso  $RC = 0.00228 \dots (3)$ Also from (2)  $\frac{R_2}{R_1 + R_2} = 0.5$ , so  $R_1 = R_2$  is required, and from (3)  $R(k\Omega) \times C(\mu F) = 2.28$  is necessary.

A suitable set of values would be:  $R_1 = R_2 = 10 \text{ k}$  R = 2.2 k $C = \frac{2.28}{2.2 \text{ k}} = 1.036 \text{ }\mu\text{F}$

In practice C would be 1  $\mu$ F and R either a variable resistor or a variable resistor in series with a fixed resistor. This would enable the frequency to be adjustable to 200 Hz while using standard value components.

Some other restrictions on component values would exist to ensure the circuit operated correctly. These would include R and  $R_1 || R_2$ both very much lower than  $R_{in}$  of the operational amplifier. R and  $R_1 || R_2$  should be such as to ensure that the output current of the operational amplifier was below its rated maximum output current, or its current limited output, as applicable.

## 3.5 Ramp-generator theory

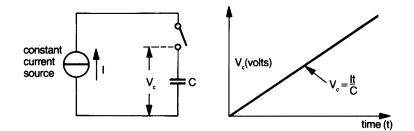

It will be useful to note the basic principles of ramp-generator theory, before considering triangular wave generator principles.

Consider a constant current source as shown in Fig 3.7. Capacitor C is charged by the constant current when the switch is closed.

#### Fig 3-7 Constant-current source ramp generation

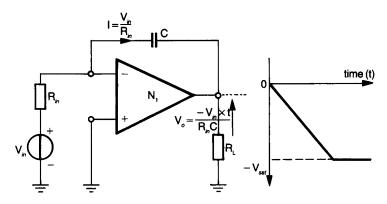

$V_c$  is called a *ramp voltage*. If the constant current source is replaced by  $V_{in}$  and  $R_{in}$  and an operational amplifier, as shown in Fig 3.8, I will equal  $\frac{V_{in}}{R_{in}}$  since negative input will remain close to ground potential, due to the high open-loop gain of the operational amplifier.

Fig 3-8 The basic integrator circuit as a ramp generator

The circuit shown in Fig 3.8 has several disadvantages:

- **a**  $V_o$  can only go to -V (sat).

- **b** When  $V_{in} = 0$ ,  $V_o \neq 0$  because the small bias currents will charge the capacitor.

- **c** To obtain a positive-going ramp,  $V_{in}$  must be reversed.

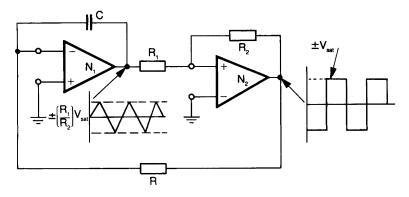

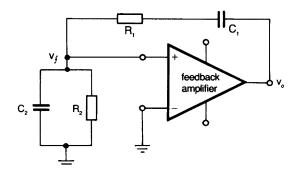

## 3.6 Basic triangular wave generator circuit

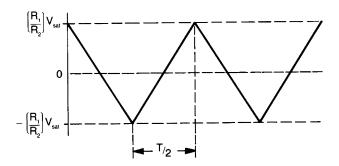

Fig 3-9 Basic triangular wave generator circuit

In Fig 3.9 the size of the triangular amplitude is equivalent to  $\frac{R_1}{R_2} V_{sat}$  (0-pk).

The frequency of the waveform is given by:  $f = \frac{R_2}{4R_1RC}$  Hz

This relationship is proved in Section 3.13A (Important review points).

## 3.7 Triangular wave generator circuit

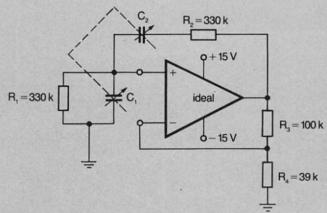

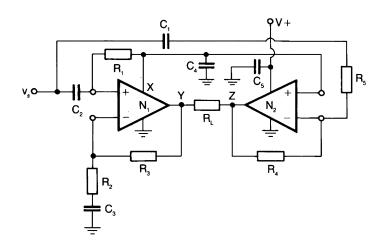

Fig 3.10 shows the essential elements of a circuit that combines positive and negative ramp generation to produce a triangular waveform.

#### Fig 3-10 Triangular wave generator

- **a** Adjustment of R controls the frequency.

- **b**  $R_1$  applies a voltage,  $V_1$ , to the inverting input of  $N_2$ . Varying the setting of  $R_1$  alters the DC level of the triangular wave.

- $\mathbf{c}$  R<sub>2</sub> controls the peak to peak swing of the triangular wave.

- **d**  $R_3$  controls the triangular waveform symmetry, ie the relative rise and fall times of the triangular waveform.

- **e** The zener diode clipping circuit limits the square wave amplitude to  $(V_Z + V_D)$  as shown in Fig 3.10:  $V_D$  is the zener diode forward voltage drop.

- f The feedback capacitor from the output to the inverting input of  $N_1$  means that this circuit can be classified as an integrator. This is consistent with the above description, because the integral of the constant capacitor charging current is a ramp voltage.

(See Section 1.14.)

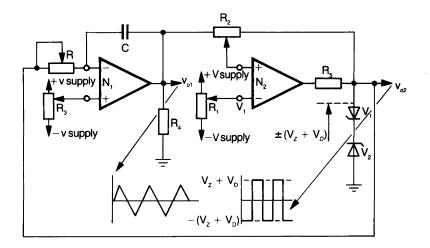

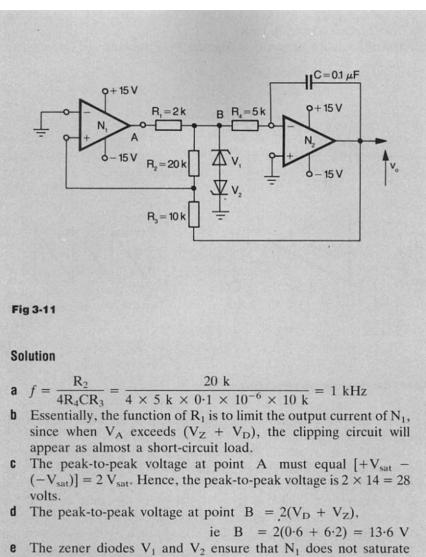

#### Example 3

In Fig 3.11 the operational amplifiers saturate at  $\pm 14$  V output levels. The reverse biased zener diode voltage drops equal 6.2 V and  $V_{D_1} = V_{D_2} = 0.6$  V.

- a Determine the frequency of oscillation of the circuit shown.

- **b** State the function of  $R_1$ .

- c What is the voltage (pk-pk) at point A?

- d What is the voltage (pk-pk) at point B?

- **e** State the function of the zener diodes  $V_1$  and  $V_2$ .

**e** The zener diodes  $V_1$  and  $V_2$  ensure that  $N_1$  does not saturate heavily, which avoids discrepancies between theoretical and practical frequency values.

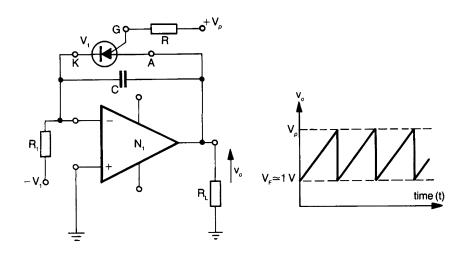

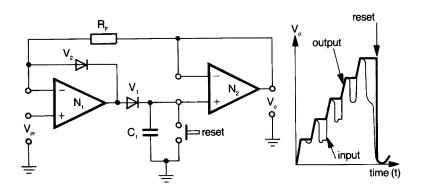

## 3.8 Sawtooth wave generator

The single ramp generator mentioned in Section 3.5 can be modified to make a sawtooth wave generator. A typical circuit is shown in Fig 3.12, where it can be seen that a programmable unijunction transistor (PUT) has been connected across C. The function of the PUT is as follows:

- **a** When the voltage across  $C = V_p$ , the PUT short-circuits C by becoming a low resistance from A to K.

- **b** When the voltage across  $C = V_F$ , the PUT becomes an open circuit from A to K.

#### Fig 3-12 Sawtooth wave generator

- **a** The voltage,  $V_p$ , applied to the gate terminal of the PUT corresponds to the peak amplitude of the sawtooth waveform.

- **b** The PUT will act as an open circuit from A to K prior to the circuit being energised. C will charge up when the circuit is energised, with the terminal connected to the amplifier output becoming more positive due to the current flowing via  $R_1$  to  $-V_1$ . This will continue until the potential at A becomes about 0.7 volts higher than that at G, ie 0.7 volts higher than that at  $V_p$ . The PUT will then act as a short circuit from A to K.

- **c** C then discharges rapidly until the current from A to K falls below the holding current of the PUT, when the PUT returns to its initial state and the cycle recommences.

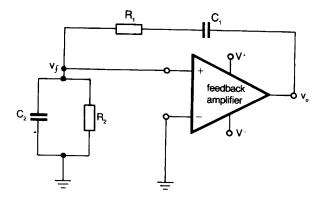

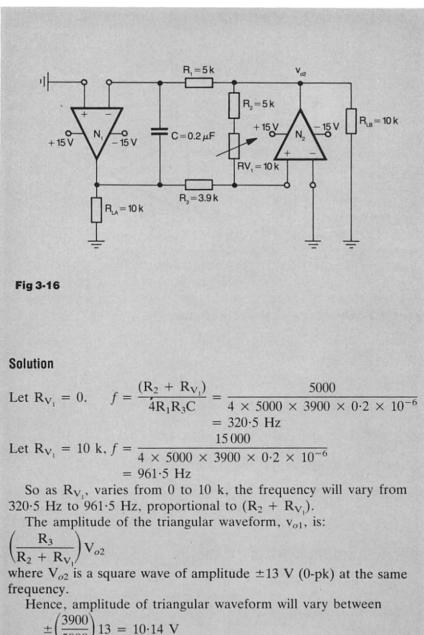

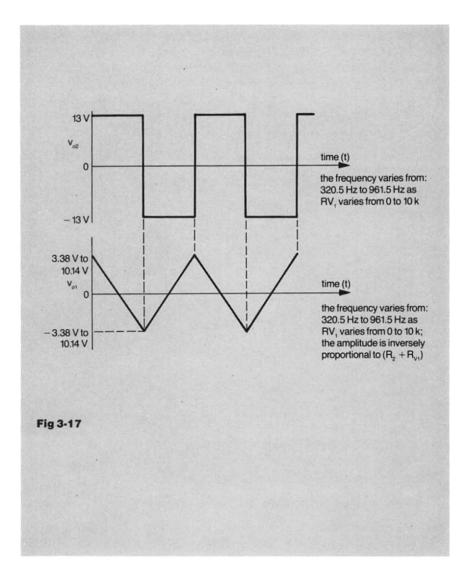

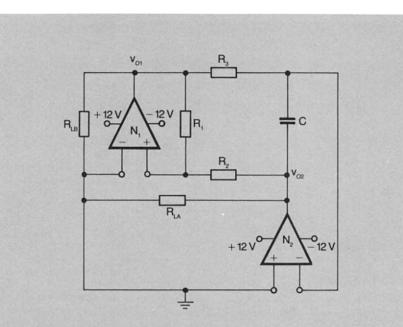

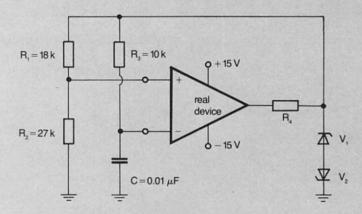

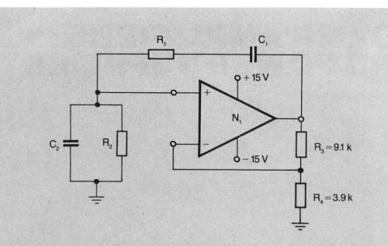

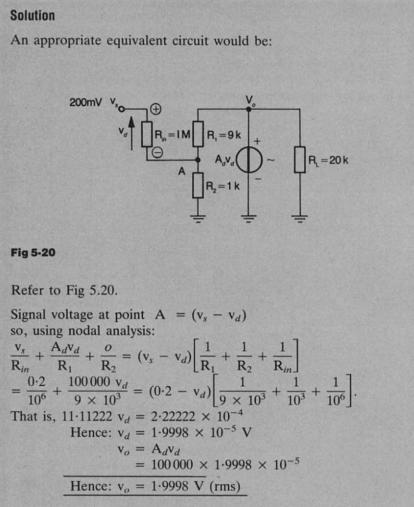

- **d** The frequency of oscillation,  $f \approx \frac{V_1}{R_1 C V_p}$