Wiley Series in Quality & Reliability Engineering

KIRK A. GRAY • JOHN J. PASCHKEWITZ

# NEXT GENERATION HALT AND HASS ROBUST DESIGN OF ELECTRONICS AND SYSTEMS

# Next Generation HALT and HASS

#### Wiley Series in Quality and Reliability Engineering

#### Dr. Andre Kleyner

Series Editor

The Wiley series in Quality & Reliability Engineering aims to provide a solid educational foundation for both practitioners and researchers in Q&R field and to expand the reader's knowledge base to include the latest developments in this field. The series will provide a lasting and positive contribution to the teaching and practice of engineering.

The series coverage will contain but is not exclusive to:

- Statistical methods

- Physics of failure

- Reliability modeling

- Functional safety

- Six sigma methods

- Lead free electronics

- Warranty analysis/management

- Risk and safety analysis

A complete list of titles in this series appears at the end of the volume.

# Next Generation HALT and HASS Robust Design of Electronics and Systems

Kirk A. Gray

Accelerated Reliability Solutions, LLC, Colorado, USA

John J. Paschkewitz

Product Assurance Engineering, LLC, Missouri, USA

This edition first published 2016 © 2016 John Wiley & Sons, Ltd

Registered Office

John Wiley & Sons, Ltd, The Atrium, Southern Gate, Chichester, West Sussex, PO19 8SQ, United Kingdom

For details of our global editorial offices, for customer services and for information about how to apply for permission to reuse the copyright material in this book please see our website at www.wiley.com.

The right of the authors to be identified as the authors of this work has been asserted in accordance with the Copyright, Designs and Patents Act 1988.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, except as permitted by the UK Copyright, Designs and Patents Act 1988, without the prior permission of the publisher.

Wiley also publishes its books in a variety of electronic formats. Some content that appears in print may not be available in electronic books.

Designations used by companies to distinguish their products are often claimed as trademarks. All brand names and product names used in this book are trade names, service marks, trademarks or registered trademarks of their respective owners. The publisher is not associated with any product or vendor mentioned in this book.

Limit of Liability/Disclaimer of Warranty: While the publisher and authors have used their best efforts in preparing this book, they make no representations or warranties with respect to the accuracy or completeness of the contents of this book and specifically disclaim any implied warranties of merchantability or fitness for a particular purpose. It is sold on the understanding that the publisher is not engaged in rendering professional services and neither the publisher nor the authors shall be liable for damages arising herefrom. If professional advice or other expert assistance is required, the services of a competent professional should be sought.

Library of Congress Cataloging-in-Publication Data

Names: Gray, Kirk, author. | Paschkewitz, John James, author.

Title: Next generation HALT and HASS: robust design of electronics and systems/

by Kirk Gray, John James Paschkewitz.

Description: Chichester, UK; Hoboken, NJ: John Wiley & Sons, 2016.

Includes bibliographical references and index.

Identifiers: LCCN 2015044935 | ISBN 9781118700235 (cloth)

Subjects: LCSH: Accelerated life testing. | Electronic systems–Design and construction. |

Electronic systems–Testing.

Classification: LCC TA169.3 .G73 2016 | DDC 621.381028/7-dc23

LC record available at http://lccn.loc.gov/2015044935

A catalogue record for this book is available from the British Library.

Set in 10.5/13pt Palatino by SPi Global, Pondicherry, India

# Contents

| Pr | eface | Editor's Foreword<br>e<br>Acronyms                    | xiv<br>xiv<br>xvi |

|----|-------|-------------------------------------------------------|-------------------|

| In | trodu | action                                                | 1                 |

| 1  | Bas   | is and Limitations of Typical Current Reliability     |                   |

|    | Met   | thods and Metrics                                     | 5                 |

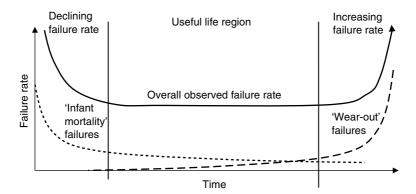

|    | 1.1   | The Life Cycle Bathtub Curve                          | 5<br>7            |

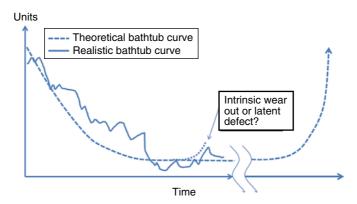

|    |       | 1.1.1 Real Electronics Life Cycle Curves              | 9                 |

|    | 1.2   | HALT and HASS Approach                                | 11                |

|    | 1.3   | The Future of Electronics: Higher Density and Speed   |                   |

|    |       | and Lower Power                                       | 13                |

|    |       | 1.3.1 There is a Drain in the Bathtub Curve           | 14                |

|    | 1.4   | Use of MTBF as a Reliability Metric                   | 16                |

|    | 1.5   | MTBF: What is it Good For?                            | 17                |

|    |       | 1.5.1 Introduction                                    | 17                |

|    |       | 1.5.2 Examples                                        | 18                |

|    |       | 1.5.3 Conclusion                                      | 24                |

|    |       | 1.5.4 Alternatives to MTBF for Specifying Reliability | 25                |

|    | 1.6   | Reliability of Systems is Complex                     | 26                |

|    | 1.7   |                                                       | 28                |

|    | 1.8   | Traditional Reliability Development                   | 33                |

|    | Bibl  | iography                                              | 34                |

**vi** Contents

| 2 The Need for Reliability Assurance Reference |                                       |                                                          |    |  |  |  |

|------------------------------------------------|---------------------------------------|----------------------------------------------------------|----|--|--|--|

|                                                | Metrics to Change                     |                                                          |    |  |  |  |

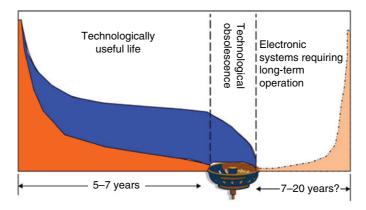

|                                                | 2.1                                   | Wear-Out and Technology Obsolescence of Electronics      | 36 |  |  |  |

|                                                | 2.2                                   | Semiconductor Life Limiting Mechanisms                   | 37 |  |  |  |

|                                                |                                       | 2.2.1 Overly Optimistic and Misleading Estimates         | 42 |  |  |  |

|                                                | 2.3                                   | Lack of Root Cause Field Unreliability Data              | 43 |  |  |  |

|                                                |                                       | Predicting Reliability                                   | 48 |  |  |  |

|                                                | 2.5                                   | Reliability Predictions – Continued Reliance on          |    |  |  |  |

|                                                |                                       | a Misleading Approach                                    | 50 |  |  |  |

|                                                |                                       | 2.5.1 Introduction                                       | 51 |  |  |  |

|                                                |                                       | 2.5.2 Prediction History                                 | 52 |  |  |  |

|                                                |                                       | 2.5.3 Technical Limitations                              | 53 |  |  |  |

|                                                |                                       | 2.5.4 Keeping Handbooks Up-to-Date                       | 54 |  |  |  |

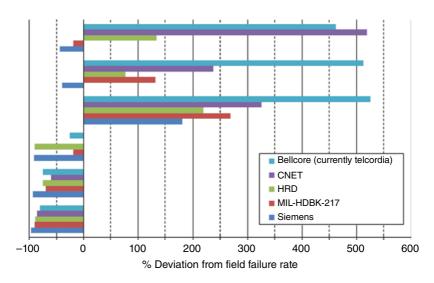

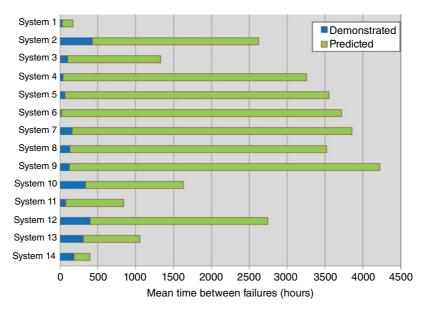

|                                                |                                       | 2.5.5 Technical Studies – Past and Present               | 58 |  |  |  |

|                                                |                                       | 2.5.6 Reliability Assessment                             | 62 |  |  |  |

|                                                |                                       | 2.5.7 Efforts to Improve Tools and Their Limitations     | 63 |  |  |  |

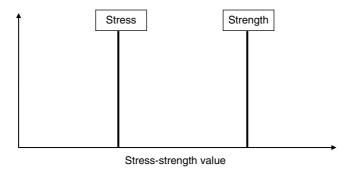

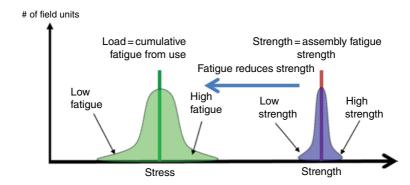

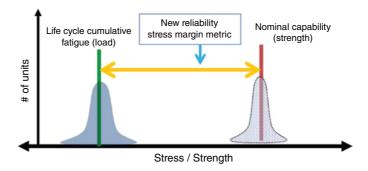

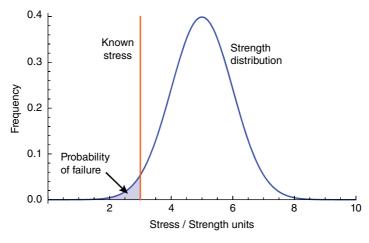

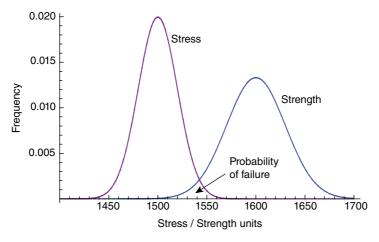

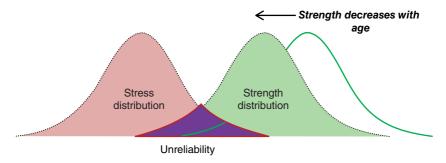

|                                                | 2.6                                   | Stress–Strength Diagram and Electronics Capability       | 64 |  |  |  |

|                                                | 2.7                                   | Testing to Discover Reliability Risks 6                  |    |  |  |  |

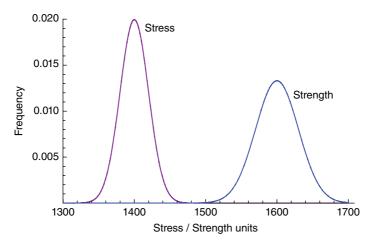

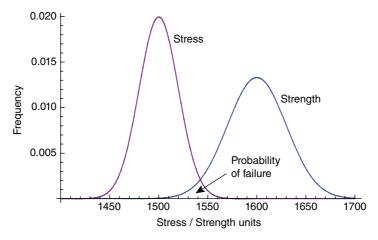

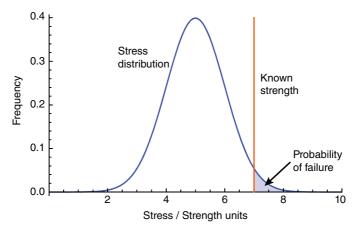

|                                                | 2.8 Stress–Strength Normal Assumption |                                                          | 69 |  |  |  |

|                                                |                                       | 2.8.1 Notation                                           | 70 |  |  |  |

|                                                |                                       | 2.8.2 Three Cases                                        | 71 |  |  |  |

|                                                |                                       | 2.8.3 Two Normal Distributions                           | 73 |  |  |  |

|                                                |                                       | 2.8.4 Probability of Failure Calculation                 | 73 |  |  |  |

|                                                | 2.9                                   | 2.9 A Major Challenge – Distributions Data               |    |  |  |  |

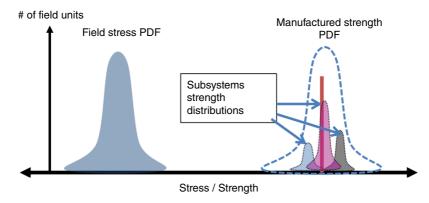

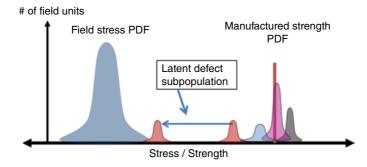

|                                                | 2.10                                  | HALT Maximizes the Design's Mean Strength                | 75 |  |  |  |

|                                                | 2.11                                  | What Does the Term HALT Actually Mean?                   | 78 |  |  |  |

|                                                | Bibl                                  | iography                                                 | 83 |  |  |  |

| 3                                              | Cha                                   | llenges to Advancing Electronics Reliability Engineering | 86 |  |  |  |

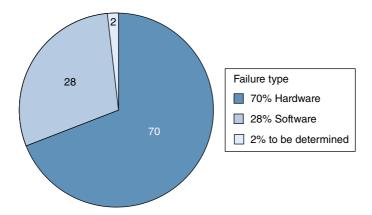

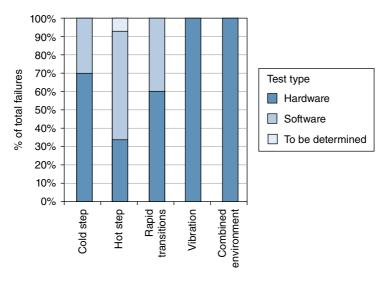

|                                                | 3.1                                   | Disclosure of Real Failure Data is Rare                  | 86 |  |  |  |

|                                                | 3.2                                   | Electronics Materials and Manufacturing                  |    |  |  |  |

|                                                |                                       | Evolution                                                | 89 |  |  |  |

|                                                | Bibl                                  | iography                                                 | 91 |  |  |  |

| 4                                              | A N                                   | ew Deterministic Reliability Development Paradigm        | 92 |  |  |  |

|                                                | 4.1                                   | Introduction                                             | 92 |  |  |  |

|                                                | 4.2                                   | Understanding Customer Needs and Expectations            | 95 |  |  |  |

|                                                | 4.3                                   | Anticipating Risks and Potential Failure Modes           | 98 |  |  |  |

Contents

|   | 4.4      | Robu             | st Design for Reliability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 104 |

|---|----------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|   | 4.5      | Diagr            | nostic and Prognostic Considerations and Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 110 |

|   | 4.6      | Know             | ledge Capture for Reuse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 110 |

|   | 4.7      | Accel            | erated Test to Failure to Find Empirical                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|   |          | Desig            | n Limits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 112 |

|   | 4.8      | Desig            | n Confirmation Testing: Quantitative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

|   |          | Accel            | erated Life Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 113 |

|   | 4.9      | Limit            | ations of Success Based Compliance Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 114 |

|   | 4.10     | Produ            | action Validation Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 115 |

|   | 4.11     | Failuı           | re Analysis and Design Review Based on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|   |          | Test F           | Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 116 |

|   | Bibl     | iograp           | hy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 120 |

| _ | <b>C</b> |                  | U. L. Start and Proceedings of the Control of the C |     |

| 5 |          | imon (<br>Succes | Understanding of HALT Approach is Critical                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 122 |

|   | 5.1      |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 123 |

|   | 5.1      |                  | Γ – Now a Very Common Term                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 123 |

|   | 3.2      |                  | Γ – Change from Failure Prediction to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 124 |

|   |          | 5.2.1            | re Discovery                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

|   | E 2      |                  | O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 125 |

|   | 5.3      |                  | Education of HALT May Increase Fear,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 130 |

|   |          |                  | rtainty and Doubt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 130 |

|   |          | 5.3.1<br>5.3.2   | While You Were Busy in the Lab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 132 |

|   |          | 5.5.2            | Product Launch Time – Too Late, But Now                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 122 |

|   |          |                  | You May Get the Field Failure Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 132 |

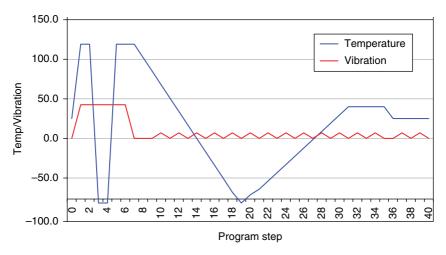

| 6 | The      | Funda            | amentals of HALT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 134 |

|   | 6.1      | Disco            | vering System Stress Limits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 134 |

|   | 6.2      | HAL              | Γ is a Simple Concept – Adaptation is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|   |          | the C            | hallenge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 135 |

|   | 6.3      | Cost             | of Reliable vs Unreliable Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 136 |

|   | 6.4      | HAL              | Γ Stress Limits and Estimates of Failure Rates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 137 |

|   |          | 6.4.1            | What Level of Assembly Should HALT be                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|   |          |                  | Applied?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 137 |