**CPSS Power Electronics Series**

# Deshang Sha Guo Xu

# High-Frequency Isolated Bidirectional Dual Active Bridge DC-DC Converters with Wide Voltage Gain

## **CPSS Power Electronics Series**

#### Series editors

Wei Chen, Fuzhou University, Fuzhou, Fujian, China Yongzheng Chen, Liaoning University of Technology, Jinzhou, Liaoning, China Xiangning He, Zhejiang University, Hangzhou, Zhejiang, China Yongdong Li, Tsinghua University, Beijing, China Jingjun Liu, Xi'an Jiaotong University, Xi'an, Shaanxi, China An Luo, Hunan University, Changsha, Hunan, China Xikui Ma, Xi'an Jiaotong University, Xi'an, Shaanxi, China Xinbo Ruan, Nanjing University of Aeronautics and Astronautics, Nanjing, Jiangsu, China Kuang Shen, Zhejiang University, Hangzhou, Zhejiang, China Dianguo Xu, Harbin Institute of Technology, Harbin, Heilongjiang, China Jianping Xu, Xinan Jiaotong University, Chengdu, Sichuan, China Mark Dehong Xu, Zhejiang University, Hangzhou, Zhejiang, China Xiaoming Zha, Wuhan University, Wuhan, Hubei, China Bo Zhang, South China University of Technology, Guangzhou, Guangdong, China Lei Zhang, China Power Supply Society, Tianjin, China Xin Zhang, Hefei University of Technology, Hefei, Anhui, China Zhengming Zhao, Tsinghua University, Beijing, China Qionglin Zheng, Beijing Jiaotong University, Beijing, China Luowei Zhou, Chongqing University, Chongqing, China

This series comprises advanced textbooks, research monographs, professional books, and reference works covering different aspects of power electronics, such as Variable Frequency Power Supply, DC Power Supply, Magnetic Technology, New Energy Power Conversion, Electromagnetic Compatibility as well as Wireless Power Transfer Technology and Equipment. The series features leading Chinese scholars and researchers and publishes authored books as well as edited compilations. It aims to provide critical reviews of important subjects in the field, publish new discoveries and significant progress that has been made in development of applications and the advancement of principles, theories and designs, and report cutting-edge research and relevant technologies. The CPSS Power Electronics series has an editorial board with members from the China Power Supply Society and a consulting editor from Springer.

Readership: Research scientists in universities, research institutions and the industry, graduate students, and senior undergraduates.

More information about this series at http://www.springer.com/series/15422

Deshang Sha · Guo Xu

# High-Frequency Isolated Bidirectional Dual Active Bridge DC–DC Converters with Wide Voltage Gain

Deshang Sha Advanced Power Conversion Center, School of Automation Beijing Institute of Technology Beijing China Guo Xu Advanced Power Conversion Center, School of Automation Beijing Institute of Technology Beijing China

ISSN 2520-8853

ISSN 2520-8861

(electronic)

CPSS Power Electronics Series

ISBN 978-981-13-0259-6

(eBook)

https://doi.org/10.1007/978-981-13-0259-6

ISBN 978-981-13-0259-6

(eBook)

Library of Congress Control Number: 2018939940

#### © Springer Nature Singapore Pte Ltd. 2019

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Printed on acid-free paper

This Springer imprint is published by the registered company Springer Nature Singapore Pte Ltd. part of Springer Nature

The registered company address is: 152 Beach Road, #21-01/04 Gateway East, Singapore 189721, Singapore

### Preface

Bidirectional DC–DC converters are widely used as power interfaces for many applications that need both changing and discharging of the energy storage components, such as batteries, super-capacitors. Among various types of bidirectional DC–DC converters, dual active bridge (DAB) converter has become popular and preferred topology during these years for its attractive advantages including symmetrical structure, zero-voltage switching, bidirectional power transfer capability, and high-power density.

This book presents different DAB converter topologies and power control strategies to achieve better power conversion performances for applications requiring both bidirectional power flow and galvanic isolation. The studied topologies can be used for applications needing a relatively wide voltage ranges such as energy storage system, automotive applications, solid-state transformer (SST)-based DC fast charger. The converter working principles, power transfer characteristics, converter losses are analyzed in this book. Based on that, the power control strategies are applied to achieve better performance aimed at different control goals. This book will benefit the researchers and engineers in the field of topology and control for dual active bridge isolated bidirectional DC–DC converters. The outcomes will enable effective development and high-quality mass production of novel high-performance DC–DC converters for the aforementioned bidirectional power applications. The main objectives are as follows,

- 1) To review and summarize the existed mainstream topologies and control methods for dual active bridge converters which are viewed as challenging research and application topic in the field of electrical engineering.

- 2) To develop new topologies for the applications that require wide voltage gain range due to the interfacing with the batteries. These applications include energy storage system, automotive applications, SST-based DC fast charger.

- To develop effective and simple control methods to achieve reduced current stress and wide ZVS ranges for the bidirectional dual active bridge DC-DC converters.

4) To present useful methodologies and philosophies to develop new topologies and controls for isolated bidirectional DC–DC converter to achieve wide voltage range.

This book consists of 12 Chapters based on our several research projects, and covering the aspects of converter topologies and power control strategies for DAB converters. Like most books, this book starts with an introduction in Chap. 1 to present a brief introduction focusing on the applications and classifications of bidirectional DC–DC converters, review of the control methods for dual active bridge control, and key issues of DAB converters. For the rest of the contents, from the topology point of view, this book can be divided into two parts. The first part is focused on topology and control for voltage fed dual active bridge converters which are from Chaps. 2 to 6, and the second part presents the topologies and controls for current-fed dual active bridge converters which are included from Chaps. 7 to 12. The detail organization of the book content is summarized in Chap. 1.

The authors wish to express their sincere thanks to Prof. Zhiqiang Guo, Beijing Institute of Technology for his contribution on the three-level DAB converter research and other contributions to this book. The author would also like to acknowledge the contributions of Mr. Yaxiong Xu and Dr. Jiankun Zhang on the voltage-type DAB converters, Dr. Xiao Wang, Mr. Deliang Chen, Mr. Lingyu Xu, Mr. Wenqi Yuan on the current-fed DAB converters.

The author would like to thank for the support from the National Natural Science Foundation of China under Grant 51577012, from State Key Laboratory of Alternate Electrical Power System with Renewable Energy Sources under Grant LATS17019, from Key Laboratory of Solar Thermal Energy and Photovoltaic System of Chinese Academy of Sciences.

The author would also like to thank their families who have given tremendous support all the time. Finally, the authors are extremely grateful to Springer and the editorial staff for the opportunity to publish this book and help in all possible manners.

Beijing, China

Deshang Sha Guo Xu

# Contents

| 1 | Intro | oduction |                                                 | 1  |

|---|-------|----------|-------------------------------------------------|----|

|   | 1.1   | Applic   | ation of Bidirectional DC–DC Converter          | 1  |

|   |       | 1.1.1    |                                                 |    |

|   |       |          | Smart Grid                                      | 2  |

|   |       | 1.1.2    | Automotive Applications                         | 3  |

|   |       | 1.1.3    | SST Application                                 | 4  |

|   | 1.2   | Classif  | ication of Bidirectional DC-DC Converter        | 5  |

|   |       | 1.2.1    | Non-isolated and Isolated DC-DC Converter       | 5  |

|   | 1.3   | Isolated | d Bidirectional DC–DC Converter                 | 7  |

|   |       | 1.3.1    | PWM Controlled, Frequency Controlled            |    |

|   |       |          | and Phase Shift Controlled Bidirectional DC-DC  |    |

|   |       |          | Converter                                       | 7  |

|   |       | 1.3.2    | Current-Fed DAB Converter                       | 9  |

|   |       | 1.3.3    | Multi-level DAB DC-DC Converter                 | 11 |

|   | 1.4   | Resear   | ch Literature of DAB Converters                 | 12 |

|   |       | 1.4.1    | Basic Principle of DAB Converters               | 12 |

|   |       | 1.4.2    | Control of Voltage-Fed DAB Converters           | 13 |

|   |       | 1.4.3    | Control of Current-Fed DAB Converters           | 15 |

|   | 1.5   | Key Is   | sues of DAB Converter                           | 16 |

|   |       | 1.5.1    | ZVS Range                                       | 16 |

|   |       | 1.5.2    | Non-active Power and Current Stress             | 16 |

|   |       | 1.5.3    | Wide Voltage Gain                               | 17 |

|   | 1.6   | Organi   | zation of the Book                              | 17 |

|   | Refe  | rences   |                                                 | 19 |

| 2 | Unifi | ied Boun | ndary Trapezoidal Modulation Control for Dual   |    |

|   | Activ |          | e DC–DC Converter                               | 25 |

|   | 2.1   |          | Duty Cycle Compensation and Magnetizing Current |    |

|   |       | -        | for DAB DC-DC Converter with Trapezoidal        |    |

|   |       | Modula   | ation                                           | 25 |

|   |       | 2.1.1    | Conventional Trapezoidal Modulation (TZM)             | 26    |

|---|-------|----------|-------------------------------------------------------|-------|

|   |       | 2.1.2    | ZVS Conditions for DAB Converter with                 |       |

|   |       |          | Conventional TZM Control                              | 27    |

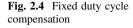

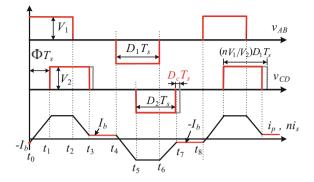

|   |       | 2.1.3    | Proposed Fixed Duty Cycle Compensation                | 29    |

|   |       | 2.1.4    | Magnetizing Current Design to Achieve ZVS             |       |

|   |       |          | for $S_7$ and $S_8$                                   | 31    |

|   | 2.2   | Power    | Transfer Characteristic and Selections of Duty Cycles |       |

|   |       | and Ph   | ase Shift Ratio                                       | 32    |

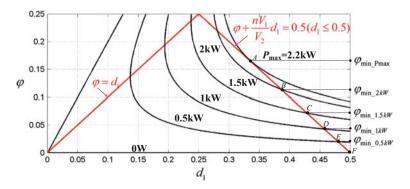

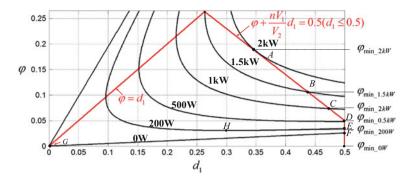

|   |       | 2.2.1    | Selections of Duty Cycles and Phase Shift Ratio for   |       |

|   |       |          | Minimum RMS Circulating Current                       | 33    |

|   |       | 2.2.2    | Maximum Power Transfer Point                          | 36    |

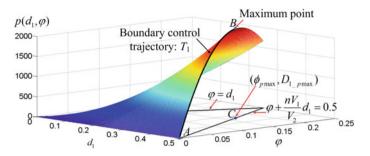

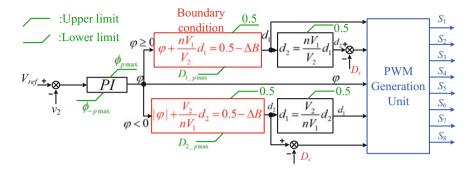

|   | 2.3   | Bound    | ary TZM Control and Its Implementation                | 37    |

|   |       | 2.3.1    | Boundary TZM Control                                  | 37    |

|   |       | 2.3.2    | Implementation of Boundary TZM Control                | 38    |

|   | 2.4   | 1        | mental Verification                                   | 39    |

|   | 2.5   | Conclu   | 1sion                                                 | 46    |

|   | Refer | ences.   |                                                       | 46    |

| 3 | Hvhr  | ·id-Brid | ge-Based DAB Converter with Wide Voltage              |       |

| • |       |          | Gain                                                  | 47    |

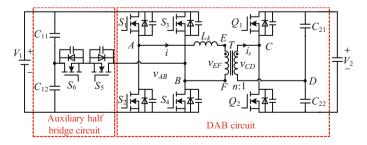

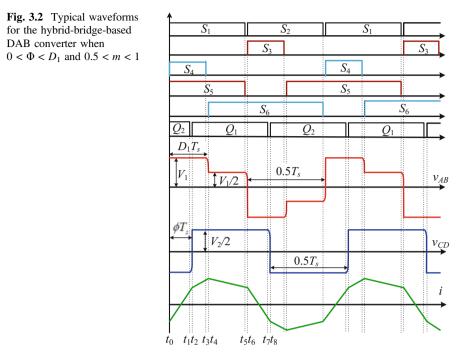

|   | 3.1   |          | ng Principle of Hybrid-Bridge-Based DAB Converter     | 47    |

|   | 5.1   | 3.1.1    | Topology and Modulation Scheme                        | • • • |

|   |       | 5.1.1    | for Hybrid-Bridge-Based DAB Converter                 | 48    |

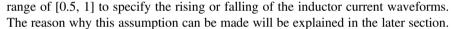

|   |       | 3.1.2    | Working Stages of the Converter                       | 50    |

|   | 3.2   |          | Conditions and Power Control                          | 52    |

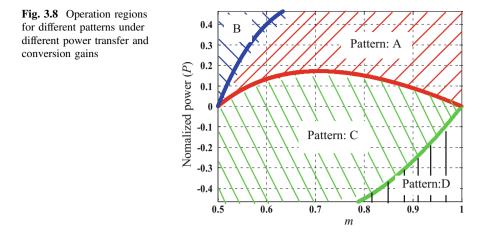

|   | 0.2   | 3.2.1    | Current Range for ZVS                                 | 52    |

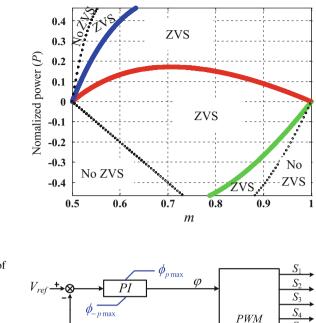

|   |       | 3.2.2    | Proposed VM Control to Ensure Wide ZVS Range          | 55    |

|   | 3.3   |          | rter Performance with Proposed Voltage                |       |

|   |       |          | Control                                               | 57    |

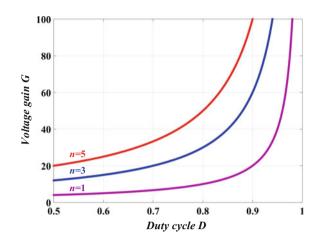

|   |       | 3.3.1    | Voltage Gain Under VM Control                         | 57    |

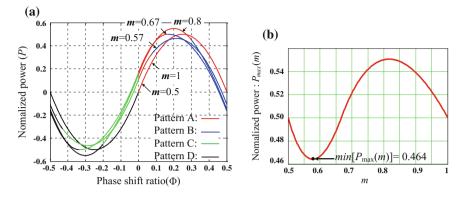

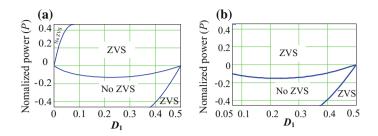

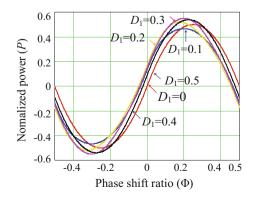

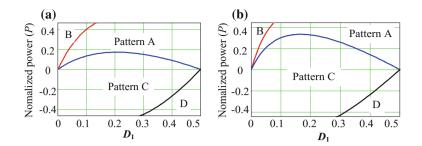

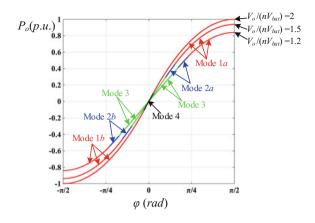

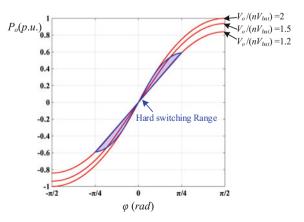

|   |       | 3.3.2    | Power Transfer Characteristics with VM Control        | 58    |

|   |       | 3.3.3    | Switches ZVS Discussion                               | 60    |

|   | 3.4   | Impler   | nentation of the Proposed Control                     | 60    |

|   | 3.5   |          | arison                                                | 61    |

|   |       | 3.5.1    | General Comparisons                                   | 61    |

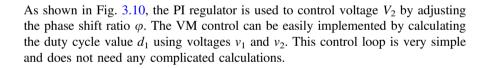

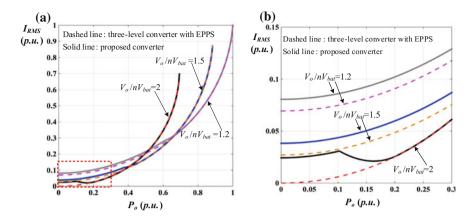

|   |       | 3.5.2    | Comparison of Inductor RMS Current and Total          |       |

|   |       |          | Conduction Loss                                       | 62    |

|   | 3.6   | Experi   | mental Verification                                   | 65    |

|   | 3.7   | Discus   | sion and Future Work                                  | 69    |

|   | 3.8   | Conclu   | ision                                                 | 69    |

|   | Refer | ences.   |                                                       | 70    |

| 4 | Dual  | Transformer-Based DAB Converter with Wide ZVS Range          |     |

|---|-------|--------------------------------------------------------------|-----|

|   | for V | Vide Voltage Gain Application                                | 71  |

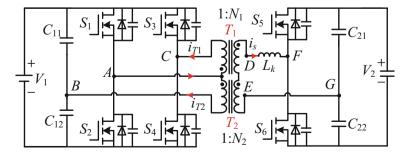

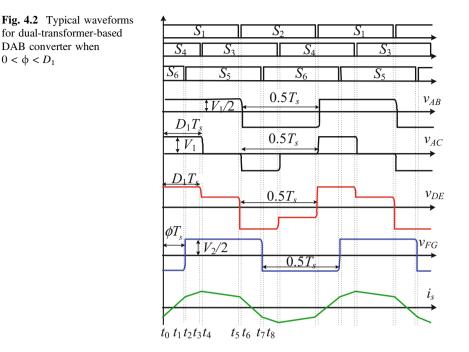

|   | 4.1   | Converter Topology and Operation Principle                   | 71  |

|   |       | 4.1.1 Topology and Modulation Schedule Using                 |     |

|   |       | Phase Shift Control                                          | 72  |

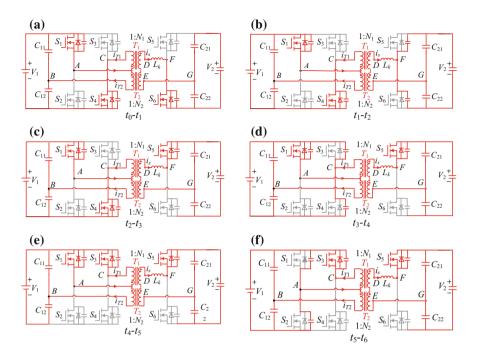

|   |       | 4.1.2 Working Stages of the Converter                        | 73  |

|   | 4.2   | ZVS Constraints and Control                                  | 75  |

|   |       | 4.2.1 Current Range for ZVS                                  | 75  |

|   |       | 4.2.2 Proposed Control Law to Achieve Full Range of ZVS      |     |

|   |       | for $S_1$ , $S_2$ , $S_5$ and $S_6$                          | 78  |

|   |       | 4.2.3 Transformer Turns Ratio Consideration and              |     |

|   |       | Extension of ZVS Range for S <sub>3</sub> and S <sub>4</sub> | 79  |

|   | 4.3   | Converter Characteristics with Proposed Control              | 80  |

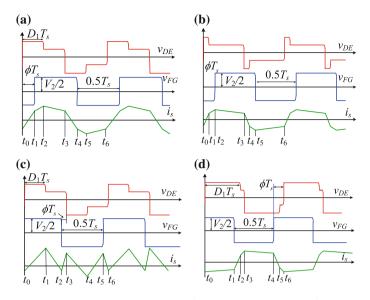

|   |       | 4.3.1 Power Characteristics Under Proposed Control           | 80  |

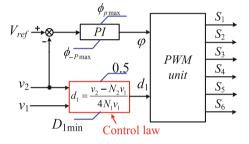

|   |       | 4.3.2 Implementation of the Proposed Control                 | 81  |

|   | 4.4   | Design Consideration and Comparison                          | 82  |

|   |       | 4.4.1 Leakage Inductance Design                              | 83  |

|   |       | 4.4.2 Turns Ratios                                           | 83  |

|   | 4.5   | Comparison                                                   | 85  |

|   |       | 4.5.1 Device RMS and Peak Current Comparison                 | 85  |

|   |       | 4.5.2 ZVS Range Comparison                                   | 86  |

|   |       | 4.5.3 Transformer Size Comparison                            | 86  |

|   | 4.6   | Experimental Verification                                    | 88  |

|   | 4.7   | Conclusion                                                   | 94  |

|   | Refe  | ences                                                        | 95  |

| 5 | Bloc  | ing-Cap-Based DAB Converters                                 | 97  |

|   | 5.1   | Topology of the Converter                                    | 97  |

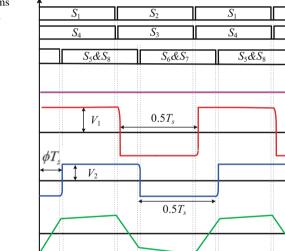

|   | 5.2   | Typical Waveforms of the Converter                           | 97  |

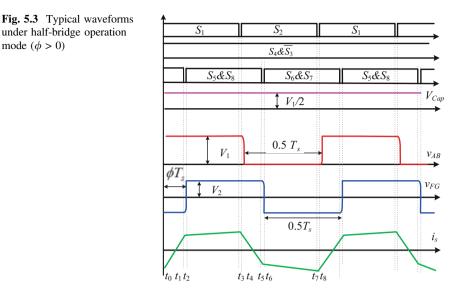

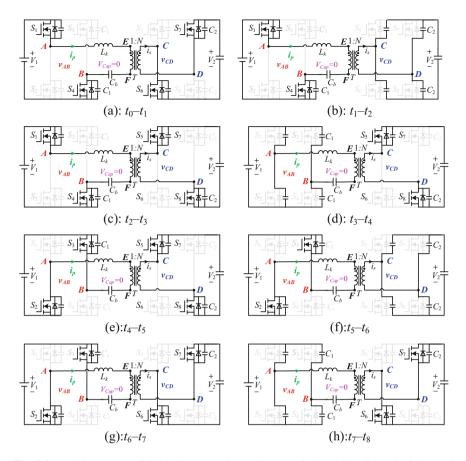

|   | 5.3   | Working Stages of the Converter                              | 99  |

|   |       | 5.3.1 Full-Bridge Operation Mode                             | 99  |

|   |       | 5.3.2 Half-Bridge Operation Mode                             | 101 |

|   | 5.4   | ZVS Conditions of the Converter.                             | 103 |

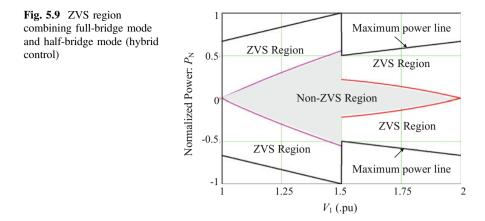

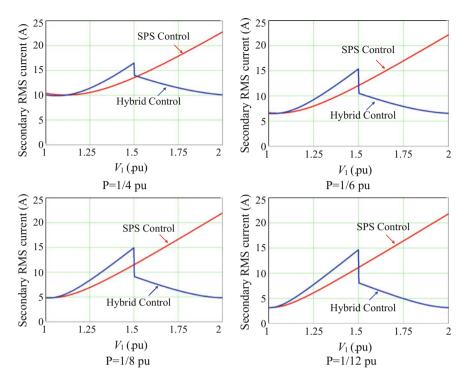

|   | 5.5   | Power Transfer Characteristic and ZVS Region                 |     |

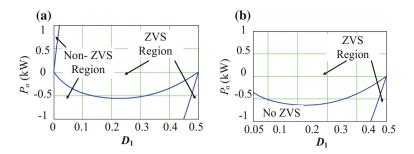

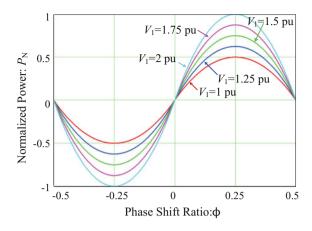

|   |       | 1                                                            | 105 |

|   |       |                                                              | 105 |

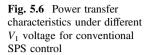

|   |       | 6                                                            | 107 |

|   |       |                                                              | 108 |

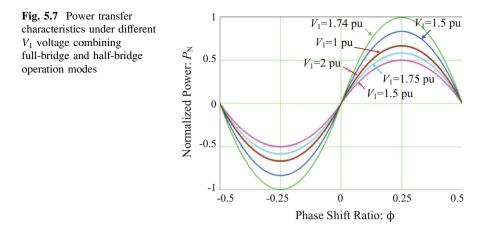

|   | 5.6   | 1                                                            | 109 |

|   |       |                                                              | 109 |

|   |       | e                                                            | 111 |

|   | 5.7   | ······································                       | 113 |

|   | Refe  | ences                                                        | 114 |

| 6 |       |         | Bidirectional DC–DC Converter with an Auxiliary   |     |

|---|-------|---------|---------------------------------------------------|-----|

|   |       |         | Adaptive Working Mode for Full-Operation          |     |

|   |       |         | Switching                                         | 115 |

|   | 6.1   |         | Level Bidirectional DAB Converter Full-Operation  | 115 |

|   |       |         | Voltage Switching.                                | 115 |

|   | 6.2   |         | eature and Modulation Scheme of the Converter     | 123 |

|   |       | 6.2.1   | Voltage Balance of the Flying Capacitor           | 123 |

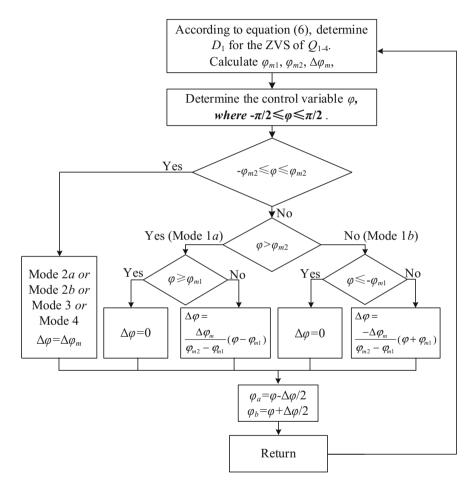

|   |       | 6.2.2   | ZVS Analyses for $Q_1 - Q_4$                      | 125 |

|   |       | 6.2.3   | ZVS Analyses for $Q_5-Q_8$                        | 126 |

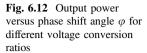

|   |       | 6.2.4   | Modulation Trajectory                             | 131 |

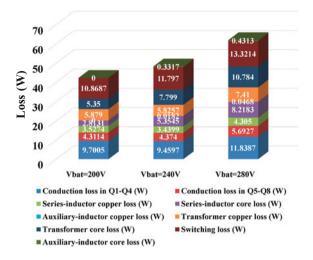

|   |       | 6.2.5   | Conduction Loss Comparison                        | 134 |

|   | 6.3   |         | mental Verifications                              | 136 |

|   | 6.4   | Conclu  | usion                                             | 144 |

|   | Refer | ences   |                                                   | 147 |

| 7 | A Cu  | rrent-F | ed Dual Active Bridge DC–DC Converter Using       |     |

|   | Dual  | PWM I   | Plus Double Phase Shifted Control                 | 149 |

|   | 7.1   | Introdu | ction to Current-Fed Dual Active Bridge           | 149 |

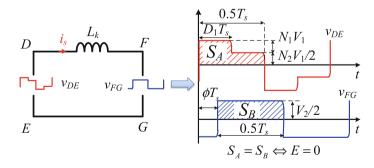

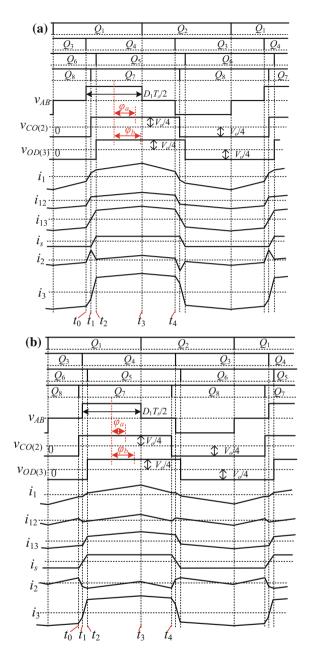

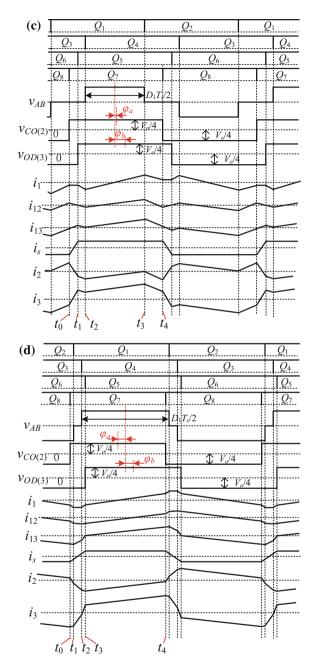

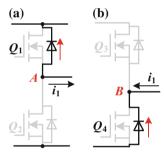

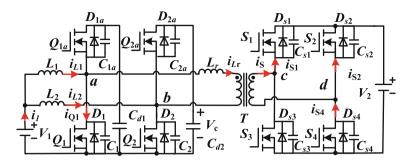

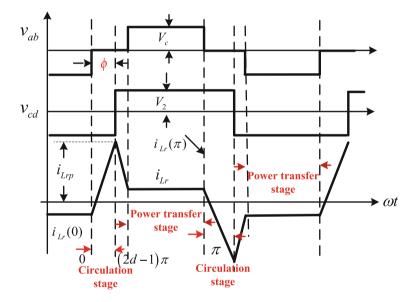

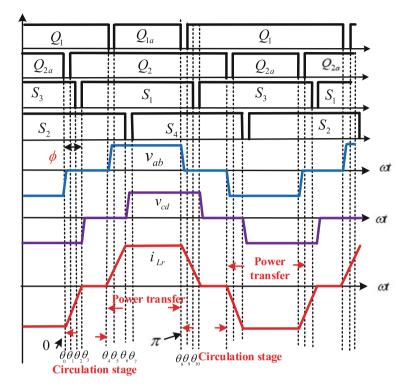

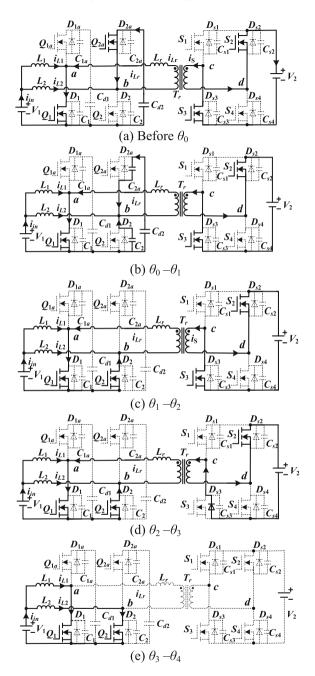

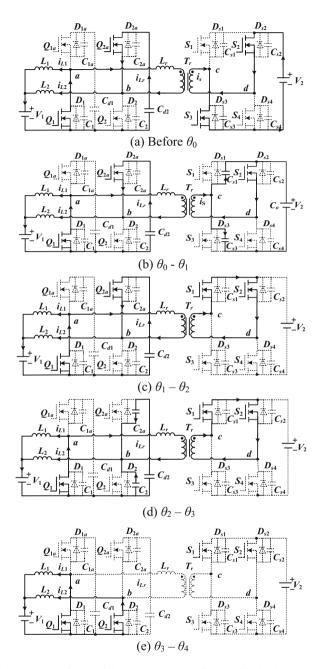

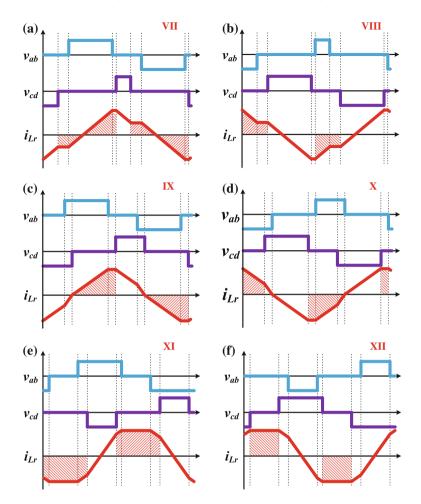

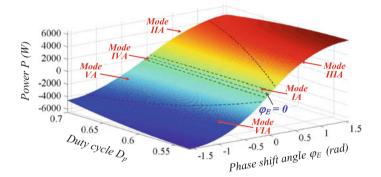

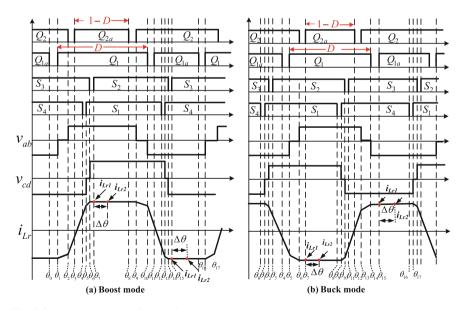

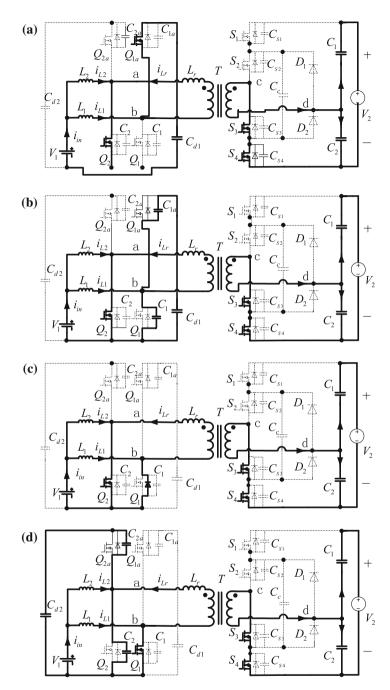

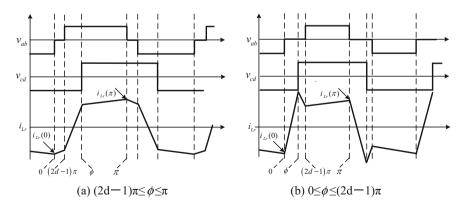

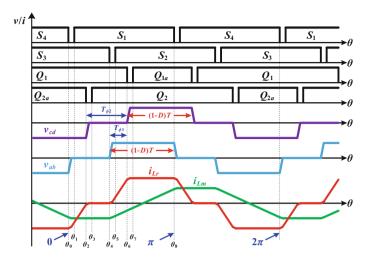

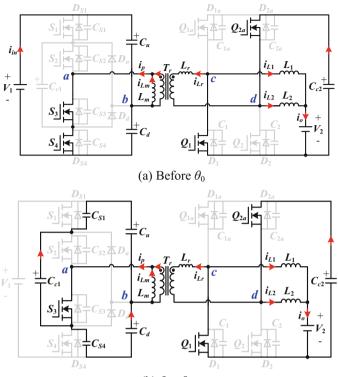

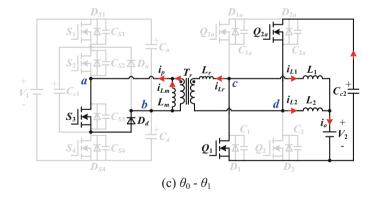

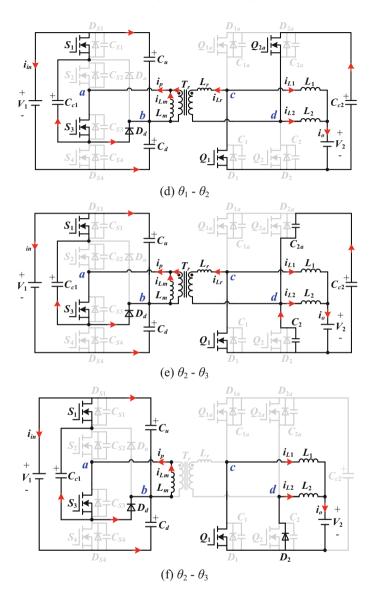

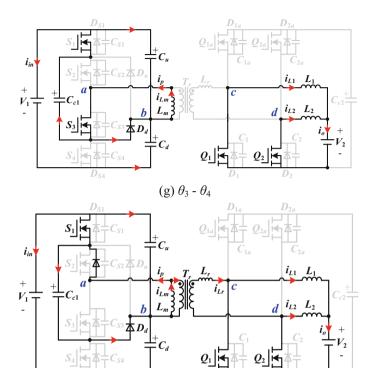

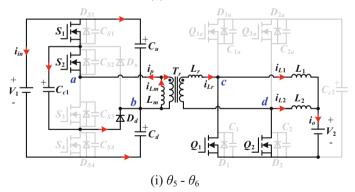

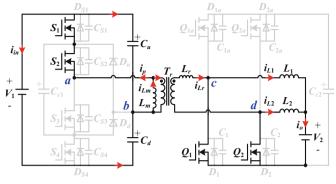

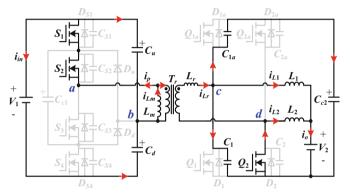

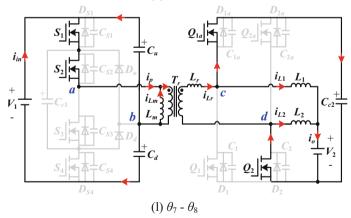

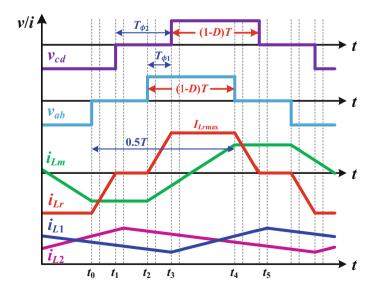

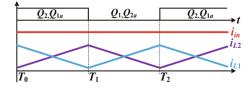

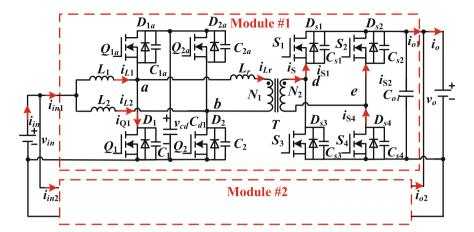

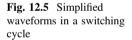

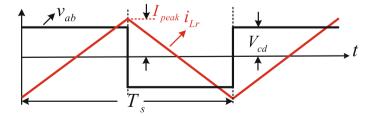

|   | 7.2   | Mode .  | Analysis with the Proposed Control Strategy       | 150 |

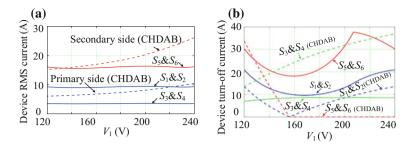

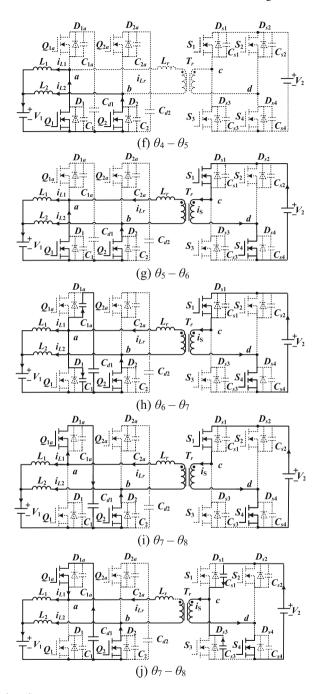

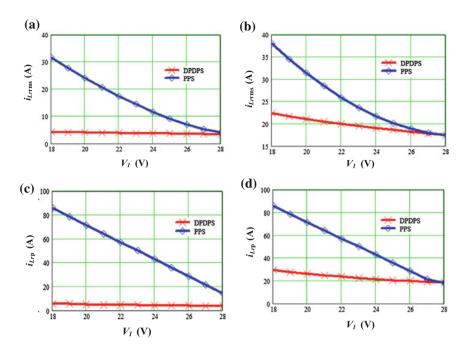

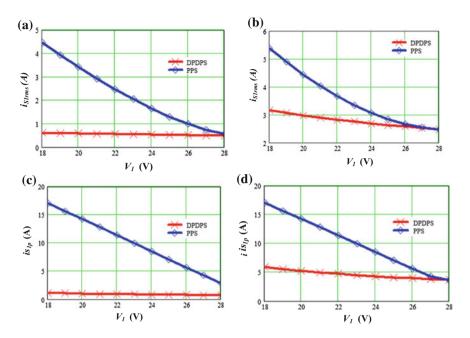

|   | 7.3   | Curren  | t Stress Comparison with PPS and DPDPS Control    | 156 |

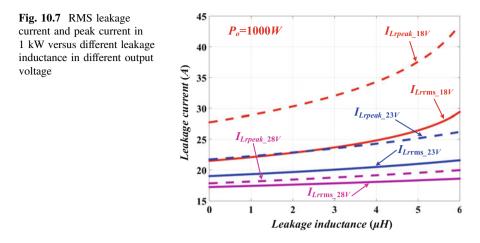

|   |       | 7.3.1   | Peak Current Analysis                             | 160 |

|   |       | 7.3.2   | RMS Current Analysis                              | 161 |

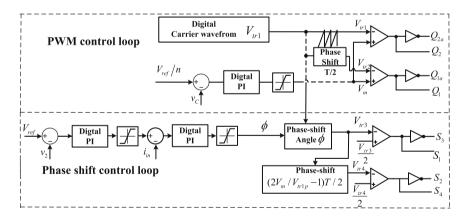

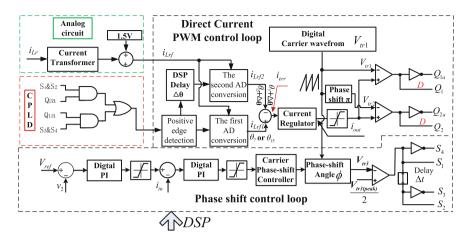

|   | 7.4   | Implen  | nentation of the Control Strategy                 | 161 |

|   | 7.5   |         | mental Results                                    | 162 |

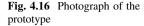

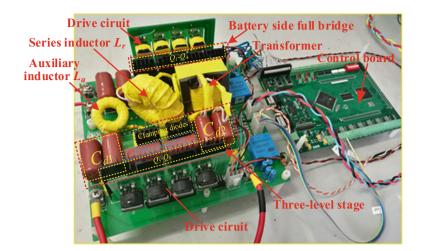

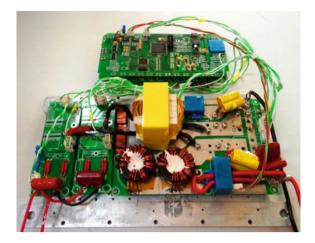

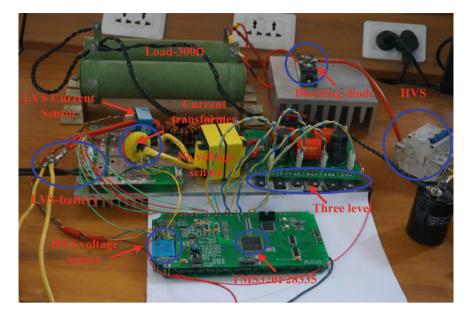

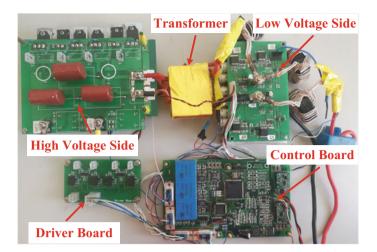

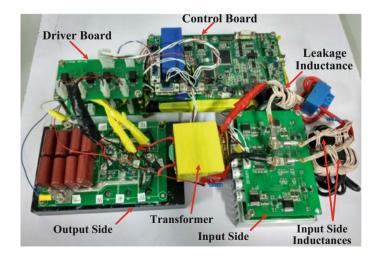

|   |       | 7.5.1   | Prototype                                         | 162 |

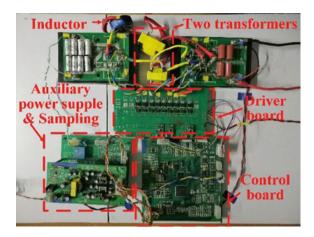

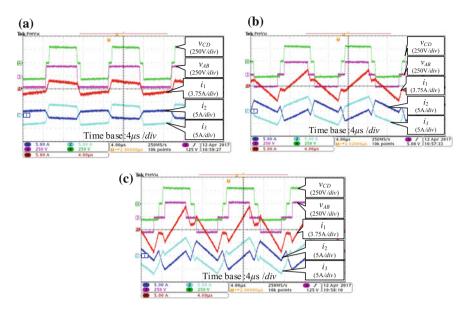

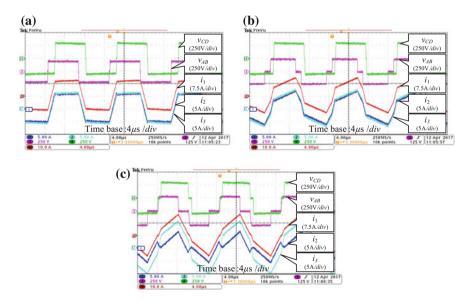

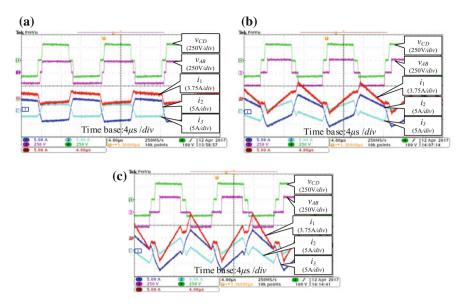

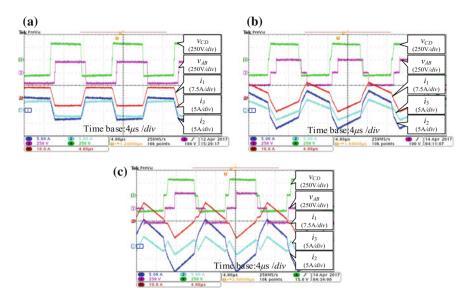

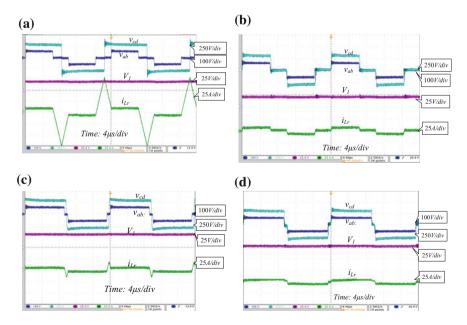

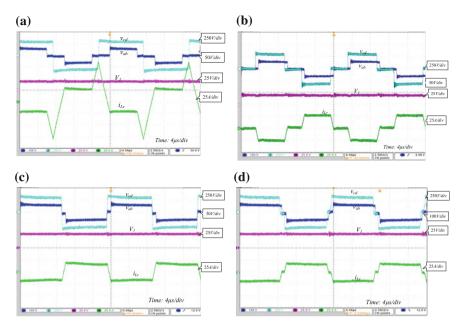

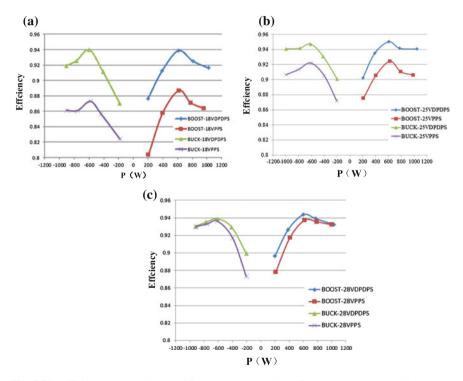

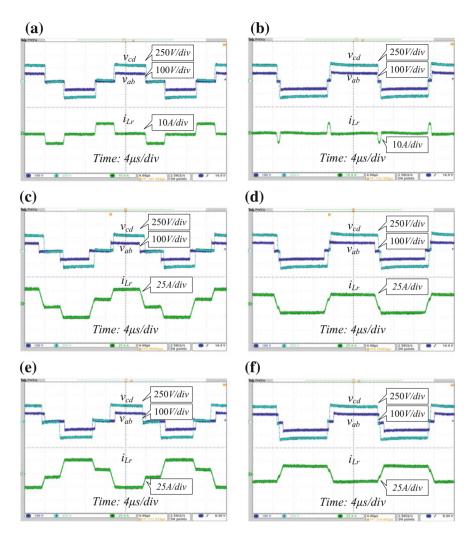

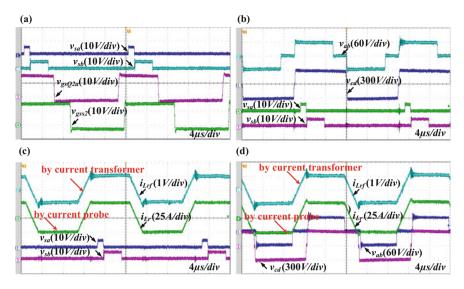

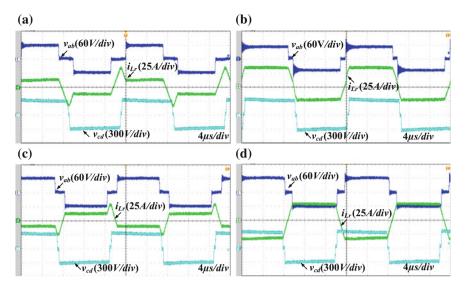

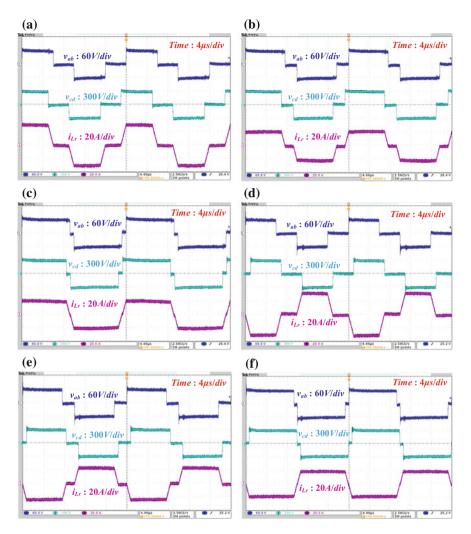

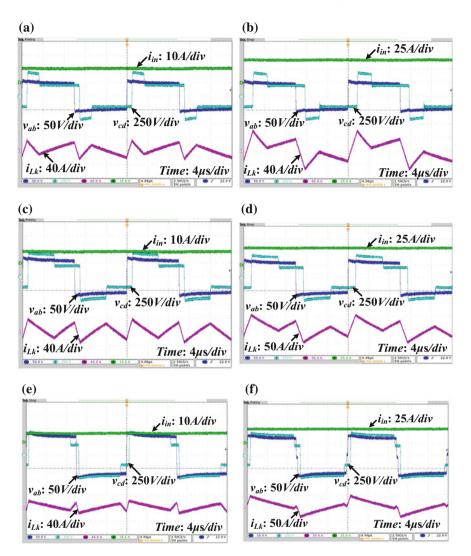

|   |       | 7.5.2   | Boost Mode Operation                              | 164 |

|   |       | 7.5.3   | Buck Mode Operation                               | 167 |

|   |       | 7.5.4   | Operation Mode Transition and Efficiency          |     |

|   |       |         | Comparison                                        | 168 |

|   | 7.6   | Conclu  | ision                                             | 171 |

|   | Refer | ences   |                                                   | 171 |

| 0 |       |         |                                                   |     |

| 8 |       |         | cy Current-Fed Dual Active Bridge DC-DC           |     |

|   |       |         | ith ZVS Achievement Throughout Full Range         | 170 |

|   |       |         | g Optimized Switching Patterns                    | 173 |

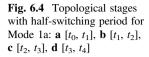

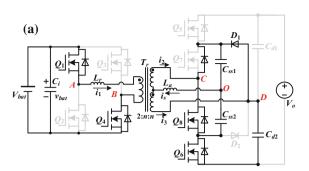

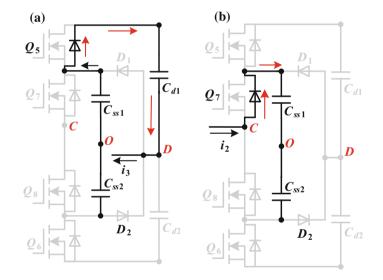

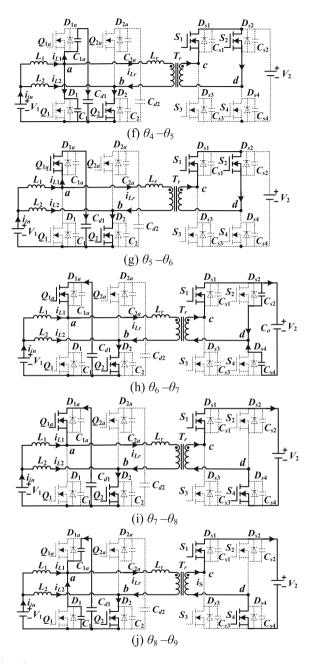

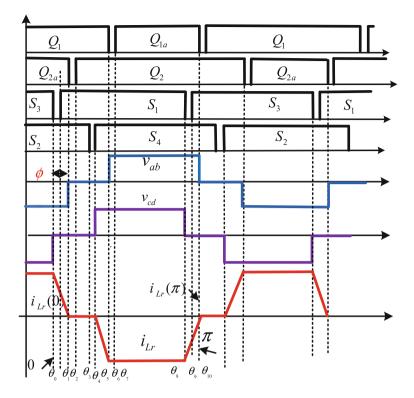

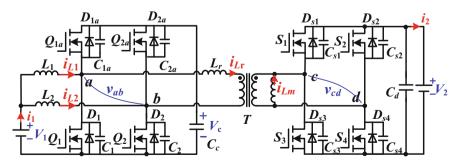

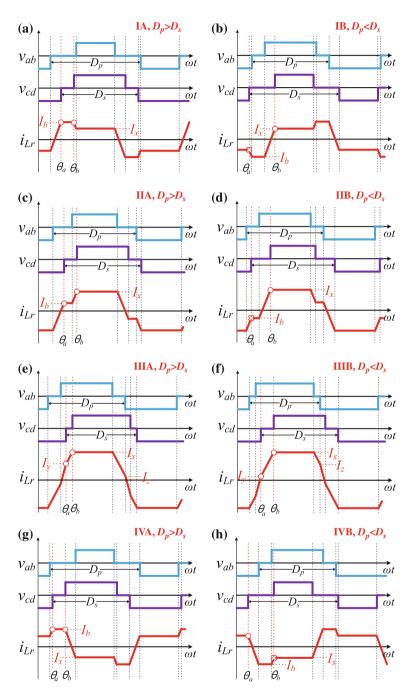

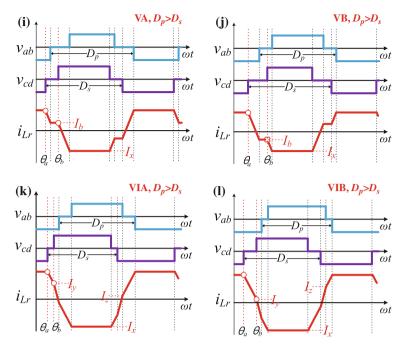

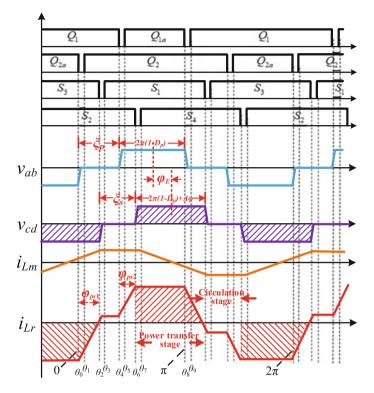

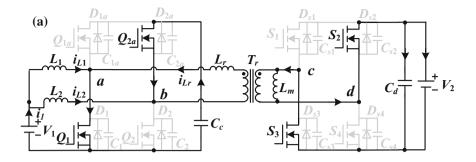

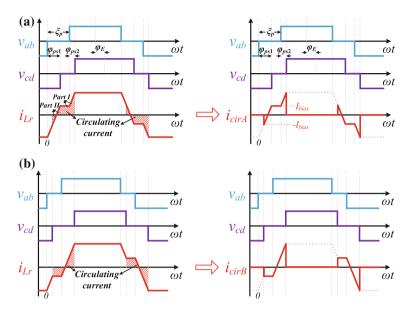

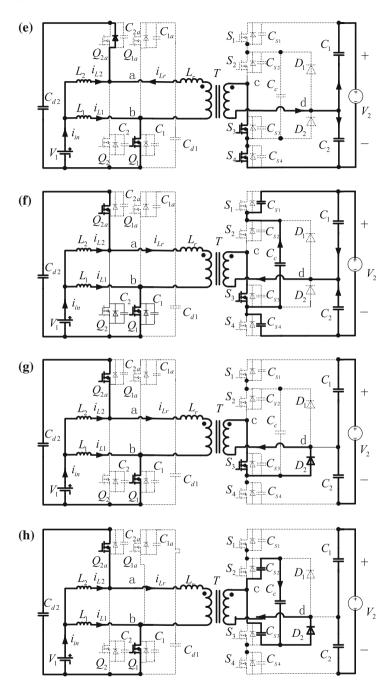

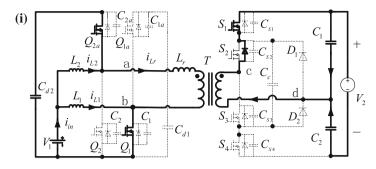

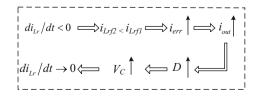

|   | 8.1   | -       | ion Principle of the Control                      | 173 |

|   |       | 8.1.1   | Topology of the Current-Fed DAB and the Operating | 174 |

|   |       | 0 1 0   | Modes with Voltage Matching Control               | 174 |

|   |       | 8.1.2   | Power Expressions of the Proposed Control         | 177 |

|   |       | 8.1.3   | Working Principle of the Proposed                 |     |

|   |       |         | Switching Pattern                                 | 179 |

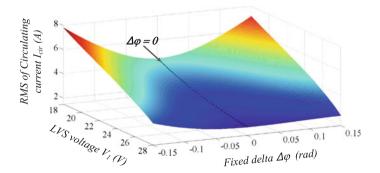

|   |       | 8.1.4   | Discussion of the Circulating Current             | 183 |

|    | 8.2   | Soft Sv   | vitching Condition                               | 186 |

|----|-------|-----------|--------------------------------------------------|-----|

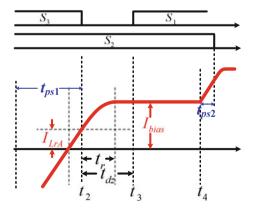

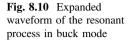

|    |       | 8.2.1     | Resonant Process Analysis                        | 186 |

|    |       | 8.2.2     | Soft Switching Condition                         | 188 |

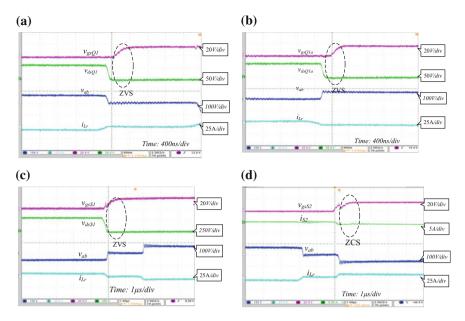

|    | 8.3   | Experir   | nental Results                                   | 190 |

|    |       | 8.3.1     | Prototype and Specifications                     | 190 |

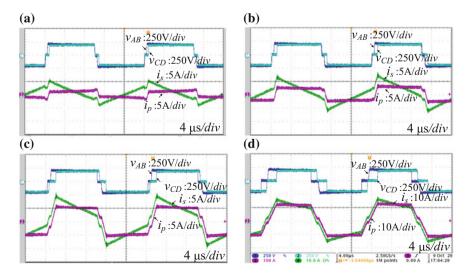

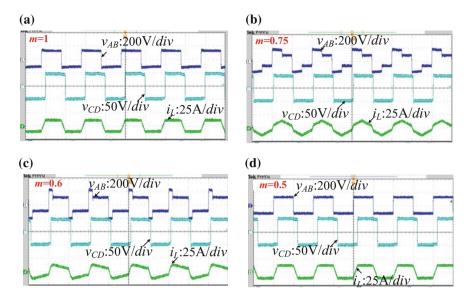

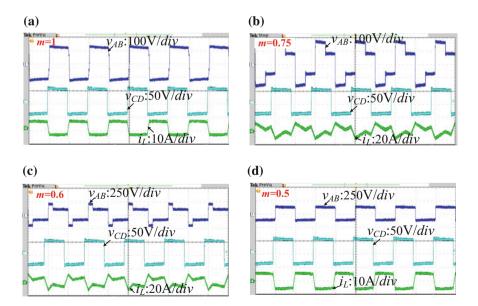

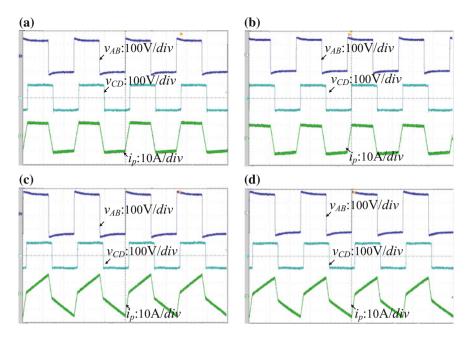

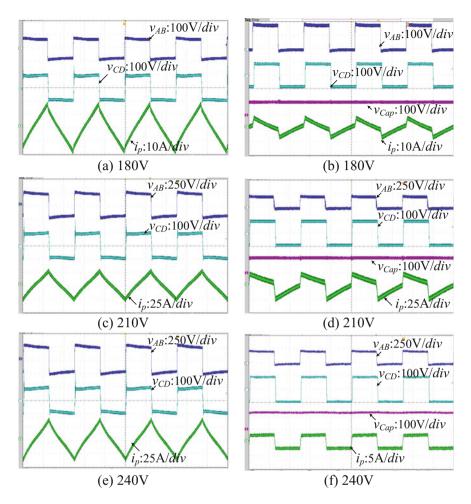

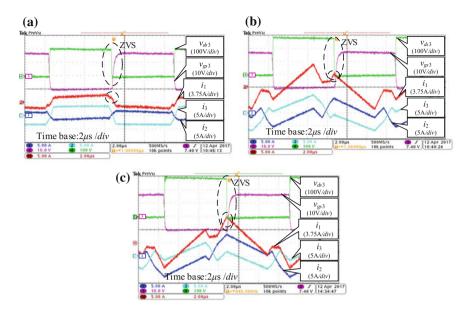

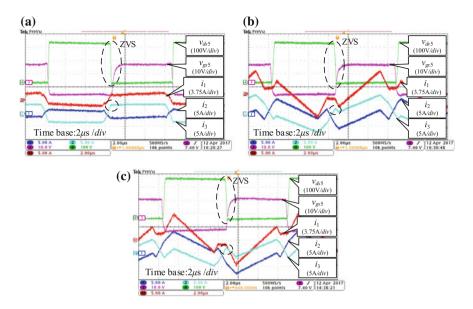

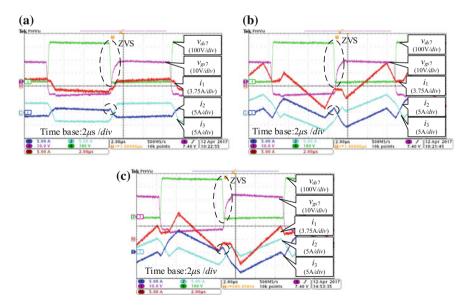

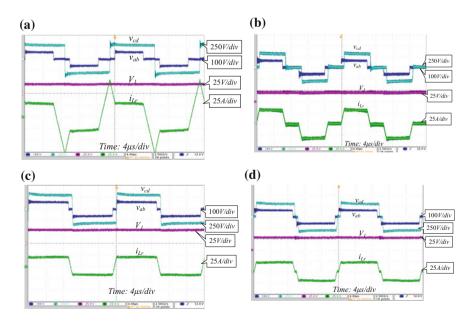

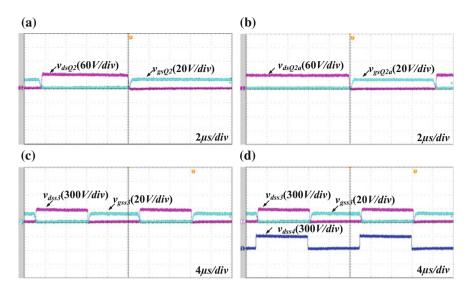

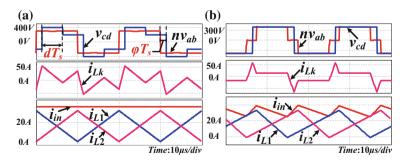

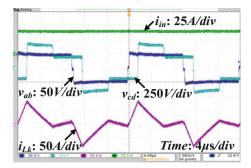

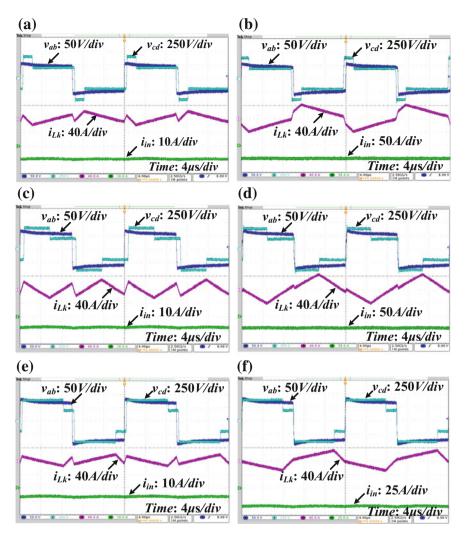

|    |       | 8.3.2     | Steady-State Operation                           | 190 |

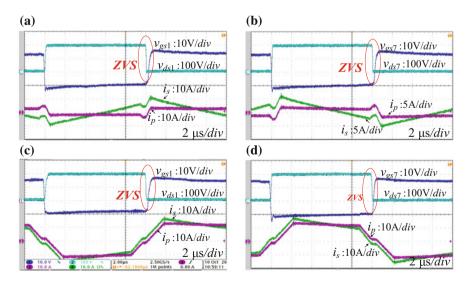

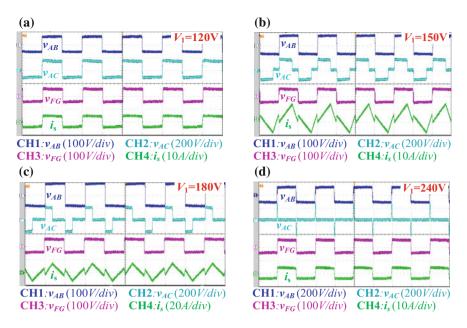

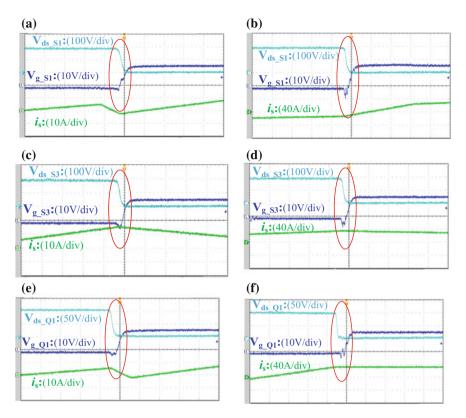

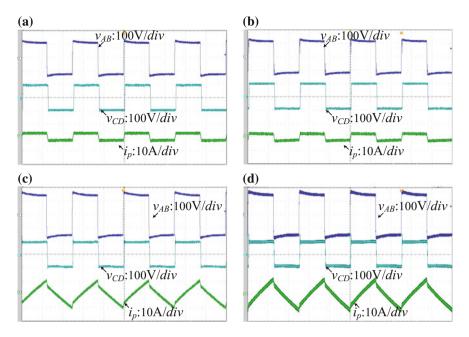

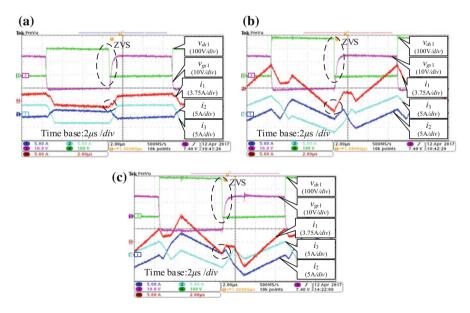

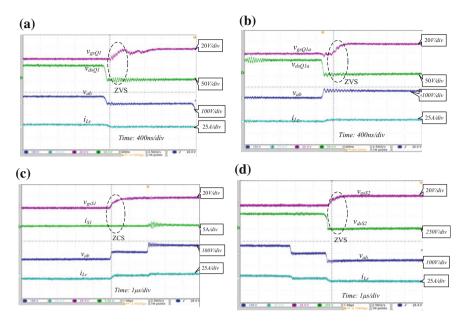

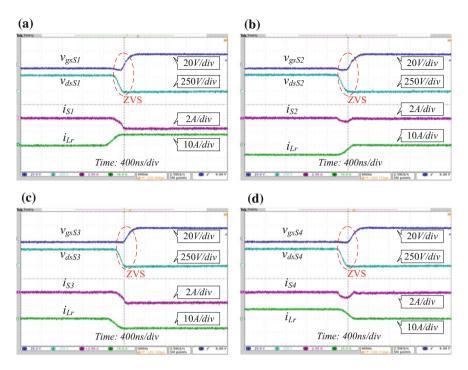

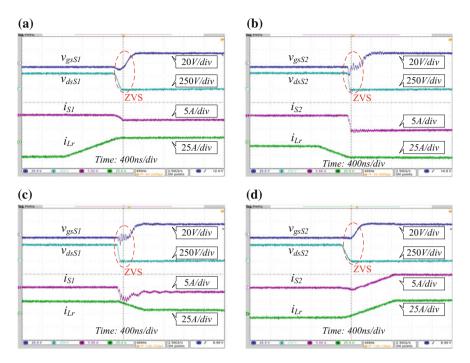

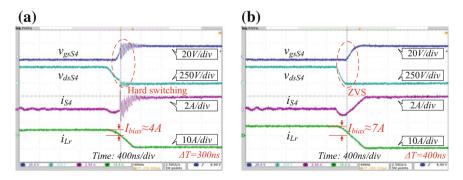

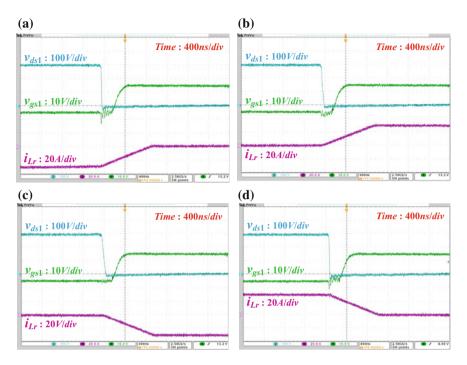

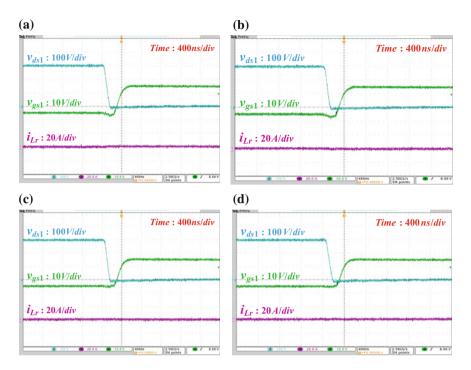

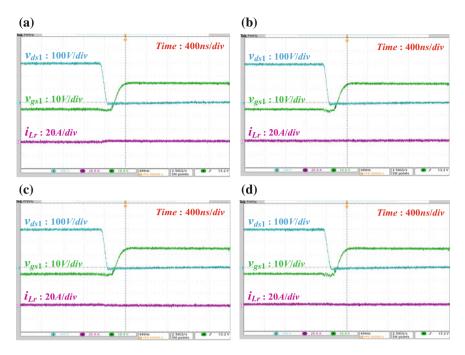

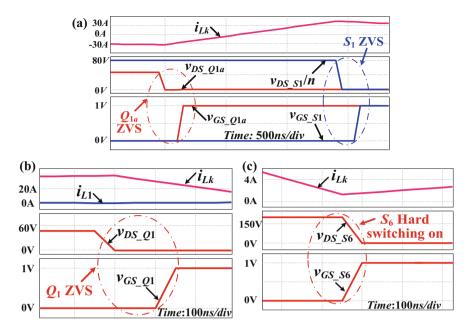

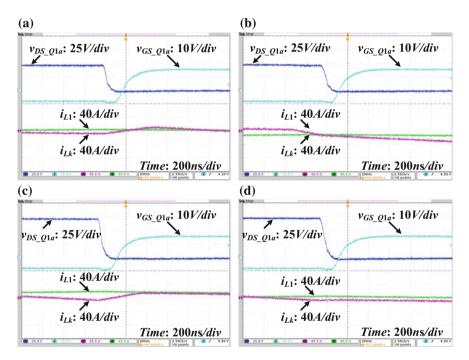

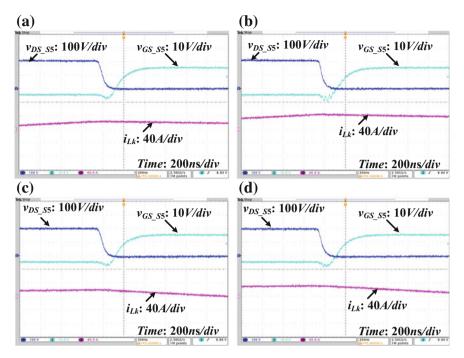

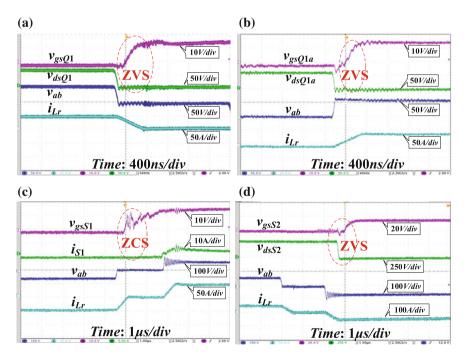

|    |       | 8.3.3     | Soft Switching Waveforms                         | 191 |

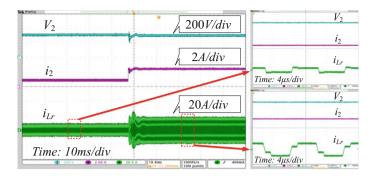

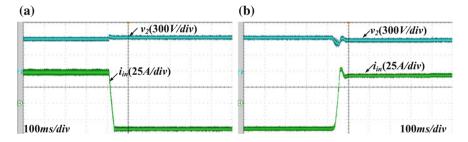

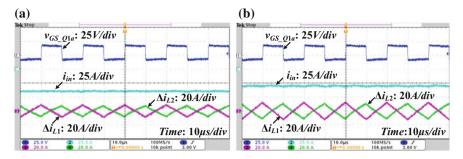

|    |       | 8.3.4     | Dynamical Operation                              | 193 |

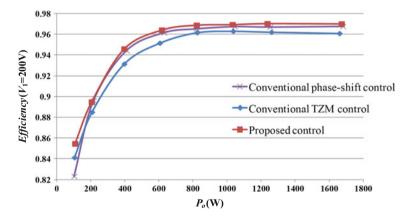

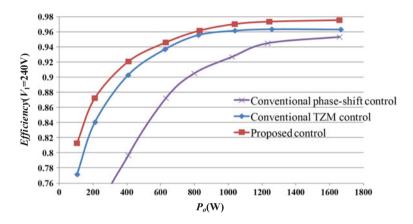

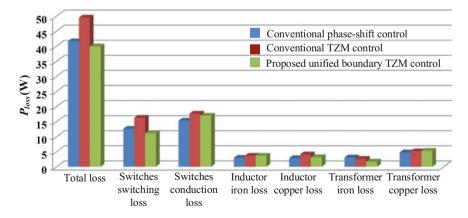

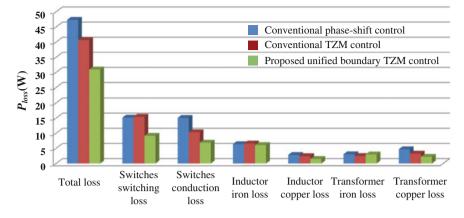

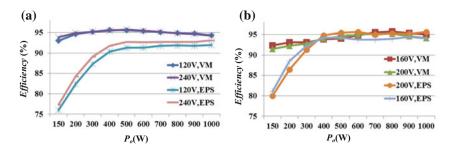

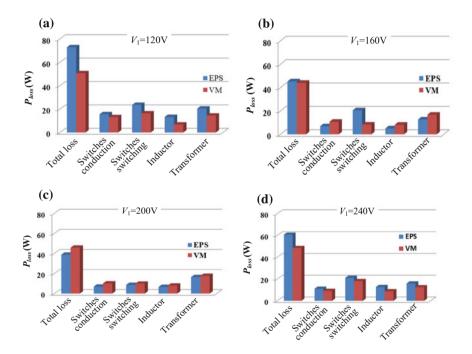

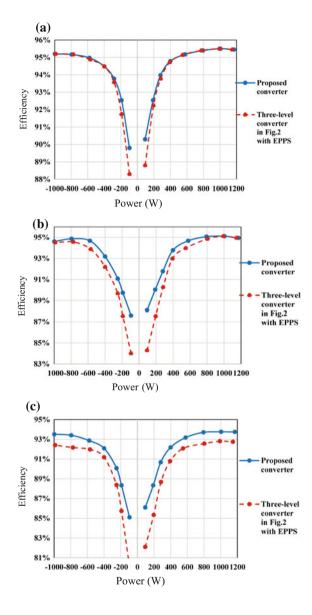

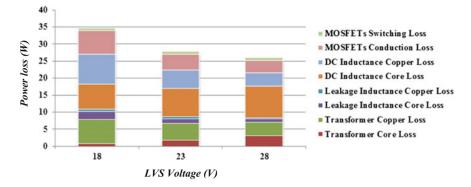

|    |       | 8.3.5     | Conversion Efficiency and Loss                   |     |

|    |       |           | Breakdown Analysis                               | 195 |

|    | 8.4   | Conclu    | sion                                             | 196 |

|    | Refer | ences     |                                                  | 196 |

| 9  | A ZV  | 'S Bidire | ectional Three-Level DC–DC Converter with Direct |     |

| -  |       |           | Rate Control of Leakage Inductance Current       | 199 |

|    | 9.1   |           | ction to Current-Fed Three-Level DAB Converter   | 199 |

|    | 9.2   |           | ed Bidirectional DC–DC Converter                 | 200 |

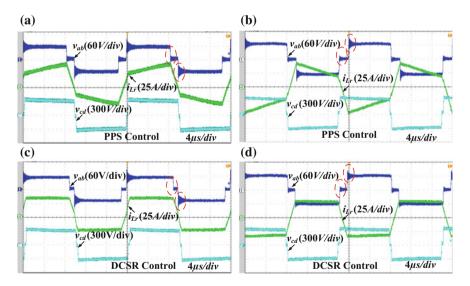

|    | 9.3   | -         | rison of PPS and DCSR Controls                   | 204 |

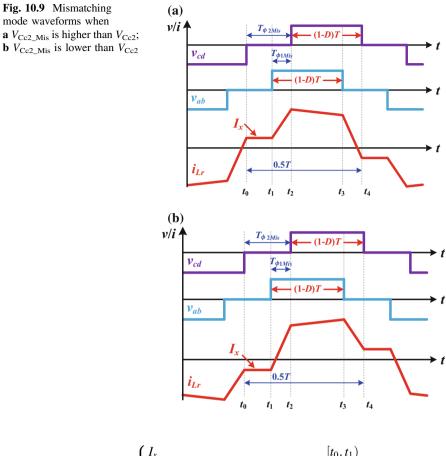

|    |       | 9.3.1     | Physical Turns Ratio Mismatch Considerations     | 204 |

|    |       | 9.3.2     | Actual Equivalent Circuit                        | 207 |

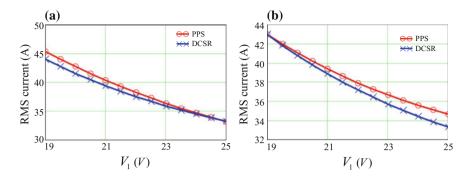

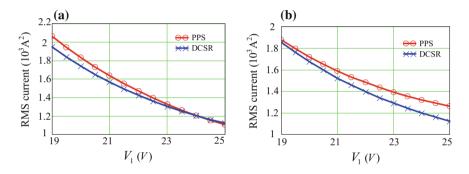

|    |       | 9.3.3     | RMS Current Comparison                           | 209 |

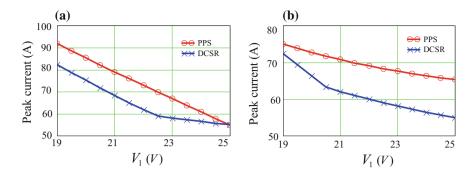

|    |       | 9.3.4     | The Peak Current of Main Switches                | 211 |

|    | 9.4   | Implem    | entation of the DCSR Control                     | 212 |

|    |       | 9.4.1     | Voltage Balance Issue for the Three-Level HVS    | 212 |

|    |       | 9.4.2     | Implementation of the Proposed Control Strategy  | 212 |

|    | 9.5   | Experin   | nental Results                                   | 214 |

|    | 9.6   | Conclu    | sion                                             | 221 |

|    | Refer | ences     |                                                  | 222 |

| 10 | A Bid | lirection | al Three-Level DC–DC Converter with Reduced      |     |

| 10 |       |           | oss and Fully ZVS Achievement for Battery        |     |

|    |       | 0         | charging                                         | 223 |

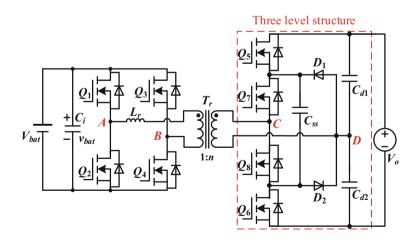

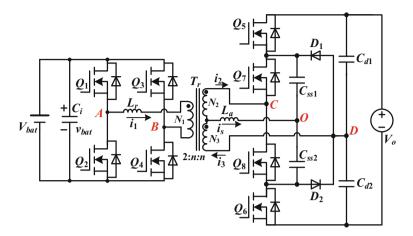

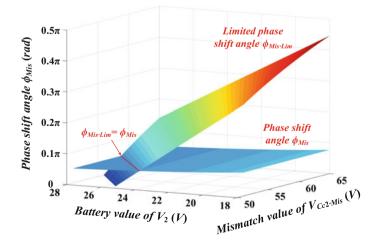

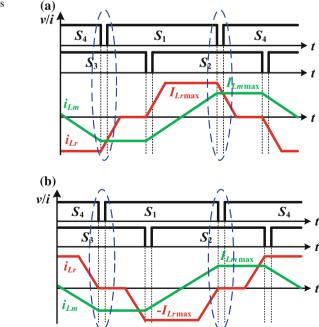

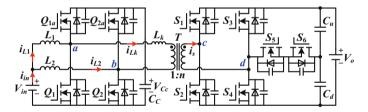

|    | 10.1  |           | ter Mode Analysis with Proposed Control Strategy | 223 |

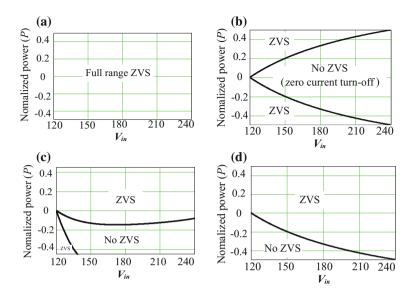

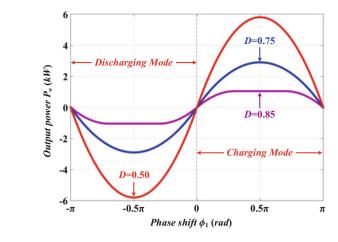

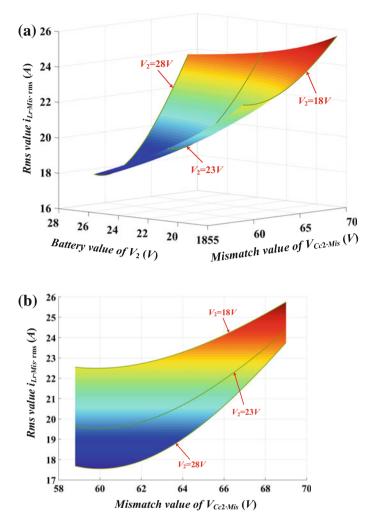

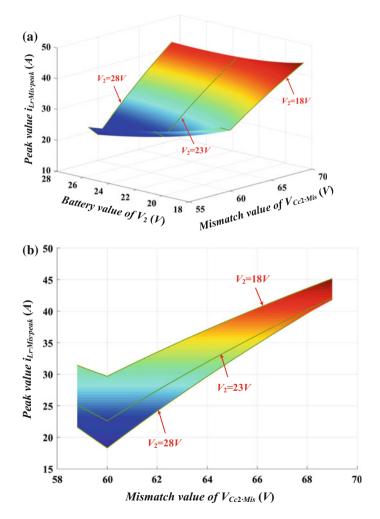

|    | 10.2  |           | nance Analysis and Discussion                    | 230 |

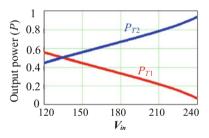

|    |       | 10.2.1    | Derivation of System Output Power                | 230 |

|    |       | 10.2.2    | Clamp Voltage and Voltage Gain of Converter      | 232 |

|    |       | 10.2.3    | Design Considerations                            | 233 |

|    |       | 10.2.4    | Comparison of Voltage Matching Mode and          |     |

|    |       |           | Mismatching Mode.                                | 236 |

|    |       | 10.2.5    | Soft-Switching Condition                         | 241 |

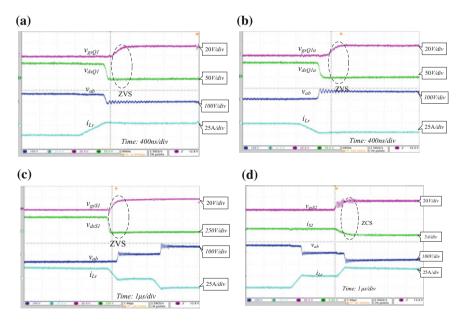

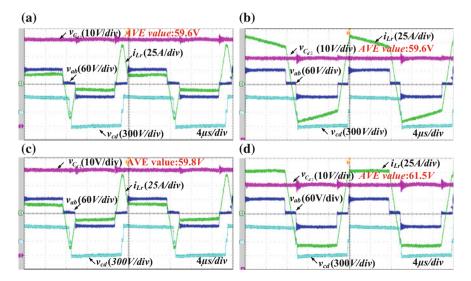

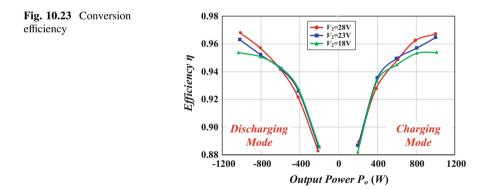

|    | 10.3  |           | nental Results                                   | 245 |

|    |       | 10.3.1    | Prototype                                        | 245 |

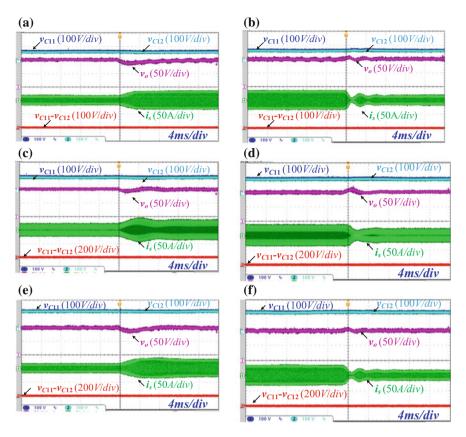

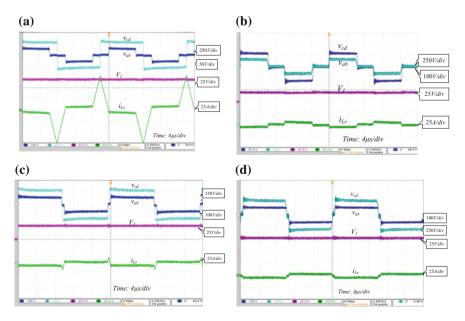

|    |       | 10.3.2    | Operation Waveforms of Charging Mode and         |     |

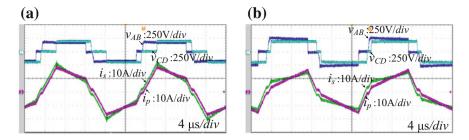

|    |       |           | Discharging Mode                                 | 245 |

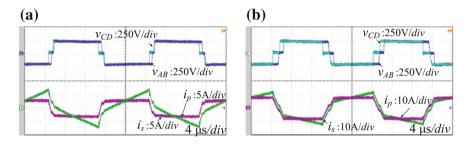

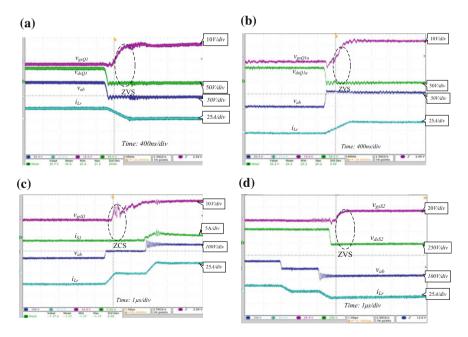

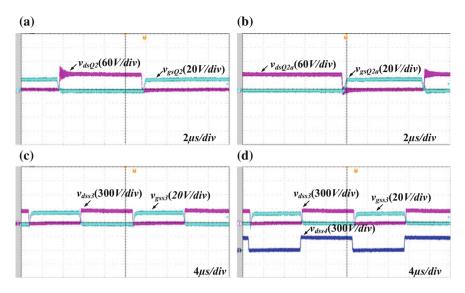

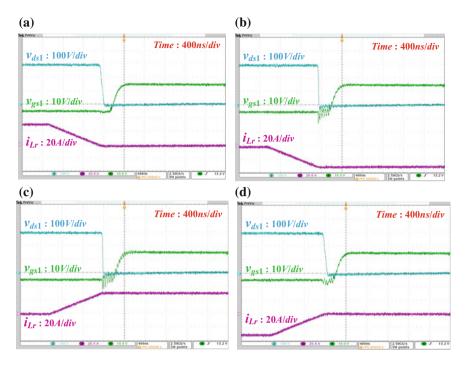

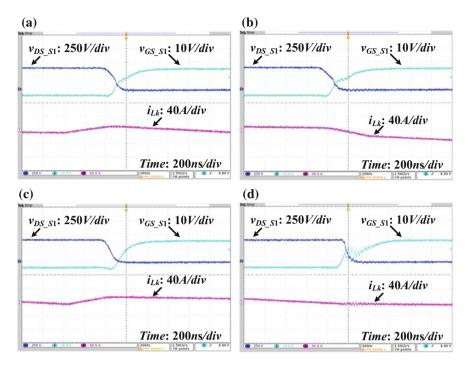

|    |       | 10.3.3  | Soft-Switching Waveforms of Discharging Mode and Charging Mode                               | 246        |

|----|-------|---------|----------------------------------------------------------------------------------------------|------------|

|    | 10.4  | Conclu  | sion                                                                                         | 240<br>251 |

|    |       |         |                                                                                              | 251        |

|    |       |         |                                                                                              | 252        |

| 11 |       |         | ed Hybrid Dual Active Bridge DC–DC Converter<br>Power Conditioning System with Reduced Input |            |

|    |       |         | ble                                                                                          | 253        |

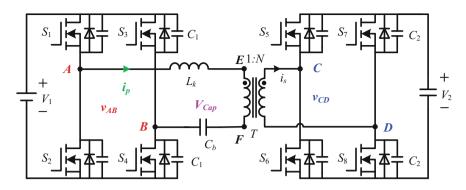

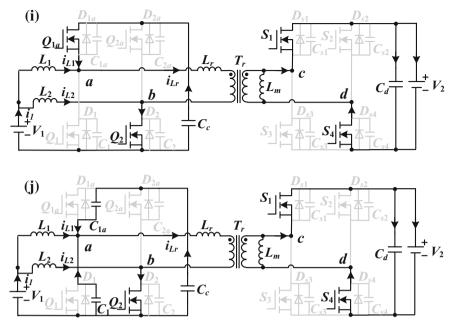

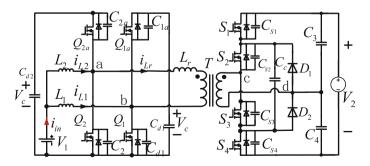

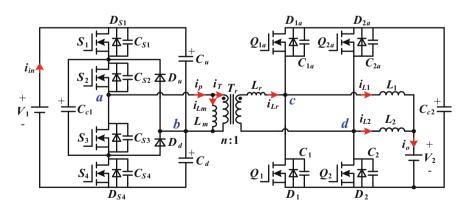

|    | 11.1  |         | ter Topology and Operating Principles                                                        | 253        |

|    |       | 11.1.1  | Proposed Converter                                                                           | 254        |

|    |       | 11.1.2  | Modulation Strategy                                                                          | 254        |

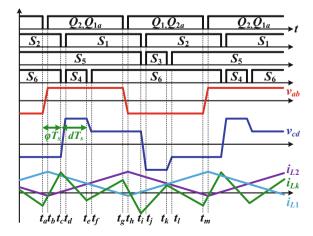

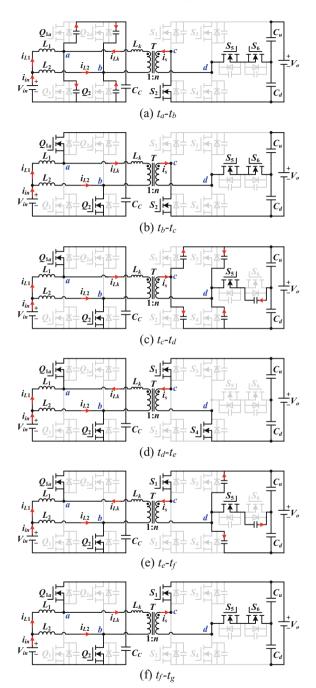

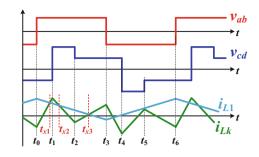

|    |       | 11.1.3  | Typical Operating Periods                                                                    | 255        |

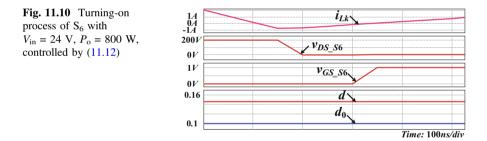

|    | 11.2  | ZVS C   | onditions and Control Strategy                                                               | 257        |

|    |       | 11.2.1  | ZVS Conditions                                                                               | 257        |

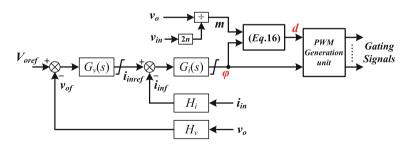

|    |       | 11.2.2  | Control Strategy                                                                             | 258        |

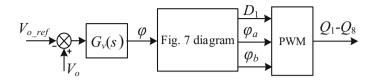

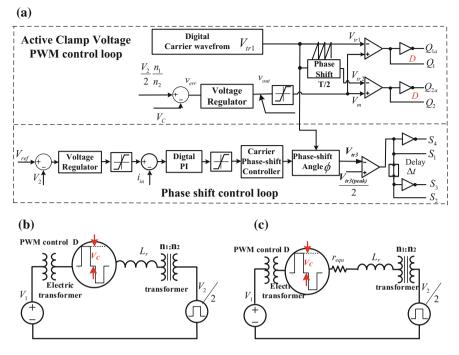

|    |       | 11.2.3  | Control Diagram Implementation                                                               | 260        |

|    | 11.3  | Charact | teristic Analysis and Parameter Design                                                       | 261        |

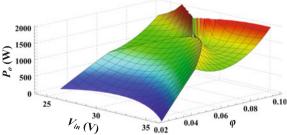

|    |       | 11.3.1  | Power Transfer Characteristics                                                               | 261        |

|    |       | 11.3.2  | Input Inductance Design                                                                      | 262        |

|    |       | 11.3.3  | Clamping Capacitor Design                                                                    | 263        |

|    |       | 11.3.4  | High-Frequency Current Ripple Analysis                                                       | 264        |

|    | 11.4  | Simulat | tion Results                                                                                 | 265        |

|    | 11.5  | Experin | nental Results                                                                               | 267        |

|    |       | 11.5.1  | Prototype                                                                                    | 267        |

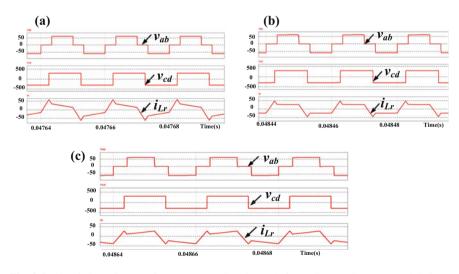

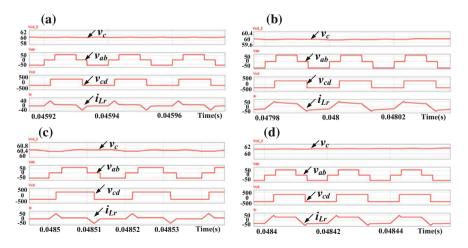

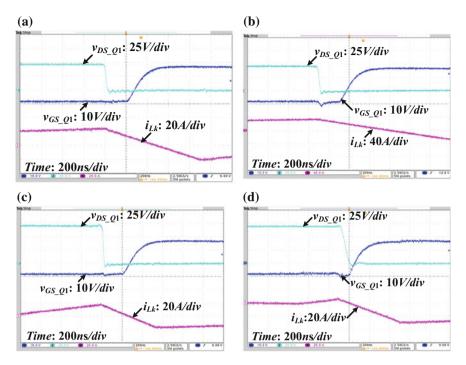

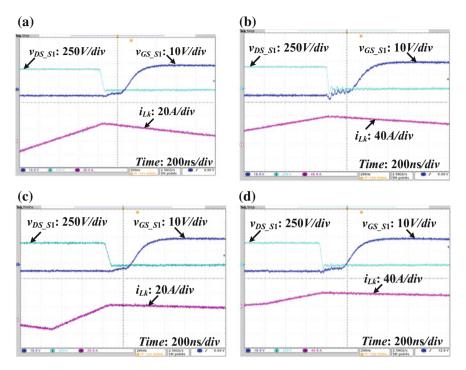

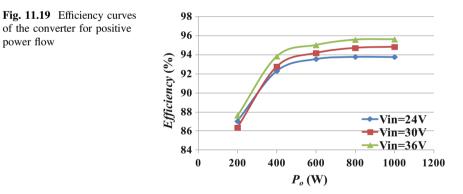

|    |       | 11.5.2  | Experimental Waveforms for Positive Power Flow                                               | 267        |

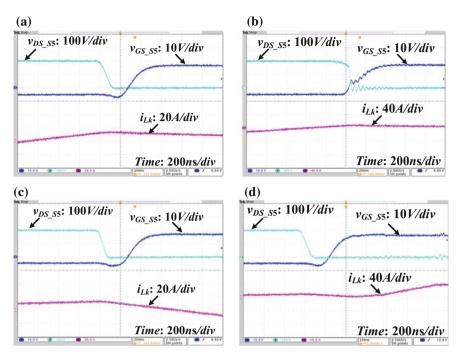

|    |       | 11.5.3  | Experimental Waveforms for Negative                                                          |            |

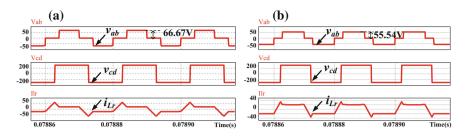

|    |       |         | Power Flow                                                                                   | 272        |

|    | 11.6  | Conclu  | sion                                                                                         | 277        |

|    | Refer | ences   |                                                                                              | 278        |

| 12 | Dvna  | mic Res | ponse Improvements of Parallel-Connected                                                     |            |

|    |       |         | DC–DC Converters                                                                             | 279        |

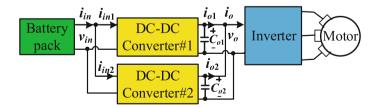

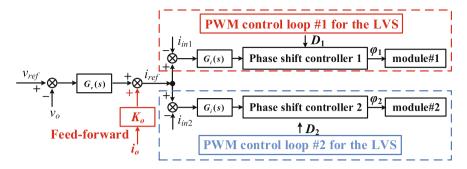

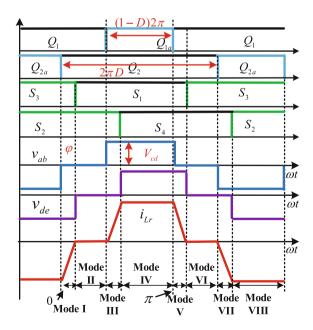

|    | 12.1  |         | ive System Overview and DPDPS Control                                                        | 279        |

|    | 12.2  |         | -Sharing and Small-Signal Modeling                                                           | 282        |

|    |       | 12.2.1  | Implementation of the Current Sharing                                                        | 282        |

|    |       | 12.2.2  | Small-Signal Modeling                                                                        | 283        |

|    |       | 12.2.3  | Analysis of the Current Sharing                                                              | 286        |

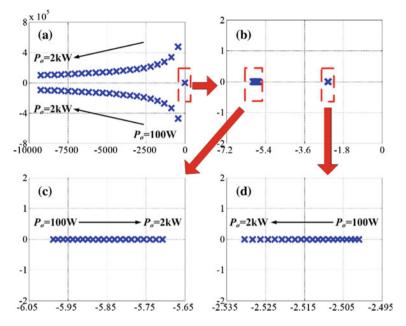

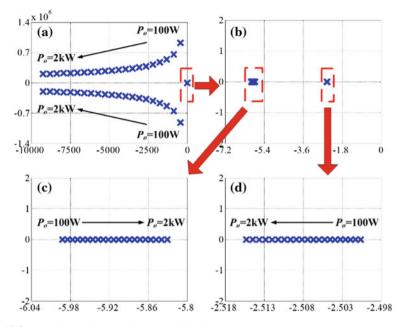

|    |       | 12.2.4  | System Stability Analysis                                                                    | 287        |

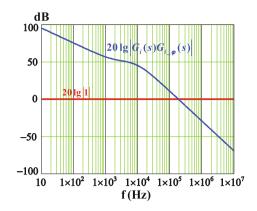

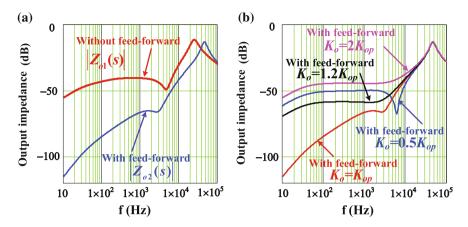

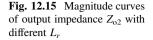

|    | 12.3  | Feed-Fe | orward Effect on the Dynamic Performance                                                     | 289        |

|    |       | 12.3.1  | Design of the Feed-Forward Coefficient K <sub>o</sub>                                        | 289        |

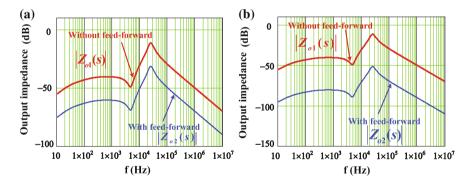

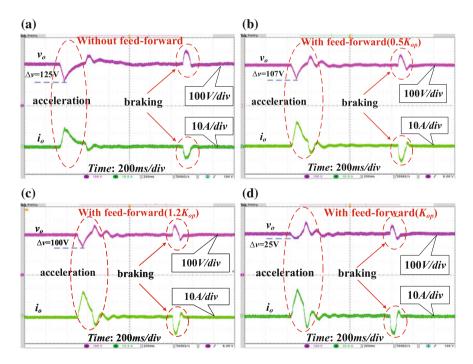

|    |       | 12.3.2  | Feed-Forward Effect on the Dynamic Performance                                               | 291        |

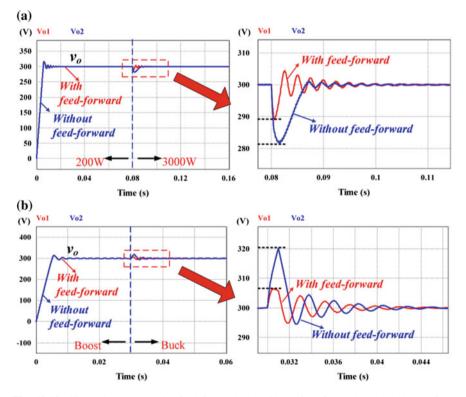

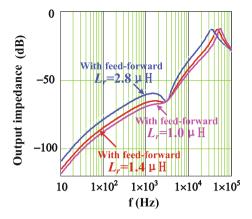

|    |       | 12.3.3  | Simulation Verification                                                                      | 291        |

|    | 12.4  | Leakag  | e Inductance Effect on the Steady State and Dynamic                                          |            |

|    |       |         | nance                                                                                        | 293        |

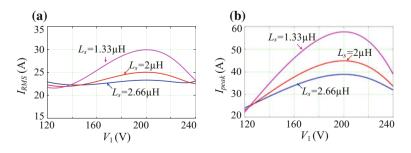

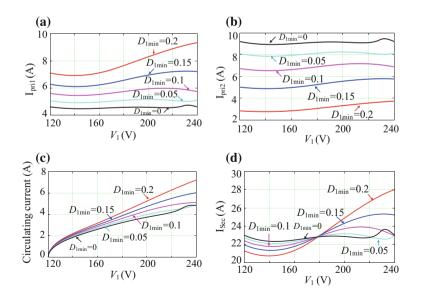

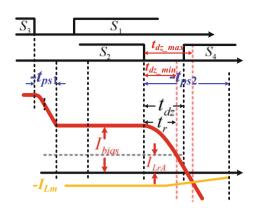

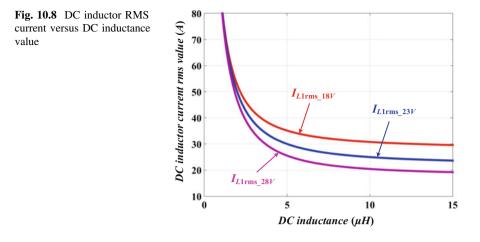

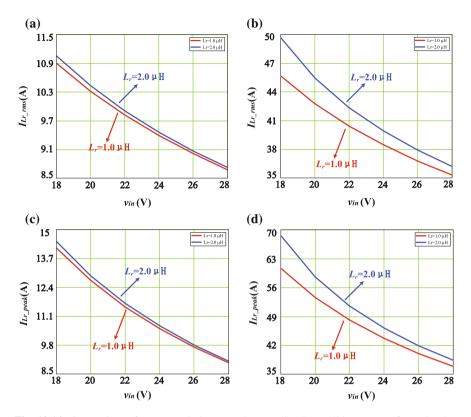

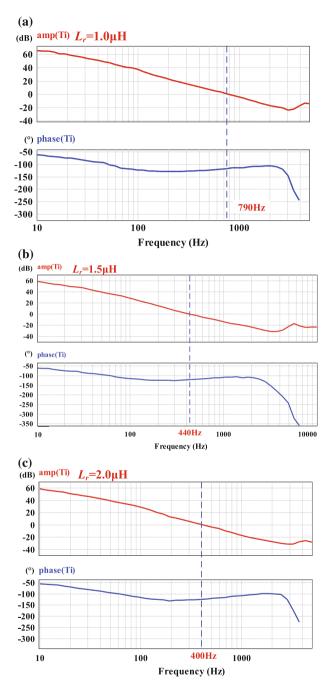

|       | 12.4.1  | Leakage Inductance Value Optimal Design and Its |     |

|-------|---------|-------------------------------------------------|-----|

|       |         | Effect on the Steady-State Performance          | 293 |

|       | 12.4.2  | Feed-Forward Effect on the Dynamic Performance  | 295 |

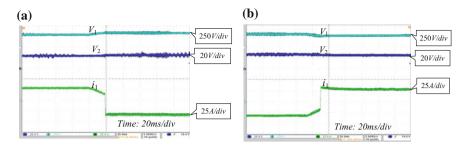

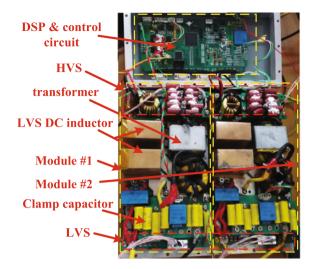

| 12.5  | Experin | nental Verifications                            | 296 |

|       | 12.5.1  | Prototype                                       | 296 |

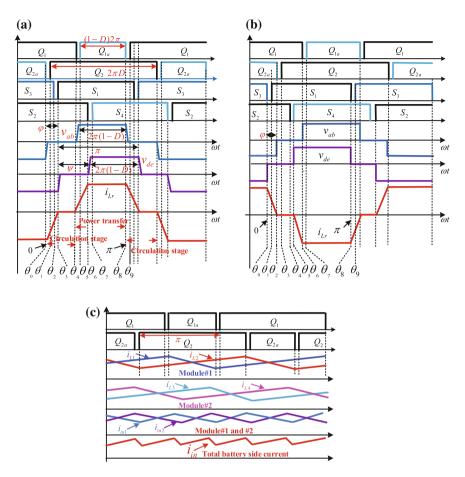

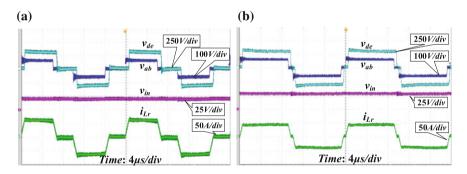

|       | 12.5.2  | Steady-State Operation                          | 296 |

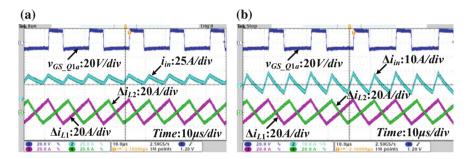

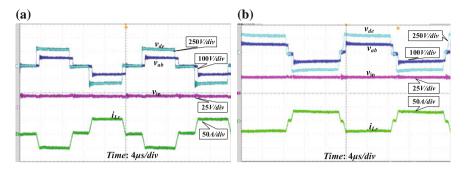

|       | 12.5.3  | Soft Switching Waveforms                        | 299 |

|       | 12.5.4  | Dynamic Performance with Inverter Driven AC     |     |

|       |         | Motor                                           | 300 |

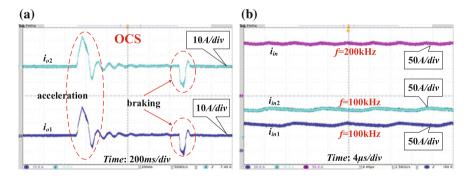

|       | 12.5.5  | Experimental Results of Current Sharing         | 301 |

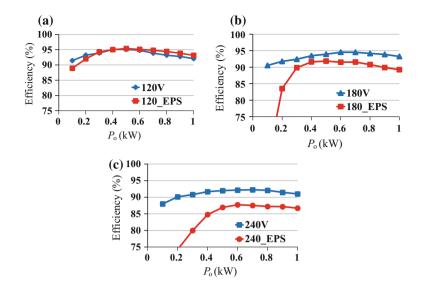

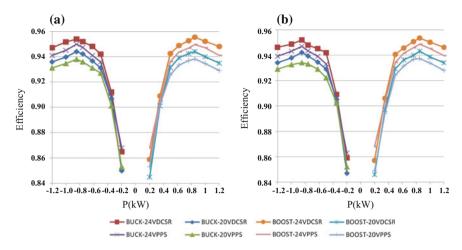

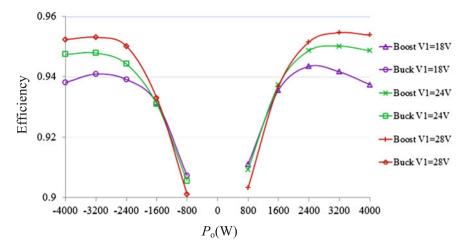

|       | 12.5.6  | Efficiency.                                     | 301 |

| 12.6  | Conclus | sion                                            | 302 |

| Refer | ences   |                                                 | 302 |

# List of Figures

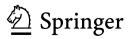

| Energy storage in a DC home grid system                                                    | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

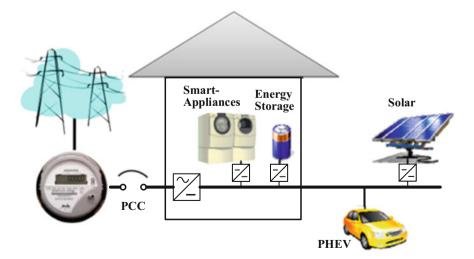

| Typical HEV power system architecture                                                      | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

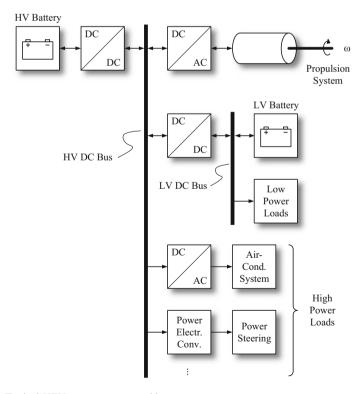

| Interface of a future home in the FREEDM system                                            | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

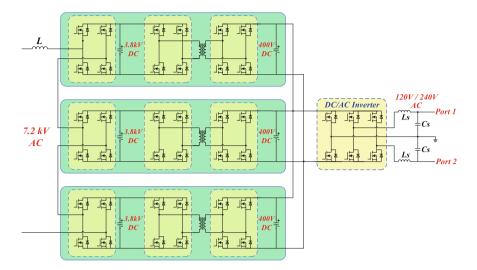

| Topology for the SST                                                                       | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

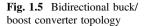

| Bidirectional buck/boost converter topology                                                | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

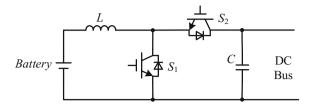

| Bidirectional isolated full-bridge DC-DC converter                                         | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Bidirectional isolated dual active bridge converter                                        | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

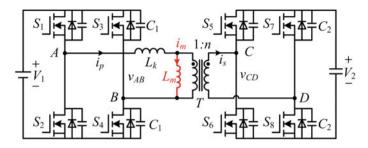

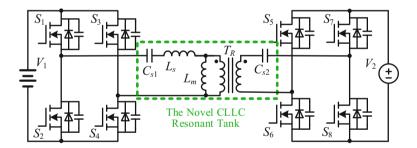

| Bidirectional CLLC resonant converter                                                      | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

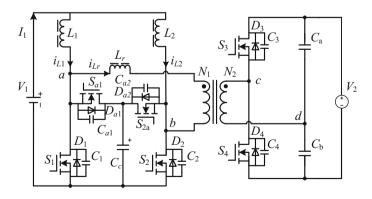

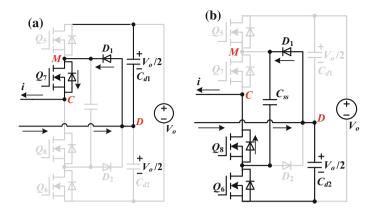

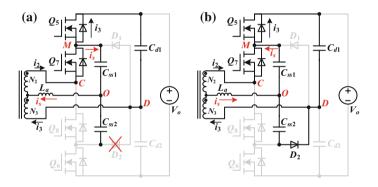

| ZCS current-fed dual active bridge                                                         | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

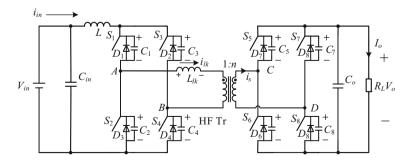

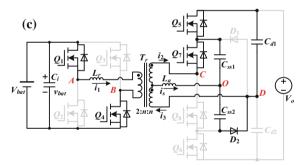

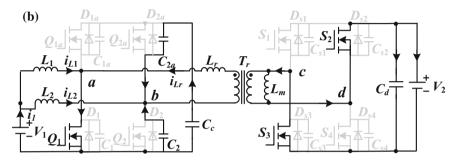

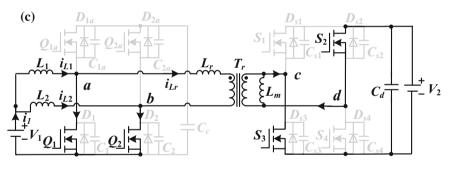

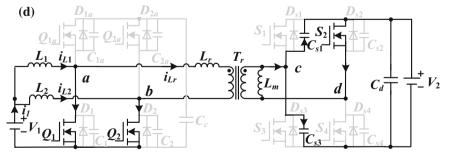

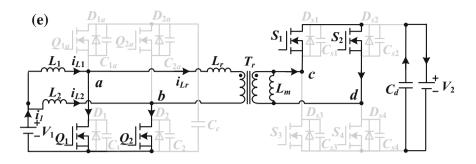

| Current-fed dual active bridge converter                                                   | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

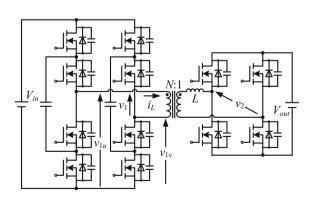

| Interleaved current-fed dual active bridge converter                                       | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

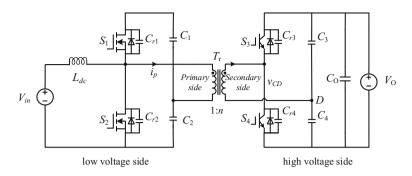

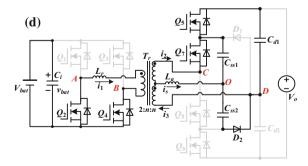

| Voltage-fed three-level DAB converter                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| with flying capacitor                                                                      | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

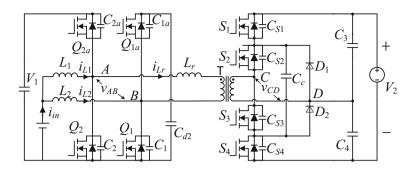

| Current-fed three-level DAB converter with active diodes                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| and flying capacitors                                                                      | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

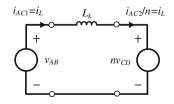

| Basic model for DAB converter                                                              | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

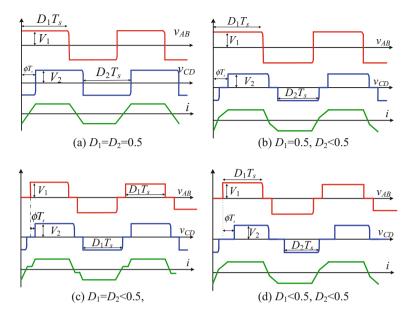

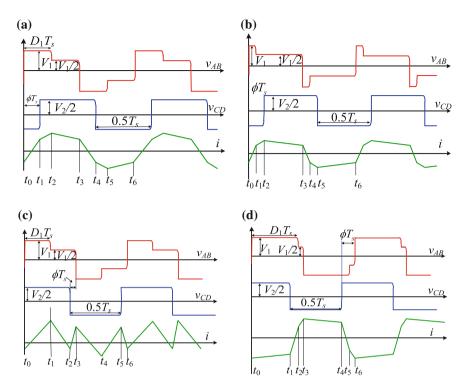

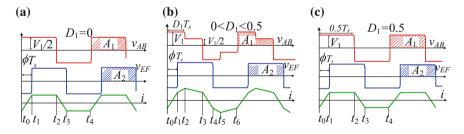

| Four different PWM modulation strategies for dual active                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| bridge converter                                                                           | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

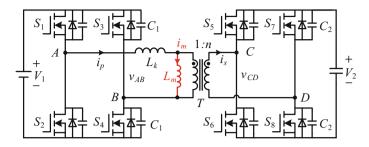

| Topology of DAB DC–DC converter                                                            | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Typical operation waveforms of TZM                                                         | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

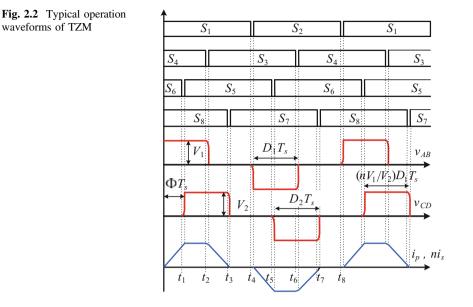

| ZVS conditions for $S_1$ and $S_2$ . <b>a</b> Circuit. <b>b</b> Waveforms                  | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

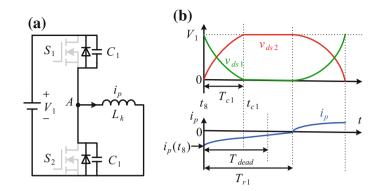

| Fixed duty cycle compensation                                                              | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Magnetizing current design to achieve ZVS for $S_7$ and $S_8$                              | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

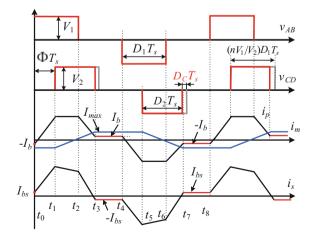

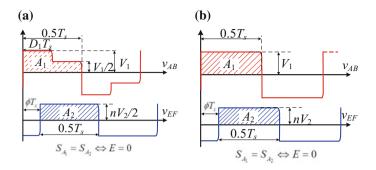

| Three conditions of $D_1$ and $\Phi$ for the same power transfer                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| with TZM control. <b>a</b> Small duty cycles and large $\Phi$ . <b>b</b> Middle            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| duty cycles and middle $\Phi$ . c Small $\Phi$ and large duty cycles                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |