**Studies in Fuzziness and Soft Computing**

Pedro Ponce-Cruz Arturo Molina Brian MacCleery

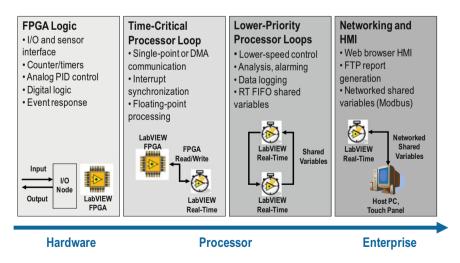

11771

# Fuzzy Logic Type 1 and Type 2 Based on LabVIEW<sup>™</sup> FPGA

**EXTRAS ONLINE**

# Studies in Fuzziness and Soft Computing

Volume 334

# Series editor

Janusz Kacprzyk, Polish Academy of Sciences, Warsaw, Poland e-mail: kacprzyk@ibspan.waw.pl

#### About this Series

The series "Studies in Fuzziness and Soft Computing" contains publications on various topics in the area of soft computing, which include fuzzy sets, rough sets, neural networks, evolutionary computation, probabilistic and evidential reasoning, multi-valued logic, and related fields. The publications within "Studies in Fuzziness and Soft Computing" are primarily monographs and edited volumes. They cover significant recent developments in the field, both of a foundational and applicable character. An important feature of the series is its short publication time and world-wide distribution. This permits a rapid and broad dissemination of research results.

More information about this series at http://www.springer.com/series/2941

Pedro Ponce-Cruz · Arturo Molina Brian MacCleery

# Fuzzy Logic Type 1 and Type 2 Based on LabVIEW<sup>™</sup> FPGA

Pedro Ponce-Cruz Tecnologico de Monterrey Campus Ciudad de México Tlalpan, Distrito Federal Mexico

Arturo Molina Tecnologico de Monterrey Campus Ciudad de México Tlalpan, Distrito Federal Mexico Brian MacCleery National Instruments Corporation Austin, TX USA

The Fuzzy Logic Type 1 and Type 2 Based on LabVIEW FPGA Toolkit can be downloading from the additional material of the book. For decompressing the toolkit you have to use the password (TOOLKITFPGA@TEC01). On the other hand, it is allowed to use the toolkit in academic and research implementations based on LabVIEW FPGAs but it has to be properly referenced. It is not allowed to use it in industrial applications without permission from the authors.

ISSN 1434-9922 ISSN 1860-0808 (electronic) Studies in Fuzziness and Soft Computing ISBN 978-3-319-26655-8 ISBN 978-3-319-26656-5 (eBook) DOI 10.1007/978-3-319-26656-5

Library of Congress Control Number: 2015955366

Springer Cham Heidelberg New York Dordrecht London

© Springer International Publishing Switzerland 2016

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made.

LabVIEW<sup>™</sup> is a trademark of National Instruments Corporation, 11500 N Mopac Expwy, Austin, TX 78759-3504, USA, http://www.ni.com/.

Printed on acid-free paper

Springer International Publishing AG Switzerland is part of Springer Science+Business Media (www.springer.com)

To Norma, Jamie, Pedro, Alize, Jorge, Aura, and Giovanna. Also, I dedicate this book to my lovely mother (Margarita) and grandmother (Catalina Vazquez<sup>†</sup>) who help me to dream in fuzzy colors

Pedro Ponce-Cruz

To my father Arturo, in memory of my mother Rosita and my family, Silvia my lovely wife and beloved kids Julio and Monse

# Arturo Molina

For Eva Jane MacCleery. Most things in life and science have a fuzzy type of logic. However, if we listen carefully and are very fortunate, we find love, a mysterious clarity to guide us through this fuzzy world

Brian MacCleery

# Foreword

Fuzzy logic is widely applied in every aspect of our daily lives. Washing machines, air conditioners, and vehicles are examples of applications in which fuzzy controllers are embedded to achieve smooth, nonlinear, and robust control. Such applications depend on a system architecture that is easy to implement, rather than on a theoretically abstract and complex methodology. Therefore, several tools, such as the NI LabVIEW PID and Fuzzy Logic Toolkit for Windows, have been proposed to assist developers in implementing fuzzy logic systems. Some tools for this purpose can even be downloaded for free and come with a user manual. Through the use of such tools, several successful applications have been demonstrated, which has further motivated the application of fuzzy logic in practice. However, most existing fuzzy logic applications in practice use ordinal fuzzy sets. Other fuzzy set types, such as interval-valued fuzzy sets, type-2 fuzzy sets, and hesitant fuzzy sets, have seldom been used. This is mainly because of the difficulties associated with implementing these generalized forms of fuzzy sets. However, several attempts have indicated that using these generalized fuzzy sets has several advantages. For example, the uncertainty behind a phenomenon can be more effectively described using a type-2 fuzzy set.

The authors of this book combined the latest research findings and practical experience with LabVIEW<sup>TM</sup> FPGA. I particularly appreciate the perspective on FPGA's most recent development strategy. This book also provides information for engineers seeking to understand fuzzy logic and how it can be applied to their products or system designs.

Prof. Dr. Tin-Chih Toly Chen Outstanding Professor Feng Chia University Founding Editor-in-Chief International Journal of Fuzzy System Applications

# Preface

This book presents fuzzy logic and LabVIEW FGPA for designing fuzzy logic controllers. This is a book for implementing fuzzy logic controllers in LabVIEW FPGAs.

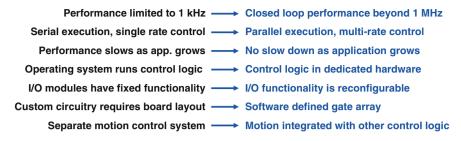

Despite the FPGA's attractive features, their adoption by industrial control and signal processing engineers has been slower than processors and DSPs. This is due to several factors. First, these engineers traditionally programmed processors and DSPs using higher level languages, such as C. However, FPGAs possessed complex development tool chains that required designs to be specified using hardware description level (HDL) and register transfer level (RTL) semantics. Furthermore, traditional FPGA development tools lacked intellectual property (IP) blocks for common industrial applications, such as ADC and encoder interface logic, PWM and commutation logic, timing and triggering functions, PID control algorithms, memory management, and data transfer functions. In addition, FPGAs natively supported integer data types only which significantly increased development complexity for analog control and signal processing applications that required math, control, and digital signal processing algorithms, as opposed to floating point processors. Also, traditional FPGA simulation tools were operated at the digital design level and were not interoperable with the type of dynamic simulation tools used by control systems and signal processing engineers for modeling continuous time dynamic system response. Moreover, FPGAs compilation times were relatively long, as compared to processors and DSPs. For example, typical FPGA compilation times today range from 15 to 90 min, whereas processor and DSP compilations are typically completed in less than one minute. Finally, the sequential text-based semantics of traditional register level development tools made it relatively difficult to specify timing and concurrency among parallel processing tasks in a way that leverages the inherent parallel processing capability of FPGA devices.

Despite these traditional development challenges, the successful adoption of FPGAs in application areas such as consumer electronics, and the resulting drop in the price of FPGAs has spurred the interest of industrial control design and simulation vendors. Such vendors are creating the next generation FPGA development

tools that are designed for engineers with little or no digital design expertise. The goal of these next generation "system-level" graphical design tools is to empower control, simulation, and signal processing engineers to harness the full power of the FPGA technology. Graphical system design tools are intended to provide a more intuitive, high level programming paradigm that simplifies the creation of complex parallel processing and control applications. Also, they are intended to provide relatively competitive performance and resource usage, as compared to traditional HDL development tools.

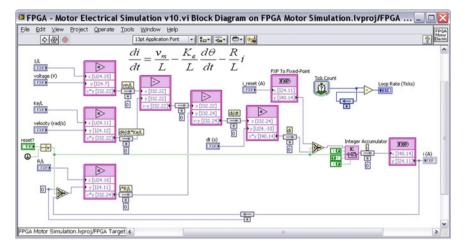

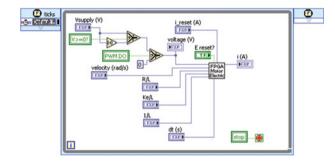

Graphical data flow programming languages are a natural fit for FPGA development due to their inherent sense of parallelism and concurrency that naturally maps to hardware design. Also, recent technological advances are enabling designers to place their FPGA code within a high-level dynamic simulation environment. This ability to cross the boundary between the digital domain of the FPGA and the analog multi-physics domain of the system is facilitating a "true" mechatronics approach to development, in which the complex interplay between FPGA silicon logic, power electronic components, electric motor drives, and mechanical systems can all be simulated in a virtual environment without the need to wait for long FPGA compilations.

The ability to quickly iterate and optimize the FPGA logic design in a mechatronics simulation environment, combined with the new high-level programming tools for FPGAs is reducing dramatically the barriers that prohibited wide adoption of FPGAs in industrial control.

In addition to the improved design and simulation tools for FPGAs, the next generation tools are providing a rapidly growing library of IP blocks for common control and DSP algorithms through code sharing services. On the other hand, the number of books that present Fuzzy logic Control is big as Fuzzy logic control is one of the most important control techniques. However, several books are only mathematical descriptions and are not focused on implementation of fuzzy logic control. Moreover, there are not enough books that deal with implementing fuzzy logic controllers in FPGAs. There is still a lot of vagueness and misunderstanding around the implementation of fuzzy logic controllers implemented in LabVIEW<sup>TM</sup> FPGA.

Since this book presents a clear description of fuzzy logic control type 1 and 2 that are the most used fuzzy logic representations, the implementation in LabVIEW<sup>™</sup> FPGA can be developed. Several experimental examples are presented in order to show the potential of Fuzzy Logic controllers implemented in FPGA.

Finally, a complete LabVIEW<sup>TM</sup> FPGA toolkit for fuzzy logic type 1 and type 2 is included in the book. This toolkit is based on fix point representation that LabVIEW<sup>TM</sup> FPGA needs. This toolkit is developed for working on LabVIEW<sup>TM</sup> real-time systems.

Pedro Ponce-Cruz Arturo Molina Brian MacCleery

# Acknowledgments

We hereby acknowledge the following organizations for their contributions to this book: Tecnologico de Monterrey, Campus Ciudad de México and National Instruments, Austin, Texas.

# Contents

| 1 | Literature Review for Digital Implementations of Fuzzy Logic |                                                 |    |  |  |  |

|---|--------------------------------------------------------------|-------------------------------------------------|----|--|--|--|

|   | Туре                                                         | pe-1 and Type-2                                 |    |  |  |  |

|   | 1.1                                                          | Advances in Applications of Fuzzy Logic Systems | 1  |  |  |  |

|   | 1.2                                                          | FPGA and Microcontrollers Used for Fuzzy        |    |  |  |  |

|   |                                                              | Logic Applications                              | 6  |  |  |  |

|   |                                                              | 1.2.1 Microcontroller Application.              | 7  |  |  |  |

|   |                                                              | 1.2.2 DSP Application                           | 7  |  |  |  |

|   |                                                              | 1.2.3 FPGA Application                          | 9  |  |  |  |

|   | 1.3                                                          | Fuzzy Logic Concepts                            | 10 |  |  |  |

|   |                                                              | 1.3.1 Type-1 Fuzzy Set (T1Fs)                   | 13 |  |  |  |

|   |                                                              |                                                 | 14 |  |  |  |

|   |                                                              |                                                 | 20 |  |  |  |

|   | 1.4                                                          | Extension Principle                             | 20 |  |  |  |

|   |                                                              | 1.4.1 Basic Identities                          | 22 |  |  |  |

|   | 1.5                                                          | Fuzzy Logic Rules                               | 22 |  |  |  |

|   | 1.6                                                          | Defuzzification Methods                         | 23 |  |  |  |

|   | 1.7                                                          | Fuzzy Inference Methods                         | 25 |  |  |  |

|   | 1.8                                                          | Takagi-Sugeno-Kang                              | 29 |  |  |  |

|   | 1.9                                                          | Numerical Example (Mandani)                     | 32 |  |  |  |

|   | 1.10                                                         |                                                 | 35 |  |  |  |

|   | 1.11                                                         | Type-2 Fuzzy Logic Set                          | 36 |  |  |  |

|   |                                                              |                                                 | 36 |  |  |  |

|   |                                                              | 1.11.2 Type-2 Fuzzy Sets (T2FS)                 | 37 |  |  |  |

|   |                                                              |                                                 | 39 |  |  |  |

|   | 1.12                                                         | Fuzzy Sets Type 2 Representations               | 39 |  |  |  |

|   |                                                              | 1.12.1 Digital and Continuous Representation    | 39 |  |  |  |

|   | 1.13                                                         | Interval Type 2 Fuzzy Sets (IT2FS)              | 42 |  |  |  |

|   | 1.14                                                         | Type Reduction and Defuzzification              | 44 |  |  |  |

|   |                                                              | 1.14.1 Karnik–Mendel Iterative Procedure (KM)   | 44 |  |  |  |

|   |                                                              | 1.14.2 Wu-Mendel Uncertain Bounds               | 46 |  |  |  |

|   |                                                              | 1.14.3 Enhanced Karnik–Mendel Algorithm         | 47 |  |  |  |

|   |       | 1.14.4 | Type 2 Fuzzy Logic Systems Block Diagram          | 49  |

|---|-------|--------|---------------------------------------------------|-----|

|   |       | 1.14.5 | Interval Type 2 Fuzzy Logic Numeric Example       | 50  |

|   | 1.15  |        | nental Implementation of a Fuzzy Logic Controller |     |

|   |       | Type-2 | in Quadrotors                                     | 54  |

|   |       | 1.15.1 | Introduction                                      | 54  |

|   |       | 1.15.2 | Quadrotor Basic Principles                        | 55  |

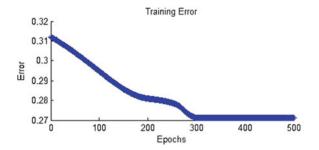

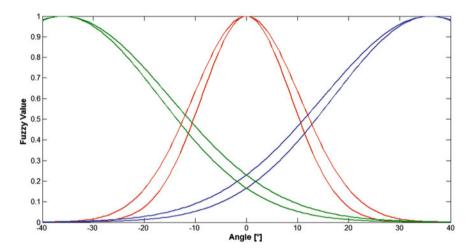

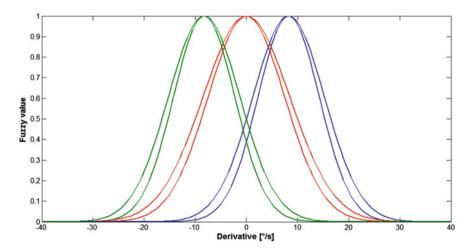

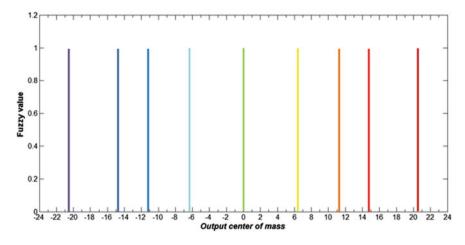

|   |       | 1.15.3 | ANFIS                                             | 56  |

|   | 1.16  | Design | of Fuzzy Logic Controller Tuned by an Expert      | 57  |

|   | 1.17  |        | of Fuzzy Logic Controller Tunned by an Anfis      | 62  |

|   | 1.18  |        | mental Results                                    | 64  |

|   | Refer | ences  |                                                   | 67  |

| 2 | LabV  | ТЕМТМ  | FPGA                                              | 71  |

|   | 2.1   |        | rogrammable Gate Array (FPGA).                    | 71  |

|   |       | 2.1.1  | How Do FPGA-Based Control Systems Compare         |     |

|   |       |        | to Processor-Based Systems?                       | 72  |

|   |       | 2.1.2  | How Do I Program My Control Application           |     |

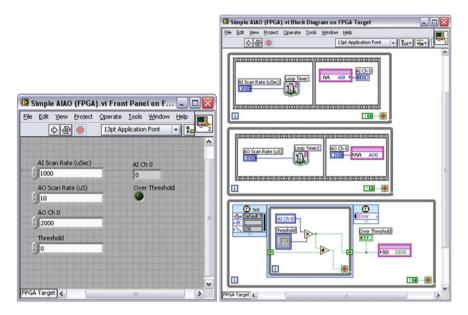

|   |       |        | Using the LabVIEW FPGA Module?                    | 74  |

|   |       | 2.1.3  | How Does the LabVIEW Compiler Translate My        | , . |

|   |       | 2.1.5  | Graphical Code into FPGA Circuitry?               | 76  |

|   |       | 2.1.4  | FPGAs Are Fast, but How Do Faster Loop Rates      | 70  |

|   |       | 2.1.1  | Improve Control System Performance?               | 77  |

|   |       | 2.1.5  | What FPGA Hardware Targets Are Available          | ,,  |

|   |       | 2.1.5  | from NI?                                          | 78  |

|   |       | 2.1.6  | What Closed-Loop Control Performance Can I        | 70  |

|   |       | 2.1.0  | Achieve?                                          | 80  |

|   |       | 2.1.7  | How Much Jitter Can I Expect in My FPGA-Based     | 00  |

|   |       | 2.1.7  | Control Loops?                                    | 81  |

|   |       | 2.1.8  | Creating a New LabVIEW Real-Time Project          | 01  |

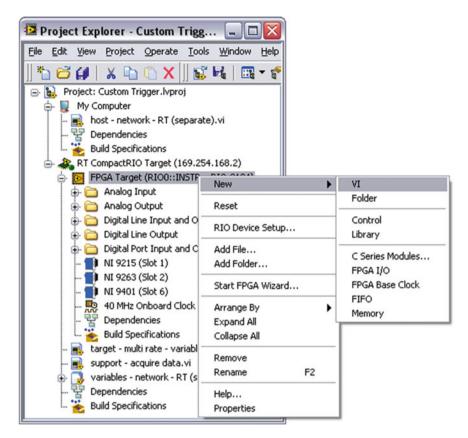

|   |       | 2.1.0  | and Adding I/O                                    | 82  |

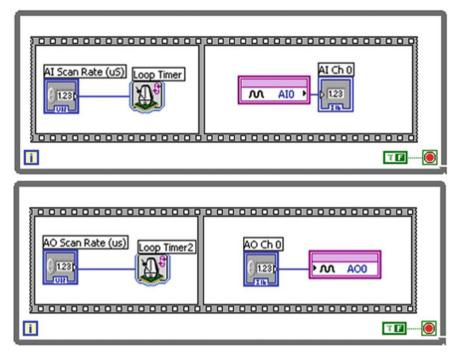

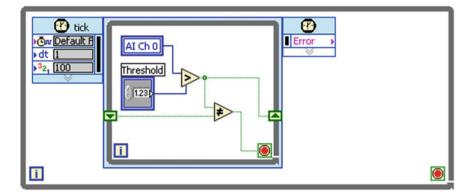

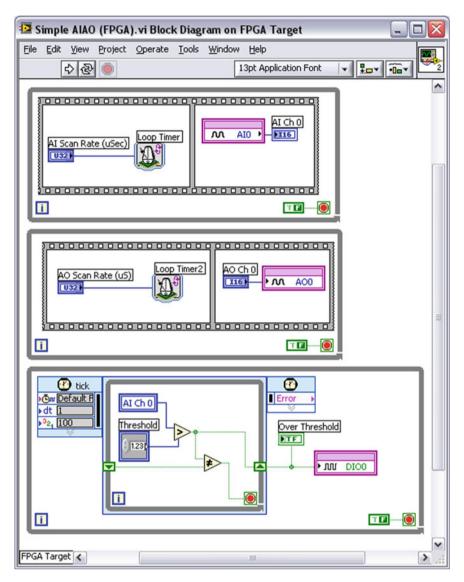

|   | 2.2   | Develo | ping the LabVIEW FPGA Application                 | 90  |

|   | 2.2   |        | ling the FPGA Application                         | 101 |

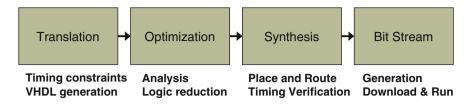

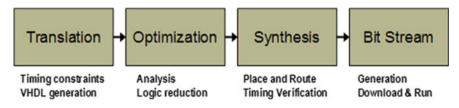

|   | 2.5   | 2.3.1  | Understanding the LabVIEW FPGA Compilation        | 101 |

|   |       | 2.3.1  | Process                                           | 102 |

|   |       | 2.3.2  | FPGA Clock Speed                                  | 102 |

|   |       | 2.3.3  | The Compilation Report                            | 103 |

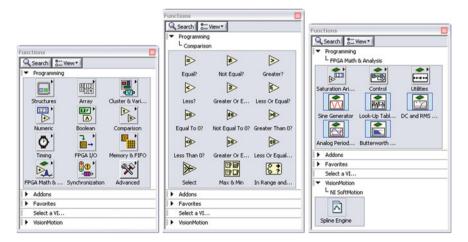

|   | 2.4   |        | ced Methods for LABVIEW FPGA.                     | 105 |

|   | 2.7   | 2.4.1  |                                                   | 104 |

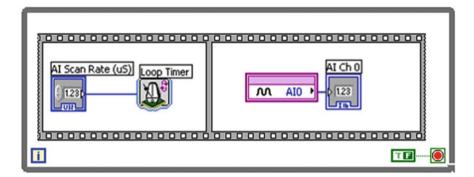

|   |       | 2.4.2  | Technique 1: Use Single-Cycle Timed Loops         | 105 |

|   |       | 2.7.2  | (SCTLs)                                           | 106 |

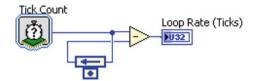

|   |       | 2.4.3  | Creating Counters and Timers                      | 110 |

|   |       | 2.4.3  | Write Your FPGA Code as Modular,                  | 110 |

|   |       | 2.7.7  | Reusable SubVIs                                   | 111 |

|   |       | 2.4.5  | Separate Logic from I/O                           | 114 |

|   |       | 2.4.5  | Holding State Values in a Function Block          | 114 |

|   |       | 2.4.0  | forming state values in a function block          | 115 |

|   |        | 2.4.7   | Run-Time Updateable Look-up Table (LUT)        | 117 |

|---|--------|---------|------------------------------------------------|-----|

|   |        | 2.4.8   | Do not Place Delay Timers in the SubVI         | 119 |

|   |        | 2.4.9   | Reentrancy                                     | 120 |

|   | 2.5    | Use Sin | nulation Before You Compile                    | 122 |

|   |        | 2.5.1   | Providing Tick Count Values for Simulation     | 123 |

|   |        | 2.5.2   | Test the LabVIEW FPGA Code Using the LabVIEW   |     |

|   |        |         | Control Design & Simulation Module             | 125 |

|   | 2.6    | Synchro | onize Your Loops                               | 128 |

|   |        | 2.6.1   | Latching Values                                | 129 |

|   |        | 2.6.2   | Application Example                            | 130 |

|   | 2.7    | Technic | que 5: Avoid "Gate Hogs"                       | 132 |

|   |        | 2.7.1   | Avoid Front Panel Arrays for Data Transfer     | 133 |

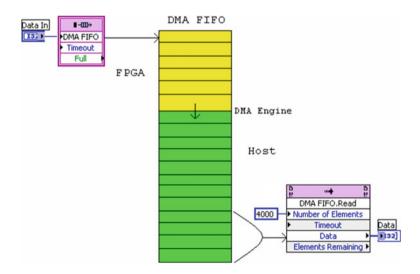

|   |        | 2.7.2   | Use DMA for Data Transfer                      | 134 |

|   |        | 2.7.3   | Use the Minimum Data Type Necessary            | 135 |

|   |        | 2.7.4   | Optimizing for Size                            | 135 |

|   |        | 2.7.5   | Additional Techniques to Optimize Your FPGA    |     |

|   |        |         | Applications                                   | 138 |

|   | Refere | ences   |                                                | 138 |

| 3 | Real-' | Time Fu | zzy Logic Controllers                          | 139 |

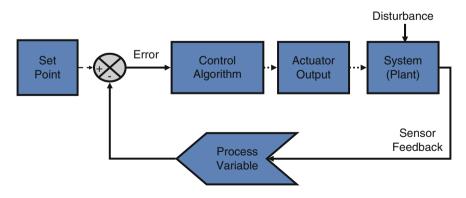

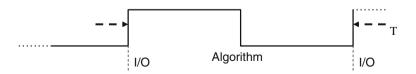

|   | 3.1    | Basic P | Parts in Real-Time Fuzzy Logic Controllers     | 139 |

|   | 3.2    | Case St | tudy: The Karnik-Mendel Algorithms Performance |     |

|   |        | Implem  | ented in Real-Time LABVIEW FPGA                | 140 |

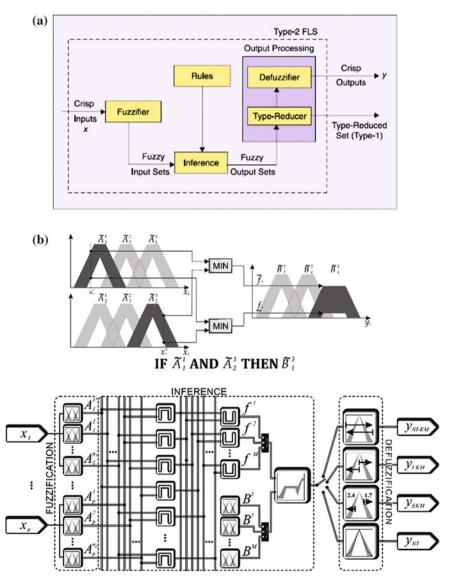

|   |        | 3.2.1   | Interval Type-2 Fuzzy Logic Systems            | 141 |

|   |        | 3.2.2   | The Karnik–Mendel Algorithm                    | 142 |

|   |        | 3.2.3   | Non-iterative Version                          | 142 |

|   |        | 3.2.4   | Iterative Version                              | 144 |

|   |        | 3.2.5   | Enhanced Karnik–Mendel Algorithm               | 146 |

|   |        | 3.2.6   | Nie-Tan Method                                 | 147 |

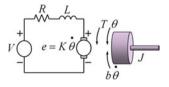

|   | 3.3    |         | vomotor                                        | 148 |

|   |        | 3.3.1   | Laplace Transform Model                        | 149 |

|   |        | 3.3.2   | State-Space Transfer Function                  | 150 |

|   |        | 3.3.3   | Servomotor Control System                      | 151 |

|   | 3.4    |         | rdware Complexity                              | 152 |

|   | 3.5    |         | lology                                         | 153 |

|   | 3.6    |         | and Discussion                                 | 155 |

|   |        | 3.6.1   | Reference Tracking                             | 155 |

|   |        | 3.6.2   | The Hardware Performance                       | 155 |

|   | Refere | ences   |                                                | 158 |

| 4 | Fuzzy  |         | Type 1 and Type 2 LabVIEW FPGA Toolkit         | 159 |

|   | 4.1    | Type-1  | Fuzzy Sets                                     | 159 |

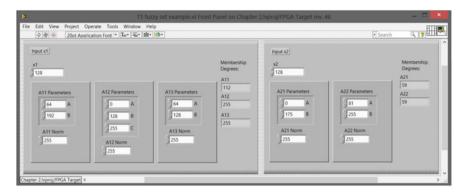

|   |        | 4.1.1   | Membership Function Parameters                 | 160 |

|   |        | 4.1.2   | Normalization                                  | 161 |

|   |        |         |                                                |     |

|       | 4.1.3   | Membership Degree                            | 161 |

|-------|---------|----------------------------------------------|-----|

|       | 4.1.4   | Error Handling.                              | 161 |

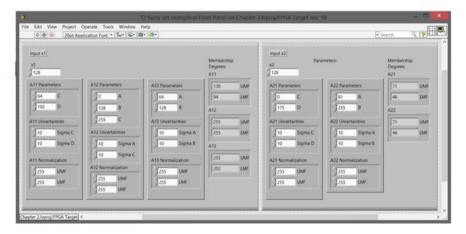

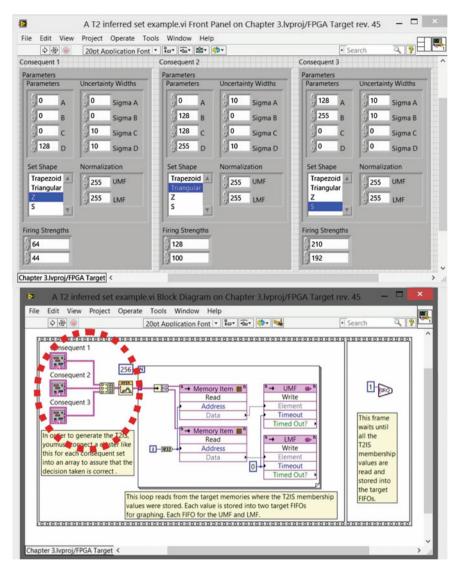

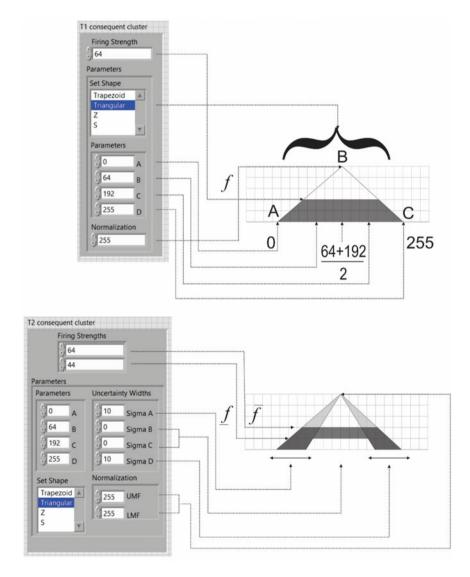

| 4.2   | Type-2  | Fuzzy Sets                                   | 162 |

|       | 4.2.1   | Membership Function Parameters               | 162 |

|       | 4.2.2   | Normalization                                | 162 |

|       | 4.2.3   | Uncertainty Widths                           | 163 |

|       | 4.2.4   | Membership Degrees                           | 163 |

|       | 4.2.5   | Error Handling                               | 164 |

|       | 4.2.6   | Examples                                     | 166 |

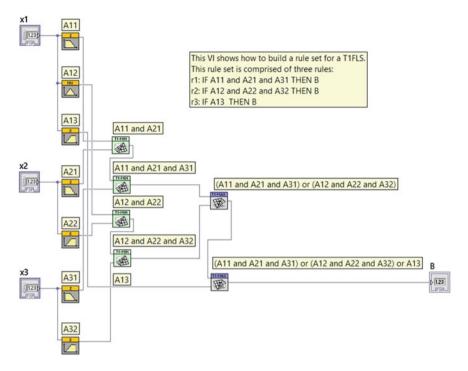

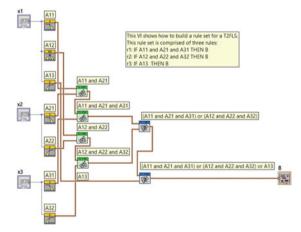

| 4.3   | Creatin | g a Knowledge Base                           | 169 |

|       | 4.3.1   | Building a Rule Set                          | 169 |

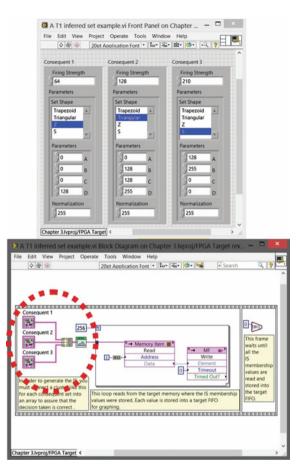

| 4.4   | The Inf | ferred Set                                   | 171 |

| 4.5   |         | ification                                    |     |

|       | 4.5.1   | T1 Mamdani Model the Centroid                | 180 |

|       | 4.5.2   | T2 Mamdani Model the Karnik-Mendel Algorithm |     |

|       | 4.5.3   | The Enhanced Karnik–Mendel Algorithm         |     |

|       | 4.5.4   | The Nie–Tan Method                           |     |

|       | 4.5.5   | The Takagi–Sugeno Model                      |     |

| 4.6   | -       | les                                          |     |

| 4.7   |         | Cases                                        |     |

|       | 4.7.1   | T1FLS Validation                             |     |

|       | 4.7.2   | Electric Wheelchair                          |     |

| 4.8   | T2FLS   | Validation                                   | 200 |

| 4.9   |         | nance T1 FLS DC Servomotor                   |     |

|       | 4.9.1   | Electric Wheelchair                          |     |

| 4.10  |         | Versus T2FLS                                 |     |

|       | 4.10.1  | Noise Response                               |     |

|       | 4.10.2  | Response Time                                |     |

|       | 4.10.3  | Resource Utilization                         |     |

| 4.11  |         | d Examples                                   | 210 |

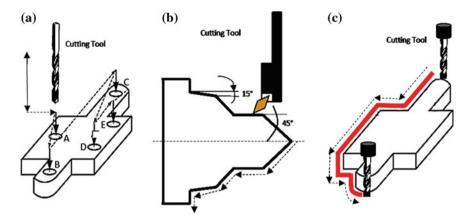

|       | 4.11.1  | Case Study: Experimental CNC Micromachine    | 210 |

|       | 4 1 1 0 | Controlled by Fuzzy Type 2                   |     |

|       | 4.11.2  | Micromachines and Fuzzy Logic                |     |

|       | 4.11.3  | Reconfigurable Micromachine Tools            |     |

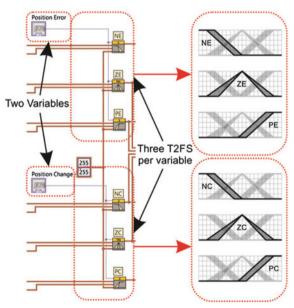

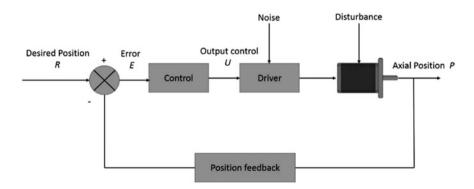

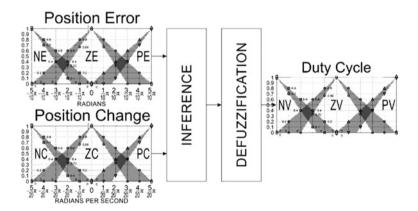

|       | 4.11.4  | Motion Control                               |     |

|       | 4.11.5  | Control Design on Real-Time FPGA             |     |

| D-f   | 4.11.6  | Experimental Results                         |     |

| Kelei | ences   |                                              | 228 |

| Indov |         |                                              | 221 |

| muex  |         |                                              | 231 |

# Chapter 1 Literature Review for Digital Implementations of Fuzzy Logic Type-1 and Type-2

# 1.1 Advances in Applications of Fuzzy Logic Systems

Some works are described below where optimization Type-1 and Type-2 FLS have had relative success according to different areas, illustrating the advantages of using methods to automate process with fuzzy controllers.

The work of Sudha and Vijai Santhi [1], deals with the load frequency control (LFC) problem, which has been a major subject in electrical power system such as design and operation. In practice, LFC systems use simple proportional integral (PI) controllers. However, it shows that fuzzy logic controller is adaptive in nature and is applied successfully for power system stabilization control. Authors propose a type-2 fuzzy approach for load frequency control of two-area interconnected reheat thermal power system with the consideration of Generation Rate Constraint (GRC). The performance of the type-2 controller is compared with conventional controller and Type-1 fuzzy controller with regard to Generation Rate Constraint (GRC). The system parametric uncertainties are verified by changing parameters by 40% simultaneously from their typical values.

The authors Jammeth and Fleury in their work [2] use an interval Type-2 FLC that gets better video quality compared with traditional controllers. They also use Type-1 FLC to show the response in different network scenarios, such like Internet cross-traffic, video streams occupy on an Internet protocol (IP) network. Type-2 FLC is designed for Internet conditions so they can react successfully to the network conditions of an IP-network. Type-2 FLC resulted in an order of magnitude performance improvement in comparison with Type-1 FLC.

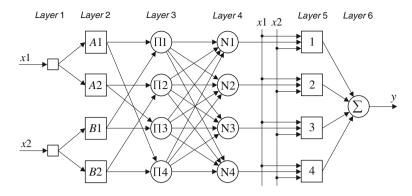

The work of Lee and Lin [3], proposes a new control scheme using type-2 fuzzy neural network (type-2 FNN) and adaptive filter for controlling nonlinear uncertain systems. This type-2 FNN model combines the advantages of type-2 fuzzy logic systems and neural networks. The type-2 FNN system has the ability of universal approximation, which identifies nonlinear dynamic systems. The control scheme consists of a PD-type adaptive FNN controller and a pre-filter. The adaptive filter is

- P. Ponce-Cruz et al., Fuzzy Logic Type 1 and Type 2 Based

- on LabVIEW™ FPGA, Studies in Fuzziness and Soft Computing, DOI 10.1007/978-3-319-26656-5\_1

used to provide better performance under transient response and to treat the problem of disturbance attenuation. The tuning parameters for the filter and the type-2 FNN controller will change according to the learning algorithm. By the Lyapunov stability theorem, the convergence of parameters is given in order to guarantee the stability of nonlinear uncertain systems.

The work of Biglarbegian et al. [4], present a novel design methodology of interval Type-2 Takagi Sugeno Kang fuzzy logic controllers for modular and reconfigurable robot manipulators with uncertain dynamic parameters. Results show that the developed controller can perform better than some linear and non-linear controllers for different configurations. Then, the structure can be adopted for the position control of robots with unknown dynamic parameters in trajectory-tracking applications.

The work of Koca et al. [5], describes a new control scheme for the robust crank angular speed control of a four-bar mechanism driven by a DC motor, based on type-2 fuzzy logic and sliding mode control (SMC) technique. Type-2 fuzzy logic and SMC can be combined to use the advantages of both methods and thus to improve the effectiveness of the controllers. One of the most important advantages of the use of SMC with type-2 FC is to reduce the number of fuzzy rules and to obtain a simpler and more practical control algorithm to use in real applications.

Poornaselvan et al. [6], focus on an agent-based approach to flight control in ground. A type-2 fuzzy interval controller can be applied to the autonomous vehicle in order to handle uncertainty in a better way. Ant colony optimization technique can be used to optimize path planning in traffic environment. They use a hybrid ant colony optimization to handle real-time dynamic environment and path planning. Both agents-based and type-2 fuzzy together with ant colony optimization technique are used to achieve another level of intelligence.

Zaher and Hagras [7], present a method to generate a type-2 FL model entirely from data to provide a dynamic footprint of uncertainty for the generated fuzzy set. The fuzzy model will be used to predict the wind speed experienced by a wind turbine without the use of sensors. This estimated wind speed is then passed for another fuzzy controller that changes the pitch angles of the wind turbine blades in order to track the maximum power available.

In the work of Galluzzo and Cosenza [8], they develop two adaptive type-2 FL controllers with minimum number of rules, compared by simulation for control of a bioreactor in which aerobic alcoholic fermentation for the growth of *Saccharomyces cerevisiae* takes place. The bioreactor model is characterized by nonlinearity and parameter uncertainty. The first adaptive fuzzy controller is a type-2 fuzzy-neuro-predictive controller (T2FNPC) that combines the capability of type-2 FL to handle uncertainties, with the ability of predictive control to predict future plant performance making use of a neural network model of the nonlinear system. The second adaptive fuzzy controller is instead a self-tuning type-2 PI controller, where the output scaling factor is adjusted online by fuzzy rules according to the current trend of the controlled process.

The work of Chaoui and Gueaieb [9], a type-2 FL controller is applied to robot manipulators with joint elasticity and structured and unstructured dynamical

uncertainties. The proposed controller is based on a SMC strategy. To enhance its real-time performance, simplified interval fuzzy sets are used. The efficiency of the control scheme is further enhanced by using computationally inexpensive input signals independent of the noisy torque and acceleration signals, and by adopting a trade-off strategy between the manipulator's position and the actuators' internal stability. The controller is validated through a set of numerical experiments and by comparing it against its type-1 counterpart. It is shown through these experiments, the higher performance of the type-2 FLC in compensating for larger magnitudes of uncertainties with severe nonlinearities.

The work of Petrović et al. [10], deals with the systematic maintenance of mining machinery and equipment. They present a model of the risk assessment of technical systems failure based on the fuzzy sets theory, fuzzy logic, and min–max composition. The risk indicators, severity, occurrence, and detectability are analyzed. The risk indicators are given as linguistic variables. The model was applied for assessing the risk level of belt conveyor elements failure which works in severe conditions in a coal mine.

Baldania et al. [11], focuses on rule base division technique to reduce the power consumption of the fuzzy logic controller based on different conditions and priorities. A new methodology is developed and implemented successfully to reduce the power consumption of the fuzzy logic controller, i.e., dynamic rule base method. The purpose is to solve complex problems efficiently with better accuracy and fast time being response. Fuzzy logic controller has the potential to solve problems which have uncertain nature and complex behavior with better, accurate, and efficient results and also with faster time response as compared to classical logic-based general purpose controllers or processors like PID controllers. The development of the fuzzy logic-based controller follows a step-by-step approach with expertize knowledge. However, there is a lack of power reduction techniques for fuzzy logic controller when the application is concerned for embedded applications. As embedded devices are battery operated and have limited power supply, there is a need of a proper approach and method to reduce the power consumption.

The work of Novak et al. [12], presents three special soft computing software systems, based on the original results in two areas: fuzzy natural logic and fuzzy transform. The first software is LFL Controller which is a universal system that can be used in fuzzy or linguistic control, and in decision making. The system implements results of fuzzy natural logic, namely the theory of evaluative linguistic expressions and perception-based logical deduction. The second system is LFL Forecaster which is a specialized SW for analysis and forecasting of time series. The analysis is realized using F-transform and forecasting using results of fuzzy natural logic. The third system is FT-Studio which is specialized for computation of fuzzy transform of functions that can be defined either using a formula, or given by data.

In the work of Arbex et al. [13], presents a model which uses fuzzy logic as the basis for the development of an inference system to aid decision making, which is based on previous results obtained by different single nucleotide polymorphisms (SNP) discovery tools and which present possibly conflicting results. A single

difference between base pairs of different aligned sequences is the most common type of genetic variability and they are called single nucleotide polymorphisms (SNPs). They are crucial for the study of species variability, since they can cause functional or phenotypic modifications which, in turn, may imply in evolutionary or biochemical consequences in the individuals of a given species.

Ai-Zhen and Feng [14], made a fuzzy controller neural network for a washing machine to reduce the wasting of electric and water. The washing machine fuzzy controller neural network is researched deeply, which is based on fuzzy logic, neural network, and its learning algorithm. The BP neural network is combined with fuzzy control and experiments are simulated by MATLAB. Water level, flow intensity, and the washing time are preset. Fuzzy control rules and membership functions are automatically generated. These parameters can be adjusted real-time to improve the performance of washing machines and achieve better water-saving effect of energy saving.

The work of Liang and Mendel [15], presents a type-2 fuzzy adaptive filter (FAF); one that is realized using an unnormalized type-2 Takagi-Sugeno-Kang (TSK) fuzzy logic system (FLS). They apply this filter to equalization of a nonlinear time-varying channel and demonstrate that it can implement the Bayesian equalizer for such a channel, has a simple structure, and provides fast inference. In 2001 [16], they presented an approach for MPEG variable bit rate (VBR) video modeling and classification using fuzzy techniques. They demonstrated that a type-2 fuzzy membership function, i.e., a Gaussian MF with uncertain variance, is most appropriate to model the log-value of I/P/B frame sizes in MPEG VBR video. The fuzzy c-means (FCM) method is used to obtain the mean and standard deviation (std) of T/P/B frame sizes when the frame category is unknown. They proposed to use type-2 fuzzy logic classifiers (FLCs) to classify video traffic using compressed data. Five fuzzy classifiers and a Bayesian classifier are designed for video traffic classification, and the fuzzy classifiers are compared against the Bayesian classifier. Simulation results show that a type-2 fuzzy classifier in which the input is modeled as a type-2 fuzzy set and antecedent membership functions are modeled as type-2 fuzzy sets performs the best of the five classifiers when the testing video product is not included in the training products and a steepest descent algorithm is used to tune its parameters.

The work of Mitchell [17], introduces a similarity measure for measuring the similarity, or compatibility, between two type-II fuzzy sets. With this new similarity measure, he shows that type-II fuzzy sets provide us with a natural language for formulating classification problems in pattern recognition. Type-II fuzzy sets are a generalization of the ordinary fuzzy sets in which the membership value for each member of the set is itself a fuzzy set in [0, 1].

The work of Herman et al. [18], examines the potential of the type-2 FLS methodology in devising an EEG-based brain-computer interface (BCI). In particular, a type-2 FLS has been designed to classify imaginary left- and right-hand movements based on time-frequency information extracted from the EEG with the short-time Fourier transform (STFT). The type-2 fuzzy classifier has been proven to outperform its type-1 counterpart on all datasets recorded from three subjects examined. It has also compared favorably to the well-known classifier based on linear discriminant analysis (LDA). Analysis of the electroencephalogram (EEG) requires a framework that facilitates handling the uncertainties associated with the varying brain dynamics and the presence of noise. Recently, the type-2 fuzzy logic systems have been found effective in modeling uncertain data.

In the work of Karnik and Mendel [19], they begin with a type-1 fuzzy logic system (FLS), trained with noisy data. They demonstrate how information about the noise in the training data can be incorporated into a type-2 FLS, which can be used to obtain bounds within which the true (noise-free) output is likely to lie. They do that with the example of a one-step predictor for the Mackey–Glass chaotic time series. They also demonstrate how a type-2 FLS can be used to obtain better predictions than those obtained with a type-1 FLS.

The paper of Ozen and Garibaldi [20], explains how the shape of type-2 fuzzy membership functions can be used to model the variation in human decision making. An interval type-2 fuzzy logic system (FLS) is developed for umbilical acid–base assessment. The influence of the shape of the membership functions on the variation in decision making of the fuzzy logic system is studied using the interval outputs. Three different methods are used to create interval type-2 membership functions. The center points of the primary membership functions are shifted, the widths are shifted, and a uniform band is introduced around the original type-1 membership functions. It is shown that there is a direct relationship between the variation in decision making and the uncertainty introduced to the membership functions.

The work of Liang and Wang [21], presents a new approach for sensed signal strength forecasting in wireless sensors using interval type-2 fuzzy logic system (FLS). They show that a type-2 fuzzy membership function with uncertain mean is most appropriate to model the sensed signal strength of wireless sensors. They demonstrate that the sensed signals of wireless sensors are self-similar, which means they can be forecasted. An interval type-2 FLS is designed for sensed signal forecasting and is compared against a type-1 FLS. Simulation results show that the interval type-2 FLS performs much better than the type-1 FLS in sensed signal forecasting. This application can be further used for power on/off control in wireless sensors to save battery energy.

The work of Castillo and Melin [22], describes the application of type-2 fuzzy logic for achieving adaptive noise cancelation. The objective of adaptive noise cancelation is to filter out an interference component by identifying a model between a measurable noise source and the corresponding unmeasurable interference. They propose the use of type-2 fuzzy logic to find this model. The use of type-2 fuzzy logic is justified due to the high level of uncertainty of the process, which makes it difficult to find appropriate parameter values for the membership functions.

In the work of Lee et al. [23], presents a type-2 fuzzy neural network system (type-2 FNN) and its learning algorithm using backpropagation algorithm. The FNN system using type-1 fuzzy logic systems (FLS) is called type-1 FNN system. It has the properties of parallel computation scheme, easy to implement,

fuzzy logic inference system, and parameters convergence. For considering the fuzzy rules uncertainties, we use the type-2 FLSs to develop a type-2 FNN system. The type-2 fuzzy sets let to model and to minimize the effects of uncertainties in rule-based fuzzy logic systems (FLSs). The previous results of type-1 FNN are extended to a type-2 one. In addition, the corresponding learning algorithm is derived by back-program algorithm. Several examples are presented to illustrate the effectiveness of the model.

The work of Rhee and Hwang [24], presents an interval type-2 fuzzy perceptron algorithm that is an extension of the type-1 fuzzy perceptron algorithm proposed by Keller et al. [25]. In their proposed method, the membership values for each pattern vector are extended as interval type-2 fuzzy memberships by assigning uncertainty to the type-1 memberships. By doing so, the decision boundary obtained by interval type-2 fuzzy memberships can converge to a more desirable location than the boundary obtained by crisp and type-1 fuzzy perception methods.

The work of Agero and Vargas [26], presents an approach of aiming at inferring the operative configuration (OC) of distribution networks. In order to attain this objective, the OC problem is decomposed in two parts. The first part, the available real-time data and expert knowledge are integrated by means of rule-based type-2 FLS. As a result, an approximate initial solution is obtained. In the second part, the initial solution is dynamically tuned using customer trouble calls. This is done by means of an approach based on fuzzy relational equations and fuzzy inference. The performance of the methodology is evaluated on a real distribution feeder and the results are presented.

# **1.2 FPGA and Microcontrollers Used for Fuzzy Logic** Applications

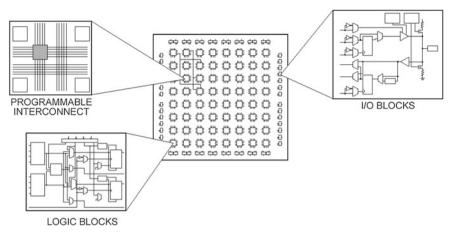

Field programmable gate array (FPGA) are two-dimensional arrays of logic blocks and flip-flops with an electrically programmable interconnection between logic blocks. The interconnections consist of electrically programmable switches which is why FPGA differs from custom integrated circuits, as a custom integrated circuit is programmed using the technology to form metal interconnections between logic blocks. In an FPGA, logic blocks are implemented using multiple-level low fan in gates, which gives it a more compact design compared to an implementation with two-level AND-OR logic [27]. Microcontrollers and FPGA's provide functional blocks to build type-1 FLS and type-2 FLS, in which crisp inputs and outputs, and parameters are defined in 8-bits. It means that in a byte one can spread all inputs or outputs discourse universe. A crisp input may be defined in speed, pressure, temperature, or another physical variable. When an inferred value is ready, the next step is to convert it into a physical value so it can be used as the control result applicable to the plant of the controller. Some applications are described since microcontrollers, DSP up to FPGA.

#### **1.2.1** Microcontroller Application

The work of Muscato [28], the position control of a planar under actuated manipulator with two revolute joints is considered. A dynamic model of the system is presented and a fuzzy control strategy is proposed. Fuzzy logic allows empirical rules to be translated into a control algorithm. A fuzzy microcontroller is adopted for the practical implementation of the system. The results of several experiments are presented and discussed.

The work of Faravelli et al. [29], pursues the numerical testing of a programmable controller driving an active mass damper (AMD) located at the top of a frame structure subject to base excitation. Its key features are the fuzzy nature of the controller and its adaptive characteristics toward fault tolerance. Numerical testing of microcontrollers is a reasonable way to design their parameters in a consistent environment. Indeed, in such a way, one avoids unrepairable failures of the device to be controlled and the consequent costs. A final experimental test will eventually provide the fine tuning of the parameters.

In the study of El-Nagar and El-Bardini [30], they propose an embedded real-time interval type-2 fuzzy proportional–integral–derivative (IT2F-PID) controller which is a parallel combination of the interval type-2 fuzzy proportional–integral (IT2F-PI) controller and the interval type-2 fuzzy proportional–derivative (IT2F-PD) controller. The proposed IT2F-PID controller is able to handle the effect of the system uncertainties due to the structure of the interval type-2 fuzzy logic controller. The proposed IT2F-PID controller is implemented practically using a low cost PIC microcontroller for controlling the uncertain nonlinear inverted pendulum to minimize the effect of the system uncertainties due to the structure in the rotation angle of the pendulum and the structural uncertainty. The test is carried out using the hardware-in-the-loop (HIL) simulation. The experimental results show that the performance of the IT2F-PID controller improves significantly the performance over a wide range of system uncertainties.

## 1.2.2 DSP Application

The work of Bal et al. [31], develops a digitally controllable two phase serial resonant inverter to drive the ultrasonic motor by using a TMS320F243 digital signal processor. The driving frequency was used as a control input in the position control loop. The position characteristics obtained from the proposed drive and control system were demonstrated and evaluated by experiments. The experimental results verify that the developed position control scheme is highly effective, reliable and applicable for the ultrasonic motor. Position control of an ultrasonic motor was implemented on the basis of fuzzy reasoning.

In the work of Goh et al. [32], they improve the overall performance of an overcurrent relay for power system protection compared to conventional relay. It is essential for a relay to work efficiently to trip the circuit breakers in the presence of faults and at the same time proficient to coordinate well with the networks to avoid maloperation. There are two different types of fuzzy logic control strategies proposed for the relay, the Fuzzy Logic Controller (FLC) and Fuzzy Bang-Bang Controller (FBBC). The FBBC is the same as the conventional FLC except that the defuzzification method uses largest of maxima (LOM). Comparisons between the fuzzy controllers and conventional relay are based on IEC 255-3 standard. These relays are implemented on a DSP TMS320F2812 and their performance is evaluated which is based on operation time, DSPs execution time and grading margin. The results obtained show a significant performance improvement compared to conventional relay.

Goh et al. as well [33], improve the performance of the relay significantly with the new numerical relay technology using digital signal processor (DSP). However, application of DSP in numerical overcurrent relays is limited especially in coordination among the group of relays. The relay must work proficiently to coordinate with the networks in order to avoid maloperation. Therefore, in this paper, an implementation of overcurrent relay with improved coordination on a DSP, TMS320F2812 is described. The fuzzy bang–bang controller is used as the control strategy for the relay to provide efficient control for overcurrent protection. The performance evaluation of the proposed system is based on steady-state analysis, transient state analysis, coordination and lastly the execution time of the DSP. The results obtained using this new proposed controller is very promising. Overcurrent relays are very important protection components that require high reliability to maintain high security in power systems.

The study of Chou et al. [34], proposes a digital signal processor (DSP)-based complementary sliding mode control (CSMC) with Sugeno type fuzzy neural network (SFNN) compensator for the synchronous control of a dual linear motors servo system installed in a gantry position stage. The dual linear motors servo system comprises two parallel permanent magnet linear synchronous motors (PMLSMs). The dynamics of the single-axis motion system with a lumped uncertainty which contains parameter variations, external disturbances, and nonlinear friction force are briefly introduced first. Then, a CSMC is designed to guarantee the precision position tracking requirement in single-axis control for the dual linear motors. Moreover, to enhance the robustness to uncertainties and to eliminate the synchronous error of dual linear motors, the CSMC with a SFNN compensator is proposed where the SFNN compensator is designed mainly to compensate the synchronous error. Furthermore, to increase the control performance of the proposed intelligent control approach, a 32-bit floating-point DSP, TMS320VC33, is adopted for the implementation of the proposed CSMC and SFNN.

# 1.2.3 FPGA Application

The work of Melgarejo and Peña-Reyes [35], presents an architectural proposal for a hardware-based interval type-2 fuzzy inference system. First, it presents a computational model which considers parallel inference processing and type reduction based on computing inner and outer bound sets. They infer that a hardware architecture with several pipeline, stages for full parallel execution of type-2 fuzzy inferences. The architectural proposal is used for specifying a type-2 fuzzy processor with reconfigurable rule base, which is implemented over FPGA technology.

The review of state of the art of FPGA of Sulaiman et al. [27], approach a large numbers of fuzzy control applications with the physical systems required a real-time operation to interface high speed constraints; higher density programmable logic devices such as field programmable gate array (FPGA) can be used to integrate large amounts of logic in a single integrated circuit (IC). In their review, they focus on FPGA-based fuzzy logic controller. The paper starts with an overview of FPGA in order to get an idea about FPGA architecture, and followed by an explanation on the hardware implementation with both type analog and digital implementation, a comparison between fuzzy and conventional controller are also provided. A survey on fuzzy logic controller with different applications. Finally, they provide the simulation and experimental results from the literature and conclude the main differences between software-based systems with respect to FPGA-based systems, and the main features for FPGA technology and its real-time applications.

The work of Ramadan et al. [36], presents an improved adaptive fuzzy logic speed controller for a DC motor, based on FPGA hardware implementation. The developed controller includes an adaptive fuzzy logic control algorithm, which is designed and verified with a nonlinear model of DC motor. Then, it has been synthesized, functionally verified, and implemented using Xilinx Integrated Software Environment (ISE) and Spartan-3E FPGA. The performance of the controller has been successfully validated with good tracking results under different operating conditions.

The work of Messai et al. [37], details the work in which they optimize and implement a FLC used as a maximum-power-point tracker for a stand-alone PV system, are presented. The near optimum design for membership functions and control rules were found simultaneously by genetic algorithms which are search algorithms based on the mechanism of natural selection and genetics. These are easy to implement and efficient for multivariable optimization problems such as in fuzzy controller design. The FLC thus designed, as well as the components of the PV control unit, were implemented efficiently on a Xilinx reconfigurable FPGA chip using VHDL Hardware Description Language. The obtained simulation results confirm the good tracking efficiency and rapid response to changes in environmental parameters.

In the work of Soares dos Santos and Ferreira [38], tests if FPGAs are able to achieve better position tracking performance than software-based soft real-time

platforms. For comparison purposes, the same controller design was implemented in these architectures. A Multi-state Fuzzy Logic controller was implemented both in a Xilinx<sup>®</sup> Virtex-II FPGA (XC2v1000) and in a soft real-time platform NI CompactRIO<sup>®</sup>-9002. The same sampling time was used. The comparative tests were conducted using a servo-pneumatic actuation system. Steady-state errors lower than 4  $\mu$ m were reached for an arbitrary vertical positioning of a 6.2 kg mass when the controller was embedded into the FPGA platform. Performance gains up to 16 times in the steady-state error, up to 27 times in the overshoot, and up to 19.5 times in the settling time were achieved by using the FPGA-based controller over the software-based FLC controller.

The work of Munoz et al. [39], describes the validation of five dispatching algorithms for elevator systems that were implemented on Spartan 3 FPGA-based boards in an integrated approach reducing the area and improving performance. The overall system is composed of several local control systems (LCS), which implement the dispatching algorithms, an RS485-based network and a virtual environment called virtual elevator interface system (VEI), which includes a simulator/monitoring system and an elevator group control system EGCS-based on fuzzy logic (FEGCS). The FEGCS runs on a PC and, under different traffic situations, determines the best algorithm to be run in each LCS in order to reduce the user waiting time and the power consumption. The novelty of this approach is that the LCSs are capable to run different dispatching algorithms independently, that are suitable for specific passenger traffic situations, while the FEGCS only must determine the best algorithm to be run in each LCS. The VEI allows the designer to test and validate in a flexible way the algorithm performance for different traffic situations. Elevator systems are administrated by an EGCS and microprocessed subsystems implementing a LCS for each elevator.

## **1.3 Fuzzy Logic Concepts**

Lofty Zadeh [40], a computer scientist at the University of California Berkeley, proposed the fuzzy set theory in 1965. "A fuzzy set is a class of objects with a continuum of grades of membership." Lofty defined fuzzy sets as a class of sets with grades of membership from 0 to 1. Expert Systems, Artificial Neural Networks and Fuzzy Systems share the property of being model-free approximations, which means that no exact mathematical model of the physical system to control or to approximate is needed.

One of the most important areas of implementing fuzzy logic is in control systems. Fuzzy logic control has been in several real-world applications. The first Fuzzy logic controller was developed by Mamdani and Assilian in 1975 for controlling a steam generator in a laboratory setting and Blue Circle Cement and SIRA in Denmark developed a cement kiln controller that is the first industrial application in 1976. Japan developed several industrial applications using fuzzy logic. For instance, a water treatment system developed by Fuji Electric. Besides, Hitachi

installed a fuzzy logic-based automatic train operation control system into the Sendai city's subway system based on fuzzy logic. These applications of fuzzy logic attracted the attention of many engineers to use fuzzy logic in control systems.

Fuzzy sets intend to model the uncertainty or vagueness associated to the natural human reasoning, which is based on linguistic words and sentences rather than in mathematical expressions and relations. Approximate reasoning or fuzzy reasoning is a mode of reasoning which is neither exact nor inexact [Zade75]. It is supported on the Fuzzy Logic theory and it offers a realistic framework for representing human reasoning. Approximate reasoning is the fundament for Fuzzy Inference Systems. To understand how it is performed, three basic concepts should be defined:

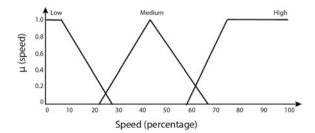

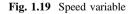

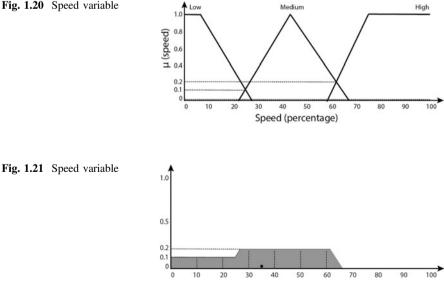

• Linguistic Variable. A linguistic variable is a variable whose values are words or sentences in a natural or artificial language rather than numerical. For instance, the variable speed can be described as it is presented below.

$TS(speed) = \{small, medium, big\} = \{S, M, B\}.$

- Fuzzy Proposition. Fuzzy proposition is a statement expressed in a natural or artificial language. In contrast to classical logic propositions, a fuzzy proposition may adopt a truth-value from the interval [0, 1].For example, Distance is Big.

- Linguistic Rule. A linguistic if-then rule has two parts:

Antecedent part (premise), expressed by: if <fuzzy proposition>,

Consequent part, expressed by: then <fuzzy proposition>,

It is used for setting the actions that can be done in a controller. For instance, if the distance is big then the controlled speed is big.

A fuzzy set is characterized by a membership function which assigns to each element a grade of membership. A fuzzy set F is entirely defined by the set of ordered pairs.

$$F = \{(x, \mu_F(x)) | X \in U\}$$

and  $\mu_F: U \to [0, 1],$

where x is an element of the universe of discourse U and  $\mu_F$  is a membership function that assigns a degree of membership  $\mu_F(x)$  to each element x of F.

In 1996, Zadeh [41] expressed a novel fuzzy logic approximation that is equated to computing with words (CW). There are two main ideas for computing with words. Initially, CW is a necessity when the available information is imprecise, and there is a tolerance for imprecision which can be exploited to achieve tractability, robustness, low solution cost, and better rapport with reality.

Fuzzy logic gradually emerged as a discipline in Artificial Intelligence, as well as expert systems and neural network [42]. Fuzzy logic helps solve complex problems, and it has been applied to several applications [43] like process control [1–9, 11, 14, 44–47], modeling [48], identification [48, 49], medicine [18], science [8, 14, 42, 50–52], and so on. Fuzzy Logic Type-2 is much computationally intensive

comparing to its type-1 counterpart. Despite their computation burden, type-2 has been applied to various type of application such as, neural network [24], signal processing [15, 16], pattern recognition [17, 18], time series forecasting [19], wireless communication [21] decision making [20], noise canceling [22], system identification [23], and power engineering [26].

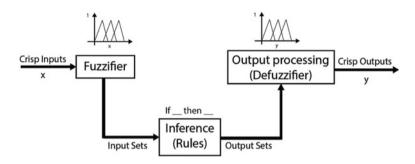

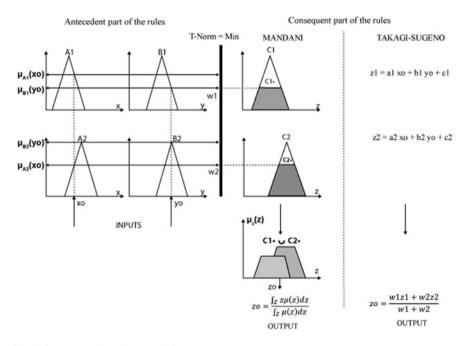

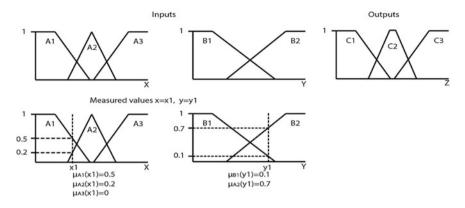

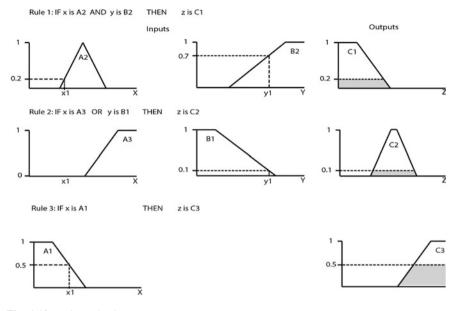

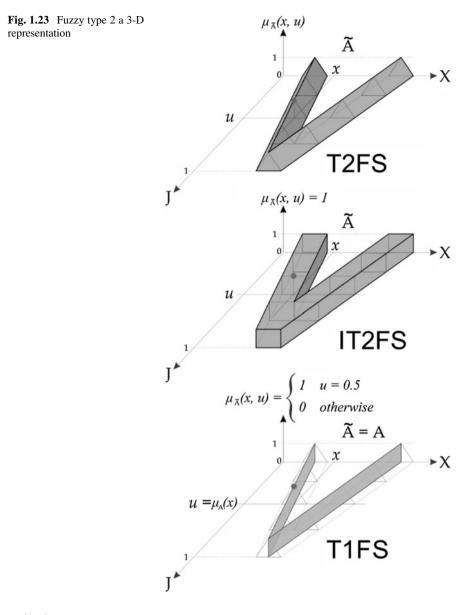

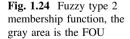

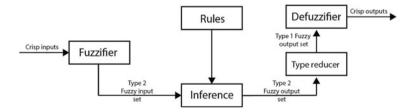

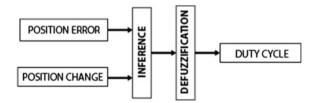

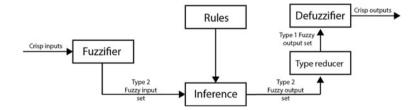

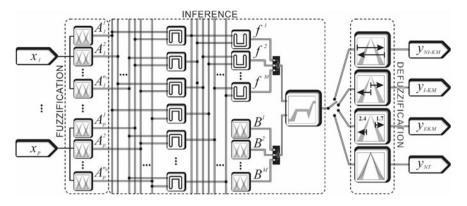

Fuzzy logic deals with real problems that have imprecise information or uncertainty. Fuzzy logic is defined as the set of mathematical descriptions based on degrees of membership. A fuzzy model includes linguistic rules that help to map the inputs and outputs of the system. Inputs in a Fuzzy logic systems can get membership values between 0 and 1. In conventional logic, the membership value is limited to only two values, 0 or 1 [53]. A Type-1 FLS has a grade of membership that is crisp, whereas Type-2 FLS has grades of membership that are fuzzy. Type-2 FLS has four basic components: fuzzification, evaluation of rules (if-then linguistic rules) and defuzzification. When membership functions are used, they can describe real-world situations where it is difficult to use binary membership values (0 or 1).

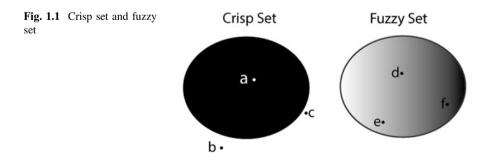

Two sets are presented in Fig. 1.1, the one on the left side is crisp and an element defined within a universe can belong or not to the set (element "a" belong the set or has a membership value of 1 and elements "b" and "c" do not belong and have a membership value of 0). On the other hand, the fuzzy set has different degrees of membership. For example, the element f has a lower degree of membership that elements d and e (if the center of the set represents the maximum membership value). A fundamental concept in mathematics is the notion of set. A set is a collection of specific, discernible elements. A set can be finite countable or uncountable elements and it could be described in two forms:

By naming all its elements:

$$A = \{a, b, c, 10, X\} \Rightarrow a, b, \dots X \in A; \text{ where as } f, \beta \notin A.$$

By stating a property for all its elements:

$$A = \{x | P(x)\},$$

where *P* defines the properties of the elements *x* belonging to  $A$  (i.e.  $A = \{x | x\} > 3$ )

#### 1.3 Fuzzy Logic Concepts

On the other hand, fuzzy sets can be represented by discrete or continues representation. A notation convention for fuzzy sets when the universe of discourse, X, is discrete and finite, it is as follows for a fuzzy set A:

$$\tilde{A} = \left\{ \frac{\mu_{\tilde{A}}(x_1)}{x_1} + \frac{\mu_{\tilde{A}}(x_2)}{x_2} + \cdots \right\} = \left\{ \sum_i \frac{\mu_{\tilde{A}}(x_i)}{x_i} \right\}$$

If the universe, X, is continuous and infinite, the fuzzy set A is defined by:

$$\tilde{A} = \left\{ \int \frac{\mu_{\tilde{A}}(x)}{x} \right\}$$

It can be defined as a *Characteristic Function* for all the elements x of the Universe of Discourse U. The set U is also called the Super Set. Therefore, for a set A belonging to U, the *Characteristic Function in a crisp set* (This function is called *membership function* in Fuzzy Set Theory) can be defined by

$$\mu_A(x) = \begin{cases} 1 & \text{if } x \in A \\ 0 & \text{if } x \notin A \end{cases}$$

The membership function of a fuzzy set corresponds to the characteristic function of a crisp set. However, while the characteristic function of a crisp set can only take values 0 or 1, the membership function of a fuzzy set can take any value from the interval [0, 1]. Hence, a fuzzy set is a generalization of the crisp set.

## 1.3.1 Type-1 Fuzzy Set (T1Fs)

Normally, Human decision thinking is not defined with mathematical methods or crisp numbers, so fuzzy numbers can be used for solving basic and advanced problems such as driving a car that deals with vague or ambiguous conditions. For example, when you are taking a shower and the temperature of the water is very hot, then your control action will be to close a little the hot water valve and open the cold water valve moderately; you can use labels like "little" and "moderately" to describe fuzzy values in the elements. Those elements have a membership value in a fuzzy set. For example, the label "a little" could mean a value between 10° and 30° degrees of rotation of the valve and "moderately" a rotation between 20° and 40° of rotation of the valve. Of course, we do not have a mathematical model which relates the temperature of the water with the rotation of the valves but we can achieve a comfortable temperature of the water without problems. Fuzzy set can help solve this description without knowing a mathematical model.

Fuzzy sets are used for describing fuzziness based on degrees of membership and they can be used in many real situations with linguistic terms: measurement of temperature, speed, distance, height, etc.; for instance: The air is **fresh**, the electric vehicle is **very fast** but it can only achieve **short** distance trips, Tony is a **very tall** guy. But considering these scales, very often it is difficult to distinguish between memberships of some class of nonmembers. One of the problems that can arise when fuzzy logic is used is how to determine the values for describing the fuzzy terms. For example, how long is a short distance trip? It is a question that can generate several linguistic responses. Fuzzy logic type-2 can deal with this kind of problems because it can deal with uncertainties in words of different persons.

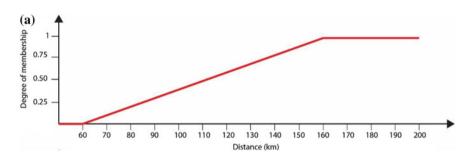

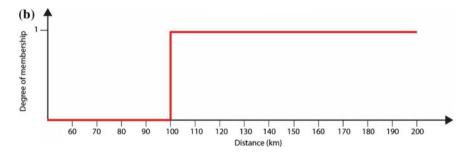

On the other hand, crisp distinctions are used to model this with conventional or Boolean sets and it forces an abrupt transition between the members and not members of a set; for example, we may say that a short trip is less than 100 km (e.g., 99.9 km) and by deduction, a trip larger than 100.1 km is in a long trip. For avoiding these inconsistencies, fuzzy logic could be used.

#### 1.3.2 Membership Function

When the Universal Set U is continuous or uncountable rather than discrete, membership functions can be expressed analytically by using continuous or piecewise explicit mathematical functions The basic idea of the Boolean logic is using only two membership values: true (1) or false (0), this Boolean logic cannot represent values between 1 and 0 that are used for defining with vague concepts. Let X be a Boolean (crisp) set and x an element of that set, then x belong to  $X (x \in X)$  or x do not belong to  $X \ (x \notin X)$ . The classical theory imposes a sharp boundary of the sets and all the values that belong to x have a set value of 1 and the others which do not belong have a value of 0. However, crisp sets do not deal with membership values. The principle of a fuzzy set is based on membership values. For instance, information can be used for describing a table of maximum distances achieved by electric vehicles, and it is possible to assign a certain degree of membership to each element. A membership function called "long distance" can be used to describe the set distance (the description of the fuzzy set can be done by discrete or continues forms). For illustrative purposes, all the membership functions shown in the following figures will be continuous. Table 1.1 presents a description for variable long distance.

Using continues approximations, it is possible to get the following representation (fuzzy membership function) in fuzzy and crisp forms (see Figs. 1.2 and 1.3).

In Fig. 1.2 is shown a fuzzy set for "long distance;" the horizontal axis represents the universe of discourse in this case which is between 50 and 200 km and the vertical axis represents the degree of membership; for crisp sets, the transition between nonmembership value and membership value is abrupt; so a value of 99 will have a degree of membership of 0 while 100 has a value of 1. On the other hand, for a fuzzy set the transition could have the form of any function; in this case, a line was selected for simplicity but it can have any shape according to the suggestions of an expert or a knowledge database, more recently artificial neural

| Table 1.1       Fuzzy set used for describing "long distance" in a discarte form | Vehicle | Distance | Crisp<br>value | Fuzzy membership<br>value |

|----------------------------------------------------------------------------------|---------|----------|----------------|---------------------------|

| a discrete form                                                                  | 1       | 80       | 0              | 0.2                       |

|                                                                                  | 2       | 160      | 1              | 1                         |

|                                                                                  | 3       | 90       | 0              | 0.3                       |

|                                                                                  | 4       | 100      | 1              | 0.4                       |

|                                                                                  | 5       | 103      | 1              | 0.43                      |

|                                                                                  | 6       | 70       | 0              | 0.1                       |

|                                                                                  | 7       | 170      | 1              | 1                         |

|                                                                                  | 8       | 190      | 1              | 1                         |

|                                                                                  | 9       | 120      | 1              | 0.6                       |

144

1

0.84

10

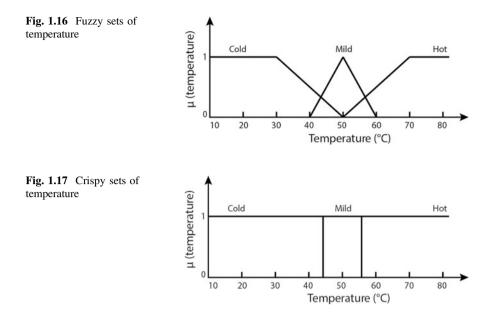

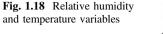

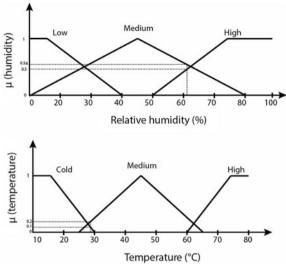

Fig. 1.2 Fuzzy set for "long distance"

Fig. 1.3 Crisp set for "long distance"

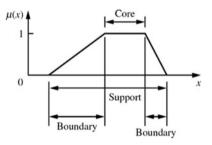

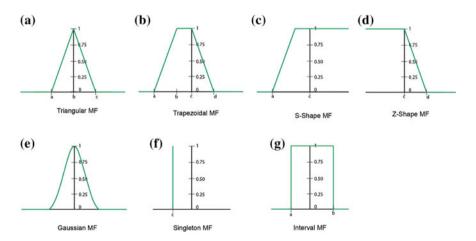

networks are combined with fuzzy logic on order to learn from the available data and derive the value of the fuzzy sets automatically. In the next sections, the most employed membership function are presented and their mathematical representation. Figure 1.4 depicts conventional membership functions.

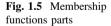

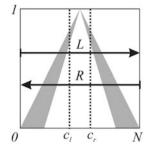

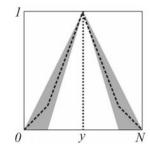

The main parts of the fuzzy membership function can be defined by the following terms (see Fig. 1.15):

Fig. 1.4 Different shapes of conventional membership functions

The *core* of a membership function for some fuzzy set *A*, is defined as that region of the universe that is characterized by complete and full membership value  $\mu_A(x) = 1$  in the set *A*. So, the elements in the set *A* that have a membership value equal to 1, are the elements that are part of the core.

**The** *support* of a membership function for some fuzzy set *A* is defined as that region of the universe that is characterized by nonzero membership value in the set *A*.

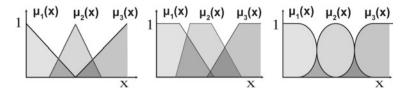

The *boundaries* of a membership function for some fuzzy set A are defined as that region of the universe containing elements that have a nonzero membership but not complete membership (Fig. 1.5).

As it was shown, there are several MF which can be used in T1FS; for example, the next normal membership functions presented above, A *normal or conventional* fuzzy set is one whose membership function has at least one element x in the universe whose membership value is one. The mathematical representation for some conventional membership functions is presented below.

#### Triangular MF

A triangular MF is defined by its parameters [a, b, c] such

$$\mu_A(x) = \begin{cases} \frac{x-a}{b-a} & a \le x \le b\\ \frac{c-x}{c-b} & b \le x \le c\\ 0 & x \le a \lor x \ge c \end{cases}$$

(1.1)

The shape of this function is shown in Fig. 1.6a.

#### Trapezoidal MF

A trapezoidal MF is defined by its parameters [a, b, c, d] such

$$\mu_{A}(x) = \begin{cases} \frac{x-a}{b-a} & a \le x \le b \\ 1 & b \le x \le c \\ \frac{d-x}{d-c} & c \le x \le d \\ 0 & x \le a \lor x \ge d \end{cases}$$

(1.2)

The shape of this function is shown in Fig. 1.6b.

# S-Shape MF

An S-shape MF is defined by its parameters [a, b] such

$$\mu_A(x) = \begin{cases} \frac{x-a}{b-a} & a \le x \le b\\ 1 & b \le x\\ 0 & x \le a \end{cases}$$

(1.3)

The shape of this function is shown in Fig. 1.6c.

#### Z-Shape MF

A Z-shape MF is defined by its parameters [c, d] such

$$\mu_A(x) = \begin{cases} 1 & x \le c \\ \frac{d-x}{d-c} & c \le x \le d \\ 0 & x \ge d \end{cases}$$

(1.4)

The shape of this function is shown in Fig. 1.6d.

Fig. 1.6 Membership functions shapes

#### Gaussian MF

A Gaussian MF is defined by its parameters  $[c, \sigma]$  such

$$\mu_A(x) = e^{-\frac{1}{2}\left(\frac{x-c}{\sigma}\right)^2}$$

(1.5)

The shape of this function is shown in Fig. 1.6e.

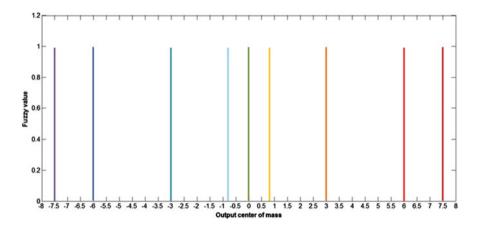

#### Singleton MF

A singleton MF is defined by its parameter c such as

$$\mu_A(x) = \begin{cases} 1 & x = c \\ 0 & \text{otherwise} \end{cases}$$

(1.6)

The shape of this function is shown in Fig. 1.6f.

#### Interval or Crisp MF

An interval or crisp MF is characterized by an interval [a, b]

$$\mu_A(x) = \begin{cases} 1 & a \le x \le b \\ 0 & \text{otherwise} \end{cases}$$

(1.7)

The shape of this function is shown in Fig. 1.6g; this membership shape is a particular case of T1FS where the membership is a crisp value as the traditional Boolean logic.

Such MF's are widely used in Type-1 FS for the fuzzification process (mapping from fuzzy to crisp value).

There are more possibly ways to assign membership values or functions to fuzzy variables than there are to assign probability density functions to random variables. This assignment process can be intuitive or it can be based on some algorithmic or logical operations. The following is a short list of methods described in the literature to assign membership values or functions to fuzzy variables.

- 1. Intuition—This method is simply derived from the capacity of humans to develop membership functions through their own innate intelligence and understanding.

- 2. Inference—It uses knowledge to perform deductive reasoning. That is to deduce or infer a conclusion, given a body of facts and knowledge.

- 3. Rank ordering—Assessing preferences by a single individual, a committee, a poll, and other opinion methods can be used to assign membership values to a fuzzy variable.

- 4. Inductive reasoning—An automatic generation of membership functions can also be accommodated by using the essential characteristic of *inductive reasoning*, which derives a general consensus from the particular (derives the generic from the specific). The induction is performed by the entropy minimization principle, which clusters most optimally the parameters corresponding to the output classes.

On the other hand, the operations on fuzzy sets are defined by means of their membership functions so that the definitions of those operations generalize their equivalents in crisp set theory.

Intersection: given the fuzzy sets A and B, defined in U with  $\mu_A$  and  $\mu_B$  membership functions and their intersection is the fuzzy set:

$$A \cap B = \{x, (\mu_{A \cap B}(x)) | x \in U\}, \quad \text{with } \mu_{A \cap B}(x) = \mu_A(x) \sim \wedge \mu_B(x)$$

Intersection operators belong to the class of Triangular Norms or T-Norms. These are binary operators defined in the interval [0, 1] satisfying the following properties:

$$T(0,1) = T(1,0) = T(0,0) = 0, T(1,1) = 1; (agreement with boolean AND).$$

$$T(x,1) = x, \forall x \in [0,1]; (identity).$$

$$T(x,y) = T(y,x), \forall x, y \in [0,1]; (commutativity).$$

$$T(x1,y) \le T(x2,y), \forall x1, x2, y \in [0,1], x1 \le x2; (monotocity).$$

Some operators have been proposed like T-Norms. The most used ones are the following:

$$\begin{array}{ll} \min: & \mu_{A \cap B}(x) = \mu_A(x) \sim \wedge \mu_B(x) = \min(\mu_A(x), \mu_B(x));\\ \text{algebraic product}: & \mu_{A \cap B}(x) = \mu_A(x) \sim \wedge \mu_B(x) = \mu_A(x)\mu_B(x);\\ \text{bounded difference}: & \mu_{A \cap B}(x) = \mu_A(x) \sim \wedge \mu_B(x) = \max(0, \mu_A(x) + \mu_B(x) - 1); \end{array}$$

Union: given the fuzzy sets A and B, defined in U with  $\mu_A$  and  $\mu_B$  membership functions and their union is the fuzzy set:

$$A \cup B = \{x, (\mu_{A \cup B}(x)) | x \in U\}, \text{ and } \mu_{A \cup B}(x) = \mu_A(x) \sim \lor \mu_B(x),$$

Union operators belong to the class of S-Norms or Triangular Co-Norms (T-Co-Norms). These are binary operators defined in the interval [0, 1] satisfying the following properties:

S(0, 1) = S(1, 0) = S(1, 1) = 1, S(0, 0) = 0; (agreement with boolean OR).  $S(x, 0) = x, \forall x \in [0, 1];$  (identity).  $S(x, y) = S(y, x), \forall x, y \in [0, 1];$  (commutativity).  $S(x1, y) \le S(x2, y), \forall x1, x2, y \in [0, 1], x1 \le x2;$  (monotonicity). Some operators have been proposed as T-CoNorms. The most used are following:

$$\begin{aligned} \max : \quad & \mu_{A\cup B}(x) = \mu_A(x) \sim \lor \mu_B(x) = \max(\mu_A(x), \mu_B(x)); \\ \text{algebraic sum} : \quad & \mu_{A\cup B}(x) = \mu_A(x) \sim \lor \mu_B(x) = \mu_A(x) + \mu_B(x) - \mu_A(x)\mu_B(x); \\ \text{bounded sum} : \quad & \mu_{A\cup B}(x) = \mu_A(x) \sim \lor \mu_B(x) = \min(1, \mu_A(x) + \mu_B(x)); \end{aligned}$$

Complement: given the fuzzy set *A* defined in the Universe of Discourse U, its complement is the fuzzy set:

$$\overline{A} = \left\{ x, (\mu_{\overline{A}}(x)) | x \in U \right\} \text{ and } \mu_{\overline{A}}(x) = \sim \neg(\mu_A(x)) = 1 - \mu_A(x)$$

where  $\sim \neg$  denotes the "fuzzy negation" of a membership function, coincident in this case with the complement operator for crisp sets. There are others complement operators  $\sim \neg$ . In general, they are C-Norms.

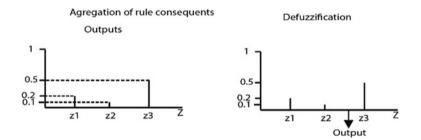

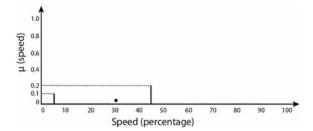

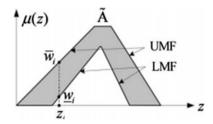

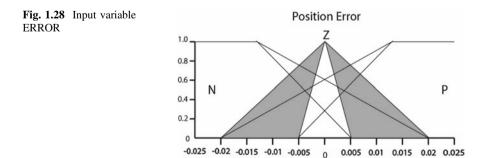

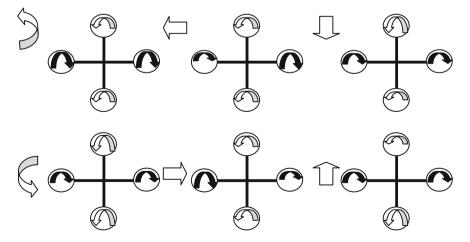

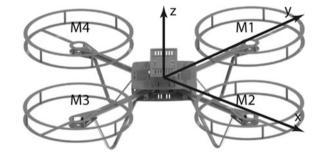

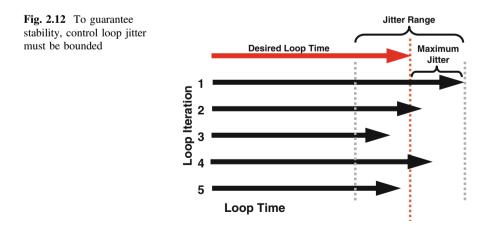

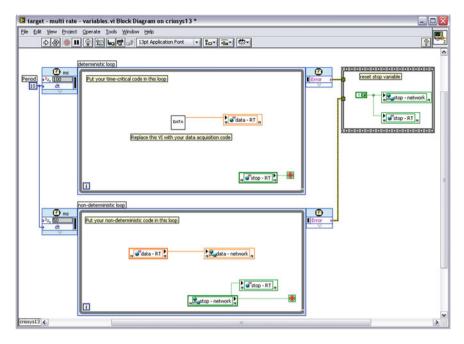

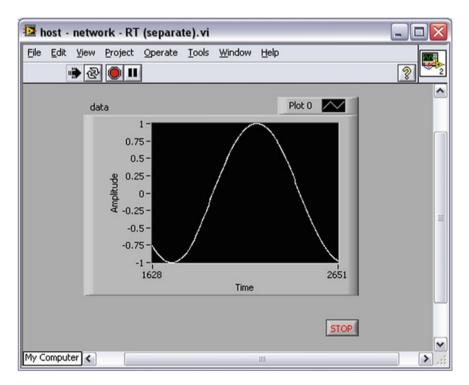

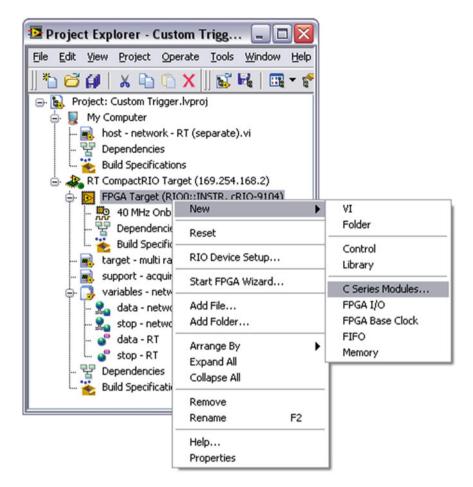

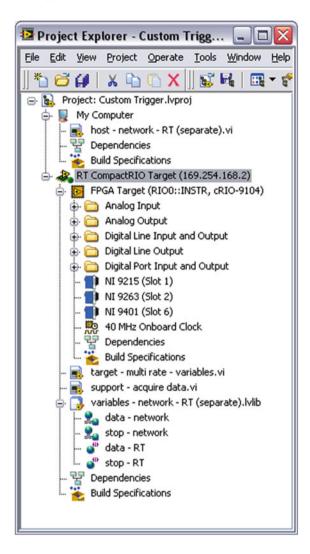

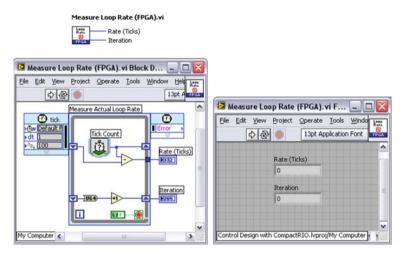

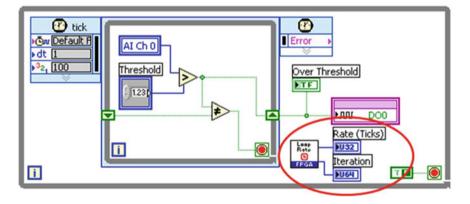

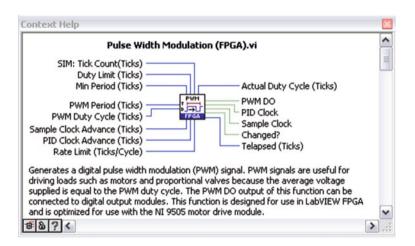

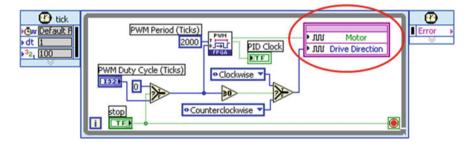

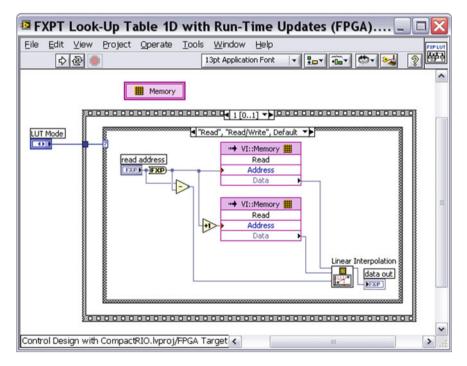

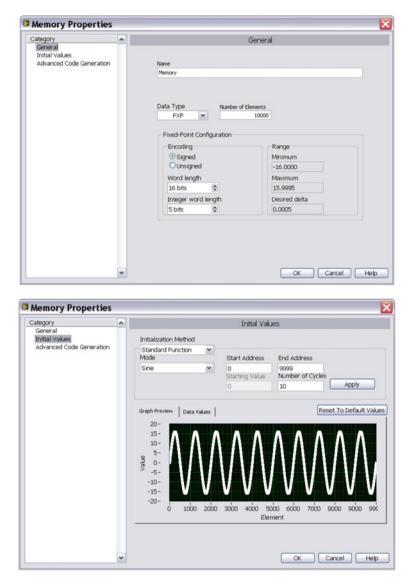

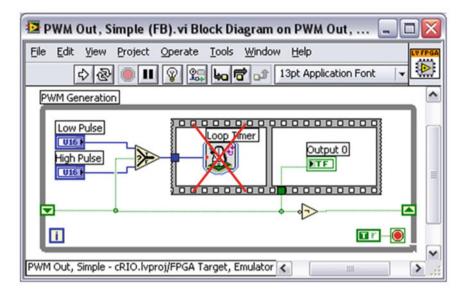

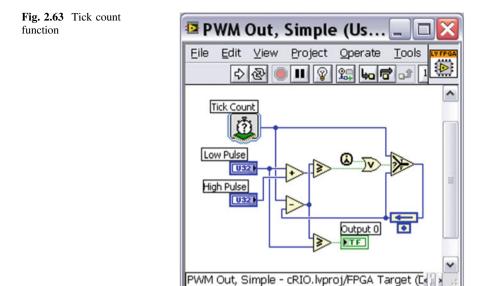

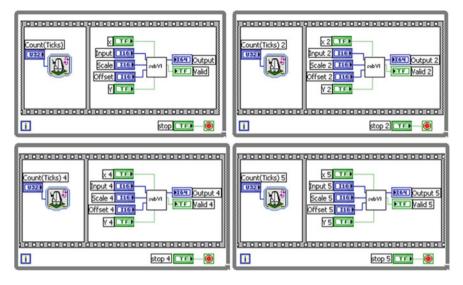

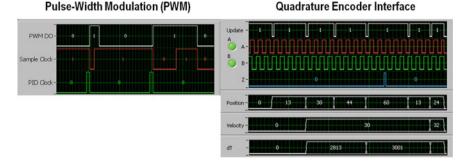

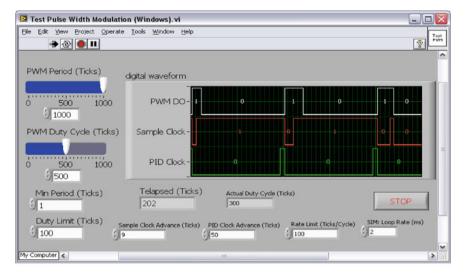

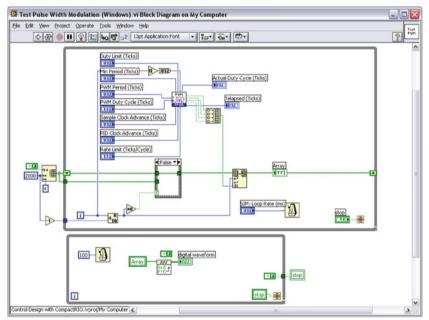

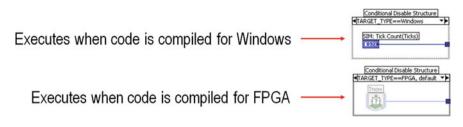

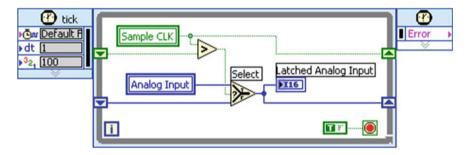

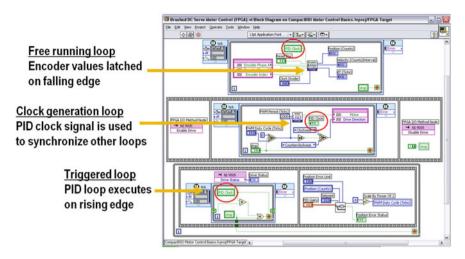

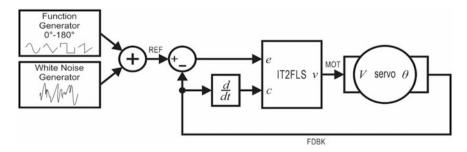

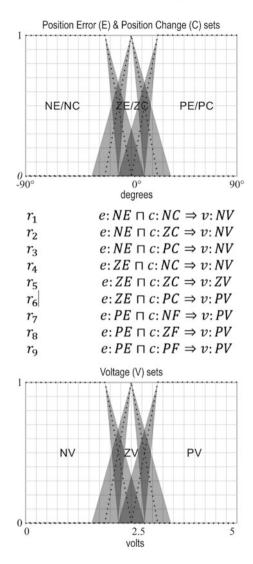

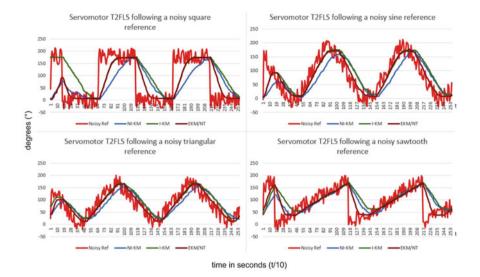

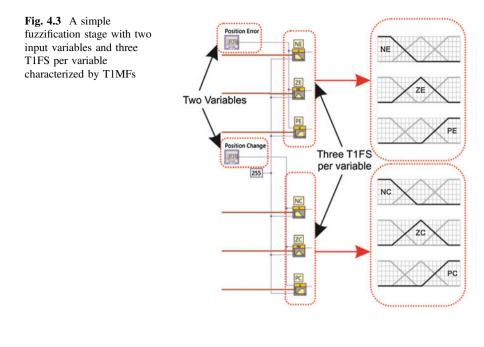

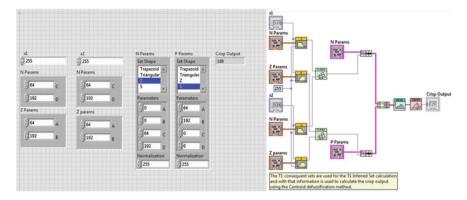

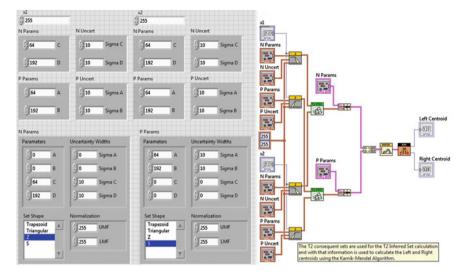

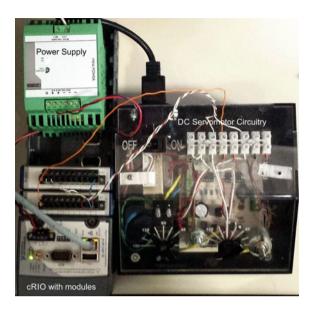

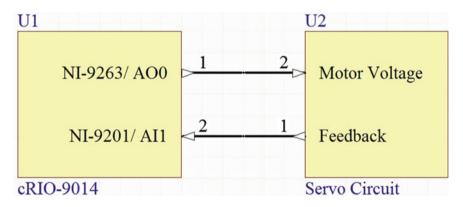

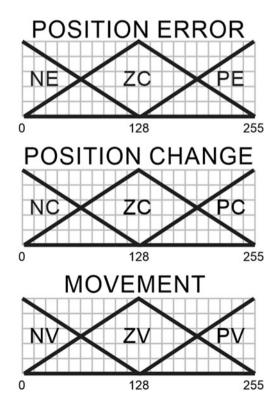

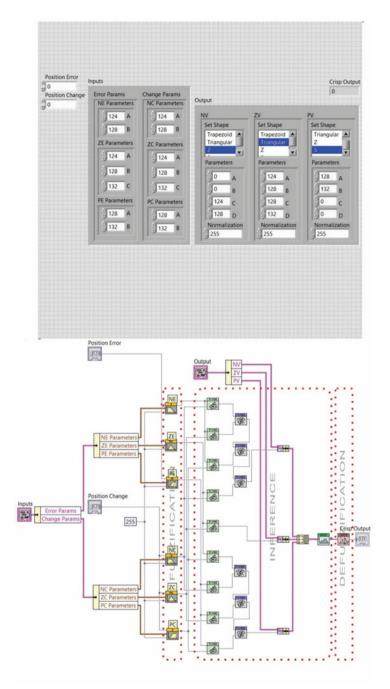

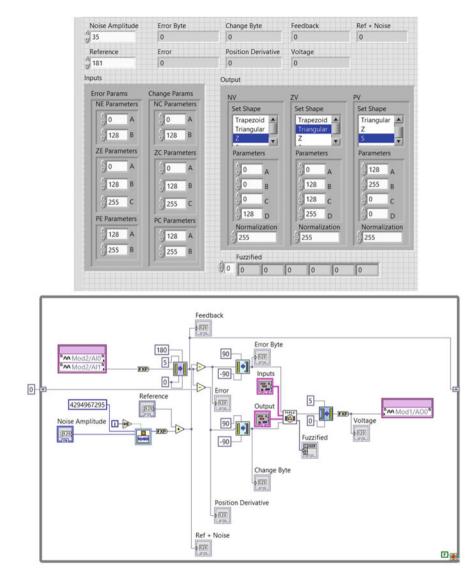

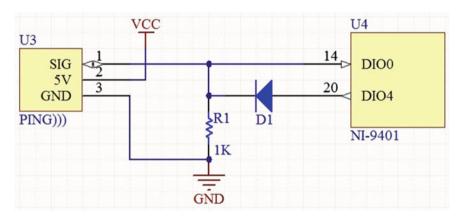

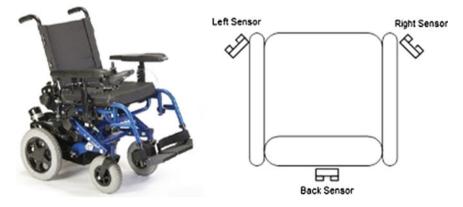

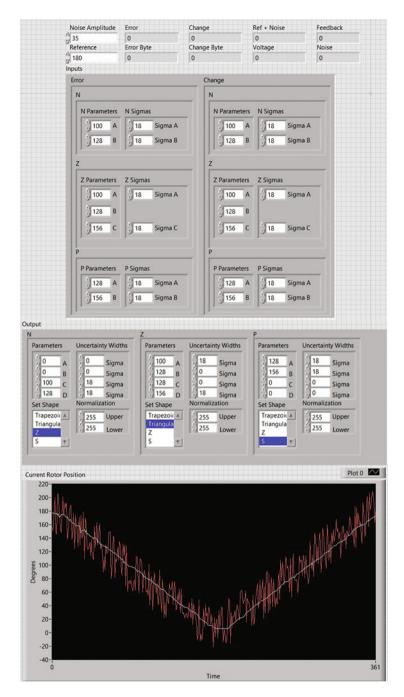

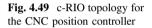

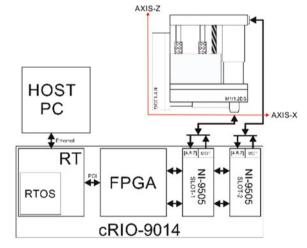

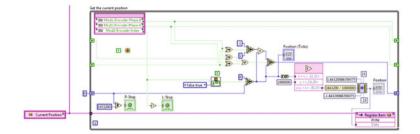

# 1.3.3 Discourse Universe and Membership Degree