# Fundamentals of Electronics 1

Electronic Components and Elementary Functions

Pierre Muret

WILEY

| First published 2017 in Great Britain and the United                                                                                                       | d States by ISTE Ltd and John Wiley & Sons, Inc.                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| permitted under the Copyright, Designs and Paten<br>stored or transmitted, in any form or by any means<br>or in the case of reprographic reproduction in a | research or private study, or criticism or review, as ts Act 1988, this publication may only be reproduced, with the prior permission in writing of the publishers, ecordance with the terms and licenses issued by the these terms should be sent to the publishers at the |

| ISTE Ltd<br>27-37 St George's Road<br>London SW19 4EU<br>UK<br>www.iste.co.uk                                                                              | John Wiley & Sons, Inc. 111 River Street Hoboken, NJ 07030 USA www.wiley.com                                                                                                                                                                                                |

The rights of Pierre Muret to be identified as the author of this work have been asserted by him in

accordance with the Copyright, Designs and Patents Act 1988.

A CIP record for this book is available from the British Library

Library of Congress Control Number: 2017944816

British Library Cataloguing-in-Publication Data

© ISTE Ltd 2017

ISBN 978-1-78630-181-9

### Contents

| Preface                                                                                                                                           | ix   |

|---------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Introduction                                                                                                                                      | xiii |

| Chapter 1. Diodes and Applications                                                                                                                | 1    |

| <ul><li>1.1. Semiconductor physics and current transport in pn diodes</li><li>1.1.1. Energy and concentration of mobile charge carriers</li></ul> | 1    |

| (electrons and holes)                                                                                                                             | 1    |

| 1.1.2. Conduction mechanisms                                                                                                                      | 6    |

| 1.2. Simplified models of the pn diode                                                                                                            | 9    |

| 1.3. Diode circuitry (reviewed in exercises)                                                                                                      | 9    |

| 1.4. Detailed model of pn diode: variable conditions and                                                                                          |      |

| effect of temperature                                                                                                                             | 10   |

| 1.4.1. Junction at equilibrium (at zero voltage or in                                                                                             |      |

| open circuit): diffusion potential                                                                                                                | 10   |

| 1.4.2. Biased junction (or out of equilibrium): effect of                                                                                         |      |

| an external potential difference                                                                                                                  | 13   |

| 1.4.3. Effects of temperature                                                                                                                     | 17   |

| 1.4.4. Capacitive effects                                                                                                                         | 19   |

| 1.5. Different types of diode and their functions                                                                                                 | 23   |

| 1.5.1. Zener diode                                                                                                                                | 23   |

| 1.5.2. Schottky diode or metal–semiconductor diode                                                                                                | 23   |

| 1.5.3. Light emitting diodes and laser diodes                                                                                                     | 25   |

| 1.5.4. Photodiodes and photovoltaic generators                                                                                                    | 25   |

| 1.6. Exercises                                                                                                                                    | 27   |

| 1.6.1. Analyze the operation of the following circuits for a                                                                                      |      |

| sinusoidal voltage generator and ideal diodes (a) with no                                                                                         |      |

| threshold and (b) with a threshold $U_0 \dots \dots \dots \dots$                                                                                  | 27   |

| 1.6.2. Study of the current variations in a forward biased                                                                                        |      |

| pn diode under influence of temperatures                                                                                                          | 30   |

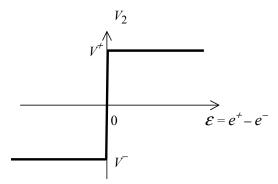

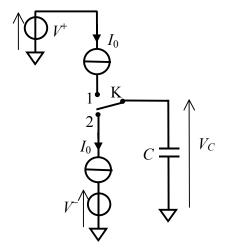

|    | $\epsilon$                                                          | 32        |

|----|---------------------------------------------------------------------|-----------|

|    | 8                                                                   | 35        |

|    | 1.6.5. Switching diode: study on opening                            | 37        |

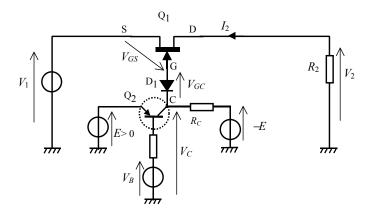

| CI | hapter 2. Bipolar Junction Transistors and Applications             | 41        |

|    | 2.1. The transistor effect                                          | 41        |

|    | 2.2. Dipolar janetion translator (of Dt 1) models and types         | 44        |

|    |                                                                     | 44        |

|    | 2.2.2. The heterojunction bipolar transistor (or HBT)               |           |

|    |                                                                     | 48        |

|    | 2.3. Bipolar junction transistor in static regimes and applications |           |

|    | C( DL)                                                              | 49        |

|    |                                                                     | 49        |

|    |                                                                     | 50        |

|    | 2.3.3. Circuits for transistor bias: current sources and            |           |

|    |                                                                     | 53        |

|    | $\epsilon$                                                          | 55        |

|    |                                                                     | 56        |

|    |                                                                     | 56        |

|    |                                                                     | 62        |

|    | 1 1                                                                 | 63<br>65  |

|    | 1                                                                   | 63<br>67  |

|    | 1 1 1                                                               | 67<br>67  |

|    |                                                                     | 70        |

|    | · · · · · · · · · · · · · · · · · · ·                               | 70<br>71  |

|    |                                                                     | 71<br>73  |

|    |                                                                     | 74        |

|    |                                                                     | , -<br>74 |

|    | 1                                                                   | 73<br>78  |

|    | 2.9.3. Amplifiers with rest current zero or low relative            | , 0       |

|    |                                                                     | 84        |

|    | 2.9.4. Cascode circuit and frequency responses                      |           |

|    |                                                                     | 89        |

|    | •                                                                   |           |

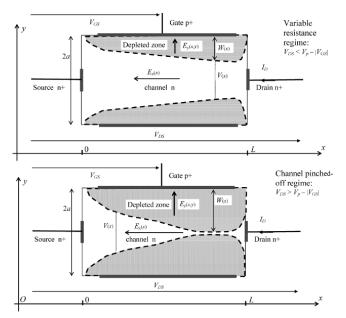

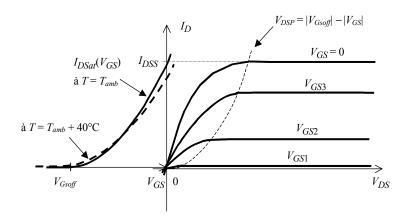

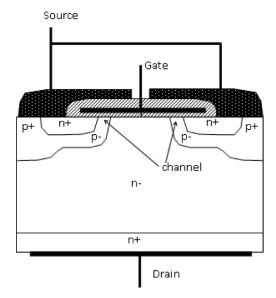

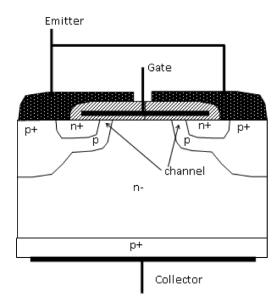

| CI | hapter 3. Field Effect Transistors and Applications                 | 95        |

|    | 3.1. Operating principle of junction field effect transistors       |           |

|    |                                                                     | 95        |

|    |                                                                     | 00        |

|    |                                                                     | 04        |

|    |                                                                     | 04        |

|    | 3.3.2. Other field effect transistors.                              | 06        |

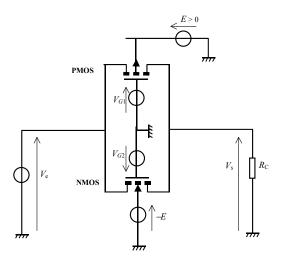

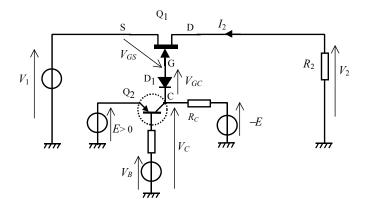

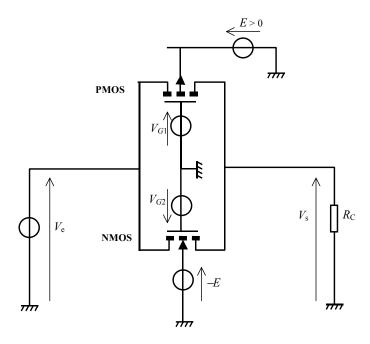

| 3.4. Applications of field effect transistors                           | 109<br>109<br>110 |

|-------------------------------------------------------------------------|-------------------|

| voltage and JFET analog switch                                          | 111               |

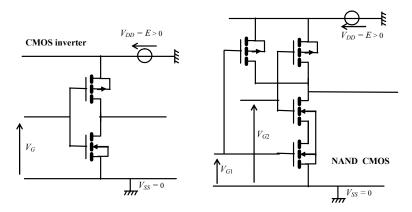

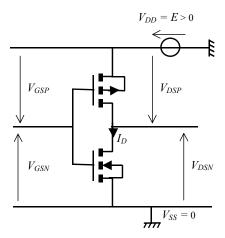

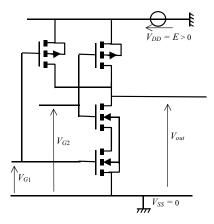

| (with complementary MOSFET)                                             | 112               |

|                                                                         |                   |

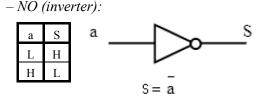

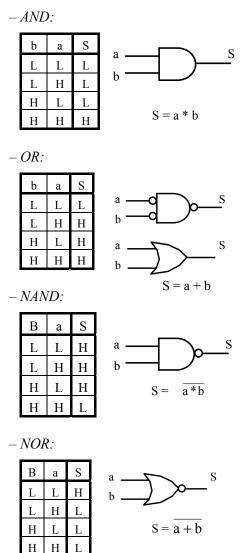

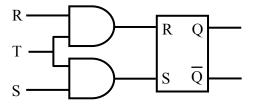

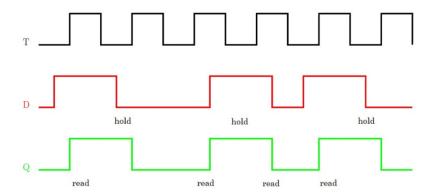

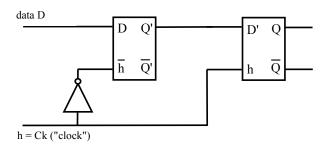

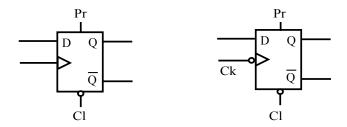

| 3.4.5. Combinatorial logic functions                                    | 114               |

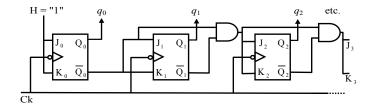

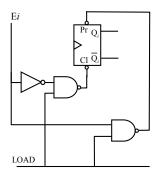

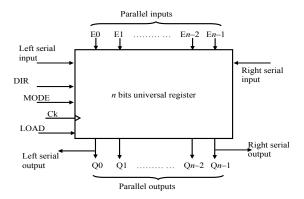

| 3.4.6. Sequential logic functions                                       | 126               |

| 3.5. Exercises                                                          | 135               |

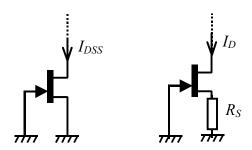

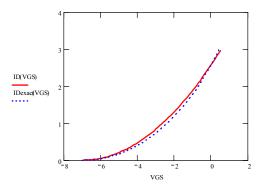

| 3.5.1. Parabolic approximation of the JFET characteristic $I_D(V_{GS})$ | 105               |

| in pinched-off (or saturated) regime                                    | 135               |

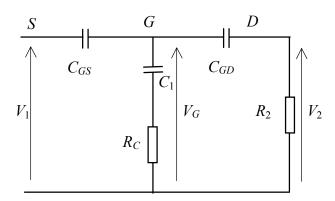

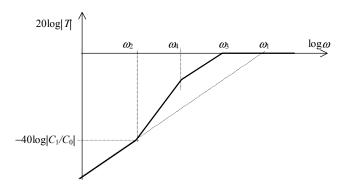

| 3.5.2. JFET analog switch; input–output insulation in off-state         | 138               |

| 3.5.3. MOSFET circuits                                                  | 141               |

|                                                                         |                   |

| Chapter 4. Amplifiers, Comparators and Other                            | 4.40              |

| Analog Circuits                                                         | 149               |

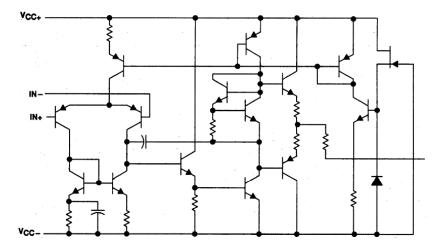

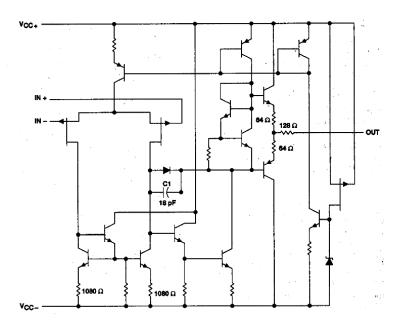

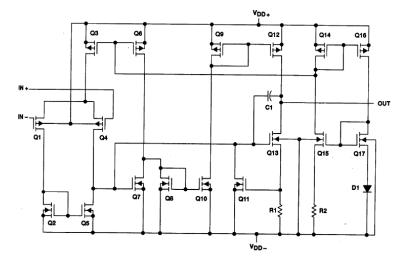

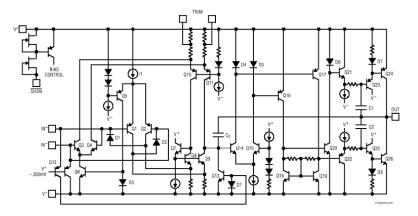

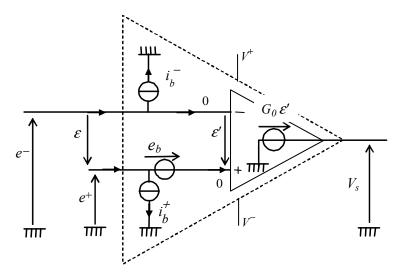

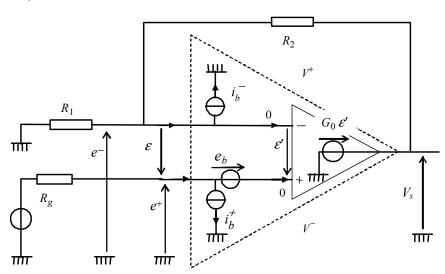

| 4.1. Operational amplifiers, operating principle and types              | 149               |

| 4.1.1. Standard operational amplifiers                                  | 149               |

| 4.1.2. Operational amplifiers with specific properties                  | 151               |

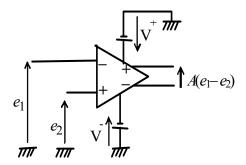

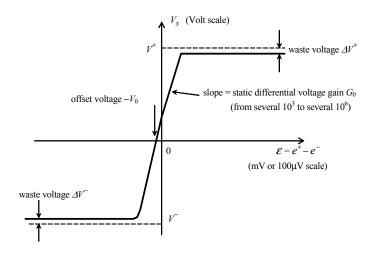

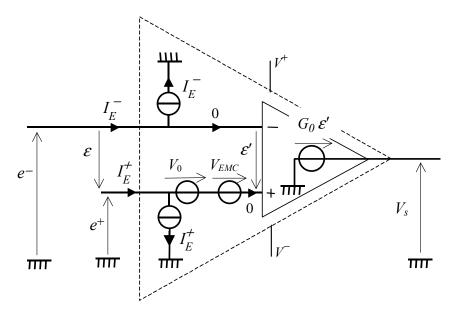

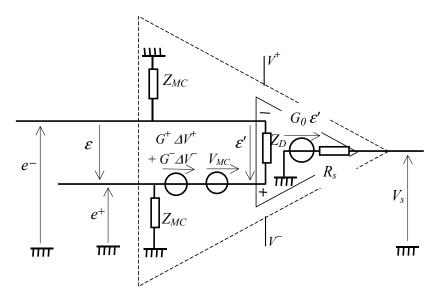

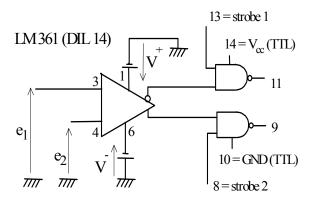

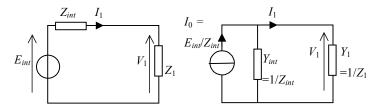

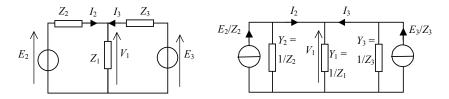

| 4.2. Operational amplifier models and responses                         | 153               |

| 4.2.1. Static model of voltage amplifier                                | 153               |

| 4.2.2. Dynamic and switched mode operations                             | 155               |

| 4.3. Comparators                                                        | 156               |

| 4.4. Noise in amplifiers                                                | 157               |

| 4.4.1. Noise nature and evaluation.                                     | 157               |

| 4.4.2. Various types of noise and their origin                          | 158               |

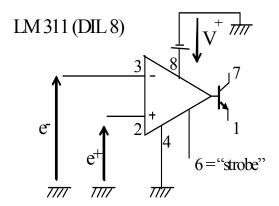

| 4.4.3. Equivalent circuit of noise sources in amplifiers                | 136               |

|                                                                         | 160               |

| and noise figure                                                        | 162               |

| 4.4.4. Low-noise amplifiers                                             | 162               |

| 4.5. Analog integrated circuits                                         | 163               |

| 4.6. Exercises                                                          |                   |

| 4.6.1. Responses of operational amplifier differential stage            | 163               |

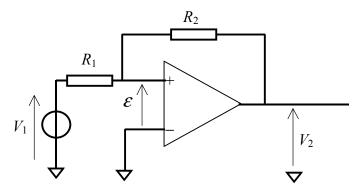

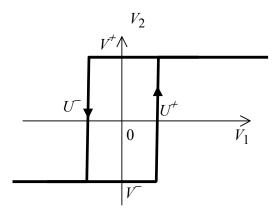

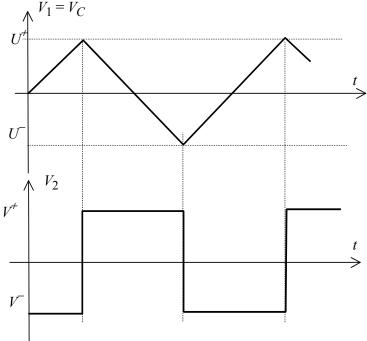

| 4.6.2. Generation of triangle and square wave signals:                  | 4.00              |

| voltage to frequency conversion                                         | 168               |

| 4.6.3. Noise figure of an operational amplifier circuit                 | 172               |

| Appendix                                                                | 175               |

| Bibligraphy                                                             | 187               |

| Index                                                                   | 189               |

### **Preface**

Today, we can consider electronics to be a subject derived from both the theoretical advances achieved during the 20th Century in areas comprising the modeling and conception of components, circuits, signals and systems, together with the tremendous development attained in integrated circuit technology. However, such development led to something of a knowledge diaspora that this work will attempt to contravene by collecting both the general principles at the center of all electronic systems and components, together with the synthesis and analysis methods required to describe and understand these components and subcomponents. The work is divided into three volumes. Each volume follows one guiding principle from which various concepts flow. Accordingly, Volume 1 addresses the physics of semiconductor components and the consequences thereof, that is, the relations between component properties and electrical models. Volume 2 addresses continuous time systems, initially adopting a general approach in Chapter 1, followed by a review of the highly involved subject of quadripoles in Chapter 2. Volume 3 is devoted to discrete-time and/or quantized level systems. The former, also known as sampled systems, which can either be analog or digital, are studied in Chapter 1, while the latter, conversion systems, we address in Chapter 2. The chapter headings are indicated in the following general outline.

Each chapter is paired with exercises and detailed corrections, with two objectives. First, these exercises help illustrate the general principles addressed in the course, proposing new application layouts and showing how theory can be implemented to assess their properties. Second, the exercises act as extensions of the course, illustrating circuits that may have been described briefly, but whose properties have not been studied in detail. The

first volume should be accessible to students with a scientific literacy corresponding to the first 2 years of university education, allowing them to acquire the level of understanding required for the third year of their electronics degree. The level of comprehension required for the following two volumes is that of students on a master's degree program or enrolled in engineering school.

In summary, electronics, as presented in this book, is an engineering science that concerns the modeling of components and systems from their physical properties to their established function, allowing for the transformation of electrical signals and information processing. Here, the various items are summarized along with their properties to help readers follow the broader direction of their organization and thereby avoid fragmentation and overlap. The representation of signals is treated in a balanced manner, which means that the spectral aspect is given its proper place, to do otherwise would have been outmoded and against the grain of modern electronics, since now a wide range of problems are initially addressed according to criteria concerning frequency response, bandwidth and signal spectrum modification. This should by no means overshadow the application of electrokinetic laws, which remains a necessary first step since electronics remains fundamentally concerned with electric circuits. Concepts related to radio-frequency circuits are not given special treatment here, but can be found in several chapters. Since the summary of logical circuits involves digital electronics and industrial computing, the part treated here is limited to logical functions that may be useful in binary numbers computing and elementary sequencing. The author hopes that this work contributes to a broad foundation for the analysis, modeling and synthesis of most active and passive circuits in electronics, giving readers a good start to begin the development and simulation of integrated circuits.

#### **Outline**

- 1) Volume 1: Electronic components and elementary functions.

- i) Diodes and applications

- ii) Bipolar transistors and applications

- iii) Field effect transistor and applications

- iv) Amplifiers, comparators and other analog circuits

- 2) Volume 2: Continuous-time signals and systems [MUR 17a].

- i) Continuous-time stationary systems: General properties, feedback, stability, oscillators

- ii) Continuous-time linear and stationary systems: Two-port networks, filtering and analog filter synthesis

- 3) Volume 3: Discrete-time signals and systems and conversion systems [MUR 17b].

- i) Discrete-time signals: Sampling, filtering and phase control, frequency control circuits

- ii) Quantized level systems: Digital-to-analog and analog-to-digital conversions

Pierre MURET June 2017

### Introduction

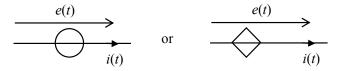

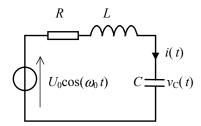

In this first volume, we address the physics of semiconductor devices directly through electrostatics and the laws steering the transport of charge carriers. This allows us to broach the governing principles at work in semiconductor electric components, which are described and quantified in order to expose the relations that control external electric quantities. Through the first three chapters, devoted, respectively, to diodes, bipolar transistors and field effect transistors, the electrical characteristics of these components can be deduced and expressed as electric models. We then consider the static or instantaneous voltages and currents present in these nonlinear or linear electric models to obtain the properties of active circuits made using these components and passive elements. In some cases, these considerations will require students to solve first-order differential equations or use complex impedance and transmittance to represent values in sinusoidal conditions (see Appendix).

Each chapter emphases the applications derived from these models, in terms of analog and logical functions, a majority of which are based on the original nonlinearity of the components. Conversely, linearized models become useful mainly from Chapter 2 onwards, to help with in-depth analysis of the amplifier circuits, and in particular for the operational amplifiers in Chapter 4. In this volume, the study of signal representations is kept to a strict minimum, largely confined to the Appendix, with the exception of the noise problem in amplifiers in Chapter 4. The content of the Appendix should be of use for the wider public who may be unfamiliar with

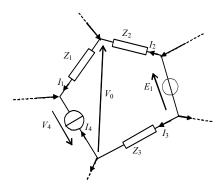

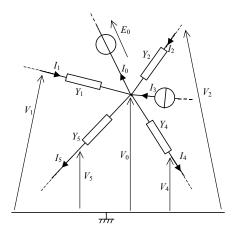

the laws and theorems of electrokinetics, which are indispensable in this volume covering a variety of electronic circuits and equivalent component circuits. Exercises allow a deeper analysis of fundamental layouts comprising a small number of active devices, typically from two to 10.

### **Diodes and Applications**

### 1.1. Semiconductor physics and current transport in pn diodes

# 1.1.1. Energy and concentration of mobile charge carriers (electrons and holes)

Studies of electrons' physical properties indicate that they appear either as particles with a movement quantity (or impulse) of p and mass m, or as waves of wavelength  $\lambda$  and wave vector k. Between these values, De Broglie's wave mechanics establishes the following relation:  $p = \hbar k = \frac{h}{\lambda}$ , where  $h = 6.62 \times 10^{-34}$  J·s and  $\hbar = h/2\pi$ .

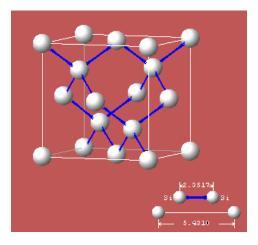

Figure 1.1. Silicon crystal lattice (Angstrom distances, equal to 0.1 nm)

Here, kinetic energy is  $E_c = \frac{p^2}{2m}$ , while potential energy corresponds to the work of the attractive force between 1 electron and 1 proton until they are approximately separated by the atomic radius, that is  $a_0 \approx 0.2$  nm;

therefore,

$$U = \int_{a_0}^{\infty} \frac{e^2}{4\pi\epsilon r^2} dr = \frac{e^2}{4\pi\epsilon a_0}$$

(with  $e = 1.6 \times 10^{-19}$  Coulomb and  $\epsilon \approx$

$10^{-10}$  Farad/m in a semiconductor such as Si) to the order of  $10^{-19}$  J, or a little less than 1 eV.

In an isolated atom, quantum mechanics makes a connection between energy and the wave frequency associated with each electron, so that the energy of each can only take certain values known as energy levels. When the atoms are in a solid such as silicon, which can hold a crystal shape where atoms are arranged in a regular and periodic manner in space (Figure 1.1), the potential in terms of the electrons is that determined by the atoms' nuclei as well as other electrons, also becoming regular and periodic in space.

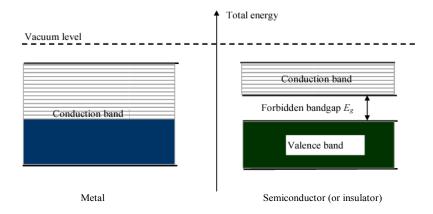

A consequence of this is the transformation of energy levels into allowed energy bands separated by a forbidden bandgap (Figure 1.2). These allowed bands are made up of as many energy levels as there are electrons in the solid, also known as energy states or quantum states, spread over an energy range of several electron volts.

Figure 1.2. Energy bands of a solid (full and empty quantum states in dark and hatched color, respectively)

Only a single electron can be placed in the allowed bands per quantum state, both for isolated atoms and in solids.

Conduction is only possible if electrons can change quantum state, as this allows them to acquire kinetic energy and movement. This change can occur in the case of metals, as the allowed band with the highest energy levels, known as the conduction band, is only ever partially filled; conversely, this can only occur when the temperature increases above absolute zero in semiconductors, since the forbidden band separates a full valence band from an empty conduction band at absolute zero. This is because thermal excitation induces the transfer of some electrons from the valence band into the conduction band. In the case of semiconductors, statistics show that the product of electron concentration n in the conduction band and of holes p (that is the absence of electrons that may be considered as positively charged particles with a positive mass) in the valence band is equal to the square of the intrinsic concentration n:

$$n.p = n_i^2 = N_c N_v \exp(-E_g/kT)$$

where  $E_g$  = width of the forbidden bandgap, k = Boltzmann constant = 1.38 × 10<sup>-23</sup> J/K and  $N_c$ ,  $N_v$  = density of effective state in the conduction and valence bands (m<sup>-3</sup>) so that  $N_c N_v = B T^3$  (T in °K and B to the order of 5 × 10<sup>43</sup> m<sup>-6</sup> K<sup>-3</sup> for silicon).

Solids with semiconductor characteristics are chiefly those whose atoms have 4 electrons on their peripheral layer, that is those in column IV of the periodic table (2s<sup>2</sup> 2p<sup>2</sup> configuration for diamond, 3s<sup>2</sup> 3p<sup>2</sup> for silicon, 4s<sup>2</sup> 4p<sup>2</sup> for germanium, or mixed for SiC) or also those made up of atoms from columns III and V (called III–V, such as GaAs, GaP, InP, InAs, GaN, AlN and InN) or columns II and VI (called II–VI, such as ZnO, ZnSe, CdTe, CdS and ZnTe).

Accordingly, we can only consider the peripheral electrons, of which there are on average 4 per atom, whose charge is balanced by four nucleus protons (either 3 and 5, or 2 and 6 for materials III–V and II–VI, respectively).

| 2        | 3              | 4  | 5        | 6  | 7  | 8                  | 9  | 10 | 11 | 12                  | 13 | 14 | 15 | 16 | 17  | 18 |

|----------|----------------|----|----------|----|----|--------------------|----|----|----|---------------------|----|----|----|----|-----|----|

| <u> </u> |                |    |          |    |    |                    |    |    |    | п                   | Ш  | IV | v  | VI | VII | Не |

| Li Be    |                |    |          |    |    |                    |    |    |    |                     | B  | C  | N  | Ö  | F   | Ne |

| Na Mg    |                |    |          |    |    |                    |    |    |    |                     | Al | Si | P  | S  | ČI  | Ār |

| K Ca     | Sc             | Ti | V 23     | Cr | Mn | Fe                 | Co | Ni | Cu | <sup>30</sup><br>Zn | Ga | Ge | As | Se | Br  | Kr |

| Rb Sr    | 39<br><b>Y</b> | Źr | Nb<br>Nb | Mo | Tc | <del>u</del><br>Ru | Rh | #d | Ag | Cd                  | In | Sn | Sb | Te | 53  | Xe |

Figure 1.3. Periodic table of elements

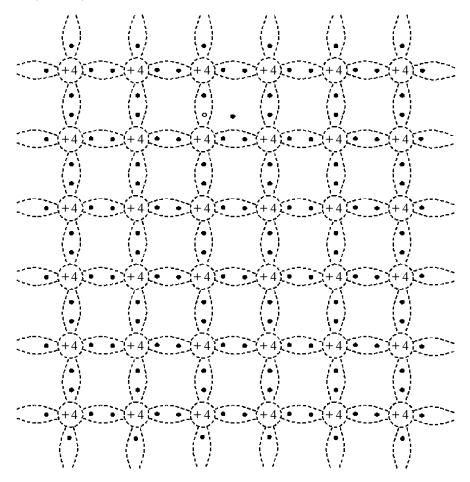

In intrinsic semiconductors, that is ideally without any impurities, there are as many holes as electrons, such that  $n = p = n_i$ , the density of intrinsic carriers, since an excited electron in the conduction band automatically leaves a hole in the valence band (Figure 1.4).

This situation is modified by doping, which corresponds to the introduction of foreign atoms, also known as impurities. Doped semiconductors are far more useful, since we can favor either conduction by electrons or conduction by holes. The relation  $n \cdot p = n_l^2$  still applies, however:

- for *n* doping of semiconductors IV-IV:  $n = N_D >> p$  by introducing atoms located in a column further to the right, which then become a concentration of  $N_D$  donors;

- for p doping of semiconductors IV-IV:  $p = N_A >> n$  by introducing atoms located in a column further to the left, which then become a concentration of  $N_A$  acceptors. For III-V and II-VI, doping occurs along the same lines, that is by increasing or decreasing the number of nucleus protons by one unit with the impurity relative to the atom that is being replaced.

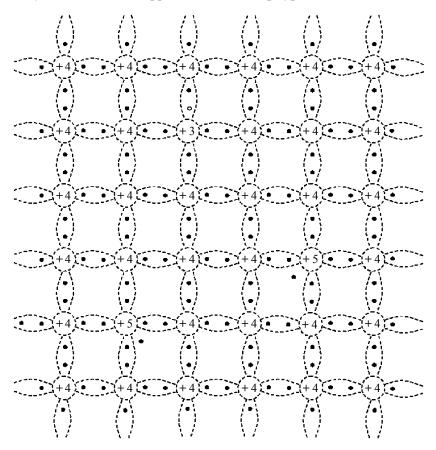

By means of doped semiconductors (Figure 1.5), we can obtain zones with localized charges (ionized donors or acceptors) if the mobile carriers (electrons or holes) have been carried into another zone of the component by an electric field.

The combination of several such zones, known as space-charge zones or more commonly, depleted zones, also allows us to obtain this electric field and create components. Moreover, a p type zone in contact with an n type zone forms a pn diode. The asymmetry of fixed charges in both zones leads to asymmetry of electrical characteristics and the rectification effect.

Figure 1.4. Flattened structure of a doped intrinsic covalent semiconductor (electrons represented by a full black circle, holes by a hollow black circle)

The fixed charges that remain in a depletion zone after the departure of electrons are positive due to the surplus positive charge (5+ on the proton and 4– for the peripheral electrons) on the nucleus of ionized donors. On the other hand, the fixed charges that remain in a type p depletion zone after the departure of holes are negative due to the electron that has taken the place of the hole when it leaves the ionized acceptor (3+ on the proton and 4– for the

peripheral electrons), which is a surplus negative charge (Figure 1.5). In an n-type semiconductor, the electrons are majority carriers while the holes are minority carriers, and the opposite is true for a p-type semiconductor.

Figure 1.5. Flattened structure of a doped covalent semiconductor (electrons represented by a full black circle, holes by a hollow black circle)

#### 1.1.2. Conduction mechanisms

In neutral semiconductors and depletion zones, we see two types current density (in  $A/m^2$  or  $A/cm^2$ ) in steady state:

– a conduction current density  $en\mu_n$  **E** for electrons and  $ep\mu_p$  **E** for holes, or in total  $\mathbf{J}_c = e(n\mu_n + p\mu_p)$  **E**, where  $\mu_n$  and  $\mu_p$  is the mobility of electrons

and holes, respectively, and **E** is the electric field vector, which gives rise to the Ohm law in conductors.

- a diffusion current density:  $eD_n \underline{grad}(n) = \mu_n kT \underline{grad}(n)$  for electrons,  $-eD_p \underline{grad}(p) = -\mu_p kT \underline{grad}(p)$  for holes, with  $D_n$  and  $D_p$  representing the diffusion coefficients according to the Einstein relation  $D_n = \mu_n kT/e$  and  $D_p = \mu_p kT/e$ , that is, in total  $J_d = \mu_n kT \underline{grad}(n) - \mu_p kT \underline{grad}(p)$ .

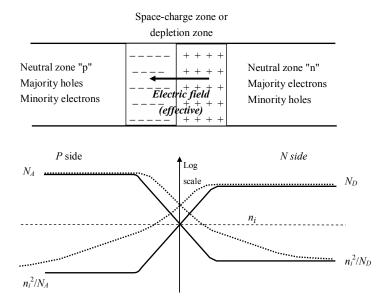

However, the spatial shape of potential in the depletion zones will determine these currents, since it is here that we find the strongest electric fields and charge carrier concentration gradients. We can discern the two p and n zones of the pn diode, each of which is divided to one neutral zone in contact with the external electrodes and one depletion zone charged by ionized impurities, positive on the n side and negative on the p side. These zones contain concentrations of the carriers represented in Figure 1.6.

The difference in carrier concentrations is very significant in the neutral zones and in most parts of the depletion zones. In addition, in the absence of any voltage applied to the diode (so at a total current of zero), the total current in terms of conduction and diffusion for each type of carrier must be cancelled out, since the electrons and holes are independent in an ideal diode. As we will see in section 1.4.1, one consequence of this is that current  $I_d$  in the diode depends exponentially on the external applied potential  $V_d$ . There exists a charge of minority carriers injected into each neutral zone that is proportional to  $I_d$  in forward bias ( $V_d > 0$ ), when the number of majority charges is increased, with a diffusion current that is predominant:

$$I_{\text{diff}} = I_0(T) \exp(eV_d/kT)$$

where  $V_d$  = voltage applied at the p terminal relative to the n terminal. We write the thermal voltage  $V_T = kT/e = 26$  mV at T = 300 K in the case of an ideal diode.

There is also a minority conduction current  $-I_0(T)$ . So, finally we write:

$$I_d = I_0(T)[\exp(V_d/V_T) - 1]$$

Solid line = diode at equilibrium (zero external voltage difference); Dotted line = forward polarization

Figure 1.6. Fixed charges and concentration of holes and electrons in the pn diode

In reverse bias, only the  $-I_0(T)$  current remains when  $V_d < -3V_T$ . The depletion zone can be approximated by an insulator, resulting in a capacitance that varies in accordance with  $V_d$ , as detailed below.

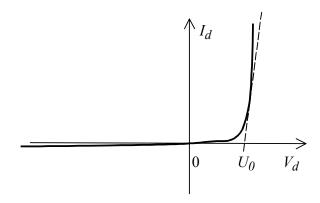

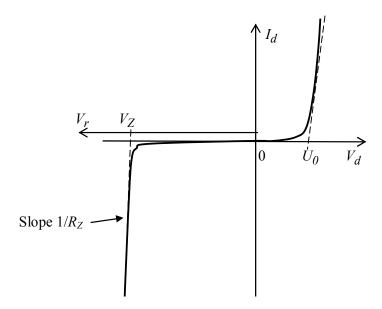

Figure 1.7. Exponential characteristic of pn diode

#### 1.2. Simplified models of the pn diode

In forward bias, if we equate the characteristic  $I_d$  ( $V_d$ ) to its tangent at the operating point, the equation of this tangent is  $V_d = U_0 + R_d I_d$ , where  $U_0$  is the diode threshold (Figure 1.7) and  $R_d$  its dynamic resistance equal to the inverse of the slope of  $I_d$  ( $V_d$ ).

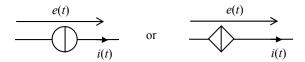

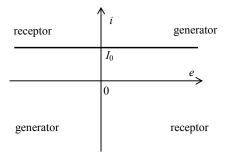

Figure 1.8. Symbolic and electric representations (in forward bias) of the pn diode

In certain cases, we can take  $R_d=0$  and even  $U_0=0$  to simplify the first stage of analysis. However, in reality  $R_d^{-1}=\frac{\partial I_d}{\partial V_d}=\frac{I_0}{V_T}\exp\left(\frac{V_d}{V_T}\right)=\frac{I_d}{V_T}$  or alternatively:  $R_d=\frac{V_T}{I_d}$ .

In reverse bias, we can consider the diode as an open circuit as a first approximation.

Accordingly, the diode is the dipole with the most basic commutation role. Its commutation is driven by the controlling voltage  $V_d$ , so that, with the simplified model:

– the diode is an open circuit (or off) if  $V_d < U_0$  and the diode is a closed circuit (or on) if  $V_d > U_0$ .

So, in a circuit with (at least) one diode, we must analyze the controlling voltage to determine its state, which can require a starting hypothesis to be verified through analysis.

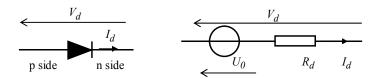

### 1.3. Diode circuitry (reviewed in exercises)

Several examples of the electronic operations performed with diodes are provided below. Remember that since diodes are commutation devices

controlled by voltage applied to them, either the on or off state of each diode must be subject to a working hypothesis that is confirmed or refuted further according to the consequences of the hypothesis. This step allows us to analysis the following circuits (Figures 1.9 and 1.10).

Figure 1.9. Rectification and detection operations

Figure 1.10. Analog switch and ring modulator

# 1.4. Detailed model of pn diode: variable conditions and effect of temperature

# 1.4.1. Junction at equilibrium (at zero voltage or in open circuit): diffusion potential

If the p zone is doped with  $N_A$  acceptors per volume unit and the n zone with  $N_D$  donors per volume unit, the carrier concentrations in neutral zones

are:  $p = N_A$  on the p side and  $n = N_D$  on the n side in semiconductors with a small forbidden bandgap such as Si and GaAs.

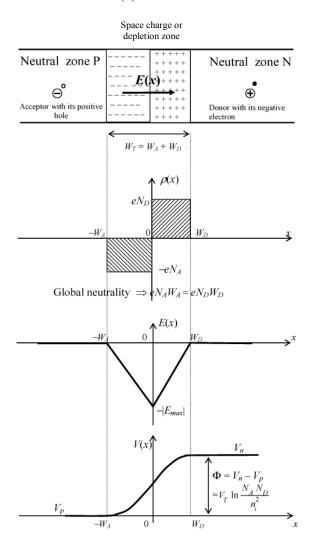

A space charge zone (thickness  $W_A$  on side p,  $W_D$  on side n, total  $W_T$ ) is created at the junction by recombination of a certain quantity of electron-hole pairs. The fixed charges that appear then balance:  $N_AW_A = N_DW_D$ , giving rise to an electric field E(x) (algebraic in Figure 1.11) obtained by integrating the Poisson equation  $\operatorname{div}(\varepsilon E(x)) = \rho(x)$ , that is, to a single dimension  $x: \frac{dE(x)}{dx} = \frac{\rho(x)}{\varepsilon}$ , where  $\rho$  is the volumic charge density and  $\varepsilon$  the absolute dielectric permittivity.

If we disregard the mobile charge density in the space charge zone, we obtain a negative electric field (essentially directing the + fixed charges toward the – fixed charges) with linear variation according to the abscissa in each p and n part, respectively (Figure 1.11).

By integrating this electric field, we obtain the variation of <u>internal</u> potential  $\Phi$  between regions p and n (not measurable on the exterior of the diode as it is compensated by the differences in contact potential  $V_{c1}$  and  $V_{c2}$ , which verifies  $\Phi = V_{c1} + V_{c2}$  in such a way that no current circulates at equilibrium).

However, it is the absence of total current (both of holes and electrons) when the diode is in open circuit, without any potential difference applied by an external source, that fixes the total value of the internal potential difference  $\Phi$ , called diffusion potential (and consequently, the width of the space charge zone  $W_T = W_A + W_D$ ).

Indeed, here we need:

$$J_n = en\mu_n E(x) + \mu_n kT \frac{dn}{dx} = 0$$

and  $J_p = ep\mu_p E(x) - \mu_p kT \frac{dp}{dx} = 0$ , where only components  $J_n$  and  $J_p$  are considered current densities along the Ox axis.

By accounting for  $E(x) = -\frac{dV(x)}{dx}$ , the equation above, for instance for holes, leads to:

$$-ep\frac{dV}{dx} = kT\frac{dp}{dx}$$

or:  $-\frac{dV}{V_T} = \frac{dp}{p}$

Hence:

$$\frac{p(x_2)}{p(x_1)} = \exp\left(\frac{V(x_1) - V(x_2)}{V_T}\right)$$

provided that  $x_1$  and  $x_2$  are within the limits of the space charge zone submitted to the electric field E(x).

**Figure 1.11.** Charges, algebraic electric field E(x) and potential in the pn diode at equilibrium (N.B.: the real field is in the inverse direction of the arrow, because negative E(x))

At equilibrium (that is under zero external voltage):

$$\frac{N_A}{\left(\frac{n_i^2}{N_D}\right)} = \frac{N_A N_D}{n_i^2} = \exp\left(\frac{\Phi}{V_T}\right) \implies \Phi = V_T \ln\left(\frac{N_A N_D}{n_i^2}\right).$$

The built-in potential  $\Phi$  represents a potential barrier for majority carriers and the electric field derived from this potential repels them into each neutral zone.

EXERCISE.— Calculate  $\Phi$  for  $N_A = 2 \times 10^{16} \text{ cm}^{-3}$ ,  $N_D = 10^{18} \text{ cm}^{-3}$ .

# 1.4.2. Biased junction (or out of equilibrium): effect of an external potential difference

Under an applied bias

$$V_d$$

, relation  $\frac{p(x_2)}{p(x_1)} = \exp\left(\frac{V(x_1) - V(x_2)}{V_T}\right)$  still

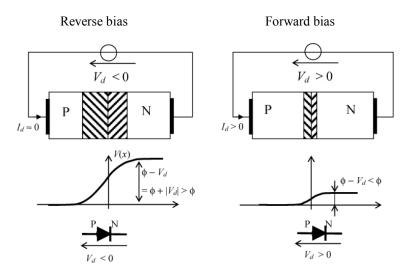

applies but we must account for the modification of internal potential by the potential difference  $V_d$  applied by the external source on the anode (P) relative to the cathode (N).

Figure 1.12. Effect of external bias on charges and potentials in a diode (depletion zones hatched)

We must then replace  $\Phi$  with  $\Phi - V_d$ , where  $V_d$  represents the voltage applied by the external source on the p side relative to n side. Indeed, since the differences in contact potential  $V_{c1}$  and  $V_{c2}$  remain the same, the closed-loop equation becomes  $\Phi - V_d = V_{c1} + V_{c2} - V_d$ . The potential barrier is then reduced when  $V_d$  is positive (forward bias) and increased when  $V_d$  is negative (reverse bias). In the first instance, this has the effect of favoring diffusion currents for majority carriers through the space charge zone, with the electric field not being strong enough to repel them.

These flows of majority carriers correspond to both the migration of electrons through the type p neutral zone and to the migration of holes into the type n neutral zone. These carriers then become minority carriers at the entry to these neutral zones, in  $-W_A$  and  $W_D$ , respectively, with  $\exp(V_d/V_T)$  concentrations higher than at equilibrium.

The direct current is linked to this increase in minority carriers at the boundaries between space charge zone and neutral zones and may be calculated by accounting for the replacement of  $\Phi$  by  $\Phi - V_d$  and the value of  $\Phi$  calculated earlier at equilibrium. For example, for holes whose concentration is fixed at  $N_A$  on abscissa  $x_2 = -W_A$ , we see the new concentration under bias  $V_d$  at the entry to the neutral zone of type n at  $x_1 = W_D$ :

$$\frac{p(W_D)}{p(-W_A)} = \exp\left(\frac{-(\Phi - V_d)}{V_T}\right) \quad \text{or} \quad p(W_D) = N_A \frac{n_i^2}{N_A N_D} \exp\left(\frac{V_d}{V_T}\right) = \frac{n_i^2}{N_D} \exp\left(\frac{V_d}{V_T}\right)$$

This concentration is higher than the minority carrier concentration at equilibrium  $n_i^2/N_D$  when  $V_d$  is positive (forward bias) and lower when  $V_d$  is negative (reverse bias). We will see an identical relation for electrons with the concentration  $n_i^2/N_A$  preceding factor  $\exp(V_d/V_T)$ . The diffusion currents

are

$$\mu_n kT \frac{dn}{dx}$$

and  $-\mu_p kT \frac{dp}{dx}$ , and become more significant in neutral zones

in which the electric field is negligible in comparison to that in depletion zones due to a sufficient concentration of majority carriers to ensure conduction. n(x) and p(x) concentrations of minority carriers, which recombine in these zones with time characteristics  $\tau_n$  and  $\tau_p$ , are determined by recombination lengths  $L_n$  and  $L_p$ , linked to each  $\tau$  and to the diffusion coefficients by  $L_n = \sqrt{D_n \tau_n}$  and  $L_p = \sqrt{D_p \tau_p}$ . Since this will be considered

in greater detail in Chapter 2, n(x) and p(x) verify the continuity equation, which accounts for the balance of mobile charges and is composed of a second-order differential equation. In a setting much greater in scale than  $L_n$  and  $L_p$ , n(x) and p(x) decrease exponentially according to the distance measured from the boundaries located at  $-W_A$  and  $W_D$  with characteristic lengths  $L_n$  and  $L_p$ , known as recombination lengths. So, their derivative is simply  $n(x)/L_n$  and  $-p(x)/L_p$ , with the signs indicating the decrease in n(x) to negative x and p(x) to positive x. Hence, a total diffusion current density that may be obtained by assessing  $eD_n \frac{dn}{dx}$  at  $x = -W_A$  and  $-eD_p \frac{dp}{dx}$  at  $x = W_D$ , or:

$$J_d = e \left( \frac{D_n}{L_n} \frac{n_i^2}{N_A} + \frac{D_p}{L_p} \frac{n_i^2}{N_D} \right) \exp \left( \frac{V_d}{V_T} \right)$$

At equilibrium  $(V_d = 0)$ , this current density is exactly compensated by the conduction current density  $\underline{J}_c = e(n\mu_n + p\mu_p) \underline{E}$ , which always has a negative sign in the circuit employed since the electric field is itself negative. So, for a diode of area A we have:

$$I_d(V_d) = Ae\left(\frac{D_n}{L_n}\frac{n_i^2}{N_A} + \frac{D_p}{L_p}\frac{n_i^2}{N_D}\right) \left[\exp\left(\frac{V_d}{V_T}\right) - 1\right]$$

with a preexponential factor  $I_0(T) = Ae \left( \frac{D_n}{L_n} \frac{n_i^2}{N_A} + \frac{D_p}{L_p} \frac{n_i^2}{N_D} \right)$  proportional to  $n_i^2$  and in which the currents of each type are in the same ratio to that of the two terms inside the brackets, that is  $\frac{D_n}{D_p} \frac{L_p}{L_n} \frac{N_D}{N_A}$ , also called the injection ratio, which can principally be adjusted by the ratio of doping concentrations on either side.

The reverse saturation current  $-I_0(T)$  is obtained when the reverse bias is high enough to allow us to disregard the diffusion currents of the majority carriers. This conduction current of the minority carriers is proportional to the concentrations of the minority carriers, so  $n_i^2/N_D$  and  $n_i^2/N_A$ , for holes and electrons, respectively.

Since all of these currents are proportional to  $n_t^2 = N_c N_v \exp(-E_g/kT) = BT^3 \exp(-E_g/kT)$  and to the area A of the diode; we define:  $I_0(T) = A \left(\frac{T}{T_0}\right)^3 J_0 \exp(-E_g/kT)$ , where  $J_0$  is a current density independent of temperature.

Typically, this current is from several dozen pA to several nA in low-power silicon diodes.

Other phenomena become significant in real diodes, notably the recombination of electron-hole pairs in the space-charge zone, which was ignored previously. This results in the forward current varying less quickly with voltage than according to the ideal law, and  $I_0(T)$  being higher than the value provided by the above-mentioned formula. We can correct for this by introducing the ideality factor  $\eta$ , typically taken between 1 and 2, to replace  $V_T$  with  $\eta V_T$ . So, for the real diode:

$$I_d(V_d, T) = I_0(T) \left[ \exp\left(\frac{V_d}{\eta V_T}\right) - 1 \right]$$

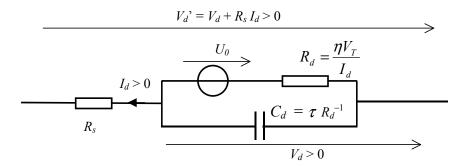

The dynamic resistance of the diode will become:  $R_d = \frac{\eta V_T}{I_d}$

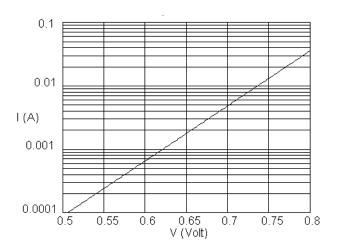

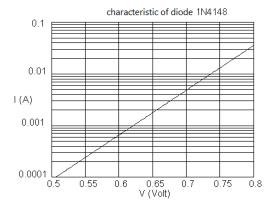

EXERCISE.— Find the real current  $I_0$  by measuring the variation factor of the current for a voltage variation of 0.1 V, the current value extrapolated to  $V_d = 0$  and the ideality factor of diode 1N4148 (Figure 1.13) at T = 300 K.

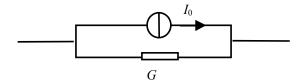

In reverse bias, real diodes pass a current whose absolute value is higher than the theoretical value  $I_0(T)$  calculated above and which increases with the reverse voltage. This effect is due to the extension of the depletion zone with the increase in the reverse voltage since the generation of electron-hole pairs, which is fostered by the presence of defects or recombinants centers in the depletion zone, occurs in greater volume. By integrating the generation rate in this volume, we can obtain a current that increases with reverse voltage, which we account for by an additional parallel conductance G in the equivalent circuit (Figure 1.14).

Figure 1.13. Characteristic of diode 1N4148 in forward bias

Figure 1.14. Equivalent circuit of diode in reverse static bias

Indeed, we should note that <u>all real diodes under reverse voltage</u> are limited to a value of  $V_{\rm rmax}$  (absolute value of  $V_d$ ). Once this voltage is reached, the electric field is strong enough to wrest electrons from their atoms (ionization), thereby creating further electron-hole pairs. In this manner, reverse current increases very quickly since the phenomenon becomes cumulative (avalanche breakdown). Dissipated power increases significantly, which can lead to the diode's immediate destruction if appropriate protection is not provided.

### 1.4.3. Effects of temperature

By deriving the logarithm of the preceding reverse current expression, we obtain:  $\frac{\partial I_0(T)}{I_0(T)} = 3\frac{dT}{T} + \frac{E_g}{kT}\frac{dT}{T}$  corresponding to a 15% per degree increase

at around 300 K, or equivalently a twofold increase approximately every 7° for silicon.

In forward bias, maintaining a current  $I_d$  constant and taking the logarithmic differentiation of  $I_d$ :

$$\frac{dI_d(T)}{I_d(T)} = 0 = \frac{\partial I_0(T)}{I_0(T)} - \frac{eV_d}{\eta kT} \frac{dT}{T} + \frac{e}{\eta kT} dV_d$$

Or, accounting for expression

$$\frac{\partial I_0(T)}{I_0(T)} = 3\frac{dT}{T} + \frac{E_g}{kT}\frac{dT}{T}$$

:  $\left[3 + \frac{E_g}{kT}\right]\frac{dT}{T} = \frac{eV_d}{\eta kT}\frac{dT}{T} - \frac{e}{\eta kT}dV_d$ , which ultimately provides:  $\frac{dV_d}{dT} = \frac{V_d}{T} - \frac{\eta k}{e}\left[3 + \frac{E_g}{kT}\right]$ ,

with  $V_d$  = 0.85 V, T = 300 K,  $\eta$  = 1.3,  $E_g$  = 1.12 eV (silicon), one obtains:  $\frac{dV_d}{dT}$  = -2.3 mV/ $^{\circ}$  (value widely provided in devices documentation but different for 1N4148).

NOTE.— When supplied with constant current in forward bias, we see the diode's forward voltage decrease as its temperature increases.

The increase in reverse current and decrease in direct voltage together with the increase in temperature represent drawbacks that limit the operating temperature of silicon components to around 200 °C. The only advantage is that the pn diode can be used as a temperature sensor.

Despite the increase in temperature coefficients

$$\frac{\partial I_0(T)}{I_0(T)}$$

and  $\frac{dV_d}{dT}$  with  $E_g$ ,

it is worthwhile to make use of semiconductors with larger forbidden bandgaps than silicon ( $E_g = 1.12 \text{ eV}$  at 300 K) for components expected to operate at higher temperatures, such as SiC ( $E_g = 2.8 \text{ at } 3.3 \text{ eV}$  depending on crystal type), GaN (3.4 eV) or diamond (5.5 eV) since the tremendous

decrease in  $I_0(T)$  easily compensates for the increase in temperature coefficients.

#### 1.4.4. Capacitive effects

If we apply the Gauss theorem to both sides of the space charge zone, then we can calculate the maximum electric field, whose absolute value  $E_{\text{max}}$  is situated on abscissa 0, and whose algebraic value is negative when accounting for the conventions in Figure 1.11:

$$E_{\text{max}} = \frac{e \, N_{\scriptscriptstyle A} \, W_{\scriptscriptstyle A}}{\varepsilon} = \frac{e \, N_{\scriptscriptstyle D} \, W_{\scriptscriptstyle D}}{\varepsilon}$$

which indicates that there is a charge per unit area identical in absolute value  $e N_A W_A = e N_D W_D$  on each side of the charge space zone. By accounting for E(x) = -dV/dx, by integration we obtain the difference of internal potential  $\Phi - V_d$  between zones n and p, that is from the total area of the triangles

representing

$$E(x)$$

,  $\frac{1}{2}(W_A + W_D)E_{\text{max}}$  or rather  $\Phi - V_d = \frac{\varepsilon}{2e}\left(\frac{1}{N_A} + \frac{1}{N_D}\right)E_{\text{max}}^2$ .

Hence, we deduce

$$E_{\text{max}} = \sqrt{\frac{2e}{\varepsilon \left(\frac{1}{N_A} + \frac{1}{N_D}\right)}} \sqrt{\Phi - V_d}$$

and the total width

$$W_T = W_A + W_D = \sqrt{\frac{\mathcal{E}}{2e} \left(\frac{1}{N_A} + \frac{1}{N_D}\right)} \sqrt{\Phi - V_d}$$

of the charge space zone or

depletion zone. The charge Q per unit area on either side of the charge space zone may then be easily calculated in absolute value by:

$$Q = e N_A W_A = e N_D W_D = \sqrt{\frac{2e\varepsilon}{\frac{1}{N_A} + \frac{1}{N_D}}} \sqrt{\Phi - V_d}$$

Technological limitations mean that we either have  $N_A >> N_D$ , or  $N_D >> N_A$  in most cases, which often means we can disregard one of the two terms in the denominator.

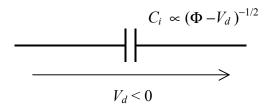

One variation of  $dV_d$  leads to variation dQ, hence the capacitance per unit area for a reverse biased diode ( $V_d < 0$ ) and in low forward voltages (<0.3 V) reads:

$$C_i = \left| \frac{dQ}{dV_d} \right| = \sqrt{\frac{e\varepsilon}{\frac{2}{N_A} + \frac{2}{N_D}}} \frac{1}{\sqrt{\Phi - V_d}}$$

Accordingly, this capacitance decreases as reverse voltage  $-V_d = V_r$  increases, corresponding to an increase in the width of the depleted zone  $W_T = W_A + W_D$ . This same expression applies for the parallel plate capacitor, which has a capacitance per unit area of  $\varepsilon/W_T$ .

The equivalent reverse circuit is thus reduced to capacitance  $C_i$  if we can disregard the reverse current and conductance:

Figure 1.15. Equivalent circuit for reverse biased diode

EXERCISE.— Find the capacitance for a square diode of 1 mm width, then for one of 10  $\mu$ m width if  $N_A = 2 \times 10^{16}$  cm<sup>-3</sup>,  $N_D = 10^{18}$  cm<sup>-3</sup>,  $\varepsilon = \varepsilon_0 \varepsilon_r$  ( $\varepsilon_r = 11.7$  for Si), under  $V_d = 0$  V then  $V_d = -10$  V (use the value of  $\Phi$  calculated earlier).

In forward bias, an additional charge  $Q_s$  of minority carriers is stored in the neutral zones, the injection and diffusion of these carriers being the very mechanism of forward current flow. In fact, this charge is neutralized by an equivalent charge of opposite sign due to the majority carriers that are attracted. While they do neutralize each other, these charges undergo variations when the applied voltage varies, which leads to a capacitive effect. Due to the exponential dependence of this charge  $Q_s$  and current  $I_d$  with forward voltage, there is proportionality between them, so:  $Q_s = \tau I_d$  in steady state.

The time constant  $\tau (= \tau_p \text{ or } \tau_n)$  is the average lifetime of minority carriers (from several ns to several  $\mu$ s) in the presence of majority carriers in concentration  $N_D$  or  $N_A$ . This is linked to the diffusion and length coefficients by the relation  $L_p = \sqrt{D_p \tau_p}$  and  $L_n = \sqrt{D_n \tau_n}$  due to the connection between minority carrier recombination and diffusion, which is a result of their concentration gradient due to the disappearance of a fraction of these mobile charges through the recombination phenomenon as we move away from the depletion zones.

This leads to the existence of a capacitance called diffusion capacitance, with small signals around an operating point:  $C_d = \frac{dQ_s}{dV_d} = \tau \frac{dI_d}{dV_d} = \frac{\tau}{R_d}$ .

Hence, the complete equivalent circuit under forward bias (Figure 1.16), which also accounts for access resistance, known as  $R_s$  series resistance, which provokes an additional voltage drop so that the real voltage between the terminals of the diode is actually  $V_d$  =  $V_d$ +  $R_sI_d$ .

Figure 1.16. Complete equivalent circuit of the pn diode in forward bias

In any variable conditions:

$$I_d(t) = \frac{dQ_s}{dt} + \frac{Q_s(t)}{\tau}$$

.

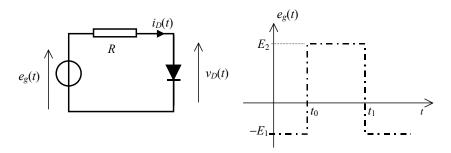

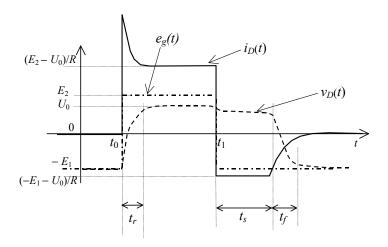

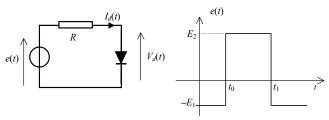

This stored charge  $Q_s$  is the cause of the diode's frequency response and its delay in commutation (overlooking the connections' inductive effects here). The switching conditions are described below (Figures 1.17 and 1.18), assuming a much higher external series resistance R than the diode's internal resistance.

– On closure (flow open state → conductive state or "off → on"), the voltage at diode terminals does not immediately go from  $-E_1$  to the forward voltage value  $U_0$  since it must first discharge the reverse capacitance  $C_i$  and charge the diffusion capacitance  $C_d$ . At the terminals, the potential difference across the resistance R is here  $E_2 - (-E_1) = E_2 + E_1$  at  $t = t_0$  while it will become  $E_2 - U_0$ , which is lower, in permanent conditions; therefore, there is a current peak and a transient  $v_D(t)$  of duration  $t_r$  to reach 0.9  $U_0$ .

Figure 1.17. Assembly for the diode test in switching conditions

Figure 1.18. Voltage and current in the diode in switching conditions

– On opening (flow conductive state  $\rightarrow$  open state or "on  $\rightarrow$  off"), the diode imposes a voltage approaching  $U_0$  due to the excess minority charges that arise during the storage time, which still corresponds to a conductive

state. The current is then deduced from the drop in voltage across the R resistance, that is  $(-E_1 - U_0)/R$ , which is constant; it is a negative or reverse current that allows for the diffusion capacitance to be discharged. According to the  $Q_s$  equation in variable setting (first-order differential equation with constant second member; see exercise),  $Q_s$  decreases exponentially toward zero (duration  $t_s$ ). Subsequently, capacitance  $C_i$  recharges under the reverse voltage  $-E_1$  with time constant  $RC_i$  (duration  $t_f$ ) by means of a reverse current tending finally to zero.

### 1.5. Different types of diode and their functions

#### 1.5.1. Zener diode

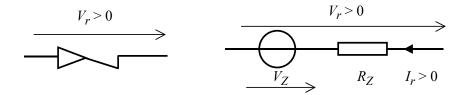

The Zener diode is a diode in which the avalanche phenomenon is safely handled (non-destructive), allowing for a near constant reverse voltage  $V_r = -V_d = V_Z$  to be maintained once attained (Figure 1.20). Dynamic resistance  $R_Z$  is in the order of several ohms to several hundred ohms and  $V_Z$  can be found between 1 and 200 V.

Figure 1.19. Symbolic and electric representations of the Zener diode

This diode allows us to make direct voltage stabilizers as well as variable voltage peak limiters.

### 1.5.2. Schottky diode or metal-semiconductor diode

In this diode, one side (p or n) of the semiconductor is replaced by a metal (Figure 1.21). The internal potential difference  $\Phi$  is consequently lower, which results in a lower drop in forward voltage and a stronger reverse current than in a pn diode under the same conditions. Since less

power is lost in forward bias, these diodes work to rectify strong currents (power diodes).

Figure 1.20. Characteristic of Zener diode

Figure 1.21. Symbol of the Schottky diode or metal-semiconductor diode

The metal injects a negligible quantity of minority carriers under forward bias, thus suppressing the stored charge  $Q_s$ . As a result, the switching times are significantly reduced and low-power diodes can have commutation times of less than a nanosecond, with operating frequencies up to 100 GHz possible.

### 1.5.3. Light emitting diodes and laser diodes

Electroluminescent diodes (light emitting diodes [LEDs]) are made exclusively with III–V semiconductors in which the phenomenon of recombination of electron-hole pairs is principally radiative: that is where the energy  $E_g$  recovered on the annihilation of two particles with opposite types is transformed into a photon of energy  $h\nu$  approaching  $E_g$  and a wavelength close to  $\lambda = \frac{c}{\nu} = \frac{hc}{E_g} = \frac{1.24}{E_g}$  (in  $\mu$ m if  $E_g$  is in eV).

Typically, these semiconductors are made up of the compound  $GaAs_xP_{1\text{-}x}$ , which allows for a forbidden bandgap of 1.8–2.6 eV, corresponding, respectively, to the colors red and blue (and at intermediate values corresponding to yellow and green) and more recently GaN and  $In_xGa_{1\text{-}x}N$  for the near ultraviolet, purple and blue.

Laser diodes make use of the stimulated emission phenomenon that occurs in a resonant cavity, allowing for a highly directive luminous beam and very precise frequency (very tight frequency, unlike LEDs). By modulating the light beam, we can transmit information optically at high speed, typically using the infrared range (1.55  $\mu$ m) in which attenuation in the optical fibers is minimal.

### 1.5.4. Photodiodes and photovoltaic generators

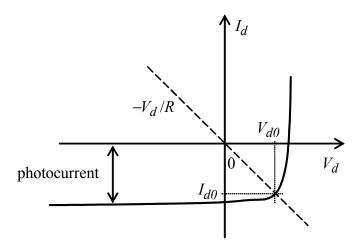

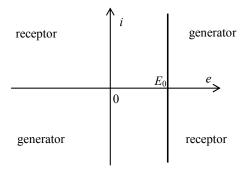

Light can generate electron-hole pairs by transferring the energy of a photon  $h\nu$  to an electron of the valence band, making it enter the conduction band if  $h\nu \ge E_g$  (by the opposite phenomenon to that at work in LEDs), thereby creating a hole in the valence band. If this phenomenon occurs in the space charge zone, the electric field separates the electron-hole pair, which gives rise to a current of the same type as the reverse current and which corresponds to a downwards shift in all  $I_d(V_d)$  characteristics (Figure 1.22).

This current, called a photocurrent, is proportional to the flow of photons reaching the charge space zone, and can be collected in an external circuit to act as a means of measuring light flow (electric transcription of coded optical information) or of transforming the energy in sunlight to electric energy (photovoltaic or solar cells). In electrical terms, this diode acts as a generator.

Figure 1.22. Characteristic of a photovoltaic cell

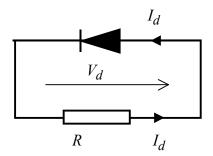

Figure 1.23. Photovoltaic generator and its load resistance

If we place resistance R between the terminals of the diode (Figure 1.23), the current flowing through it is  $-\frac{V_d}{R}$ , which is the equation of a straight line whose intersection with the photodiode's characteristic determines the operating point, with a current  $I_{d0} < 0$  (Figure 1.22). In this quadrant, where  $I_d < 0$  and  $V_d > 0$ , the diode is a generator due to it converting light energy into electrical energy. This is how photovoltaic cells operate. We can easily show that the power delivered in the load reaches maximum when the

intersection of the straight line  $-\frac{V_d}{R}$  with  $I_d(V_d)$  occurs at the furthest point

from the origin, situated in the elbow of its characteristic curve. Accordingly, the production of renewable electrical energy depends on this type of component, which can now provide yields approaching 20%. The peak power that can be obtained is determined by that of the sun, which reaches a maximum of around  $1 \text{ kW/m}^2$ .

#### 1.6. Exercises

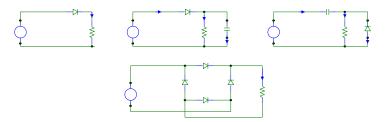

# 1.6.1. Analyze the operation of the following circuits for a sinusoidal voltage generator and ideal diodes (a) with no threshold and (b) with a threshold $U_0$

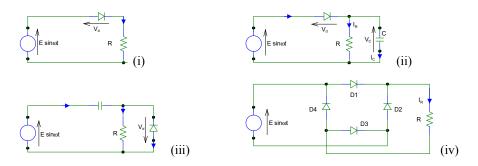

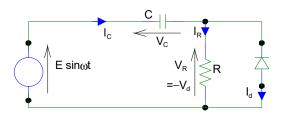

Perform a qualitative analysis of operations, assuming that for (b) the diodes' threshold  $U_0$  is far below the maximum voltage supplied by the generator and that the frequency is of the same order as the reverse of the circuit's time constant, where there is one. Complete all the circuits by identifying the electrical quantities with name and arrow.

#### Answer:

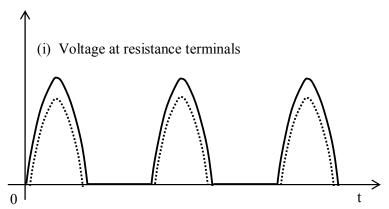

i) The diode is conductive when (a) Esin $\omega$ t > 0 or (b) Esin $\omega$ t –  $U_0$ > 0 and like an open circuit in other cases. When it is conductive, we find the voltage Esin $\omega$ t or Esin $\omega$ t –  $U_0$  at the resistance terminals. When it has been opened, current is zero in resistance, as is voltage. This circuit acts as a half-wave rectifier.

- a) Without diode threshold, solid line

- b) With diode threshold, dotted line

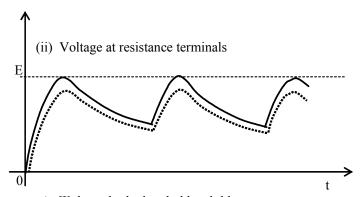

ii) As above, however this time the capacitor charges so that  $V_C$  becomes positive and remains so. The C capacitor discharges in the resistor when the diode is opened ( $I_C < 0$ ), that is, if (a)  $\operatorname{Esin}\omega t < V_C$  or (b)  $\operatorname{Esin}\omega t - U_0 < V_C$  and charges ( $I_C > 0$ ) under voltage (a)  $V_C = \operatorname{Esin}\omega t$  or (b)  $V_C = \operatorname{Esin}\omega t - U_0$  if the diode is conductive. This circuit acts as a filtered half-wave rectifier or works for signal envelope detection.

- a) Without diode threshold, solid line

- b) With diode threshold, dotted line

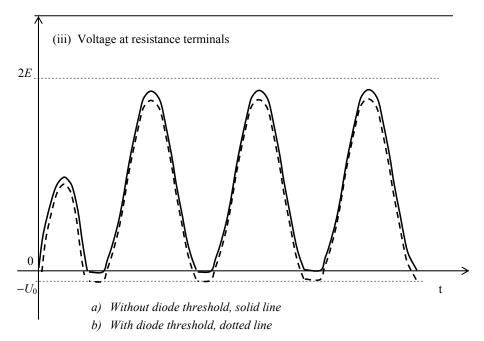

iii) Current  $I_d$  can only be negative inside the diode if voltage  $V_R$  at the resistance terminals is negative too, or zero if  $V_R > 0$ . During the two initial half-waves, current in the capacitor  $I_C$  is more negative than positive on average since for  $V_C$  we find (a) Esin $\omega$ t or (b) Esin $\omega$ t +  $U_0$  when the diode is

conductive, that is when Esin $\omega$ t < 0 and (a)  $V_R = 0$  or (b)  $-U_0$ , while we have only Esin $\omega$ t –  $V_R$  when  $V_R > 0$ . Consequently, the capacitor charges to a mean value  $V_{Cavg} < 0$ . As  $V_R = \text{Esin}\omega$ t –  $V_C$ , this means  $V_{Ravg} > 0$  since, the mean value of Esin $\omega$ t being zero, we obtain, approximately,  $V_R = \text{Esin}\omega$ t –  $V_{Cavg}$  (with  $V_{Cavg} < 0$ ). Hence, the voltage Esin $\omega$ t is shifted upward except when the diode is conductive, that is when  $V_R$  becomes (a) = 0 or (b) =  $-U_0$ . The increase in voltage at the R terminals, caused by the initial charge of C, is required to attain stationary conditions in which the mean current becomes zero, since the capacitor would otherwise continue to charge indefinitely.

This circuit works to restore the signal's mean value by clamping, that is, forcing the most negative instantaneous value to become close to zero.

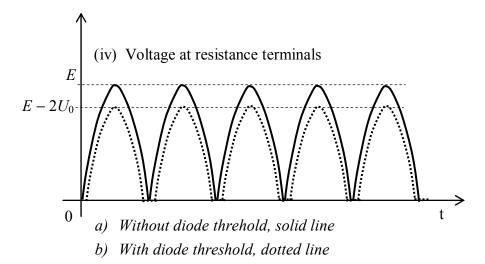

iv) This circuit operates as (i) but with D1, D3 conductive and D2, D4 opened when  $E\sin\omega t > 0$  and reverse when  $E\sin\omega t < 0$ . The conductive diodes are always in series with the resistance here and the generator current is orientated toward resistance, so that  $I_R$  is always positive or zero. This is a full wave rectifier circuit.

# 1.6.2. Study of the current variations in a forward biased pn diode under influence of temperature

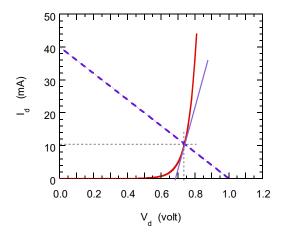

Plot the forward characteristic  $I_d(V_d)$  (at 300 K) of the 1N4148 diode with linear scales from 0 to 20 mA on a voltage scale from 0 to 1.2 V.

Find the literal expression of the load equation, that is, of  $I_d = aV_d + b$  when a voltage generator E supplies the diode in forward bias, in series with an R resistance. Plot it for E = 1 volt and  $R = 25 \Omega$ . Find the operating point  $(I_{d0}, V_{d0})$ , the threshold voltage  $U_0$  and the dynamic resistance  $R_d$  of the diode from the plotted characteristic tangent at the operating point as well as the power dissipated in the diode.

By means of expressions in the course, use the provided, or calculated, diode characteristics and load resistance R to determine the relative variation of the current  $dI_d/I_d$  according to the relative variation dT/T of temperature. What happens if, by adjusting E so that current remains  $I_{d0}$ , R is equal to  $R_d$ ? R becomes  $\langle R_d \rangle$ ? Conclude with the thermal stability of such a circuit.

#### Answer:

Load equation:

$$E = V_d + R I_d$$

or  $I_d = \frac{E - V_d}{R}$

At the intersection,  $V_{d0} = 0.74 \text{ V}$  and  $I_{d0} = 10.3 \text{ mA}$ .

The plotted tangent gives a threshold of  $U_0 = 0.68$  V and a dynamic resistance (the reciprocal slope of the tangent) of  $R_d = 5.4~\Omega$  (compare this with the theoretical value  $\eta kT/eI_{d0} = 50~\text{mV}/10.3~\text{mA} = 5~\Omega$ ). The dissipated power is  $V_{d0}~I_{d0} = 7.6~\text{mW}$ .

By deriving the load equation,

we obtain:

$$\frac{dI_d}{I_d} = -\frac{dV_d}{RI_d}$$

which we carry on to

$$\frac{dI_d(T)}{I_d(T)} = \frac{\partial I_0(T)}{I_0(T)} - \frac{eV_d}{\eta kT} \frac{dT}{T} + \frac{e}{\eta kT} dV_d$$

and accounting for

$$\frac{\partial I_0(T)}{I_0(T)} = 3\frac{dT}{T} + \frac{E_g}{kT}\frac{dT}{T}$$

and  $R_d = \frac{\eta kT}{I_d}$

we obtain:

$$\frac{dI_d(T)}{I_d(T)} = \frac{dT}{T} \frac{3 + \frac{E_g}{kT} - \frac{eV_d}{\eta kT}}{1 + \frac{R}{R_d}}$$

The numerator for silicon is  $3 + 43 - 15 \approx 31$  with  $E_g = 1.12$  eV, kT = 26 meV and  $\eta kT/e = 50$  mV for the 1N4148 diode at ambient, deduced from the characteristic curve  $I_d(V_d)$  in semilog,  $V_{d0} = 0.74$  V. So for a variation of

+10 °C from 300 K,

$$\frac{dI_d(T)}{I_d(T)} = \frac{10}{300} \frac{31}{1 + \frac{R}{R_d}} \approx \frac{1}{1 + \frac{R}{R_d}}$$

which gives a 0.5 or

50% increase in  $I_d$  when  $R = R_d$  and the relative variation approaches 100% if  $R \ll R_d$ . In this last instance, there is a danger of a cumulative effect, since the dissipated power increases, which contributes to further increase the component's temperature and thereby current, up to its destruction by overheating due to this thermal runaway.

Accordingly, it is crucial to maintain a load resistance  $R > R_d$ .

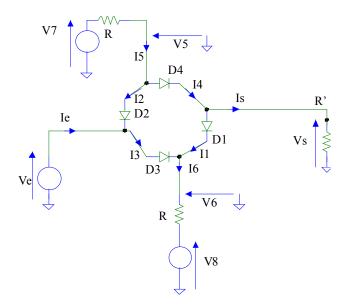

# 1.6.3. Analog switch

The diodes are identical, each having a conduction threshold of  $U_0 = 0.6 \text{ V}$ , with negligible dynamic resistance and reverse current.

First case:

$$V7 = -10 \text{ V}$$

;  $V8 = +10 \text{ V}$ .

Find the state of the diodes when Ve = 0. Deduce Is and Vs. Between what boundaries of Ve does the diodes' state remain identical to the state above?

Second case: V7 = +10 V; V8 = -10 V.

Find the state of the diodes when Ve = 0. Now find the relationship between Ve and Vs assuming that the diodes remain in this state when  $Ve \neq 0$ . In what boundaries of Ve is this hypothesis verified? What happens if Ve leaves these boundaries, toward higher values for example?

#### Answer:

First case: V7 = -10 V; V8 = +10 V; the loop equations going through V7, R, D2, Ve, on the one hand, and Ve, D3, R, V8, on the other hand, show that the diodes are open circuits when Ve = 0, so I5 and I6 are zero too, which leads to V5 = V7 = -10 V and V6 = V8 = +10 V. As a result, diodes D4 and D1 are also open circuits, which leads to Is = 0 and so Vs = 0. This remains true so long as the value of Ve does not change the state of the diodes: D2 only becomes conductive if Ve < -10.6 V and D3 only becomes conductive if Ve > +10.6 V; this interval -10.6 V < Ve < +10.6 V thus defines the range at which the switch is an open circuit, isolating the output from the input.

Second case: V7 = +10 V; V8 = -10 V.

With Ve = 0 and still going through the two same loops, we must conclude that diodes D2 and D3 are conductive, so V5 =  $U_0$  and V6 =  $-U_0$ . The value of these two voltages V5 and V6 thus imposes that diodes D4 and D1 are also in a conductive state. Going through loop Ve, D2, D4, Vs or Ve, D3, D1, Vs, the diode thresholds compensate for each other since we have Ve  $-U_0 + U_0 - \text{Vs} = 0$ , or Vs = Ve = 0. However, this equation applies so long as the diodes remain in a conductive state, so Vs = Ve even if Ve  $\neq 0$ . The switch is in the closed state, that is output and input voltages are the same, and current can flow from input to output or in the reverse direction.

If Ve increases in positive values, current Ie will increase and lead I2 to decrease to the point of cancelling it, closing diode D2. In order to assess this boundary, let us superimpose case Ve = 0, V7 = +10 V; V8 = -10 V with case Ve > 0, V7 = V8 = 0 V. When Ve = 0 = Vs, current I5 is symmetrically shared between I2 and I4 since the diodes are identical and operate under the same voltages, and Is = 0 since Ve = 0; so it is  $(10V - U_0)/R$ . In case Ve > 0, Ve = Ve = 0 V, current I2 should become a reverse current but we know that it will only subtract itself from  $(10V - U_0)/R$  when we superimpose two conditions; so we can continue to assume that diode D2 remains conductive with Ue = Ve = Ve, and we will apply the same hypothesis to the state of other diodes. So, we must write the node equations, which provide:

$$\begin{bmatrix} 0 & 1 & -1 & 0 \\ 0 & -1 & 0 & -1 \\ -1 & 0 & 0 & 1 \\ 1 & 0 & 1 & 0 \end{bmatrix} \begin{bmatrix} I1 \\ I2 \\ I3 \\ I4 \end{bmatrix} = \begin{bmatrix} -Ie \\ -I5 \\ Is \\ I6 \end{bmatrix}$$

This system is of rank 3, as we see by replacing line 4 by the total of the 4 lines, and only allows a solution if we also have -Ie - I5 + Is + I6 = 0. In physical terms, this means that Ie has no choice other than to be equal to -I5 + Is + I6, which we know how to calculate according to the voltage drops in resistance. However, since there are only three independent equations for four unknowns, the system allows an infinite number of solutions for I1, I2, I3, I4, which can also not be known independently.

Nonetheless, we can consider the voltages, estimating that D2 will become an open circuit if Ve exceeds the value  $(V7 - U_0)R'/(R'+R) + U_0$ , which is obtain by making I5 = I4, I1 = 0 and Ie = I3. Indeed, two opposite

diodes D2 and D1 will become open circuits for the same reason: too high a cathode potential relative to the anode; while on the other hand D3 and D4 remain conductive. In this case, the switch does not fulfill its role since  $Vs \neq Ve$ .

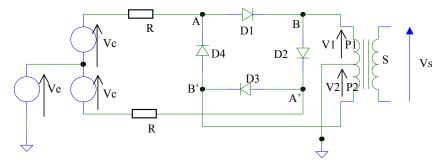

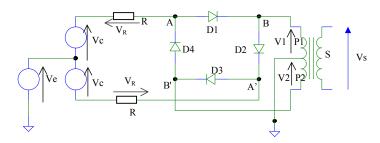

## 1.6.4. Ring modulator

Use the same hypotheses as in the previous exercise. Let us assume that voltage V2 induced in the winding P2 when P1 is subjected to voltage V1 is equal to V1 and vice versa. The secondary S of the transformer provides voltage Vs = V1 + V2 so long as V1 + V2 are alternative symmetric.

- Study in instantaneous values:

First case: Vc = +1.6 V.

Find the state of four diodes. Deduce from this the relation between Ve and V1 assuming that the current circulating in P1 does not disturb the state of the diodes. What condition must this current respect in order for this to occur? Where does it flow in a closed circuit?

Second case: Vc = -1.6 V. Same questions, replacing V1 by V2 and P1 by P2.

- Alternating Vc voltage: Vc is a periodic voltage of period T in symmetrical time levels of + or -1.6 V of equal duration to the half period. So, what is the shape of Vs and what are its limiting values? What happens if Ve is a voltage that varies much more slowly than T?

#### Answer:

– Study in instantaneous values:

First case: Vc = +1.6 V.

By circulating in the loop composed of sources Vc, resistors R, D1 and D2, we see that diodes D1 and D2 are conductive, since they are subject to a positive voltage between anode and cathode; and  $2\text{Vc} - 2\text{V}_R - 2U_0 = 0$ , so  $\text{V}_R = \text{Vc} - U_0 = 1 \text{ V}$ . Consequently, D4 and D3 are open circuits and the potential of the low point of V2 (B') is therefore not imposed by these diodes.

Accordingly, we again find that  $V1 = Ve + Vc - V_R - U_0 = Ve$  at the terminals of P1 and V2 = V1 due to the coupling of two primary windings P1 and P2. The current output by Ve in P1 closes by ground, and is spread between arms Vc, R, D1 and Vc, R, D2 superimposing itself on the current already flowing into the loop composed of Vc, resistors R, D1 and D2. So, in absolute value, this must be less than  $(Vc - U_0)/R$  in order not to induce blocking of one of the two diodes.

Second case: Vc = -1.6 V.

When the Vc sources are negative, D3 and D4 are conductive, hence  $2\text{Vc} - 2\text{V}_R + 2U_0 = 0$  and D1 and D2 are opened. So, we have  $\text{V}_R = -1\text{V}$  and  $-\text{V2} = \text{Ve} + \text{Vc} - \text{V}_R + U_0 = \text{Ve}$ ; hence V2 = -Ve = V1, D1 and D2 indeed being open circuits.

– Alternating Vc voltage: According to the results above, Vs = V1 + V2 is alternatively 2Ve and –2Ve. So, Vs is a symmetrical alternative voltage of 2Ve maximum amplitude, which amounts to the product of Ve by a rectangular signal of  $\pm 2$  value. The slow variable voltage Ve may be transformed into a much faster varying alternative voltage between  $\pm 2$ Ve,

which is equivalent to modulating the amplitude of a symmetric rectangular signal.

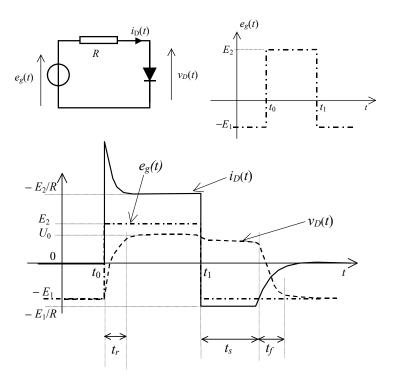

## 1.6.5. Switching diode: study on opening

In forward bias and any given conditions, the (excess) minority stored charge is  $Q_s(t)$  and is linked to direct current  $I_d(t)$  by  $I_d(t) = \frac{dQ_s}{dt} + \frac{Q_s(t)}{\tau}$ , where  $\tau$  is the lifetime of the minority carriers. The diode model in forward bias is reduced to the threshold voltage  $U_0 = 0.75$  V.

- Static conditions in forward bias (state "on" or closed switch): Calculate current  $I_d(t) = I_{d0}$  according to R,  $U_0$ ,  $E_2$ . Deduce the stored charge  $Q_{s0}$  in these conditions according to  $I_{d0}$  and  $\tau$ .

- Storage time  $t_s$  on opening:

At  $t_1 = 0$ , we apply  $e(t) = -E_1$ . Assuming that the stored minority charge continues to impose  $V_d(t) = U_0$ , find current  $I_d(t) = I_{d1}$ . Next, solve the differential equation to obtain  $Q_s(t)$  according to  $\tau$ ,  $E_1$ ,  $E_2$ , R and t. Deduce from this the storage time  $t_s$  that separates instant  $t_1$  from the instant when  $Q_s(t)$  is cancelled out. How will this evolve with  $E_1$  and  $E_2$  (compare with the cases of  $E_1 = 0$ ,  $E_2 = 5U_0$  and  $E_1 = E_2 = 5U_0$  for instance)?

# – Fall time $t_f$ of $V_d(t)$ on opening:

Following the cancellation of  $Q_s$ , the diffusion capacitance is negligible and the diode can be replaced by its only depletion zone capacitance  $C_i$  that we will consider as approximately constant.  $V_d(t)$  is no longer held equal to  $U_0$  and can move toward its final value. Draw the circuit and write the differential equation of  $V_d(t)$ . Solve this from the instant  $t_2 = 0$  when these conditions apply with  $V_d(0) = U_0$ . Deduce the fall time  $t_f$  that separates the instant  $t_2$  from that where  $V_d(t_d) = -0.9 E_1$  if  $E_1 \neq 0$  or  $V_d(t_d) = 0.1 U_0$  when  $E_1 = 0$ . How will this occur with  $E_1$  evolution?

– Calculate  $t_f$ ,  $t_s$ ,  $E_2$ , then  $\tau$  for the diode 1N4153 in which  $C_i = 2$  pF, with  $R = 100 \Omega$ ,  $I_{d0} = 10$  mA and  $E_1 = 6$  V if we measure  $t_f + t_s = 2$  ns.

#### **Answer:**

1) In static conditions and a conductive state,  $I_{d0}=\frac{E_2-U_0}{R}$  and  $Q_{s0}=\tau I_{d0}=\tau\frac{E_2-U_0}{R}$ .

2) Switch conductive state  $\rightarrow$  open state: at  $t_1 = 0$ , we apply  $e(t_1) = -E_1$ .

Assuming that the stored minority charge (which allows direct current to circulate), imposes  $V_d = U_0$ , providing  $I_d = I_{d1} = \frac{-E_1 - U_0}{R} = -\frac{E_1 + U_0}{R}$ ; the differential equation is solved with  $I_d(t) = I_{d1}$ , and we write  $Q_{s1} = \tau I_{d1}$ :  $\tau \frac{dQ_s}{dt} + Q_s = Q_{s1}$ .

At

$$t = 0$$

,  $Q_s = Q_{s0}$ , or finally  $Q_s(t) = (Q_{s0} - Q_{s1}) \exp\left[-\frac{t}{\tau}\right] + Q_{s1}$ ;  $Q_s(t) = \tau \frac{E_2 + E_1}{R} \exp\left[-\frac{t}{\tau}\right] - \tau \frac{E_1 + U_0}{R}$ .

From this, we may deduce the storage time  $t_s$  which goes from  $t_1 = 0$  to the instant when  $Q_s(t_s) = 0$ , or

$$t_{s} = \tau \ln \frac{E_{2} + E_{1}}{E_{1} + U_{0}}$$

If

$$E_1 = 0$$

,  $t_{s0} = \tau \ln \frac{E_2}{U_0}$ ; for example, for  $E_2 = 5$   $U_0 = 3.75$  V,  $\ln \frac{E_2}{U_0} = 1.6$

while for  $E_1 = E_2 = 5U_0$ ,  $\ln \frac{E_2 + E_1}{E_1 + U_0} = 0.51$ . So, we gain a factor 3 on  $t_s$  by

using reverse voltage to switch the diode off, since there is a greater current allowing the stored charge to flow.

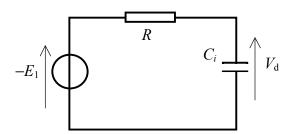

# 2) Ramp-down time of $V_d(t)$ between $U_0$ and $-0.9E_1$

Following the cancellation of  $Q_s(t)$ , the diffusion capacitance becomes negligible and we have the equivalent dynamic circuit below, where  $C_i$  is the capacitance of the space charge zone, assumed constant. The conditions below are represented with  $t_2 = 0$ ,  $V_d = U_0$ .

Hence,

$$C_i \frac{dV_d}{dt} = I_d(t) = -\frac{-E_1 - V_d(t)}{R}$$

, or rather  $RC_i \frac{dV_d}{dt} + V_d(t) = -E_1$ .

Accounting for the initial and final conditions, we obtain:

$$V_d(t) = (E_1 + U_0) \exp \left[ -\frac{t}{RC_i} \right] - E_1$$

which provides for  $V_d(t_f) = -0.9E_1$ .

Applying

$$V_d(t_f) = -0.9E_1$$

,  $t_f = RC_i \ln \frac{E_1 + U_0}{0.1E_1}$

Numerical application for diode 1N4153: calculate  $RC_i = 2 \times 10^{-10} \text{ s} = 0.2$  ns;  $t_d = 0.2 \ln \frac{6.75}{0.6} = 0.48$  ns; hence: 0.48 ns +  $t_s = 2$  ns; then  $t_s = 1.52$  ns and otherwise  $E_2 = 100 \times 10^{-2} + 0.75 = 1.75$  V;  $t_s = \tau \ln \frac{7.75}{6.75} = 0.138$   $\tau$ , hence  $\tau = 11$  ns.

NOTE.— According to the initial and final voltage values, the delay time can be either less or more than the respective time constants.

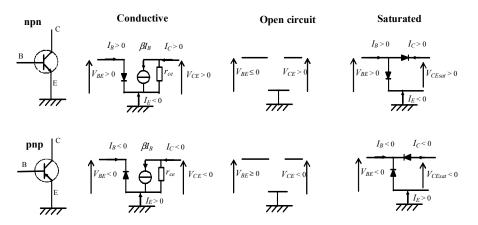

# Bipolar Junction Transistors and Applications

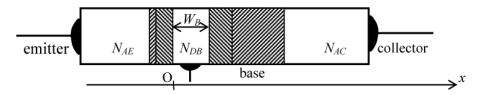

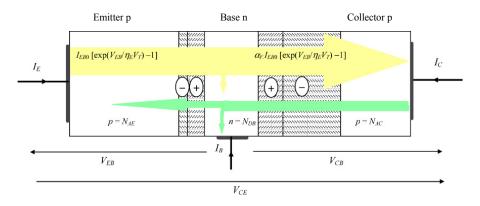

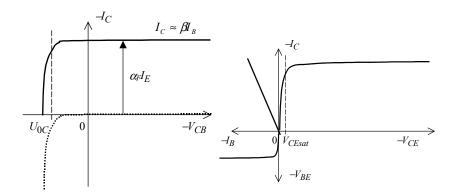

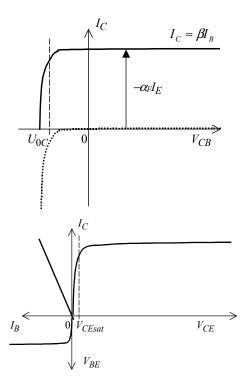

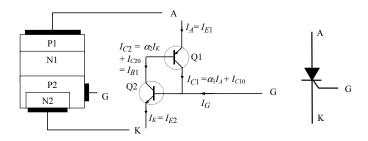

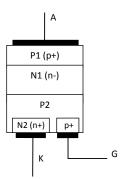

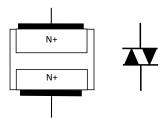

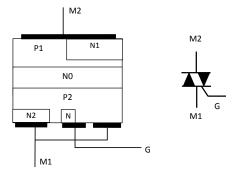

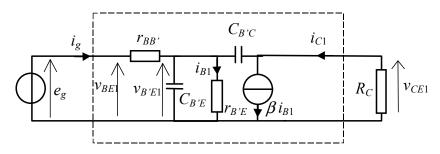

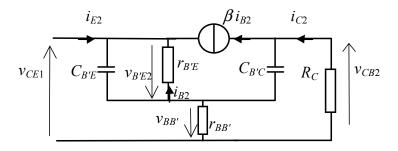

#### 2.1. The transistor effect

By the 1950s, the transistor effect had inspired the first semiconductorcontrolled devices in which one electrode regulates the current flowing between two others. The effect relies on the injection of minority carriers into an electrode, called the "base", from the "emitter" electrode of the opposite type, in which the charge carriers are majority carriers. The third electrode, or the "collector", of the same type as the emitter, collects less current than that issued by the emitter but is dependent on the potential difference between base and emitter and on the emitter current. Let us consider the example of the pnp type, in which the base is p type. Historically, the term "base" was used due to the central position of this semiconductive part, which was originally used to diffuse doping impurities of the opposite type in order to create the emitter and collector on either side. Subsequent developments in semiconductor technology led to the production of bipolar junction transistors with architecture better matched to the regimes that favor the transistor effect, foremost of which were the control of base thickness and concentration of doping impurities in the collector. Indeed, base thickness affects the transistor effect by determining the percentage of emitter current that reaches the base-collector junction. The main factor affecting this current gain below 1 is due to the recombination of minority carriers in the base before they reach the depletion zone at the base-collector junction where they are aspirated by the electric field. We will consider