INCLUDES

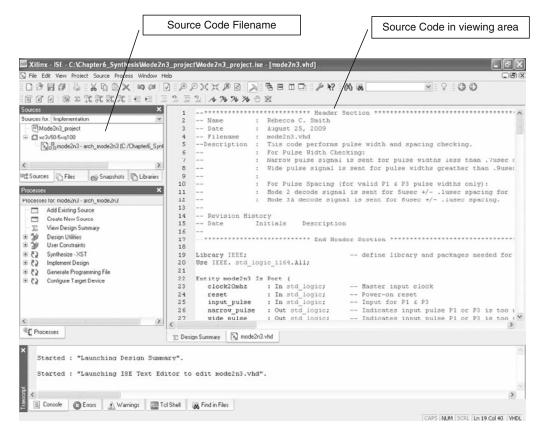

FREE NEWNES ONLINE MEMBERSHIP

# FPGAs 101

Everything you need to know to get started

- Learn how to design and develop FPGAs no prior experience necessary!

- Breaks down the complex design and development of FPGAs into easy-to-learn building blocks

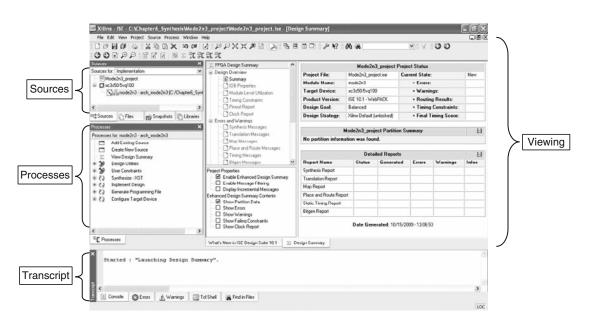

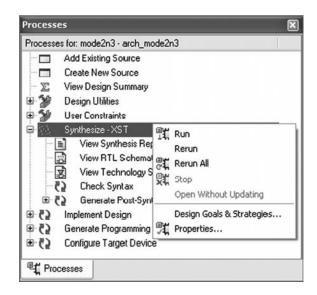

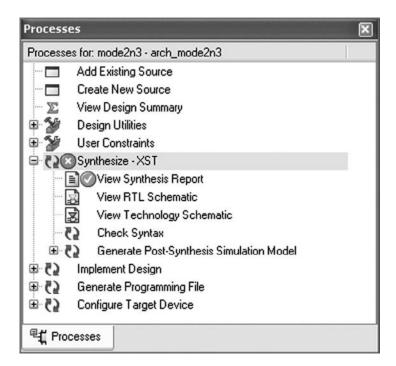

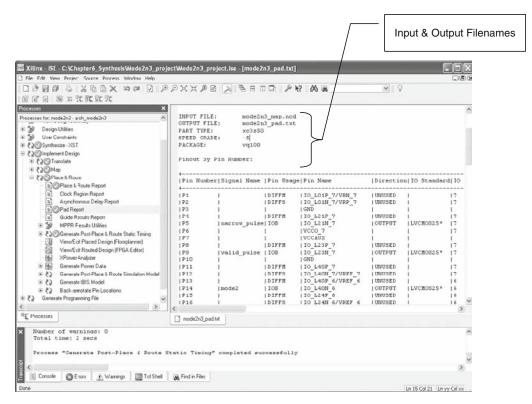

- Contains examples, helpful tips, and step-by-step tutorials for synthesis, implementation, simulation, and programming phases

# Gina R. Smith

# FPGAs 101

This page intentionally left blank

# FPGAs 101

Everything you need to know to get started

Gina R. Smith

AMSTERDAM • BOSTON • HEIDELBERG • LONDON NEW YORK • OXFORD • PARIS • SAN DIEGO SAN FRANCISCO • SINGAPORE • SYDNEY • TOKYO Newnes is an imprint of Elsevier

Newnes is an imprint of Elsevier 30 Corporate Drive, Suite 400, Burlington, MA 01803, USA The Boulevard, Langford Lane, Kidlington, Oxford, OX5 1GB, UK

#### © 2010 Elsevier Inc. All rights reserved.

No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying, recording, or any information storage and retrieval system, without permission in writing from the publisher. Details on how to seek permission, further information about the Publisher's permissions policies and our arrangements with organizations such as the Copyright Clearance Center and the Copyright Licensing Agency, can be found at our website, www.elsevier.com/permissions. This book and the individual contributions contained in it are protected under copyright by the Publisher (other than as may be noted herein).

#### Notices

Knowledge and best practice in this field are constantly changing. As new research and experience broaden our understanding, changes in research methods, professional practices, or medical treatment may become necessary.

Practitioners and researchers must always rely on their own experience and knowledge in evaluating and using any information, methods, compounds, or experiments described herein. In using such information or methods they should be mindful of their own safety and the safety of others, including parties for whom they have a professional responsibility.

To the fullest extent of the law, neither the Publisher nor the authors, contributors, or editors, assume any liability for any injury and/or damage to persons or property as a matter of products liability, negligence or otherwise, or from any use or operation of any methods, products, instructions, or ideas contained in the material herein.

#### Library of Congress Cataloging-in-Publication Data

Smith, Gina R.

FPGAs 101: Everything you need to know to get started / Gina R. Smith.

p. cm.

Includes bibliographical references and index.

ISBN 978-1-85617-706-1 (alk. paper)

1. Field programmable gate arrays.

2. Programmable array logic.

3. VHDL (Computer hardware description language)

4. Digital electronics.

I. Title.

TK7895.G36S6525 2010

621.39'5-dc22

2009041496

#### **British Library Cataloguing-in-Publication Data**

A catalogue record for this book is available from the British Library.

ISBN: 978-1-85617-706-1

For information on all Newnes publications, visit our website, www.elsevierdirect.com

$10 \quad 11 \quad 12 \quad 9 \quad 8 \quad 7 \quad 6 \quad 5 \quad 4 \quad 3 \quad 2 \quad 1$

Printed in the United States of America

## **Contents**

| About the Author                                               | ix |

|----------------------------------------------------------------|----|

| Acknowledgments                                                | xi |

| About This Book                                                |    |

| Acronyms                                                       |    |

| Chapter 1: Getting Started                                     |    |

| 1.1 Introduction                                               |    |

| 1.1.1 VHDL                                                     |    |

| 1.2 Reserved Words                                             | 2  |

| 1.3 Tips for Writing Good Code                                 |    |

| 1.3.1 Tip 1. Use Comments to Convey Information about the Code |    |

| 1.3.2 Tip 2. Indent for Clarity and Readability                |    |

| 1.3.3 Tip 3. Use Standard Format Convention                    |    |

| 1.3.4 Tip 4. Include a Header Section                          |    |

| 1.3.5 Tip 5. Use Brief Descriptive Names                       |    |

| 1.4 HDL Text Editors                                           | 6  |

| 1.4.1 Standalone Text Editor                                   | 6  |

| 1.4.2 Fee-Based Text Editor                                    | 7  |

| 1.5 Editor Features                                            |    |

| 1.5.1 Syntax Color Highlighting                                | 7  |

| 1.5.2 Language Templates                                       | 8  |

| 1.5.3 Row and Column Editor                                    | 8  |

| 1.5.4 Comment/Uncomment Selected Text                          | 9  |

| 1.5.5 Indent/Unindent Selected Text                            |    |

| 1.5.6 Predefined Font Convention                               | 11 |

| 1.6 Signals                                                    |    |

| 1.6.1 Signal Data Types                                        |    |

| 1.6.2 Signal Names                                             |    |

| 1.7 File Structure                                             |    |

| 1.7.1 Optional Header Section                                  |    |

| 1.7.2 Library Declaration                                      |    |

| 1.7.3 Entity Section                                           |    |

| 1.7.4 Architecture Section                                     | 17 |

| 1.8 Starter Tips                             | 19 |

|----------------------------------------------|----|

| 1.9 Chapter Overview                         | 20 |

| Chapter 2: Simple Designs                    |    |

| 2.1 Introduction                             |    |

| 2.2 Starter Template                         |    |

| 2.3 Mathematical Functions                   |    |

| 2.4 Logic Gate                               |    |

| 2.5 D Flip-Flop                              |    |

| 2.6 Latch                                    |    |

| 2.7 Shift Register                           |    |

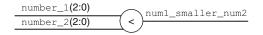

| 2.8 Comparator                               |    |

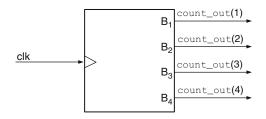

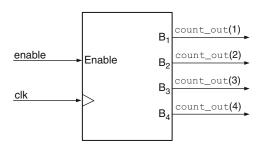

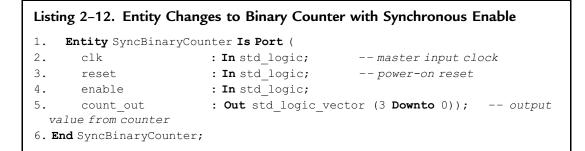

| 2.9 Binary Counter                           |    |

| 2.10 Conversion Functions                    |    |

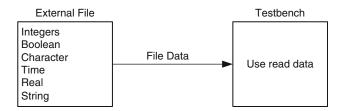

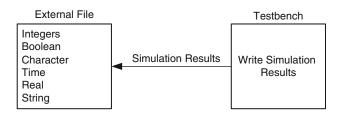

| 2.11 Read File                               |    |

| 2.12 Write File                              | 40 |

| 2.13 Chapter Overview                        |    |

| Chapter 2. EDCA Development Dhases           | 12 |

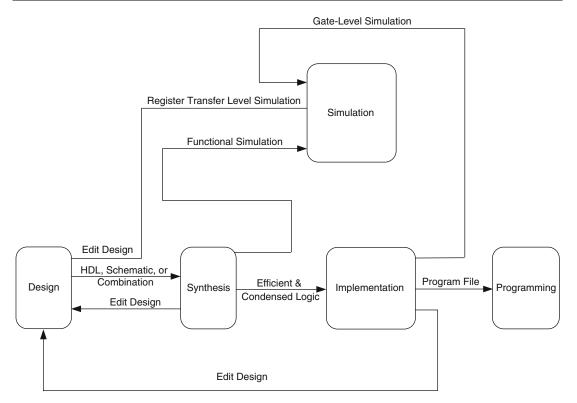

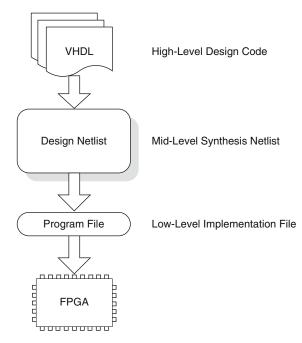

| Chapter 3: FPGA Development Phases           |    |

| 3.1 Introduction                             |    |

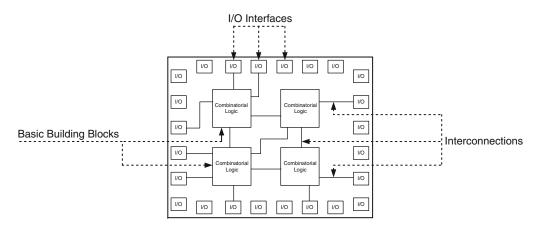

| 3.2 What Is a Field Programmable Gate Array? |    |

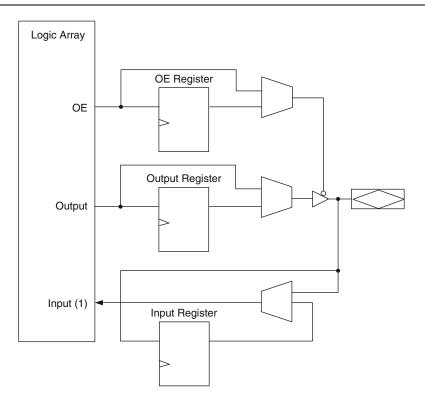

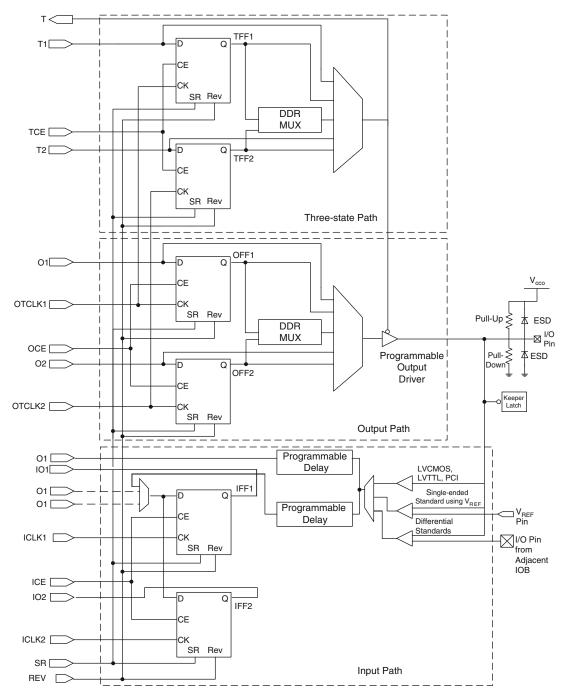

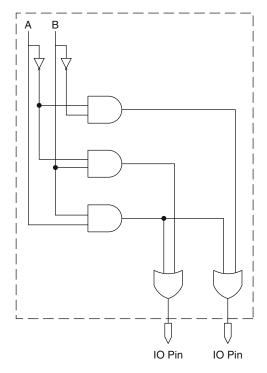

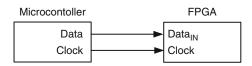

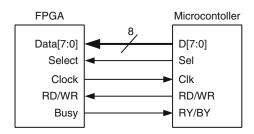

| 3.3 I/O Interfaces                           |    |

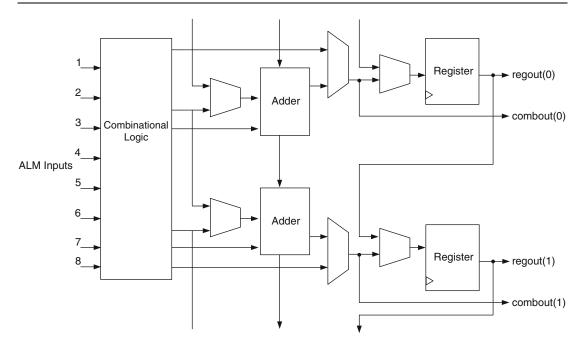

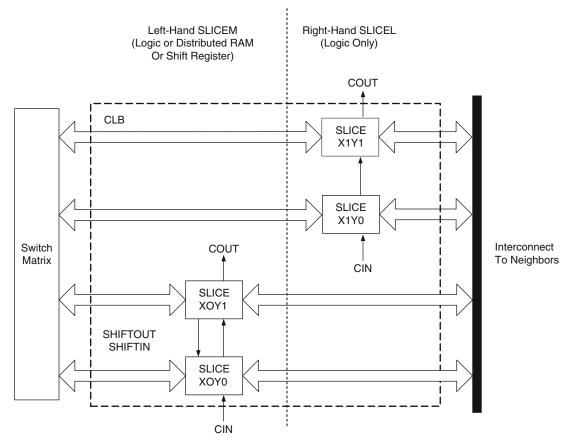

| 3.4 Basic Logic Building Blocks              |    |

| 3.5 Ability to Interconnect                  |    |

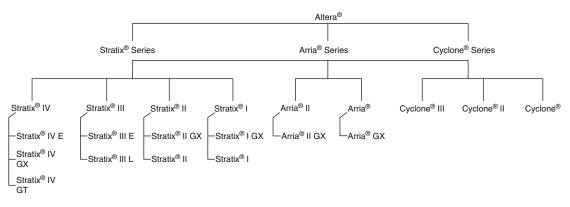

| 3.6 Programmable Logic Device Options        |    |

| 3.7 FPGA Development Phases                  |    |

| 3.8 Chapter Overview                         |    |

| Chapter 4: Design                            | 57 |

| 4.1 Introduction                             |    |

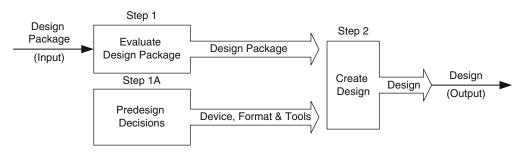

| 4.2 What Is the Design Phase?                | 57 |

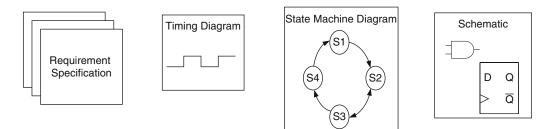

| 4.3 Design Package                           |    |

| 4.4 Evaluating the Design Package            | 59 |

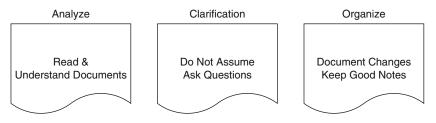

| 4.4.1 Package Analysis                       | 60 |

| 4.4.2 Getting Clarification                  | 60 |

| 4.4.3 Organization                           | 61 |

| 4.5 Predesign Decisions                      | 62 |

| 4.5.1 Design Format                          | 63 |

| 4.5.2 FPGA Manufacturer                      | 65 |

| 4.5.3 Development Tools                      | 66 |

| 4.6 Creating Design Options                  |    |

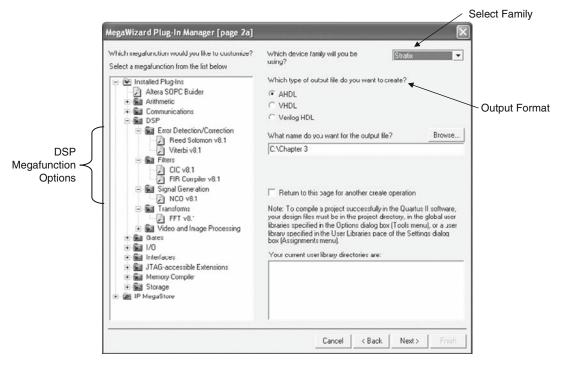

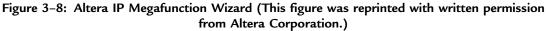

| 4.7 Automatic Code Generators                |    |

| 4.8 Manual Code Generation                   |    |

| 4.8.1 Design Package                         |    |

| 4.9 Chapter Overview                         | 81 |

| Chapter 5: Simulation                       |     |

|---------------------------------------------|-----|

| 5.1 Introduction                            | 83  |

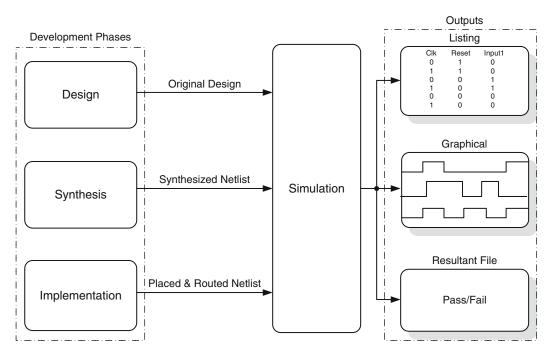

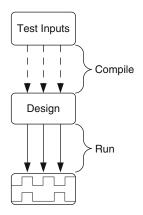

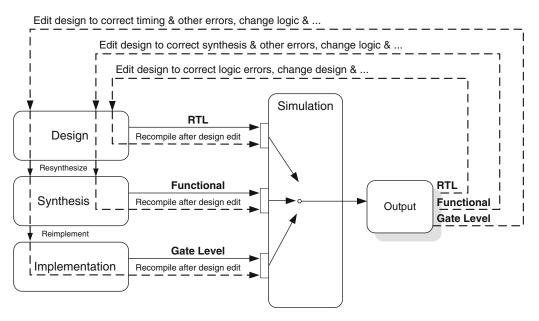

| 5.2 What Is Simulation?                     |     |

| 5.3 Simulation Tools                        | 85  |

| 5.4 Levels of Simulation                    | 86  |

| 5.5 Test Cases                              |     |

| 5.6 Stimulus                                | 89  |

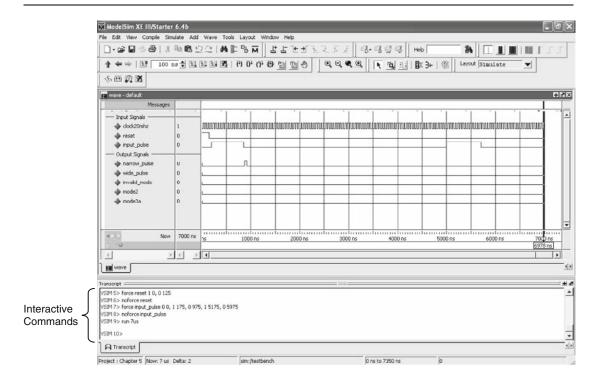

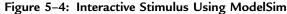

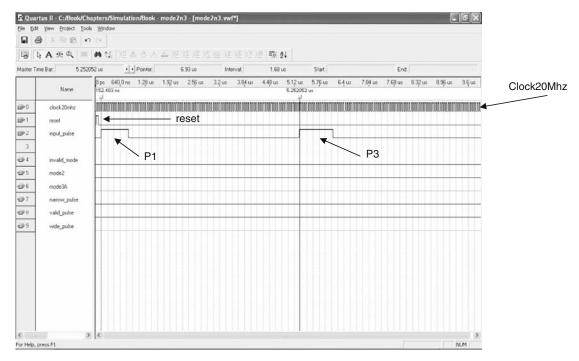

| 5.6.1 Interactive Stimulus                  | 89  |

| 5.6.2 Graphical Test Bench                  |     |

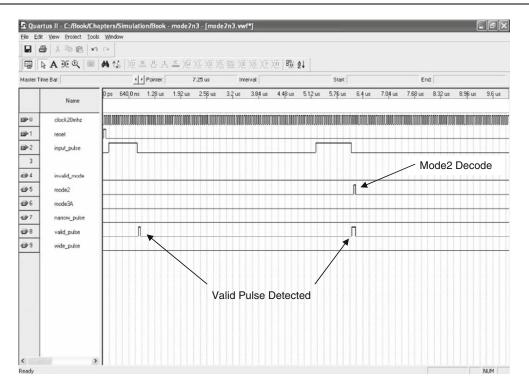

| 5.6.3 HDL Testbench                         | 92  |

| 5.6.4 Manual Testbench                      | 95  |

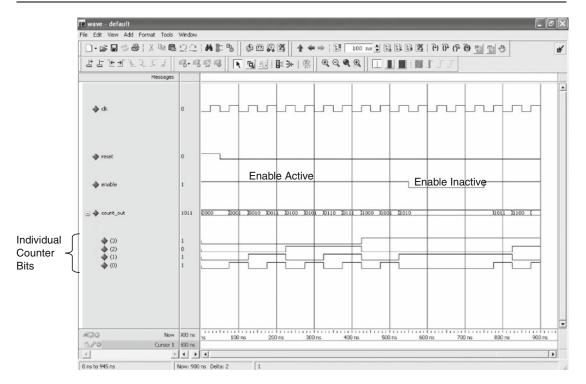

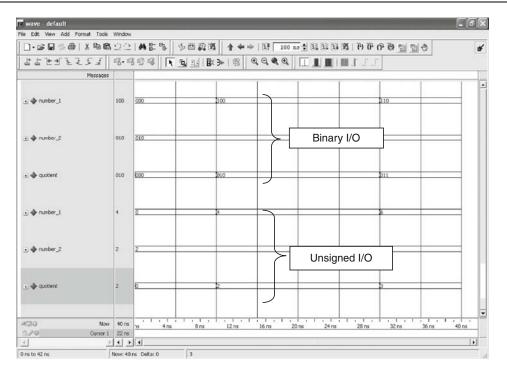

| 5.6.5 Simulation Phase Outputs              | 100 |

| 5.6.6 Automatic Testbench                   |     |

| 5.6.7 Capture Data                          |     |

| 5.7 Simulation Tutorial                     |     |

| 5.8 Chapter Overview                        |     |

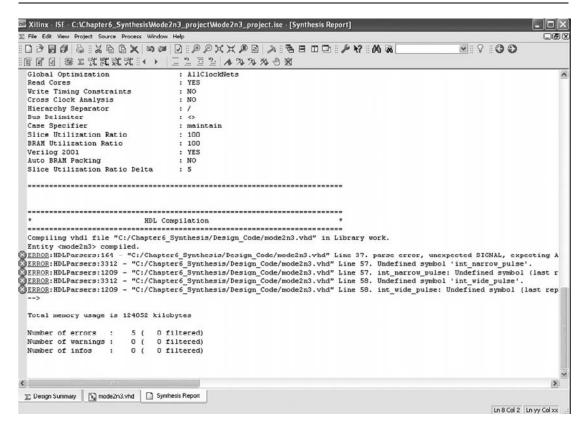

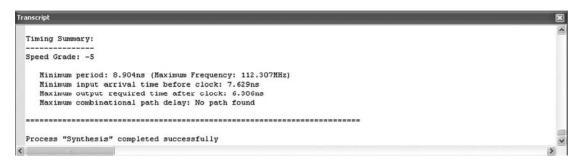

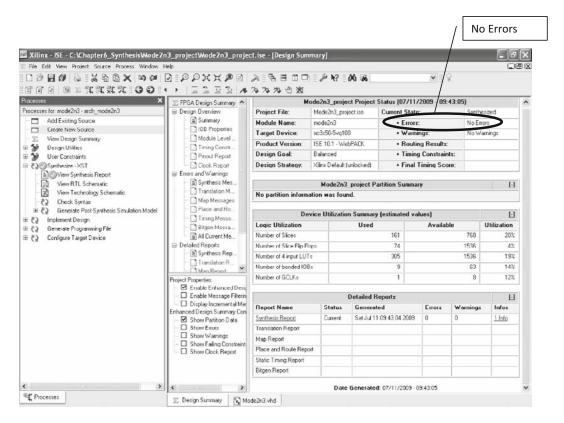

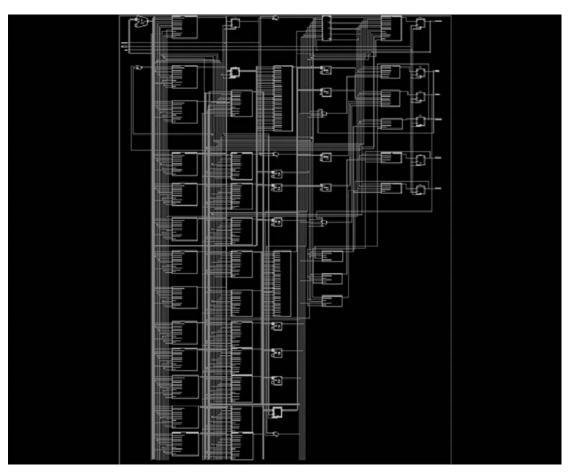

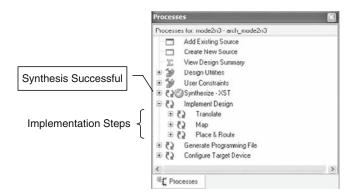

| Chapter 6: Synthesis                        | 127 |

| 6.1 Introduction                            |     |

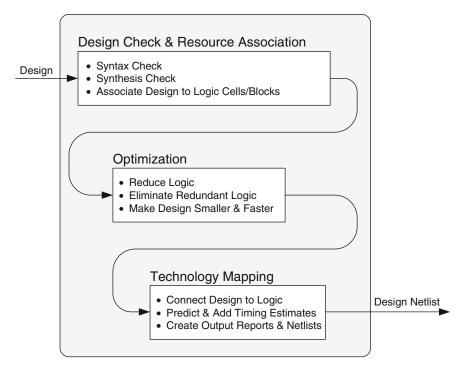

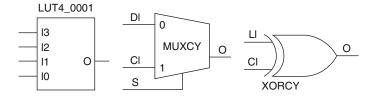

| 6.2 What Is Design Synthesis?               |     |

| 6.2.1 Design Check and Resource Association |     |

| 6.2.2 Optimization                          |     |

| 6.2.3 Technology Mapping                    |     |

| 6.3 Synthesis Phase Tools                   |     |

| 6.3.1 Vendors and Features                  |     |

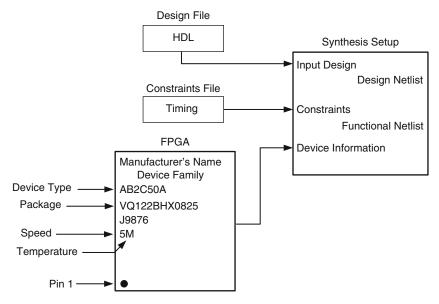

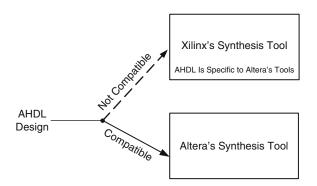

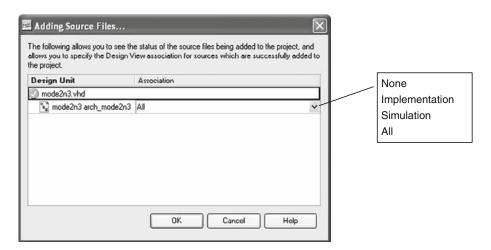

| 6.3.2 Synthesis Tool Setup                  |     |

| 6.4 Synthesis Input                         |     |

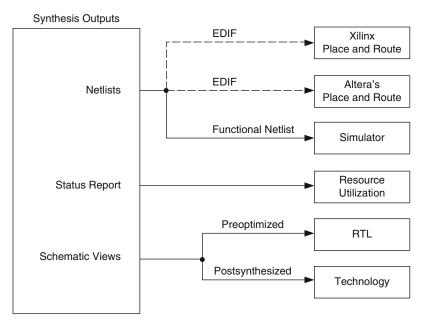

| 6.5 Synthesis Output Files                  |     |

| 6.5.1 Netlists                              |     |

| 6.5.2 Status Reports                        |     |

| 6.5.3 Schematic Views                       |     |

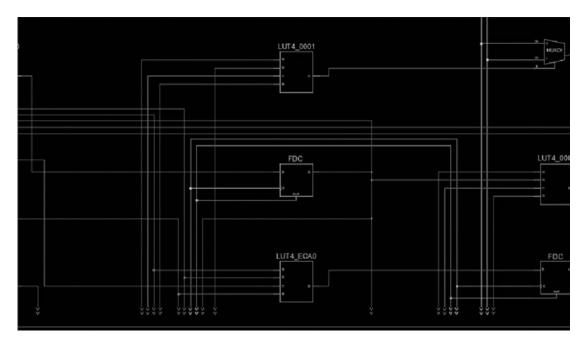

| 6.5.4 Technology Schematic View             |     |

| 6.6 Synthesis Tutorial                      |     |

| 6.7 Chapter Overview                        |     |

|                                             |     |

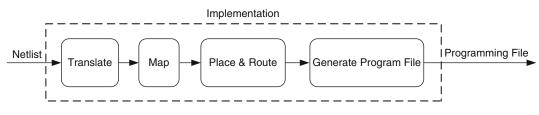

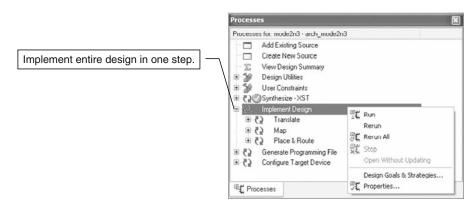

| Chapter 7: Implementation                   |     |

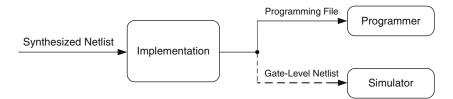

| 7.1 Introduction                            |     |

| 7.2 What Is Implementation?                 |     |

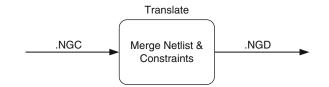

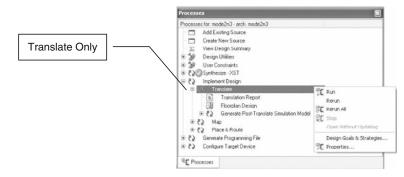

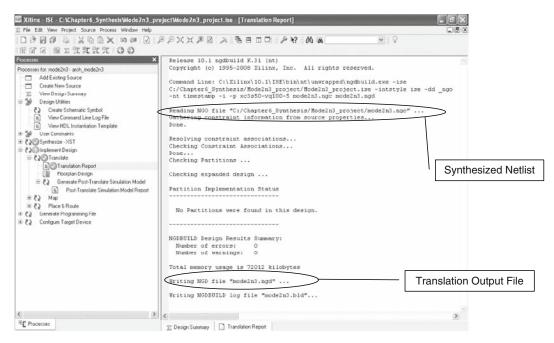

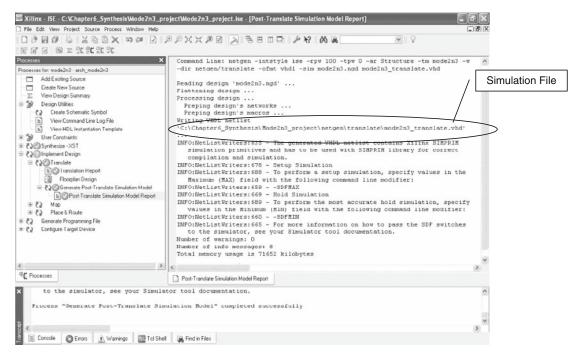

| 7.2.1 Translate                             |     |

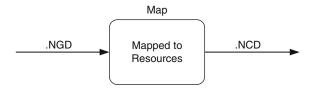

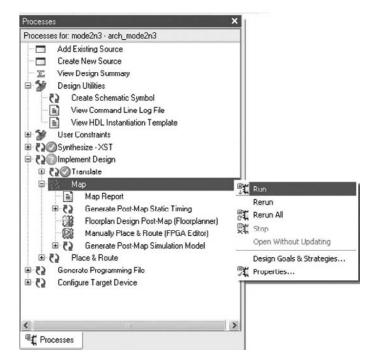

| 7.2.2 Map                                   |     |

| 7.2.3 Place and Route                       |     |

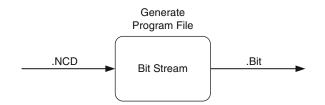

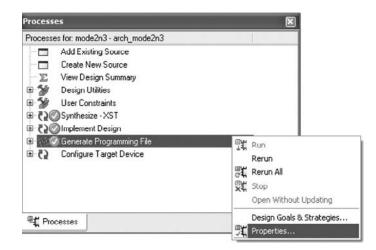

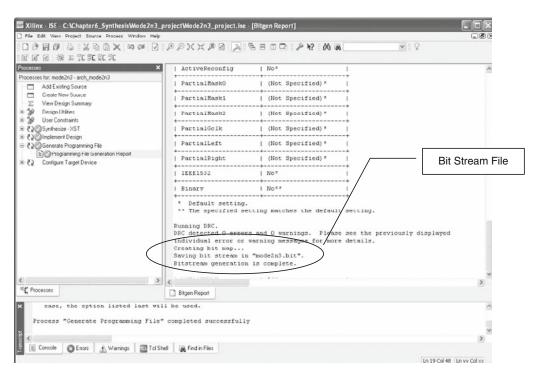

| 7.2.4 Generate Program File                 |     |

| 7.3 Implementation Tools                    |     |

| 7.4 Implementation Inputs                   |     |

| 7.5 Implementation Outputs                  | 166 |

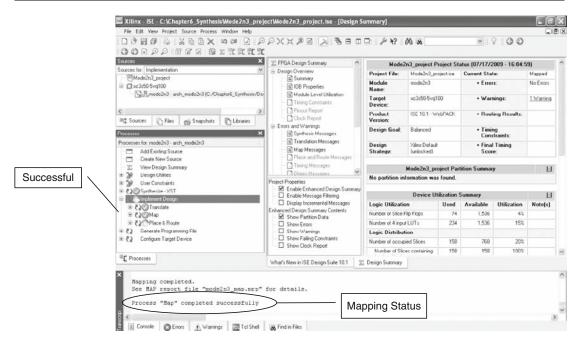

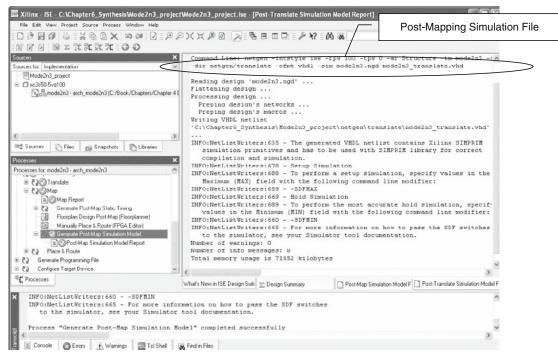

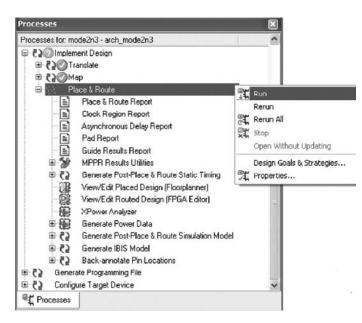

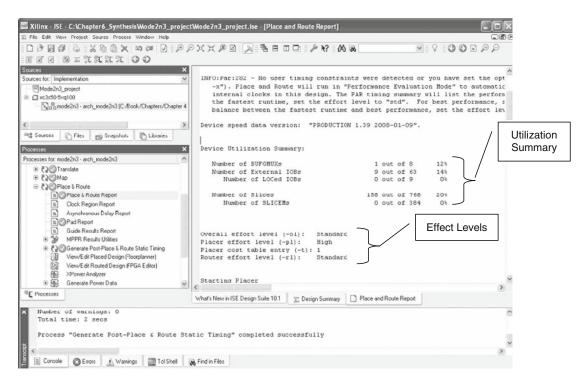

| 7.6 Implementation Tutorial                          |     |

|------------------------------------------------------|-----|

| 7.7 Chapter Overview                                 |     |

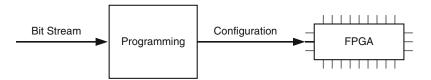

| Chapter 8: Programming                               | 191 |

| 8.1 Introduction                                     |     |

| 8.2 What Is Programming?                             |     |

| 8.3 Tools and Hardware                               |     |

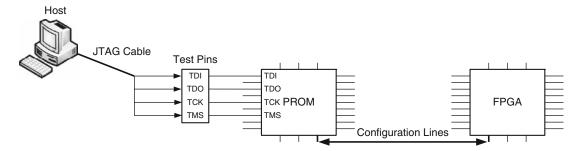

| 8.3.1 Joint Test Advisory Group                      | 193 |

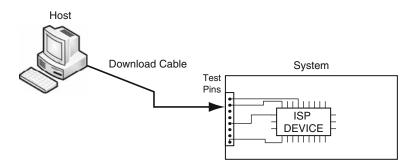

| 8.3.2 In-System Programming                          | 194 |

| 8.3.3 Third Party Programmers                        | 194 |

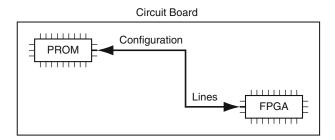

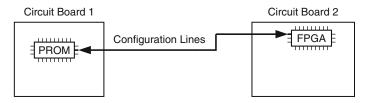

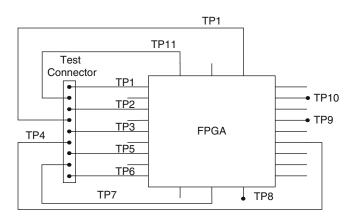

| 8.4 Hardware Configuration                           |     |

| 8.5 Programming Tutorial                             | 198 |

| 8.6 Chapter Overview                                 | 202 |

| References and Sources                               | 205 |

| Web Sites                                            |     |

| Data I/O                                             |     |

| Appendix: Testbenches                                | 207 |

| A–1 Adder and Subtracter Testbench                   |     |

| A-2 Logic Gates Testbench                            |     |

| A–3 D Flip-Flop Testbench                            |     |

| A-4 DFF with Synchronous Enable Testbench            |     |

| A-5 Latch Design Testbench                           |     |

| A-6 Manual Shift Register Testbench                  |     |

| A–7 Comparator Testbench                             |     |

| A-8 Binary Counter Testbench                         |     |

| A-9 Binary Counter with Synchronous Enable Testbench |     |

| A-10 Conversion Testbench                            |     |

| Index                                                | 225 |

### About the Author

Gina R. Smith is the CEO and founder of Brown-Smith RDL Inc., located in Maryland. She is a Senior Electrical/Systems Engineer with an Associate's degree in Applied Science in Electronic Engineering Technology, a B.S. degree in Electrical Engineering, magna cum laude, and an M.S. degree in Systems Engineering with honors, from Johns Hopkins University. Through her company, Gina provides systems engineering and FPGA consulting services. Her accomplishments include a Technical Merit Award from Northrop Grumman, for one of her high-voltage designs. She wrote *The Art of FPGA Construction*, published in *Embedded Systems Design*, January 2008. She is a member of the International Council on Systems Engineering, Women in Defense, and National Defense Industrial Association. She has numerous years experience as a design and project engineer and technical leader. She worked in the fields of avionics, chemistry and biology, primary and secondary surveillance radar systems, information, friend or foe technology, and various other military and defense systems.

Gina has one daughter, Rebecca C. Smith, and lives in Maryland. She enjoys snow skiing, NASCAR, hiking, cooking, and fishing.

Gina can be reached via email at gina.smith@bsrdl.com.

This page intentionally left blank

# Acknowledgments

I thank my daughter, Rebecca C. Smith, who is always so patient, loving, supportive, and understanding with me. She is my true source of motivation. I also thank my mother, Rebecca B. Smith, sisters Julie P. Webb and Sharon C. Smith, and my brother Maurice R. Smith for all their support and encouragement during this project. I am truly an engineer and not a writer. Without the support of my daughter and family, this book journey would have been almost impossible. Many thanks for the technical support I received from Mike Hines, Livia Castrucci, Christopher Loberg, Lawrence Wilson at Tektronix, Scott Silver at The Moving Pixel Company, and Brian Jacobsen at Synopsys for getting me a temporary license. Thanks to Xilinx, Altera, and ModelSim for letting me use their material.

I dedicate this book to my dad, who was my hero and number 1 supporter. He is one of "heaven's angels."<sup>1</sup> I love and miss him very much.

<sup>&</sup>lt;sup>1</sup>James Wellington Smith, June 4, 1932–July 21, 2007

This page intentionally left blank

### About This Book

This book describes the field programmable gate array (FPGA) development process in five development phases: design, synthesis, simulation, implementation, and programming. Each phase is presented in an easy-to-read and easy-to-understand format with examples, helpful tips, and step-by-step tutorials for the synthesis, implementation, simulation, and programming phases. The reader is provided Web addresses for the tools used in the tutorials. This book makes it easy for beginners to learn and understand how to create, modify, and work with FPGA designs. Experienced engineers will find it to be a good reference manual. A primer and some simple digital designs have been provided for those with no programming knowledge. It provides some basic information about writing, reading, and understanding high-level design languages, coding, and other tips. The primer may not be necessary for all readers, but as my mother always says, "It is better to have it and not need it than need it and not have it."

This page intentionally left blank

# Acronyms

| ABEL    | advanced Boolean equation language                |

|---------|---------------------------------------------------|

| AHDL    | Altera hardware description language              |

| ALM     | adaptive logic module                             |

| B.E.S.T | behavior extracting synthesis technology          |

| BGA     | ball grid array                                   |

| CAN     | controller area network                           |

| CIC     | cascaded integrator comb                          |

| CLB     | configurable logic block                          |

| CTRL    | control                                           |

| DFF     | D flip-flop                                       |

| DoD     | Department of Defense                             |

| DRC     | design rule check                                 |

| DSP     | digital signal processor                          |

| EDIF    | electronic digital interchange format             |

| FBGA    | fine-pitch ball grid array                        |

| FFT     | fast Fourier transform                            |

| FIR     | finite impulse response                           |

| FPGA    | field programmable gate array                     |

| FSM     | finite state machine                              |

| GTL     | gunning transceiver logic                         |

| GUI     | graphical user interface                          |

| HDL     | hardware description language                     |

| HSTL    | high-speed transceiver logic                      |

| IEEE    | Institute of Electrical and Electronics Engineers |

| IFF     | information, friend or foe                        |

| I/O     | input/output                                      |

| IOB     | I/O block                                         |

| IOE     | I/O element                                       |

| IP      | intellectual property                             |

| ISE     | Integrated Software Environment                   |

|         |                                                   |

| ISP    | in-system programming                                            |

|--------|------------------------------------------------------------------|

| JTAG   | Joint Test Advisory Group                                        |

| LDT    | lightning data transport                                         |

| LED    | light emitting diodes                                            |

| LSB    | least significant bit                                            |

| LUT    | look-up table                                                    |

| LVCMOS | low-voltage CMOS                                                 |

| LVDS   | low-voltage differential signaling                               |

| LVTTL  | low-voltage transistor-transistor logic                          |

| MSB    | most significant bit                                             |

| NCD    | native circuit description                                       |

| NGC    | native generic compiler                                          |

| NGD    | native generic database                                          |

| OTP    | one-time programming                                             |

| PAR    | place and route                                                  |

| PCI    | peripheral component interconnect                                |

| PROM   | programmable read only memory                                    |

| QoR    | quality of results                                               |

| RAM    | random access memory                                             |

| RTL    | register transfer level                                          |

| SPI    | serial peripheral interface                                      |

| SRAM   | Static random access memory                                      |

| Std    | standard                                                         |

| TCK    | test clock                                                       |

| TDI    | test data in                                                     |

| TDO    | test data out                                                    |

| TMS    | test mode select                                                 |

| TQFP   | thin quad flat pack                                              |

| TRST   | test reset                                                       |

| VHDL   | very high speed integrated circuit hardware description language |

| XST    | Xilinx Synthesis Technology                                      |

|        |                                                                  |

### CHAPTER 1

# Getting Started

#### 1.1. Introduction

This chapter is a primer that provides beginners with some background information that will help in understanding the field programmable gate array (FPGA) development process described in this book. The FPGA process can be confusing and frustrating, making it more difficult to learn or understand, especially if you do not have at least a basic understanding of some background concepts. So, it is my hope this primer will fill in some, if not all, of the gaps. I am a firm believer that we can always learn something new; so for experienced engineers, I believe this book will be both a good refresher and an opportunity to learn something new. The chapter also provides some helpful hints and tips that I found to be useful over the years. I hope they will prove beneficial to you.

Some basic examples are provided to help you better understand hardware description language (HDL) and the FPGA development process. This primer is not meant to teach you all the ins and outs of writing HDL code but to help you better understand some of the terminology as you read the later chapters on the FPGA development process.

In this chapter, you will learn

- HDL coding.

- Tips for writing code.

- HDL editor features.

- HDL file structure.

#### 1.1.1. VHDL

VHDL is a high-level hardware description language used to describe digital circuits that can be programmed into an FPGA. It is a softwarelike programming language that some people, myself included, refer to as *firmware*. It was developed based on a need by the U.S. Department of Defense (DoD). In 1987, the Institute of Electrical and Electronics

Engineers (IEEE) adopted VHDL as a standard, which was released as IEEE Standard (Std) 1076–1987 or VHDL-87. About every five years, the IEEE Standards Committee is supposed to reconvene to review, enhance, and make other modifications to the language. VHDL is also available as VHDL-93, VHDL-2000, VHDL-2002, and VHDL-2008.

VHDL is not case sensitive and requires no special formatting, such as spaces, tabs, or indentations. Each line of code or statement must end with a semicolon, ;. Filename extensions can be either .vhd or .vhdl.

#### 1.2. Reserved Words

Reserved words are words that are defined by the language. Of the many reserved words, you will use some more often than others. Some common VHDL reserved words are shown in Table 1–1. Because VHDL is not case sensitive, reserved words may be in any case.

| Reserved word | Description                                                                          |  |  |  |

|---------------|--------------------------------------------------------------------------------------|--|--|--|

| All           | References what precedes the .all                                                    |  |  |  |

| And           | Logic AND function                                                                   |  |  |  |

| Architecture  | Secondary design unit                                                                |  |  |  |

| Begin         | Signifies the start of sequential statements                                         |  |  |  |

| Bus           | A signal mode that has multiple drivers or signal bits                               |  |  |  |

| Case          | Creates a multiplexer for a signal                                                   |  |  |  |

| Component     | Used to define a component                                                           |  |  |  |

| Constant      | Fixed signal value                                                                   |  |  |  |

| Downto        | Defines range of values                                                              |  |  |  |

| Else          | Precedes alternate action following the "If-Then" statement                          |  |  |  |

| End           | Signifies the end for many things, like entity, architecture, and If-Then statements |  |  |  |

| Entity        | Primary design unit                                                                  |  |  |  |

| If            | Precedes initial conditional                                                         |  |  |  |

| In            | Input signal port                                                                    |  |  |  |

| Inout         | Bidirection signal port                                                              |  |  |  |

| Is            | A connective in a variety of statements                                              |  |  |  |

| Мар           | Maps or connectors actual signal parameters                                          |  |  |  |

| Not           | Logic NOT function                                                                   |  |  |  |

| Then          | Used for conditional statements                                                      |  |  |  |

| Туре          | Enumerated type allows user to define data values                                    |  |  |  |

| Or            | Logic OR function                                                                    |  |  |  |

| Others        | Shortcut used to define all values in a range                                        |  |  |  |

| Out           | Output signal port                                                                   |  |  |  |

| Port          | Used for interface definition                                                        |  |  |  |

Table 1-1: VHDL Reserved Words

(Continues)

| Reserved word    | Description                                               |  |  |  |  |

|------------------|-----------------------------------------------------------|--|--|--|--|

| Process          | Group of sequentially executed code                       |  |  |  |  |

| Read             | Allows an external file to be read                        |  |  |  |  |

| Std_logic        | Signal type defining a single bit                         |  |  |  |  |

| Std_logic_vector | Signal type defining multiple bits                        |  |  |  |  |

| Signal           | Used to assign an object a signal name and data type      |  |  |  |  |

| То               | Used in the middle of some keywords like range and downto |  |  |  |  |

| Write            | Allows you to write to an external file                   |  |  |  |  |

Table 1-1: Cont'd

#### 1.3. Tips for Writing Good Code

Over my many years as a digital designer, I had the opportunity to write many lines of code as well as review, modify, and inherit others' code. Through these sometimes hard experiences, I have developed some tips for writing good code. Some of the tips come from trying to remember code I previously wrote or understanding someone's code. As you become more experienced, you will discover tips that make writing, modifying, and reviewing code much easier.

#### 1.3.1. Tip 1. Use Comments to Convey Information about the Code

Comments are a very important part of coding. You should provide comments as a way of conveying pertinent information about the line or section of code, see Example 1-1.

#### ■ Example 1–1. Good and Bad Code Comments

| Count <= NumberOfBaskets; | number of baskets = $5$        |  |

|---------------------------|--------------------------------|--|

|                           | count equals number of baskets |  |

|                           | count <= NumberOfBaskets;      |  |

#### Good Comment.

Number of baskets = 5 is a good comment, because it defines the actual value being assigned to Count. There is no need to search through the code or another file to find the actual value.

#### Bad Comment.

In Count equals number of baskets, the comment states the obvious and provides no additional information. You have no way of knowing the actual value without further research.

You may find it hard to believe, but I have actually reviewed code that had comments like count <= NumberOfBaskets. The comment was the actual code commented out. I guess the coder did not really know what commenting meant. It is so easy to remember all the ins and outs of your code while you are developing it but not so easy if you have to revisit the same code several weeks or months later. It can be even more difficult when you try to understand someone else's code.

Some would say that each line of code should have a comment. My personal opinion is that obvious code needs no comments. However, you should never generate code without some comments.

VHDL comments are preceded by double dashes: --. The double dashes denote the start of a comment and continue until a carriage return is encountered.

There will be times when you will thank yourself or someone else for providing good comments.

#### 1.3.2. Tip 2. Indent for Clarity and Readability

Indent using spaces or tabs to align groupings of codes. This makes it much easier to read the code and identify common groups of code. See Example 1-2.

#### 1.3.3. Tip 3. Use Standard Format Convention

Standard format convention means that reserved words and user-defined names are presented in the same format. Some companies predefine coding conventions for writing code. If this is not the case, you may decide that all reserved words will be in upper case and user-defined names in lower case. This makes it easy to immediately identify reserved words from userdefined signals. See Example 1–3 for some suggested format conventions.

#### 1.3.4. Tip 4. Include a Header Section

The header section is an optional section that you should include prior to your code. This section may contain information such as the author's name, date created, filename, a brief description summarizing the design, and revision history. You are free to include whatever information you feel will be beneficial. Example 1–4 shows one possible outline for the header section.

#### Example 1–2. Indention

| Not Indented          | Indented              |  |  |

|-----------------------|-----------------------|--|--|

| If count = '100' Then | If count = '100' Then |  |  |

| count = '1';          | count = '1';          |  |  |

| Else                  | Else                  |  |  |

| count <= count + '1'; | count <= count + '1'; |  |  |

| End If;               | End If;               |  |  |

#### Example 1–3. Suggested Format Conventions

Capitalize the first letter; for example, Signal. Lower case all letters; for example, signal. Upper case all letters; for example, SIGNAL. Upper and lower case to separate words; for example, StartCounter. Underscore to separate words; for example, Start\_Counter.

#### Example 1-4. Optional VHDL Header Section

#### 1.3.5. Tip 5. Use Brief Descriptive Names

Always use *brief* but *descriptive* names. Descriptive names make the code easier to read and understand. A good descriptive name should provide information about a signal's function, see Example 1–5.

#### ■ Example 1–5. Descriptive User-Defined Names

You need to name a 40 MHz clock signal.

**Descriptive signal name:** clock40Mhz or clk40MHz.

At first glance, anyone reading the code will know this signal is a 40 MHz clock.

Nondescriptive signal name: c40Mhz or c40.

At first, second, and third glance, it would be very difficult to know anything about the signal based on the nondescriptive signal name, unless there were a comment defining the signal. While comments are very important, they should not be used as a substitute for good signal names. A lot can be said about being brief with your signal names. One good reason for not having long signal names is that, the more you type the name, the more you increase the chance of typos. There is no hard and fast rule as to what is too long, but keep in mind you can use abbreviations to shorten a name.

Once I inherited a coworker's code and *all* the signal names were only a single letter (i.e., a, b, c, etc.) with no comments to be found in the entire design. It took me a while but I finally got the code straightened out and that is how this became one of my "tips." For that code, the signal names were too brief and not descriptive.

#### 1.4. HDL Text Editors

Having a good editor is really important because it is the tool you use to develop and edit code. It should be something that you find easy to use, and it should have HDL features, such as language templates or syntax color highlighting. Many of the FPGA development tools offered by manufacturers like Xilinx and Altera include a text editor. Standalone editors are available for free or purchase. I found some really good free editors just by searching the Internet. My personal preference is a standalone editor. There are many standalone editors. My advice is to make sure that the standalone editor provides support for HDL.

#### 1.4.1. Standalone Text Editor

HDL Works offers Scriptum, a free text editor that supports VHDL and Verilog on Windows and UNIX platforms. I found this editor to be easy to use, with a lot of helpful features. Some of its features are

- Language templates.

- Syntax coloring.

- Multiline comment and uncomment.

- Column and row select/edit.

- Change of case for selected reserved words.

- Bookmarks.

- Standard search, find, and replace.

HDL Works Scriptum text editor can be downloaded for free at www.translogiccorp.com/ index.html.

#### 1.4.2. Fee-Based Text Editor

Symphony EDA offers both free and fee-based text editors. The editors are a part of its simulation/debug software package. The fee-based edition offers more features than the free editor. It has some of the same standard features, which include

- Language templates.

- Syntax coloring.

- Multiline comment and uncomment.

- Column and row select/edit.

Symphony EDA can be found at www.symphonyeda.com.

Downloading and evaluating different editors is an excellent way to try the editor before you buy it. Who knows, you may find a free editor is sufficient for your needs. I did.

Although not required, I highly suggest selecting an editor that is on the same platform (Windows or UNIX) as your FPGA development tools. As simple as this sounds, when I first started with VHDL and FPGA development, some of the tools were Windows based and others were UNIX. We had to ftp the files between the two systems. It was so confusing and created such a mess. When the lead engineer left the company, I jumped at the chance to have all the applications on one platform.

#### 1.5. Editor Features

VHDL code is just a text file, meaning you can use any text editor to create your design. However, it is best to use a text editor that provides special HDL coding features, such as syntax color highlighting, language templates, row/column editor, comment/uncomment selected text, indent/unindent selected text, and predefined keyword font convention. There are many different editors, offering various features, so evaluate a few to determine the best fit for you. Following are some of the features often offered and beneficial during developing and editing code.

#### 1.5.1. Syntax Color Highlighting

This occurs when syntax items are displayed or highlighted in a specific color. Syntax items can be keywords (sometimes defined as various levels or categories), regular text, comments, variables, or strings. They can vary from editor to editor. Generally, the syntax color highlight is set to a default value; however, many editors allow the user to redefine the colors. See Example 1–6 for a snapshot color highlight, where bold and italics represent specific colors.

#### Example 1–6. Syntax Color Highlighting

Syntax highlighting makes it easy to quickly identify specific code elements such as keywords and comments. While some editors offer more syntax highlight items than others, I consider it a must-have feature.

#### 1.5.2. Language Templates

The language template presents HDL syntax for specific language functions in a fill-in-theblank format. For beginners, code templates can be a lifesaver. For example, if you need to know how to write an "If-Then-Else" statement but cannot remember or do not know the syntax, then you may be provided a fill-in-the-blank template similar to the one shown in Example 1–7.

#### **Example 1-7. Language Template:** If-Then-Else

Now all you have to do is insert your code where indicated by the placeholders on the template. Templates vary from editor to editor, but they have the same basic concept.

#### 1.5.3. Row and Column Editor

Most people are familiar with row editing; however, column editing is not as familiar. A row editor is used when multiple rows are selected at one time, see Example 1–8. Similarly, a column editor allows you to select multiple columns on different rows at once, see Example 1–9. Column editing is a great feature to use when the data you want to edit is in the same column but on different rows. For most HDL editors, the alternate,

#### Example 1–8. Row Edit

Select, copy, and paste the second row. The gray area indicates the text selected using the row editor.

```

Row edit copy:

If front_door_open = `1' Then -- 1 means front door was opened

alarm_timer <= alarm_timer + `1'; -- increment time to sound alarm

End If;</pre>

```

Row edit paste:

$alarm_timer <= alarm_timer + '1'$ ; -- increment time to sound alarm Notice that only the selected row was copied and pasted.

#### Example 1–9. Column Edit

Use the column edit to select, copy, and paste the two comments. The gray area shows the selected text. If front door open = 1' Then -- 1 means front door was opened

```

alarm_timer <= alarm_timer + `1'; -- increment time to sound alarm</pre>

```

End If ;

Column edit paste:

-- 1 means front door was opened

-- increment alarm counter

With column editing, I am able to copy and delete selected data without affecting the surrounding text, but I have little success with pasting.

alt, key with the mouse button is used for column editing; however, in Microsoft Word, it is the control, Ctrl, key with the mouse.

#### 1.5.4. Comment/Uncomment Selected Text

Sometimes it is necessary to comment out multiple lines of code instead of individually commenting each line. Some editors provide an option to comment/uncomment select lines. Some editors comment/uncomment only at the beginning of a row. This means that, if the cursor is put on any part of a row, the comments syntax or double dashes (--) for VHDL, see Example 1–10, are inserted as the first two characters on that row. When uncommenting, some editors delete only the comment syntax at the beginning of the row, ignoring any other comment syntax on the row, see Example 1–11.

#### Example 1–10. Comment

```

Select and comment to the three lines of code. The gray area shows selected text.

If front_door_open = '1' Then -- 1 means front door was opened

alarm_timer <= alarm_timer + '1'; -- increment time to sound alarm

End If;

The selected text is now commented.

-- If front_door_open = '1' Then -- 1 means front door was opened

-- alarm_timer <= alarm_timer + '1'; -- increment time to sound alarm

-- End If;</pre>

```

#### Example 1–11. Uncomment Text

Select text to be uncommented. The gray area shows the selected text.

-- If front\_door\_open = '1' Then -- 1 means front door was opened -- alarm\_timer <= alarm\_timer + '1'; -- increment time to sound alarm -- End If;

#### Selected text is now uncommented.

```

If front_door_open = `1' Then -- 1 means front door was opened

alarm_timer <= alarm_timer + `1'; -- increment time to sound alarm

End If;</pre>

```

#### Example 1–12. Indent Text

Select and indent the second and third lines. The gray area shows the selected text.

```

If front_door_open = '1' Then -- 1 means front door was opened

alarm_timer <= alarm_timer + '1'; -- increment time to sound alarm

End If;</pre>

```

#### The second and third lines are indented.

```

If front_door_open = '1' Then -- 1 means front door was opened

alarm_timer <= alarm_timer + '1'; -- increment time to sound alarm

End If;</pre>

```

#### Example 1–13. Unindent Text

The **End If;** should be aligned under If. Now select and unindent the last line. The gray area shows selected text.

```

If front_door_open = `1' Then -- 1 means front door was opened

alarm_timer <= alarm_timer + `1'; -- increment time to sound alarm

End If;

The third line is now properly aligned.

If front_door_open = `1' Then -- 1 means front door was opened

alarm_timer <= alarm_timer + `1'; -- increment time to sound alarm

End If;</pre>

```

#### 1.5.5. Indent/Unindent Selected Text

Some editors allow you to indent only a portion of the row, while others indent the entire row. This feature generally works like the comment/uncomment feature. Example 1-12 shows selected text being indented, and Example 1-13 shows how selected text is unindented.

#### 1.5.6. Predefined Font Convention

The predefined font convention is when the editor converts keywords or selected text to a specific font style or size, such as all lower or upper case. This feature can be used to keep your code consistent, because sometimes you may miss applying your font convention during the development process. Some editors may require you to highlight the text you want to convert, while others perform it automatically. In Example 1–14, the line(s) or code are highlighted for the font conversion.

#### Example 1–14. Font Convention

```

Convert keywords to upper case.

```

Upper case keywords converted.

```

IF front_door_open = `1' THEN -- 1 means front door was opened

deactivate_alarm <= deactivate_alarm + `1'; -- increment alarm counter

END IF;</pre>

```

#### 1.6. Signals

In VHDL, signals represent some kind of data. They are assigned a name and data type. The basic signal syntax follows:

Signal <signal name>: <data type>;

More advanced signal assignments are possible but not discussed in this book.

You can use signals in mathematical equations, to assign values, to connect other signals, and to store values in them. They must be assigned unique, nonreserved word names and a data type.

#### 1.6.1. Signal Data Types

The VHDL data are of a specific type such as std\_logic, std\_logic\_vector, bit, bit\_vector, or user defined. Std\_logic is read as standard logic and std\_logic\_vector as standard logic vector. Bit and bit\_vector are read as written. The user-defined type is when the coder defines the signal type. This is a little more advanced and can be somewhat confusing when you are first starting out, so it is not covered in this book. Once you are more comfortable with the language, it will be easier to understand and implement the more advanced aspects of the language. Plus std\_logic and std\_logic\_vector are generally the most commonly used data types. Each signal type has acceptable values. There are nine acceptable values for std\_logic and std logic vector, see Table 1–2.

Std\_logic signals represent one data bit and std\_logic\_vector represents several data bits. The signal assignments for standard logic and standard logic vector data types are shown in Example 1–15. The number of data bits for a std\_logic\_vector is defined in the signal assignment statement.

| Value | Description              |

|-------|--------------------------|

| 0     | Low or logic zero        |

| 1     | High or logic one        |

| W     | Weak unknown signal      |

| L     | Weak low                 |

| Н     | Weak high                |

| U     | Unknown or uninitialized |

| Z     | High impedance           |

| Х     | Unknown                  |

| -     | Don't care               |

Table 1-2: Standard Logic Acceptable Values

#### Example 1–15. Standard Logic and Standard Logic Vector Signal Assignment

Signalclock\_in: std\_logic;Signalup\_counter: std\_logic\_vector (4 downto 0);

#### Example 1–16. Valid Standard Logic Signal Values

```

clock_in value is "1"

up_counter value is "1XZOU".

```

The signal named clock\_in has a data type of std\_logic. This means clock\_in can have only one of the nine acceptable values, while the signal named up\_counter is 5 data bits wide and each of the bits can be one of the nine acceptable values. The most significant bit (MSB) is bit 4 and the least significant bit (LSB) is 0. See Example 1–16 for valid signal values.

Bit and bit vector have two acceptable types, see Table 1–3.

Bit represents one data bit, and bit\_vector represents several data bits. Example 1–17 shows signals clock out being assigned data type bit and down counter2 bit vector.

The signal named clock\_out has a data type of bit. This means clock\_out can have only one of the two acceptable values, while the signal named down\_counter2 is 4 bits wide and each of the bits can be one of the two acceptable values. See Example 1–18 for valid bit signal values. The MSB is bit 3 and the LSB is 0.

It is okay to use bit and bit vector; however; they are rarely the deserved data type.

| Table | 1-3: | Bit | Accepta | ble | Va | ues |

|-------|------|-----|---------|-----|----|-----|

|-------|------|-----|---------|-----|----|-----|

| Value | Description       |

|-------|-------------------|

| 0     | Low or logic zero |

| 1     | High or logic one |

#### Example 1–17. Bit Signal Assignment

| Signal | clock_out     | : bit;                     |

|--------|---------------|----------------------------|

| Signal | down_counter2 | : bit_vector (3 downto 0); |

#### Example 1–18. Valid Bit Values

clock\_out is "0"

down\_counter2 is "0011"

RuleAcceptableNot AcceptableMust start with letterfour4Cannot be a keywordinput\_signalinputDon't use special charactersinput\_data\$idMust not contain spacesInputDataInput Data

#### Table 1-4: VHDL Signal Name Restrictions

#### 1.6.2. Signal Names

Signal names are user defined, but VHDL has some name restrictions, such as those provided in Table 1–4. In addition to the VHDL restrictions, remember to make your names descriptive.

#### 1.7. File Structure

The VHDL file structure consists of three sections: the library declaration, entity section, and architecture section with an optional header section.

#### 1.7.1. Optional Header Section

As stated before, the header section is completely optional but highly suggested. However, I found the revision history to be beneficial, especially when modifying someone else's code. When I fix code problems, the revision history enables me to see if the current problem existed before any previous code changes. I have mixed feeling about keeping the prereleased code revision history in the released code. It is a good idea to have the revision history while developing, just in case someone else inherits the code. However, for the released code, this history may not add any value, in which case should be removed. It all depends on the specific situation.

#### 1.7.2. Library Declaration

Just like software code, VHDL must be compiled. The place where the compiler stores the design information and other files to be used for analysis, synthesis, and simulation is called the *library*. The library declaration section is where you declare or call out libraries. By using the library clause you make the library visible and its contents available to the

design. The use clause, which follows the library clause, states which package from the library to use. Libraries can be a defined by standards, users, or third parties, like manufacturers.

IEEE is a commonly used standard library. Some of the packages in IEEE are Std\_logic\_1164 and Std\_logic\_arith, see Table 1–5 for some of the data types and functions defined by these packages.

User-defined libraries are those created by regular users or designers. Oftentimes design groups or projects utilize user-defined libraries by storing common constants, data types, and other commonly used things in a library shared by the group. This can save a lot of time, because each individual is not spending time creating the same information. The user-defined library is placed in a common, team-accessible area. Another benefit to groups using a user-defined library is that it ensures everyone uses the same values, functions, definitions, and the like. This does not guarantee the values are correct; however, it makes it easier to correct something wrong in one place rather than in several files.

Third party libraries are supplied by companies like Xilinx and Altera. These libraries contain such information as timing used for simulation, IP cores and logic gates.

The library syntax is the reserved word *Library* followed by the library's name. The "use" clause syntax specifies the package, its library, and how much of the package is used, see Example 1–19. A package is a separate VHDL file that defines things like functions, data types, constants, and procedures.

| Package         | Data Types                                                                        | Functions                     |

|-----------------|-----------------------------------------------------------------------------------|-------------------------------|

| Std_logic_1164  | <pre>std_logic,<br/>std_logic_vector,<br/>std_ulogic,<br/>std_ulogic_vector</pre> | AND, NAND, OR, NOR, XNOR, NOT |

| Std_logic_arith | Unsigned, signed                                                                  | +, -, *, ABS, <, <=, =, >=, > |

Table 1-5: IEEE Standard Library Packages, Data Types, and Functions

#### Example 1–19. Library and Use Syntax

Library <library name>;

Use <library name>.<package>.<what portion are you using>;

For example, std\_logic is a widely used data type, which is defined in the

std\_logic\_1164 package. To use this data type, you need to declare the library

where it is defined and state the package using the use clause in the library declaration

(Continues)

section, see Example 1–20. Some additional packages included in the IEEE library are std\_logic\_arith, std\_logic\_unsigned, and std\_logic\_signed. If you are using several packages from the same library, the library needs to be stated only once.

What these two lines say is this: Make the IEEE library visible to the design and make the entire (i.e., all) std\_logic\_1164 package available to your design. So whatever is defined in the std\_logic\_1164 package can now be used in your code. You are not required to use all the features in the package and can specify only the portion you want: however, using the all just makes things easier. So my advice is, unless you have a good reason for not wanting to include everything, it is a good idea to stick with all. Now you need not worry about changing the use statement if your design requires additional features.

#### 1.7.3. Entity Section

The entity section is where you define all the inputs and outputs. The syntax for the entity section is shown in Example 1–21, and Example 1–22 shows a simple design entity.

Note: Entities can be a little more complex; however, for this primer, the entity is the top level of the design and represents the inputs and output pins on the FPGA.

#### Example 1-20. Library and Use

```

Library IEEE; -- IEEE library is visible to the design

Use IEEE.std_logic_1164.all; -- The contents in the std_logic

-- package can now be used

-- in the design code

```

#### Example 1–21. Entity Syntax

```

Entity <entity name> Is Port(

<signal name : <signal direction> <data type>);

End <entity name>;

```

#### Example 1–22. Entity Code

```

Entity test_code Is Port(

```

| clk                       | : In std_logic;    | input clock                        |

|---------------------------|--------------------|------------------------------------|

| start_counter             | :Instd_logic;      | starts counter when door is opened |

| ready_signal              | : Inout std_logic; | indicates alarm status             |

| sound_alarm               | : Out std_logic);  | alarms buzzer when timer expires   |

| <pre>End test_code;</pre> |                    |                                    |

|                           |                    |                                    |

#### 1.7.4. Architecture Section

The architecture section is where you write the design code, see Example 1–23. The design code describes the functions by using the software-like programming language VHDL.

Now, you use the defined functions, data types, and so for the package(s) declared or called out in the library declaration section. Your design receives and passes design data using the input, bidirectional (inout), and output ports defined in the entity section.

#### Example 1–23. Architecture Syntax

```

Architecture <architecture name> Of <entity name> Is

<Define signals and constants>

```

Begin

This section is where the design is written. It consists mainly of component instantiations, synchronous logic, sequential statements, processes, concurrent statements, and asynchronous logic.

*Component instantiation* basically makes a direct connection to a library component. The actual code for the component is predefined in another file. More details about component instantiation are provided in the testbench section.

Synchronous logic is code that gets updated based on an event, such as the rising or falling edge of a clock.

Sequential statements are found in processes and executed in the order in which they appear.

A process is a group of code that is executed sequentially. They are like mini programs with very specific format, which includes the use of the reserved words process, begin, and end process, and a sensitivity list, see Example 1–24.

#### Example 1–24. Process Syntax

It is good coding practice to perform only one function in a process. The code inside a process is executed only when any signal in the sensitivity list changes state.

The process name is optional and user defined. Even though it is optional, you should always name your processes. The name should be short and descriptive enough to allow you to distinguish one process from another.

One good reason to make the name descriptive is that you may have a design with four counters, so naming them <code>counter1</code>, <code>counter2</code>, . . ., tells you nothing about the counters. Let us say one counter counts the number of times the temperature sensor goes below 32°F, above 95°F, stays at 0°F for longer than 5 minutes and another one at 60°F for longer than 10 minutes. You may decide to name them <code>count\_below32F</code>, <code>count above95F</code>, temp at0F, and temp at60F.

The sensitivity list is where you list all the signals that you want to cause the code in the process to be evaluated whenever it changes state. For example, clock or master reset is often used in a sensitivity list. Whenever the reset or clock changes state, the code inside the process is executed.

*Concurrent statements* are outside of processes and executed or updated at any time any of the signals changes, see Example 1-25.

#### Example 1–25. Concurrent Statement

Sum\_Temp <= count\_above95F + count\_below32F; Sum\_Temp changes and is updated any time count\_above95F or count\_below32F changes.

Asynchronous logic is updated or changed independent of events. End <architecture name>;

Now that you have all the pieces, Example 1–26 shows how it looks all put together. Using this or a similar template is a good way to start each design.

```

■ Example 1–26. VHDL File Structure

-- Name

:

-- Date

:

-- Filename

:

-- Description

:

-- Revision History

Initials

Description

-- Date

Library IEEE;

Use IEEE.std logic 1164.all;

Entity <entity name> Is Port

(<list of ports or design inputs and outputs>);

End <entity name>;

Architecture <architecture name> Of <entity name> Is

<in this section define signals and constants>

Signal <signal name> : Data Type;

Begin

<concurrent statements>

<process name>: Process (sensitivity list)

Begin

<sequential statements>

End;

End <architecture name>;

```

So far the entity defines only the design's interface; however, your design most likely requires additional signals. These signals are defined in this section, prior to them being used and the actual design code. Once this is complete, you can take the signal names and the available features from the packages and develop code using asynchronous, synchronous, concurrent, and sequential code.

#### 1.8. Starter Tips

A lot is involved in developing FPGA designs. Here are some tips to help as you get started.

- Utilize field application engineers and salespeople, who can really provide some good help and guidance. They can provide information on the latest hardware and tool developments, suggest devices, clarify details about their products and services, provide samples, arrange demos and software/hardware trials and temporary licenses, and many other things. If they cannot help you, they will at least point you in the correct direction. I realize some salespeople can be pushy, but I have found most of them to be very helpful and not very pushy.

- Evaluation boards are a good way to get experience. The evaluation boards are offered by manufacturers and third party companies. They come with different FPGA devices, development software, programming and other cables, power supplies and other resources like light emitting diodes, LEDs, pushbuttons, switches, and oscillators. Check out the specific manufacturer's Web site for specific details on the board and suppliers. Some companies purchase evaluation boards to try specific devices or features before using them in designs. So, if you are considering using an FPGA that has an embedded processor, then it may be a good idea to purchase an evaluation board and try it before using it in a design.

- Take advantage of the many free and trial offers. This will give you a good opportunity to experiment and discover your likes and dislikes.

# 1.9. Chapter Overview

Everyone has his or her style and approach to FPGA development. As you work with it, you will develop your style. So do not worry if you see things differently from everyone else; the process should be the same. Once you learn the general process you will have no problem using your knowledge to develop and understand designs and switching between different development tools and manufacturers.

### Key Points to Remember

- Select an editor that you find easy to use and that has features you like. You will be using your editor a lot to develop and modify code.

- Take the time to include the optional headers section prior to your design code. Use this section to briefly describe the design and provide revision information.

- Always include "good," meaningful comments in your code.

- Make your user names brief and descriptive.

### Chapter Links

For your convenience, here is a list of links to the editors discussed in this chapter:

HDL Works Scriptum located at www.translogiccorp.com/index.html.

Symphony EDA located at www.symphonyeda.com.

# CHAPTER 2

# Simple Designs

### 2.1. Introduction

The purpose of this chapter is to present some simple VHDL design code. These designs can easily be modified to perform advanced functions or be copied and used as a standalone design or a part of a larger design. In this section, the design code consists of a combination of processes, concurrent and sequential statements, and synchronous and asynchronous logic. When appropriate, the designs have a block diagram, corresponding to the VHDL design code and some brief comments to help explain the code.

In this chapter, you will learn

- How to create simple VHDL designs.

- How to add more complexity to simple designs.

- VHDL shortcuts.

# 2.2. Starter Template

For each new design, I like to start with a "starter" HDL template. The starter HDL template consists of a header section, library declaration section, entity, and architecture syntax placeholders. Because I always use the IEEE library and the std\_logic\_1164 package, I have made line 10 Library IEEE; and line 11 Use.IEEE.std\_logic\_1164.all; statements a part of my template instead of syntax placeholders. While many editors provide a starter HDL template, I present my template as an additional option.

When I first started writing VHDL, I could not remember if the signal name assignments went before or after the Begin in the architecture section. Therefore, a signal assignment was included as a placeholder in my template. The template can save you time, because it keeps you from retyping the same information from program to program. As you write code, you may decide to make your own template or modify a preexisting template. My starter HDL template is shown in Listing 2–1. Because the header section has no importance for the examples in this section, it is shown only in the first example.

```

Listing 2–1. VDHL Starter Template

1.

2.

: Rebecca B. Smith

-- Name

3.

-- Date

: August 25, 2009

4. -- Filename

: Entity Name.vhd

5.

-- Description : This starter HDL template provides placeholders and

syntax that can be used

6.

--: to help develop design code. Modify the template to meet your needs.

7.

Revision History

8.

-- Date

Initials

Description

9.

10.

Library IEEE;

-- define library and packages needed for

this design

11.

Use IEEE.std logic 1164.All;

12.

13. Entity <entity name> Is Port( -- define interface signals

14.

<signal name> : <direction> <data type>;

15.

<siqnal name>

: <direction> <data type>);

16. End <entity name>;

17.

18.

Architecture <architecture name> Of <entity name> Is

19.

Signal <signal name> : data type; -- define internal signals

if necessary

20.

21.

Begin

<concurrent statements> -- add concurrent statements if necessary

22.

23.

-- statement(s) will update anytime

24. <process name>: Process (sensitivity list) -- add process if

necessary

25. Begin

26.

<sequential statements>; -- statement updates when a signal

in sensitivity list changes

27. End Process;

28.

End <architecture name>

```

# 2.3. Mathematical Functions

Mathematical functions, such as adder, subtractor, multiplier, and divider, are performed using arithmetic operators; see Table 2–1. The arithmetic operators can be used in concurrent and/or sequential statements; it depends on the circuit. To keep things simple, this example uses only a concurrent statement, and a sequential statement is demonstrated in later examples.

| Symbol         | Data Ty                                          | rpes             | Package            |

|----------------|--------------------------------------------------|------------------|--------------------|

| Symbol         | Accepts                                          | Returns          | Гаскаде            |

| +              | <pre>std_logic, integer, std_logic_vector</pre>  | std_logic_vector | std_logic_unsigned |

| Addition       | signed, unsigned,<br>natural, integer            | signed, unsigned | numeric_std        |

| _              | <pre>std_logic, integer, std_logic_vector,</pre> | std_logic_vector | std_logic_unsigned |

| Subtraction    | signed, unsigned,<br>natural, integer            | signed, unsigned | numeric_std        |

| *              | std_logic_vector                                 | std_logic_vector | std_logic_unsigned |

| Multiplication | signed, unsigned,<br>natural, integer            | signed, unsigned | numeric_std        |

| /<br>Division  | signed, unsigned,<br>natural, integer            | signed, unsigned | numeric_std        |

Table 2-1: Mathematical functions

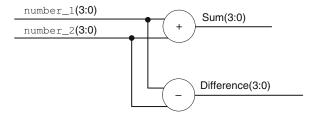

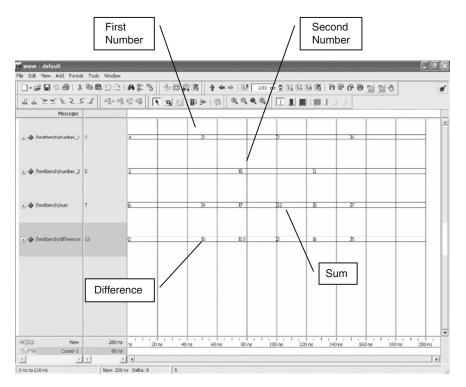

Figure 2-1: Adder and Subtractor

Figure 2–1 shows a simple two-input adder and subtractor. The design code is shown in Listing 2–2. If you are writing design code based on a schematic, it is best that the code and schematic signal names match. This makes writing and debugging the code much easier.

### Lines 10–12. Library Declaration

The addition and subtraction operators are defined in the std\_logic\_unsigned package, which is made visible to the design in the library declaration section. You may not know all the libraries required at the beginning of your design, but you can add them as needed. Knowing which library to use can be challenging, until you remember which library contains the function(s) you need. So, at first, you may have to open different libraries to find what you need.

```

Listing 2-2. Adder and Subtracter

1.

2.

-- Name

:

3.

-- Date

•

4.

-- Filename

5.

-- Description

:

6.

-- Revision History

7.

-- Date

Initials

Description

8.

___

9.

10. Library IEEE;

11.

Use IEEE.std logic 1164.All;

12.

Use IEEE.std logic unsigned.All;

13.

14.

Entity MathematicalOperators Is Port (

number_1 : In std_logic_vector (3 Downto 0);

15.

16.

number 2

: In std logic vector (3 Downto 0);

17.

sum

: Out std logic vector (3 Downto 0);

18. difference : Out std logic_vector (3 Downto 0));

19. End MathematicalOperators;

20.

21.

Architecture arch MathematicalOperators Of MathematicalOperators Is

22.

23.

Begin

24.

-- the sum and difference are calculated and provided as output for two

4-bit numbers

25.

sum

<= number 1 + number 2;

26. difference <= number 1 - number 2;

27. End arch MathematicalOperators;

```

#### Lines 14–19. Entity Section

The interface signals for this design are defined as follows.

Two inputs:

Signal Names: number\_1 and number\_2

Data Type: std logic vector

Size: 4 bits

Two outputs:

Signal Names: sum and difference

```

Data Type: std_logic_vector

Size: 4 bits

```

Line 14 defines the entity's name as MathematicalOperators. This name was selected because it provides some detail about the design code's function. You should develop and use a naming convention for your entity, architecture, and filename. I found the naming convention to be useful, especially when working with multiple files. Using a name that gives an indication of the design code's function makes it easy to quickly identify files without having to open them.

Developing a standard naming convention can be tricky, especially when using different development tools, as they may have different filename restrictions. I have encountered tools that did not allow spaces in filenames, while another required my entity's name to be the same as the filename. So my naming convention for the entity does not include spaces and my filename is always the same as my entity. While this naming convention was based on older tool versions and those restrictions may no longer apply, I maintain this naming convention.

The input and output signals are defined as std\_logc\_vector, meaning they have multiple bits. The reserved word Downto (as used in this example) or Upto defines the range of data bits. The number before the keyword downto represents the most significant bit (MSB) and the number after it represents the least significant bit (LSB). In other words, number\_1 (3 downto 0) means number\_1 has 4 bits, where the MSB is number\_1 (3) and LSB is number 1(0).

### Lines 21–27. Architecture Section

This section contains the code that describes the design's functions. The output signal sum is assigned the result from adding together number\_1 and number\_2. While the output signals sum and difference are concurrent statements (update any time number\_1 or number\_2 changes), they could have been sequential (i.e., inside a process and updated only when a signal from the sensitivity list changes).

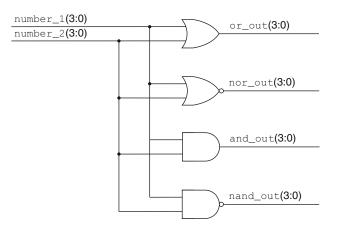

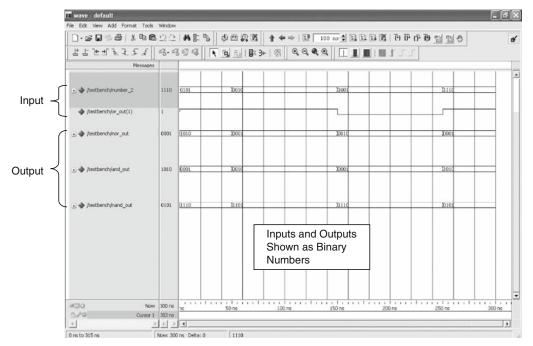

# 2.4. Logic Gate

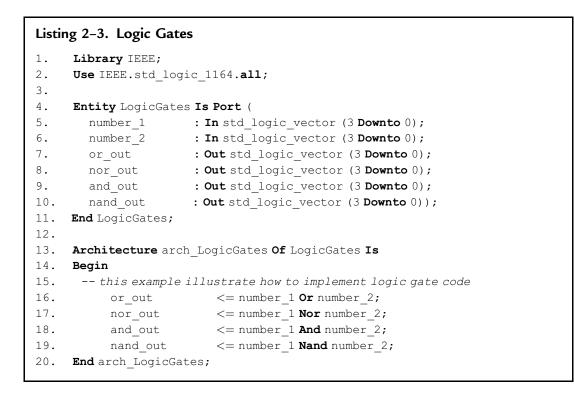

Logic gate circuits, such as OR, NOR, AND, and NAND, are implemented using the logic operators. The logic gate circuits shown in Figure 2–2 are represented by the design code shown in Listing 2–3.

### Lines 16–19. Logic Operations

The output signals are assigned the result from performing the logic operation on the right side of the statement. These signal assignments are concurrent but could have been sequential statements.

Figure 2-2: Logic Gates

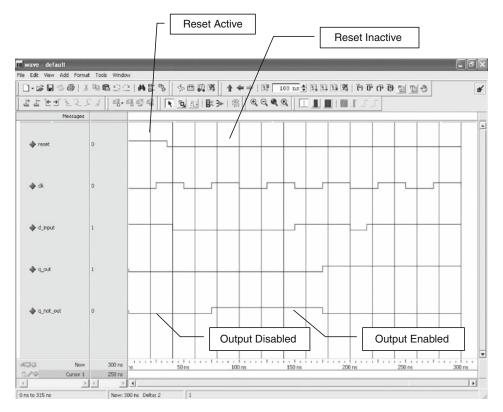

# 2.5. D Flip-Flop

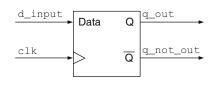

A simple D flip-flop (DFF) is shown in Figure 2–3. The VHDL design code for the DFF is shown in Listing 2–4.

Figure 2-3: DFF

```

Listing 2-4. DFF

1.

Library IEEE;

2.

Use IEEE.std logic 1164.All;

3.

4.

Entity Dff Is Port (

5.

: In std logic;

reset

6.

clk

: In std logic;

7.

d input

: In std logic;

8.

q_out

: Out std logic;

9.

: Out std logic);

q not out

10.

End Dff;

11.

12.

Architecture arch Dff Of Dff Is

13.

Begin

14.

15.

<= Not (d input);

-- inverted output of the DFF

q not out

16.

17.

dff process: Process (reset, clk)

18.

Begin

19.

If reset = '1' Then

20.

<= `0';

q out

21.

Elsif rising edge (clk) Then

2.2.

q out

<= d input; -- after the rising edge the output

gets the value of the input

23.

End If;

24.

End Process;

25.

End arch Dff;

```

### Lines 17–24. DFF Process

Remember that the code inside a process is executed sequentially and only when a signal in the sensitivity list (i.e., reset and clk) changes state. The reset signal is asynchronous, so whenever it goes active or high, the outputs of the D flip-flop immediately (minus normal internal chip delays) goes low. Under normal operating conditions, when reset is inactive or low, on the rising edge of the clock, the input data is transferred to the outputs.

#### Line 22. DFF Output

The input data of the DFF is clocked or transferred to the output on the rising edge of the input clock, clk. This is a sequential operation, which is performed inside the process named dff\_process, line 17.

#### Line 15. Inverted DFF Output

This is the inverted Q output from the DFF. The invert Q output only changes when Q changes on the rising edge of the clock.

Note: The reset signal shown on line 19 is used to set the outputs to a known or initial condition. This signal represents the power-on reset, it is not a part of the DFF, and does not appear on the symbol.

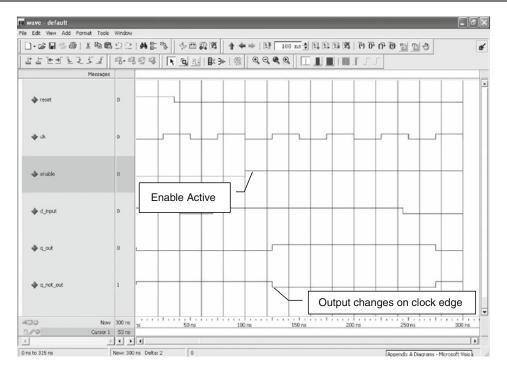

A synchronous enable can easily be added to this design by making some changes to the entity and the process in the architecture section. The entity change, shown in Listing 2–5, is the insertion of line 4. The process changes in the architecture section, shown in Listing 2–6, are lines 7 and 10.

### Listing 2-5. Synchronous Enable DFF Entity Changes

| 1. | <b>Entity</b> DffSynEa | a <b>Is Port</b> ( |

|----|------------------------|--------------------|

| 2. | reset                  | : In std_logic;    |

| 3. | clk                    | : In std_logic;    |

| 4. | enable                 | : In std_logic;    |

| 5. | d_input                | : In std_logic;    |

| 6. | q_out                  | : Out std_logic;   |

| 7. | q_not_out              | : Out std_logic);  |

| 8. | <b>End</b> DffSynEa;   |                    |

|    |                        |                    |

#### Listing 2-6. Synchronous Enable Process Changes 1. DffSynEa process: Process (clk, reset) 2. Begin 3. If reset = '1' Then 4. q out <= '0'; 5. q not out <= `1'; 6. Elsif rising edge (clk) Then 7. If enable = '1' Then -- sync enable statement q out <= d input; 8. -- after the rising edge the output gets the value of the input 9. q not out <= Not (d input); -- inverted output of the DFF 10. End If; 11. End If; 12. End Process;

### Line 4

Add input signal named enable to the entity.

### Lines 7 and 10

Add an If -Then condition following rising edge statement in the dff\_process; where enable = 1 indicates active high or enable = 0 indicates active low.

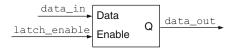

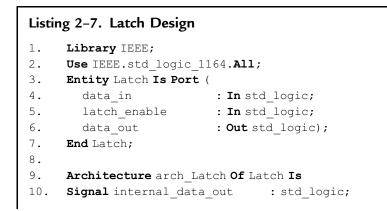

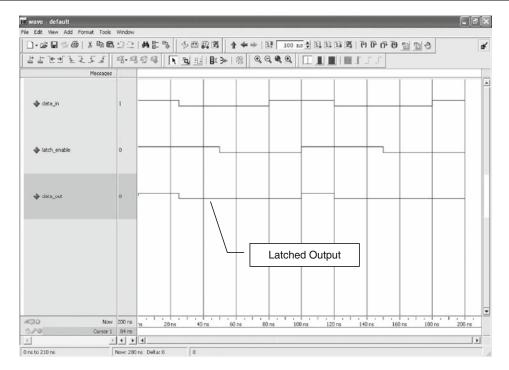

# 2.6. Latch

Sometimes you need to latch data. You can create latches by using the reserved word When. This example demonstrates only one of several uses for the reserved word When. The syntax for When is shown in Example 2–1.

The code for the latch shown in Figure 2–4 is shown in Listing 2–7.

# **Example 2–1.** When Syntax

```

<output data signal name> <= <input data signal name> When

<latch condition>

Else < output data signal name>;

```

```

11.

12.

Begin

13.

-- creating a latch signal

internal data_out

14.

<= data in When latch enable

=

11

Else internal data out;

15.

16.

data out

<= internal data out; -- output signal is

assigned internal signal value

End arch Latch;

17.

```

### Line 10. Internal Signal Created for Output Signal Data Assignment

This latch is created with a concurrent statement; therefore, it does not appear in a process. In VHDL, entity signals defined as outputs can only be assigned values and cannot be used for things like conditions or calculations. The reason this is important is because the output signal data\_out needs to be used in the concurrent statement. Since this is not allowed in VHDL, the problem is solved by creating the internal signal internal\_data\_out.

Line 14. Latch Data

The internal data out latch is created by the When statement.

### Line 16. Output Signal Assigned Value of Internal Signal

The output signal is then set equal to the internal signal. The internal signals must have the same data type and size as the output signal.

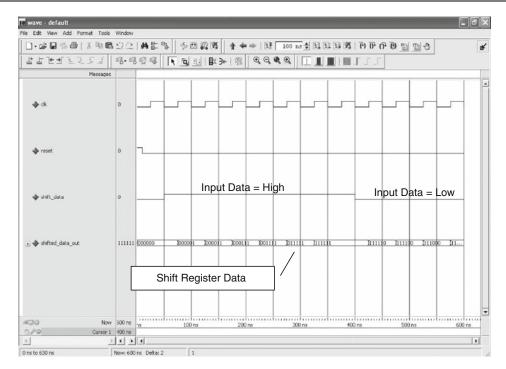

# 2.7. Shift Register

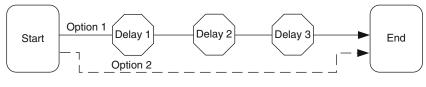

Figure 2–5 shows a simple shift register, where a single bit is shifted from the LSB to the MSB. There are a couple of ways to write the code. Option 1 requires manually writing each bit shift signal assignment, as shown in Listing 2–8.

Lines 23–28

Each bit is assigned the value of the data bit to its right.

Figure 2-5: Shift Register

```

Listing 2-8. Manual Shift Register

1.

Library IEEE;

2.

Use IEEE.std logic 1164.All;

3.

4.

Entity ShiftRegister Is Port (

5.

clk

: In std logic;

6.

reset

: In std logic; -- power-on reset

7.

shift data

: In std logic;

8.

shifted data out : Out std logic vector (5 Downto 0));

End ShiftRegister;

9.

10.

Architecture arch ShiftRegister Of ShiftRegister Is

11.

12.

Signal internal shifted data out : std logic vector (5 Downto 0);

13.

14.

Begin

15.

shifted data out <= internal shifted data out; -- output signal

is assigned internal signal value

16.

17.

left shift: Process (clk, reset)

18. Begin

19.

If reset = '1' Then

20.

internal_shifted_data_out <= ((Others => '0'));

Elsif rising_edge (clk) Then

21.

22.

-- manually creating a shift register

23.

internal_shifted_data_out(0) <= shift_data;</pre>

24.

internal shifted data out(1)

<= internal shifted

data out(0);

25.

internal shifted data out(2) <= internal shifted

data out(1);

26.

internal shifted data out(3)

<= internal shifted

data out(2);

27.

internal shifted data out(4) <= internal shifted

data out(3);

28.

internal shifted data out(5) <= internal shifted

data out(4);

29.

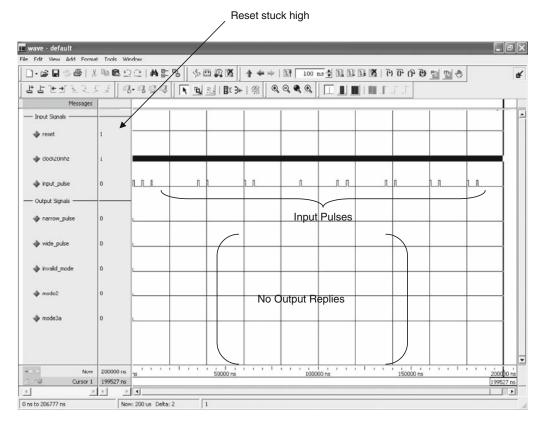

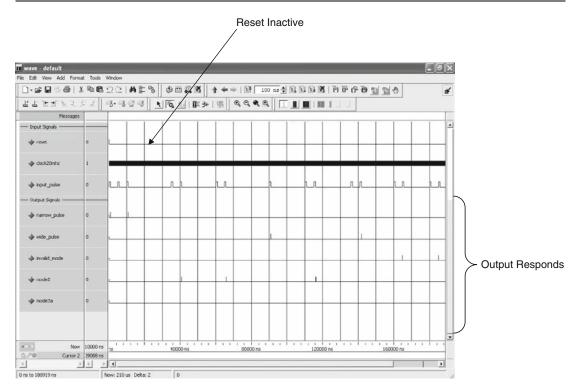

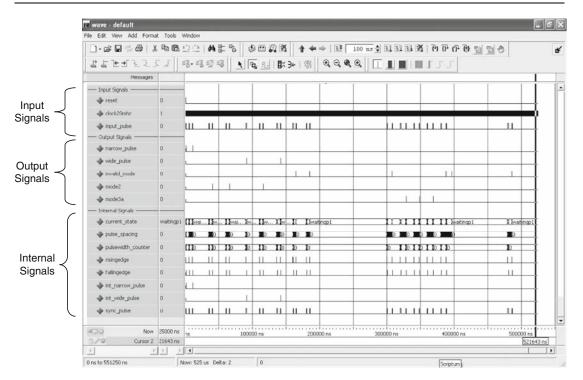

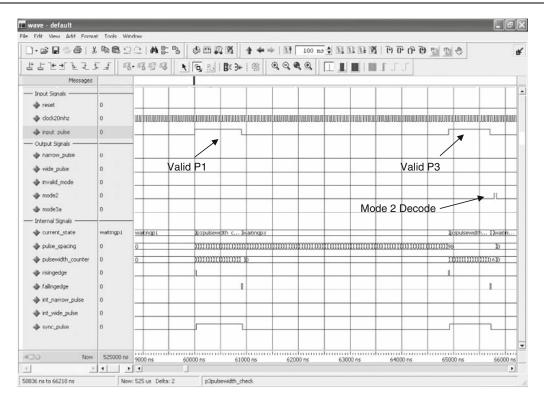

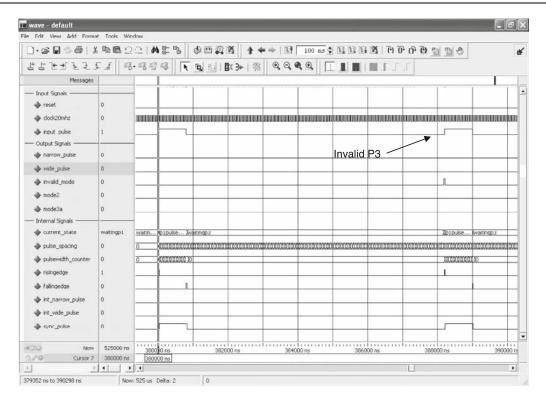

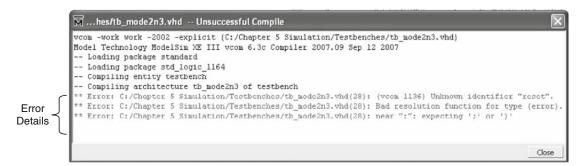

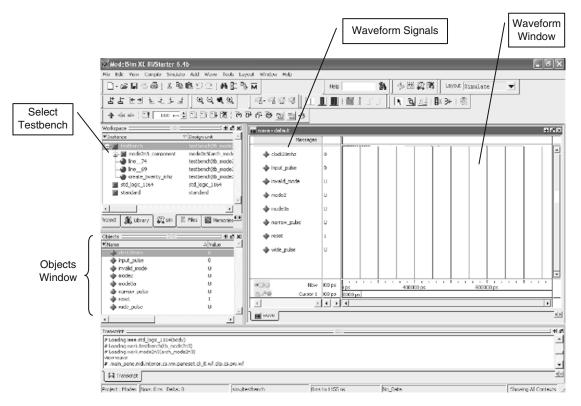

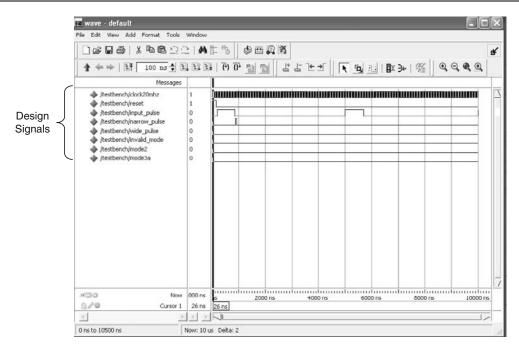

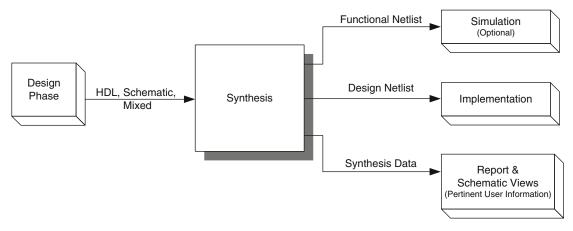

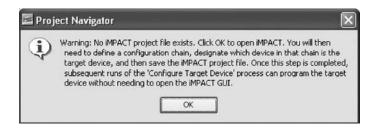

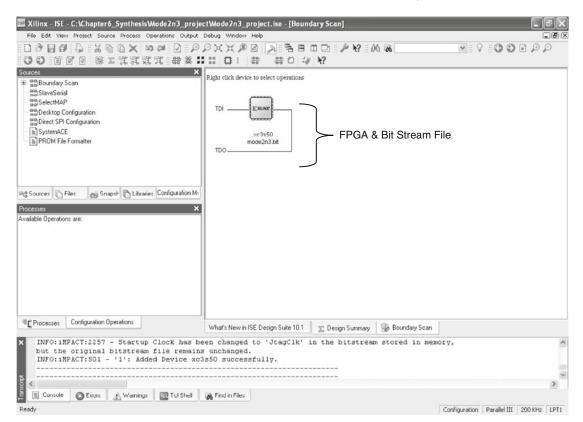

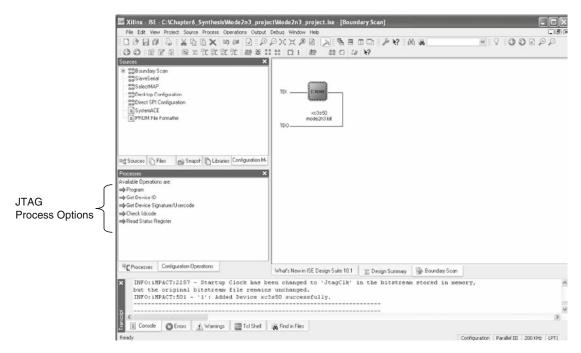

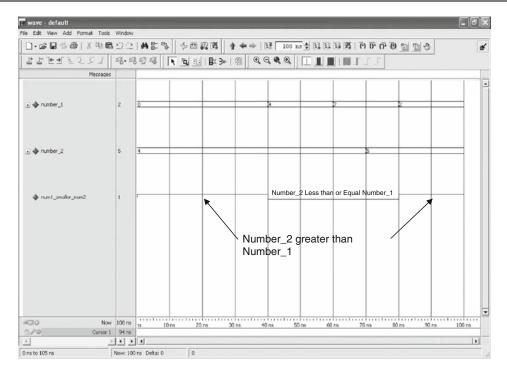

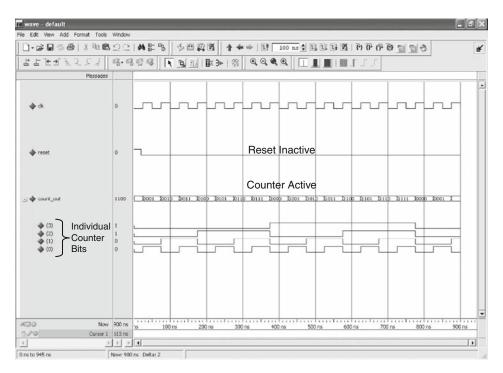

End If;