# EXPERIMENTS IN ELECTRONIC DEVICES

Third Edition

To Accompany

FLOYD'S

ELECTRONIC DEVICES

and

ELECTRONIC DEVICES:

ELECTRON FLOW VERSION

Prentice Hall Career & Technology Englewood Cliffs, New Jersey 07632 Editor: David Garza

Developmental Editor: Carol Hinklin Robison

Production Editor: Constantina Geldis

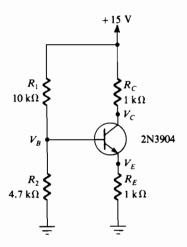

Cover Designer: Russ Maselli

Production Buyer: Patricia A. Tonneman

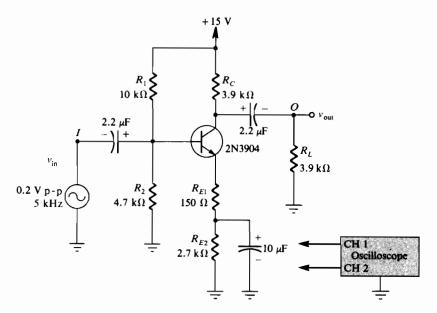

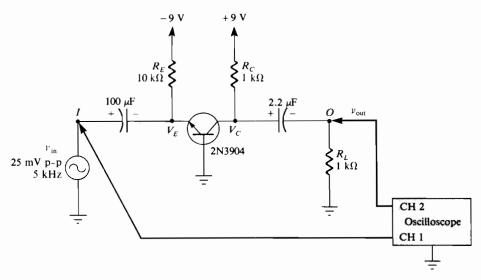

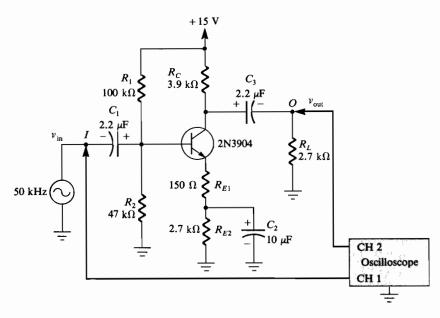

This book was set in Century Schoolbook by Publication Services and was printed and bound by R. R. Donnelley & Sons Company. The cover was printed by New England Book Components.

#### C 1988,1984 by Merrill Publishing Company

All rights reserved. No part of this book may be reproduced, in any form or by any means, without permission in writing from the publisher.

Printed in the United States of America

10 9 8 7 6 5 4

7-55480E-50-0 N8ZI

Prentice-Hall International (UK) Limited, London

Prentice-Hall of Australia Pty. Limited, Sydney

Prentice-Hall Canada Inc., Toronto

Prentice-Hall Hispanoamericana, S.A., Mexico

Prentice-Hall of India Private Limited, New Delhi

Prentice-Hall of Japan, Inc., Tokyo

Simon & Schuster Asia Pte. Ltd., Singapore

Editora Prentice-Hall do Brasil, Ltda., Rio de Janeiro

## **PREFACE**

This laboratory workbook is designed for use with the texts *Electronic Devices*, Third Edition, and *Electronic Devices: Electron Flow Version* by Thomas L. Floyd. The 43 experiments cover virtually every basic aspect of circuits containing rectifier and zener diodes; bipolar, field effect (JFET, MOSFET), and unijunction transistors; silicon-controlled rectifiers; operational amplifiers; and integrated-circuit voltage regulators, timers, and phase-locked loops.

Although the experiments are specifically referenced to the companion text, they are nevertheless general enough to be easily integrated with any other textbook on semiconductor devices at the electrical/electronics technology level. The experiments in this book reinforce and expand upon the concepts presented in the classroom. The student is able to verify these concepts by performing detailed step-by-step experiments that are easily accomplished in a typical two- to three-hour lab session. In all cases, experimental measurements can be reasonably compared to theory. Although there are 43 experiments, the student will be expected to perform only a select number of them. It is not necessary to treat all the experiments separately; some may be conveniently combined as a single major experiment. Experiments 9 through 12, for example, concentrate on the biasing of bipolar transistors and can easily be consolidated.

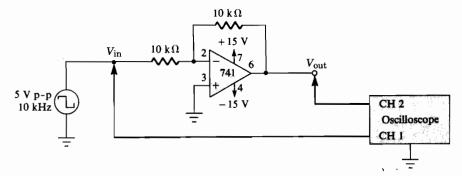

Several features enhance the utility of this workbook:

- 1. The purpose of each experiment is clearly defined. In addition, a short background summary on the operation of the circuit to be investigated is included.

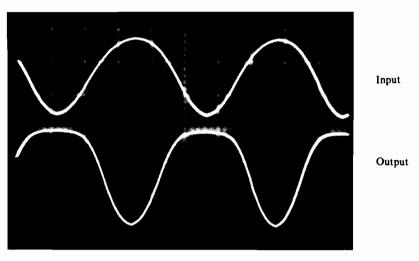

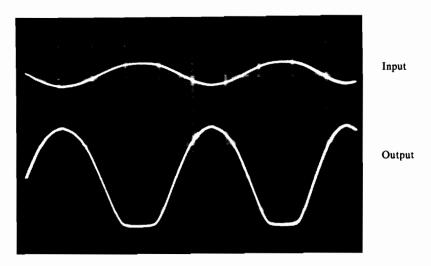

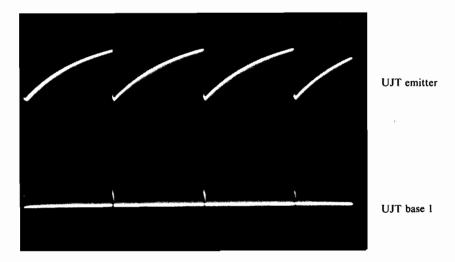

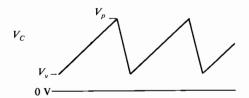

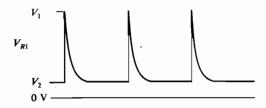

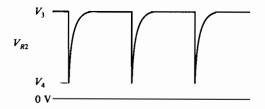

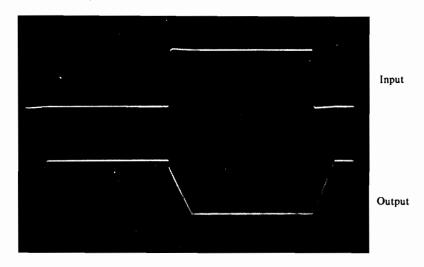

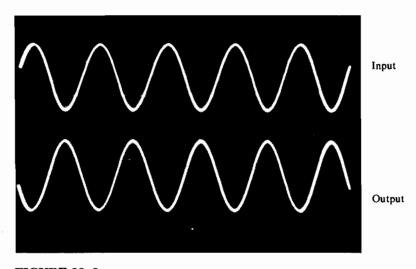

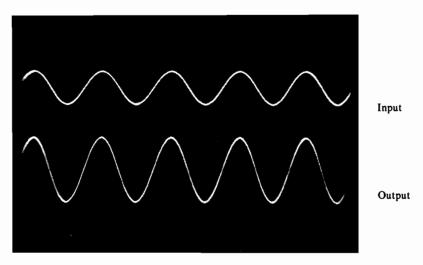

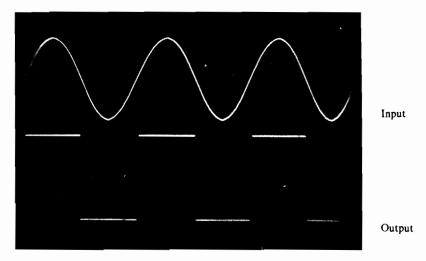

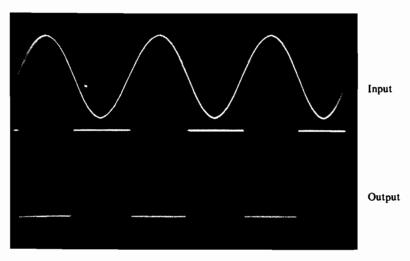

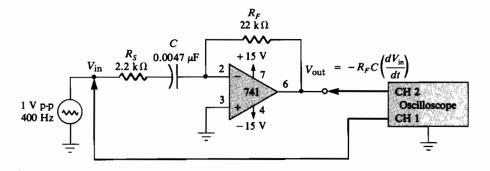

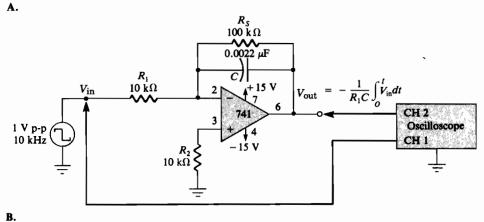

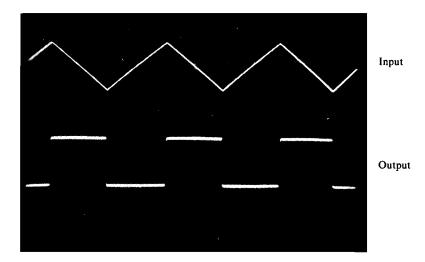

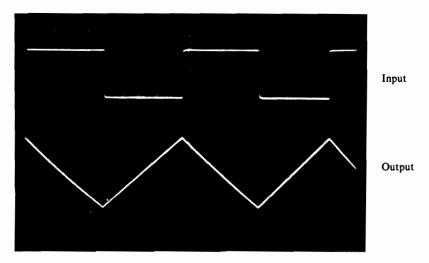

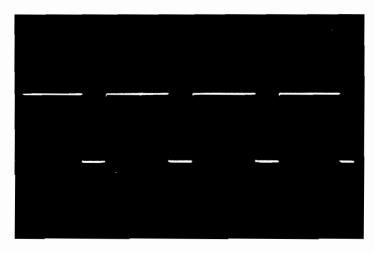

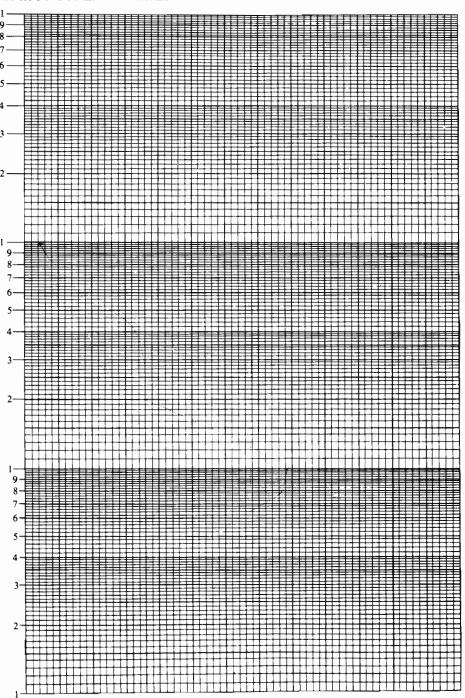

- 2. At selected portions in a number of experiments, photographs of the oscilloscope's display give students a picture of what they should observe on the screen.

- 3. For each experiment, a list of required parts and test equipment is included. All parts are low in cost and are readily obtainable from a number of sources, including Radio Shack. For convenience, a summary list of these required parts appears in the Appendix.

- 4. When appropriate, a summary of useful formulas is included to enable the student to compare measured results to theory.

- 5. A summary of "What You Have Done," presented at the end of each experiment, restates and re-emphasizes the main points of the experiment as stated in the "Purpose and Background" section of the experiment.

- 6. There are "student response" pages at the end of each experiment. These pages are for the student to enter the objectives/purpose, the schematic diagram(s), all measured data (on a blank graph page when required), and the results and conclusions of the experiment. These pages are perforated so that they, along with the optional review questions, can be easily removed to be submitted to the instructor as a complete laboratory report.

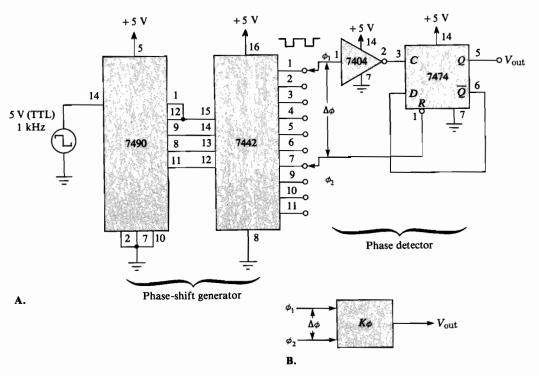

- 7. Multiple-choice review questions are included.

I would like to thank the many users of the previous two editions who have offered their helpful suggestions for improvement. I also wish to express my gratitude to the reviewers, who offered both praise and constructive suggestions: Richard Burchell, Riverside City College; Ronald Emery, Indiana University-Purdue University; Gary House, DeVry Institute of Technology—Atlanta; Maurice Nadeau, Central Minnesota Vocation-Technical Institute; Tim Staley, DeVry Institute of Technology—Dallas; Guy Tolbert, Surry Community College; Ulrich Zeisler, Utah Technical College at Salt Lake City; Steve Harsanny, Mount San Antonio College, who checked this manual for accuracy; and especially Thomas L. Floyd, the author of the text to which this book is a companion.

Howard M. Berlin

## **CONTENTS**

#### **PERFORMING THE EXPERIMENTS**

Introduction 1

Breadboarding 1

Rules for Setting Up the Experiments 2

Format for the Experiments 3

Helpful Hints and Suggestions 5

The Laboratory Report 6

#### **EXPERIMENTS**

| 1 | The Diode 11                            |    |

|---|-----------------------------------------|----|

| 2 | Diode Rectifier Circuits 23             |    |

| 3 | The Capacitor Input Rectifier Filter 33 |    |

| 4 | The Diode Limiter 41                    |    |

| 5 | The Diode Clamper 51                    |    |

| 6 | The Diode Voltage Doubler 59            |    |

| 7 | The Zener Diode and Voltage Regulation  | 67 |

|   |                                         |    |

vii

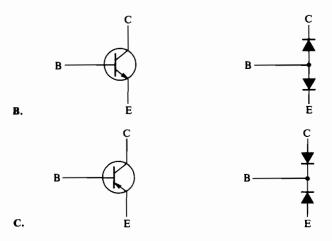

| 8          | Using an Ohmmeter to Test Transistor Diode<br>Junctions 79        |

|------------|-------------------------------------------------------------------|

| 9          | Transistor Base Biasing 89                                        |

| 10         | Transistor Emitter Biasing 97                                     |

| 11         | Transistor Voltage-Divider Biasing 105                            |

| 12         | Transistor Collector-Feedback Biasing 113                         |

| 13         | The Common-Emitter Amplifier 121                                  |

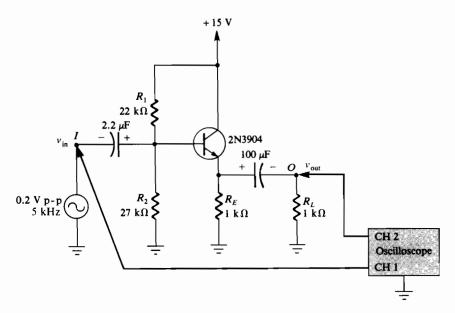

| 14         | The Common-Collector Amplifier (Emitter-Follower) 129             |

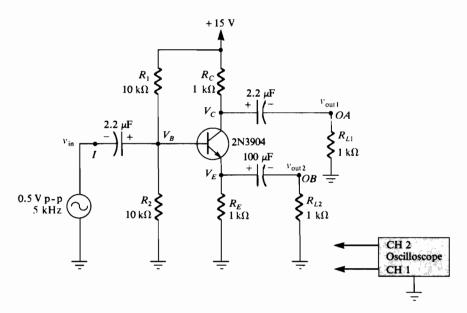

| 15         | The Combination Common-Emitter Amplifier and Emitter-Follower 137 |

| 16         | The Common-Base Amplifier 145                                     |

| 17         | The JFET Drain Curve 153                                          |

| 18         | The JFET Transfer Characteristic Curve 161                        |

| 19         | JFET Self-Bias 169                                                |

| <b>20</b>  | The Depletion-Mode MOSFET 179                                     |

| 21         | The Enhancement-Mode MOSFET 187                                   |

| 22         | VMOSFET Relay Driver 195                                          |

| 23         | The Common-Source Amplifier 203                                   |

| <b>24</b>  | The Common-Drain Amplifier (Source-Follower) 211                  |

| 25         | The Class A Common-Emitter Power Amplifier 219                    |

| 26         | The Class B Push-Pull Emitter-Follower Power Amplifier 229        |

| <b>27</b>  | Amplifier Low-Frequency Response 239                              |

| <b>2</b> 8 | The Silicon-Controlled Rectifier 249                              |

| 29         | The Unijunction Transistor 261                                    |

| 30         | Op-Amp Slew Rate 271                                              |

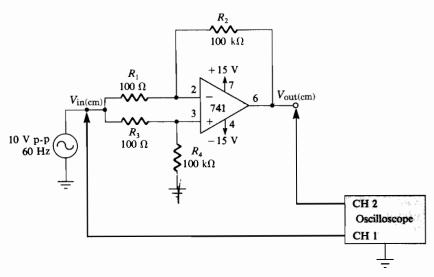

| 31         | Op-Amp Common-Mode Rejection 279                                  |

| 32         | Op-Amp Inverting and Noninverting Amplifiers 287                  |

| 33         | Op-Amp Comparators 297                                            |

| 34         | Op-Amp Differentiator and Integrator 307                          |

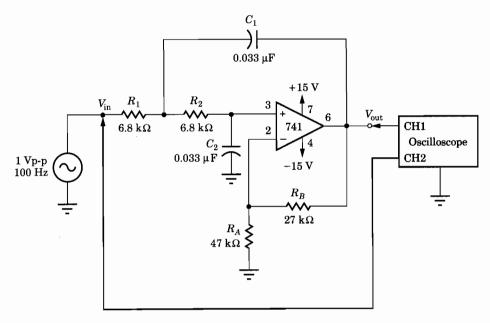

| 35         | The Phase-Shift Oscillator 317                                    |

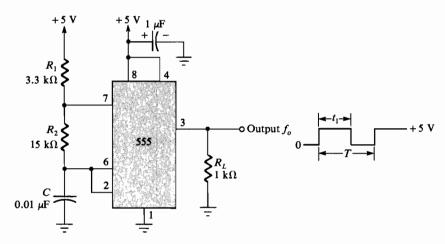

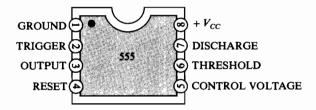

| 36         | The 555 Timer Astable Multivibrator 325                           |

| 37         | The Phase Detector 333                                            |

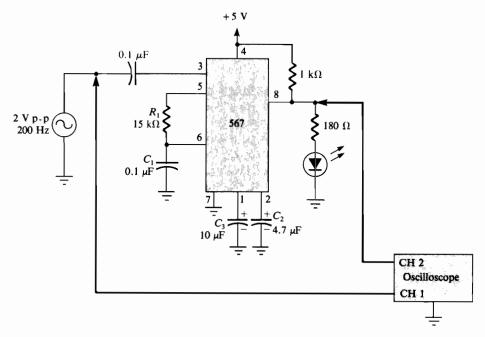

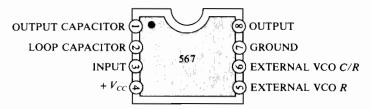

| 38         | The 567 Phase-Locked Loop Tone Decoder 343                        |

| 39         | The Butterworth 2nd-Order Low-Pass Active Filter 351              |

CONTENTS

| <b>4</b> 0 | The Butterworth 2nd-Order High-Pass    | Active Filter | 359 |

|------------|----------------------------------------|---------------|-----|

| 41         | The Active Band-Pass Filter 367        |               |     |

| <b>42</b>  | The Active Band-Stop Filter 379        |               |     |

| 43         | The Integrated-Circuit Voltage Regulat | tor 391       |     |

#### **APPENDIX**

Required Parts and Equipment for the Experiments 401

\_ \_\_\_\_

## PERFORMING THE EXPERIMENTS

#### INTRODUCTION

A laboratory experiment, although a powerful learning tool in the educational process, is a double-edged sword. In order to receive the benefits it can provide, you must follow several rules so that your experiment will be successful. This section illustrates these rules and describes how each of the 43 experiments is presented.

#### BREADBOARDING

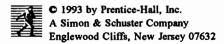

The breadboard is designed to accommodate the experiments that you will perform. The various transistors, diodes, integrated circuit devices, resistors, capacitors, and other components, as well as power and signal connections, all tie directly to the breadboard. Figure 1 shows the top view of the "solderless" breadboarding socket, which is manufactured or sold by several companies, including AP Products, Continental Specialties, and Radio Shack.

Breadboarding is an art that cannot be learned in a few minutes. Rather, it takes practice and experience to develop an efficient technique. An artist plans his creation, making sure that the picture

#### FIGURE 1

will fit on the canvas in the proper proportions without crowding, and the same is true for breadboarding electronic circuits.

When breadboarding, keep the following rules in mind:

- 1. Only no. 22, 24, or 26 insulated wire should be used, and it must be *solid*, not stranded!

- 2. Never insert too large a wire or component lead into a bread-boarding terminal.

- 3. Never insert a bent wire. Straighten out the bent end with a pair of pliers before insertion.

- **4.** Try to maintain an orderly arrangement of components and wires, keeping all connections as short as possible. Generally, the circuit is arranged on the breadboard in the same way that it appears on a schematic diagram. This rule is useful when you are trying to locate possible wiring errors.

#### **RULES FOR SETTING UP THE EXPERIMENTS**

Throughout this laboratory workbook, you will have the opportunity to breadboard a variety of circuits. Before setting up any experiment, you should do the following:

- 1. Plan your experiment. Know what types of results you are expected to observe.

- **2.** Disconnect, or turn off, *all* power and external signal sources from the breadboard.

- **3.** Clear the breadboard of all wires and components from previous experiments, unless instructed otherwise.

- 4. Check the wired-up circuit against the schematic diagram to make sure that it is correct.

- 5. Unless otherwise instructed, never make component or wiring changes on or to the breadboard with the power or external signal connections to the breadboard. This rule reduces the possibility of accidentally destroying electronic components and equipment.

- 6. When you have finished, make sure that you disconnect everything before you clear the breadboard of wires and components.

#### FORMAT FOR THE EXPERIMENTS

The instructions for each experiment are presented in the following format:

- 1. Purpose and Background. The material under this heading states the purpose of the experiment. You should have this purpose in mind as you conduct the experiment. In addition, there is a short summary about the operation and characteristics of the circuit that you will be building.

- 2. Text Reference. The corresponding section number and title in *Electronic Devices* are given here. These sections discuss the background for the experiment.

- 3. Required Parts and Equipment. A listing of the required circuit components and test equipment necessary for the experiment is given under this heading. Virtually all parts are low-cost and readily available from a variety of commercial sources, including local Radio Shack stores. (A list of the necessary components needed for all the experiments is given in the Appendix; in most cases, each component also includes Radio Shack's catalog number.)

Several pieces of equipment will be required for the experiments:

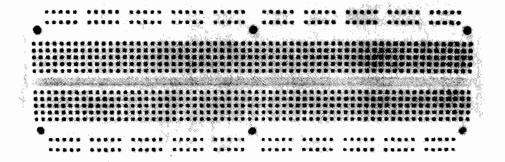

Oscilloscope. Just about any general-purpose type will do, and it should be a dual trace type. Input sensitivity generally ranges from 5 mV/division to 10 V/division and has a bandwidth from 5 MHz to 20 MHz. When needed, the schematic symbol of Figure 2 will be used.

FIGURE 2

VOM, VTVM, or DMM. A general-purpose type capable of measuring dc and ac voltages and current, as well as resistance, is necessary. If you can obtain one, use a digital type; otherwise, any VOM used should have at least a 50 k $\Omega$ /V rating so as not to introduce serious loading errors.

Adjustable dc power supply. The dc power supply should have an adjustable output voltage range from 0 V to at least 15 V, with the capability of delivering 500 mA. Some experiments will require two power supplies.

Frequency counter. It need not be an expensive one, but it should have a resolution of 1 Hz for precise measurements. There are several units available in kit form for less than \$80.

Function generator. A function generator is a signal source capable of producing selectable sine, triangle, and square waveforms of variable frequency and amplitude. Generally, they will have voltage levels from several millivolts to approximately 20 V peak-to-peak with an output impedance to 50  $\Omega$  over a frequency range from 1 Hz to 100 kHz. Also, there is usually a TTL level pulse output. When needed, the schematic symbol of Figure 3 will be used.

#### FIGURE 3

- 4. Useful Formulas. Under this heading is a summary of the equations, when applicable, that apply to the design and operation of the circuit. These formulas are presented so that you can compare measured results with theory.

- 5. Procedure. First the following diagrams are presented:

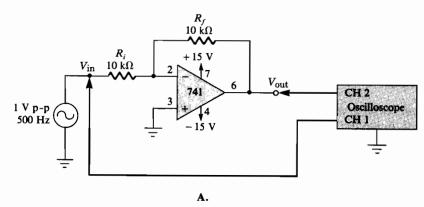

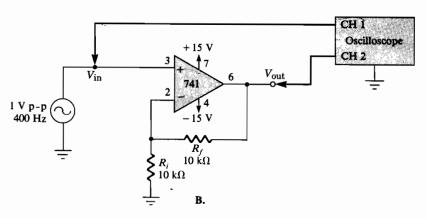

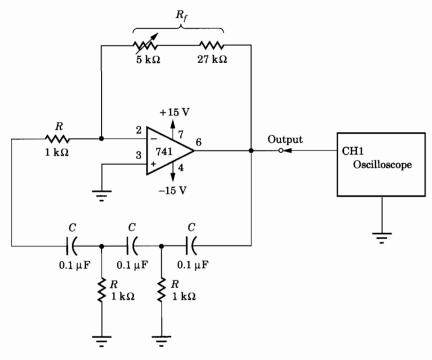

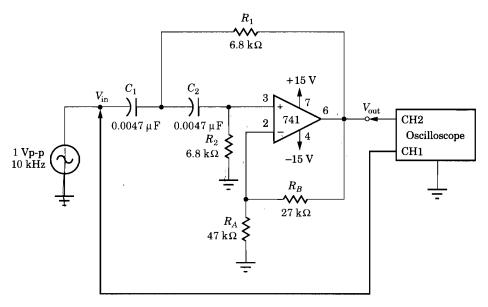

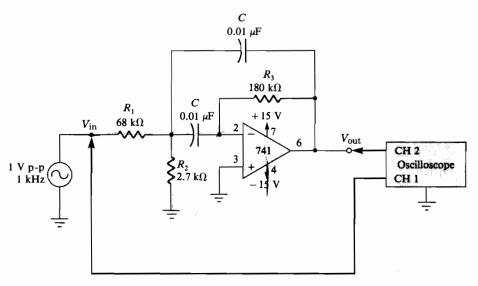

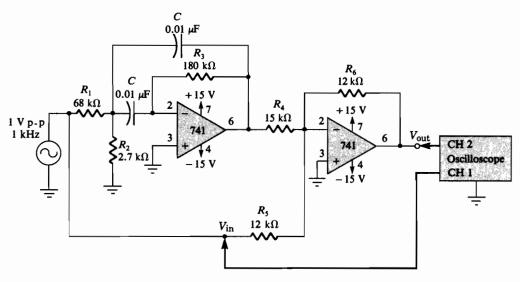

Schematic diagram of circuit. This figure shows the completed circuit that you will wire up for the experiment. You should analyze this diagram in an effort to obtain an understanding of the circuit before you proceed. When used, the oscilloscope connections to the circuit are shown with bolder lines so that they will not be confused with the normal circuit.

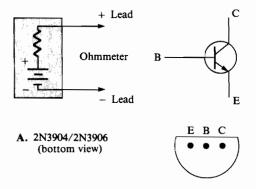

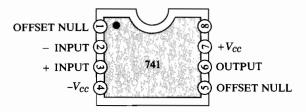

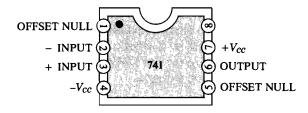

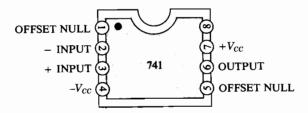

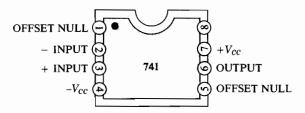

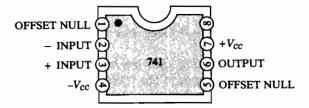

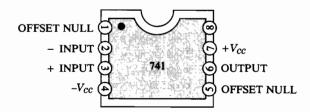

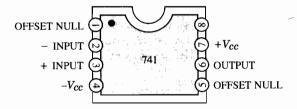

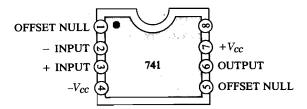

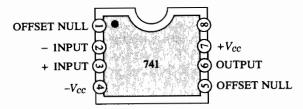

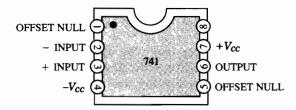

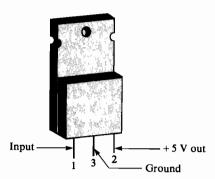

Pin configuration. These configurations are given for all transistors and integrated circuit devices used in the experiment.

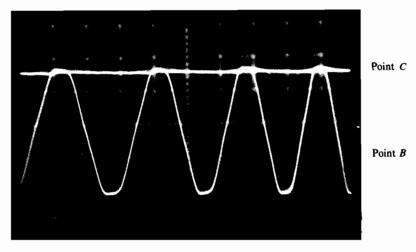

Next, a series of numbered, sequential steps gives detailed instructions for performing portions of the experiment. When appropriate, photographs of the oscilloscope's display are included so that you will be able to compare your results. In addition, questions are included at appropriate points. Any numerical calculations are performed easily on many of the pocket-type calculators.

**6.** What You Have Done. Under this heading is an explanation of the main points gained in performing the experiment.

#### **HELPFUL HINTS AND SUGGESTIONS**

Besides the necessary parts and equipment, only three small hand tools are necessary for all of the experiments given in this book:

- 1. A pair of long-nosed pliers

- 2. A wire stripper/cutter

- 3. A small screwdriver

The *pliers* are used to straighten out the bent ends of hookup wires that are used to wire the circuits on the breadboard. They are also used to straighten out or bend the resistor, capacitor, and other component leads to the proper position so that they can be conveniently inserted into the breadboard.

The wire stripper/cutter is used to cut the hookup wire to size and strip about  $\frac{3}{8}$  inch of insulation from each end.

The *screwdriver* can be used to remove the integrated-circuit devices from the solderless breadboarding socket by gently prying them loose.

In general, each experiment will ask you to compare a measured value with an expected value, that is, a value you would expect to obtain if you had not done the experiment. Generally, this value will be determined from theory. To compare your experimental result with the predicted value, calculate the *percent error*, or *percent difference*. The formula for determining the percent error is

$$\% \text{ error} = \frac{\text{measured value} - \text{true value}}{\text{true value}} \times 100\%$$

For example, if you measure a voltage of 5.36 V and you expect the value (from theory) to be 4.97 V, the percent error is

$$\% \text{ error} = \frac{5.36 - 4.97}{4.97} \times 100\% = 7.8\%$$

The most common sources of error are the tolerance of component values and the loading effects of meters. The measured result is generally acceptable if the percent error is within 10%.

#### THE LABORATORY REPORT

As with any laboratory-oriented course, there is usually more to the laboratory exercise than merely performing the experiment. Performing the laboratory experiment should be followed by writing what was done in a technical report. As an educational exercise, writing the report serves two major purposes. First, a written report documents what took place in the laboratory and gives the instructor an indication of how well the student has understood the principles and concepts that were supposed to be demonstrated by a particular experiment. Second, writing a technically oriented report provides the student with the practice of developing the communications skills that will be useful in his or her professional career. It is my experience that many students, even in standard courses in English composition, receive little or no instruction in writing technical material about their particular area of study.

Many instructors or departments may have their own guidelines and rules concerning the format of the laboratory report. Following is a brief discussion of the guidelines used in the Electrical and Electronics Technology program here at Delaware Technical and Community College, Stanton Campus.

The completed laboratory report may be either neatly hand-written in *ink* (black or blue) or typewritten. The point here is that neatness and legibility are important. If the instructor cannot read a sloppily written or typed report, then the effort and time taken in its preparation has been wasted. In our courses, ample time (usually one week) is given from the date the experiment was performed until the report is due. A report should contain the following elements:

- 1. Title. The title of the experiment at the beginning of the report should be a descriptive phrase that identifies the experiment. As an example, "The Common-Emitter Amplifier" is more descriptive than "Experiment 4" because it may not be apparent what the substance of Experiment 4 actually is. In addition, the name of the person submitting the report should be included, along with the names of other laboratory partners. Finally, the date the experiment was performed must be included.

- 2. Purpose or Objective. The particular experiment is to be performed for some definite reason. A brief statement (one to three sentences) that explains why the experiment is being performed is included.

- 3. Wiring (Schematic) Diagram. A schematic diagram of the circuit(s) used in the experiment must be included. The diagram must be neatly drawn and properly labeled with all

component values used. The use of templates to draw electronic symbols is not mandatory, and the symbols can be drawn freehand. However, all connecting lines must be drawn with a straightedge.

- 4. Equipment and Special Supplies. The serial number and model number of the equipment used in the experiment should be recorded. In some cases, the student may be asked to repeat the experiment to show why unusual results have been obtained. In practice, faulty results may be obtained because of a faulty meter or other equipment, a fact the student can prove only if the exact instrument is used in the repeated experiment.

- 5. Procedure. This contains short comments in chronological order about the measurements, instruments used, and any special techniques used. Such comments are usually sufficient to explain what was done during the experiment. Long explanations are generally not necessary and usually not desirable. The comments nevertheless should be complete enough to allow another person to perform the experiment for verification.

- 6. Data Tables. In almost all experiments, a number of measured values should be recorded in ink. Charts are the most convenient method of recording these data, since all values are readily available for analysis. The data sheet on the perforated page at the end of each experiment in this laboratory workbook serves as the format for the data table.

The student should also understand that all erasures and changes in data are observed by others with great suspicion. Recording errors should not be erased. They should be indicated as errors by drawing a *single* line through the incorrect data and writing the correct value beside it. Many industrial firms also require that the employee initial the change along with the date. Indicating the error by the single-line method retains the original measurement for future analysis if it should be found to be important. In some experiments, the possible error is the only interesting part of the experiment, and the measurement would be completely lost if it were erased, scratched out, or otherwise defaced.

- 7. Calculations. All experiments require a certain number of calculations before final results are obtained. Sample calculations that are completely identified should be included. It is not necessary to show repeated calculations.

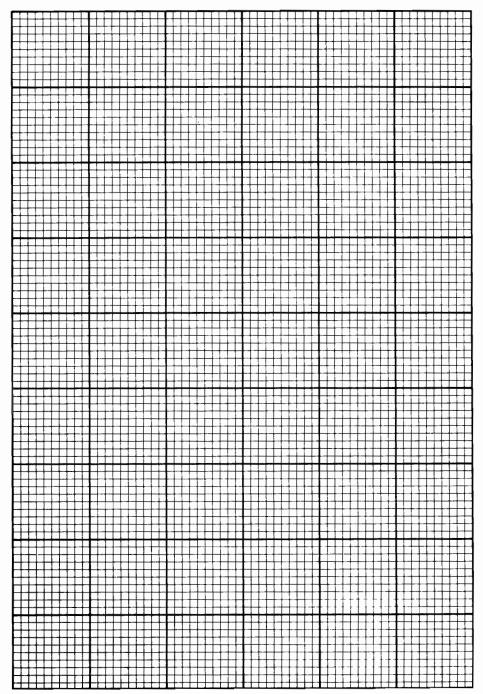

- 8. Graphs. Data that have been recorded in long columns on charts cannot be analyzed quickly, but the graph provides a visual, or pictorial, presentation of the data. The graph can be used to determine trends and unusual results, such as a data point that is probably in error.

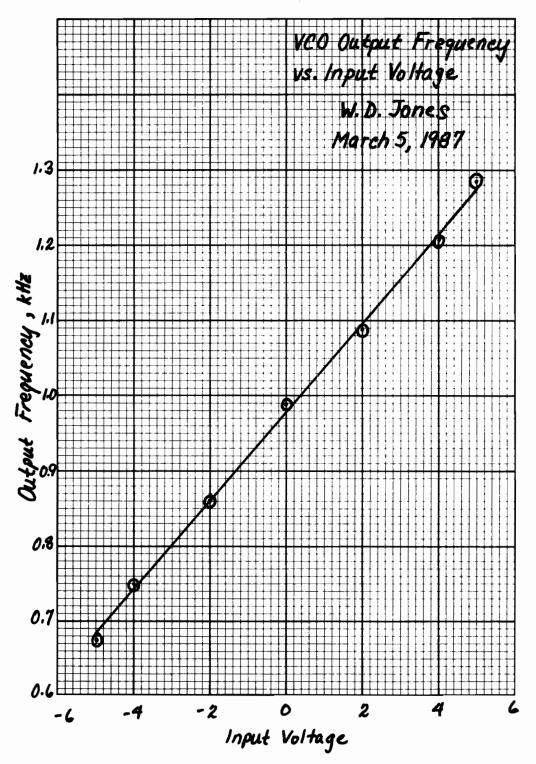

FIGURE 4 Sample hand-drawn graph.

- The guidelines in constructing a graph are very simple:

- Always label the axes. Generally, one parameter is plotted as another parameter is varied. The dependent variable is represented on the vertical axis, and the independent variable on the horizontal axis. If, for example, the gain of the amplifier is measured as the input frequency is changed, the amplifier gain is the dependent variable because its value depends on the value of the input frequency.

- All graphs should include a title, name of the preparer, and the date the graph was made. At some later time, this basic information pins down what the graph depicts, who did it, and when it was done.

- If various conditions plotted on the same graph result in more than one curve or line, the data points from one set of data should be easily distinguishable from data points belonging to a different set. Data points are frequently marked using a dot surrounded by a small circle, or Δ, +, ×,\* symbols.

- The data points should be connected smoothly with the best-fit straight line between all points, or with a "French curve" to construct a smooth curve between points. Figure 4 shows an example of a completed hand-drawn graph of the measured output frequency of an oscillator as the input voltage is varied.

- 9. Results and Conclusions. The results and conclusions are probably the most important part of the experiment. The entire experiment is considered a failure if the student does not understand the results and cannot decide how to express the conclusion. Many instructors read this part of the report first and then refer to the first eight items for supporting information. The conclusion should be as brief as possible (less than one written page). Long conclusions often tend to bury the actual results of the experiment and instead become a procedure sheet. One statement that should be avoided is "Everything went well, as expected."

- 10. Answers to Review Questions (optional). At the end of each experiment in the workbook are several multiple-choice questions. Some instructors may want to have the student include the answers to these questions as part of the laboratory report.

1

## THE DIODE

#### **PURPOSE AND BACKGROUND**

The purpose of this experiment is to examine characteristics of a silicon diode. When the diode's anode is at a higher potential than is the cathode, the diode is *forward biased*. For **conventional current flow**, current will flow through the diode from anode to cathode. For **electron flow**, current will flow from cathode to anode. Unlike a resistor, in which the current is directly (that is, linearly) proportional to the voltage across it, the diode is a *nonlinear* device. When the diode is forward biased, a small but measurable voltage drop, called the *barrier potential*, occurs across the diode. For germanium diodes, this value is typically 0.3 V; for silicon diodes, it is approximately 0.7 V.

REQUIRED PARTS AND EQUIPMENT

Text Reference: 2-1, Rectifier Diodes.

| Resistors (1/4 W):                                         | ☐ 0–15 V dc power supply  |

|------------------------------------------------------------|---------------------------|

| $\square$ 10 $\Omega$                                      | ☐ Signal generator        |

| □ 100 Ω                                                    | ☐ Dual trace oscilloscope |

| □ 1 kΩ                                                     | □ VOM                     |

| ☐ 1N914 (1N4148 or equivalent) silicon, small-signal diode | ☐ Breadboarding socket    |

|                                                            |                           |

#### **USEFUL FORMULA**

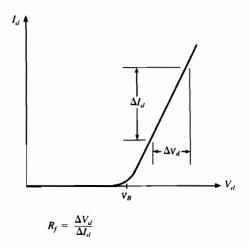

FIGURE 1-1 Graphic determination of diode forward resistance.

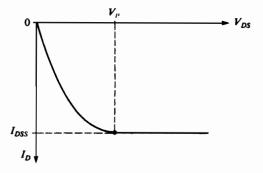

The determination of  $R_f$ , the diode forward resistance, is shown graphically in Figure 1–1.

$$R_f = \frac{\Delta V_d}{\Delta I_d}$$

#### **PROCEDURE**

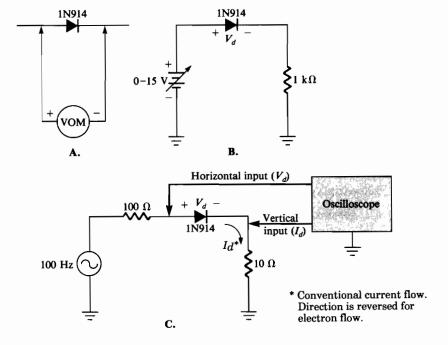

1. Very often one can use a VOM to check quickly whether a diode is good or bad. Unless they have a specific function for this purpose, most DMMs are not able to perform this test properly. Using your VOM as an ohmmeter, first select a low-resistance meter range, such as the "R × 100" range. Then connect the positive lead of the VOM to the diode's anode terminal while the negative lead is connected to the diode's cathode terminal, as shown in Figure 1-2A. (Most diodes have a single colored band, several bands, the diode symbol, or the letter "K" at one end to indicate the cathode terminal.) The VOM's internal battery then forward biases the diode. Note the resistance reading.

If a DMM with a "diode check" feature is used, the display usually indicates the voltage drop across a good diode from anode to cathode when it is forward biased. When reverse biased, the DMM generally indicates some form of out-of-range condition, such as a blinking display or the letters "OL."

FIGURE 1-2 Schematic diagram of circuits.

2. Now reverse the VOM's leads so that the meter's positive terminal is connected to the cathode terminal of the diode, which is now reverse biased. Note the resistance reading.

The reading you have just obtained should be much higher (typically several hundred thousand ohms) compared to the resistance reading of Step 1, which is typically a few hundred ohms or less. Consequently, the diode exhibits a low forward resistance while having a high, or nearly infinite, reverse resistance. The actual resistance readings obtained are not as important as their relationship to each other. If both readings indicate virtually the same low resistance, then the diode is shorted; if a very high resistance is obtained in both directions, the diode is open.

When measuring resistances, some VOMs have the polarity of their leads reversed from the normal sense. That is, the positive lead is actually wired to the internal battery's negative terminal. In this case, the forward and reverse resistance readings will be the opposite of those indicated in these two steps. When it functions as a voltmeter or an ammeter, this type of VOM has its leads internally connected in the normal sense.

3. Wire the circuit shown in Figure 1–2B. Adjust the dc power supply to give the voltages across the 1-k $\Omega$  resistor shown in

- Table 1–1. For each voltage, measure and record the dc voltage drop  $(V_d)$  across the diode. The diode current is also the current flowing through the 1-k $\Omega$  resistor. Determine the diode current by using Ohm's law in each case.

- 4. Plot the resulting diode curve (diode current versus voltage) on the graph page in this experiment. Graphically determine the diode's barrier potential  $(V_B)$  and forward resistance  $(R_F)$ , recording your results in Table 1–2.

- 5. Disconnect the power from the breadboard and wire the circuit shown in Figure 1-2C. In this part, the oscilloscope is set up to function as an X-Y plotter. Set the oscilloscope controls to the following approximate settings:

$\begin{array}{c} \text{Vertical (or Y) input sensitivity: 10 mV/division,} \\ \text{dc coupling} \end{array}$

Horizontal (or X) input sensitivity: 1 V/division, dc coupling

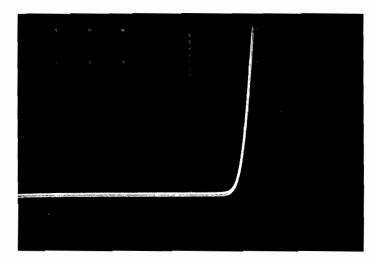

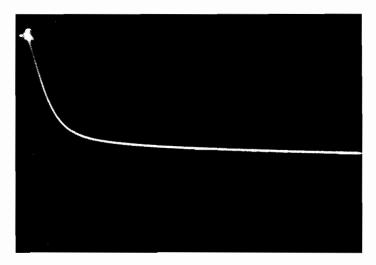

6. After the oscilloscope has warmed up, center the trace dot at the center of the scope's screen. Adjust the sine wave frequency of the signal generator to approximately 100 Hz, and vary the generator's output level so that you observe the characteristic diode curve similar to the one plotted in Step 4. The oscilloscope display should be similar to that shown in Figure 1-3. If it is not, the leads of the oscilloscope may be interchanged or there may be wiring error.

The horizontal input measures the voltage across the diode  $(V_d)$ , neglecting the small voltage drop across the 10- $\Omega$  resistor. The vertical input measures the voltage drop across the 10- $\Omega$

FIGURE 1-3

resistor. By Ohm's law, the vertical input can be made to show the diode current  $(I_d)$ . If the vertical sensitivity is 10 mV/division, then in terms of the current through the 10- $\Omega$  resistor, which is the same as the diode current,

Vertical sensitivity =

$$\frac{10 \text{ mV/division}}{10 \Omega}$$

= 1 mA/division

7. As in Step 4, from the oscilloscope's display graphically determine the diode's barrier potential and forward resistance, recording your results in Table 1–2. How does this compare with Step 4 for the same diode?

#### WHAT YOU HAVE DONE

This experiment examined the characteristics of a silicon diode. You learned how to properly test a diode using a VOM or DMM, and how to determine the diode's barrier potential and forward resistance. By graphing the diode's forward characteristic, you observed that the diode is a nonlinear device.

## NOTES

16

| Name                  | Date |

|-----------------------|------|

| THE DIODE             |      |

|                       |      |

| OR IECTIVES/DIIDDOSE: |      |

#### **SCHEMATIC DIAGRAM:**

| Name Da | te |

|---------|----|

|---------|----|

#### **DATA FOR EXPERIMENT 1**

TABLE 1-1

| Voltage across<br>1-kΩ Resistor | Diode<br>Voltage | Diode Forward<br>Current |

|---------------------------------|------------------|--------------------------|

| 0.1 V                           |                  |                          |

| 0.2 V                           |                  |                          |

| 0.3 V                           | _                |                          |

| 0.4 V                           |                  |                          |

| 0.5 V                           |                  |                          |

| 0.6 V                           |                  |                          |

| 0.7 V                           |                  |                          |

| 0.8 V                           |                  |                          |

| 0.9 V                           |                  |                          |

| 1 V                             |                  |                          |

| 2 V                             |                  |                          |

| 3 V                             |                  |                          |

| 4 V                             |                  |                          |

| 5 V                             |                  |                          |

| 6 V                             |                  |                          |

| 7 V                             |                  |                          |

| 8 V                             |                  |                          |

| 9 V                             |                  |                          |

| 10 V                            |                  |                          |

| Name Date |

|-----------|

|-----------|

TABLE 1-2

| Parameter                       | Step 4 | Step 7 |

|---------------------------------|--------|--------|

| Diode barrier potential, $V_B$  |        |        |

| Diode forward resistance, $R_F$ |        |        |

## NOTES

| Name | Date |

|------|------|

|      |      |

#### **DATA FOR EXPERIMENT 1**

| Name  | Date    |

|-------|---------|

| valle | <b></b> |

#### **RESULTS AND CONCLUSIONS:**

#### **REVIEW QUESTIONS FOR EXPERIMENT 1**

| 1. | When an ohmmeter is used to test a diode, as in Figure 1–2A, a very low resistance (but not zero) in one direction means that        |          |      |  |  |

|----|--------------------------------------------------------------------------------------------------------------------------------------|----------|------|--|--|

|    | the diode is (a) open (b) shorted                                                                                                    |          |      |  |  |

|    | (c) forward biased (d) reverse biased                                                                                                | (        | )    |  |  |

| 2. | In this experiment, the measured diode barrier potential is approximately                                                            |          | ,    |  |  |

|    | (a) 0.3 V (b) 0.6 V (c) 0.9 V (d) 1.2 V                                                                                              | (        | )    |  |  |

| 3. |                                                                                                                                      | `        | ŕ    |  |  |

|    | (a) 0.5 mA/division (b) 5 mA/division                                                                                                |          |      |  |  |

|    | (c) 50 mA/division (d) 0.5 A/division                                                                                                | (        | )    |  |  |

| 4. | For which region of your experimental diode curve does the diode look like an open circuit?                                          |          | ,    |  |  |

|    | (a) Diode voltages less than the barrier potential                                                                                   |          |      |  |  |

|    |                                                                                                                                      |          |      |  |  |

| 5. | (b) Diode voltages greater than the barrier potential  For the region of the diode curve greater than the diode's barrier potential, | (        | )    |  |  |

|    | (a) the curve is essentially horizontal                                                                                              |          |      |  |  |

|    | (b) the diode forward resistance approaches an open circuit                                                                          |          |      |  |  |

|    | (c) the diode voltage increases rapidly                                                                                              |          |      |  |  |

|    | (d) the diode current increases rapidly                                                                                              | (        | )    |  |  |

| 22 | ©1992 Macmillan Publishing Company. All rights                                                                                       | s reserv | /ed. |  |  |

## DIODE RECTIFIER CIRCUITS

#### **PURPOSE AND BACKGROUND**

The purpose of this experiment is to demonstrate the characteristics of three different diode rectifier circuits: half-wave rectifier, center-tapped full-wave rectifier, and full-wave bridge rectifier. Each type causes an ac input voltage to be converted into a pulsed waveform having an average, or dc, voltage output.

*Text References:* 2–2, Half-Wave Rectifiers; 2–3, Full-Wave Rectifiers.

#### REQUIRED PARTS AND EQUIPMENT

| $1-k\Omega$ resistor, $1/2$ W | ☐ Dual trace oscilloscope |

|-------------------------------|---------------------------|

| Four 1N4001 silicon           | ☐ VOM or DMM              |

| rectifier diodes              | ☐ Breadboarding socket    |

| 12.6-V rms secondary          | _                         |

| center-tapped transformer     |                           |

#### **USEFUL FORMULAS**

Half-wave rectifier

- (1) dc voltage output =  $\frac{V_S V_B}{\pi}$  (sine wave input)

- (2) Diode PIV =  $V_p$

- (3) Output frequency = input frequency

Center-tapped full-wave rectifier

- (4) dc voltage output =  $\frac{2V_S V_B}{\pi}$  (sine wave input)

- (5) Diode PIV  $-2V_p$

- (6) Output frequency =  $2 \times \text{input frequency}$

Full-wave bridge rectifier

- (7) dc voltage output =  $\frac{2(V_S V_B)}{\pi}$  (sine wave input)

- (8) Diode PIV =  $V_p$

- (9) Output frequency =  $2 \times \text{input frequency}$

#### **PROCEDURE**

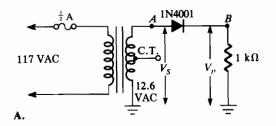

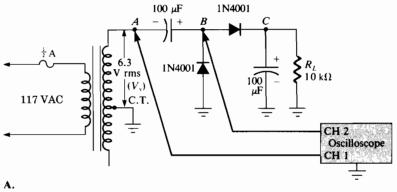

- 1. Wire the half-wave rectifier circuit shown in Figure 2–1A, paying careful attention to the polarity of the 1N4001 diode. You should be very careful to be sure that your connections to the 117-V primary of the transformer are properly protected so that you will not get a shock by accidentally touching them. Furthermore, you should have a 1/2-A fuse on the primary side of the transformer. Note that neither of the transformer's primary leads is grounded, while the center-tapped secondary lead is not used in this section!

- 2. Set your oscilloscope to the following approximate settings:

Channels 1 and 2: 10 V/division, dc coupling

Time base: 5 ms/division

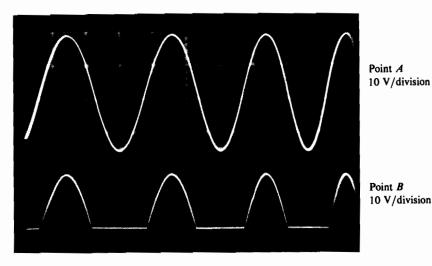

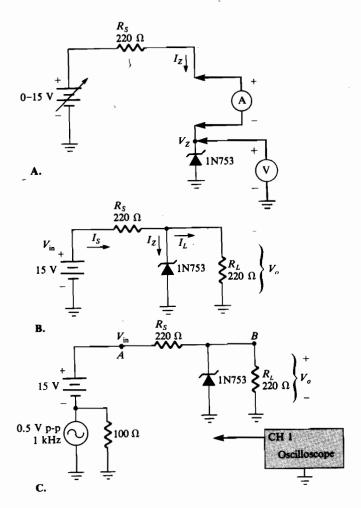

Apply 117 VAC (rms) to the transformer's primary leads. Connect one scope probe to the anode terminal of the 1N4001 diode (point A), and the other probe to the diode's cathode terminal (point B). If everything is working properly, you should obtain the waveforms shown in Figure 2–2.

3. Measure the transformer's peak secondary voltage  $(V_S)$ , as well as the peak voltage  $(V_p)$  across the 1-k $\Omega$  resistor, recording your results in Table 2–1. Are the two readings the same?

FIGURE 2-1 Schematic diagram of circuits.

You should find that these two readings differ slightly. The voltage difference is the barrier potential of the diode  $(V_B)$ , which is approximately 0.7 V for silicon diodes. When the peak voltage is at least ten times larger than this diode voltage drop, the barrier potential usually can be safely neglected, so that these two readings can be considered essentially the same.

4. With your VOM or DMM, measure the dc voltage  $(V_{DC})$  across the 1-k $\Omega$  resistor, and record your result in Table 2–1. Compare this result with that obtained from the equation for the average or dc voltage of a half-wave rectifier (Equation 1).

Observe both waveforms. Notice that the frequency of the rectified output sine wave is the same as that of the input sine wave, even though half of each cycle of the output is zero. Why?

5. Turn off the power to the transformer, and wire the centertapped full-wave rectifier circuit shown in Figure 2-1B. Again, pay careful attention to the polarity of both diodes and the

FIGURE 2-2 Time base: 5 ms/division.

connections to the 117-V primary of the transformer. The center-tapped lead is grounded for this section.

6. Now set your oscilloscope to the following approximate settings:

Channels 1 and 2: 5 V/division, dc coupling Time base: 5 ms/division

Apply 117 VAC (rms) to the transformer's primary leads. Connect one probe to the anode terminal of the 1N4001 diode (point A), and the other probe to one of the diode's cathode terminals (point B). If everything is working properly, you should obtain the waveforms as shown in Figure 2–3.

7. Measure the transformer's peak secondary voltage  $(V_S)$  with respect to the grounded center tap, as well as the peak voltage  $(V_p)$  across the 1-k $\Omega$  resistor, recording your results in Table 2-1. How do these readings compare with those of Step 3?

The peak secondary voltage should be half that of Step 3.

8. With your VOM or DMM, measure the dc voltage  $(V_{DC})$  across the 1-k $\Omega$  resistor, and record your result in Table 2–1. Compare this result with that obtained from the equation for the average or dc voltage of a center-tapped full-wave rectifier (Equation 4).

Observe both waveforms. Notice that the frequency of the rectified output sine wave is now twice that of the input sine wave. Why?

9. Turn off the power to the transformer, and wire the full-wave bridge rectifier circuit shown in Figure 2–1C. Pay careful attention to the polarity of all four diodes and the connections to the 117-V primary of the transformer. The center-tapped lead is not used for this section. Remove the oscilloscope probe from the anode of the diode.

Point A

5 V/division

Point B 5 V/division

FIGURE 2-3 Time base: 5 ms/division.

- 10. Apply 117 VAC (rms) to the transformer's primary leads. With the channel set to dc coupling, connect only the probe to the ungrounded lead of the 1-k $\Omega$  resistor (point A). If everything is working properly, you should obtain the same full-wave rectified waveform obtained in Step 6.

- 11. Measure the peak voltage  $(V_p)$  across the 1-k $\Omega$  resistor, recording your result in Table 2–1. How does this reading for  $V_p$  compare with those of Steps 3 and 7?

The peak secondary voltage should be the same as that of Step 3 and *twice* that of Step 7. In addition, you should find that the peak voltage across the  $1-k\Omega$  resistor is smaller than the secondary voltage by twice the barrier potential. Why?

12. With your VOM or DMM, measure the dc voltage  $(V_{DC})$  across the 1-k $\Omega$  resistor, and record your result in Table 2–1. Compare this result with that obtained from the equation for the average or dc voltage of a full-wave bridge rectifier (Equation 7).

Observe both waveforms. Notice that the frequency of the rectified output sine wave is twice that of the input sine wave. Why?

#### WHAT YOU HAVE DONE

This experiment compared the output characteristics of three types of rectifier circuits: half-wave rectifier, full-wave rectifier using a center-tapped transformer secondary, and a full-wave bridge rectifier. Each converts an ac voltage into a pulsed waveform having an average or dc voltage output.

28

| Name                     | Date |

|--------------------------|------|

| DIODE RECTIFIER CIRCUITS |      |

|                          |      |

| OBJECTIVES/PURPOSE:      |      |

## **SCHEMATIC DIAGRAM:**

29

## **DATA FOR EXPERIMENT 2**

**TABLE 2-1**

| Measured<br>Parameter | Half-Wave<br>Rectifier | Center-Tapped<br>Full-Wave<br>Rectifier | Bridge<br>Full-Wave<br>Rectifier                |

|-----------------------|------------------------|-----------------------------------------|-------------------------------------------------|

| $V_S$                 |                        |                                         | Same as<br>center-tapped<br>full-wave rectifier |

| $V_p$                 |                        |                                         |                                                 |

| $V_{ m DC}$           |                        |                                         |                                                 |

| Name | Date |

|------|------|

|------|------|

## **RESULTS AND CONCLUSIONS:**

## **REVIEW QUESTIONS FOR EXPERIMENT 2**

| 1.           | For the half-wave rectifier circuit of Figure 2–1A, the peak load                        |   |            |

|--------------|------------------------------------------------------------------------------------------|---|------------|

|              | voltage is approximately                                                                 |   |            |

|              | (a) 6 V (b) 12 V (c) 18 V (d) 24 V                                                       | ( | )          |

| 2.           | For an input frequency of 60 Hz, the period of the half-wave                             |   |            |

|              | signal is approximately                                                                  |   |            |

|              | (a) 4 ms (b) 8 ms (c) 16 ms (d) 32 ms                                                    | ( | )          |

| 3.           | Compared to the dc output voltage of the half-wave rectifier                             |   |            |

|              | of Figure 2-1A, the dc output voltage of the full-wave bridge                            |   |            |

|              | rectifier of Figure 2–1C is approximately                                                |   |            |

|              | (a) one-half as large (b) the same (c) twice as large                                    | ( | )          |

| 4.           |                                                                                          | ( | ,          |

| <b>±.</b>    |                                                                                          |   |            |

|              | peak inverse voltage is the                                                              |   |            |

|              | (a) half-wave rectifier (b) full-wave center-tapped rectifier                            | , | ,          |

|              | (c) full-wave bridge rectifier (d) both a and c                                          | ( | )          |

| 5.           | In this experiment, the rectifier circuit that has the greatest dc output voltage is the |   |            |

|              | (a) half-wave rectifier (b) full-wave center-tapped rectifier                            |   |            |

|              | (c) full-wave bridge rectifier                                                           | ( | )          |

|              | (c) Iun-wave bridge recurrer                                                             | ( | ,          |

| @ <b>4</b>   | 2000 Magnillan Dublishing Company All rights recoved                                     |   | 31         |

| $\mathbf{e}$ | 992 Macmillan Publishing Company. All rights reserved.                                   |   | <b>J</b> I |

32

# THE CAPACITOR INPUT RECTIFIER FILTER

#### **PURPOSE AND BACKGROUND**

The purpose of this experiment is to demonstrate the operation of a capacitor input filter when connected to the output of a full-wave bridge rectifier. The filter, which consists of a single resistor and capacitor in parallel, smooths out the pulsating output voltage of the rectifier.

Text References: 2-4, Rectifier Filters; Appendix B, Derivations.

#### REQUIRED PARTS AND EQUIPMENT

| $\square$ 1-k $\Omega$ resistor, 1/2 W | ☐ 12.6-V rms secondary    |

|----------------------------------------|---------------------------|

| Capacitors (25 V):                     | center-tapped transformer |

| $\square$ 100 $\mu$ F                  | □ Dual trace oscilloscope |

| $\Box$ 470 $\mu$ F                     | □ VOM or DMM              |

| ☐ Four 1N4001 silicon                  | ☐ Breadboarding socket    |

| rectifier diodes                       |                           |

#### **USEFUL FORMULAS**

dc output voltage

(1)

$$V_{

m dc} = \left(1 - \frac{0.00417}{R_L C}\right) V_{p(

m in)}$$

(when  $R_L C \gg T_{

m input}$ )

rms ripple voltage

$$(2) \ V_r = \frac{0.0024}{R_L C} V_{p(\mathrm{in})} \ \ (\mathrm{when} \ R_L C \gg T_{\mathrm{input}})$$

Percent ripple factor

(3)

$$\%r = \frac{V_r}{V_{dc}} \times 100\%$$

### **PROCEDURE**

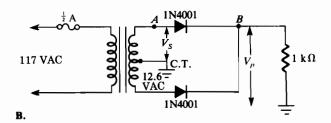

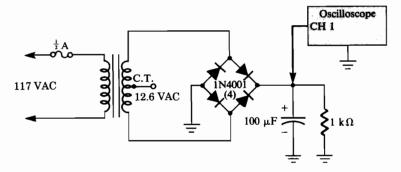

FIGURE 3-1 Schematic diagram of circuit.

- 1. Wire the full-wave bridge rectifier circuit shown in Figure 3-1, paying careful attention to the polarity of the 1N4001 diodes. You should be very careful to be sure that your connections to the 117-V primary of the transformer are properly protected so that you will not get a shock by accidentally touching them. Furthermore, you should have a 1/2-A fuse on the primary side of the transformer. Note that neither of the transformer's primary leads is grounded, while the center-tapped secondary lead is not used. Also observe the polarity of the 100-μF filter capacitor.

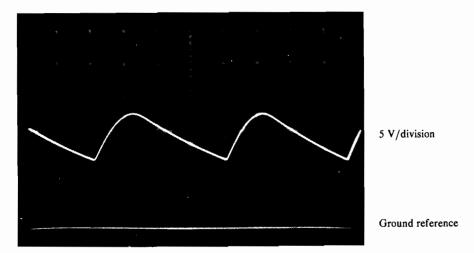

- 2. Apply 117 VAC (rms) to the transformer's primary leads. With one oscilloscope channel set to dc coupling, connect the probe to the ungrounded junction of the 1-k $\Omega$  resistor and the 100- $\mu$ F capacitor. If everything is working properly, you should obtain the waveform shown in Figure 3–2.

FIGURE 3-2 Time base: 2 ms/division.

- 3. With the oscilloscope, measure the peak output voltage  $(V_p)$  across the 1-k $\Omega$  resistor and the 100- $\mu$ F capacitor. With your VOM or DMM, measure the dc voltage  $(V_{dc})$  and compute the expected dc voltage, rms ripple, and percentage ripple factor using Equations 1, 2, and 3. Record all results in Table 3–1.

- 4. Turn off the 177-VAC primary voltage, and then place a piece of wire or a screwdriver across both capacitor leads, which, in effect, discharges the capacitor. With the relatively low secondary voltages used in this experiment, the risk of getting a severe shock is small. However, this practice is a good habit to acquire when working with power supplies and filters. By discharging (that is, shorting) the filter capacitor after the supply voltage has been turned off or removed, you then eliminate the possibility of coming in contact with a fully charged capacitor, which, depending on its capacitance and voltage, can deliver quite an unexpected jolt.

Remove the  $100-\mu F$  capacitor from the circuit and replace it with a  $470-\mu F$  capacitor. Then apply 117 VAC to the transformer's primary.

- 5. With your oscilloscope, measure the peak output voltage across the 1-k $\Omega$  resistor and the 470- $\mu$ F capacitor. As in Step 3, measure the dc output voltage and, using Equations 1, 2, and 3, calculate the expected values for the dc voltage, rms ripple voltage, and percent ripple factor. Record all results in Table 3-1.

- **6.** If you have wired the circuit correctly, you should now observe very little ripple voltage on the oscilloscope's display. Now change the input to *ac* coupling, and increase the sensitivity of

- the oscilloscope channel to about 10 mV/division so that you can clearly see the output ripple.

- 7. For each capacitor value, compare your values for dc output voltage, rms ripple voltage, and percent ripple factor. When you increase the value of the filter capacitor, what happens to the dc output voltage, rms ripple voltage, and percent ripple factor?

For a fixed load resistance of  $1~k\Omega$ , increasing the capacitance of the input filter capacitor should increase the dc output voltage toward the peak output voltage while decreasing both the rms ripple voltage and the percent ripple factor.

#### WHAT YOU HAVE DONE

This experiment demonstrated the operation of a capacitor input filter when connected to the output of a full-wave bridge rectifier. The filter, using a parallel resistor-capacitor circuit, smooths out the pulsating output voltage of the rectifier. As the RC time constant of the filter was made larger, the ripple voltage of the filter was reduced further.

| Name                          | Date   |

|-------------------------------|--------|

| THE CAPACITOR INPUT RECTIFIER | FILTER |

|                               |        |

**SCHEMATIC DIAGRAM:**

**OBJECTIVES/PURPOSE:**

| Name | Date |

|------|------|

|      |      |

## **DATA FOR EXPERIMENT 3**

TABLE 3-1

| Parameter                                | Step 3 | Step 5 |

|------------------------------------------|--------|--------|

| Secondary peak voltage, $V_p$ : Measured |        |        |

| dc output voltage, $V_{ m dc}$ :         |        |        |

| Measured                                 |        |        |

| rms ripple voltage, $V_r$ : Calculated   |        |        |

| Measured (peak-to-peak)                  |        |        |

| % ripple factor, % r: Calculated         |        |        |

| Name                     | Date |

|--------------------------|------|

| RESULTS AND CONCLUSIONS: |      |

### **REVIEW QUESTIONS FOR EXPERIMENT 3**

| 1.  | For the circuit of Figure 3–1, the time constant of the capacitor input filter is |   |    |

|-----|-----------------------------------------------------------------------------------|---|----|

|     | (a) 1 ms (b) 10 ms (c) 100 ms (d) 1 s                                             | ( | )  |

| 2.  | In Step 5, the dc output voltage is approximately                                 |   |    |

|     | (a) 6 V (b) 12 V (c) 18 V (d) 24 V                                                | ( | )  |

| 3.  | As the time constant of the input filter is decreased, the dc output voltage      |   |    |

|     | (a) decreases (b) increases (c) remains the same                                  | ( | )  |

| 4.  | As the time constant of the input filter is decreased, the output ripple voltage  |   |    |

|     | (a) decreases (b) increases (c) remains the same                                  | ( | )  |

| 5.  | In a well-designed power supply, the percent ripple factor should be              |   |    |

|     | (a) close to 0% (b) approximately 50%                                             |   |    |

|     | (c) close to 100%                                                                 | ( | )  |

| ©19 | 992 Macmillan Publishing Company. All rights reserved.                            |   | 39 |

40

\_\_\_\_\_

## THE DIODE LIMITER

#### PURPOSE AND BACKGROUND

The purpose of this experiment is to demonstrate the operation of a diode limiter. Diode limiters are wave-shaping circuits in that they are used to prevent signal voltages from going above or below certain levels. The limiting level may be either equal to the diode's barrier potential or made variable with a dc source voltage. Because of this clipping capability, the limiter is also called a *clipper*.

Text Reference: 2-5, Diode Limiting and Clamping Circuits.

#### REQUIRED PARTS AND EQUIPMENT

| $\square$ 15-k $\Omega$ resistor, 1/4 W  | ☐ 0–15 V dc power supply  |

|------------------------------------------|---------------------------|

| $\square$ 5-k $\Omega$ potentiometer, or | ☐ Signal generator        |

| 10-turn "trimpot"                        | ☐ Dual trace oscilloscope |

| ☐ 1N4001 silicon rectifier               | ☐ Breadboarding socket    |

| diode                                    |                           |

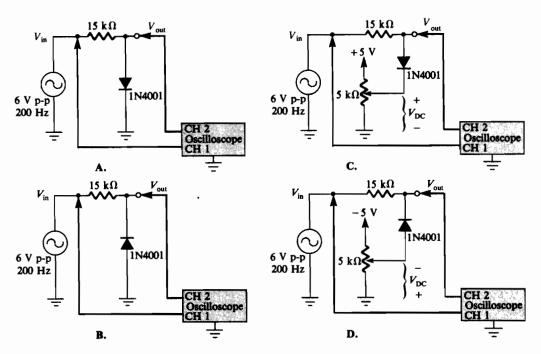

FIGURE 4-1 Schematic diagram of circuits.

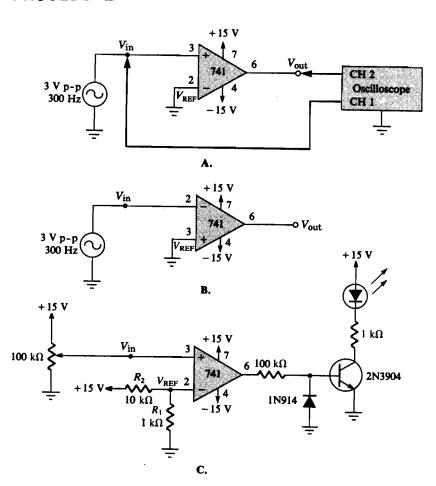

Wire the limiter circuit shown in the schematic diagram of Figure 4-1A. Set your oscilloscope to the following approximate setting:

> Channels 1 and 2: 1 V/division, dc coupling Time base: 1 ms/division

Without any input signal connected to the breadboard, position the two lines on the oscilloscope's display so that they are at the same level (that is, zero volts).

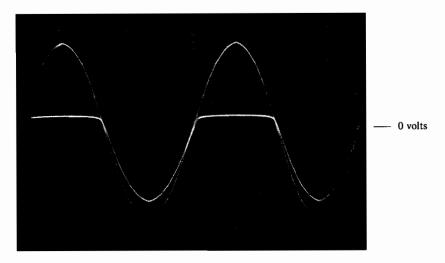

2. Now connect the signal generator to the breadboard. Adjust the signal generator's output level at 6 V peak-to-peak at a frequency of 200 Hz. You should see two waveforms similar to those shown in Figure 4-2. Notice that the positive peaks of the limiter's output waveform are removed, or clipped off. Notice also that the clipping level is not perfect; the positive peaks are clipped not at zero volts, but at a small positive voltage. When the input waveform goes positive at a level greater than the barrier potential of the diode, the diode is forward biased, the equivalent of a short circuit in series with a small dc voltage source. Thus, approximately 0.5 to 0.7 volt (the barrier potential

for a silicon diode) is dropped across the diode. When the input waveform goes negative, the diode looks like an open circuit, and essentially all of the input appears at the output. Such an arrangement is called a *positive* limiter because the circuit limits the positive peaks of the input waveform. On the data page at the end of this experiment, sketch your clipped waveform, showing the positive and negative peak values.

FIGURE 4-2

3. Now reverse the polarity of the diode in the circuit, as shown in Figure 4–1B. How does this waveform compare with that of Step 2?

The behavior is opposite that of the positive limiter. The waveform has all *negative* peaks of the input signal removed, as shown in Figure 4–3. Again, notice that the clipping level is not perfect; the negative peaks are clipped not at zero volts, but at a small negative voltage. Such an arrangement is called a *negative* limiter because the circuit clips off the negative peaks of the input waveform. On the data page at the end of this experiment, sketch your clipped waveform, showing the positive and negative peak values.

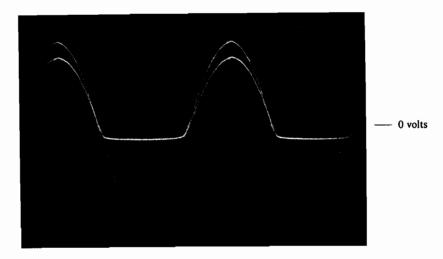

**4.** Now connect the circuit of Figure 4–1C. Apply power to the breadboard and adjust the potentiometer so that the dc voltage  $(V_{\rm DC})$  is +1.5 V. Connect the signal generator, set at 6 V peak-to-peak, to the breadboard. What do you notice about the output of the limiter?

The clipping level is *higher* than that measured in Step 2. The circuit uses a dc source voltage to *bias*, or set, the clipping

FIGURE 4-3

level. Consequently this arrangement is called a *positive-biased* limiter. On the data page at the end of this experiment, sketch the clipped waveform, showing the dc positive and negative peak values.

Note that the positive clipping level is the dc source voltage *plus* the diode's barrier potential. For the diode to become forward biased, the positive peaks of the input signal must be greater than the dc source voltage and the diode's barrier potential.

5. Vary the resistance of the potentiometer from one extreme to the other. What happens to the clipping level?

The clipping level changes with the setting of the potentiometer. At one extreme, when the dc bias voltage  $(V_{DC})$  is zero, the positive clipping level should be the same as was measured in Step 2. At the other extreme, there should be no clipping, as the dc bias voltage is about +5 V. Since the input positive peaks are at +3.0 V, the diode is effectively reverse biased and looks like an open circuit, and thus the input appears unchanged at the output.

6. Now reverse the polarities of both the diode and the dc power supply in the circuit, as shown in Figure 4–1D. Adjust the potentiometer so that the dc voltage  $(D_{\rm DC})$  is -1.5 V. Connect the signal generator, set at 6 V peak-to-peak, to the breadboard. What do you notice about the output of the limiter?

Note that the clipping level is *lower* than that measured in Step 3. The circuit uses a dc source voltage to *bias*, or set, the clipping level. Consequently, this arrangement is called a

negative-biased limiter. On the data page at the end of this experiment, sketch the clipped waveform, showing the dc positive and negative peak values.

Notice also that the negative clipping level is the dc source voltage plus the diode's barrier potential. For the diode to become forward biased, the negative peaks of the input signal must be greater than the dc source voltage and the diode's barrier potential.

7. Vary the resistance of the potentiometer from one extreme to the other. What happens to the clipping level?

The clipping level changes with the setting of the potentiometer. At one extreme, when the dc bias voltage  $(V_{DC})$  is zero, the positive clipping level should be the same as was measured in Step 3. At the other extreme, there should be no clipping, as the dc bias voltage is about -5 V. Since the input negative peaks are at -3.0 V, the diode is effectively reverse biased and looks like an open circuit, and thus the input appears unchanged at the output.

#### WHAT YOU HAVE DONE

This experiment demonstrated the operation of a diode limiter, or *clipper*, which limits signal voltages from going above or below preset levels. You worked with both positive and negative limiters whose clipping level was equal to the diode's barrier potential. In addition, it was shown how to make the clipping level variable by using an external dc voltage source.

46

| Name                | Date |

|---------------------|------|

| THE DIODE LIMITER   |      |

|                     |      |

|                     |      |

| OBJECTIVES/PURPOSE: |      |

**SCHEMATIC DIAGRAM:**

48

## **DATA FOR EXPERIMENT 4**

Volts/div=\_\_\_\_ Time/div=\_\_\_

Positive clipper (Step 2)

Volts/div=\_\_\_\_\_ Time/div=\_

Negative clipper (Step 3)

Volts/div=\_\_\_\_ Time/div=\_\_\_

Positive-biased clipper (Step 4)

Volts/div=\_\_\_\_\_ Time/div=\_

| Name | Date |

|------|------|

|------|------|

## **RESULTS AND CONCLUSIONS:**

## **REVIEW QUESTIONS FOR EXPERIMENT 4**

| 1. | For the positive limiter circuit of Figure 4–1A, the positive peak           |            |     |

|----|------------------------------------------------------------------------------|------------|-----|

|    | voltage is approximately                                                     | ,          |     |

|    | (a) $0 \text{ V}$ (b) $+0.6 \text{ V}$ (c) $+3 \text{ V}$ (d) $+6 \text{ V}$ | (          | )   |

| 2. | For the negative limiter circuit of Figure 4-1B, the positive                |            |     |

|    | peaks are not clipped because the diode is                                   |            |     |

|    | (a) reverse biased (b) forward biased                                        | (          | )   |

| 3. | In all the limiting circuits in this experiment, the 15-k $\Omega$ resistor  |            |     |

|    | is used to                                                                   |            |     |

|    | (a) set the clipping level                                                   |            |     |

|    | (b) set the peak output voltage                                              |            |     |

|    | (c) limit the voltage across the diode                                       |            |     |

|    | (d) limit the peak forward diode current                                     | (          | )   |

| 4. | For the circuit of Figure 4–1C, the potentiometer is used to set             | `          | ,   |

|    | the clipping level of the output's                                           |            |     |

|    | (a) positive peaks (b) negative peaks                                        |            |     |

|    | (c) positive and negative peaks                                              | (          | `   |

| 5  | For the circuit of Figure 4–1D, the potentiometer is used to set             | (          | ,   |

| J. | the clipping level of the output's                                           |            |     |

|    |                                                                              |            |     |

|    | (a) positive peaks (b) negative peaks                                        | ,          | `   |

|    | (c) positive and negative peaks                                              | (          | )   |

| EΛ |                                                                              |            |     |

| 50 | ©1992 Macmillan Publishing Company. All right                                | is reserve | ed. |

## THE DIODE CLAMPER

#### **PURPOSE AND BACKGROUND**

The purpose of this experiment is to demonstrate the operation of a diode clamper. Like the diode clipper, the clamper is a waveshaping circuit, but it adds a dc level to the input waveform. Thus, the clamper is often referred to as a *dc restorer*. However, unlike that of the clipper, the *shape* of the input signal of a clamper is not changed.

Text Reference: 2-5, Diode Limiting and Clamping Circuits.

#### **REQUIRED PARTS AND EQUIPMENT**

| $10\text{-k}\Omega$ resistor, $1/4$ W | Signal generator          |

|---------------------------------------|---------------------------|

| 10-μF electrolytic capacitor,         | ☐ Dual trace oscilloscope |

| 25 V                                  | ☐ Breadboarding socket    |

| 1N4001 silicon rectifier              |                           |

| diode                                 |                           |

#### **USEFUL FORMULAS**

Clamper time constant

(1)

$$10R_LC \gg T_{\rm input}$$

Peak output voltage

(2)  $V_{\text{out}}(\text{peak}) = V_{\text{in}} (\text{peak-to-peak}) - V_d$

#### **PROCEDURE**

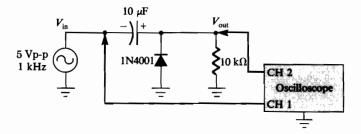

FIGURE 5-1 Schematic diagram of circuit.

1. Wire the clamper circuit shown in the schematic diagram of Figure 5-1. Set your oscilloscope to the following approximate settings:

Channels 1 and 2: 2.0 V/division, dc coupling Time base: 0.2 ms/division

Without any input signal connected to the breadboard, position the two lines on the oscilloscope's display so that they are at the same level (that is, zero volts).

- 2. Now connect the signal generator to the breadboard. Adjust the signal generator's output level at 5 V peak-to-peak at a frequency of 1 kHz. You should see two sine waves. Notice that the clamper's output signal level is above the input's. This action is that of a positive clamper, so the input waveform is shifted upward. This effect is the same as that obtained by adding a dc voltage onto the input waveform. On the data page at the end of this experiment, sketch both the input and the output waveforms, showing the positive and negative peak values for both.

- 3. Note that the clamping action is not perfect. The negative peaks of the output waveform are clamped not at zero volts, but at a small negative voltage. When the input waveform goes negative at a level greater than the barrier potential of the diode, the diode is forward biased, the equivalent of a short circuit

in series with a small dc voltage source. Thus, approximately 0.5 to 0.7 volt (the barrier potential for a silicon diode,  $V_d$ ) is dropped across the diode, while the remainder of the peak negative voltage ( $V_p - V_d$ ) charges the 10- $\mu$ F capacitor. On the next positive-going half-cycle, the diode is reverse biased, looking like an open circuit, and the voltage stored on the capacitor is then added to the time-varying input voltage. The result is that the peak output voltage is now approximately equal to the peak-to-peak input voltage, less the voltage drop of the diode.

4. Increase the peak-to-peak input voltage. What happens?

Although the peak-to-peak output voltage increases, its negative peak remains clamped at the same negative voltage level measured in Step 3. You should find that the positive peak output voltage is again approximately equal to the peak-to-peak input voltage.

5. Now reverse the polarity of the diode in the circuit, and repeat Steps 2, 3, and 4. Now what happens?

The behavior is opposite that of the positive clamper. Notice that the clamper's output signal level is *below* the input's. This action is that of a *negative* clamper, so the input waveform is shifted downward. This effect is the same as that obtained by adding a negative dc voltage onto the input waveform. On the data page at the end of this experiment, sketch both the input and the output waveforms, showing the positive and negative peak values for both.

- **6.** Again you should notice that the clamper action is not perfect. The positive peaks of the output waveform are clamped not at zero volts, but at a small positive voltage.

- 7. Increase the peak-to-peak input voltage. What happens?

You should see that although the peak-to-peak output voltage increases, its positive peak remains clamped at the same positive voltage level measured in Step 6. You should find that the negative peak output voltage is again approximately equal to the peak-to-peak input voltage.

#### WHAT YOU HAVE DONE

This experiment demonstrated the operation of a diode clamper. This circuit does not change the waveshape of the input signal, but merely adds a dc level to the input waveform.

54

\_\_\_\_\_

| Name                | Date |

|---------------------|------|

| THE DIODE CLAMPER   |      |

|                     |      |

| OBJECTIVES/PURPOSE: |      |

## **SCHEMATIC DIAGRAM:**

56

## **DATA FOR EXPERIMENT 5**

Volts/div=\_\_\_\_ Time/div=\_

Positive clamper (step 2)

Volts/div=\_\_\_\_\_ Time/div=\_\_\_\_

Negative clamper (step 5)

| Name Date _ |

|-------------|

|-------------|

## **RESULTS AND CONCLUSIONS:**

## **REVIEW QUESTIONS FOR EXPERIMENT 5**

| 1. |                                                                  |   |   |

|----|------------------------------------------------------------------|---|---|

|    | quency should be at least                                        | , | , |

|    | (a) 1 Hz (b) 10 Hz (c) 100 Hz (d) 1 kHz                          | ( | ) |

| 2. | For the circuit of Figure 5–1, if the input signal has a peak    |   |   |

|    | voltage of $V_p$ , then the output signal is                     |   |   |

|    | (a) shifted upward by approximately $V_p$                        |   |   |

|    | (b) shifted upward by approximately $2V_p$                       |   |   |

|    | (c) shifted downward by approximately $V_p$                      |   |   |

|    | (d) shifted downward by approximately $2V_p$                     | ( | ) |

| 3. | For the circuit of Figure 5–1, the negative peak voltage of the  |   |   |

|    | output signal is approximately                                   |   |   |

|    | (a) $-V_p$                                                       |   |   |

|    | <b>(b)</b> $-0.7 \text{ V}$                                      |   |   |

|    | (c) 0 V                                                          |   |   |

|    | (d) $+0.7 \text{ V}$                                             | ( | ) |

| 4. | If the peak-to-peak input voltage is increased,                  |   |   |

|    | (a) the peak-to-peak output voltage remains approximately        |   |   |

|    | equal to the peak-to-peak input voltage                          |   |   |

|    | (b) the negative peak output voltage remains clamped at ap-      |   |   |

|    | proximately -0.7 V                                               |   |   |

|    | (c) the output peak voltage approximately equals the peak-to-    |   |   |

|    | peak input voltage                                               |   |   |

|    | (d) all of the above                                             | ( | ) |

| 5. | In order to change the circuit of Figure 5-1 to a negative clam- | ` | , |

|    | per, you must                                                    |   |   |

|    | (a) reverse the polarity of the signal source                    |   |   |

|    | (b) reverse the polarity of the diode                            |   |   |

|    | (c) reverse the polarity of the capacitor                        |   |   |

|    | (d) all of the above                                             | ( | ١ |

|    | (w) an or one above                                              | ( | , |

# THE DIODE VOLTAGE DOUBLER

### **PURPOSE AND BACKGROUND**

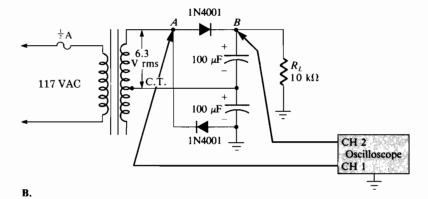

The purpose of this experiment is to demonstrate the operation of both the half-wave and the full-wave diode voltage doublers. Diode voltage doublers are used to double the peak rectified voltage without the necessity of increasing the input transformer's voltage rating. The half-wave voltage doubler is actually a positive clamper followed by a half-wave rectifier with a capacitor input filter (peak detector). It charges a series capacitor on each positive half-cycle. Consequently, the ripple frequency is the same as the input frequency.

The full-wave voltage doubler, on the other hand, has the same rectified peak output voltage as the half-wave doubler. It charges one of two series capacitors on the first half-cycle, while the other capacitor is charged on the remaining half-cycle. Therefore, it has a ripple frequency that is twice the input frequency. Consequently, for the same filter time constant, the peak-to-peak ripple voltage is smaller when a full-wave voltage doubler is used.

Text Reference: 2-6, Voltage Multipliers.

#### **REQUIRED PARTS AND EQUIPMENT**

| $\square$ 10-k $\Omega$ resistor, 1/4 W | $\square$ 12.6-V rms secondary |

|-----------------------------------------|--------------------------------|

| $\square$ Two 100- $\mu$ F capacitors,  | center-tapped transformer      |

| 25 V                                    | ☐ Dual trace oscilloscope      |

| ☐ Two 1N4001 silicon                    | □ VOM or DMM                   |

| rectifier diodes                        | ☐ Breadboarding socket         |

#### **USEFUL FORMULAS**

Output voltage

(1)  $V_0 = 2V_s - 2V_d$

Ripple frequency

(2)  $f_{\text{ripple}} = f_{\text{in}}$

(half-wave doubler)

(3)  $f_{\text{ripple}} = 2f_{\text{in}}$

(full-wave doubler)

Diode peak inverse voltage

(4)  $PIV = 2V_s$

#### **PROCEDURE**

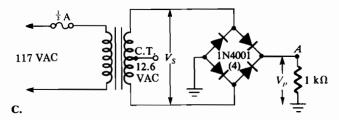

- 1. Wire the half-wave diode voltage doubler shown in the schematic diagram of Figure 6-1A.

- 2. Set your oscilloscope to the following approximate settings:

Channels 1 and 2: 5 V/division, dc coupling

Time base: 2 ms/division

Apply the 117-V rms ac, 60-Hz power line voltage to the transformer's primary.

3. You should see two sine waves on the oscilloscope's display. On Channel 1 at point A, it should show the secondary voltage of the transformer. Measure the positive peak voltage  $V_s$  and the frequency  $f_{\rm in}$ , recording these values in Table 6-1.

On Channel 2, you should see the same waveform at point B, but it should be positively clamped near zero volts and the positive peak voltage should be nearly twice that of the transformer's secondary voltage. Measure this peak voltage,  $V_p$ , and record this value in Table 6–1.

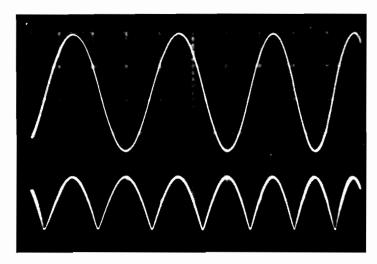

4. Now take the Channel 1 probe and connect it to the 10-k $\Omega$  load resistor (point C). You should see two signals similar to those shown in Figure 6–2. Measure the dc voltage  $V_{\rm DC}$  across the 10-k $\Omega$  resistor with a VOM or DMM, and record this value in

FIGURE 6-1 Schematic diagram of circuits.

FIGURE 6-2

- Table 6–1. You should have measured a dc voltage that is nearly twice that of the transformer's peak secondary voltage, less two diode voltage drops.

- 5. Now switch Channel 1 to ac coupling, and increase the sensitivity to 0.05 V/division to display adequately the output ripple voltage. Measure both the peak-to-peak ripple voltage and the ripple frequency. Record both values in Table 6-1. You should find that both the ripple frequency and the input power line frequency are the same.

- 6. Disconnect the power line voltage from the transformer, and wire the full-wave diode voltage doubler shown in the schematic diagram of Figure 6–1B.

- 7. Set your oscilloscope to the following approximate settings:

Channels 1 and 2: 5 V/division, dc coupling Time base: 2 ms/division

Apply the 117-V rms ac, 60-Hz power line voltage to the transformer's primary.

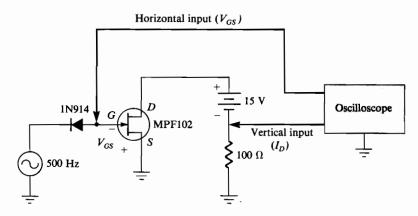

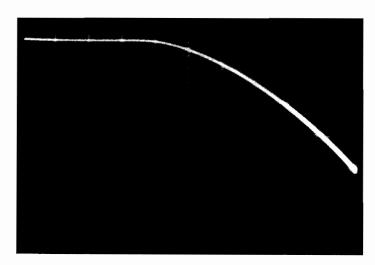

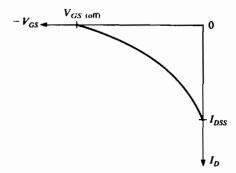

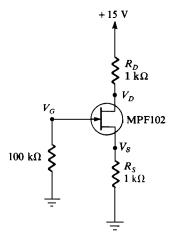

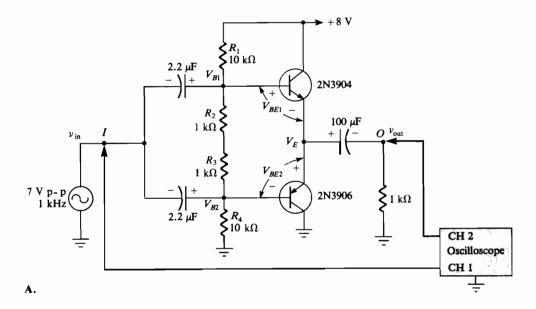

- 8. You should see two sine waves on the oscilloscope's display. On Channel 1 at point A, you should see the transformer's secondary voltage positively clamped near zero volts. Measure its positive peak voltage  $V_p$  and its frequency  $f_{\rm in}$ , recording these values in Table 6–2. Measure the dc voltage  $V_{\rm dc}$  across the 10-k $\Omega$  resistor with a VOM or DMM, and record this value in Table 6–2. You should have measured a dc voltage that is nearly twice that of the transformer's peak secondary voltage, less two diode voltage drops.