GENETIC AND EVOLUTIONARY COMPUTATION Series Editors: David E. Goldberg and John R. Koza

Edited by Tetsuya Higuchi Yong Liu Xin Yao

# Evolvable Hardware

Evolvable Hardware

#### Genetic and Evolutionary Computation Series

#### **Series Editors**

David E. Goldberg Consulting Editor IlliGAL, Dept. of General Engineering University of Illinois at Urbana-Champaign Urbana, IL 61801 USA Email: deg@uiuc.edu

John R. Koza Consulting Editor Medical Informatics Stanford University Stanford, CA 94305-5479 USA Email: john@johnkoza.com

Selected titles from this series:

David E. Goldberg The Design of Innovation: Lessons from and for Competent Genetic Algorithms, 2002 ISBN 1-4020-7098-5

John R. Koza, Martin A. Keane, Matthew J. Streeter, William Mydlowec, Jessen Yu, Guido Lanza Genetic Programming IV: Routine Human-Computer Machine Intelligence ISBN: 1-4020-7446-8 (hardcover), 2003; ISBN: 0-387-25067-0 (softcover), 2005

Carlos A. Coello Coello, David A. Van Veldhuizen, Gary B. Lamont Evolutionary Algorithms for Solving Multi-Objective Problems, 2002 ISBN: 0-306-46762-3

Lee Spector Automatic Quantum Computer Programming: A Genetic Programming Approach, 2004 ISBN: 1-4020-7894-3

William B. Langdon Genetic Programming and Data Structures: Genetic Programming + Data Structures = Automatic Programming! 1998 ISBN: 0-7923-8135-1

For a complete listing of books in this series, go to http://www.springer.com

Tetsuya Higuchi Yong Liu Xin Yao (Eds.)

# Evolvable Hardware

Tetsuya Higuchi National Institute of Advanced Industrial Science and Technology, Japan

Yong Liu The University of Aizu, Japan

Xin Yao The University of Birmingham, United Kingdom

Library of Congress Control Number: 2006920799

| ISBN-10: 0-387-24386-0    | e-ISBN-10: 0-387-31238-2    |

|---------------------------|-----------------------------|

| ISBN-13: 978-0387-24386-3 | e-ISBN-13: 978-0387-31238-5 |

© 2006 by Springer Science+Business Media, LLC.

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science + Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden.

The use in this publication of trade names, trademarks, service marks and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Printed in the United States of America

987654321

springer.com

# PREFACE

Evolvable hardware refers to hardware that can learn and adapt autonomously in a dynamic environment. It is often an integration of evolutionary computation and programmable hardware devices. The objective of evolvable hardware is the autonomous reconfiguration of hardware structure in order to improve performance over time. The capacity for autonomous reconfiguration with evolvable hardware makes it fundamentally different from conventional hardware, where it is almost impossible to change the hardware's function and architecture once it is manufactured. While programmable hardware devices, such as a PLD (Programmable Logic Device) and a FPGA (Field Programmable Gate Array), allow for some functional changes after being installed on a print circuit board, such changes cannot be executed without the intervention of human designers (i.e., the change is not autonomous). With the use of evolutionary computation, however, evolvable hardware has the capability of autonomously changing its hardware architectures and functions.

The origins of evolvable hardware can be traced back to Mange's work and Higuchi's work, which were conducted independently around 1992. While Mange's work has led to bio-inspired machines that aim at self-reproduction or self-repair of the original hardware structure rather than evolving new structures, Higuchi's work has led to evolvable hardware research utilizing evolutionary algorithms for the autonomous reconfiguration of hardware structures. This book focuses primarily on the second line of research.

Departing from the initial interest of the artificial intelligence and artificial life communities in evolvable hardware to autonomously evolve hardware structures, recent evolvable hardware research has come to address some important topics for semiconductor engineering and mechanical engineering, such as:

- post-fabrication LSI adjustment,

- LSI tolerance to temperature change,

- self-testing/self-repairing LSI,

- human-competitive analog design,

- MEMS fine-tuning,

- adaptive optical control with micron-order precision, and

- evolvable antenna for space missions.

Research activities relating to evolvable hardware are mainly reported at two international conferences. The first one is the series of International Conferences on Evolvable Systems (ICES). The second is the NASA-DoD Evolvable Hardware Conferences that have been held every year in the USA since 1999. While it is rather difficult to neatly classify this body of research activities, this book adopts the following three categories:

- 1. Digital hardware evolution

- (1-1) Digital evolvable hardware based on genetic algorithms

- (1-2) Bio-inspired machines

- 2. Analog hardware evolution

- (2-1) Analog evolvable hardware based on genetic algorithms

- (2-2) Analog circuit design with evolutionary computation

- 3. Mechanical hardware evolution

This book brings together 11 examples of cutting-edge research and applications under these categories, placing particular emphasis on their practical usefulness.

Tetsuya Higuchi Yong Liu Xin Yao

# CONTENTS

| Pre | eface                                                                                                                                                                      | v  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.  | Introduction to Evolvable Hardware<br>Tetsuya Higuchi, Yong Liu, Masaya Iwata and Xin Yao                                                                                  | 1  |

| 2.  | EHW Applied to Image Data Compression<br>Hidenori Sakanashi, Masaya Iwata and Tetsuya Higuchi                                                                              | 19 |

| 3.  | A GA Hardware Engine and Its Applications<br>Isamu Kajitani, Masaya Iwata and Tetsuya Higuchi                                                                              | 41 |

| 4.  | Post-Fabrication Clock-Timing Adjustment Using Genetic<br>Algorithms<br>Eiichi Takahashi, Yuji Kasai, Masahiro Murakawa<br>and Tetsuya Higuchi                             | 65 |

| 5.  | Bio-Inspired Computing Machines with Artificial Division<br>and Differentiation<br>Daniel Mange, André Stauffer, Gianluca Tempesti,<br>Fabien Vannel and André Badertscher | 85 |

| 6.  | The POEtic Hardware Device: Assistance for Evolution,<br>Development and Learning<br>Andy M. Tyrrell and Will Barker                                                       | 99 |

| 7.   | Evolvable Analog LSI<br>Masahiro Murakawa, Yuji Kasai, Hidenori Sakanashi<br>and Tetsuya Higuchi                                                                                                                                                                            | 121 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 8.   | Reconfigurable Electronics for Extreme Environments<br>Adrian Stoica, Didier Keymeulen, Ricardo S. Zebulum<br>and Xin Guo                                                                                                                                                   | 145 |

| 9.   | Characterization and Synthesis of Circuits at Extreme Low<br>Temperatures<br>Ricardo S. Zebulum, Didier Keymeulen, Rajeshuni Ramesham,<br>Lukas Sekanina, James Mao, Nikhil Kumar and Adrian Stoica                                                                         | 161 |

| 10.  | Human-Competitive Evolvable Hardware Created by Means of<br>Genetic Programming<br>John R. Koza, Martin A. Keane, Matthew J. Streeter,<br>Sameer H. Al-Sakran and Lee W. Jones                                                                                              | 173 |

| 11.  | Evolvable Optical Systems<br>Hirokazu Nosato, Masahiro Murakawa, Yuji Kasai<br>and Tetsuya Higuchi                                                                                                                                                                          | 199 |

| 12.  | Hardware Platforms for Electrostatic Tuning of<br>MEMS Gyroscope Using Nature-Inspired Computation<br>Didier Keymeulen, Michael I. Ferguson, Luke Breuer,<br>Wolfgang Fink, Boris Oks, Chris Peay, Richard Terrile,<br>Yen-Cheng, Dennis Kim, Eric MacDonald and David Foor | 209 |

| Inde | ex                                                                                                                                                                                                                                                                          | 223 |

# Chapter 1

# **INTRODUCTION TO EVOLVABLE HARDWARE**

Tetsuya Higuchi<sup>1</sup>, Yong Liu<sup>2</sup>, Masaya Iwata<sup>1</sup>, and Xin Yao<sup>3</sup>

<sup>1</sup>Advanced Semiconductor Research Center, National Institute of Advanced Industrial Science and Technology (AIST), Email: t-higuchi@aist.go.jp; <sup>2</sup>The University of Aizu, Fukushima, Japan; <sup>3</sup>The University of Birmingham, UK.

Abstract: This chapter provides an introduction to evolvable hardware. First, the basic idea of evolvable hardware is outlined. Because evolvable hardware involves the integration of programmable logic device and evolutionary computation, these are both explained briefly. Then, an overview of current research on evolvable hardware is presented. Finally, the chapter discusses some directions for future research.

Key words: genetic algorithm, genetic programming, FPGA, programmable logic device.

#### **1. INTRODUCTION**

This book describes a new hardware paradigm called "Evolvable Hardware" and its real-world applications.

Evolvable hardware is the integration of evolutional computation and programmable hardware devices. The objective of evolvable hardware is the "autonomous" reconfiguration of hardware structure in order to improve performance. The capacity for autonomous reconfiguration with evolvable hardware makes it fundamentally different from conventional hardware, where it is almost impossible to change the hardware's function once it is manufactured. While programmable hardware devices, such as a PLD (Programmable Logic Device) and a FPGA (Field Programmable Gate Array), allow for some functional changes after being installed on a print circuit board, such changes cannot be executed without the intervention of human designers (i.e., the change is not autonomous). With the use of evolutional computation, however, evolvable hardware has the capability to autonomously change its hardware functions. The origins of evolvable hardware can be traced back to two papers by Daniel Mange (Mange, 1993a, 1993b) and a paper by Tetsuya Higuchi (Higuchi, 1992), which were written independently around 1992. While the Mange papers led to bio-inspired machines that aim at self-reproduction or self-repair of the original hardware structure rather than evolving new structures, the Higuchi paper led to evolvable hardware research utilizing genetic algorithms for the autonomous reconfiguration of hardware structure. This book focuses primarily on the second line of research.

Departing from an initial interest in artificial intelligence and artificial life for hardware to autonomously evolve its own structure, recent evolvable hardware research has come to address important topics for semiconductor engineering and mechanical engineering, such as:

- post-fabrication LSI adjustment

- LSI tolerance to temperature change

- self-testing/self-repairing LSI

- human-competitive analog design

- MEMS (Micro Electro Mechanical System) fine-tuning

- adaptive optical control with micron-order precision

- evolvable antenna for space missions

Research activities relating to evolvable hardware are mainly reported at two international conferences. The first one is the series of International Conferences on Evolvable Systems (ICES) held in 1996 (Japan), 1998 (Switzerland), 2000 (UK), 2001 (Japan), 2003 (Norway), 2005 (Spain), 2007 (to be in China) and 2008 (to be in Czecho-Slovakia). The second is the NASA-DOD Evolvable Hardware Conferences that have been held every year in the USA since 1999. While it is rather difficult to neatly classify this body of research activities, this book adopts the following three categories:

- 1. (Category 1) Digital hardware evolution

- (1-1) Digital evolvable hardware based on genetic algorithms

- (1-2) Bio-inspired machines

- 2. (Category 2) Analog hardware evolution

- (2-1) Analog evolvable hardware based on genetic algorithms

- (2-2) Analog circuit design with evolutionary computation

- 3. (Category 3) Mechanical hardware evolution

This book brings together nine examples of cutting-edge research and applications under these categories, placing particular emphasis on their practical usefulness.

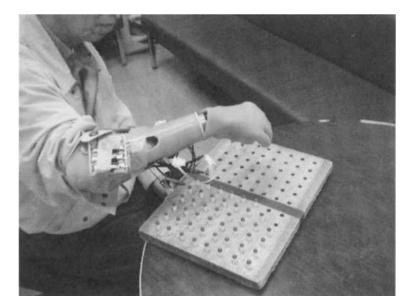

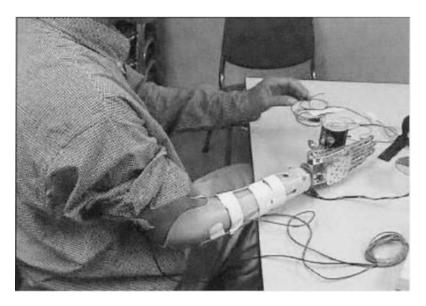

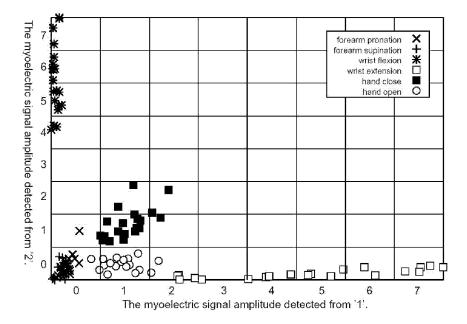

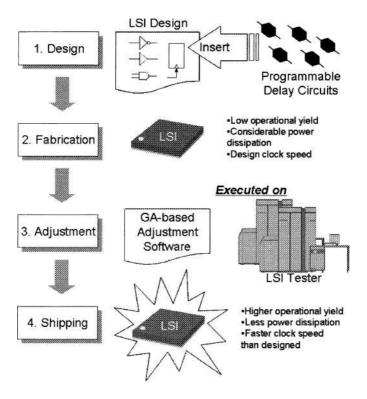

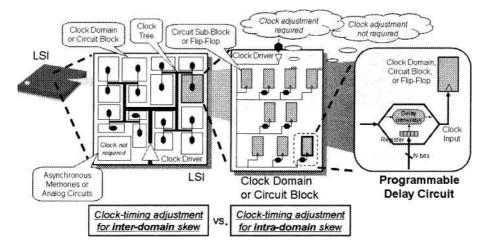

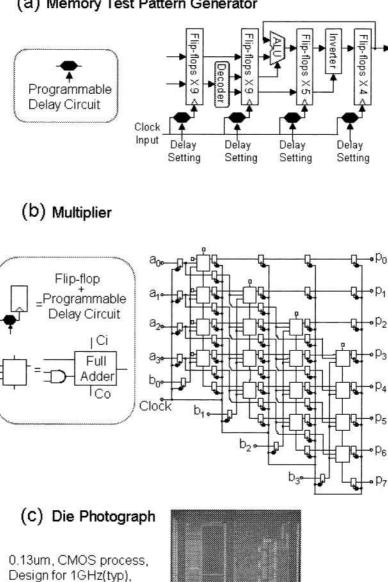

Category 1-1 of digital evolvable hardware based on genetic algorithms includes a data compression method for print images proposed by H. Sakanashi that has been accepted by the International Standards Organization (ISO) (Chapter 2), the first evolvable hardware chip developed for myoelectric hand control by I. Kajitani (Chapter 3), and E. Takahashi's work on clock-timing adjusting (Chapter 4). According to a report, a similar method to Takahashi's was used in the clock-timing adjustment for engineering samples of the Intel Pentium 4.

Under Category 1-2, the pioneering work on bio-inspired machines is discussed by D. Mange (Chapter 5), while Chapter 6 by A. Tyrrell describes an LSI implementation of a bio-inspired machine.

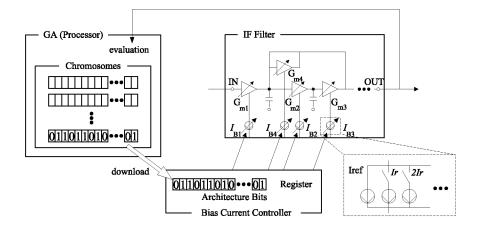

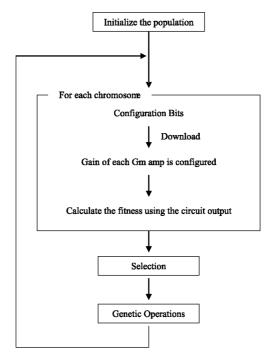

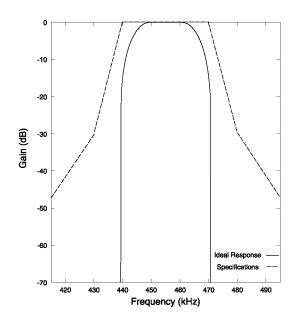

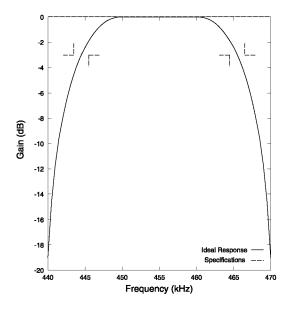

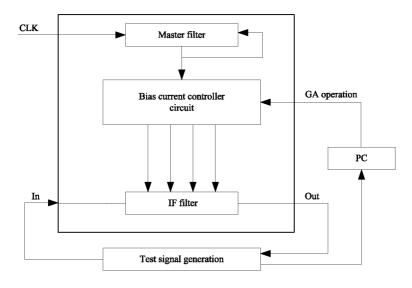

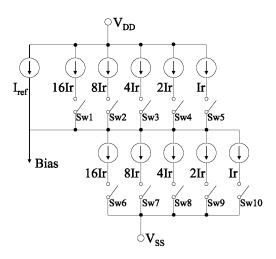

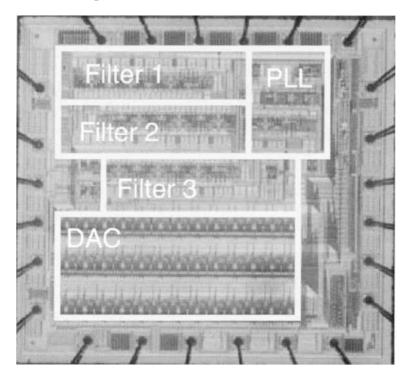

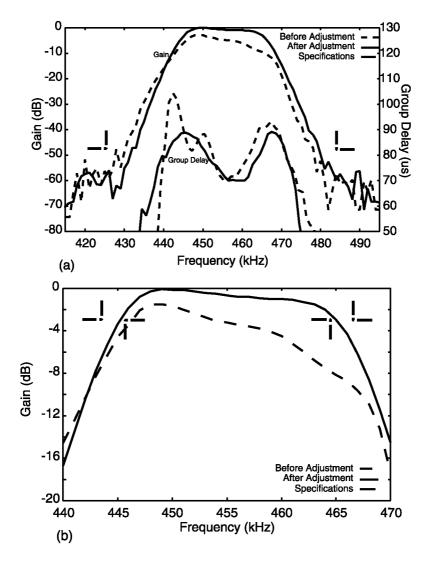

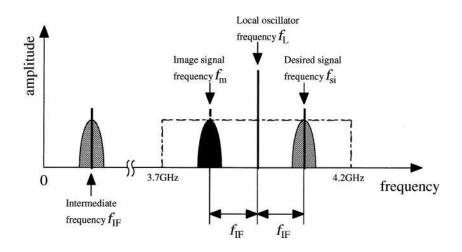

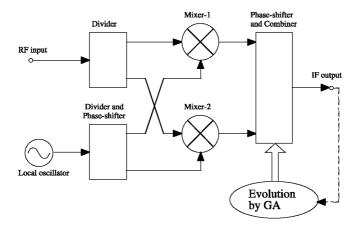

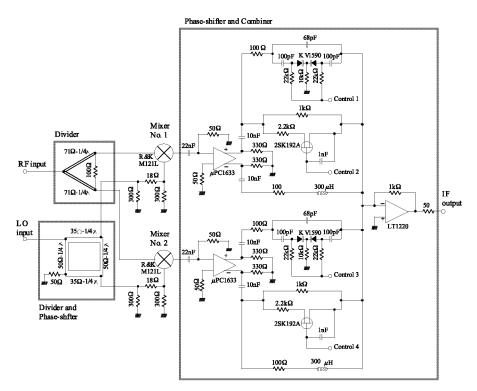

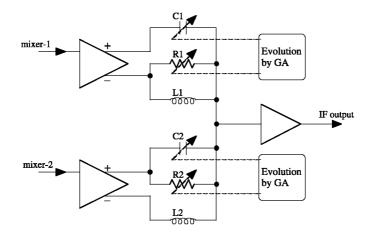

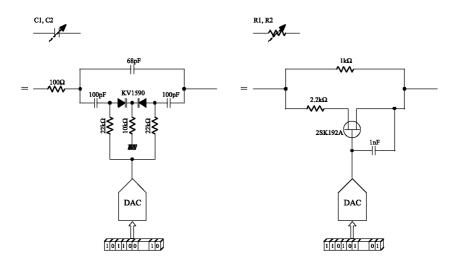

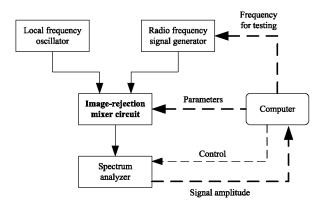

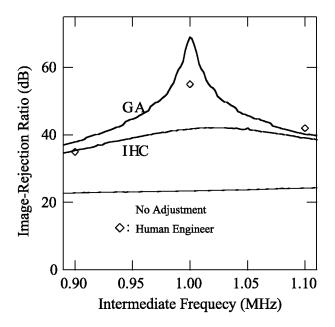

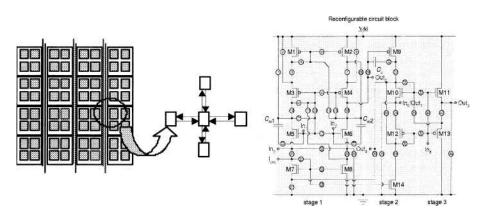

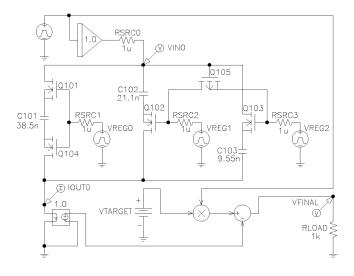

As representative work on analog evolvable hardware based on genetic algorithms (Category 2-1), M. Murakawa describes the analog intermediate filter LSI used in commercial cellular phones (Chapter 7) and A. Stoica outlines NASA's FPTA (Field Programmable Transistor Array) (Chapter 8). Employing a FPTA, Chapter 9 by R. Zebulum demonstrates how adaptation to extreme low temperatures is possible with the genetic algorithm approach.

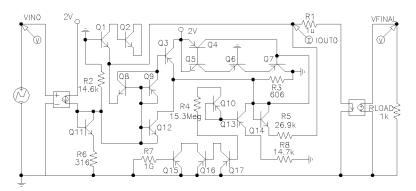

In Category 2-2, Chapter 10 presents J. Koza's work which highlights the great potential of evolvable hardware for innovative analog circuit design.

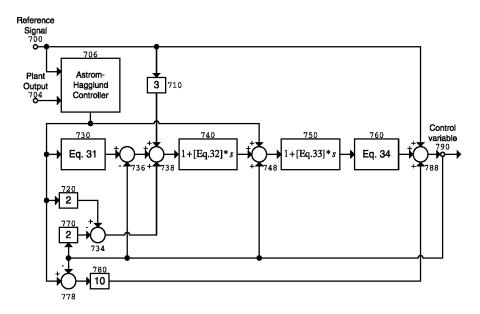

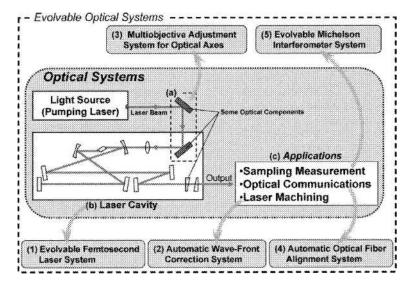

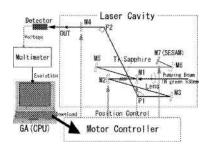

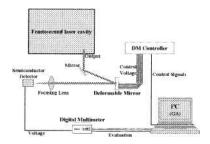

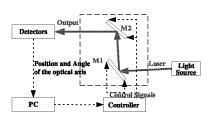

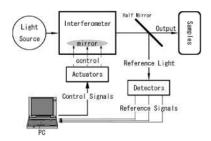

Two pioneering works in mechanical hardware evolution are described within Category 3: H. Nosato's work on evolvable femtosecond laser systems (Chapter 11) and D. Keymulen's evolvable gyro system (Chapter 12). These works suggest that optimization by genetic algorithms can open up a new paradigm of mechanical evolutions that has a potentially wide application for MEMS.

Before each of these eleven works are described in detail in the following chapters, the remainder of this chapter briefly discusses three aspects of evolvable hardware research: (1) the basic idea of evolvable hardware, (2) an overview of evolvable hardware research being conducted around the world, and (3) directions for future research on evolvable hardware.

#### 2. BASIC IDEA OF EVOLVABLE HARDWARE

As previously noted, two concepts are combined in realizing evolvable hardware: programmable hardware devices such as FPGA, and evolutionary computation such as genetic algorithms and genetic programming. In this section, these two concepts are briefly explained.

#### 2.1 **Programmable Hardware Devices**

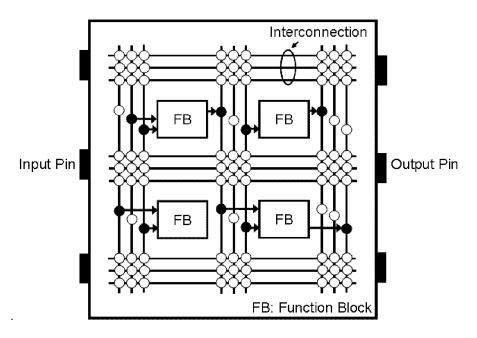

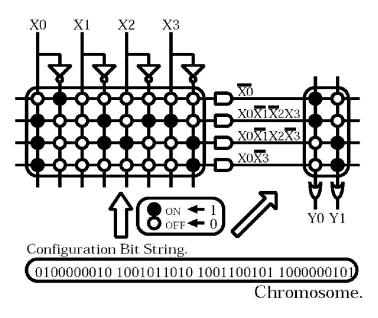

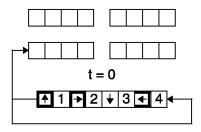

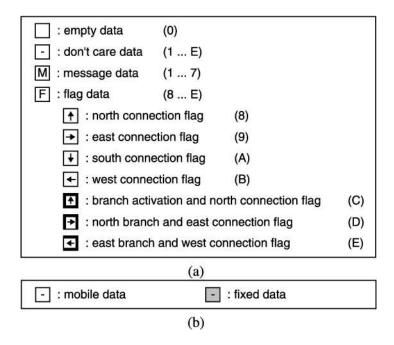

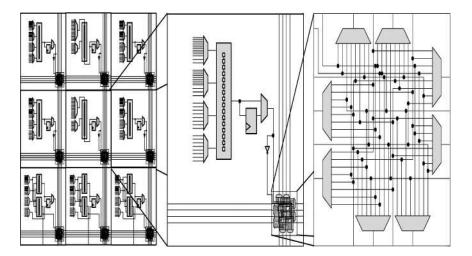

The advantage of programmable devices is that the hardware architecture can be changed any number of times by loading software string bits that determine the specific hardware structure. Because this advantage leads to fast prototyping and reductions in repair costs, the market for FPGAs as programmable hardware devices has grown rapidly over the last two decades. Typically, a FPGA has a structure, as depicted in Figure 1-1, consisting of functional blocks (FBs) and interconnections among the FBs. The function of an FB can be specified by setting some bit string into the block. The interconnections to FBs are also determined by setting the bit strings. These bit strings, shown as dots in the figure, are called configuration bits. Thus, the specific hardware structure of a programmable hardware device is actually determined by downloading the configuration bits.

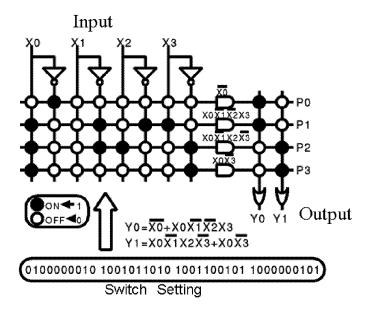

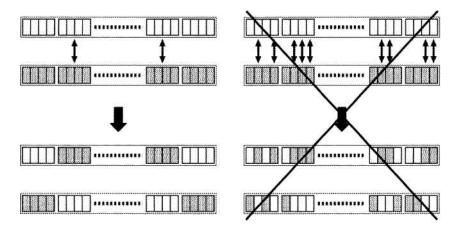

Figure 1-2 is a more specific example of hardware reconfiguration with a programmable logic array (PLA) which is an early PLD product of the 1980's. A PLA consists of a Boolean AND part (left side of Figure 1-2) and a Boolean OR part (right side of Figure 1-2). In Figure 1-2, there are four inputs (X0 to X4) and two outputs (Y0 and Y1). By setting the switch dots, various hardware functions can be realized.

For example, on the first row of the switch setting for the AND part, only one switch dot is *on*, which means that negation of input X0 is allowed to enter the Boolean AND part of the PLA. So, the output from the first row of the AND part becomes  $\overline{X0}$ . On the second row, four switch dots are *on*, which means that X0 and X3, as well as the negations of X1 and X2, can enter the second row of the AND part. So, the output from the second row becomes  $X0\overline{X1X2X3}$ . Similarly, the outputs for the third and fourth rows would be  $X0\overline{X1X2X3}$  and  $X0\overline{X3}$ , respectively.

Figure 1-1. FPGA organization

Figure 1-2. Reconfiguration of PLA

The outputs from the AND part go to the OR part. The switch settings for the OR part mean that for the second column from the right the outputs from the first and second rows of the AND part are allowed to enter. So, the output Y0 from this second column of the OR part becomes  $\overline{X0} + X0\overline{X1X2X3}$ . Similarly, for the other column, the output Y1 becomes  $X0\overline{X1X2X3} + X0\overline{X3}$  with the switch settings in Figure 1-2. The switch setting is shown at the bottom of Figure 1-2. By downloading this bit string, Y0 and Y1 would be defined as explained above. If a different bit string is downloaded into the PLA, a different hardware function for the PLA would be easily realized.

# 2.2 Evolutionary Computation

This section briefly outlines the principles of evolutionary computation. After describing genetic algorithm in the first subsection in terms of the initial preparation stage and the search process, involving crossover, mutation, evaluation and selection procedures, the second subsection introduces genetic programming as the application of GAs to the evolution of computer programs.

#### 2.2.1 Genetic Algorithm

Within artificial intelligence, one frequently encounters search problems where the solution cannot be identified within a finite period of time due to the combinatorial explosion of the search space. Genetic Algorithm (GA) is a general search technique that can be applied to such problems because it does not require user specific or a priori knowledge concerning the problem to be solved. First proposed by J. Holland, GA is loosely based on the notion of population genetics. Accordingly, some GA terms (e.g., chromosome, mutation) are derived from population genetics, although they do not correspond strictly to their senses within population genetics.

A search executed by a GA involves two stages: the preparation and the search stages:

(Preparation)

- 1. First, a set of candidate search solutions, called a population, must be prepared, because GA is a parallel search method that starts searching from this initial candidate population.

- 2. Each candidate is referred to as a chromosome, which is typically a binary bit string. The initial values of candidates are determined randomly.

- 3. An evaluation function, known as the fitness function, must also be designed for each problem. The fitness function is used to evaluate each chromosome in terms of being a good solution to the problem.

(Search)

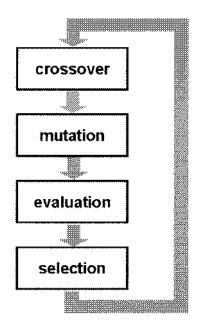

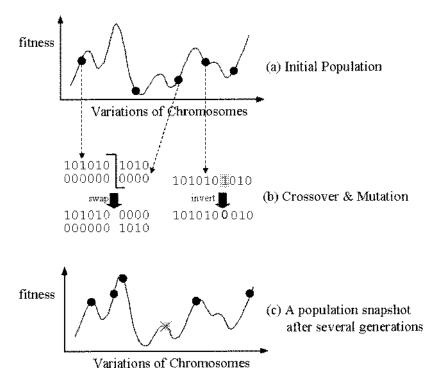

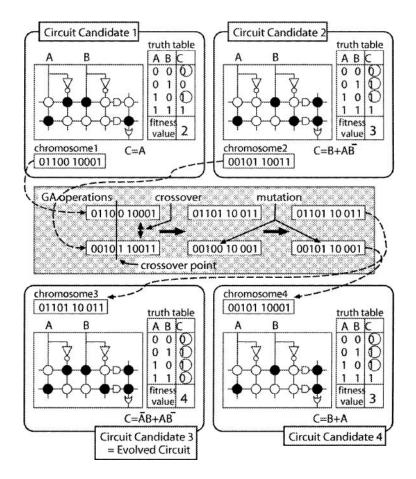

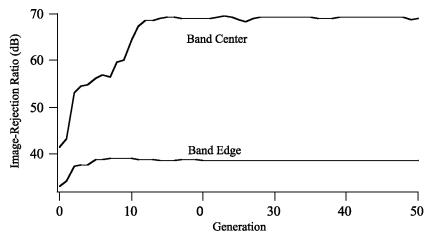

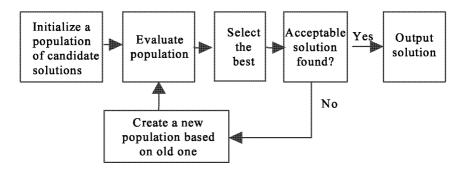

The basic idea behind GA is to obtain a new chromosome with the optimal fitness value that can be regarded as a search solution. Until this chromosome is obtained, genetic operations, such as crossover and mutation, are repeatedly executed on the population. As shown in Figure 1-3, GA search involves repeatedly executing a cycle, referred to as a "generation," consisting of a crossover operation, a mutation operation, an evaluation, and selection.

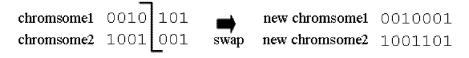

- 1. Crossover operation: One of the methods of generating new chromosomes is the crossover operation. The operation randomly chooses two chromosomes as parents and exchanges parts of them, as shown in Figure 1-4.

- 2. Mutation operation: A particular bit is stochastically chosen and its value is flipped to generate a new chromosome.

- 3. Evaluation: In order to identify the candidates that may survive to the next generation, each chromosome is evaluated according to the fitness function and assigned a fitness value.

Figure 1-3. GA cycle

Figure 1-4. Crossover operation

4. Selection: By executing the crossover and mutation operations, new chromosomes are generated that may have higher fitness values. However, because the number of chromosomes in a population is fixed during a search, it is necessary to select from among the old and new chromosomes. While there are various policies concerning selection, the typical operation is the roulette wheel selection. With the roulette selection, chromosomes with higher fitness values are likely to survive as members of the next generation. Once selection is completed, a new population is ready for the next generation.

Let us consider the following search problem as an example of a GA search:

find

$$x_{\max}$$

where  $f(x_{\max}) = Max f(x)$ . (1)

First, the fitness function for this problem is set to be f(x). Then, as shown in Figure 1-5(a), an example population of five 10-bit chromosomes is generated at random. Each chromosome can be decoded to the variable x in (1). Pairs of chromosomes are then randomly selected. These are mated and undergo genetic operations such as crossover and mutation, to yield better chromosomes in subsequent generations. After several generations of the GA search, chromosomes with lower fitness values tend to be eliminated from the population and relatively high-fitness chromosomes remain, as shown in Figure 1-5(c) (in contrast to Figure 1-5(a)).

Figure 1-5. An example of GA search

#### 2.2.2 Genetic Programming

A special subbranch of GAs is genetic programming proposed by J. Koza as the application of GAs to the evolution of computer programs. Trees (particularly, Lisp expression trees) are often used to represent individuals. Both crossover and mutation are used in genetic programming.

#### 1. Introduction to Evolvable Hardware

Genetic programming can be used to automatically create both the topology and sizing of an electrical circuit by establishing program trees for electrical circuits and defining a fitness that measures how well the behavior and characters of a given candidate circuit satisfy the design requirements. A developmental process can be employed to transform a program tree into a fully developed electrical circuit by executing component creation, topology modification, and development control functions, as well as arithmetic performance and automatic defining functions. One advantage of this kind of developmental process is in preserving the electrical validity of the circuit. Another advantage is the ability to preserve locality. Most of the functions involved in the developmental process operate on a small local area of the circuit, so subtrees within a program tree tend to operate locally. The crossover operation transplants subtrees and preserves their locality. The mutation and architecture-altering operations also both preserve locality because they only affect subtrees.

The evolutionary design offers several advantages over conventional design carried out by human designers. First, evolutionary design can explore a wider range of design alternatives in the hope of evolving novel designs. Second, evolutionary design does not assume a priori knowledge about any particular design domain, which is advantageous, where a priori knowledge is scarce or too costly to obtain. Finally, evolutionary design can cope with all kinds of constraints to satisfy the design requirements.

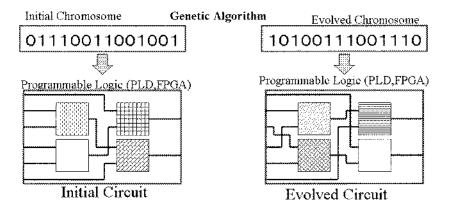

# 2.3 Integration of Genetic Algorithm and Programmable Hardware Devices

The key concept of evolvable hardware is to regard the configuration bits of programmable hardware devices as the chromosomes of GAs. By designing a fitness function to achieve a desired hardware function, the GA becomes a means of autonomous hardware reconfiguration. Figure 1-6 explains this idea. Configuration bits "evolved" by the GA are repeatedly downloaded into the programmable hardware devices until the evolved hardware performance is satisfactory in terms of fitness function values. A GA for evolvable hardware is executed either outside or inside the evolvable hardware, depending on its purpose. For example, if the speed of hardware reconfiguration is an important factor, then the GA should be inside the evolvable hardware.

Figure 1-6. Basic idea of evolvable hardware

# 3. OVERVIEW OF EVOLVABLE HARDWARE RESEARCH AROUND THE WORLD

This section presents a brief overview of evolvable hardware research around the world. In this selective survey, we highlight research reported at the International Conference on Evolvable Systems (ICES). First held in 1996, ICES was the first conference to focus mainly on evolvable hardware, including all aspects of evolvable systems. As already mentioned, we are classifying evolvable hardware research under three categories: digital hardware evolution, analog hardware evolution, and mechanical hardware evolution. Some works are singled out in each category. For readers with further interest, it is recommended to read X. Yao's overview (Yao, 1999).

# 3.1 Digital Hardware Evolution

Digital hardware evolution is the most active category of evolvable hardware research. In this book, this category is further classified into two types: evolvable hardware based on genetic algorithms and bio-inspired machines.

#### 3.1.1 Digital Evolvable Hardware Based on Genetic Algorithms

This category covers work in designing digital circuits using GA. Many of the works under this category have been presented at ICES.

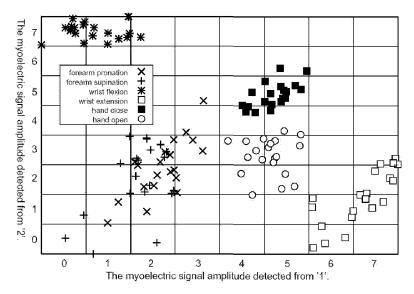

Some new methods for the evolutionary design of digital circuits have been proposed. The first evolvable hardware chip developed for myo-electric hand control is described in Chapter 3. J. Torresen (Torresen, 2001) has proposed a new evolvable hardware architecture for pattern classification including incremental evolution. He showed that the method is applicable to prosthetic hand controllers. M. Garvie, et al. (Garvie, 2003) have shown the evolution of digital circuits capable of performing built-in self-test behavior in simulations for a one-bit adder and a two-bit multiplier. Their results suggest that evolved designs can perform a better diagnosis using less resource than hand-designed equivalents. J. Korenek, et al. (Korenek, 2005) have developed and evaluated a specialized architecture to evolve relatively large sorting networks in an ordinary FPGA.

Some new and practical applications have also been studied. For instance, a lossless data compression method for bi-level images using evolvable hardware, and a clock-timing adjusting technique are described in Chapter 2 and 4, respectively. T. Martinek, et al. (Martinek, 2005) have proposed an evolvable image filter that was completely implemented in an FPGA. The system is able to evolve an image filter in a few seconds if corrupted and original images are supplied by the user. S. L. Smith, et al. (Smith, 2003) have presented an application of GA to evolve new spatial masks for nonlinear image processing operations, which are ultimately to be implemented on evolvable hardware.

Digital evolvable hardware has also been applied to evolving robot controllers. J. G. Kim, et al. (Kim, 2001) have shown that their proposed GA guarantees satisfactory smooth and stable walking behavior in an experiment involving a real biped robot. M. M. Islam, et al. (Islam, 2001) have applied an incremental approach—a two-stage evolutionary system—to develop the control system of an autonomous robot for a complex task. Harding, et al. (Harding, 2005) have discussed the stability and reconfigurability of a realtime robot controller evolved in liquid crystal. They envisage these issues will be important when programming or evolving in other physical systems.

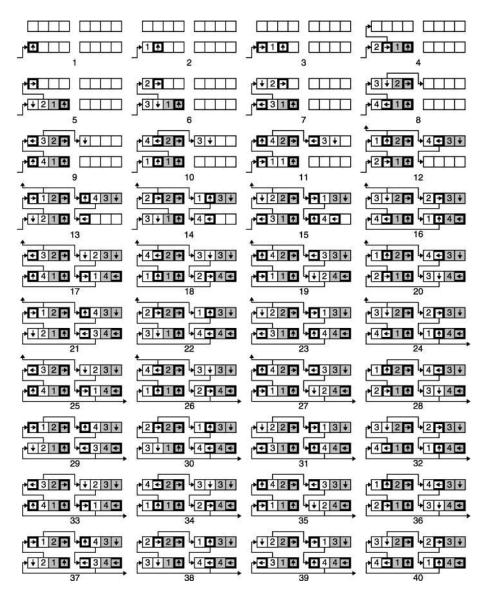

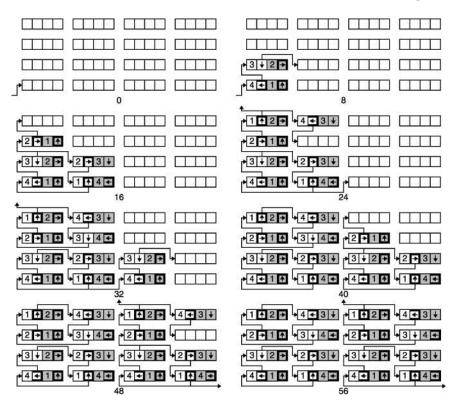

#### 3.1.2 **Bio-inspired Machines**

Under this category, many ideas for applying the biological process to evolutionary systems have been studied. This topic has been discussed since the very beginning of evolvable hardware research.

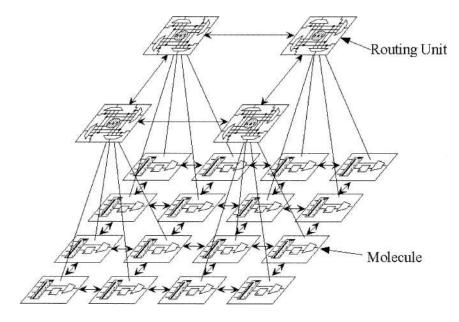

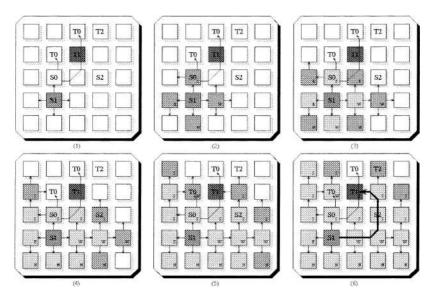

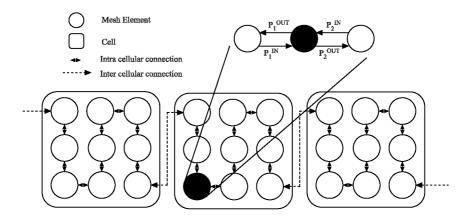

Embryonic electronics (embryonics) (Mange, 1998) is a research project that draws inspiration from the biological process of ontogeny in seeking to implement novel digital computing machines with better levels of fault tolerance. H. F. Restrepo, et al. (Restrepo, 2001) have proposed a multicellular universal Turing machine implementation that is endowed with self-replication and self-repair capabilities. L. Prodan, et al. (Prodan, 2001) have proposed artificial cells driven by artificial DNA to implement their embry-onic machines. A. Stauffer, et al. (Stauffer, 2001) have fabricated a selfrepairing and self-healing electronic watch: the BioWatch, with a system based on an array of small processors. Their recent work is described in Chapter 5.

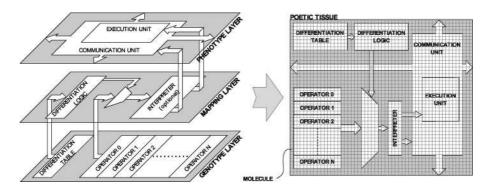

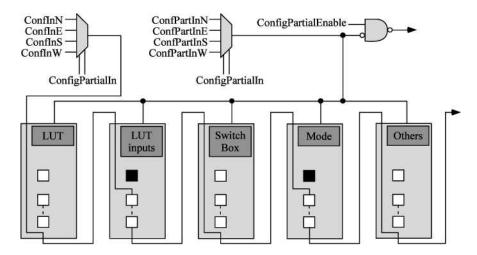

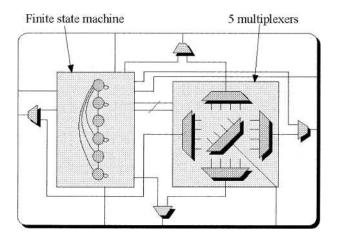

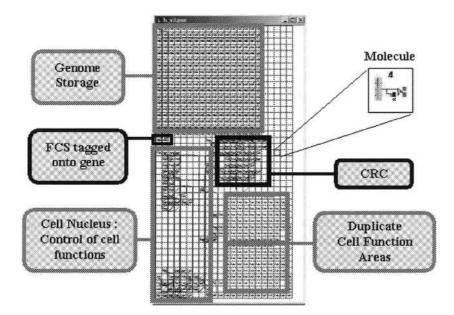

As described in Chapter 6, a new research project has also been proposed on "reconfigurable POEtic tissue." The project goal is to develop a hardware platform capable of implementing with digital hardware systems that are inspired by all three major bio-inspiration axes (phylogenesis, ontogenesis, and epigenesis). While W. Barker, et al. (Barker, 2005) have presented results of hardware fault-tolerance within the POEtic system, J. M. Moreno, et al. (Moreno, 2005) have conceived an architecture for POEtic devices, internally organizing the main constituent elements.

Some other works in this category have also been reported. For example, J. Greensted, et al. (Greensted, 2003) have proposed a software model for multiprocessor system design that uses an interprocessor communication system similar to the endocrine system. The system is able to perform arbitrary dataflow processing. P. C. Haddow, et al. (Haddow, 2001) presented the first case study using the mathematical formalism called L-systems and have applied their principles to the development of digital circuits. D. W. Bradley, et al. (Bradley, 2001) have analyzed the body's approach to fault tolerance based on immune system and have demonstrated how such techniques can be applied to hardware fault tolerance.

#### 3.2 Analog Hardware Evolution

Analog hardware evolution is a relatively newer category compared to digital hardware evolution. The two subcategories involved here are analog evolvable hardware based on genetic algorithms and analog circuit design with evolutionary computation.

#### 3.2.1 Analog Evolvable Hardware Based on Genetic Algorithms

This category covers work on designing analog circuits using GA. While there have been fewer reports on analog hardware compared to digital hardware, there has been some interesting work in this category.

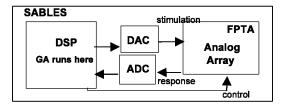

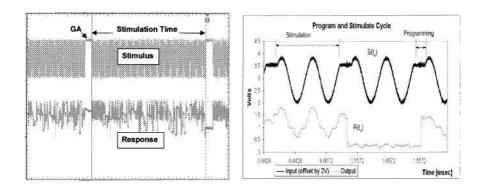

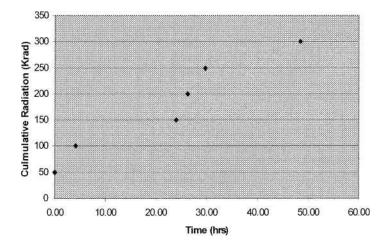

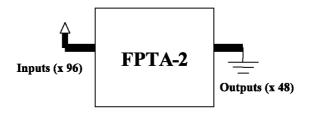

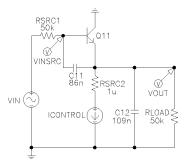

An FPTA (Field Programmable Transistor Array) is an implementation of an evolution-oriented reconfigurable architecture for evolving analog circuits. A number of interesting reported works involve FPTAs. For instance, R. S. Zebulum, et al. (Zebulum, 2003) have presented a hardware evolution of analog circuits to perform signal separation tasks using their system called Stand-Alone Board-Level Evolvable System (SABLES). SABLES integrates an FPTA-2 chip and a digital signal processor to implement the evolutionary platform. Results demonstrate that SABLES is sufficiently flexible to adapt to different input signals without human intervention. L. Sekanina, et al. (Sekanina, 2005) have reported that simple one-bit and two-bit controllable oscillators were intrinsically evolved using only four cells of FPTA-2. These oscillators can produce different oscillations for different settings of control signals. Trefzer, et al. (Trefzer, 2005) have tackled the problem of synthesizing transferable and reusable operational amplifiers on an FPTA. A multiobjective evolutionary algorithm has been developed, in order to be able to include various specifications of an operational amplifier into the process of circuit synthesis. Some recent works on FPTAs and SABLES for extreme environments are described in Chapters 8 and 9.

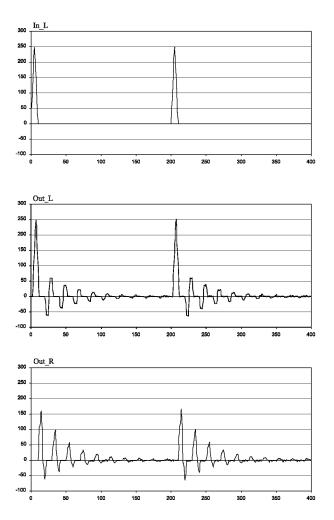

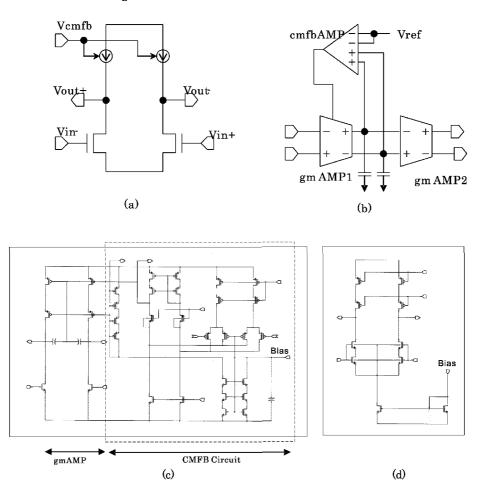

Some effective applications for analog hardware have also been studied. An analog intermediate filter LSI used in commercial cellular phones is described in Chapter 7. Y. Kasai, et al. (Kasai, 2005) have proposed adaptive waveform control in a data transceiver and demonstrated an adaptive transceiver LSI with the waveform controller. Utilizing a GA, the method has achieved a transmission speed that is four times faster than the current standards for IEEE1394. J. D. Lohn, et al. (Lohn, 1998) have proposed a method of evolving analog electronic circuits using a linear representation and a simple unfolding technique. Using a parallel GA, they have presented initial results of applying their system to two analog filter design problems.

#### 3.2.2 Analog Circuit Design with Evolutionary Computation

Within this category, evolutionary computation is used to evolve analog circuits. J. R. Koza, et al. (Koza, 1996) have proposed utilizing genetic programming for evolving analog circuits. Genetic programming is a systematic method to get computers to automatically solve problems. Genetic programming is an extension of the GA concept into the arena of computer programming. J. R. Koza, et al. have successfully evolved a design for a twoband crossover filter using genetic programming. They have also succeeded in evolving an op amp with good frequency generalization (Bennett, 1996). Their recent works are described in Chapter 10.

#### **3.3 Mechanical Hardware Evolution**

This category includes works using evolutionary algorithms to adjust machine parts. Although this is the newest category, some interesting applications have already been reported. While an evolvable femtosecond laser system is described in Chapter 11, a tuning method for MEMS gyroscopes based on evolutionary computation is explained in Chapter 12. J. D. Lohn, et al. (Lohn, 2001) have proposed a GA-based automated antenna optimization system that uses a fixed Yagi-Uda topology and a byte-encoded antenna representation. They have also succeeded in evolving new antenna designs for NASA's Space Technology 5 mission (Lohn, 2005).

# 4. PERSPECTIVES FOR EVOLVABLE HARDWARE RESEARCH

There are two promising application areas for future research on evolvable hardware. One is semiconductor engineering and the other is mechanical engineering, including MEMS. This section briefly reviews important works related to these areas.

# 4.1 Research Direction Towards Semiconductor Engineering

Although early research interests within evolvable hardware were mainly centered on artificial intelligence and artificial life, more recent evolvable hardware research is addressing important topics for semiconductor engineering. These include post-fabrication LSI adjustment, tolerance for temperature changes, waveform control for high-speed data transmission, and human-competitive analog design, as well as self-test/self-repair LSI, which is discussed briefly below.

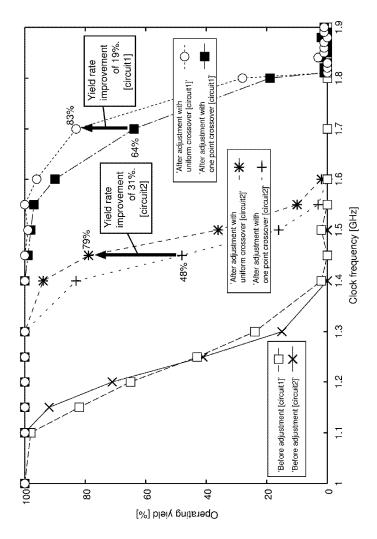

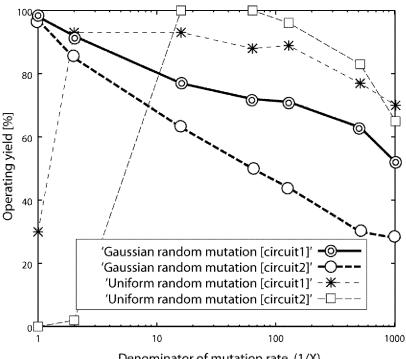

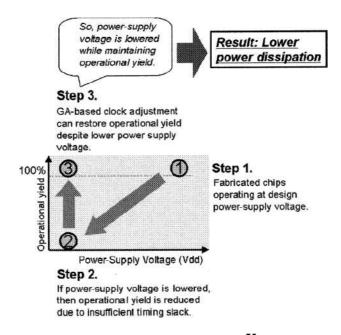

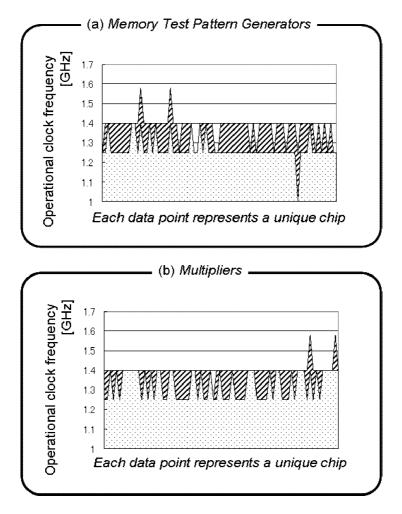

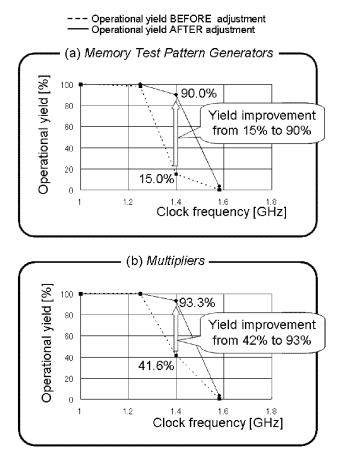

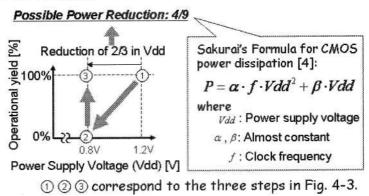

In current LSI manufacturing, degradation in the operational yield rate is a very serious problem because a poor LSI yield rate results in increased LSI costs. One of the main reasons for a poor yield rate is the variations in the LSI manufacturing processes. For example, some transistors in the LSI may not achieve the required performance (e.g., threshold voltage) due to inaccuracies in the manufacturing process. Due to such variations, it is not possible to guarantee the final performance of LSI products simply by making more elaborate LSI designs. However, one practical solution to achieving acceptable operational yield rates is post-fabrication LSI adjustment with GA (see Chapter 4). Adjustment circuitries are inserted in advance wherever yield rates might be degraded. Then, the parameters of the adjustment circuitries are determined by the GA after LSI fabrication. If the GA adjustment time and the adjustment circuitry space are sufficiently small, this approach represents a very important remedy for improving yield rates.

The capability of evolvable hardware to adapt to a changing environment is also very important for semiconductor engineering. For example, performance degradation due to temperature fluctuations can be controlled for by the GA approach. Stoica's work (NASA) and Zebulum's work (NASA) in this direction (see Chapter 8 and Chapter 9, respectively), which is based on Stoica's FPTA (see Chapter 8), is very important in this respect. While this book does not touch on the issue directly, performance for high-speed data transmission (over Giga-Hertz) is heavily influenced by noise through cable transmission. With the GA approach, however, circuitry to control the waveforms can be adjusted in order to satisfy the requirement for actual cable installations. While digital hardware design has made rapid progress due to advances in EDA software tools, analog hardware design is still highly reliant on the experience and maturity of analog hardware designers. Koza's work on analog hardware design (see Chapter 10) suggests that genetic programming can generate human-competitive analog design.

Recent LSI testing has shifted away from using LSI testers to BIST (Built-In Self Test) and BISR (Built-In Self-Repair) for the following reasons. Recent LSIs have high clock frequency over Giga-Hertz and complicated functions. While they also require a number of test pins, there are severe restrictions for these test pins, which creates problems for developing customized LSI testers. Instead of testing an LSI with dedicated LSI testers, one feasible solution that has emerged is to incorporate BIST/BISR functions with the LSI. Research on bio-inspired machines such as Stauffer's work (see Chapter 5) and Tyrrell's work (see Chapter 6) are pioneering works in this direction.

# 4.2 Research Direction Towards Mechanical Engineering

While not covered in this book, NASA's evolvable antenna is a very important work which demonstrates the potentiality of evolvable hardware. The shape of NASA's antenna is beyond the human imagination, while maintaining its required performance.

The evolvable femtosecond laser, described in Chapter 11, is another example illustrating how the evolvable hardware approach is effective for mechanical evolution. The approach allows for very precise setting of physical laser component devices. In general, high performance mechanical systems tend to be vulnerable to environmental changes such as vibrations and temperature changes. The precise physical setting of the components in terms of position and angle is key to attaining high performance, but there may be limitations with using human engineers when such systems are used in extreme environments (e.g., extreme high/low temperatures and radiation). Autonomous positioning with the GA approach can be very effective in such circumstances.

Moreover, D. Keymulen's work (NASA) is the first paper showing that the evolvable hardware approach is effective for MEMS tuning. As with manufacturing LSIs with fine patterns (i.e. submicron), there are also unavoidable fabrication inaccuracies involved with MEMS manufacturing. Following his work (see Chapter 12), further explorations of other MEMS applications utilizing the GA approach are expected.

#### References

- Barker, W. and A. M. Tyrrell. 2005. Hardware fault-tolerance within the POEtic system. In *Evolvable Systems: From Biology to Hardware, LNCS 3637*, 25-36. Springer.

- Bennett III, F. H., et al. 1996. Evolution of a 60 decibel op amp using genetic programming. In Evolvable Systems: From Biology to Hardware, LNCS 1259, 455-469. Springer.

- Bradley, D. W. and A. M. Tyrrell. 2001. Multi-layered defence mechanisms: architecture, implementation and demonstration of a hardware immune system. In *Evolvable Systems: From Biology to Hardware, LNCS 2210*, 140-150. Springer.

- Garvie, M. and A. Thompson. 2003. Evolution of self-diagnosing hardware. In *Evolvable Systems: From Biology to Hardware, LNCS 2606*, 238-248. Springer.

- Greensted, J. and A. M. Tyrrell. 2003. Fault tolerance via endocrinologic based communication for multiprocessor systems. In Evolvable Systems: From Biology to Hardware, LNCS 2606, 24-34. Springer.

- Haddow, P. C., G. Tufte and P. van Remortel. 2001. Shrinking the genotype: L-systems for EHW? In Evolvable Systems: From Biology to Hardware, LNCS 2210, 128-139. Springer.

- Harding, S. and J. F. Miller. 2005. Evolution in materio: investigating the stability of robot controllers evolved in liquid crystal. In *Evolvable Systems: From Biology to Hardware*, *LNCS 3637*, 155-164. Springer.

- Higuchi, T., et al. 1993. Evolvable hardware with genetic learning. In *Proc. of Simulated* Adaptive behavior, 417-424. MIT Press.

- Islam, M. M., S. Terao and K. Murase. 2001. Effect of fitness for the evolution of autonomous robots in an open-environment. In *Evolvable Systems: From Biology to Hardware*, *LNCS 2210*, 171-181. Springer.

- Kasai, Y., et al. 2005. Adaptive waveform control in a data transceiver for multi-speed IEEE1394 and USB communication. In *Evolvable Systems: From Biology to Hardware, LNCS 3637*, 198-204. Springer.

- Kim, J. G., K.-G. Noh and K. Park. 2001. Human-like dynamic walking for a biped robot using genetic algorithm. In *Evolvable Systems: From Biology to Hardware, LNCS 2210*, 159-170. Springer.

- Korenek, J. and L. Sekanina. 2005. Intrinsic evolution of sorting networks: a novel complete hardware implementation for FPGAs. In *Evolvable Systems: From Biology to Hardware*, *LNCS 3637*, 46-55. Springer.

- Koza, J. R., et al. 1996. Reuse, parameterized reuse, and hierarchical reuse of substructures in evolving electrical circuits using genetic programming. In *Evolvable Systems: From Biol*ogy to Hardware, LNCS 1259, 312-326. Springer.

- Lohn, J. D. and S. P. Colombano. 1998. Automated analog circuit synthesis using a linear representation. In. *Evolvable Systems: From Biology to Hardware, LNCS 1478*, 125-133. Springer.

- Lohn, J. D., et al. 2001. Evolutionary optimization of Yagi-Uda antennas. In *Evolvable Systems: From Biology to Hardware, LNCS 2210, 236-243. Springer.*

- Lohn, J. D., G. S. Hornby and D. S. Linden. 2005. Evolution, re-evolution, and prototype of an X-band antenna for NASA's space technology 5 mission. In *Evolvable Systems: From Biology to Hardware, LNCS 3637*, 205-214. Springer.

- Mange, D. 1993. Wetware as a bridge between computer engineering and biology. In Preliminary Proceedings, 2nd European Conference on Artificial Life, 658-667.

- Mange, D. 1993. Life in Silico. In 11th European Conference on Circuit Theory and Design (ECCTD '93), 145-149.

- Mange, D., A. Stauffer and G. Tempesti. 1998. Embryonics: a macroscopic view of the cellular architecture. In *Evolvable Systems: From Biology to Hardware, LNCS 1478*, 174-184 Springer.

- Martinek, T. and L. Sekanina. 2005. An evolvable image filter: experimental evaluation of a complete hardware implementation in FPGA. In *Evolvable Systems: From Biology to Hardware, LNCS 3637*, 76-85. Springer.

- Moreno, J. M., Y. Thoma and E. Sanchez. 2005. POEtic: a prototyping platform for bioinspired hardware. In *Evolvable Systems: From Biology to Hardware, LNCS 3637*, 177-187. Springer.

- Prodan, L., et al. 2001. Embryonics: artificial cells driven by artificial DNA. In Evolvable Systems: From Biology to Hardware, LNCS 2210, 100-111. Springer.

- Restrepo, H. F. and D. Mange. 2001. An embryonics implementation of a self-replicating universal turing machine. In *Evolvable Systems: From Biology to Hardware, LNCS 2210*, 74-87. Springer.

- Sekanina, L. and R. S. Zebulum. 2005. Intrinsic evolution of controllable oscillators in FPTA-2. In Evolvable Systems: From Biology to Hardware, LNCS 3637, 98-107. Springer.

- Smith, S. L., D. P. Crouch and A. M. Tyrrell. 2003. Evolving image processing Operations for an evolvable hardware environment. In *Evolvable Systems: From Biology to Hardware*, *LNCS 2606*, 332-343. Springer.

- Stauffer, A., et al. 2001. A self-repairing and self-healing electronic watch: the BioWatch. In *Evolvable Systems: From Biology to Hardware, LNCS 2210*, 112-127. Springer.

- Torresen, J. 2001. Two-step incremental evolution of a prosthetic hand controller based on digital logic gates. In *Evolvable Systems: From Biology to Hardware, LNCS 2210*, 1-13. Springer.

- Trefzer, M., et al. 2005. Operational amplifiers: an example for multi-objective optimization on an analog evolvable hardware platform. In *Evolvable Systems: From Biology to Hardware, LNCS 3637*, 86-97. Springer.

- Yao, X. and T. Higuchi. 1999. "Promises and challenges of evolvable hardware", *IEEE Trans. Systems, Man, and Cybernetics, C* 29(1), 87-97.

- Zebulum, R. S., et al. 2003. Automatic evolution of signal separators using reconfigurable hardware. In *Evolvable Systems: From Biology to Hardware, LNCS 2606*, 286-295. Springer.

# Chapter 2

# EHW APPLIED TO IMAGE DATA COMPRESSION

Hidenori Sakanashi, Masaya Iwata, and Tetsuya Higuchi MIRAI Project, Advanced Semiconductor Research Center (ASRC), National Institute of Advanced Industrial Science and Technology (AIST) {h.sakanashi, m.iwata, t-higuchi}@aist.go.jp

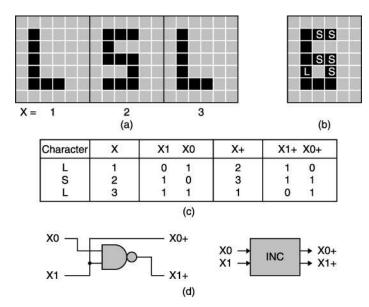

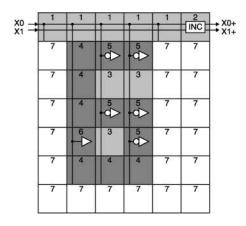

- Abstract: In this chapter, EHW is applied to the lossless image compression, and it is implemented in a chip. The current international standard for bi-level image coding, JBIG2-AMD2, is modified by the proposed method to achieve high compression ratios, where compression parameters are optimized by the enhanced genetic algorithm (GA). The results of computer simulations show a 171% improvement in compression ratios with the proposed method compared to JBIG2 without optimization. The experiment shows that when the method is implemented by hardware with an evolvable hardware chip, the processing speed is dramatically faster than execution with software. This chapter also describes activities concerning ISO standardization to adopt part of the technology used in this method to the JBIG2 standard.

- Key words: data compression, JBIG2 (Joint Bi-level Image experts Group, 2), ISO/IEC standard, EHW chip.

#### **1. INTRODUCTION**

Since the emergence of Desk Top Publication (DTP) in the graphic (imaging, printing and publishing) industry, digital image data has been handled in many ways, such as with digital printers, on-demand printing/publishing (ODP), and so on. On the other hand, the large costs for storage and transfer of an enormous amount of huge images have become a serious problem. For example, the electrophotographic printer must have the large storage and the broad data-bus to process many high-resolution images quickly. In the case To overcome these problems, image data must be compressed as much as possible and must be restored to its original state very quickly. Unfortunately, traditional data compression methods cannot satisfy these requirements, because the image data used in the printing/publishing industry have distinctive characteristics.

In this chapter, Evolvable Hardware (EHW) is applied to a data compression system. The proposed method has the following 4 features; (1) adoption of JBIG2 (ISO/IEC Int. Stand. 14492, 2001), the latest international standard, as basis, (2) introduction of a simplified initialization procedure for effective analysis in the genetic algorithm (GA) (Holland, 1975), (3) simplification of the evaluation procedure, and (4) enhanced crossover operations. The results of computer simulations show that the proposed method has a compression ratio that is 171% better than that of JBIG2 without optimization.

We have developed an EHW chip for the proposed method. The result of an experiment using the chip has demonstrated that the compression ratio is higher than for conventional data compression chips, and, moreover, that the speed is dramatically faster than with software execution.

# 2. LOSSLESS COMPRESSION OF HIGH-RESOLUTION GRAPHIC ART IMAGES

# 2.1 Image Data for Graphic Arts

In general graphic arts technology, color images are basically transformed into four high-resolution bi-level images before going to press, because press machines can only represent two levels (inked or not-inked). These bi-level images correspond to four colors (cyan (C), magenta (M), yellow (Y) and black (K)). Differences in brightness are represented by varying the density and size of the ink dots, known as halftone dots, which are composed from bi-level pixels located on a fixed rectangular grid.

Thus, the graphic arts images have the following features:

- Sets of bi-level images,

- Very high resolution, and

- Large frequency with which the pixel values switch is high in both the horizontal and vertical directions of a raster scan.

Traditionally, because the image data must be compressed in lossless fashion (reversibly) to avoid distortion or degradation in press quality, MH (Modified Haffman), MR (Modified Read) (CCITT Recommendation T.4, 1998) and MMR (Modified Modified Read) (CCITT Recommendation T.6, 1998) methods, which are well-known international standards for facsimile, have been used for encoding. These methods are based on run-length coding. MH uses a one-dimensional model, while a two-dimensional model is adopted in MR and MMR (the principle in MMR is the same as that in MR, but some error correction mechanisms are eliminated to achieve higher compression efficiency). These methods provide fairly good compression for line-art or text images. However, these methods are unsuitable for data where the switching frequency for pixel values is high, like halftone images, because they code the positions where pixel values are switched for each line.

In contrast, JBIG, a template-based arithmetic coding method (Sayood, 2000), was a general-purpose compression method for bi-level images, and JBIG2 (ISO/IEC Int. Stand. 14492, 2001) was standardized as its successor in 2000. JBIG2 was designed to upgrade the lossless JBIG encoding method and to add a lossy compression mode based on pattern matching. As lossy encoding is not relevant to the compression of graphic art images, this chapter focuses only on the lossless encoding mode in JBIG2.

#### 2.2 Lossless Image Compression with JBIG2

The template-based arithmetic coding method is based on the hypothesis that the probability of a given "pixel to be coded" having a specific value depends on the values of a limited number of preceding pixels. In JBIG2, the MQ-Coder is adopted as an arithmetic coder; we shall limit our discussion here to this template-based coding method because a detailed explanation of the MQ-Coder would be beyond the scope of this chapter (the principle of arithmetic encoding and the procedure for the MQ-Coder are detailed in (Sa-yood, 2000) and (ISO/IEC Int. Stand. 14492, 2001), respectively).

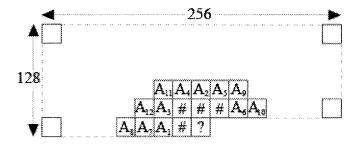

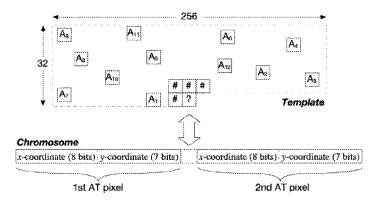

In JBIG2 and its enhanced version called JBIG2-AMD2 (ISO/IEC Int. Stand. 14492/Amd.2, 2003), 16 pixels preceding the pixel to be coded are observed in calculating the probability that it takes a specific value  $\{0, 1\}$ . This probability is used to predict the values of the pixels to be coded, and the accuracy of prediction strongly influences the compression efficiency. Here, these observed pixels are called "reference pixels," and the configuration of their positions is called a "template." Figure 2-1 is a diagram of the template consisting of 16 reference pixels used by JBIG2-AMD2. The question mark in the figure represents the pixel to be coded and is not part of the template. While the positions for the 4 reference pixels are fixed, as marked with a #, there are also 12 special reference pixels called the adaptive template (AT) pixels, indicated in the figure as  $A_i$  {i = 1, ..., 12}. AT pixels can arbitrarily change positions within the range marked by the dotted line to achieve higher prediction accuracy and, in turn, higher compression efficiency.

However, it is a very difficult problem to optimize AT pixels according to the characteristics of images to be compressed. Therefore, the next section proposes an extended GA to optimize the configuration of the template of JBIG2-AMD2 quickly and efficiently.

Figure 2-1. Default configuration of JBIG2-AMD2 template

# 3. EXTENDED GA FOR TEMPLATE OPTIMIZATION

Since the basics and procedures of GA are already described in the previous chapter, this chapter shows some of the modifications and enhancements for the problem of optimizing the JBIG2 templates.

# 3.1 Coding of Chromosomes and Initialization of a Population

As each AT pixel exists within an area of  $256 \times 128$ , as shown in Figure 2-1, its location can be specified by 15 bits. If the number of AT pixels is M, then the total length of a chromosome is 15M bits. The enhanced template proposed in this chapter has 12 AT pixels, so the length of the chromosome is  $180 \ (=15 \times 12)$  bits, as shown in Figure 2-2. In the computational simulation described later, the population consists of 30 chromosomes.

An initial population is usually generated at random, although some GAs adopt a kind of biased initialization, based on certain information related to the problem. For example, in our previous method, the initial population was generated from a seed template by a mutation operation that was derived from a multiple regression analysis (Sakanashi, 2001). However, the computational complexity of the multiple regression analysis was enormous. Accordingly, in this chapter, the seed template is determined by assigning reference pixels one by one based on their degree of correlation to the pixel to be coded. In order to calculate the degree of correlation between the pixel to be coded and each candidate AT pixel, it is necessary to scan the entire image to check whether the pixels are of the same value. Defining image size as XY, because the number of AT pixel candidates is approximately  $256 \times 128$ , the number of observations and comparisons required will be XY  $\times 256 \times 128$ . When the image size is small, the number of calculations would not pose a major problem. However, because graphic art images have very high resolutions, this number becomes extremely large. For example, as an A4 image with a resolution of 2400 dpi consists of roughly 20000  $\times$  28000 pixels, approximately  $1.8 \times 10^{13}$  observations and comparisons would be needed to calculate the correlations.

Thus, to reduce the number of comparisons between pixel values, the degree of correlation is only checked for pixels to be coded, which are stochastically selected at a probability  $P_{\text{scan}}$ , and the respective candidate AT pixels. Investigating this  $P_{\text{scan}}$  probability in a second preliminary experiment, we found that a template of sufficient quality to serve as the seed template in initializing the population can be obtained with  $P_{\text{scan}} = 5000/XY$ , which is the  $P_{\text{scan}}$  value used in this chapter.

In the proposed method, one chromosome in the initial population is the bit string representing this seed template, with the remaining chromosomes being created by mutating this chromosome at twice the mutation rate to be explained later.

Figure 2-2. Coding of chromosomes

#### **3.2 Random Partial Evaluation**

As the objective function to calculate the fitness value of a chromosome, the proposed method uses the inverse of the compressed data size achieved by the template represented by the chromosome. Thus, a chromosome representing a good template that compresses the image data well will have a higher fitness value.

Incidentally, although it would be possible from an information theory perspective to use entropy as the fitness value rather than the compressed data size, there are two reasons, examined in preliminary experiments, for not doing so: (1) there are no significant differences between the costs for executing the MQ-Coder and for calculating entropy. (2) As the MQ-Coder can dynamically learn the statistics of the given data sequence, the template with the lowest entropy calculated in a static way does not always yield the maximum compression ratio.

Employing the compressed data size for evaluation, however, means that the image data must be repeatedly compressed to obtain the fitness value for each chromosome. The number of times the image data must be compressed will be  $N \times G$  times, where N is the population size and G is the number of generations until the termination. Although the easiest way to reduce the evaluation costs is to only use a small part of the image rather than the entire image, evaluation accuracy and the reliability of the fitness value would deteriorate, making it impossible to discover the best template yielding the greatest compression efficiency.

Accordingly, this chapter proposes a procedure to solve this problem, consisting of the following two steps:

- Evaluation of the chromosomes is carried out using a small area of the entire image. The location of this area is changed at random, if a new best chromosome fails to emerge in the population within a given generation interval, G<sub>interval</sub>. (If the location of the area is changed at every generation, the GA will fail because it cannot cope with such drastic fluctuations in the evaluation criteria.)

- When a new best chromosome does emerge, a hillclimb search is executed with this chromosome as the starting point. To avoid over-fit to the small area of the image, in the hillclimb search the pixels for evaluation are chosen from the entire image at a probability P<sub>SamplePixel</sub>.

In this chapter, this procedure is referred to as "random partial evaluation," and the computational simulation described later uses the following parameters:  $G_{interval} = 20$ ,  $P_{SamplePixel} = 0.005$ , and an area size of  $1024 \times 1024$  pixels.

#### **3.3** Genetic Operations with Template Crossover

This section proposes a new crossover operator suitable for template optimization. For other genetic operators, this chapter adopts existing methods such as tournament selection (Goldberg, 1991) and bit-wise point mutation. In the computational simulation in the next section, 80% of the chromosomes are chosen by tournament selection with a tournament size of 2, and the mutation ratio is 1/180.

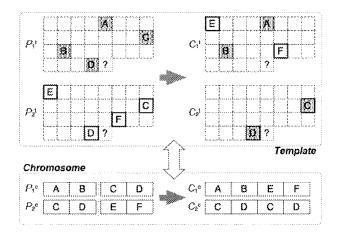

In the template representation, there is no notion of order for the reference pixels. That is, if the AT pixels A1 and A2 in Figure 2-2 were exchanged, we would obtain the same compressed data. However, the pixels must be arranged in a certain order within the chromosome representation and this causes a serious problem.

If a simple 1-point crossover method is used, chromosomes with common reference pixels are frequently generated. For example, Figure 2-3 illustrates a case where the chromosomes C1 and C2 are generated by the 1-point crossovers of P1 = A|B|C|D and P2 = C|D|E|F. These chromosomes represent the templates PT1 and PT2, consisting of the set of reference pixels {A, B, C, D} and {C, D, E, F}, respectively. With the crossover point between the second and third pixels, one child, C2 = C|D|C|D, would unfortunately contain only two unique reference pixels, as shown as CT2 in the figure. Because the compression ratio generally tends to be higher when the number of pixels is larger, a chromosome representing a template with overlapping reference pixels will have a poorer evaluation.

Thus, in this chapter, we propose a special crossover procedure called template crossover, as follows:

- 1. A pair of chromosomes, P1 and P2, is compared to identify any common reference pixels, P<sub>common</sub>.

- 2. If present, common reference pixels are removed from P1 and P2, respectively, to produce P1' and P2'.

- 3. If the lengths of P1' and P2' are 0, P2 is mutated and the process is terminated.

- 4. Otherwise, reference pixels in P1' and P2' are exchanged in a fashion similar to bit-wise uniform crossover, with the results being defined as P1" and P2".

- 5. Finally, P<sub>common</sub> is concatenated at the ends of both P1" and P2", with the results overwriting the original P1 and P2, respectively.

The check in step 3 for the lengths of P1' and P2' ensures that identical templates never appear in the population. Moreover, this elimination of redundancy efficiently reduces the search space and so contributes to improve GA search efficiency. Because a template with *m* reference pixels can be represented in  $({}_mP_m = m!)$  different ways as chromosomes, the number of redundant evaluations is greatly reduced by removing identical chromosomes.

The parameters of the proposed method mentioned above are summarized in Table 2-1.

Figure 2-3. Example of a template with overlapping AT pixels being generated by a one-point crossover operation

| Table 2-1. Parameter settings   |                         |

|---------------------------------|-------------------------|

| Population size                 | 30                      |

| Length of chromosome            | 180                     |

| Max generation                  | 10000                   |

| Selection method                | Tournament selection    |

| Crossover method                | Template crossover      |

| Crossover ratio                 | 0.8                     |

| Mutation method                 | Bit-wise point mutation |

| Mutation rate                   | 1/180                   |

| P <sub>scan</sub>               | 5000/[Image size]       |

| Sample area size for evaluation | $1024 \times 1024$      |

| Ginterval                       | 20                      |

| P <sub>SamplePixel</sub>        | 0.005                   |

# 4. COMPUTATIONAL SIMULATIONS

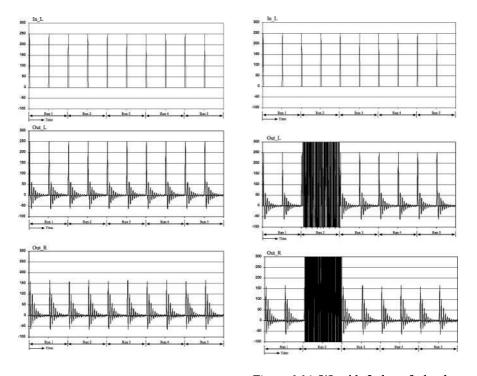

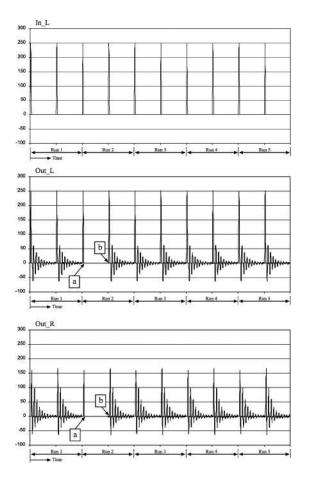

This section presents the results of the computational simulations executed to examine the performance of the proposed method. This experiment used a set of test images containing the cyan and magenta images of N5, N6 and N8 in SCID (ISO/IEC Int. Stand. 12640, 1997), which were processed by raster image processor (RIP) to decompose the color image into the four bi-level images and to increase the resolution to 2400 dpi. They were chosen as a test image because they have the medium, smallest and greatest entropy levels of the eight images in SCID. Similarly, the cyan and magenta image has a larger level of entropy than the yellow and black images. Firstly, to verify the effect of extending the GA for template optimization, an experiment was carried out with the 4 conditions shown in Table 2-2, using only the cyan N8 image.

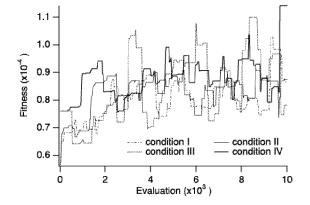

Figure 2-4 shows a graph plotting the mean best fitness values achieved in 3 runs for each condition. As the evaluation areas changed at random periods, the fitness values fluctuated sharply, making it difficult to differentiate the performances across the 4 conditions.

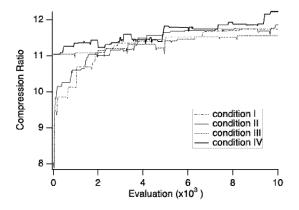

The graph in Figure 2-5 plots the compression ratios rather than the fitness values, and Figure 2-6 is a close-up of Figure 2-5. These show that compression ratios improved as the GA search progressed, which is almost saturated within 1000 evaluations in every condition, and one of our future tasks would be to develop the appropriate termination criteria.

Looking at the contrast between the pairs of conditions [i]+[iii] and [ii]+[iv], which differ in terms of whether initialization was based on correlation analysis, the fact that the results for [iii] and [iv] are respectively better than [i] and [ii] indicates that the proposed population-initialization method effectively boosts the search performance of the GA.

Moreover, we can observe that the results for [ii] and [iv] are better than [i] and [iii] even though the initial populations were the same for the pairs of conditions ([i]+[ii] and [iii]+[iv]). This fact demonstrates the efficiency of the template crossover operator, which was adopted in the conditions [ii] and [iv] but not in conditions [i] and [iii].

Table 2-3 provides the results of the simulations executed to compare the performances of (1) JBIG2-AMD2 with the default template, (2) our method only with the initialization, and (3) the complete proposed method with the enhanced GA (condition [iv]). This table shows that the proposed method can achieve much better compression ratios than the default state of JBIG2-AMD2.

Additionally, the compression ratio achieved by the initialization-only method is about  $16.6\% \sim 99.7\%$  better than JBIG2-AMD2 with the default template, although there is little difference between them in terms of computational costs. We can say that, from the viewpoint of practical use, it is a very reasonable performance in terms of compression efficiency and processing speed.

| Tuble 2-2. Simulation conditions as a function of the proposed genetic operators |     |                    |      |

|----------------------------------------------------------------------------------|-----|--------------------|------|

|                                                                                  |     | Template crossover |      |

|                                                                                  |     | OFF                | ON   |

| Initialization with                                                              | OFF | [i]                | [ii] |

| correlation analysis                                                             | ON  | [iii]              | [iv] |

Table 2-2. Simulation conditions as a function of the proposed genetic operators

|      |          | JBIG2-AMD2         | Proposed method       |                  |

|------|----------|--------------------|-----------------------|------------------|

|      |          | (Default template) | (Initialization-only) | (Condition [iv]) |

| N5   | С        | 6.58               | 9.47 (+44.0%)         | 10.82 (+64.5%)   |

|      | Μ        | 6.42               | 8.88 (+38.4%)         | 9.90 (+54.3%)    |

| N6   | С        | 6.10               | 12.18 (+99.7%)        | 16.58 (+171.9%)  |

|      | Μ        | 5.56               | 10.30 (+85.3%)        | 13.34 (+140%)    |

| N8   | С        | 4.99               | 5.90 (+18.3%)         | 6.51 (+30.5%)    |

|      | Μ        | 5.15               | 6.00 (+16.6%)         | 6.49 (+26.1%)    |

| Proc | ess time | 33 sec.            | 45 sec.               | 1.2 hours        |

Figure 2-4. Learning curve

Figure 2-5. Improvements in compression ratios

Figure 2-6. Improvements in compression ratios (close-up)

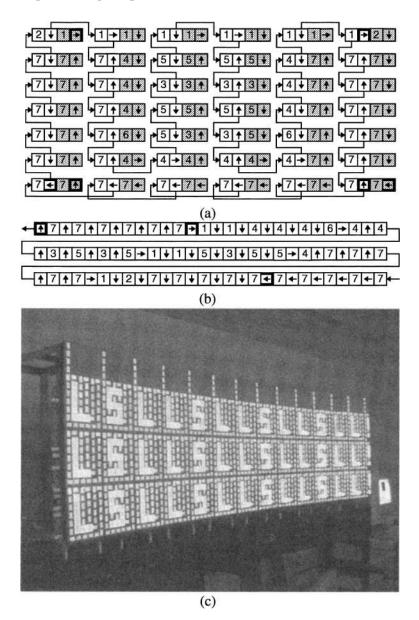

#### 5. IMPLEMENTATION OF THE EVOLVABLE HARDWARE

As described in the previous section, our proposed method provides very high compression efficiency. However, from the practical perspective of use in the graphic industry, it is also necessary to implement high-speed compression/decompression because the data for the graphic art images handled by this method is huge. In this section, we explain the implementation of evolvable hardware (EHW) to speed up this method.

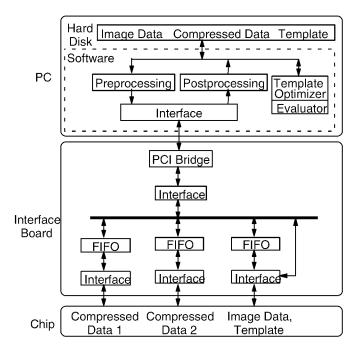

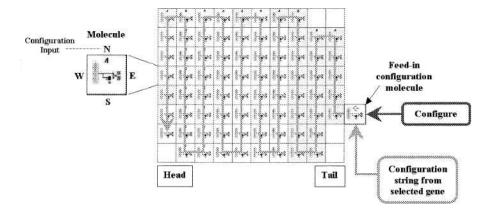

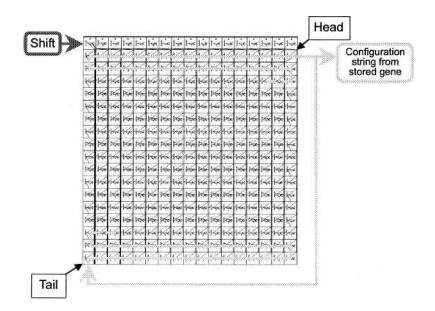

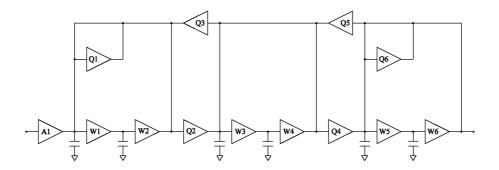

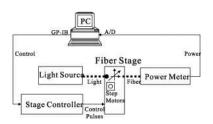

#### 5.1 Architecture

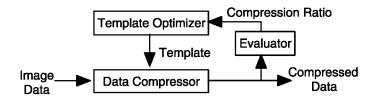

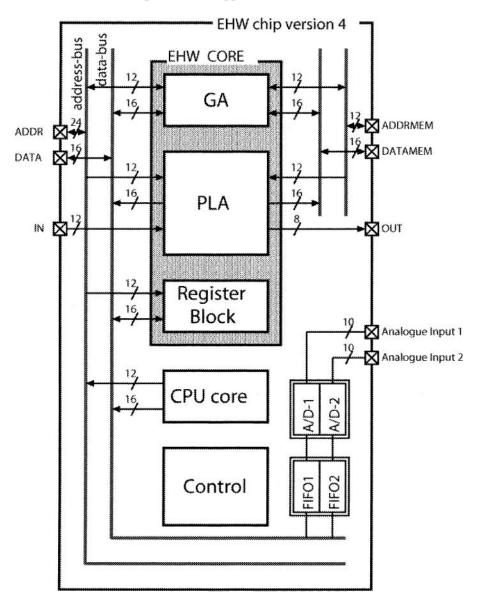

The data compression EHW chip consists of a template optimizer, a data compressor, and an evaluator, as shown in Figure 2-7. In this implementation, both template optimization and evaluation are executed on the host PC. We adopted this kind of implementation because the systems that would employ our proposed compression method, e.g. electrographic printers, are equipped with the latest CPUs that can execute these procedures sufficiently and quickly for practical use. Moreover, processing with high flexibility becomes possible by executing optimization and evaluation on a PC. In addition, when our compression technique is in practical use on electrographic printers, only fast compression and decompression are required. In most cases, optimization and evaluation are executed in advance before the equipment is manufactured, and then the results are embedded in the equipment. For these reasons, this chip is optimized for practical use.

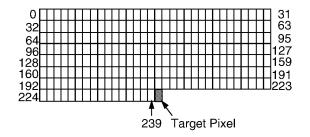

In the trial chip, which we discuss in this section, the area of the template is limited to  $32 \times 8$  pixels with 10 reference pixels (Figure 2-8). In this case, 8 bits are required to specify the location of each reference pixel, so a template can be represented by 80 bits.

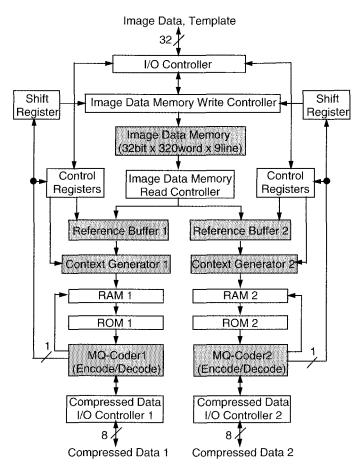

A block diagram of the chip is shown in Figure 2-9. The chip mainly consists of an MQ-Coder (ISO/IEC Int. Stand. 14492, 2001), which is the encoder/decoder, an image data memory that stores the input data, a reference buffer, and a context generator (shown as the hatched areas in Figure 2-9).

In order to execute the encoding/decoding procedures in parallel, and thus speed up processing, a feature of this architecture is the incorporation of two MQ-Coders.

The specifications of the sample chip are shown in Table 2-4, and a layout image of the chip is shown in Figure 2-10.

Figure 2-7. Configuration of the data compression system for our method

Figure 2-8. The area of the template in the chip

### 5.2 Elements of the Chip

#### 5.2.1 Image Data Memory

The image data memory stores each line of the image data so that the reference buffers can extract reference areas efficiently from the image data. The size of this memory is 320 words  $\times$  32 bits  $\times$  9 lines. Each line in the memory holds one line of image data. If a line of image data is longer than a line of memory, then the image data line is divided into memory-line length units at preprocessing. The PC accesses the memory in 32-bits groups. The lines are updated whenever a process is completed. Accordingly, this memory always holds the areas for extraction by the reference buffers. The memory is divided into two groups at the middle of each line, which are used by reference buffer 1 and 2, respectively.

Figure 2-9. Block diagram of the chip

Figure 2-10. Layout image of the chip

| Table 2-4. | Sample | chip | specifications |

|------------|--------|------|----------------|

|------------|--------|------|----------------|

| Technology            | 0.18µm CMOS                   |  |  |

|-----------------------|-------------------------------|--|--|

| Package               | 160 pin QFP plastic           |  |  |

| Die Size              | 5.14 mm × 5.19 mm             |  |  |

| Gate Count            | about 56,000                  |  |  |

| Clock Frequency       | 133 MHz (maximum)             |  |  |

| Supply Voltage        | 1.8 V (internal), 3.3 V (I/O) |  |  |

| Acceptable Image Size | 10,240 × 65,536 (maximum)     |  |  |

|                       |                               |  |  |

#### 5.2.2 Reference Buffer

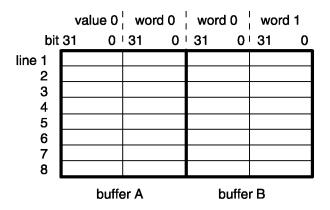

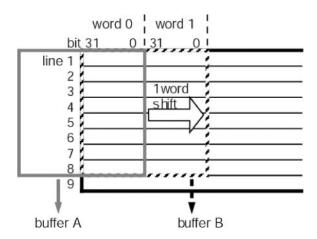

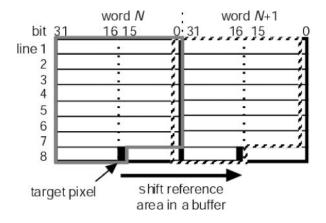

The reference buffers are buffers for the reference areas of the templates. This chip has two buffers corresponding to the two MQ-Coders. Each reference buffer has two buffers of 64 bits  $\times$  8 lines, as shown in Figure 2-11. The data stored in the buffer represents the reference area of a template and is extracted from the image data memory (Figure 2-12). In the extraction procedure, the data is extracted by shifting the reference area in one-word (32 bits) increments, with each data set being stored into buffers A and B in turn. At the edge of an image, the data is clipped so that one-word of data protrudes from the edge, as shown in Figure 2-12. Data outside the image border is set with a pixel value of 0. The data assigning each column, as shown at the top of Figure 2-11, is used to match the data into the columns in Figure 2-12. The data is clipped in this way in order to efficiently process the data across each word. For example, a reference area crossing the border of the image would be processed with the data in the buffer A in Figure 2-11. and an area covering word0 and word1 would be processed with the data in the buffer B. The buffers are updated after the processes using the buffers are complete.

Figure 2-11. A reference buffer

Figure 2-12. Extraction of reference data from the image data memory

#### 5.2.3 Context Generator

The context generator generates a context (10 bits) from a template stored in the register and the data for a reference area in the reference buffer. A context, which is used by MQ-Coder, is the values of the 10 reference pixels for a template. The circuit mainly consists of 10 multiplexers of 240-inputs and 1-output. The multiplexer extracts the pixels specified by the template from the 240 pixels in the reference area of the template (Figure 2-8).

In this method, because the circuit in the context optimizer is optimized for each image, a template is selected in the learning mode as being optimal for that image. Thus, in this system the context optimizer has the same role as the reconfigurable device in EHW.

#### 5.2.4 Encoder/Decoder (MQ-Coder)

The encoder/decoder used here is the same as that in the international standard for bi-level image encoding, JBIG2. It executes arithmetic encoding using pairs of context (10 bits) and a pixel value (1 bit). The circuit is based on the specification of JBIG2 (ISO/IEC Int. Stand. 14492, 2001) and JBIG2-AMD2 (ISO/IEC Int. Stand. 14492/Amd.2, 2003). The chip has two MQ-Coders executed in parallel. The RAM and the ROM placed in front of each MQ-Coder are also defined in the JBIG2 specifications.

#### 5.2.5 Other Components

There is an I/O controller for the data I/O control between the chip and the PC. A shift register is used in decompression to send the decompressed data immediately into the image data memory and the reference buffers.

## 5.3 Execution Procedure

#### 5.3.1 Compression

The procedure for compressing one image is as follows:

- (1) Set a template in the control register.

- (2) Set image data in the image data memory.

- (3) Compress the data for one line. (The subprocedure is shown in (a) (e).)

- (a) Clip data of 64 bits  $\times$  8 lines from the beginning of the image data memory and store in the reference buffer. Assign a pixel value of 0 for out of image areas (Figure 2-12).

- (b) Extract 10 pixels as directed by the template from the reference data in the reference buffer using the context optimizer.

- (c) The context (10 bits) and the image data (1 bit) are sent to the MQ-Coder (encoder part) via the RAM and the ROM. The encoded data are sent to the I/O controller.

- (d) Iterate (b) (c) for the data in one buffer of the reference buffer. In this procedure, the reference area is shifted by 1 bit from the beginning to the end of the buffer, as shown in Figure 2-13.

- (e) Iterate (a) (d) for the data of one line.

- (4) Iterate (2) (3) and send the compressed data into the I/O controller. The data is picked up from the external PC.

Figure 2-13. Shift of reference area in a reference buffer

#### 5.3.2 Decompression

The procedure for decompressing one image is as follows:

- (1) Set a template in the control register. Set all data in the image data memory to 0.

- (2) Set the compressed data in the compressed data I/O controller.

- (3) Decompress the data for one line. (The subprocedure is shown in (a)-(e).)

- (a) Clip data of 64 bits  $\times$  8 lines from the beginning of the image data memory and store in the reference buffer. A pixel value of 0 represents either an out of image area or a pixel that is not decompressed yet.

- (b) Extract 10 pixels directed by the template from the reference data in the reference buffer using the context optimizer.

- (c) The context (10 bits) and the compressed data (8 bit) are sent to the MQ-Coder (decoder part) via the RAM and the ROM. The decoded data is sent to the reference buffer and the image data memory via the shift register.

- (d) Iterate (b) (c) for the data in a buffer in the reference buffer. In this procedure, the reference area is shifted by 1 bit from the beginning to the end of the buffer, as shown in Figure 2-13.

- (e) Iterate (a) (d) for the data of one line.

- (4) Iterate (2) (3) and send the decompressed data into the image data memory. The data are picked up from the external PC.

#### 5.4 **Performance Evaluation**

#### 5.4.1 Evaluation System

We have conducted an experiment to evaluate compression and decompression performance. The architecture of the evaluation system is shown in Figure 2-14. The system consists of a PC, an interface board, and the chip.

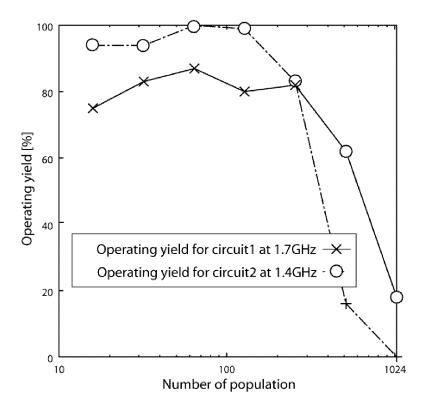

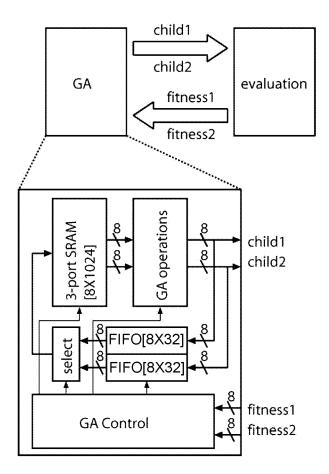

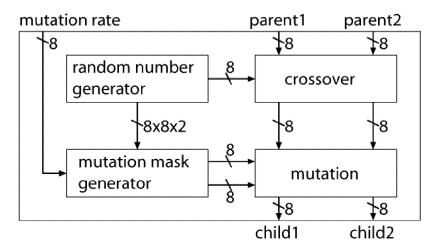

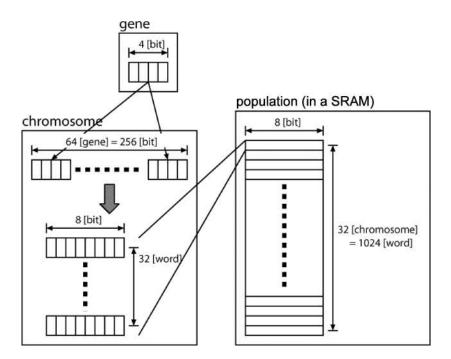

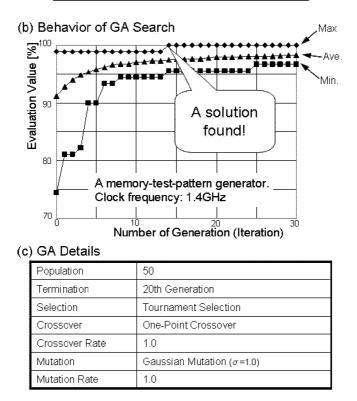

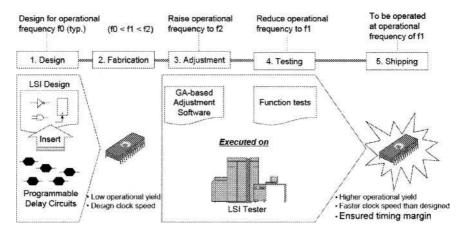

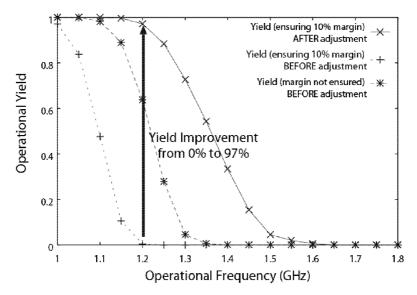

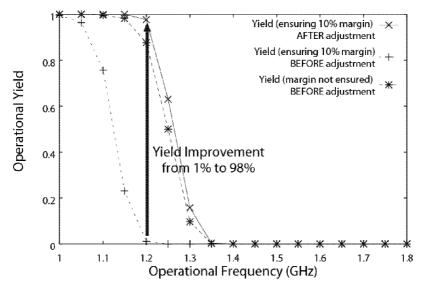

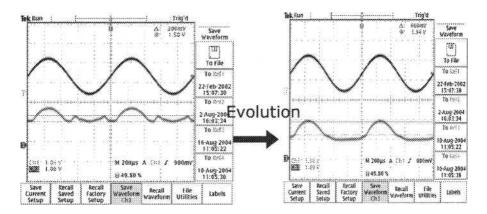

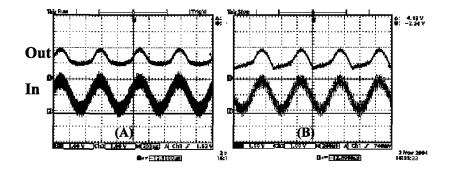

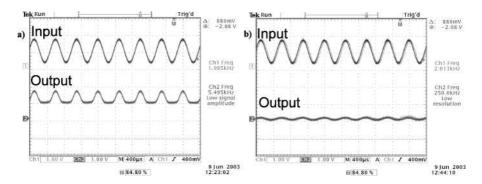

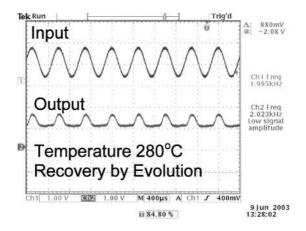

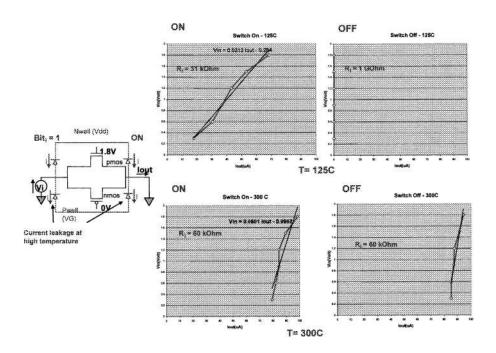

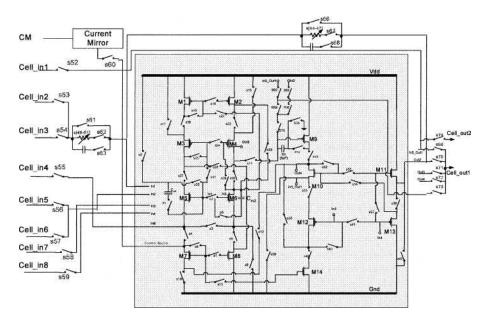

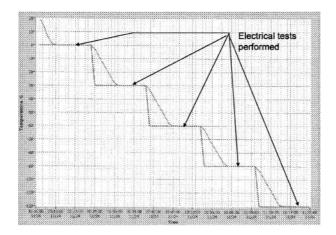

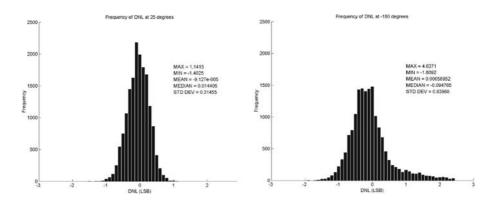

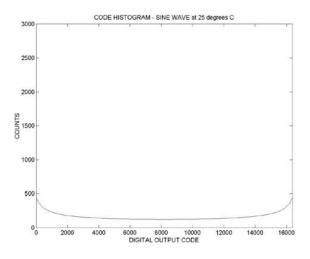

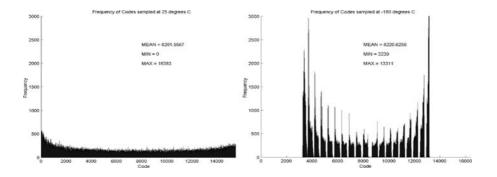

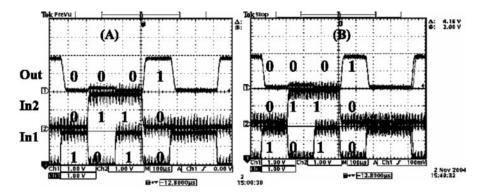

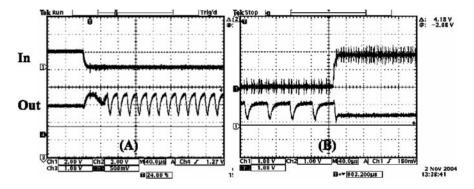

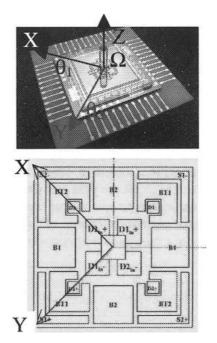

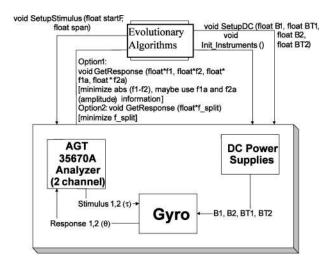

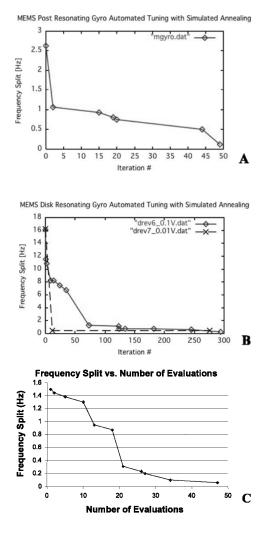

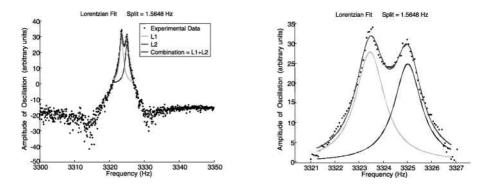

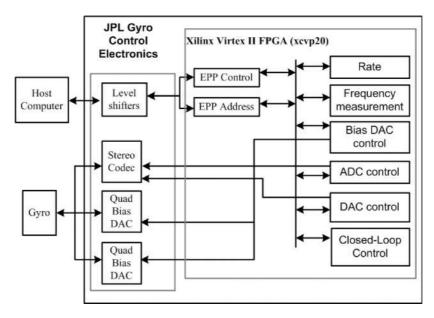

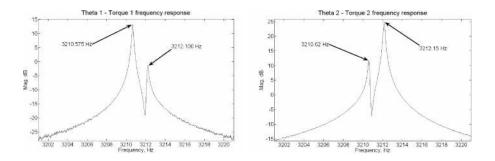

The PC has a hard disk and software. The hard disk stores the input and output data. The original data before compression is stored in TIFF format. The software mainly consists of I/O preprocessing and postprocessing, the interface between the board and the PC, the template optimizer, and the evaluator. The I/O preprocessing includes data reading and format conversion. The postprocessing executes header-making and combining compressed data in compression, as well as combining expanded data and conversion into TIFF format in decompression, and writing data into a file. The interface board executes the interface processing between the chip and the PC.