DEVICES, CIRCUITS, & SYSTEMS SERIES

# Energy Efficient Computing & Electronics

Devices to Systems

Edited by Santosh K. Kurinec Sumeet Walia

## Energy Efficient Computing & Electronics

#### Devices, Circuits, and Systems

#### **Series Editor**

*Krzysztof Iniewski* Emerging Technologies CMOS Inc. Vancouver, British Columbia, Canada

#### PUBLISHED TITLES: 3D Integration in VLSI Circuits: Implementation Technologies and Applications Katsuyuki Sakuma

Advances in Imaging and Sensing Shuo Tang and Daryoosh Saeedkia

Analog Electronics for Radiation Detection Renato Turchetta

Atomic Nanoscale Technology in the Nuclear Industry Taeho Woo

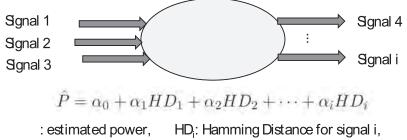

Biological and Medical Sensor Technologies Krzysztof Iniewski

Biomaterials and Immune Response: Complications, Mechanisms, and Immunomodulation Nihal Engin Vrana

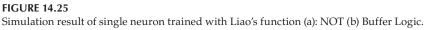

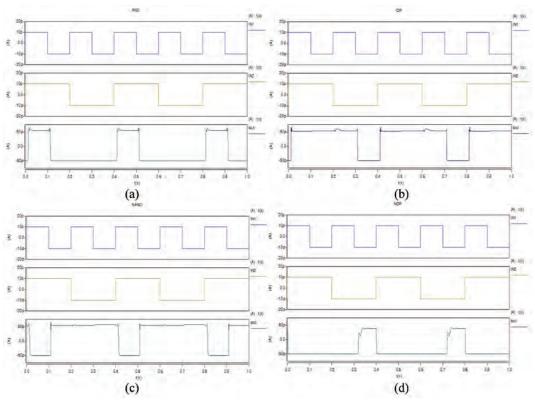

Building Sensor Networks: From Design to Applications Ioanis Nikolaidis and Krzysztof Iniewski

Cell and Material Interface: Advances in Tissue Engineering, Biosensor, Implant, and Imaging Technologies Nihal Engin Vrana

> **Circuits and Systems for Security and Privacy** *Farhana Sheikh and Leonel Sousa*

Circuits at the Nanoscale: Communications, Imaging, and Sensing Krzysztof Iniewski

> CMOS: Front-End Electronics for Radiation Sensors Angelo Rivetti

CMOS Time-Mode Circuits and Systems: Fundamentals and Applications

Fei Yuan

Design of 3D Integrated Circuits and Systems Rohit Sharma

**Diagnostic Devices with Microfluidics** *Francesco Piraino and Šeila Selimović*

**Electrical Solitons: Theory, Design, and Applications** David Ricketts and Donhee Ham

> Electronics for Radiation Detection Krzysztof Iniewski

Electrostatic Discharge Protection: Advances and Applications Juin J. Liou

> **Embedded and Networking Systems: Design, Software, and Implementation** *Gul N. Khan and Krzysztof Iniewski*

**Energy Harvesting with Functional Materials and Microsystems** Madhu Bhaskaran, Sharath Sriram, and Krzysztof Iniewski

Gallium Nitride (GaN): Physics, Devices, and Technology Farid Medjdoub

Graphene, Carbon Nanotubes, and Nanostuctures: Techniques and Applications James E. Morris and Krzysztof Iniewski

High-Speed and Lower Power Technologies: Electronics and Photonics Jung Han Choi and Krzysztof Iniewski

High-Speed Devices and Circuits with THz Applications Jung Han Choi

> High-Speed Photonics Interconnects Lukas Chrostowski and Krzysztof Iniewski

High Frequency Communication and Sensing: Traveling-Wave Techniques Ahmet Tekin and Ahmed Emira

High Performance CMOS Range Imaging: Device Technology and Systems Considerations Andreas Süss

Integrated Microsystems: Electronics, Photonics, and Biotechnology Krzysztof Iniewski

> **Integrated Power Devices and TCAD Simulation** *Yue Fu, Zhanming Li, Wai Tung Ng, and Johnny K.O. Sin*

Internet Networks: Wired, Wireless, and Optical Technologies Krzysztof Iniewski

Introduction to Smart eHealth and eCare Technologies Sari Merilampi, Krzysztof Iniewski, and Andrew Sirkka

Ionizing Radiation Effects in Electronics: From Memories to Imagers Marta Bagatin and Simone Gerardin

IoT and Low-Power Wireless: Circuits, Architectures, and Techniques Christopher Siu

> Labs on Chip: Principles, Design, and Technology Eugenio Iannone

Laser-Based Optical Detection of Explosives Paul M. Pellegrino, Ellen L. Holthoff, and Mikella E. Farrell

Low Power Circuits for Emerging Applications in Communications, Computing, and Sensing Fei Yuan

> Low Power Emerging Wireless Technologies Reza Mahmoudi and Krzysztof Iniewski

Low Power Semiconductor Devices and Processes for Emerging Applications in Communications, Computing, and Sensing Sumeet Walia

Magnetic Sensors and Devices: Technologies and Applications Kirill Poletkin and Laurent A. Francis

> Medical Imaging: Technology and Applications Troy Farncombe and Krzysztof Iniewski

> > Metallic Spintronic Devices Xiaobin Wang

MEMS: Fundamental Technology and Applications Vikas Choudhary and Krzysztof Iniewski

Micro- and Nanoelectronics: Emerging Device Challenges and Solutions Tomasz Brozek

Microfluidics and Nanotechnology: Biosensing to the Single Molecule Limit Eric Lagally

MIMO Power Line Communications: Narrow and Broadband Standards, EMC, and Advanced Processing

Lars Torsten Berger, Andreas Schwager, Pascal Pagani, and Daniel Schneider

Mixed-Signal Circuits Thomas Noulis

Mobile Point-of-Care Monitors and Diagnostic Device Design Walter Karlen

Multisensor Attitude Estimation: Fundamental Concepts and Applications Hassen Fourati and Djamel Eddine Chouaib Belkhiat

#### Multisensor Data Fusion: From Algorithm and Architecture Design to Applications

Hassen Fourati

MRI: Physics, Image Reconstruction, and Analysis Angshul Majumdar and Rabab Ward

Nano-Semiconductors: Devices and Technology Krzysztof Iniewski

Nanoelectronic Device Applications Handbook James E. Morris and Krzysztof Iniewski

Nanomaterials: A Guide to Fabrication and Applications Sivashankar Krishnamoorthy

Nanopatterning and Nanoscale Devices for Biological Applications Šeila Selimovic

> Nanoplasmonics: Advanced Device Applications James W. M. Chon and Krzysztof Iniewski

Nanoscale Semiconductor Memories: Technology and Applications Santosh K. Kurinec and Krzysztof Iniewski

> Noise Coupling in System-on-Chip Thomas Noulis

Novel Advances in Microsystems Technologies and Their Applications Laurent A. Francis and Krzysztof Iniewski

**Optical, Acoustic, Magnetic, and Mechanical Sensor Technologies** *Krzysztof Iniewski*

**Optical Fiber Sensors: Advanced Techniques and Applications** *Ginu Rajan*

**Optical Imaging Devices: New Technologies and Applications** *Ajit Khosla and Dongsoo Kim*

Organic Solar Cells: Materials, Devices, Interfaces, and Modeling Qiquan Qiao

> **Physical Design for 3D Integrated Circuits** *Aida Todri-Sanial and Chuan Seng Tan*

**Power Management Integrated Circuits and Technologies** Mona M. Hella and Patrick Mercier

> Radiation Detectors for Medical Imaging Jan S. Iwanczyk

Radiation Effects in Semiconductors Krzysztof Iniewski

**Reconfigurable Logic: Architecture, Tools, and Applications** *Pierre-Emmanuel Gaillardon*

**Semiconductor Devices in Harsh Conditions** *Kirsten Weide-Zaage and Malgorzata Chrzanowska-Jeske*

Semiconductor Radiation Detection Systems Krzysztof Iniewski

Semiconductor Radiation Detectors, Technology, and Applications Salim Reza

Semiconductors: Integrated Circuit Design for Manufacturability Artur Balasinski

> Sensors for Diagnostics and Monitoring Kevin Yallup and Laura Basiricò

Smart Grids: Clouds, Communications, Open Source, and Automation David Bakken

> Smart Sensors for Industrial Applications Krzysztof Iniewski

**Soft Errors: From Particles to Circuits** *Jean-Luc Autran and Daniela Munteanu*

Solid-State Radiation Detectors: Technology and Applications Salah Awadalla

Structural Health Monitoring of Composite Structures Using Fiber Optic Methods Ginu Rajan and Gangadhara Prusty

> **Technologies for Smart Sensors and Sensor Fusion** *Kevin Yallup and Krzysztof Iniewski*

> > **Telecommunication Networks** *Eugenio Iannone*

**Testing for Small-Delay Defects in Nanoscale CMOS Integrated Circuits** Sandeep K. Goel and Krishnendu Chakrabarty

Tunable RF Components and Circuits: Applications in Mobile Handsets Jeffrey L. Hilbert

> VLSI: Circuits for Emerging Applications Tomasz Wojcicki

Wireless Medical Systems and Algorithms: Design and Applications Pietro Salvo and Miguel Hernandez-Silveira

> Wireless Technologies: Circuits, Systems, and Devices Krzysztof Iniewski

Wireless Transceiver Circuits: System Perspectives and Design Aspects Woogeun Rhee

X-Ray Diffraction Imaging: Technology and Applications Joel Greenberg

#### FORTHCOMING TITLES:

Compressed Sensing for Engineers Angshul Majumdar

Energy Efficient Computing: Devices, Circuits, and Systems Santosh K. Kurinec and Sumeet Walia

> Radio Frequency Integrated Circuit Design Sebastian Magierowski

Spectral Computed Tomography: Technology and Applications Katsuyuki Taguchi, Ira Blevis, and Krzysztof Iniewski

## Energy Efficient Computing & Electronics Devices to Systems

Krzysztof Iniewski Managing Editor

Edited by Santosh K. Kurinec Sumeet Walia

CRC Press is an imprint of the Taylor & Francis Group, an **informa** business

CRC Press Taylor & Francis Group 6000 Broken Sound Parkway NW, Suite 300 Boca Raton, FL 33487-2742

© 2019 by Taylor & Francis Group, LLC CRC Press is an imprint of Taylor & Francis Group, an Informa business

No claim to original U.S. Government works

Printed on acid-free paper

International Standard Book Number-13: 978-1-138-71036-8 (Hardback)

This book contains information obtained from authentic and highly regarded sources. Reasonable efforts have been made to publish reliable data and information, but the author and publisher cannot assume responsibility for the validity of all materials or the consequences of their use. The authors and publishers have attempted to trace the copyright holders of all material reproduced in this publication and apologize to copyright holders if permission to publish in this form has not been obtained. If any copyright material has not been acknowledged please write and let us know so we may rectify in any future reprint.

Except as permitted under U.S. Copyright Law, no part of this book may be reprinted, reproduced, transmitted, or utilized in any form by any electronic, mechanical, or other means, now known or hereafter invented, including photocopying, microfilming, and recording, or in any information storage or retrieval system, without written permission from the publishers.

For permission to photocopy or use material electronically from this work, please access www.copyright.com (http://www. copyright.com/) or contact the Copyright Clearance Center, Inc. (CCC), 222 Rosewood Drive, Danvers, MA 01923, 978-750-8400. CCC is a not-for-profit organization that provides licenses and registration for a variety of users. For organizations that have been granted a photocopy license by the CCC, a separate system of payment has been arranged.

**Trademark Notice:** Product or corporate names may be trademarks or registered trademarks, and are used only for identification and explanation without intent to infringe.

#### Library of Congress Cataloging-in-Publication Data

Names: Kurinec, Santosh K., editor. | Walia, Sumeet, editor. Title: Energy efficient computing & electronics : devices to systems / edited by Santosh K. Kurinec and Sumeet Walia. Other titles: Energy efficient computing and electronics Description: Boca Raton : CRC/Taylor & Francis, [2019] | Series: Devices, circuits, & systems | Includes bibliographical references and index. Identifiers: LCCN 2018042978| ISBN 9781138710368 (hardback : alk. paper) | ISBN 9781315200705 (ebook) Subjects: LCSH: Electronic apparatus and appliances--Power supply. | Computer systems--Energy conservation. | Low voltage systems. | Wireless communication systems--Energy conservation. Classification: LCC TK7868.P6 E54 2019 | DDC 621.381028/6--dc23 LC record available at https://lccn.loc.gov/2018042978

Visit the Taylor & Francis Web site at http://www.taylorandfrancis.com

and the CRC Press Web site at http://www.crcpress.com

## Contents

| Preface                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------|

| Editorsxvii<br>Contributorsxix                                                                                                    |

|                                                                                                                                   |

| Section I Emerging Low Power Devices                                                                                              |

| <b>1. A FinFET-Based Framework for VLSI Design at the 7 nm Node</b>                                                               |

| <b>2. Molecular Phenomena in MOSFET Gate Dielectrics and Interfaces</b>                                                           |

| <b>3. Tunneling Field Effect Transistors</b>                                                                                      |

| 4. The Exploitation of the Spin-Transfer Torque Effect for CMOS Compatible<br>Beyond Von Neumann Computing                        |

| Thomas Windbacher, Alexander Makarov, Siegfried Selberherr, Hiwa Mahmoudi,<br>B. Gunnar Malm, Mattias Ekström, and Mikael Östling |

| <b>5. Ferroelectric Tunnel Junctions as Ultra-Low-Power Computing Devices</b>                                                     |

| Section II Sensors, Interconnects, and Rectifiers                                                                                 |

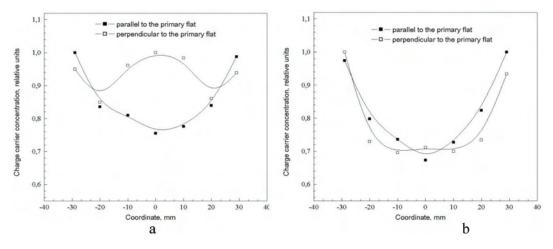

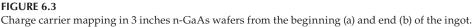

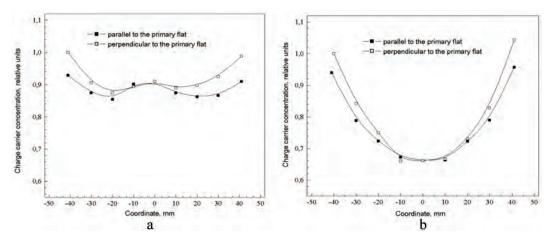

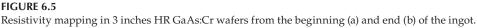

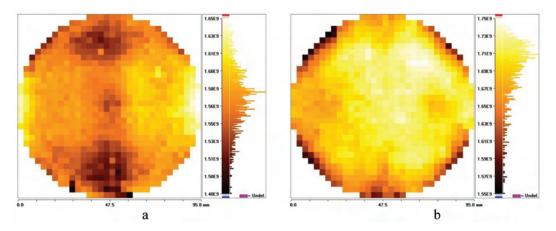

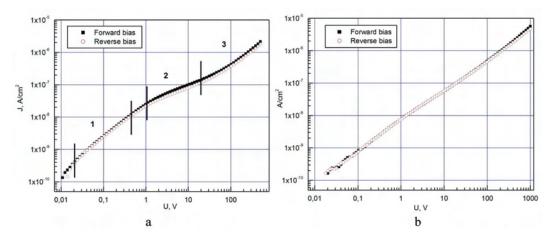

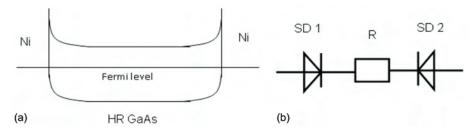

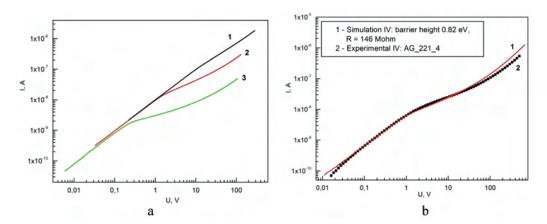

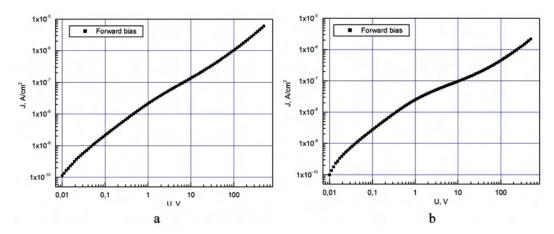

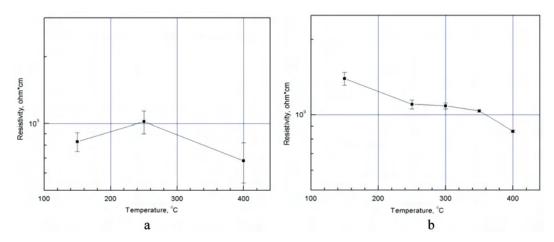

| 6. X-ray Sensors Based on Chromium Compensated Gallium Arsenide<br>(HR GaAs:Cr)                                                   |

| 7. Vertical-Cavity Surface-Emitting Lasers for Interconnects                                                                      |

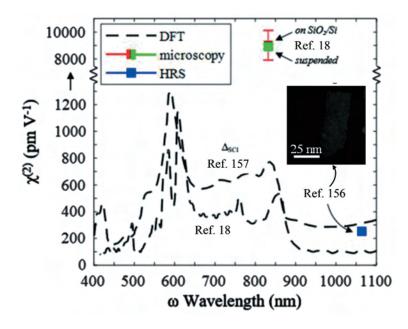

| 8. Low-Power Optoelectronic Interconnects on Two-Dimensional<br>Semiconductors                                                    |

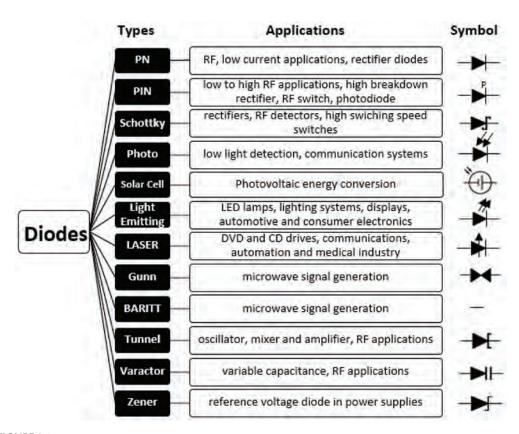

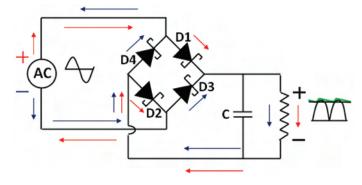

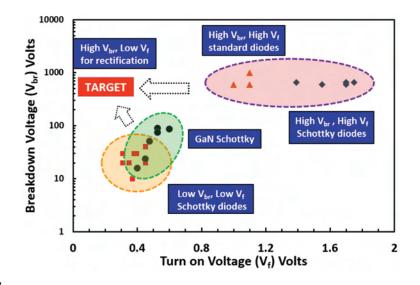

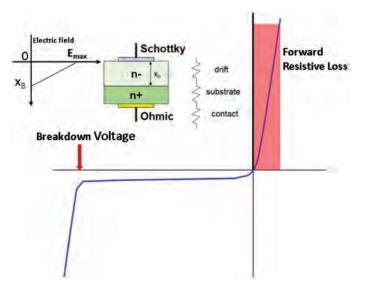

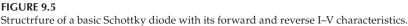

| <b>9. GaN-Based Schottky Barriers for Low Turn-On Voltage Rectifiers</b>                                                          |

| 10. Compound Semiconductor Oscillation Device Fabricated by Stoichiometry<br>Controlled-Epitaxial Growth and Its Application to Terahertz and Infrared<br>Imaging and Spectroscopy<br>Takeo Ohno, Arata Yasuda, Tadao Tanabe, and Yutaka Oyama | . 267 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Section III Systems Design and Applications                                                                                                                                                                                                    |       |

| <b>11. Low Power Biosensor Design Techniques Based on Information</b><br><b>Theoretic Principles</b><br><i>Nicole McFarlane</i>                                                                                                                | . 287 |

| <b>12. Low-Power Processor Design Methodology: High-Level Estimation</b><br><b>and Optimization via Processor Description Language</b><br><i>Zheng Wang and Anupam Chattopadhyay</i>                                                           | .301  |

| <b>13. Spatio-Temporal Multi-Application Request Scheduling in Energy-Efficient</b><br><b>Data Centers</b><br><i>Haitao Yuan, Jing Bi, and MengChu Zhou</i>                                                                                    | .343  |

| <b>14. Ultra-Low-Voltage Implementation of Neural Networks</b> <i></i>                                                                                                                                                                         | . 379 |

| <b>15. Multi-Pattern Matching Based Dynamic Malware Detection in Smart Phones</b><br>V. S. Devi, S. Roopak, Tony Thomas, and Md. Meraj Uddin                                                                                                   | . 421 |

| Index                                                                                                                                                                                                                                          | .443  |

### Preface

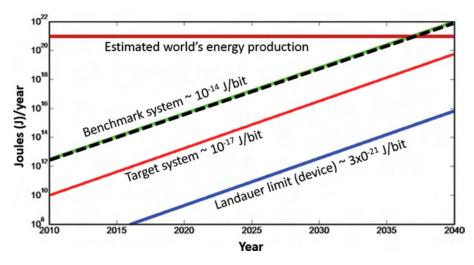

Performance of electronic systems are limited by energy inefficiencies that result in overheating and thermal management problems. Energy efficiency is vital to improving performance at all levels. This includes transistors to devices and to large Internet Technology and electronic systems, as well from small sensors for the Internet-of-Things (IoT) to large data centers in cloud and supercomputing systems. The electronic circuits in computer chips still operate far from any fundamental limits to energy efficiency. A report issued by the Semiconductor Industry Association and Semiconductor Research Corporation bases its conclusions on system-level energy per bit operation, which are a combination of many components such as logic circuits, memory arrays, interfaces, and I/Os. Each of these contributes to the total energy budget. For the benchmark energy per bit, as shown in Figure 1, computing will not be sustainable by 2040. This is when the energy required for computing is estimated to exceed the world's estimated energy production. The "benchmark" curve shows the growing energy demand for the system level energy per bit values of mainstream systems. The target system curve uses the practical lower limit system level energy per bit value, set by factors such as materials. The Landauer limit curve uses the minimal device energy per bit value provided by the Landauer's Principle that relates to the Second Law of Thermodynamics to computation. As such, significant improvement in the energy efficiency of computing is needed.

There is a consensus across the many technologies touched by our ubiquitous computing infrastructure that future performance improvements across the board are now severely limited by the amount of energy it takes to manipulate, store, and critically transport data. Revolutionary device concepts, sensors, and associated circuits and architectures that will greatly extend the practical engineering limits of energy-efficient computation are being investigated. Disruptive new device architectures, semiconductor processes, and emerging

#### FIGURE 1

Estimated total energy expenditure for computing, directly related to the number of raw bit transitions. Source: SIA/SRC (*Rebooting the IT Revolution: A Call to Action*, Semiconductor Industry Association, September 2015).

new materials aimed at achieving the highest level of computational energy efficiency for general purpose computing systems need to be developed. This book will provide chapters dedicated to some of such efforts from devices to systems.

The book is divided into three sections each consisting of five chapters.

Section I is dedicated to device level research in developing energy efficient device structures.

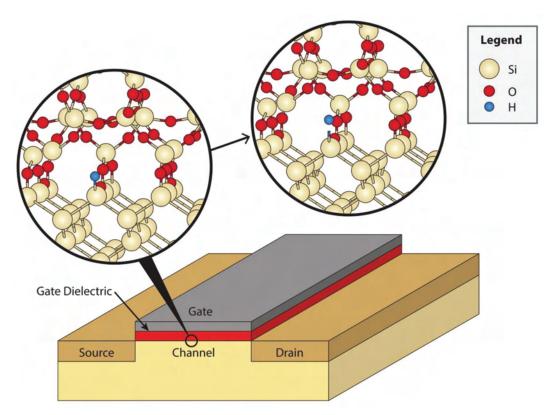

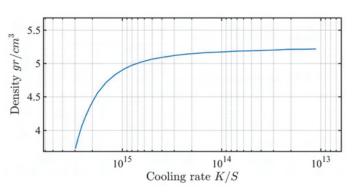

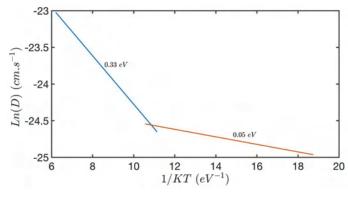

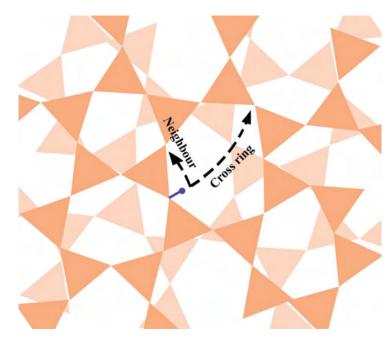

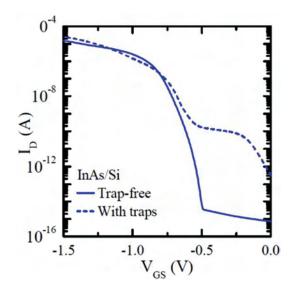

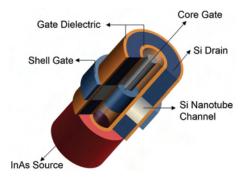

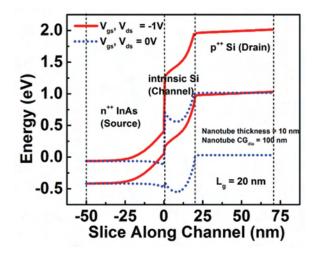

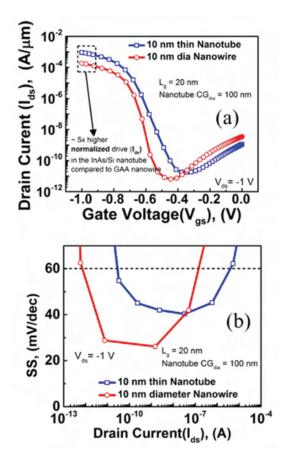

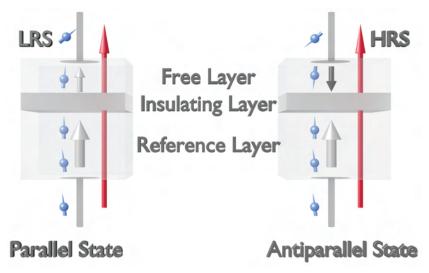

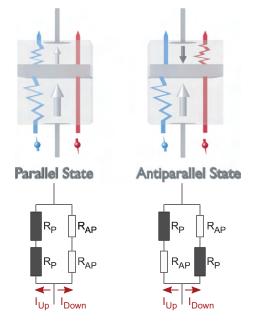

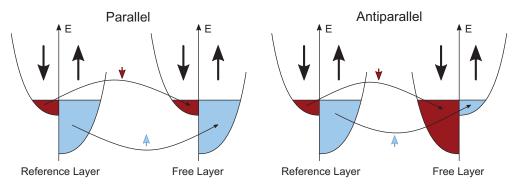

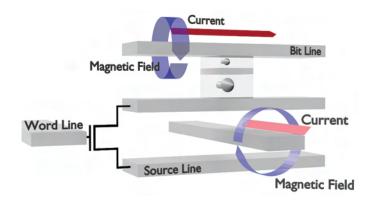

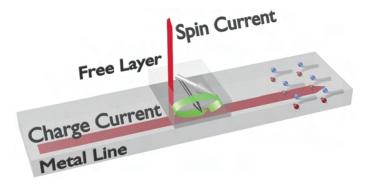

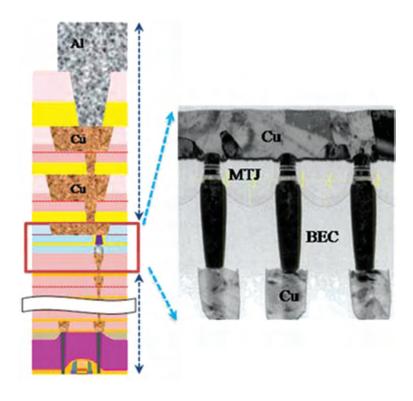

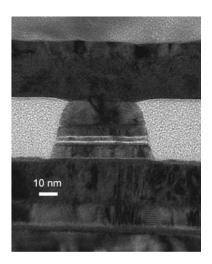

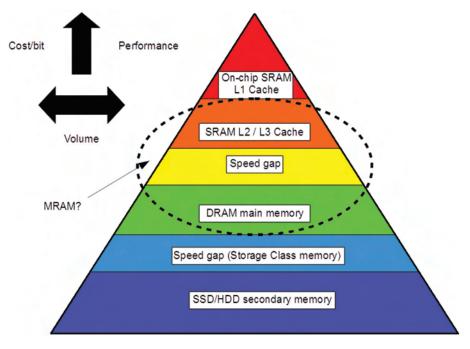

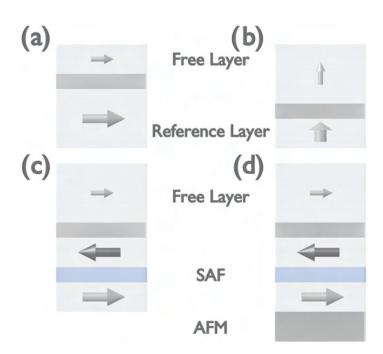

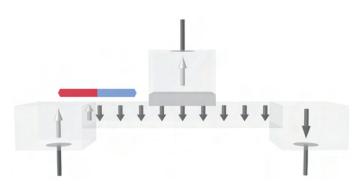

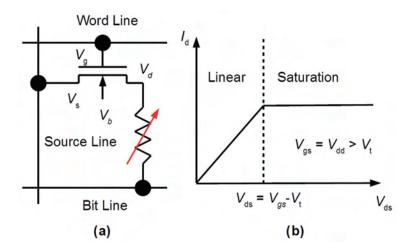

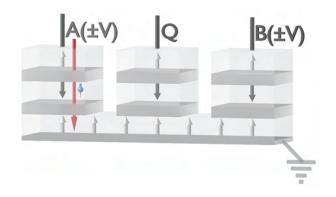

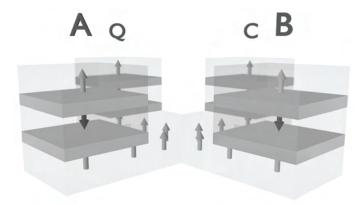

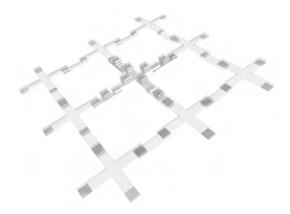

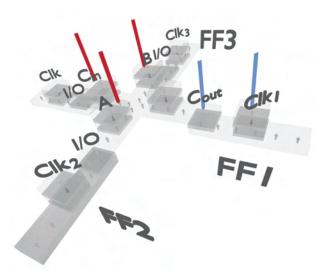

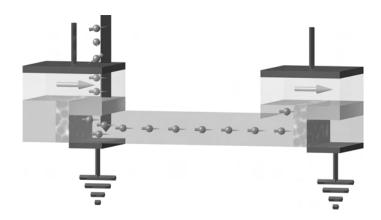

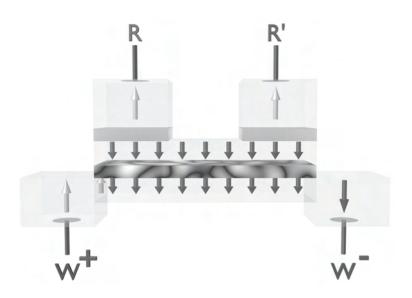

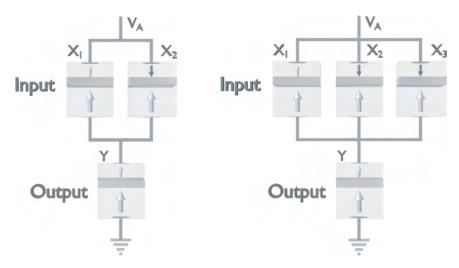

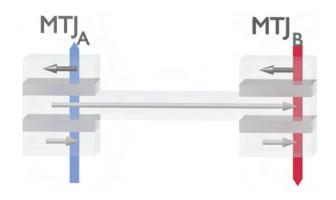

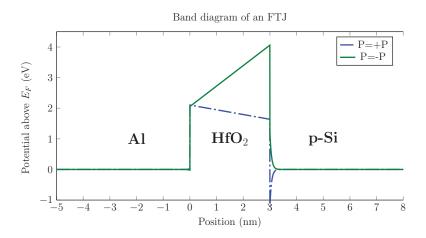

Non-planar finFETs dominate highly scaled processes, such as sub-20 nm, CMOS processes, due to their ability to provide lower leakage and enable continued power supply scaling (VDD). Chapter 1 gives a comprehensive overview of the finFET-based predictive process design kit (PDK) that supports investigation into both the circuit as well as physical design, encompassing all aspects of digital design. Prevention of various degradation mechanisms in transistors is the key to increase the reliability and efficiency of electronic systems. Chapter 2 discusses the understanding of molecular phenomena at the MOSFET channel/dielectric interface, focussing on ZrO2 system aimed at minimizing the degrading mechanisms in transistors. Chapter 3 provides an important insight into the nanotube Tunneling field effect transistors (TFETs) device, which promise to exhibit steep slope faster than the Boltzmann limit of 60 mV/dec. TFETs address two major challenges faced by aggressively scaled conventional CMOS technology; scaling the supply voltage (VDD) and minimizing the leakage currents. Chapter 4 gives an in-depth introduction and potential of spin based devices. It gives an overview of spintronic devices, circuits, and architecture levels that include thermally assisted (TA)-MRAM, STT-MRAM, domain wall (DW)-MRAM, spin-orbit torque (SOT)-MRAM, spin-transfer torque and spin Hall oscillators, logic-in-memory, all-spin logic, buffered magnetic logic gate grid, ternary content addressable memory (TCAM), and random number generators. A large bottleneck for energy efficiency has long been the information storage units, which typically rely on charge-storage for programming and erasing. Chapter 5 describes the promise of ferroelectric tunnel junctions (FTJs) as memristors. Memristor-based logic systems for XOR, XNOR, full-adder, DAC, and ADC outperform CMOS with as low as 50% the delay and 0.1% the power consumption.

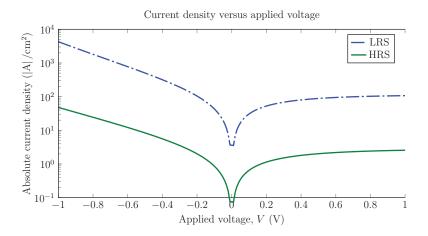

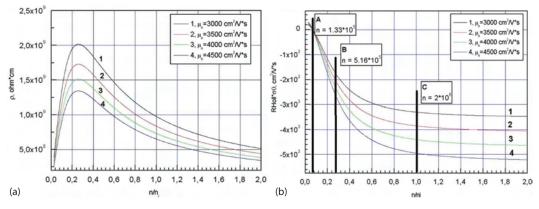

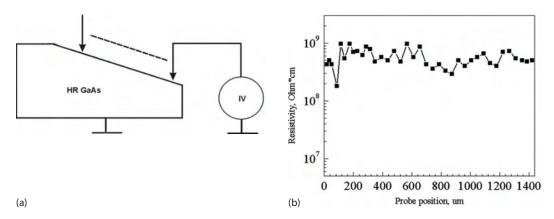

Section II deals with sensors, interconnects, and rectifiers aimed at consuming lower power.

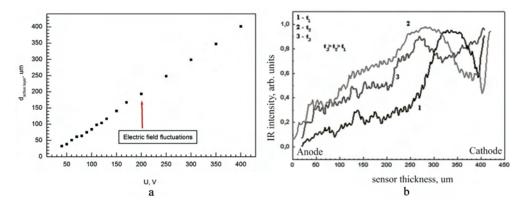

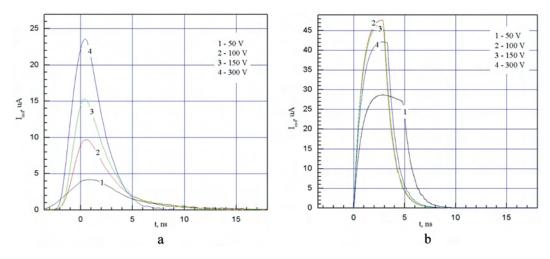

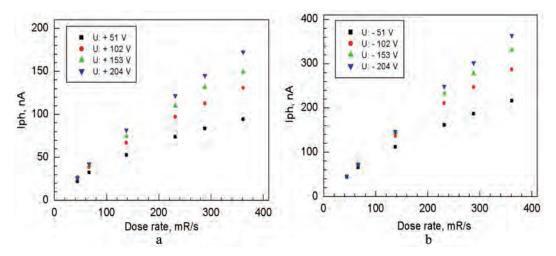

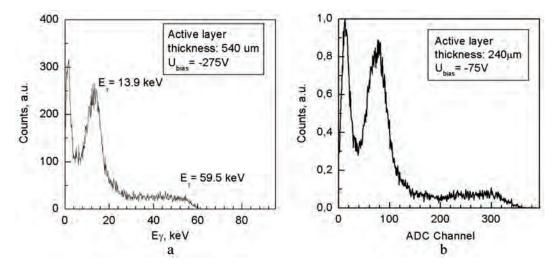

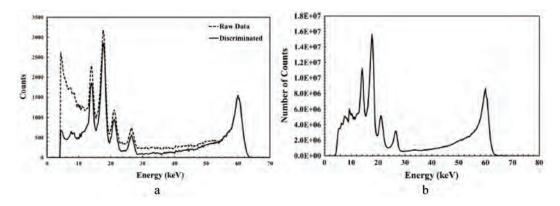

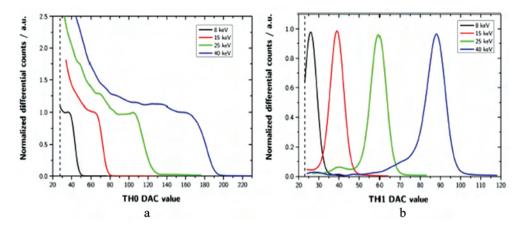

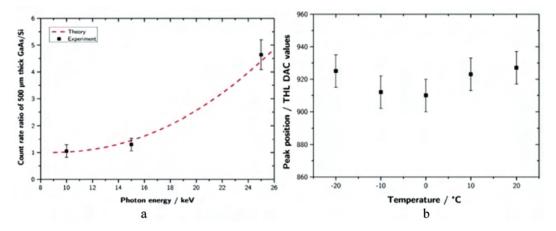

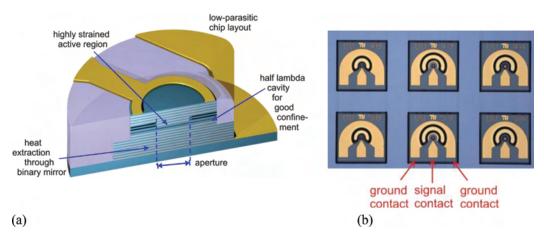

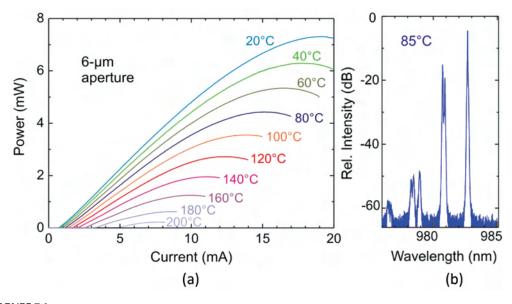

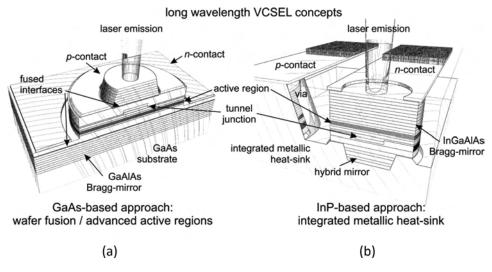

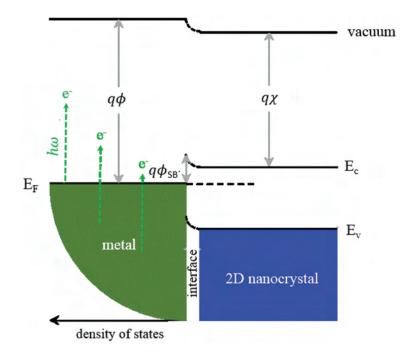

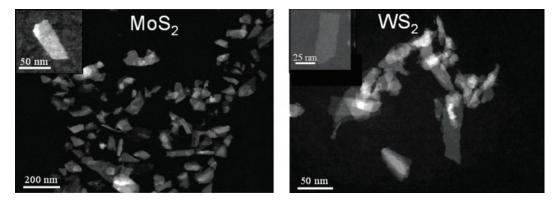

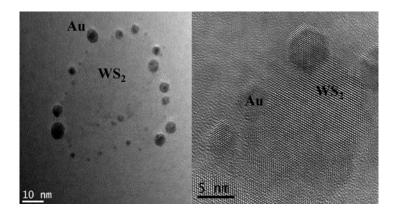

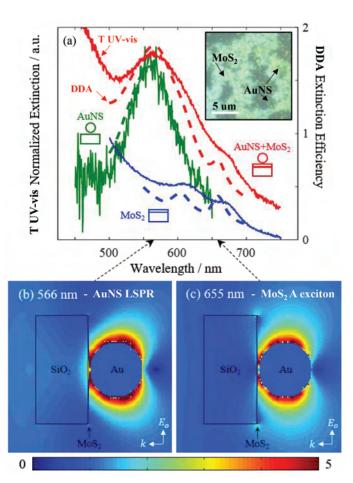

Chapter 6 provides insight into X-ray sensors based on chromium compensated GaAs for the development of modern X-ray imaging systems. Chapters 7 and 8 deal with optical interconnects, which are actively being pursued to reduce power requirements and increase speed. Chapter 7 provides an overview of the challenges and developments of various types of Vertical-Cavity Surface-Emitting Laser (VCSEL)-based interconnects. Optoelectronic interactions at interconnective hetero-interfaces between nanoparticles and two-dimensional semiconductors, motivated by their enhancement of electronic and photonic properties are described in Chapter 8. Chapter 9 investigates AlGaN/GaN heterostructures based Schottky diodes with low turn-on voltage of  $V_f < 0.4V$ , and high breakdown voltage of  $V_{br} > 400V$  for applications in energy efficient 230V AC-DC rectifiers. In Chapter 10, the authors have discussed the stoichiometry-controlled crystal growth technique and its application to compound semiconductor oscillation devices for extending to THz region The THz wave generators can be used in applications of non-destructive evaluation, safe for human tissues.

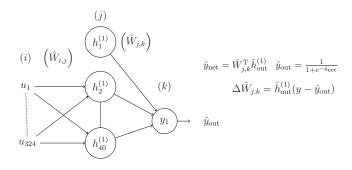

Section III has five chapters aimed at low power system designs.

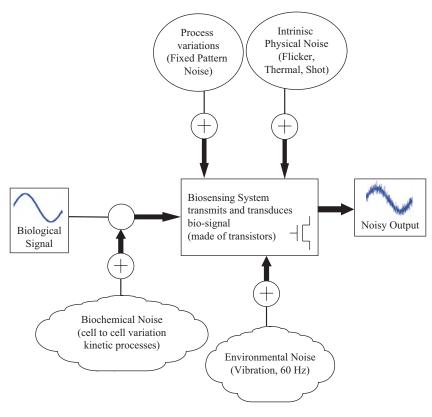

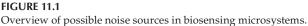

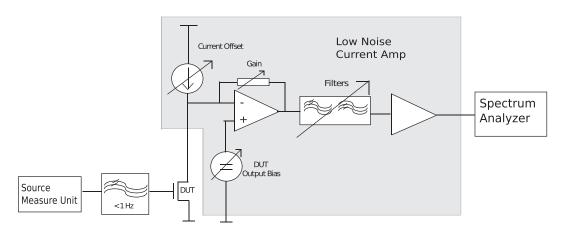

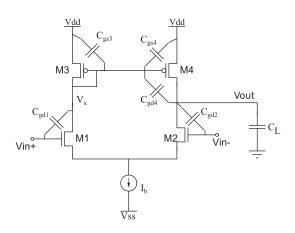

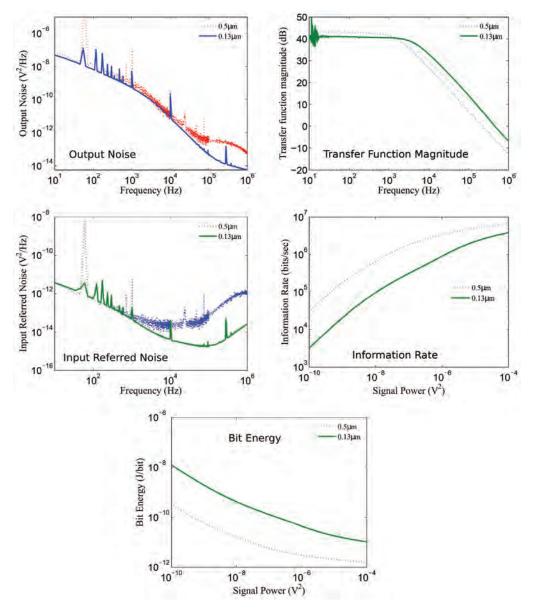

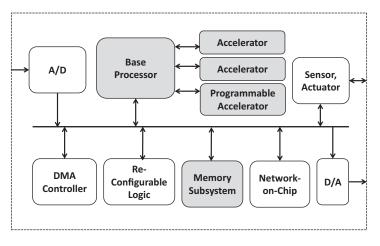

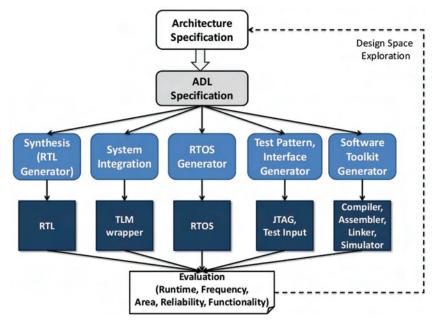

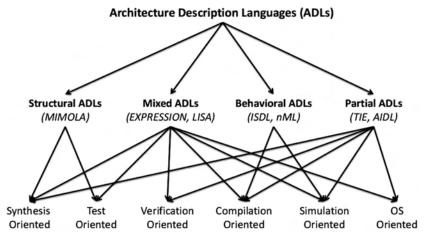

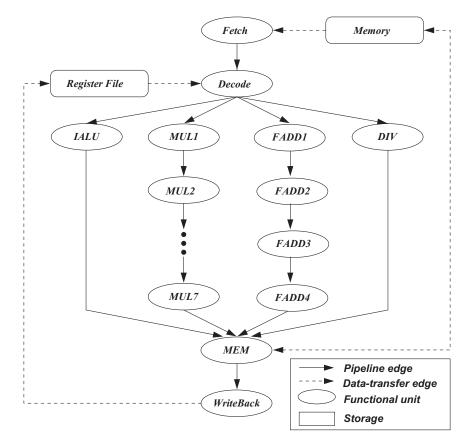

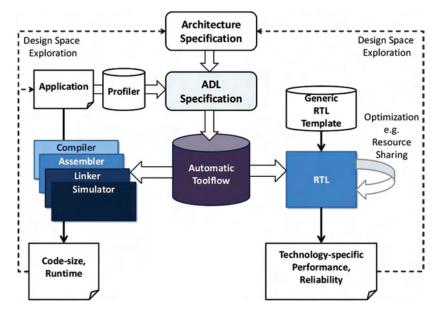

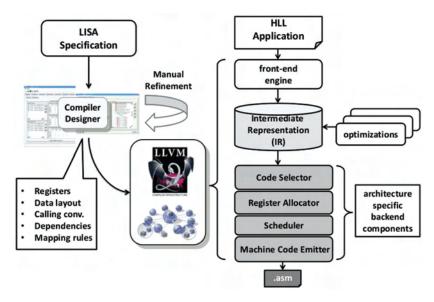

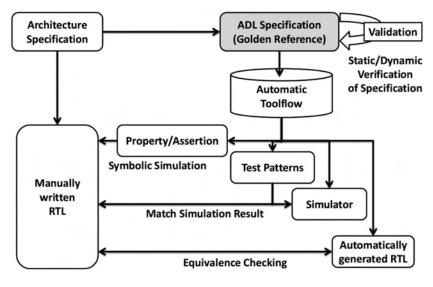

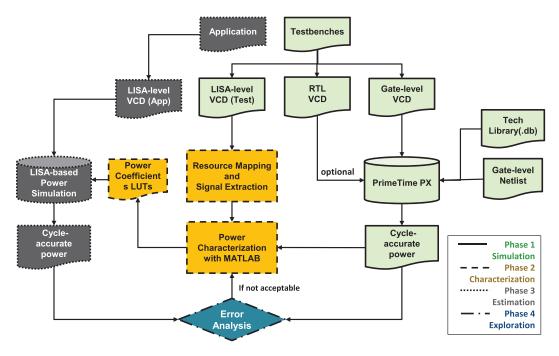

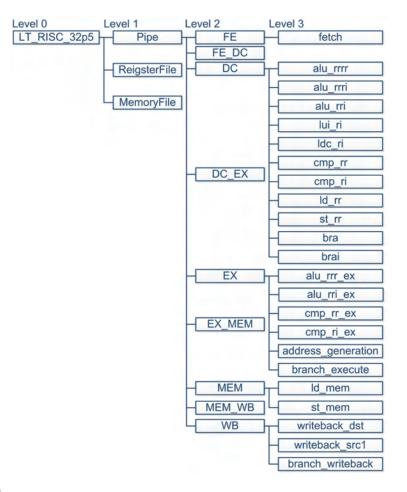

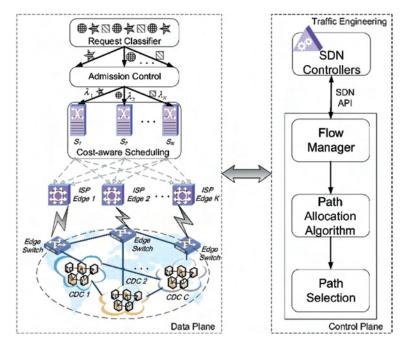

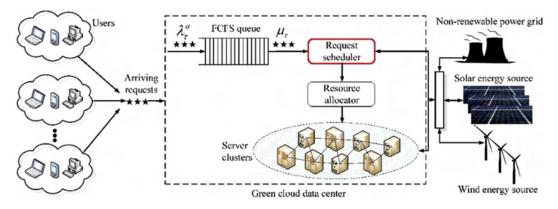

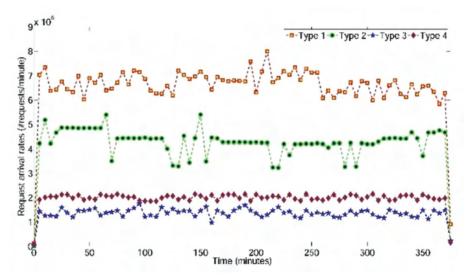

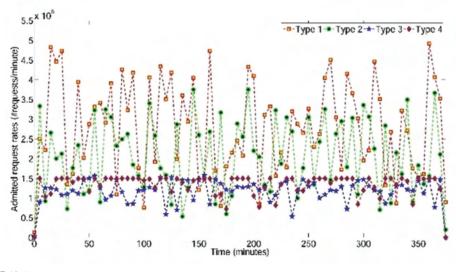

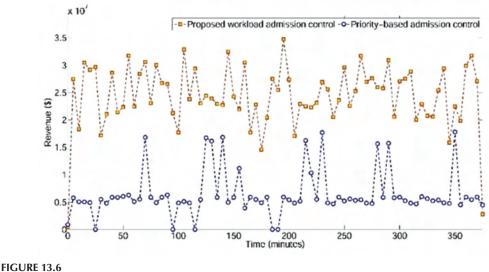

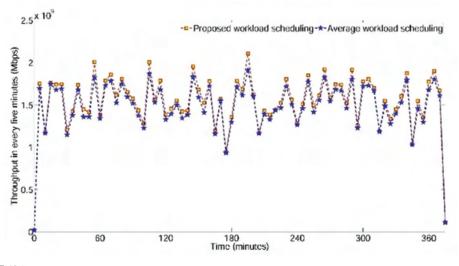

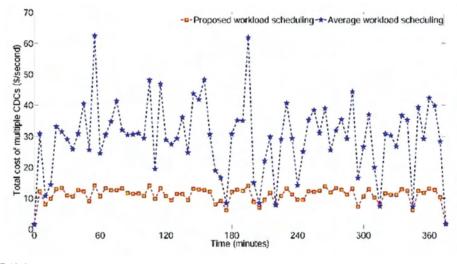

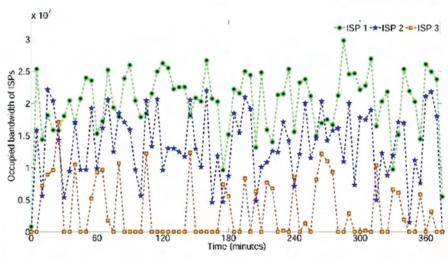

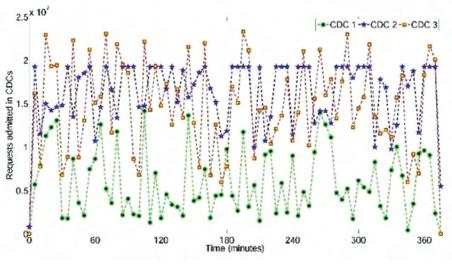

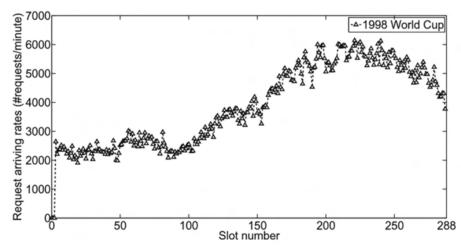

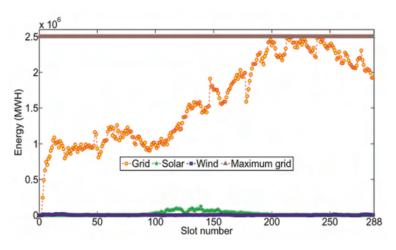

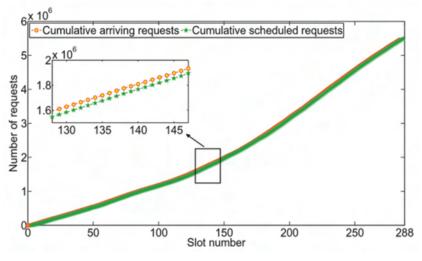

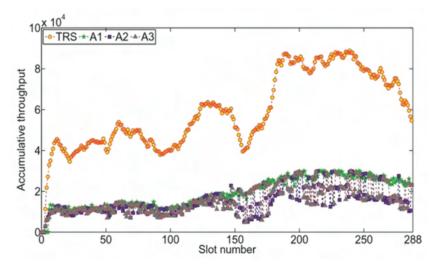

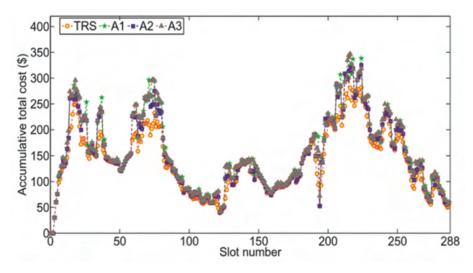

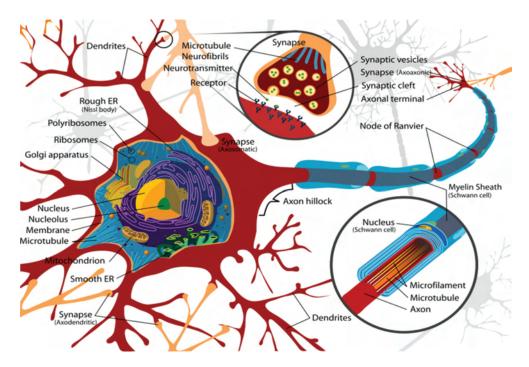

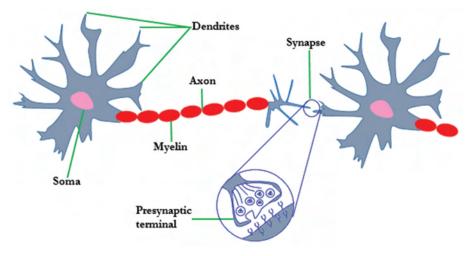

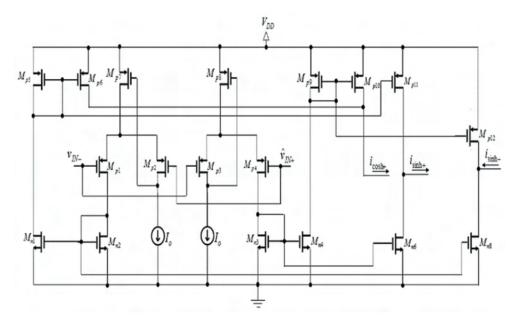

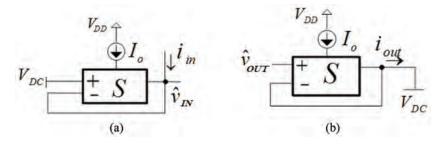

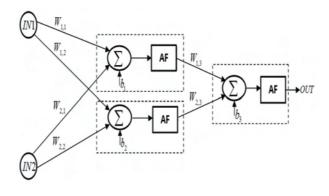

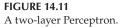

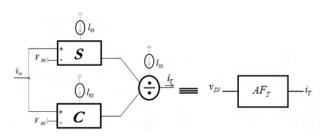

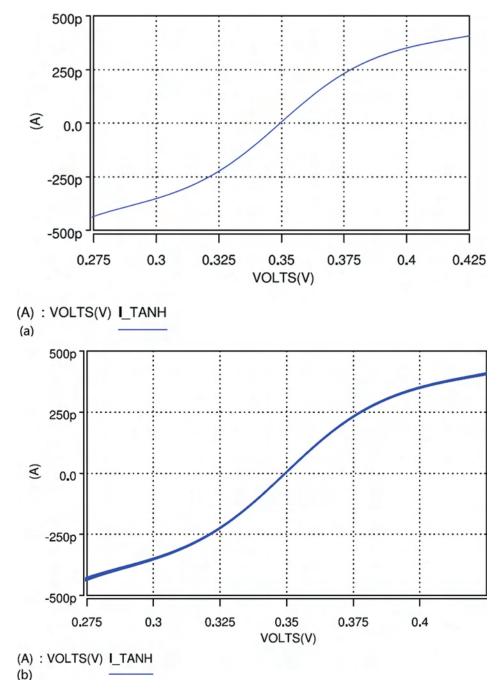

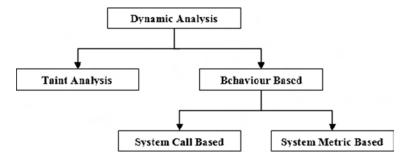

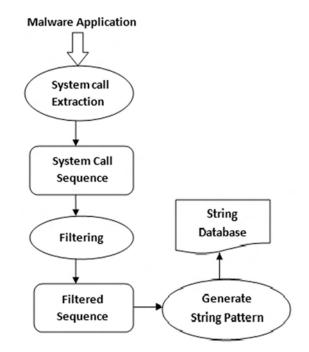

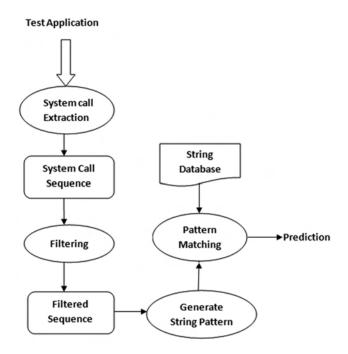

The imminent concern of inherent physical noise with low power biosensing mixed signal CMOS technology is addressed in Chapter 11. The information rate and bit energy have been incorporated into a design methodology for detecting weak signals in the presence of fixed system noise. Chapter 12 provides an overview of the high-level processor architecture design methodologies using Architecture Description Languages (ADLs). Chapter 13 focuses on challenging problems related to energy-efficient Cloud Data Centers (CDC). It presents how to minimize the total cost of a CDC provider in a market, and how to migrate to green cloud data centers (GCDCs). The authors propose a Temporal Request Scheduling algorithm (TRS) that can achieve higher throughput and lower grid energy cost for a GCDC. Chapter 14 presents an innovative brain inspired approach of implementing neural network in hardware implementation for ultra-low-voltage implementation of the perceptron and the inertial neuron. The final chapter (Chapter 15) addresses a large system-level problem of malware attacks to mobile devices. It presents a multi-pattern matching based dynamic malware detection mechanism in smart phones as an alternative to machine learning based methods. The proposed mechanism is more efficient and uses fewer resources.

Thus, this book brings together a wealth of information that will serve as a valuable resource for researchers, scientists, and engineers engaged in energy efficient designs of electronic devices, circuits, and systems. The editors express their sincere appreciation to the authors who have contributed their knowledge and expertise to this book. Special thanks to Nora Konopka and Erin Harris of Taylor & Francis Group/CRC Press for their publishing efforts and coordinating with the authors. The authors also express their sincere appreciation for Joanne Hakim, project manager of Lumina Datamatics, for coordinating the production of this book.

### **Editors**

**Santosh K. Kurinec** is a professor of electrical and microelectronic engineering at Rochester Institute of Technology (RIT), Rochester, New York. She received a PhD in physics from University of Delhi, India and worked as a scientist at the National Physical Laboratory, New Delhi, India. She worked as a postdoctoral research associate in the Department of Materials Science and Engineering at the University of Florida, Gainesville, Florida where she researched thin metal film composites. Prior to joining RIT, she was assistant professor of electrical engineering at Florida State University/Florida

A&M University College of Engineering in Tallahassee, Florida. She is a Fellow of Institute of Electrical and Electronics Engineers (IEEE), Member APS, NY State Academy of Sciences, and an IEEE EDS Distinguished Lecturer. She received the 2012 IEEE Technical Field Award. In 2016, she received the Medal of Honor from the International Association of Advanced Materials (IAAM). She was inducted into the International Women in Technology (WiTi) Hall of Fame in 2018. She has worked on a range of materials covering magnetic, ferroelectrics, semiconductors, photonic luminescent thin films, and metal composites for device applications. Her current research activities include nonvolatile memory, advanced integrated circuit materials and processes, and photovoltaics. She has over 100 publications in research journals and conference proceedings. She can be reached at Santosh.kurinec@rit.edu.

**Sumeet Walia** is a senior lecturer and a Vice Chancellor's Fellow at RMIT University, Melbourne, Australia. He is an expert in materials engineering for nanoelectronics, sensing, and wearable devices. He has been recognized as one of the Top 10 Innovators under 35 in Asia-Pacific by the MIT Technology Review in 2017, was awarded the Victorian Young Achiever Award for Research Impact in 2017, and named among the most innovative Engineers in Australia in 2018 by Engineers Australia. He can be reached at waliasumeet@gmail.com or sumeet.walia@rmit.edu.au.

### Contributors

#### Jing Bi

Faculty of Information Technology Beijing University of Technology Beijing, China

#### Anupam Chattopadhyay

School of Computer Science and Engineering Nanyang Technological University Singapore

#### Lawrence T. Clark

School of Electrical, Computer, and Energy Engineering Arizona State University Tempe, Arizona, USA

#### Mohammad Rafiq Dar

Department of Electronics and Instrumentation Technology University of Kashmir Srinagar, India

#### Nishant Darvekar

Electrical and Microelectronic Engineering Rochester Institute of Technology Rochester, New York, USA

#### V. S. Devi

Department of Computer Science Indian Institute of Information Technology and Management – Kerala (IIITM-K) Thiruvananthapuram, India

#### Mattias Ekström

Department of Electronics KTH Royal Institute of Technology Kista, Sweden

#### **Cristian Grecu**

Department of Electrical and Computer Engineering University of British Columbia Vancouver, British Columbia, Canada

#### Amir N. Hanna

Department of Electrical Engineering King Abdullah University of Science and Technology (KAUST) Thuwal, Saudi Arabia

#### Werner H. E. Hofmann

Institute of Solid State Physics and Center of Nanophotonics Technical University of Berlin Berlin, Germany

#### Muhammad Mustafa Hussain

Department of Electrical Engineering King Abdullah University of Science and Technology (KAUST) Thuwal, Saudi Arabia

#### Andre Ivanov

Department of Electrical and Computer Engineering University of British Columbia Vancouver, British Columbia, Canada

#### Nasir Ali Kant

Department of Electronics and Instrumentation Technology University of Kashmir Srinagar, India

#### Farooq Ahmad Khanday

Department of Electronics and Instrumentation Technology University of Kashmir Srinagar, India

#### Santosh K. Kurinec

Electrical and Microelectronic Engineering Rochester Institute of Technology Rochester, New York, USA

#### Hiwa Mahmoudi

Institute of Electrodynamics, Microwave and Circuit Engineering TU Wien Vienna, Austria

#### Alexander Makarov

Institute for Microelectronics TU Wien Vienna, Austria

#### B. Gunnar Malm

Department of Electronics KTH Royal Institute of Technology Kista, Sweden

#### Hegoi Manzano

Department of Condensed Matter Physics University of the Basque Country UPV/ EHU Barrio Sarriena s/n, 48330 Leioa, Bizkaia, Spain

#### Nicole McFarlane

Min H. Kao Department of Electrical Engineering & Computer Science Tickle College of Engineering The University of Tennessee Knoxville, Tennessee, USA

#### Takeo Ohno

Department of Innovative Engineering Oita University Oita, Japan

#### Mikael Östling

Department of Electronics KTH Royal Institute of Technology Kista, Sweden

#### Yutaka Oyama

Department of Materials Science and Engineering Tohoku University Sendai, Japan

#### Spencer Allen Pringle

Electrical & Microelectronic Engineering Rochester Institute of Technology Rochester, New York, USA

#### S. Roopak

Department of Computer Science Indian Institute of Information Technology and Management – Kerala (IIITM-K) Thiruvananthapuram, India

#### D. Keith Roper

Ralph E. Martin Department of Chemical Engineering and Microelectronics-Photonics Graduate Program and Institute for Nanoscience and Engineering University of Arkansas Fayetteville, Arkansas, USA

#### Siegfried Selberherr

Institute for Microelectronics TU Wien Vienna, Austria

#### S. Arash Sheikholeslam

Department of Electrical and Computer Engineering University of British Columbia Vancouver, British Columbia, Canada

#### Tadao Tanabe

Department of Materials Science and Engineering Tohoku University Sendai, Japan **Tony Thomas** Department of Computer Science Indian Institute of Information Technology and Management – Kerala (IIITM-K) Thiruvananthapuram, India

**Oleg Tolbanov** Functional Electronics Laboratory Tomsk State University Tomsk, Russia

#### Anton Tyazhev

Functional Electronics Laboratory Tomsk State University Tomsk, Russia

#### Md. Meraj Uddin

Department of Computer Science Indian Institute of Information Technology and Management – Kerala (IIITM-K) Thiruvananthapuram, India

#### Vinay Vashishtha

School of Electrical, Computer, and Energy Engineering Arizona State University Tempe, Arizona, USA

#### Zheng Wang

Shenzhen Institute of Advanced Technology Chinese Academy of Sciences Beijing, China

#### **Thomas Windbacher**

Institute for Microelectronics TU Wien Vienna, Austria

#### Arata Yasuda

Department of Creative Engineering National Institute of Technology Tsuruoka College Tsuruoka, Japan

#### Haitao Yuan

School of Software Engineering Beijing Jiaotong University Beijing, China

#### MengChu Zhou

Helen and John C. Hartmann Department of Electrical and Computer Engineering New Jersey Institute of Technology Newark, New Jersey, USA

## Section I

## **Emerging Low Power Devices**

# 1

## A FinFET-Based Framework for VLSI Design at the 7 nm Node

#### Vinay Vashishtha and Lawrence T. Clark

#### CONTENTS

| 1.1 | Intro                                                   | duction                                      |                                                         | 4  |  |

|-----|---------------------------------------------------------|----------------------------------------------|---------------------------------------------------------|----|--|

|     | 1.1.1                                                   | Chapte                                       | r Outline                                               | 5  |  |

| 1.2 | ASAF                                                    | 97 Electri                                   | cal Performance                                         | 5  |  |

| 1.3 | Litho                                                   | graphy C                                     | Considerations                                          | 7  |  |

|     | 1.3.1                                                   | Lithogr                                      | aphy Metrics and Other Considerations for Design Rule   |    |  |

|     |                                                         |                                              | ination                                                 |    |  |

|     |                                                         | 1.3.1.1                                      | Critical Dimension Uniformity (CDU)                     | 7  |  |

|     |                                                         |                                              | Overlay                                                 |    |  |

|     |                                                         | 1.3.1.3                                      | Mask Error Enhancement Factor (MEEF) and Edge Placement |    |  |

|     |                                                         |                                              | Error (EPE)                                             | 8  |  |

|     |                                                         | 1.3.1.4                                      | Time-Dependent Dielectric Breakdown (TDDB)              | 9  |  |

|     | 1.3.2 Single Exposure Optical Immersion Lithography     |                                              |                                                         |    |  |

|     | 1.3.3 Multi-Patterning Approaches                       |                                              |                                                         |    |  |

|     |                                                         |                                              | Litho-Etch <sup>x</sup> (LE <sup>x</sup> )              |    |  |

|     |                                                         | 1.3.3.2                                      | Self-Aligned Multiple Patterning (SAMP)                 | 11 |  |

|     |                                                         |                                              | Multiple Patterning Approach Comparison                 |    |  |

|     | 1.3.4 Extreme Ultra Violet Lithography (EUVL)           |                                              |                                                         | 15 |  |

|     |                                                         | 1.3.4.1                                      | EUVL Necessity                                          | 15 |  |

|     |                                                         | 1.3.4.2                                      | EUVL Description and Challenges                         | 16 |  |

|     |                                                         | 1.3.4.3                                      | EUVL Advantages                                         |    |  |

|     | 1.3.5                                                   |                                              | ing Cliffs                                              |    |  |

|     | 1.3.6                                                   | Design                                       | Technology Co-Optimization (DTCO)                       | 18 |  |

| 1.4 | Front End of Line (EOL) and Middle of Line (MOL) Layers |                                              |                                                         |    |  |

| 1.5 | Back End of Line (BEOL) Layers                          |                                              |                                                         |    |  |

|     | 1.5.1                                                   | 1 Self-Aligned Via (SAV) and Barrier Layer   |                                                         |    |  |

|     | 1.5.2                                                   | EUV Lithography Assumptions and Design Rules |                                                         |    |  |

|     | 1.5.3                                                   | Multipl                                      | e Patterning (MP) Optical Lithography Assumptions and   |    |  |

|     |                                                         |                                              | Rules                                                   |    |  |

|     |                                                         |                                              | Patterning Choice                                       |    |  |

|     |                                                         | 1.5.3.2                                      | SADP Design Rules and Derivations                       | 24 |  |

| Cell L | ibrary Architecture                                                                                                                                 | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|        |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 1.6.2  |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 1.6.3  |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 1.6.4  |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 1.6.5  |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 1.6.6  |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|        |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 1.7.1  | Power Routing and Self-Aligned Via (SAV)                                                                                                            | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 1.7.2  |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 1.7.3  |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|        |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 1.8.1  | FinFET Implications and Fin Patterning                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 1.8.2  | Statistical Analysis                                                                                                                                | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 1.8.3  |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

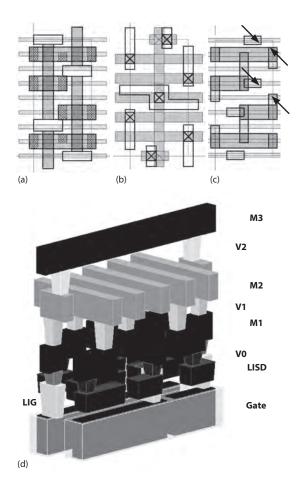

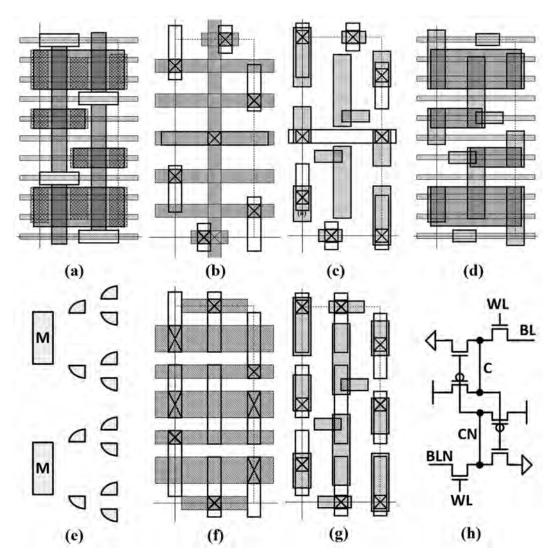

|        | 1.8.3.1 MOL Patterning                                                                                                                              | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|        | 1.8.3.2 1-D Cell Metallization                                                                                                                      | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

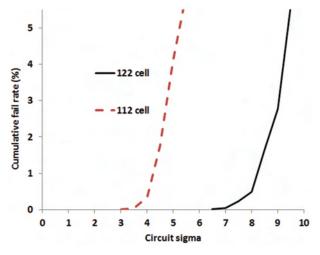

|        | 1.8.3.3 Stability and Yield Analysis                                                                                                                | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

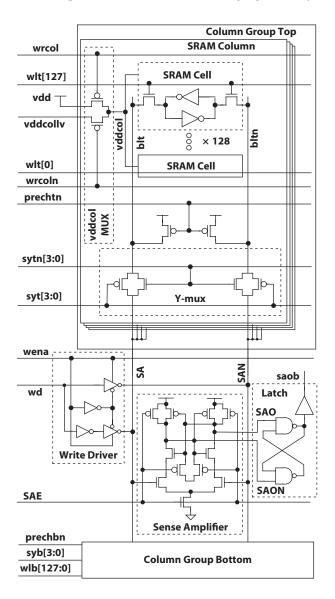

| 1.8.4  | Array Organization and Column Design                                                                                                                | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 1.8.5  |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Chapt  | ter Summary                                                                                                                                         | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|        |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|        | 1.6.1<br>1.6.2<br>1.6.3<br>1.6.4<br>1.6.5<br>1.6.6<br>Autor<br>1.7.1<br>1.7.2<br>1.7.3<br>SRAN<br>1.8.1<br>1.8.2<br>1.8.3<br>1.8.4<br>1.8.5<br>Chap | <ul> <li>1.6.3 Standard Cell Middle of Line (MOL) Usage</li> <li>1.6.4 Standard Cell Pin and Signal Routing.</li> <li>1.6.5 Library Collaterals</li> <li>1.6.6 DTCO Driven DR Changes Based on APR Results</li> <li>Automated Place and Route with ASAP7</li> <li>1.7.1 Power Routing and Self-Aligned Via (SAV)</li> <li>1.7.2 Scaled Layout Exchange Format (LEF) and QRC TechFile</li> <li>1.7.3 Design Experiments and Results.</li> <li>SRAM Design</li> <li>1.8.1 FinFET Implications and Fin Patterning</li> <li>1.8.2 Statistical Analysis.</li> <li>1.8.3 SRAM Cell Design and DTCO Considerations</li> <li>1.8.3.1 MOL Patterning.</li> <li>1.8.3.2 1-D Cell Metallization</li> <li>1.8.3 Stability and Yield Analysis</li> <li>1.8.4 Array Organization and Column Design</li> </ul> |  |

#### 1.1 Introduction

Recent years have seen finFETs dominate highly scaled (e.g., sub-20 nm) complementary metal-oxide-semiconductor (CMOS) processes (Wu et al. 2013; Lin et al. 2014) due to their ability to alleviate short channel effects, provide lower leakage, and enable some continued V<sub>DD</sub> scaling. However, availability of a realistic finFET-based predictive process design kit (PDK) for academic use that supports investigation into both circuit, as well as physical design, encompassing all aspects of digital design, has been lacking. While the finFET-based FreePDK15 was supplemented with a standard cell library, it lacked full physical verification, layout vs. schematic check (LVS) and parasitic extraction (Bhanushali et al. 2015; Martins et al. 2015) at the time of development of the PDK described in this chapter. Consequently, the only available sub-45 nm educational PDKs are the planar CMOS-based Synopsys 32/28 nm and FreePDK45 (45 nm PDK) (Stine et al. 2007; Goldman et al. 2013). The cell libraries available for those processes are not very realistic since they use very large cell heights, in contrast to recent industry trends. Additionally, the static random access memory (SRAM) rules and cells provided by these PDKs are not realistic. Because finFETs have a 3-D structure and result in significant density impact, using planar libraries scaled to sub-22 nm dimensions for research is likely to give poor accuracy.

Commercial libraries and PDKs, especially for advanced nodes, are often difficult to obtain for academic use and access to the actual physical layouts is even more restricted. Furthermore, the necessary non-disclosure agreements (NDAs) are unmanageable for

5

large university classes, and the plethora of design rules can distract from the key points. NDAs also make it difficult for the publication of physical design as these may disclose proprietary design rules and structures.

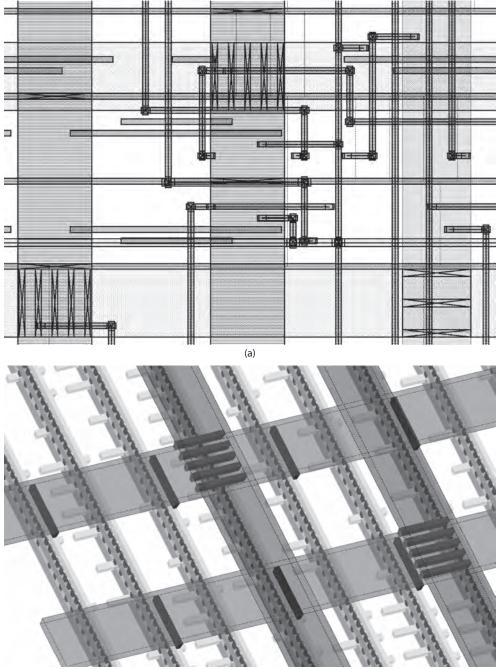

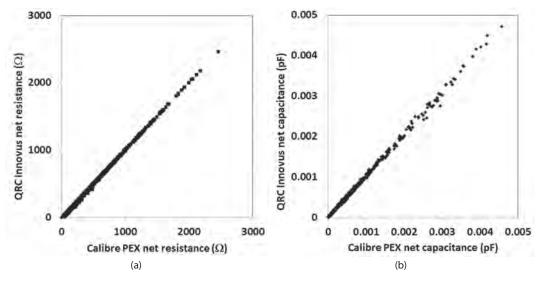

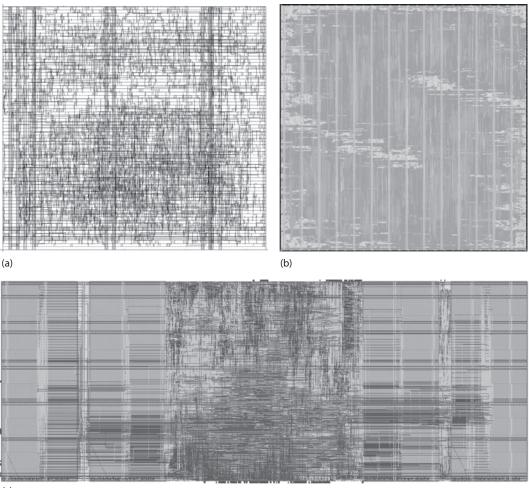

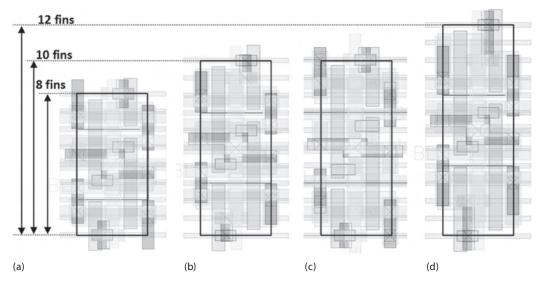

This chapter focuses on the development of a realistic PDK for academic use that overcomes these limitations. The PDK, developed for the N7 node even before 7 nm processes were available in the industry, is thus *predictive*. The predictions have been based on publications of the continually improving lithography, as well as our estimates of what would be available at N7. The original assumptions are described in Clark et al. (2016). For the most part, these assumptions have been accurate, except for the expectation that extreme ultraviolet (EUV) lithography would be widely available, which has turned out to be optimistic. The background and impact on design technology co-optimization (DTCO) for standard cells and SRAM comprises this chapter. The treatment here includes learning from using the cells originally derived in Clark et al. (2016) in realistic designs of SRAM arrays and large digital designs using automated place and route tools.

#### 1.1.1 Chapter Outline

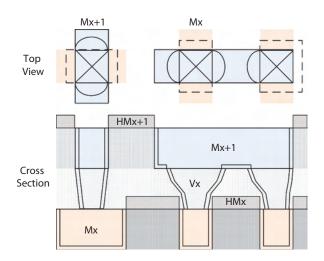

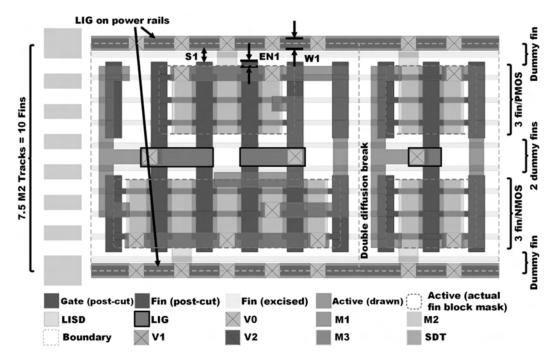

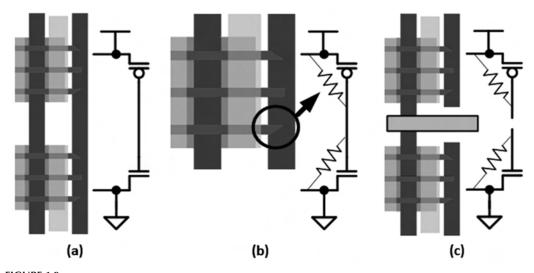

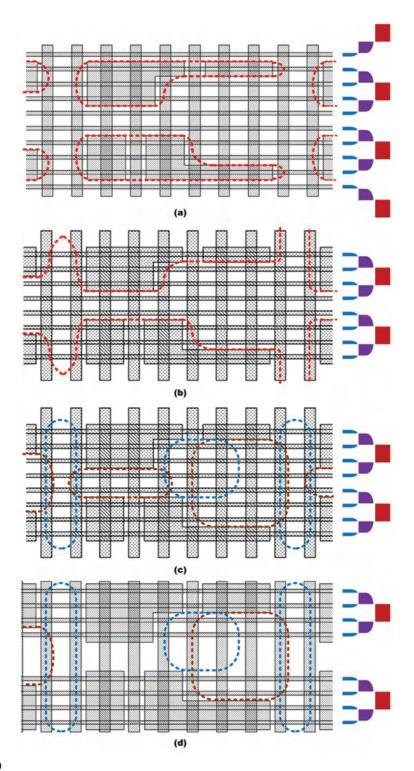

The chapter first outlines the important lithography considerations in Section 1.3. Metrics for overlay, mask errors and other effects that limit are described first. Then, modern liquid immersion optical lithography and its use in multiple patterning (MP) techniques that extend it beyond the standard 80 nm feature limit are discussed. This sets the stage for a discussion of EUV lithography, which can expose features down to about 16 nm in a single exposure, but at a high capital and throughput cost. This section ends with a brief overview of DTCO. DTCO has been required on recent processes to ensure that the very limited possible structures that can be practically fabricated are usable to build real designs. Thus, a key part of a process development is not just to determine transistor and interconnect structures that are lithographically possible, but also ensuring that successful designs can be built with those structures. This discussion is carried out by separating the front end of line (FEOL), middle of line (MOL), and back end of line (BEOL) portions of the process, which fabricate the transistors, contacts and local interconnect, and global interconnect metallization, respectively. The cell library architecture and automated placement and routing (APR) aspects comprise the next section, which with the SRAM results, comprise most of the discussion. The penultimate section describes the SRAM DTCO and array development and performance in the ASAP7 predictive PDK. The final chapter section summarizes.

#### 1.2 ASAP7 Electrical Performance

The PDK uses BSIM-CMG SPICE models and the value used are derived from publicly available sources with appropriate assumptions (Paydavosi et al. 2013). Drive current increase from 14 to 7 nm node is assumed to be 15%, which corresponds to the diminished  $I_{dsat}$  improvement over time. In accordance with modern devices, saturation current was assumed to be 4.5x larger than that in the linear region (Clark et al. 2016). A relaxed 54 nm contacted poly pitch (CPP) allows a longer channel length and helps

with the assumption of a near ideal subthreshold slope (SS) of 60 mV/decade at room temperature, along with a drain-induced barrier lowering (DIBL) of approximately 30 mV/V. P-type metal-oxide-semiconductor (PMOS) strain seems to be easier to obtain according to the 16 and 14 nm foundry data and larger Idsat values for PMOS than those for n-type metal-oxide-semiconductor (NMOS) have been reported (Wu et al. 2013; Lin et al. 2014). Following this trend, we assume a PMOS to NMOS drive ratio of 0.9:1. This value provides good slew rates at a fan-out of six (FO6), instead of the traditional four.

Despite the same drawn gate length, the PDK and library timing abstract views support four threshold voltage flavors, viz. super low voltage threshold (SLVT), low voltage threshold (LVT), regular threshold voltage (RVT), and SRAM, to allow investigation into both high performance and low-power designs. The threshold voltage is assumed to be changed through work function engineering. For SRAM devices the very low leakage using both a work function change and lightly doped drain (LDD) implant removal. The latter results in an effective channel length ( $L_{eff}$ ) increase, GIDL reduction and, the overlap capacitance reduction. The drive strength reduces from SLVT to SRAM. The SRAM V<sub>th</sub> transistors are convenient option for use in retention latches and designs that prioritize low-standby power. In addition to typical-typical (TT) models, fast-fast (FF) and slow-slow (SS) models are also provided for multi-corner APR optimization. Tables 1.1 and 1.2 show the electrical parameters for single fin NMOS and PMOS, respectively, for the TT corner at 25°C (Clark et al. 2016). The nominal operating voltage is  $V_{DD} = 700 \text{ mV}$ .

| Turite in the second se |       |       |       |       |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|--|--|

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SRAM  | RVT   | LVT   | SLVT  |  |  |

| I <sub>dsat</sub> (μA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 28.57 | 37.85 | 45.19 | 50.79 |  |  |

| $I_{eff}(\mu A)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 13.07 | 18.13 | 23.56 | 28.67 |  |  |

| I <sub>off</sub> (nA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0.001 | 0.019 | 0.242 | 2.444 |  |  |

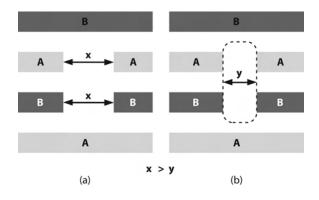

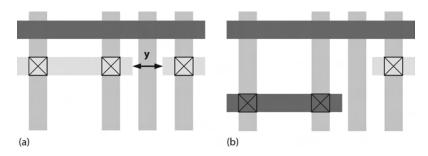

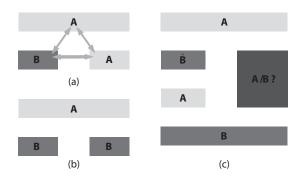

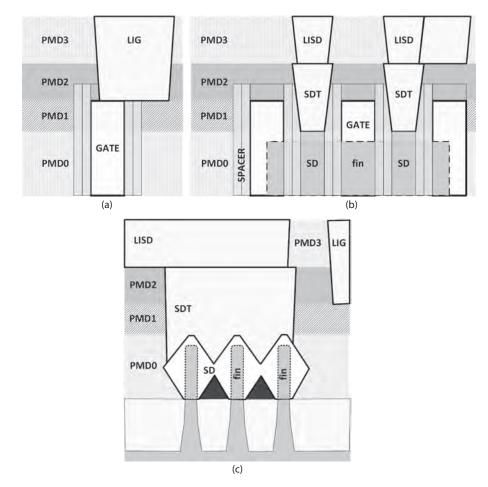

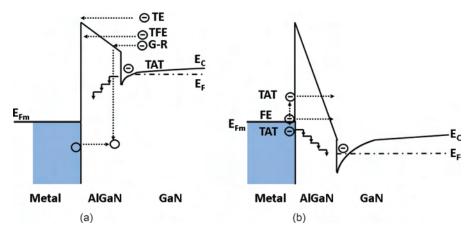

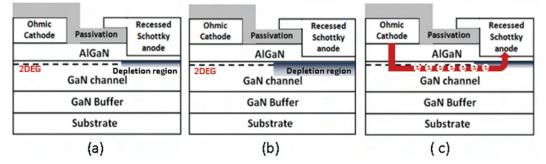

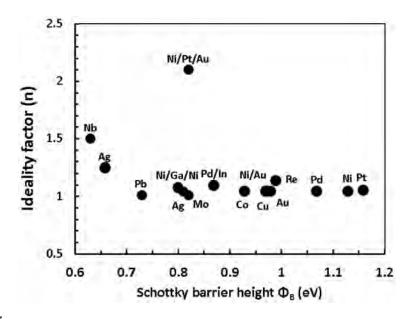

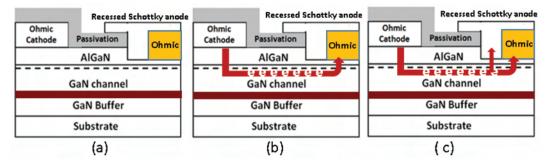

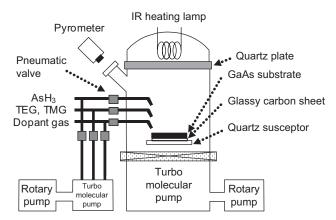

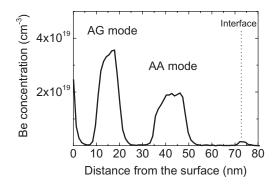

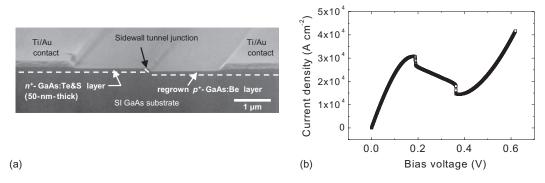

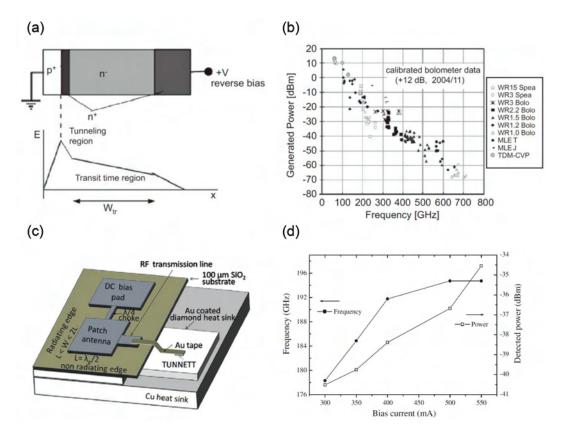

| V <sub>tsat</sub> (V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0.25  | 0.17  | 0.10  | 0.04  |  |  |