# ELECTRONIC AND PHOTONIC CIRCUITS AND DEVICES

## IEEE Press 445 Hoes Lane, P.O. Box 1331 Piscataway, NJ 08855-1331

#### **IEEE Press Editorial Board**

Roger F. Hoyt, Editor-in-Chief

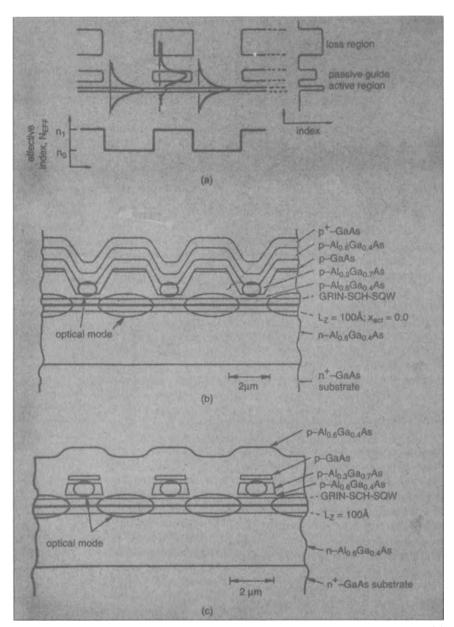

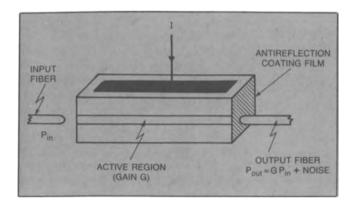

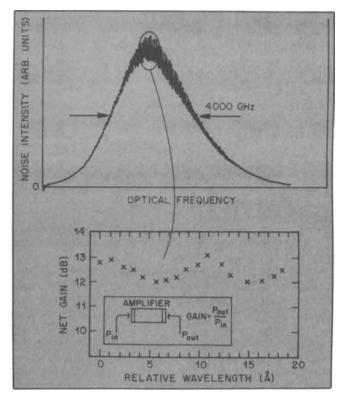

J. B. Anderson P. M. Anderson M. Eden M. E. El-Hawary S. Furui A. H. Haddad R. Herrick S. Kartalopoulos D. Kirk P. Laplante M. Padgett W. D. Reeve G. Zobrist

Kenneth Moore, Director of IEEE Press John Griffin, Acquisition Editor Marilyn G. Catis, Assistant Editor Mark Morrell, Assistant Production Editor

IEEE Circuits and Systems Society, Sponsor CAS-S Liaison to IEEE Press, Gordon Roberts IEEE Components, Packaging, and Manufacturing Technology Society, Sponsor CPMT-S Liaison to IEEE Press, Joe Brewer

Cover design: Bill Donnelly, WT Design

#### Books of Related Interest from IEEE Press ...

#### NONVOLATILE SEMICONDUCTOR MEMORY TECHNOLOGY: A Comprehensive Guide to Understanding and Using NVSM Devices Edited by William Brown and Joe Brewer 1997 ISBN 0-7803-1173-6 Hardcover 616 pp IEEE Order No. PC5644 THE CIRCUITS AND FILTERS HANDBOOK Edited by C. H. Chen 2896 pp 1995 Hardcover ISBN 0-8493-8341-2 IEEE Order No. PC5631 **INTRODUCTION TO OPTICS AND OPTICAL IMAGING Craig Scott** 1998 Hardcover 400 pp IEEE Order No. PC4309 ISBN 0-7803-3440-X **PHOTONIC SWITCHING TECHNOLOGY: Systems and Networks** Edited by Hussein T. Mouftah and Jaafar M. H. Elmirghani

1999 Hardcover 612 pp IEEE Order No. PC5761 ISBN 0-7803-4707-2

# ELECTRONIC AND PHOTONIC CIRCUITS AND DEVICES

**Edited by**

**Ronald W. Waynant** Food and Drug Administration, U. S. Government

> John K. Lowell Jekyll Consulting, Dallas, Texas

IEEE Circuits and Systems Society, *Sponsor* IEEE Components, Packaging, and Manufacturing Technology Society, *Sponsor*

A Selected Reprint Volume

IEEE Press Series on Microelectronic Systems Stuart K. Tewksbury, *Series Editor*

The Institute of Electrical and Electronics Engineers, Inc., New York

This book may be purchased at a discount from the publisher when ordered in bulk quantities. Contact:

> IEEE Press Marketing Attn: Special Sales 445 Hoes Lane, P.O. Box 1331 Piscataway, NJ 08855-1331 Fax: (732) 981-9334

For more information on the IEEE Press, visit the IEEE home page: http://www.ieee.org/

© 1999 by the Institute of Electrical and Electronics Engineers, Inc., 3 Park Avenue, 17th Floor, New York, NY 10016-5997

All rights reserved. No part of this book may be reproduced in any form, nor may it be stored in a retrieval system or transmitted in any form, without written permission from the publisher.

Printed in the United States of America

10 9 8 7 6 5 4 3 2 1

ISBN 0-7803-3496-5

**IEEE Order Number: PP5748**

#### Library of Congress Cataloging-in-Publication Data

Electronic and photonic circuits and devices / edited by Ronald W. Waynant, John K. Lowell. p. cm.—(IEEE Press series on microelectronic systems) "IEEE Circuits and Systems Society, sponsor; IEEE Components, Packaging, and Manufacturing Technology Society, sponsor." "A selected reprint volume." ISBN 0-7803-3496-5 1. Electronic circuits. 2. Electronic apparatus and appliances. 3. Optoelectronic devices. I. Waynant, Ronald W. II. Lowell, John. III. IEEE Circuits and Systems Society. IV. IEEE Components, Packaging & Manufacturing Technology Society. V. Series. TK7867.E36 1998 621.3815—dc21 98-41717 CIP

# CONTENTS

Preface vii

Acknowledgments ix

1

Theme Paper

Maxwell's Children Light the Way 3 Anthony J. DeMaria (*IEEE Circuits and Devices Magazine*, March 1991).

# Chapter 1 Integrated Circuit Technology 11

Modeling GaAs/AlGaAs Devices: A Critical Review13Herbert S. Bennett (IEEE Circuits and Devices Magazine, January 1985).OverviewOverview22Harry T. Weaver (IEEE Circuits and Devices Magazine, July 1987).Latchup in CMOS Technologies25Ronald R. Troutman (IEEE Circuits and Devices Magazine, May 1987).Porous Silicon Techniques for SOI Structures32Sylvia S. Tsao (IEEE Circuits and Devices Magazine, November 1987).Ferroelectric Materials for 64 Mb and 256 Mb DRAMs37Laureen H. Parker and Al F. Tasch (IEEE Circuits and Devices Magazine, January 1990).

# Chapter 2 Integrated Circuit Manufacturing and Novel Circuit Design 47

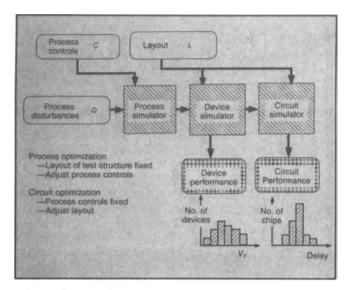

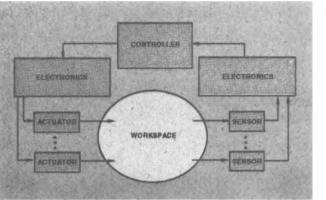

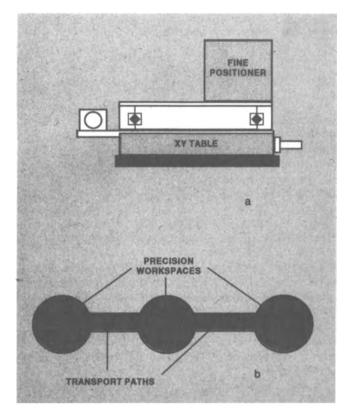

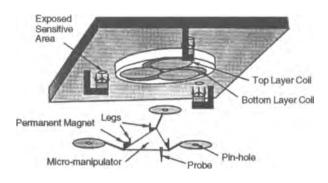

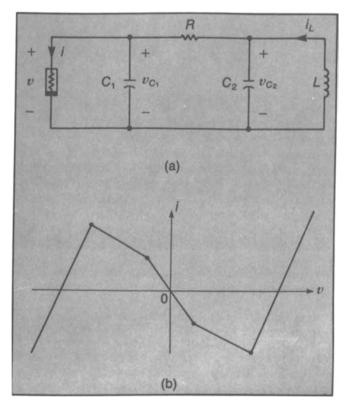

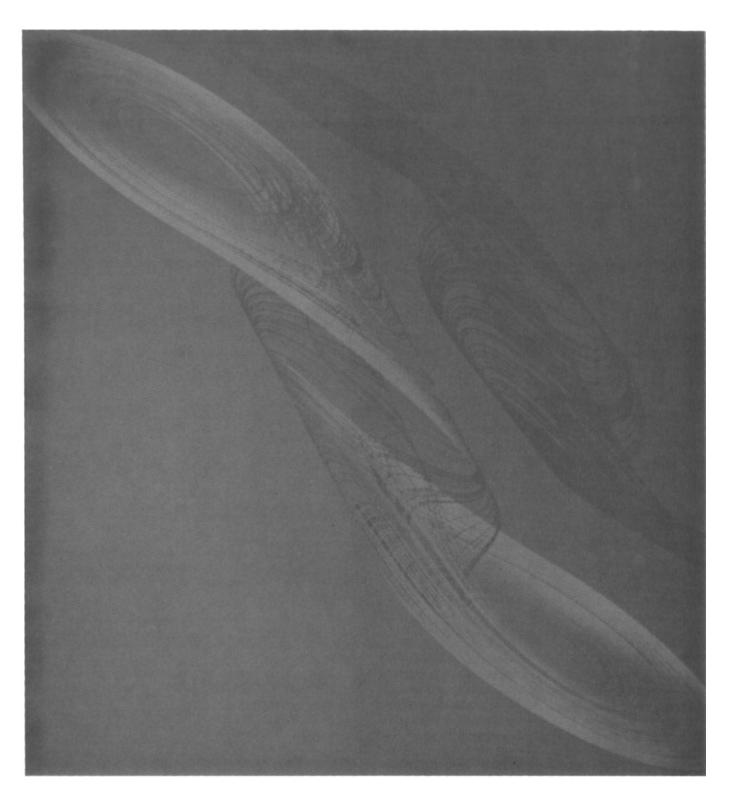

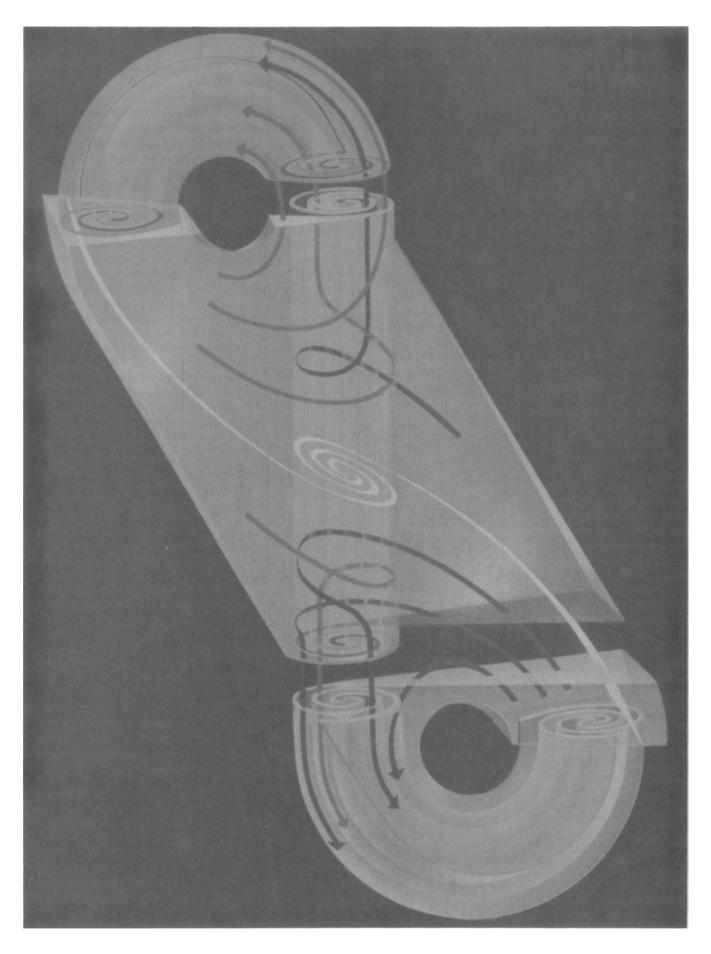

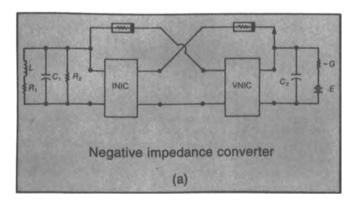

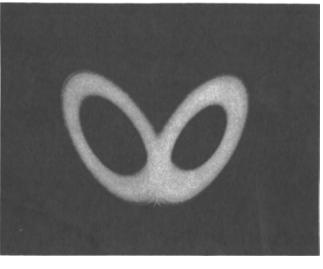

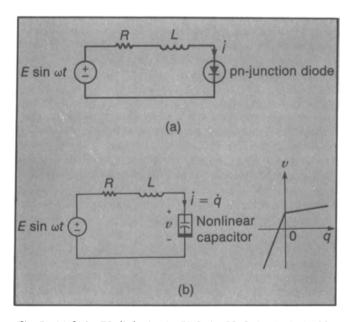

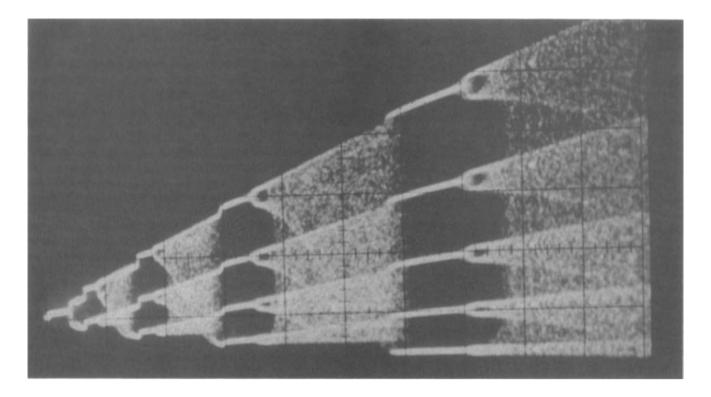

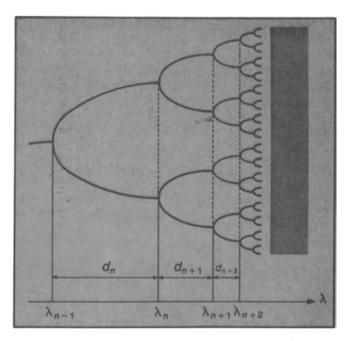

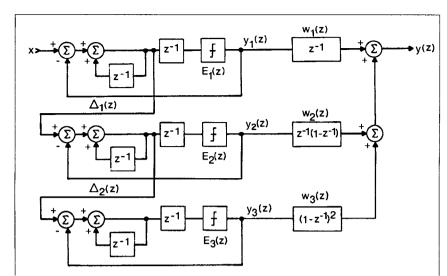

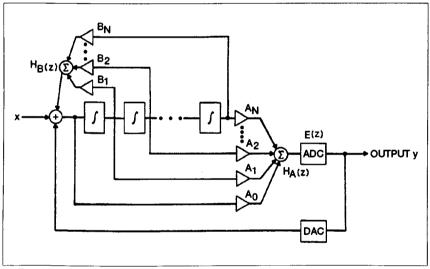

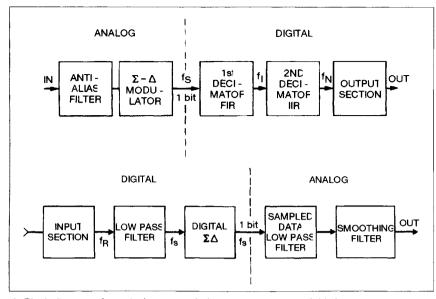

Manufacturing-Based Simulation: An Overview 49 Stephen W. Director (IEEE Circuits and Devices Magazine, September 1987). Micro-Automating Semiconductor Fabrication 56 Ilene J. Busch-Vishniac (IEEE Circuits and Devices Magazine, July 1991). **Robotic Applications in Electronic Manufacturing** 62 John H. Powers, Jr. (IEEE Circuits and Devices Magazine, January 1985). Sights and Sounds of Chaos 66 Leon O. Chua and Rabinder N. Madan (IEEE Circuits and Devices Magazine, January 1988). Introduction to Implantable Biomedical IC Design 77 Larry J. Stotts (IEEE Circuits and Devices Magazine, January 1989). **Oversampled Data Conversion Techniques** 84 Vladimir Friedman (IEEE Circuits and Devices Magazine, November 1990).

# Chapter 3 Optical Technology 91

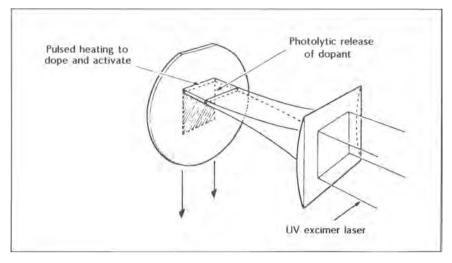

Photochemical Processing of Semiconductors: New Applications for Visible and Ultraviolet Lasers 93 J. Gary Eden (*IEEE Circuits and Devices Magazine*, January 1986). Contents

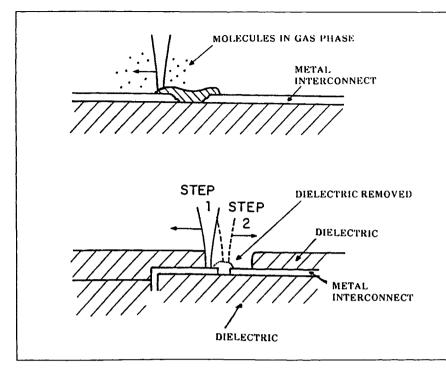

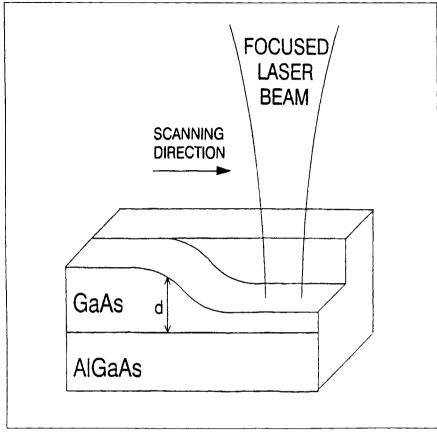

Laser-Enhanced Plating and Etching for Microelectronic Applications100Robert J. von Gutfeld (IEEE Circuits and Devices Magazine, January 1986).Excimer Laser Ablation and Etching104James Brannon (IEEE Circuits and Devices Magazine, March 1997).Laser-Fabrication for Solid-State Electronics112Richard M. Osgood, Jr. (IEEE Circuits and Devices Magazine, September 1990).Phase-Shifting Masks Gain an Edge119B.J. Lin (IEEE Circuits and Devices Magazine, March 1993).Advanced Lithography for ULSI127J. Bokor, A.R. Neureuther, and W.G. Oldham (IEEE Circuits and Devices Magazine, January 1996).

# Chapter 4 Optoelectronic Integrated Circuit Device Technology 133

Phase-locked Laser Arrays Revisited 135 Dan Botez and Luke J. Mawst (IEEE Circuits and Devices Magazine, November 1996). Quantum Well Semiconductor Lasers Are Taking Over 143 Amnon Yariv (IEEE Circuits and Devices Magazine, November 1989). Organic-on-Inorganic Semiconductor Heterojunctions: Building Blocks for the Next Generation of **Optoelectronic Devices** 147 S.R. Forrest (IEEE Circuits and Devices Magazine, May 1989). Semiconductor Optical Amplifiers 153 Gadi Eisenstein (IEEE Circuits and Devices Magazine, July 1989). Lasers Primer for Fiber-Optic Users 159 Joanne LaCourse (IEEE Circuits and Devices Magazine, March 1992).

# Chapter 5 Optical Fiber 165

Optical Fiber—The Expanding Medium167Suzanne R. Nagel (IEEE Circuits and Devices Magazine, March 1989).ViewPoint: Bringing Fiber to the Home177Richard K. Snelling (IEEE Circuits and Devices Magazine, January 1991).Fiber Optic Backbone Boosts Local-Area Networks181Scott F. Midkiff (IEEE Circuits and Devices Magazine, January 1992).

# Chapter 6 Optical Communication and Switching 187

Optoelectronic Integration: A Technology for Future Telecommunication Systems189R. F. Leheny (IEEE Circuits and Devices Magazine, May 1989).Photonic-Time Division Switching Systems193H.S. Hinton (IEEE Circuits and Devices Magazine, July 1989).Ultrashort Light Pulses198Peter W. Smith and Andrew M. Weiner (IEEE Circuits and Devices Magazine, May 1988).Optical Interconnects Speed Interprocessor Nets203John D. Crow (IEEE Circuits and Devices Magazine, March 1991).203

| Author | Index | 209 |  |

|--------|-------|-----|--|

|        |       |     |  |

Subject Index211

# About the Editors 217

# PREFACE

For nearly 14 years the IEEE has published *Circuits and Devices Magazine*, making it available first to the Societies of Division 1 but later to all IEEE members. We are proud of the accomplishments attributed to the magazine by its readers and its designation among the magazines with the greatest impact based on citations. During that time, we have solicited and published numerous tutorial papers describing new technology and new ideas. But the theme of what we believe is the future of our field of engineering was so well described by an article written by Anthony DeMaria that we wanted to preserve it and a number of supporting papers by others in a special collection. This collection expresses the state of the art and the thinking of the 1990s, and it projects the likely path that developers and engineers will follow for the next 25 or more years. It details the gradual, but inevitable, shift from electronic devices now being devised and improved to optoelectronics, in which a combination of optical and electronic devices predominate and on to the future systems in which photonics will be dominant. This kind of perspective, given in well-written, understandable form by experts in their field, can help direct students in choosing their future work in science.

Ronald W. Waynant John K. Lowell

# ACKNOWLEDGMENTS

We thank the authors who have kindly given permission for the reprinting of their original or revised papers and the IEEE for its permission and encouragement. We also thank Eve Protic and Mark Protic for their assistance at the beginning of this project and Marcia Patchan for pushing it through to completion.

Ronald W. Waynant John K. Lowell

# **THEME PAPER**

# Maxwell's Children Light the Way

Photonics, as a complement to electronics, will initially capture markets where connection to the electronic interface is easy

# Ĩ

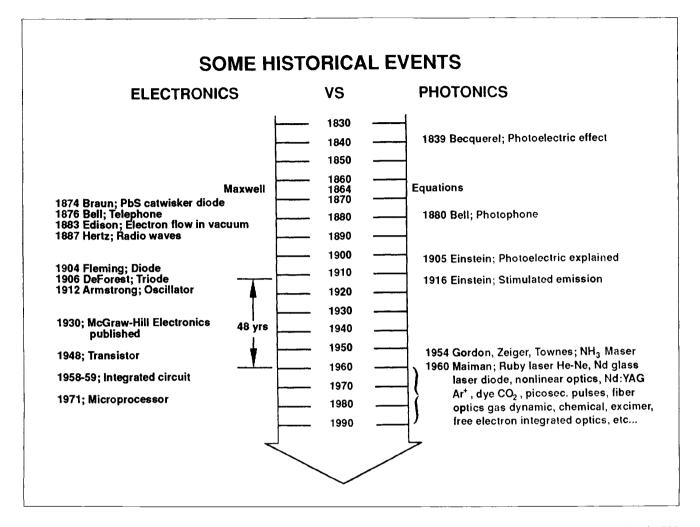

wentieth-century electronics is the child of 19th-century electromechanics and the parent of 21st-century photonics. The electronics industry, and its growth, is certainly in-

debted in large part to E. H. Armstrong, and his first electronic oscillator in 1912. The first optical oscillator. i.e., Ted Maiman's ruby laser, didn't glow until 48 years later (Fig. 1). It took electronics approximately 80 years to develop its markets and technology to where they are today. In contrast, last year marked the 30th anniversary of Maiman's first laser. If we assume that photonics will experience the same rate of technology, market, and manufacturing development that electronics did, we can predict that the photonics market will equal that of its electronics counterpart as we approach midway into the 21st century. Unfortunately, the prediction may be too optimistic, because electronics possesses the lower-cost advantage associated with a mature technology. Consequently, photonics will initially be most successful when we use it (1) to perform functions that cannot be performed as well, or at all, by electronics; and (2) in applications where photonics can easily interface with electronics.

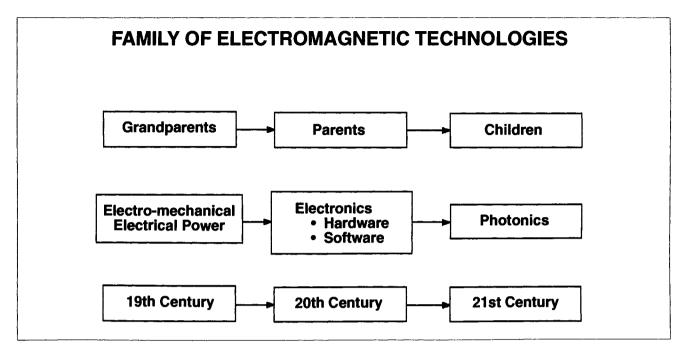

Three major technological generations have their genealogical roots in the equations James Clerk Maxwell formulated in 1864. Technologies based on electromagnetics and electromechanics such as motors, generators, magnetics, and power transmission, experienced their major growth in the 19th century and began to mature in the first part of the 20th century. (The membership of the American Institute of Electrical Engineers— AIEE—reached a peak of 18,344 in 1927. In 1955 or 1956, the membership of the Institute of Radio Engineers (IRE) surpassed the AIEE's membership. In 1963, the two organizations merged to form the IEEE.)

The last three quarters of the 20th century have been a period of dramatic growth for electronics-based technologies. The rate of development does not yet show evidence of slowing down, but these technologies can be expected to mature in the first half of the 21st century.

In the family tree of major technologies that are based on Maxwell's equations, one can think of electrically and magnetically based technologies as the grandparents; electronics hardware and software as the parents; and the subgroups of photonics technology as the children (Fig. 2). The growth of photonics is just beginning. Its maturity will probably begin in the latter half of the 21st century.

Reprinted from IEEE Circuits and Devices Magazine, Vol. 7, No. 2, pp. 36-43, March 1991.

#### by Anthony J. DeMaria

#### **Electronics Overview**

Ferdinand Braun, working in Marburg, Germany, in 1874, discovered the first metal semiconductor junction by establishing the rectifying properties of galena (i.e., lead sulfide). These "cat whisker" diode detectors played an important role in researching radio waves and their propagation before the invention of vacuum tubes, but their physics was not understood until the development of semiconductor solid-state physics in this century.

While working on his carbon filament lamp in 1883, Thomas Edison discovered that electrical current could be made to flow in a vacuum when an electrically positive charged plate was positioned near a heated filament within a vacuum envelope. This discovery remained essentially unused until John Ambrose Fleming invented the vacuum diode rectifier for converting alternating current to direct current in 1904 [1]. This invention was followed two years later by Lee DeForest's vacuum triode— the first electronic amplifier. Armonstrong's oscillator followed, the first generation of temporal coherent electromagnetic radiation.

Following Armstrong's invention, the electronics industry developed very rapidly. Electronic vacuum-tube devices became the heart of the industry and were responsible for the rapid development of radio, radar, television, electronic controls, telecom-

munications, and electronic information processing, among many other technologies. Twenty-nine years elapsed from Edison's discovery to the operation of the first electronic oscillator. McGraw-Hill published the first trade magazine with the title Electronics beginning on April 30, 1930. (The word "electronic" did not appear in dictionaries until many years later.) The term is now used to denote the broad range of technologies dependent on controlling the flow of electrical charges in a vacuum, solid, liquid, or plasma. But until the invention of the transistor in 1948, the field of electronics was primarily dependent on vacuum tubes, which exerted control over the flow of an electron stream in a vacuum.

In 1948, John Bardeen, Walter H. Brattain and William Shockley of Bell Labs announced the invention of the transistor. Transistor-type devices control the flow of either positive charged particles (holes) or negative charged particles (electrons) in a crystalline solid. At first germanium was the crystal of choice, but silicon soon came into almost exclusive use because of its superior mechanical and electrical properties. In addition, it was soon recognized that silicon's easily grown native protective oxide has exceptional electrical properties. For a short while, transistor-type devices were resisted by the electronics industry. But their small

1. Major historical events in the development of the electronic and photonic fields.

Ć

size, high efficiency, mass producibility, lower unit cost, lower voltage requirements, and higher reliability in comparison with vacuum tubes led to their eventual dominance in the electronics field, a dominance that occurred even though the manufacturability of transistors was considerably more capital intensive and difficult to master.

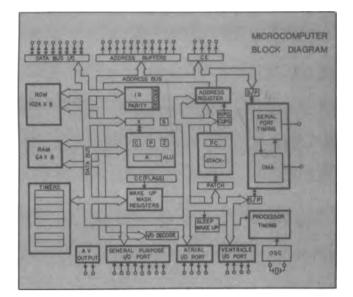

In 1958-59, the semiconductor integrated circuit was invented by Jack Kilby of Texas Instruments and Robert Noyce of Fairchild Semiconductor [2]. The integrated circuit chip enabled an entire electronic system to be miniaturized on a small piece of silicon and launched the modern information processing revolution. The development of the microprocessor by Intel in 1971 gave birth to the pocket calculator and, eventually, to personal computers and workstations.

If the invention of the triode in 1906 marked the start of the electronics revolution, then the field of electronics is today a little over eighty years old. Clearly, its tempo is still increasing. In 1970, \$1,000 could purchase approximately 400 barrels of oil or 40 kilobytes of semiconductor random access memory (RAM). In 1985, \$1,000 could purchase approximately 30 barrels of oil or 25 megabytes of RAM. The amount of oil one could buy per dollar decreased by over an order of magnitude over a 15 year period while the amount of RAM bytes per dollar increased by over two orders of magnitude. The long-term cost of semiconductor memory circuits is still dropping rapidly, which indicates that the information revolution is still continuing at a rapid pace.

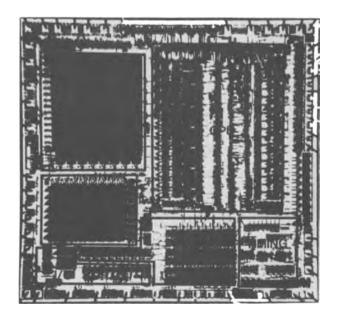

The semiconductor industry has been on an exponential growth path for the last 30 years. Worldwide revenues now total about \$30 billion. The industry produces the equivalent of 250,000 transistors per year for every person on earth. Over the last two decades, the numbers of transistors produced per year has doubled every year. An integrated circuit with a million transis-

tors today sells for the same price as did a single transistor in the early days of the industry. The layout print of a 4-megabit dynamic random access memory (DRAM) chip is equivalent to the task of drawing a road map of the entire United States showing every side street. A deficiency, during the manufacturing process of such a chip, is equivalent to a large pothole showing up on any street on such a map, and such a defect would necessitate rejecting the whole chip. Such chips will enter production in the near future. Work has started on 16- and 64-megabit DRAM chips. The layout for these chips is like drawing a map of the entire United States in such detail that even sidewalks are shown in the drawing. Such designs could not be effectively accomplished without sophisticated computers.

Advances in integrated circuits produce advances in computers, which in turn produce more advances in integrated circuits. This process continues to repeat itself, and electronics provides effective technological feedback that contributes to it's own explosive growth.

#### **Parallel Advances in Photonics**

In 1839, Alexandre Edmond Becquerel of France discovered the photodetector—the first opto-electronic device— when he generated a voltage by irradiating the junction of an electrolyte. The effect was not understood until Albert Einstein explained it in 1905.

Even though photoelectric devices were not understood, they were used by researchers. Alexander Graham Bell used a photoelectric device in his photophone of 1880, which was the first electro-optical system [1]. Einstein presented his formulation of stimulated and spontaneous emission processes and their relationship to the radiation absorption process in atomic and molecular systems in 1916. After 1916, many scientists investigating the spectroscopic properties of gases realized that population inversion in atomic and molecular systems would result in amplification of radiation through the stimulated emission process, but they ignored its development.

Why didn't scientists in the 1916-to-1954 time period ask themselves how they could exploit stimulated emission to obtain an optical oscillator? The most likely answer is that the researchers investigating the spectroscopic properties of gases did not adequately appreciate the principle of positive feedback, revealed by Armstrong in 1912 with electronic oscillators.

The cultural divide between physicists and electrical engineers was bridged by World War II. The importance of microwave radar during the war caused many scientists to work on microwave oscillators and amplifiers. One of these scientists was C. H. Townes, whose research exposed him to the principles of positive feedback in 2. In the family tree of major technologies that are based on Maxwell's equations, electrically and magnetically based technologies may be viewed as the grandparents; electronics hardware and software as the parents; and the subgroups of photonics technology as the children.

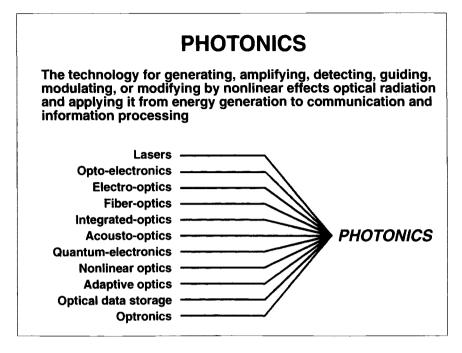

3. The term "photonics" now denotes a large number of optically related technologies.

electronic microwave oscillators. This experience, coupled with his spectroscopic training, provided him with the technical foundation required for the invention of the microwave NH<sub>3</sub> maser in 1954 [3]. This device was the first quantum electronic oscillator. In retrospect, providing positive feedback in the microwave region in a population-inverted molecular system was a relatively straightforward undertaking. But doing the same thing in the optical region required another new invention: the use of a Fabry-Perot interferometer as a multipleaxial-mode, positive-feedback optical cavity for population-inverted atomic or molecular amplifiers [4].

T. H. Maiman's ruby laser of 1960 was the first operation of a coherent electromagnetic oscillator in the optical region [5]. Contrary to the relatively mild attention given the announcement of the transistor in 1948, the laser was greeted with great excitement and expectation by the scientific and engineering communities, as well as the general public. The technical community realized that the laser would make possible the transportation of techniques and technologies from the audio, video, radio-frequency, and microwave regions into the optical portion of the electromagnetic spectrum.

Researchers quickly made the transition from maser to laser research, and there was an explosion of scientific activity and discovery. In less than 20 years, the following lasers were rapidly developed: helium-neon, glass, argon, argon ion, dye, CO<sub>2</sub>, chemical, excimer, free-electron, gas dynamic, Nd<sup>3+</sup>: glass, Nd<sup>3+</sup>:YAG, and semiconductor laser diodes. Broad advances were secured in the areas of optical parametric amplifiers; picosecond laser-pulse generation; fiber optics; Q-switching, holography, nonlinear optics, optical mixing, integrated optics; optical phase conjugation; and optically squeezed states. Laser devices provided the major stimulation for the broad field of photonics after 1960 in the same way that the vacuum tube stimulate electronics after 1906.

After the invention of the laser, new terms such as quantum electronics, electrooptics, lidar, and optical information processing, were coined to name the numerous new specialties that depended on laser devices. It soon became apparent that an umbrella term was needed to refer to all of these specialties, much as the term "electronics" covered the large number of fields dependent on electronic devices. Since these optical specialties are dependent on the control of a light beam, i.e., a stream of photons, the term "photonic" was formed by adding "ic" to the word "photon." The term is now used to refer to the technologies for generating, amplifying, detecting, guiding, and modulating coherent optical radiation and applying these technologies to fields such as energy generation, communications, and information processing (Fig. 3).

#### **Going Down the Same Road**

The parallelism is apparent in the development of electronics and photonics. Optically pumped solid-state lasers, gas lasers, and dye lasers, for example, perform the same role in photonics as vacuum-tube devices perform in electronics. Both devices were responsible for the initial rapid development of their respective fields, and they all enjoy much the same advantages and disadvantages. Lasers, like vacuum tubes, are capable of the highest power and operating frequency within their electromagnetic regions. And, like vacuum tubes, they suffer from heavier weight, larger size, higher power consumption, and lower life expectancy than their solid-state counterparts.

Semiconducting laser and transistor devices also play parallel roles in their respective fields. As in electronics, it is the semiconductor lasers and their associated applications that offer the largest market opportunities because of their small size, lower weight and power consumption, mass producibility, lower cost, higher reliability, and ability to be integrated on monolithic substrates utilizing microelectronic fabrication techniques. Semiconductor lasers also interface easily with transistors. Consequently, semiconductor lasers can take advantage of the rapid market growth and the large existing technology infrastructure that transistor devices presently enjoy.

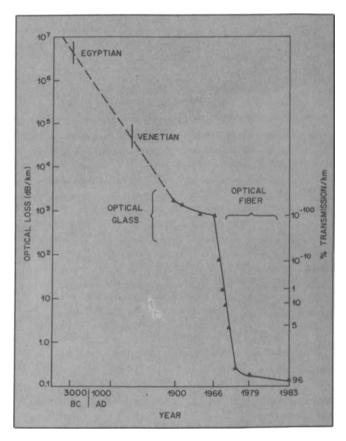

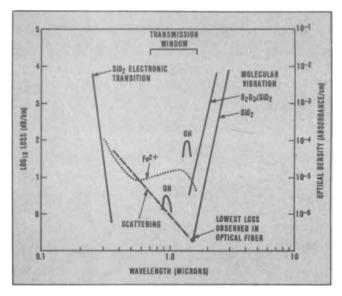

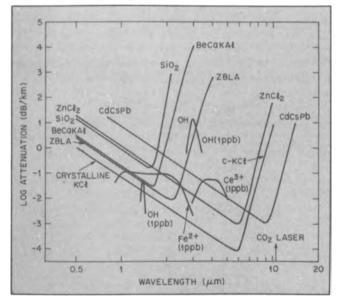

In electronics, waveguides such as coaxial cables, strip lines, and metal guides were used before active semiconductor devices became dominant. In photonics, semiconductor laser devices were invented a few years after the announcement of the ruby laser. Until K. C. Kao proposed it in 1966, researchers did not appreciate that losses could be greatly reduced in glass fibers [6]. Then, research programs were launched in earnest by several organizations to develop glass fibers for telecommunication optical-waveguide applications. In 1970, Corning Glass Works achieved losses below 20 dB/km, a level considered critical to the extensive application of fiber optics to telecommunication. Today, glass-fiber losses have been reduced to near the theoretical limit, and glass fibers are the transmission line of choice for telecommunication applications. Telecommunication is presently the largest market for photonics.

Researchers today are busy developing integrated optical technology to achieve the benefits for the photonics field that semiconductor integrated circuits have achieved for the electronics field. It is important not to confuse the huge role that integrated digital electronic circuits have played in digital data processing with the role that integrated optics chips are expected to play in photonics. At present, it appears that the appropriate parallelism is between the role that microwave integrated circuits, microwave/millimeter-wave strip lines, and microwave/millimeter-wave hybrid circuits play in the lower frequency region, and the role that optical integrated circuits are expected to play in the optical region. With present technology, microwave monolithic integrated circuits (MIMICs) cannot match the density of digital integrated circuits. And optical integrated circuits will not match the density of MIMIC chips with presently

foreseen optical technology.

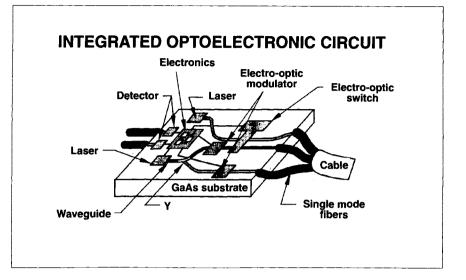

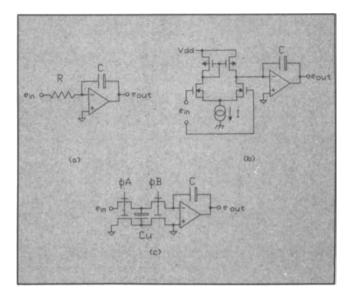

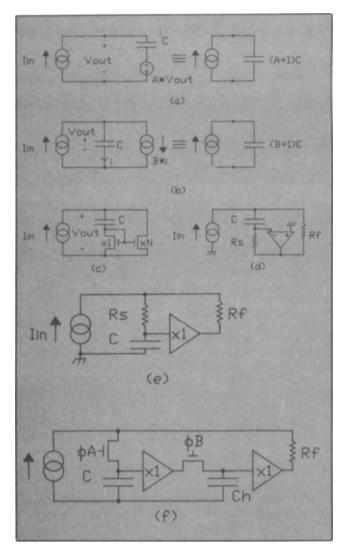

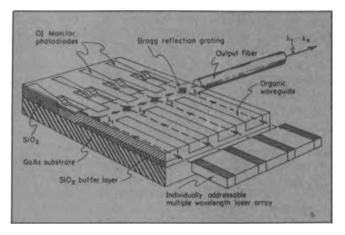

Compound semiconductor materials such as GaAs and GaAlAs are unique when compared to silicon and germanium, because they can be used to generate optical radiation. They are also electro-optically and piezoelectrically active, and have good semiconductor properties for the fabrication of transistors. Consequently, current research efforts are being aimed at merging integrated electronic circuits with integrated-optic, opto-electronic, electrooptic, and even acousto-optic devices on monolithic substrates of GaAs and similar compound materials (Fig. 4). Monolithic optical chips do exist today, typically combining a few optical components on a LiNbO3 substrate (Fig. 5).

#### **Microelectronics and Photonics**

Light emitting diodes fabricated from GaAs for numerical display applications appeared in the late 1950s. In 1962, GaAs lasers operating in the near infrared were first reported by General Electric, IBM, and Lincoln Lab researchers. These reports ensured that semiconductor devices would play a major role in photonics. Today, lead-salt semiconductor lasers have extended the operating-wavelength range of semiconductor lasers into the far infrared region, and GaAs-based semiconductor lasers have operated in the red portion of the visible spectrum. In the future, higher-bandgap materials may permit semiconductor lasers in the blue portion of the spectrum.

The compatibility of semiconductor lasers with microelectronic devices has

4. An example of a potential integrated optoelectronic circuit that researchers may some day realize [7]. Optical signals can be brought to such a chip by optical fibers. Optical radiation from these fibers can be coupled into planar waveguides embedded within the chip. Photodetectors fabricated on the chip can convert the optical signals to electrical signals, which can be digitally processed by electronic devices also fabricated on the chip. These electrical signals can then be used to modulate semiconductor lasers directly or to energize electro-optic modulators that are also fabricated directly on the chip. The modified optical signals are then transported through the chip by embedded planar waveguides and eventually coupled to optical fibers for transmission to remote locations. Only small portions of such a chip have been reported in the technical literature thus far, but the potential is clear.

\*

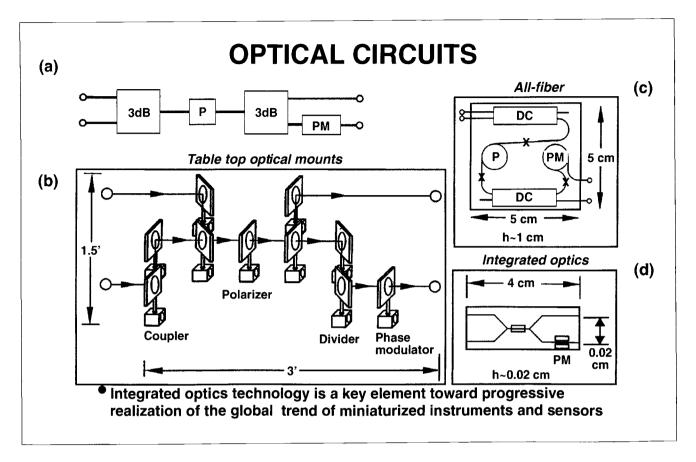

5. This typical optical circuit (a) contains four optical components: a 3 dB power combiner, a polarizer (P), a 3 dB power splitter, and a phase modulator (PM). It is useful in realizing miniature, low cost fiber-optic gyros for navigational applications. It is possible to fabricate a discrete-optical-component version consisting of mirrors, a polarizer and an electro-optics phase modulator (b). The all-fiber configuration (c) is much smaller, with typical dimensions of  $5 \times 5 \times 1$  cm. An integrated-optics-chip configuration (d) can be as small as  $4 \times 0.02 \times 0.02$  centimeters.

Ò

launched major segments of existing markets. Among these are fiber-optic telecommunication, optical data recording, audio disks, video disks, laser printers, and bar-code readers. These markets are served by the semiconductor laser. (The He-Ne laser is now a far-distant second in annual production.) Manufacturers are producing several hundred thousand semiconductor lasers per month.

Laser weapons, controlled fusion with lasers, and semiconductor laser development are the three areas of laser technology that have received continuous and extensive R & D support over the last 25 years. The first two are still a long way from making a national impact, but they have received extensive government support in many countries because of their perceived importance to national security and economical well-being. The semiconductor laser, on the other hand, has been developed primarily with industrial R&D funds, and it has been the most successful in spawning new sectors of existing industries. It is therefore important to have a manufacturing competitiveness in semiconductor lasers if a nation is to maintain competitiveness in photonics.

Microelectronics processing technology has developed a large assortment of processing techniques that yield feature dimensions that fall within the range of optical wavelengths. Consequently, the application of semiconductor processing technology such as epitaxial film deposition, etching, milling, photolithography, and ion implantation, advances photonics by advancing optical technology and originating new subfields. These subfields include binary/diffractive optics, micro<sup>1</sup>ens fabrication, new optical coatings, integrated optics, and super-lattice devices.

Such contributions are enabling photonics to interface easily with microelectronics and are producing many instances in which photonics are being integrated directly with microelectronics devices and subsystems. This "partnership" between photonics and electronics contributes to the explosive growth of photonics in telecommunications, signal and data processing, information storage, entertainment products, computing, data buses, interconnections of electronic subsystems, sensors, medical applications, and scientific instrumentation. The growth is pushing photonics into large-volume, low-cost, mass-production manufacturing that requires large capitalization rivaling that required for manufacturing of electronic components and subsystems.

The strong interdependence of photonics and electronics has educational effects, too; more and more university-based programs offer a wide selection of graduate and undergraduate optics-related courses. As a result, the center of mass for training in optics has shifted from physics departments to electrical engineering departments.

#### Things to come

Photonics is still in a state of infancy. It is young and robust with a highly promising and exciting future. The field is now spawning new products and opening major new segments of basic industries. Accelerating growth in fiber-optic telecommunications, optical data buses, optical data storage, optical interconnects between electronic subsystems, and many other applications, will ensure the growth of photonics well into the next century.

Photonics and electronics are complementary and not competitive; indeed, photonics is heavily dependent on electronics. Consequently, the most success in the near term will be in applications where photonics interfaces easily with electronics and advantages can be taken from the large infrastructure and momentum for growth that the electronic revolution still enjoys. And by its own growth, photonics will reciprocate and further expand the growth of electronics.

The most serious challenge facing photonics is the shortage of the photonics engineers required to develop the numerous new and rapidly evolving products, and to work at the interface between electronics and photonics. Offering a formal undergraduate engineering curriculum in photonics engineering would be a big boost to this important, though still emerging, field. A formal curriculum would ensure that the photonics revolution will succeed the electronics revolution just as the electronics revolution succeeded the old industrial revolution.

Just how large can photonics get? Can it exceed the field of electronics in market size? The answer will probably be "no" for a very long time, because of the relative maturity of electronics. Electronics has a half-century head start on photonics. It has a very large infrastructure, and large capital and knowledge bases that will difficult to abandon or overcome with a new technology. Indeed, comparing the memberships of electronics- and photonicsoriented professional societies illustrates the entrenchment of electronics. The Institute of Electrical and Electronics Engineers has approximately 300,000 members. The total membership of the Optical Society of America, the Society of Photo-optical and Instrumentation Engineers, the IEEE Lasers and Electro-optics Society, the Laser Association of America (LAA), and the Laser Institute of America (LIA), which together represent the field of photonics, have only about 30,000 members (and many of these have joint memberships.) It will be some time before the number of photonics engineers exceeds the the world's present number of electronics engineers. The arrival of photonics, however, will be no less important to society than was electronics.

#### Acknowledgment

This article was first presented as an invited

paper at the First International Workshop on Photonic Networks, Components and Applications, held in Montebello, Quebec, Canada on October 10-13, 1990, under the title Electronics and Photonics: Partners or Competitors.

#### Biography

Dr. Anthony J. DeMaria [F] is Assistant Director of Research for Electronics and Photonics Technologies at the United Technologies Research Center, East Hartford, Connecticut.

#### References

1. Special Commemorative Issue, 50 Years of Electronics (McGraw-Hill Publications, 1980).

2. The 30th Anniversary of the Integrated Circuit, VLSI System Design, Vol. IX, No. 9A, (1988).

3. J. P. Gordon, H. J. Zeiger, and C. H. Townes, *Physical Review* 95, (1954) p. 282.

4. A. L. Schawlow and C. H. Townes, *Physical Review* **112**, (1958) p. 1940.

T. H. Maiman, *Physical Review* 4, (1960) p. 564.

K C. Kao and G. A. Hockharn, Proceedings of the IEEE, 133, (1966) p. 1151.

7. Photonics, Maintaining Competitiveness in The Information Age, National Academy Press, Washington, DC, (1988).

# INTEGRATED CIRCUIT TECHNOLOGY

# Modeling GaAs/AlGaAs Devices: A Critical Review

Herbert S. Bennett

#### Abstract

Device models for GaAs devices and GaAs/AlGaAs heterostructures are much less advanced than those for silicon devices. This paper critically reviews recent advances in the modeling of GaAs/AlGaAs devices. It is based on the examination of five selected device models that contain features common to the majority of device models for heterostructure bipolar and field effect transistors. Areas requiring improved measurement techniques on processed GaAs and improved physical concepts for GaAs/AlGaAs device models are identified.

## Introduction

This review summarizes recent advances in modeling GaAs/AlGaAs heterostructure bipolar transistors (HBT) and GaAs and GaAs/AlGaAs field effect transistors (FET). It identifies those physical concepts that are not adequately included in present device models for HBTs, for conventional metal semiconductor FETs (MESFETs), and for heterostructure FETs (HFETs) such as two-dimensional electron gas FETs (TEG-FETs), modulation doped FETs (MODFETs), high electron mobility FETs (HEMTs), and selectively doped FETs (SDFETs). This review also identifies areas requiring increased efforts for measurement techniques on processed GaAs. The term processed GaAs refers to material that is representative of the active regions of devices and not to bulk material. This review is based on the examination of five device models that have been selected from among several available GaAs device models. The five device models discussed contain features and assumptions found in the majority of device models reported in the archival literature.

Developing computationally efficient models that simulate the operation of solid-state devices is one goal of workers in this area. Achieving this goal requires compromises between the sophistication of solid-state physics and the pragmatic demands of electrical engineering. There are two classes of computer models:

- (a) Compact models, which use the methods of Gummel-Poon or Ebers-Moll, based on closed form solutions to approximate device equations.

- (b) Detailed models based on doping profiles and numerical solutions to the coupled nonlinear semiconductor device equations with appropriate boundary conditions [1]. These equations are usually solved self-consistently by either finite element or finite difference procedures and in-

clude Poisson's equation, current-density equations for holes and electrons, and continuity equations for holes and electrons.

The discussion that follows pertains to detailed device models.

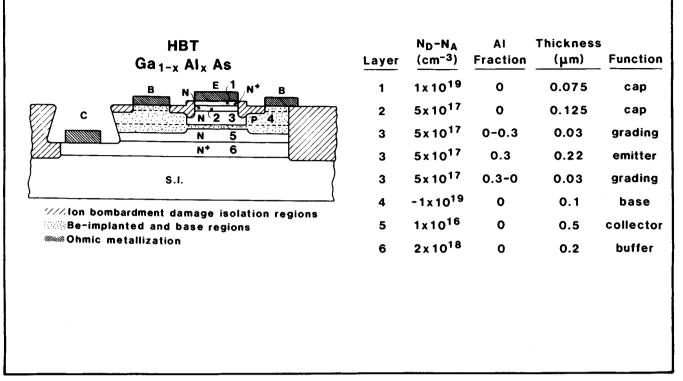

# **Typical Device Structures**

Figure 1 gives the structure for a device similar to the one investigated by Asbeck et al. [2]. This HBT avoids many of the tradeoffs in the design of homojunction bipolar transistors. The HBT has a wider bandgap emitter (layer 3). The greater bandgap of the emitter compared to the base reduces substantially the hole injection from the base into the emitter. Reducing the basewidth decreases the electron transit time in the device and thereby increases  $f_{\tau}$ . The conduction band spike is reduced by the compositional grading [3]. This increases the injected electron current and, therefore, the gain of the HBT. Such HBT devices with thin bases and high  $f_{\tau}$ s are fabricated by molecular beam epitaxy (MBE) or by organometallic vapor phase epitaxy (OMVPE).

Circuits containing HBTs, which are similar to the HBT in Fig. 1, and operating at 300 K or 77 K may compete with or exceed the ultrahigh performance of Josephson junction circuits at 4K [4]. However, before HBTs can be used in high-speed integrated circuits, improved fabrication technology needs to be devised. In particular, the number of defects in the substrate and the number of interface states at junctions need to be reduced.

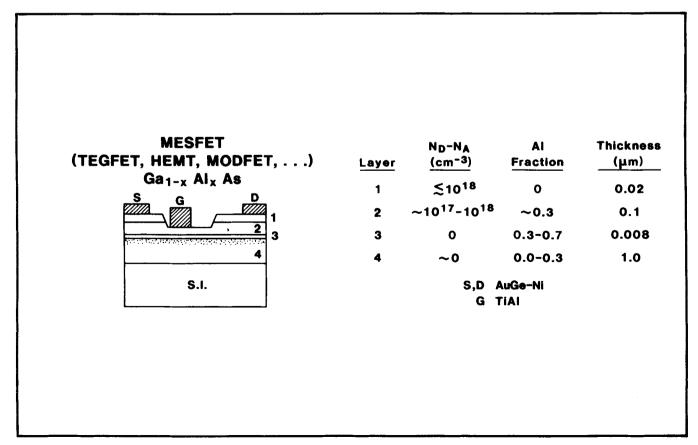

Figure 2 shows a typical heterostructure HFET, which is similar to the one reported in Ref. [5]. The main feature of these devices is to have the donors in a wider bandgap GaAl<sub>x</sub>As<sub>1-x</sub> layer (layer 2) and to have the electrons move in a nearby undoped GaAs channel (layer 4). These devices frequently have a spacer layer of undoped GaAs (layer 3) to shield the two-dimensional electron gas from the fields of the donors in layer 2. When the donor densities in layer 2 exceed about  $10^{17}$  cm<sup>-3</sup>, the electrons do not have a bound state associated with the donor ions. The electron-ion scattering becomes significant in layer 2 and lowers the electron mobility. The undoped layers 3 and 4 provide the required high mobility, active region of the device.

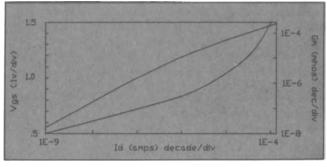

The nonlinearity of the HFET is good for  $L_s s \sim 1 \mu m$ and very good for  $L_s s \sim 0.5 \mu m$  [4]. This nonlinearity is the increase of  $g_m$  with small ( $V_{ss} - V_T$ ) and increases as  $\mu_n/L_s$  increases, where  $\mu_n$  is the mobility of the electron in the channel. The current gain-band-

Reprinted from *IEEE Circuits and Devices Magazine*, Herbert S. Bennett, "Modeling GaAs/AlGaAs Devices: A critical review, Vol. 1, No. 1, pp. 35-42, January 1985, U.S. Government work not protected by U.S. Copyright.

The views stated in this paper are those of the author and do not represent necessarily the views of the National Bureau of Standards.

width product increases as  $L_g$  decreases. Hence, to increase  $g_m$ s and  $f_r$ s, shorter gate lengths and higher mobilities are needed. Gate lengths less than  $0.5\mu$ m place unacceptable demands on lithographic precision for commercial production. Heterostructure HFETs offer ways to achieve mobilities that are higher than those for GaAs alone. Such FETs are called TEG-FETs [5], MODFETs, HEMTs [6], and SDFETs. One reason that similar devices are referred to by many names is that the understanding of how the devices function is incomplete. Most workers concentrate on how the carriers move in the channel and place less emphasis on how the carriers move from the source to the channel and from the channel to the drain.

# Representative Device Models and Associated Assumptions

Many HBT, MESFET, and HFET models exist in the literature. Most authors use the predictions from such models to perform numerical experiments and thereby to suggest ways to improve device performance. Few compare the predictions with measurements from devices. In this section, five representative device models are presented to illustrate the recent advances in modeling GaAs devices. These five device models have been selected from among the many models reported in the archival literature, since as a set, they contain most of the essential features and assumptions found in HBT, MESFET, and HFET models. The many other models that are not discussed or referenced here are, with few exceptions, variations on those outlined below. Including discussions of additional models would detract from the main purposes of this review; namely, identifying areas for which improved physical concepts and measurement techniques are needed.

#### Formulation of Lundstrom and Schuelke

Lundstrom and Schuelke have developed a numerical method for analyzing heterostructure semiconductor devices (HBTs and HFETs)[7]. Their analysis is based on a macroscopic description of semiconductors with nonuniform composition. The Lundstrom-Schuelke (LS) model contains conventional device equations. It discretizes the basic equations by the finite difference technique and uses the Scharfetter-Gummel [8] formulation for the current densities.

These authors have modified conventional device analysis programs to evaluate the two band parameters  $V_n$  and  $V_p$ . They describe the nonuniform composition by position dependent  $\kappa_s(x)$ ,  $V_n(x)$ , and  $V_p(x)$ . These modifications are valid only for heterostructures in equilibrium. Also, the LS model is strictly valid only when the material composition changes slowly and the concept of a position dependent effective mass is reasonable [9].

However, the above restrictions may not be appropriate for processed GaAs.

The main assumptions of the LS class of models are summarized below. The equilibrium *pn* product is assumed to have the form

$$n_0 p_0 = n_i^2 \exp(-\Delta E_g / \kappa T) \tag{1}$$

where  $\Delta E_s = -q(V_n + V_p)$ . Recent work [10] has shown that Eq. (1) gives incorrect descriptions for heavily doped silicon devices with emitter widths less than 3  $\mu$ m. Preliminary results indicate that similar difficulties occur with Eq. (1) for GaAs above  $10^{17}cm^{-3}$ . Also, this and most other models assume that the temperature is uniform throughout the device and that no strains are present. However, Moglestue has shown that local heating occurs between the gate and drain of *n*-type GaAs FETs [11].

Lundstrom and Schuelke have applied their model to both the HBT in Ref. [2] and to the TEGFET in Refs. [5,12]. They have not compared the predictions of the LS model for HBTs with measured I-V data. Only numerical experiments to understand better the behavior of HBTs are reported. They have compared the LS model predictions with measured quasi-static capacitance versus reverse gate voltage for the TEGFET [12]. The agreement is good except at high voltages (> 8V), for which breakdown may occur.

#### Formulation of Asbeck et al.

Asbeck et al. [13] have modified the one-dimensional, finite difference code SEDAN [14] to be applicable for HBTs. The basic semiconductor equations are similar to those for the LS model in the "Formulation of Lundstrom and Schuelke," section except the constitutive relation for  $J_n$

$$\mathbf{J}_n = -nq\mu_n \nabla (V + V_n) + D_n \nabla_n \qquad (2)$$

is replaced with the equation

$$\mathbf{J}_n = -qn\mathbf{v}(\mathbf{x}) \tag{3}$$

The electron velocities are obtained from equilibrium and ballistic transport relations for v(E). They have considered the dependence of  $f_r$  on current density and on various v(E) relations [15] by performing numerical experiments on HBTs [2]. They have used these predictions to suggest new designs for devices.

Because adequate measurements and theories for the dependence of  $n_{ie}^2/n_i^2$  on the high carrier and dopant densities present in their HBTs do not exist, HBT models contain the assumptions that  $n_{ie}^2/n_1^2 = 1$ and that  $\mu_p(\text{maj}) = \mu_p(\text{min})$  and  $\mu_n(\text{maj}) = \mu_n(\text{min})$  at the same doping densities. These physically questionable assumptions exist also in the recent Monte Carlo simulations reported by Tomizawa et al. [16].

Using the current crowding under the emitter as a variational parameter, Asbeck et al. have compared the dc common emitter gain versus collector current with measured values. The agreement is marginally acceptable. Continuing additional numerical experiments without better input data for mobilities, band edge changes, and effective intrinsic carrier concentrations has limited value to assist in improving HBTs.

#### Formulation of Riemenschneider and Wang

Riemenschneider and Wang have developed a twodimensional, finite-element program for analyzing transient and steady-state characteristics of GaAs MESFETs [17]. The devices that they have analyzed are dominated by electrons, and the contribution of holes to the total current flow is negligible. The holes would be important if the model were to include parasitic effects, such as backgating or other mechanisms for minority carrier injection. But, few, if any, twodimensional, finite-element models consider parasitics. The generation and recombination terms in the relation for the conservation of electrons are set to zero. The electron current in the model is derived from classical transport theory

$$\mathbf{J}_{\mathbf{n}} = -qn\mathbf{v}_{\mathbf{n}} + D_{\mathbf{n}}\nabla n \tag{4}$$

Equation (4) contains transport by diffusion, whereas Eq. (3) does not.

The values of the electron velocity are based on steady-state data from the Monte Carlo calculations of Ref. [18]. The diffusivity  $D_n$  values are interpolated between the low field values computed by Einstein's

relationship and the high field values [19]. They do not include the effect of dynamic velocity overshoot. Since most velocity overshoot formulations such as Cook and Frey [20] do not consider the multivalley nature of electron transport in GaAs in detail, Riemenschneider and Wang consider the accuracy of the models that use them to be doubtful.

Riemenschneider and Wang have reported only numerical experiments on comparing the predicted performance of planar MESFETs with recessed gate MESFETs. They have no experimental verification of their calculations. This tends to be the rule and not the exception for modeling GaAs devices. Verification of models to the extent accomplished for silicon devices is rare for GaAs device models.

#### Formulation of Cook and Frey

Cook and Frey [20] have presented computer simulations of GaAs MESFETs that include transport effects (velocity overshoot). They offer an engineering-level description of hot electron effects in GaAs MESFETs. Their transport model contains many assumptions. Some of the more significant ones are as follows:

(1) Including the upper and lower valleys in the transport equations makes the procedure too complicated, so they have used an equivalent single valley model [21].

| List of Symbols |                                 |                            |                                            |  |  |

|-----------------|---------------------------------|----------------------------|--------------------------------------------|--|--|

| D               | Dielectric displacement         | R                          | Recombination rate                         |  |  |

| D               | Defect or trap density          | t                          | Time                                       |  |  |

| $D_n$           | Electron diffusivity            | Т                          | Temperature                                |  |  |

| Ε               | Carrier energy                  | $V_{gs}$                   | Gate-source voltage                        |  |  |

| E <sub>F</sub>  | Fermi energy                    | $V_{BE}$                   | Base-emitter voltage                       |  |  |

| E <sub>G</sub>  | Bandgap                         | $V_{\tau}$                 | Threshold voltage                          |  |  |

| Ε               | Electric field                  | $V_n$ and $V_p$            | Band parameters                            |  |  |

| f,              | Current-gain bandwidth products | W                          | Carrier energy                             |  |  |

| g <sub>m</sub>  | Transconductance                | $W_{\scriptscriptstyle B}$ | Base width                                 |  |  |

| Ğ               | Generation rate                 | $W_{E}$                    | Emitter width                              |  |  |

| ħ               | Planck's Constant/ $2\pi$       | x                          | Position vector                            |  |  |

| I–V             | Current-voltage characteristic  | β                          | Gain                                       |  |  |

| J               | Current density                 | Γ, L, Χ                    | Symmetry points in Brillouin Zone          |  |  |

| k               | Boltzmann Constant              | $\Delta_{\Gamma L}$        | Subband energy difference between $\Gamma$ |  |  |

| k               | Carrier wave vector             |                            | and L points                               |  |  |

| L <sub>g</sub>  | Gate length                     | $\Delta_{\Gamma x}$        | Subband energy difference between $\Gamma$ |  |  |

| m*              | Carrier effective mass          |                            | and X points                               |  |  |

| n               | Electron density                | E                          | Dielectric constant                        |  |  |

| $n_0$           | Electron equilibrium density    | Ks                         | Position-dependent dielectric              |  |  |

| $n_i$           | Intrinsic carrier concentration |                            | constant                                   |  |  |

| n <sub>ie</sub> | Effective intrinsic carrier     | $\mu_{\pi}(maj)$           | Electron mobility n-type                   |  |  |

|                 | concentration                   | $\mu_n(\min)$              | Electron mobility p-type                   |  |  |

| $N_D$           | Donor density                   | $\mu_{p}(maj)$             | Hole mobility p-type                       |  |  |

| Ň               | Acceptor density                | $\mu_p(\min)$              | Hole mobility n-type                       |  |  |

| p               | Hole density                    | $	au_p(W)$                 | Momentum relaxation time                   |  |  |

| $p_0$           | Hole equilibrium density        | $\tau_w(W)$                | Energy relaxation time                     |  |  |

| q               | Electronic charge               |                            | 0,                                         |  |  |

(2) The electron-phonon and electron-ionized impurity scattering processes can be described by energy-dependent relaxation times for electron momentum and energy,  $\tau_p(W)$  and  $\tau_w(W)$ , respectively, i.e.,

$(\mathrm{dv} / dt) \mathrm{coll} = \mathrm{v} / \tau_{\nu}(\mathrm{W}) \tag{5}$

$(dW / dt) \text{coll} = (W - W_o) / \tau_w(W)$  (6)

(3) Equations (5) and (6) require the assumption that  $\tau_p(W(t_1)) = \tau_p(W(t_2))$  and  $wt_w(W(t_1)) = \tau_w(W(t_2))$ .

Most discussions of energy transport in GaAs use expressions such as those given by Eqs. (5) and (6). However, these expressions may not be valid for GaAs. Nougier et al. have shown in Ref. [22] that the transient velocity in a semiconductor is the solution of a relaxation time equation, such as Eq.(5), when impurity and polar (longitudinal long range) optical phonon scatterings are negligible. However, impurity and optical phonon scatterings [23] are large for the structures shown in Figs. 1 and 2.

Hence, a very significant question remains to be answered in the modeling of state-of-the-art GaAs devices. Namely, do the two assumptions (5) and (6) compensate each other and lead to good quantitative simulations or do they add and lead to additional errors? Before this question may be answered, however, the quantitative correctness of the boundary conditions used in GaAs device models must be determined. The convoluted nature of boundary conditions representing the physical device and of assumptions (5) and (6) makes verifying GaAs device models a challenge. Others [24] state that, at present, the boundary conditions used in most GaAs models may be quantitatively in much greater error than the errors associated with any of the above assumptions. If this is true, then comparing the predictions of energy transport and conventional models with measured I-V data is not of value until knowledge of the boundary conditions improves.

Cook and Frey have compared the predictions of conventional models with their energy transport model for the case of a uniformly doped planar MES-FET. They have concluded that whenever *W* (E) increases rapidly with E, then the transport model should be quantitatively superior to conventional models. However, they have performed only numerical experiments.

#### Formulation of Yoshii, Tomizawa, and Yokoyama

Using a Monte Carlo scattering description, which is similar to that given by W. Hockney et al. [25], Yoshii, Tomizawa, and Yokoyama [26] follow in space and time the trajectories for all particles under the inhomogeneous, local electric field. Their method is a valid way to solve the Boltzmann transport equation. As is the case for the formulation of Cook and Frey, the formulation of Yoshii et al. requires that the scattering mechanisms and the band structure be quantitatively given as functions of carrier concentrations and/or doping densities. However, since it also requires substantial computer resources compared to the other methods, it is used rarely to optimize devices. Instead, full Monte Carlo particle simulations may provide a sound physical basis for parameters in the relaxation time approximation. The latter then may be used with improved confidence to optimize device performance.

Using their two-dimensional full Monte Carlo particle simulations, the authors of reference [26] have concluded that nonstationary carrier transport influences considerably the device characteristics of submicrometer-gate GaAs MESFETs and that the relaxation time approproximation may overestimate the nonstationary effects.

## Physical Concepts for GaAs Devices

Reducing the number of unknown parameters in device models increases the effectiveness of computer models for product development. The extent to which manufacturers of GaAs ICs will be successful in "forward engineering" with computer models depends, in part, on the correctness of the physical concepts used. An example of "forward engineering" based on detailed models is the recently reported improvement in the performance of short-channel NMOS devices [27].

It is essential that any changes in the device physics be anticipated at the time that computer codes for solving, numerically, the device model are developed. The numerical stability of the solutions depends greatly on the algorithms employed [24]. The latter may be sensitive to the dependences of the device parameters on densities, electric fields, temperatures, and position.

The remaining parts of this section contain examples of how improved device physics might contribute to better performance of GaAs/AlGaAs HBTs and FETs.

#### GaAs/AlGaAs Bipolar Heterostructures

The potential for high-frequency performance has increased the effort devoted to GaAs/AlGaAs heterojunction bipolar transistors (HBT). Proposed devices [28] have  $p^+$  bases with Be acceptor densities of  $10^{19}cm^3$  and  $n^+$  emitters with Si donor densities of  $5 \times 17^{17}cm^{-3}$ . Estimates for GaAs indicate that its band structure is perturbed whenever dopant ion or carrier concentrations exceed  $6 \times 10^{18} cm^{-3}$  in p-type GaAs and exceed  $10^{17} cm^{-3}$  in n-type GaAs [29]. Above these concentrations, theory suggests that quantities such as  $E_{G}$ ,  $\Delta_{\tau L}$ ,  $\Delta_{\tau X}$ ,  $n_{ie}$ , mobilities, and lifetimes should be calculated in terms of the perturbed band structure for the intrinsic material.

Any bipolar-detailed device model planned for the immediate application to GaAs/AlGaAs HBTs, such

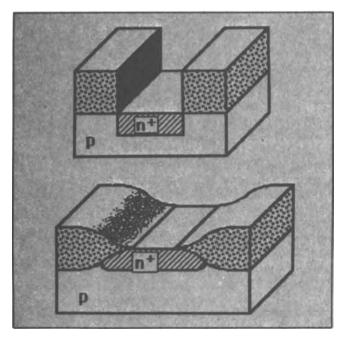

Fig. 1 Cross section of the HBT described in Ref. 2.

Fig. 2 Cross section of the enhancement mode TEGFET described in Ref. 12.

as those described in Ref. [13], would not incorporate these effects because of high dopant and carrier concentrations. This would occur because expressions for such quantities as  $n_{ir}$  as a function of doping or carrier density are not available in a form suitable for use in detailed models. The usual expressions for the majority carrier mobilities and drift velocities would also be used, because acceptable expressions for minority carriers do not exist. A third area of difficulty is that knowledge of recombination centers and minority carrier lifetimes is very meager in GaAs. For example, if the number of recombination centers is too great, carrier transport becomes impeded. As a result of this lack of verified input data for GaAs bipolar device models, no discernible correlation between measurements and model predictions should be expected.

#### FETs

Numerical simulations for the carrier transport in the channel of MESFETs reveal three distinct effective field regions: contact, channel, and a rapidly forming space charge dipole [30]. For a  $1\mu$ m-gate with an n-type dopant density of  $2 \times 10^{17} cm^{-3}$  in the channel of a conventional MESFET, the carrier density in the accumulation region of the dipole region is about  $3.5 \times 10^{17} cm^{-3}$  and the carrier density in the depletion region is about  $10^{17} cm^{-3}$ . This dipole forms in about 10ps when ideal voltage sources are assumed [31].

Device performance characteristics, such as transconductance, are sensitive to changes in the carrier mobility. The changes in mobilities for the channel and dipole regions depend in part on the band structure parameters, particularly on  $\Delta_{\Gamma L}$  [29,24]. These band parameters are expected to differ from the intrinsic band parameters due to carrier-dopant ion and carrier-carrier interactions.

Backgating and light sensitivity, which degrade circuit performance and may limit packing densities [32,33] in MESFETs, have been shown by C. P. Lee and coworkers [34,35] to be related to carrier injection from the substrate and to carrier transport from the substrate to the active region. Many proposals for reducing the effects of backgating [34,36,37] involve the transport of minority carriers.

The source and drain contacts and the Schottkybarrier gate provide other areas where physical concepts are not adequate. For example, the transition from the n-type channel, through the  $n^+$  drain, to the highly degenerate alloy contact has abrupt concentration changes and large mobility variations. Also, the presence of trapping states at the Schottky-barrier interface greatly influences the Fermi energy and the work function and may contribute a new mechanism of charge storage. The latter may limit device speed. Design engineers need detailed models for ohmic contacts and Schottky barriers to predict their highfrequency behavior. They are particularly interested in knowing before fabrication whether any upper limits for the frequency responses of contacts or gates will affect their design considerations.

Breakdown in the region between the drain side of the gate and the drain has been observed. Device engineers need to know more precisely where the avalanche process begins and how the carrier injection mechanism takes place in their search for strategies to increase the gate to drain breakdown voltage.

# New Measurements for Processed GaAs/AlGaAs

As devices become faster and smaller, understanding the ultrafast behavior and nonequilibrium transport must improve. Designers of high-speed devices lack accurate techniques to measure device performance. An underlying principle is that the measurement technique must be faster than the device under test. Electrical measurements are usually used to test devices. This approach is successful when the electrical techniques for device characterization are faster than the devices under development. However, when the goal is to build the fastest device, the usual electrical techniques use the device to measure itself. An example of the latter approach is the ring oscillator technique applied to MESFETs. Since the time resolution of the electrical measurements based on a ring oscillator is determined by the individual devices themselves, only estimates of device speed are possible and little understanding of ultrafast processes and nonequilibrium transport result.

Pulsed optical or electron beam techniques offer alternative methods by which to measure many of the parameters listed in the Appendix and to increase understanding ultrafast devices. Pulsed optical techniques are faster than most high-speed technologies such as semiconductor and superconducting electronics. Pulsed optical techniques may, therefore, be the preferred way to measure key parameters for device models and to measure the electrical behavior of fast devices. One new technique [38] introduces discrete charge packets by a pulsed laser. This time of flight method has been applied to measure high-field transport at Si-SiO<sub>2</sub> interfaces. Whether such techniques are applicable to interfaces involving GaAs needs to be determined. A basic problem is that a technology for building a resistive gate in GaAs does not exist. Other challenges include: (1) pulsed optical or electron beam techniques may not be fast enough for GaAs; (2) sample quality may not be adequate over the path length needed [24]; and (3) applying a uniform, lateral electric field to the sample over the entire path length has not been demonstrated for GaAs.

#### Conclusions

The major conclusions from the discussions above are

- (1) The measured and theoretical data for many of the electrical and material properties of GaAs devices are not adequate for reliable engineering without detailed verification by measurements. The input quantities for detailed device models contain many unknown parameters.

- (2) The interdependence of numerical stability and device physics dictates that any changes in the device physics must be anticipated at the time the algorithms and computer codes are developed.

- (3) Many physical concepts are not adequate for GaAs devices. These include carrier scattering rates due to ionized impurities and polar optical phonons and carrier transport when carrier or doping concentrations exceed 10<sup>17</sup> cm<sup>-3</sup> in n-type and 10<sup>19</sup> cm<sup>-3</sup> in p-type GaAs/AlGaAs. Incorporating adequate physical concepts in GaAs device models requires new measurement techniques, perhaps based on ultrafast spectroscopy, for mobilities and lifetimes as functions of electric fields, dopant density, carrier energy, and carrier density in processed GaAs. Specially designed test structures will be needed to resolve many of the uncertainties concerning the physical concepts to be incorporated into GaAs device models.

# Appendix: Input Parameters for GaAs Device Modeling

Several of the input parameters that are needed for modeling GaAs devices are listed below.

Band Structure

Bandgap  $E_c(N_D)$  and valley separations  $\Delta_{\Gamma L}(N_D)$  and  $\Delta_{\Gamma x}(N_D)$

Equilibrium Carrier Densities  $n_{ie}^{2}(N_{D}) = np$  and  $n_{ie}^{2}(N_{A}) = np$

Transport Parameters for Majority and Minority Carriers

$\mu_n(\mathbf{E}, N_D)$  and  $\mu_n(\mathbf{E}, N_A)$   $v_n(\mathbf{E}, N_D)$  and  $v_n(\mathbf{E}, N_A)$   $\mu_p(\mathbf{E}, N_D)$  and  $\mu_p(\mathbf{E}, N_A)$  $v_p(\mathbf{E}, N_D)$  and  $v_p(\mathbf{E}, N_A)$

where E is the electric field

*Recombination Parameters* Auger recombination lifetimes for holes and electrons

Shockley-Read-Hall (defect) lifetimes for holes and electrons

*Generation Parameters* Impact ionization rates and tunnel rates

Dopant Density Profiles  $N_D(x,y,z)$  and  $N_A(x,y,z)$

## **Defect Density Profiles**

D(x,y,z) and the extent to which D(x,y,z) depends on  $N_D$  and  $N_A$

#### Contact and Interface Parameters

Interface trap density, Fermi energy, and work function at Schottky-barrier interface

Interface trap densities at ohmic contacts and other interfaces

#### Acknowledgments

The author thanks the staff members of the Semiconductor Devices and Circuits Division who have provided helpful comments during the preparation of this article.

#### References

- J. L. Blue and C.L. Wilson, "Two-Dimensional Analysis of Semiconductor Devices Using General Purpose PDE Software," *IEEE Trans. Electron Devices*, vol. 30, p. 1056, 1983.

- [2] P. Asbeck, D. L. Miller, R. A. Milano, J. S. Harris, G. R. Kaelin, and R. Zucca, "(Ga,A1)As/GaAs Bipolar Transistors for Digital Integrated Circuits," *Technical Digest*, 1981 International Electronic Devices Meeting (IEEE, New York), pp. 629–632.

- [3] H. Kroemer, "Heterostructure Bipolar Transistor and Integrated Circuits," Proc. IEEE, vol. 70, p. 13, 1982.

- [4] R. C. Eden, "Comparison of GaAs Device Approaches for Ultrahigh-Speed VLSI," Proc. IEEE, vol. 70, p. 5, 1982.

- [5] D. Delagebeaudeuf, P. Delescluse, P. Etienne, M. Laviron, J. Chaplant, and N. T. Linh, "Two-Dimensional Electron Gas MESFET Structure," *Electron. Lett.*, vol. 16, p. 667, 1980.

- [6] T. Mimura, S. Hiyamizu, and K. Nanbu, "A New Field-Effect Transistor with Selectively Doped GaAs/n-Al<sub>x</sub>Ga<sub>1-x</sub>As Heterojunctions," *Jap. J. Appl. Phys. Lett.*, vol. 19, p. 225, 1980.

- [7] M. S. Lundstrom and R. J. Schuelke, "Numerical Analysis of Heterostructure Semiconductor Devices," *IEEE Trans. Electron Devices*, ED-30, p. 1151, 1983.

- [8] D. L. Scharfetter and H. K. Gummel, "Large-Signal Analysis of a Silicon Read Diode Oscillator," *IEEE Trans. Electron De*vices, ED-16, p. 64, 1969.

- [9] K. M. van Vliet and A. H. Marshak, "Wannier-Slater Theorem for Solids With Position Dependent Band Structure," *Phys. Rev.*, B26, p. 6734, 1982.

- [10] H. S. Bennett, "Improved Concepts for Predicting the Electrical Behavior of Bipolar Structures in Silicon," *IEEE Trans. Electron Devices*, ED-30, p. 920, 1983.

- [11] C. Moglestue, IEE Proc., vol. 128, p. 131, 1981.

- [12] M. Le Brun, P. R. Jay, C. Rumelhard, G. Rey and P. Delescluse, "Low Noise Performance of Two-Dimensional Electron Gas FETs," Proc. IEEE/Cornell Conference on High-Speed Semiconductor Devices and Circuits, IEEE Cat. No. 83CH1959-6, p. 187, Aug. 1983.

- [13] P. M. Asbeck, D. L. Miller, R. Asatourian, and C. G. Kirkpatrick, "Numerical Simulation of GaAs/AlGaAs Heterojunction Bipolar Transistors," *IEEE Electron Device Lett.*, EDL-3, p., 402, 1982.

- [14] Semiconductor Device Analysis (Stanford University), Jan. 1980 version. Certain materials and computer codes are identified in this paper in order to specify the procedures adequately. Such identification does not imply recommendation or endorsement by the National Bureau of Standards, nor does it imply that the materials or computer codes identified are necessarily the best available for the purpose.

- [15] S. Katzer and J. Frey, "Transient Velocity Characteristics of Electrons in GaAs With Γ-L-X Conduction Band Ordering," J. Appl. Phys., vol. 49, p. 4064, 1978.

- [16] K. Tomizawa, Y. Awano, and N. Hashizume, "Monte Carlo Simulation of AlGaAs/GaAs Heterojunction Bipolar Transistors," *IEEEE Electron Device Lett.*, EDL-5, p. 362, 1984.

- [17] P. R. H. Riemenschneider and K. L. Wang, "A Finite-Element Program for Modeling Transient Phenomena in GaAs MES-FETs," IEEE Trans. Electron Devices, ED-30, p. 1142, 1983.

- [18] M. A. Littlejohn, J. R. Hauser, and T. H. Glisson, "Velocity-Field Characteristics of GaAs with Γ-L-X Conduction Band Ordering," J. App. Phys., vol. 48, p. 4587, 1977.

- [19] J. Pozela and A. Reklaitis, "Electron Transport Properties in GaAs at High Electric Fields," *Solid-State Electronics*, vol. 23, p. 927, 1980.

- [20] R. K. Cook and J. Frey, "Two-Dimensional Numerical Simulation of Energy Transport Effects in Si and GaAs MESFETs," *IEEE Trans. Electron Devices*, ED-29, p. 970, 1982.

- [21] D. E. McCumber and A. G. Chynoweth, "Theory of Negative Conductance Amplication and of Gunn Instabilities in 'Two Valley' Semiconductors," *IEEE Trans. Electron Devices*, ED-13, p. 4, 1966.

- [22] J. P. Nougier, J. C. Vaissiere, and D. Gasquet, "Determination of Transient Regime of Hot Carriers in Semiconductors, Using the Relaxation Time Approximations," J. Appl. Phys., vol. 52, p. 825, 1981.

- [23] J. W. Harrison and J. R. Hauser, "Theoretical Calculations of Electron Mobility in Ternary III-V Compounds," J. Appl. Phys., vol. 47, p. 292, 1976.

- [24] C. L. Wilson, "High Accuracy Physical Modeling of Submicron MOSFET's," IEEE Trans. Electron Devices, ED-30, p. 1579, 1983.

- [25] R. W. Hockney, R. A. Warriner, and M. Reiser, "Two-Dimensional Particle Models in Semiconductor-Device Analysis," *Electron. Lett.*, vol. 10, p. 484, 1974.

- [26] A. Yoshii, M. Tomizawa, and K. Yokoyama, "Accurate Modeling for Submicrometer-Gate Si and GaAs MESFET's Using Two-Dimensional Particle Simulation," *IEEE Trans. Electron Devices*, ED-30, p. 1376, 1983.

- [27] W. Fichtner, "Physics and Simulation of Small MOS Devices," *Technical Digest*, 1982 International Electron Devices Meeting (IEEE, New York), p. 638.

- [28] P. M. Asbeck, D. L. Miller, W. C. Petersen and C. G. Kirkpatrick, "GaAs/AIGaAs Heterojunction Bipolar Transistors with Cutoff Frequencies Above 10 GHz," *IEEE Electron Device Lett.*, EDL-3, p. 366, 1982.

- [29] H. S. Bennett, to be published.

- [30] S. Swierkowski and L. F. Jelsma, "Two-Dimensional Computer Modeling of GaAs Devices," *IEEE Trans. Electron Devices*, ED-28, p. 1219, 1981.

- [31] S. Swierkowski, private communication.

- [32] M. S. Birrittella, W. C. Seelbach, and H. Goronkin, "The Effect of Backgating on the Design and Performance of GaAs Digital Integrated Circuits," *IEEE Trans. Electron Devices*, ED-29, p. 1135, 1982.

- [33] H. Goronkin, M. S. Birrittella, W. C. Seelbach, and R. Vaitkus, "Backgating and Light Sensitivity in Ion-Implanted GaAs Integrated Circuits," *IEEE Trans. Electron Devices*, ED-29, p. 845, 1982.

- [34] C. P. Lee and B. M. Welch, "GaAs MESFETs with Partial p-Type Drain Regions," IEEE Trans. Electron Devices, ED-29, p. 1687, 1982 and "GaAs MESFETs with Partial p-Type Drain Regions," IEEE Electron Device Lett., EDL-3, p. 200, 1982.

- [35] C. P. Lee, S. J. Lee, and B. M. Welch, "Carrier Injection and Backgating Effects in GaAs MESFETs," IEEE Electron Device Lett., EDL-3, p. 97, 1982.

- [36] C. Kocot and C. A. Stolte, "Backgating in GaAs MESFETs," IEEE Trans. Electron Devices, ED-29, p. 1059, 1982.

- [37] D. C. D'Avanzo, "Proton Isolation for GaAs Integrated Circuits," IEEE Trans. Electon Devices, ED-29, p. 1051, 1982.

- [38] J. A. Cooper, Jr. and D. F. Nelson, "High-Field Drift Velocity of Electrons at the Si-SiO<sub>2</sub> Interface as Determined by a Time-of-Flight Technique," J. Appl. Phys., vol. 54, p. 1445, 1983.

#### Update...

Since the publication of the Critical Review in 1985, much progress has occurred in the sophistication and integration of computer programs to simulate the processing and operation of devices made from compound semiconductors such as GaAs and AlGaAs. This progress includes not only simulations for transistors but also simulations for optoelectronic devices such as lasers, sensors, and components for flat panel displays and for microelectromechanical structures. The abstracts and proceedings of the three international conferences on process and devices modeling [1-3] and the modeling and simulations session of the International Electron Devices Meetings (IEDM) are excellent sources and guides for additional archival information.

Some of the major challenges for process and devices simulations are:

- 1. Verifying independently the chemical and physical models that these simulations contain.

- 2. Comparing or benchmarking the predictions of different approaches to simulating the same process, device or structure.

- 3. Calibrating or validating the simulations by comparing their prediction with measurements.

The latter is crucial if such simulations are to be used effectively in competitive design and manufacturing. At the 1993 IEDM Evening Panel on Funding Technology Development, one panel member stated that process and device simulations are among the top three highest priority items from a list of 12 priority items for reducing the high costs of transferring technologies from research and development to the marketplace [4].

Some progress also has occurred in first principles calculations of the input parameters listed in the Appendix of the foregoing Critical Review. For example, researchers [5 and 6] have completed calculations and experimental verifications for minority and majority mobilities in heavily doped GaAs. This was an international effort. The next tasks include such calculations and verifications for AlGaAs. Supporting this effort will require more complete experimental data on the optical and electronic properties of AlGaAs as functions of the Al concentration.

Until more resources become available for advancing the knowledge and understanding that underlies the infrastructure of computer assisted design and manufacturing, those who develop computer simulations of manufacturing process and devices using these materials will in the interim have to rely more on empirical models than on first principles calculations. Also, parametric fits to the results of theoretical calculations will continue to be useful for interpolating between calculated points on curves and for reducing the costs and times requires for process and devices simulations.

#### **References:**

- 1. International Workshop on Numerical Modeling of Processes and Devices for Integrated Circuits. This meeting is known as NUPAD and is held during May or June in even numbered years.

- 2. International Workshop on VLSI Process and Device Modeling. This meeting is known as VPAD and is held during May or June of odd numbered years.

- 3. International Conference on Simulation of Semiconductor Devices and Processes. This meeting is known as SISDEP and is held during September in odd numbered years.

- 4. B. Cambou, from presentation given at Session 25 of the 1993 International Electron Devices Meeting (IEDM): Evening IEDM Panel on Funding Technology Development, December 7, 1993, Washington Hilton and Towers, International Ballroom Center, Washington, DC.

- H.S. Bennett, J.R. Lowney, M. Tomizawa, and T. Ishibashi, "Experimentally Verified Majority and Minority Mobilites in Heavily Doped GaAs for Device Simulations," IEICE Transactions Electronics, Volume E75-C, Number 2, February 1992, pp. 161-171, and references 1, 2, 4, 11, and 24-27.

- M. Tomizawa, T. Ishibashi, H.S. Bennett, and J.R. Lowney, "Effects of Heavy Doping on Numerical Simulations on Gallium Arsenide Bipolar Transistors," Solid State Electronics, Volume 35, Number 6, 1992, pp. 865-874, and references 1-8, 12-18, 20, 25, 26 and 28-34.

# Overview

# Harry T. Weaver, Guest Editor

#### Background

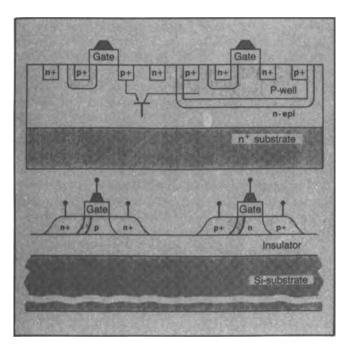

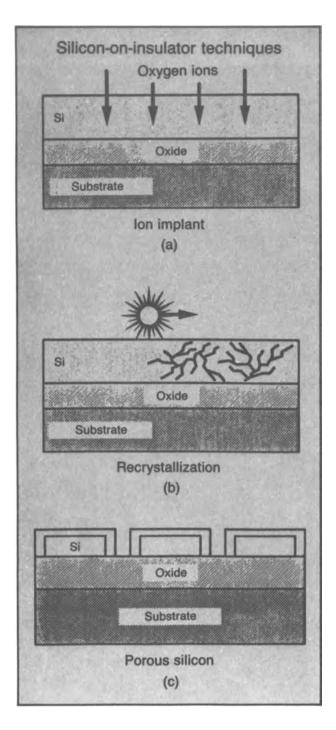

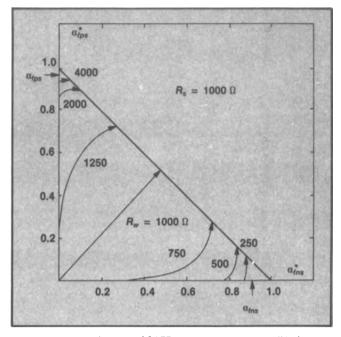

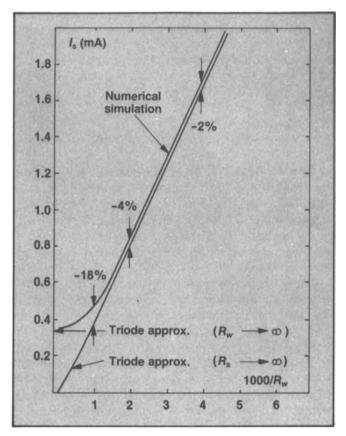

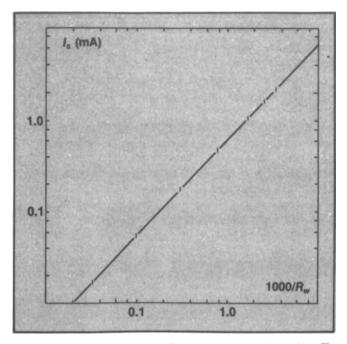

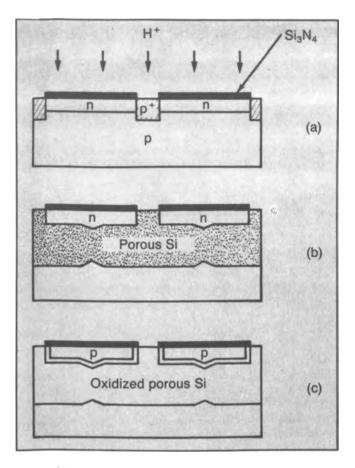

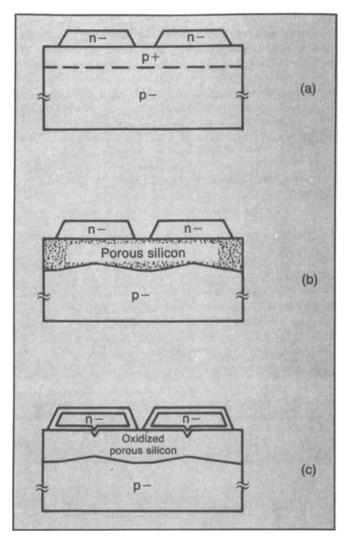

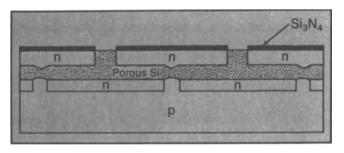

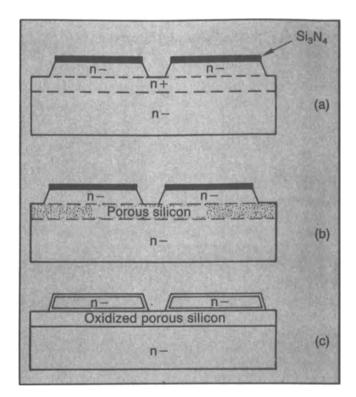

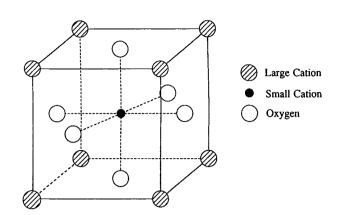

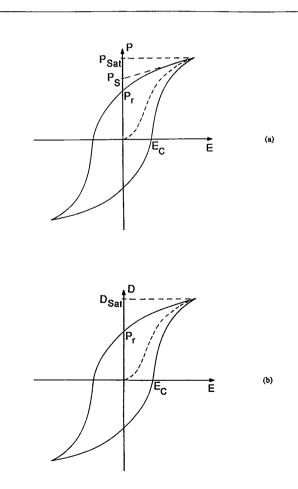

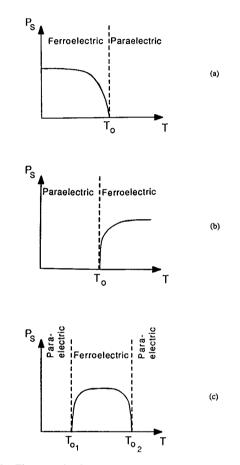

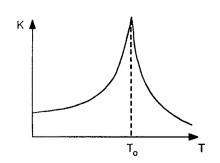

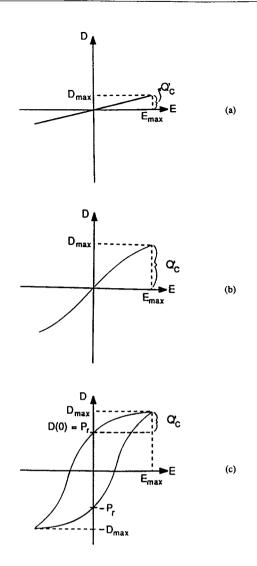

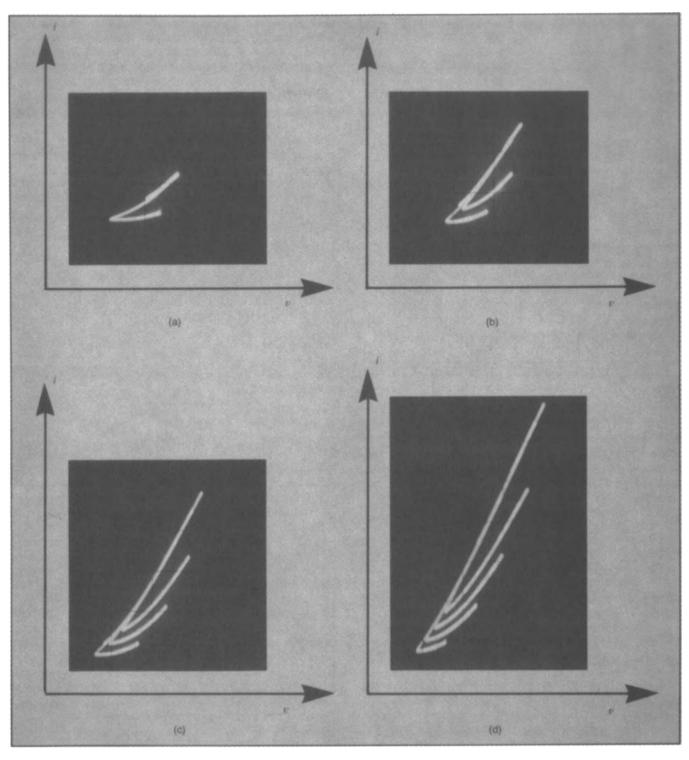

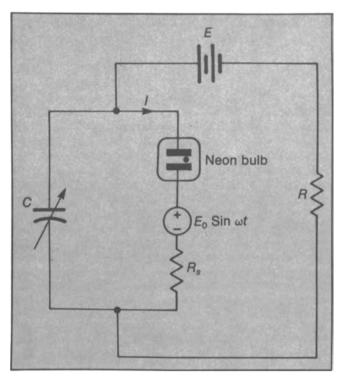

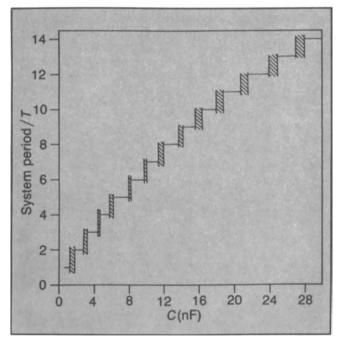

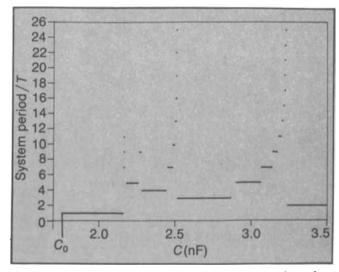

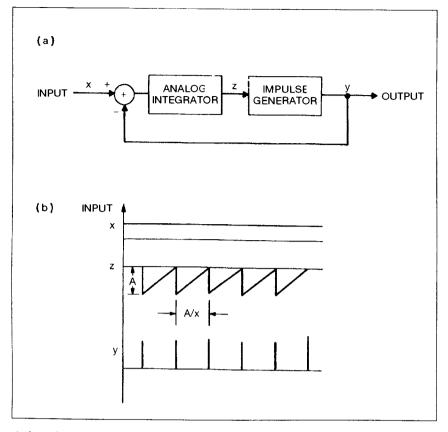

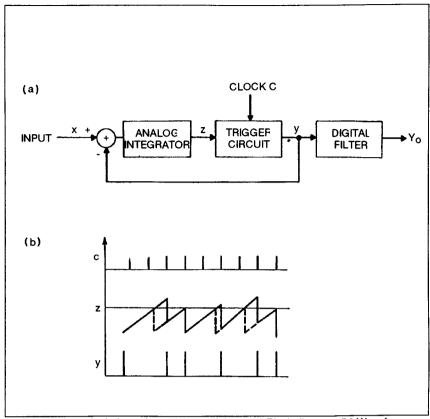

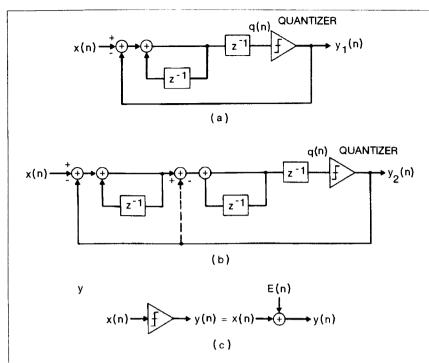

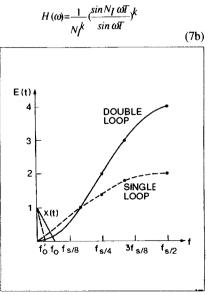

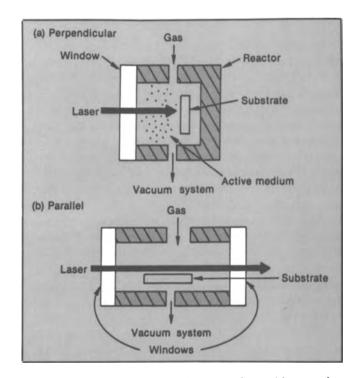

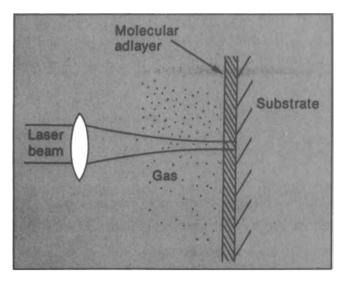

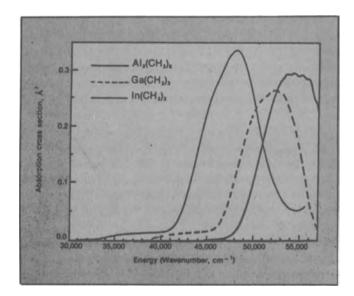

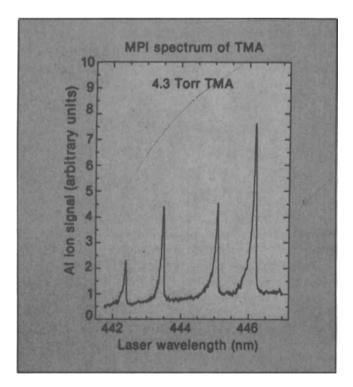

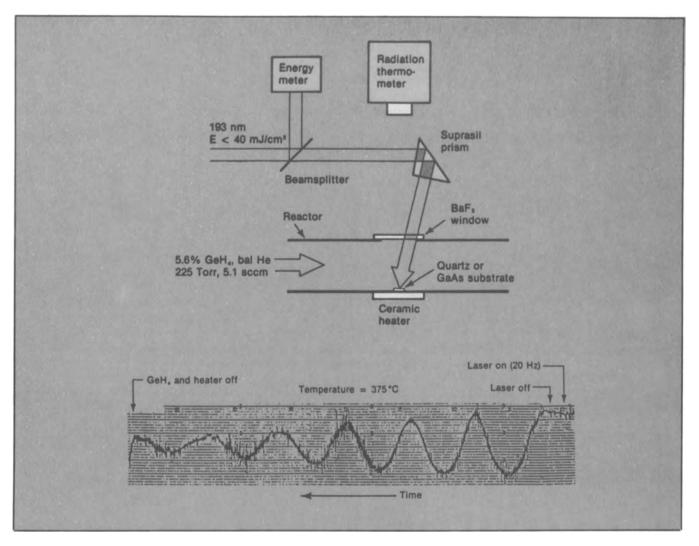

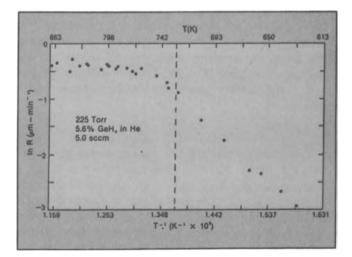

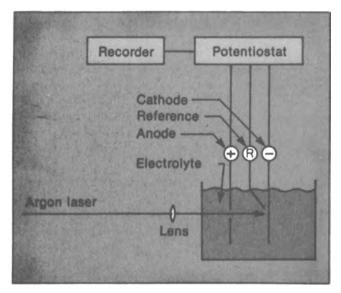

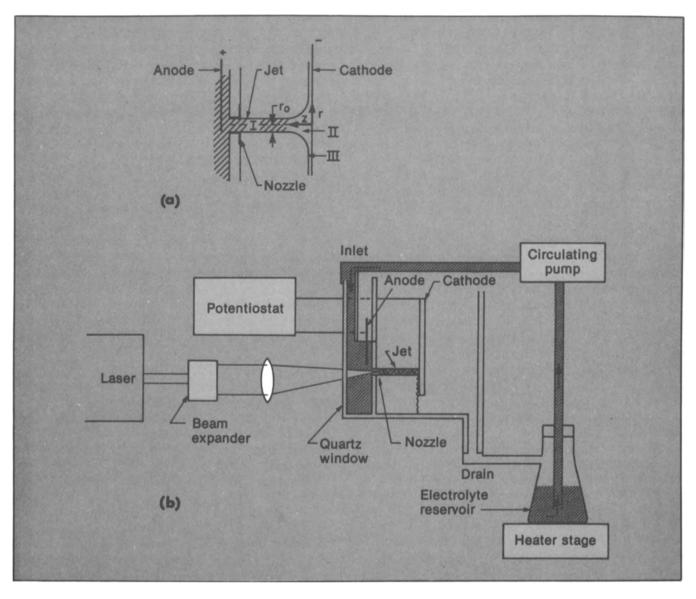

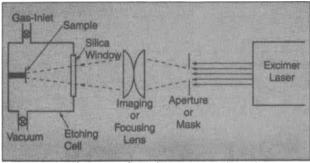

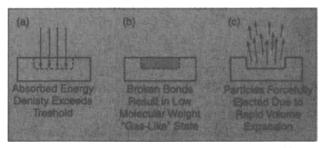

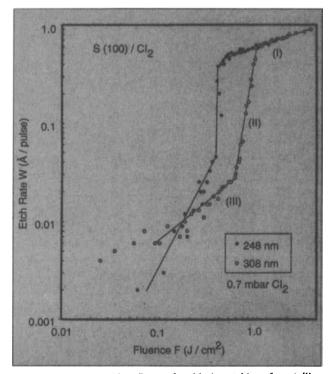

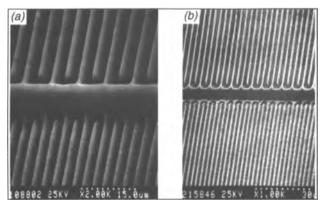

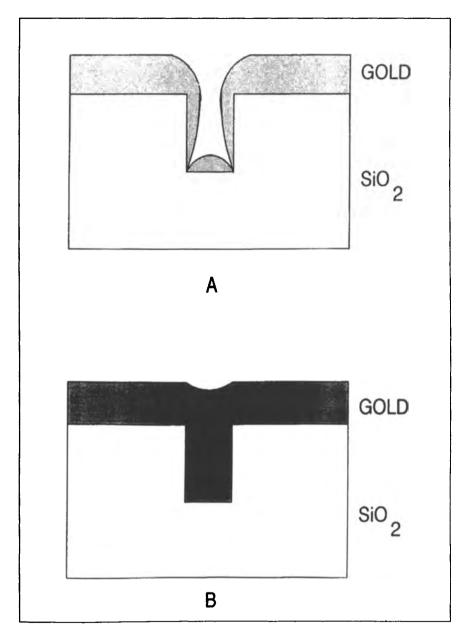

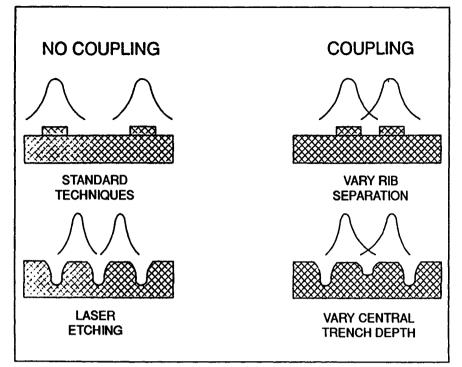

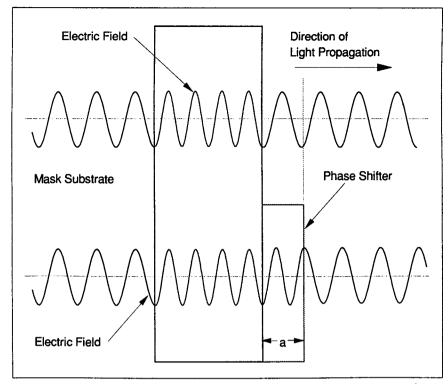

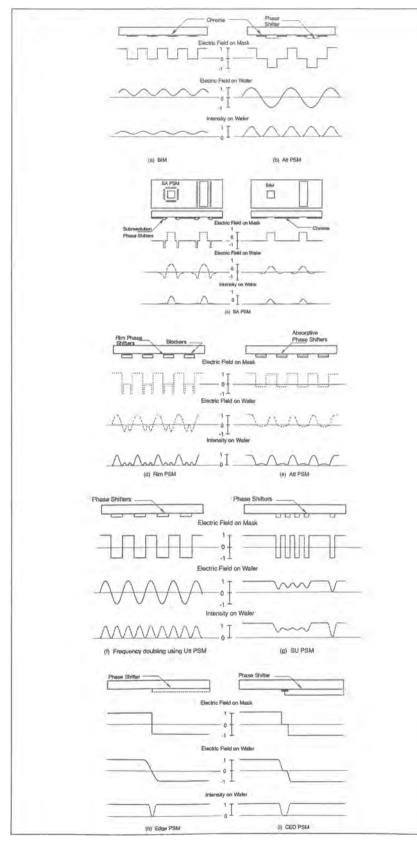

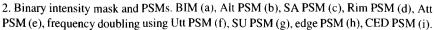

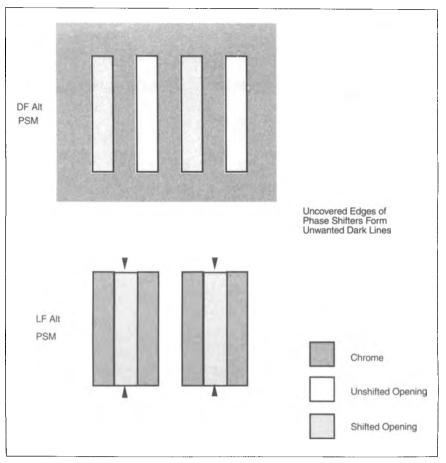

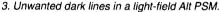

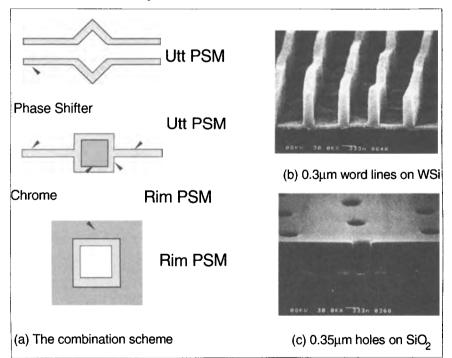

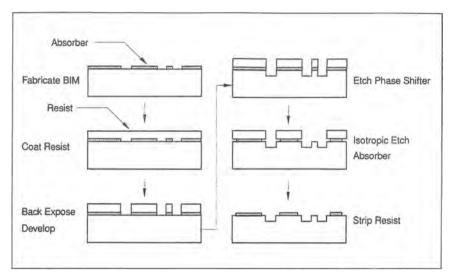

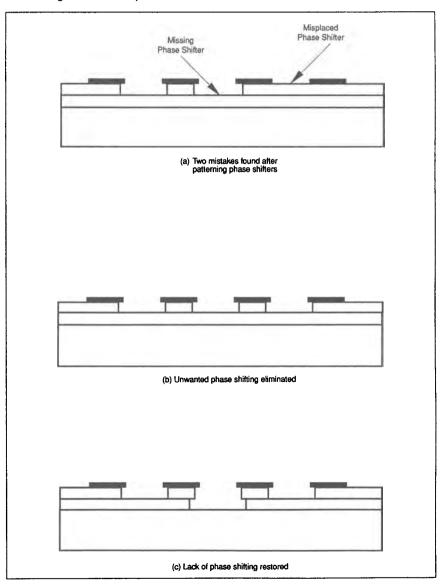

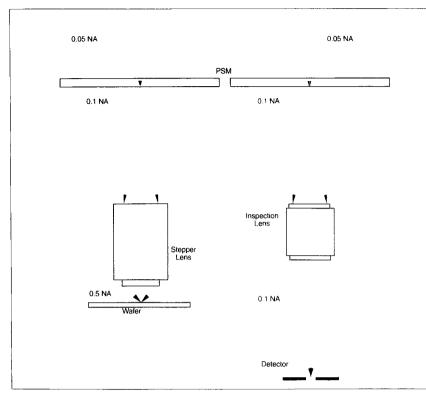

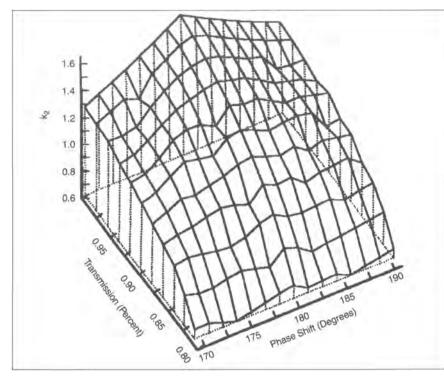

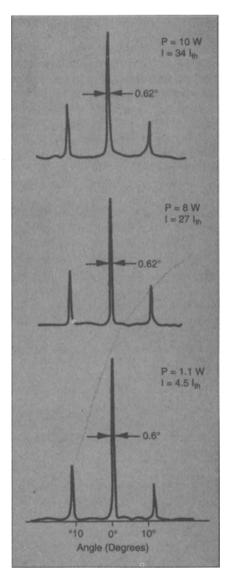

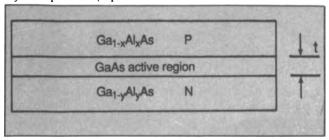

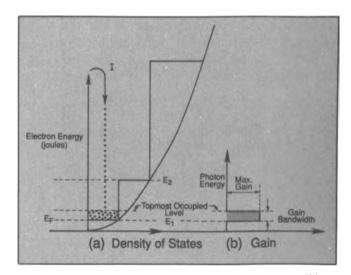

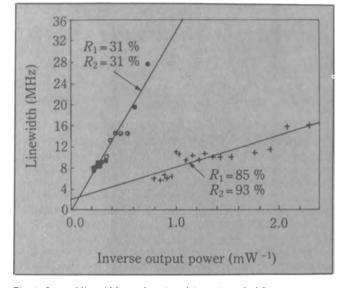

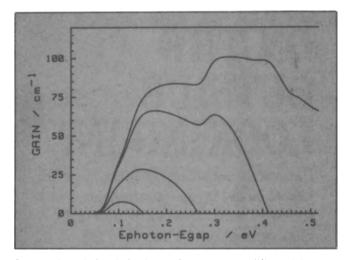

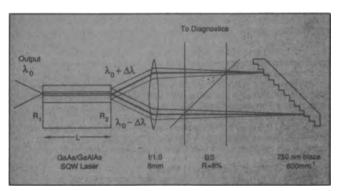

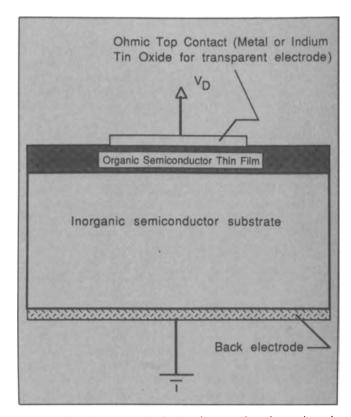

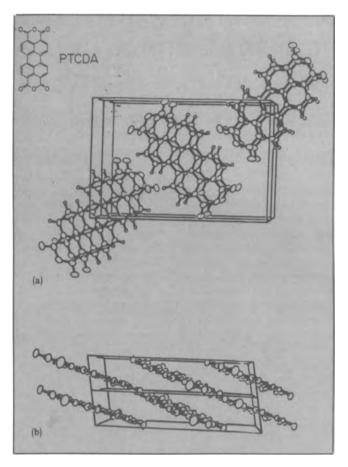

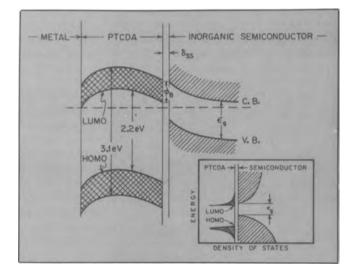

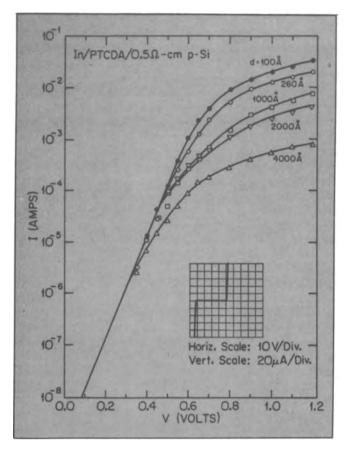

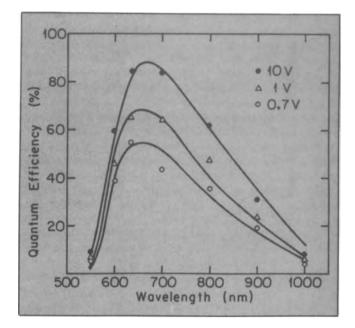

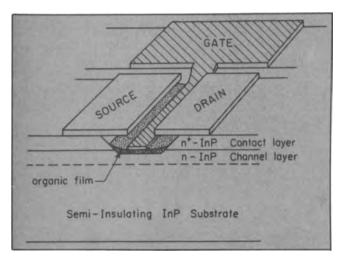

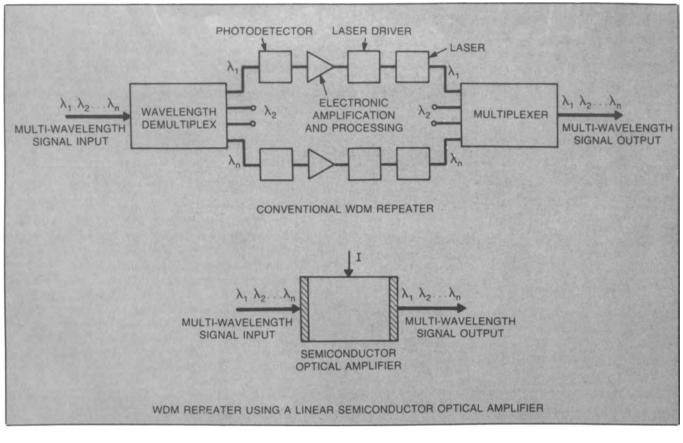

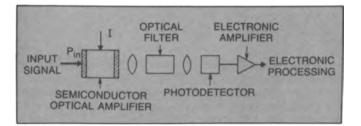

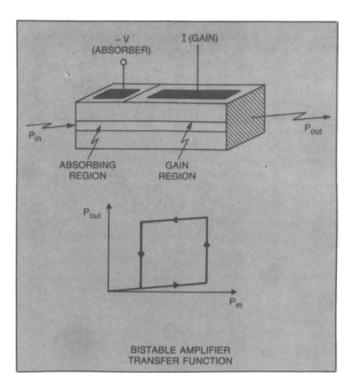

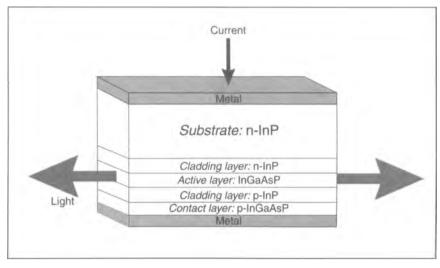

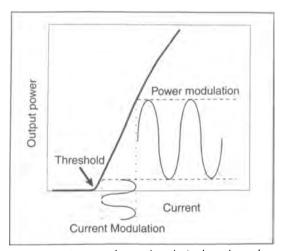

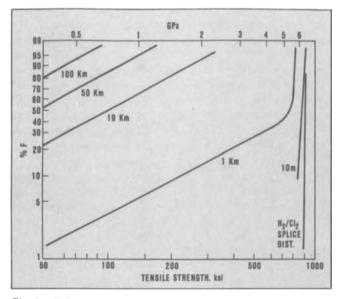

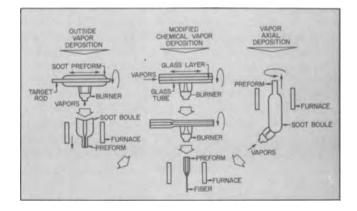

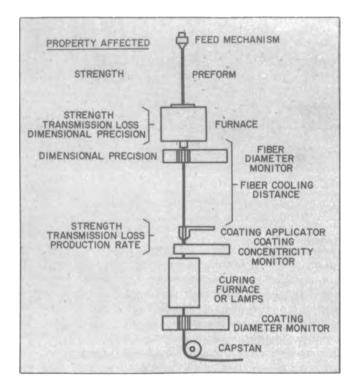

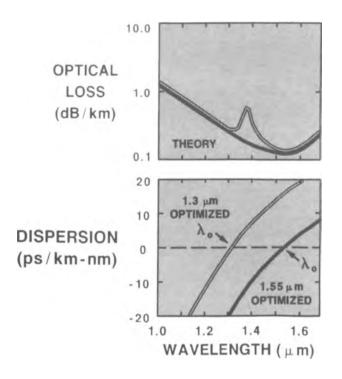

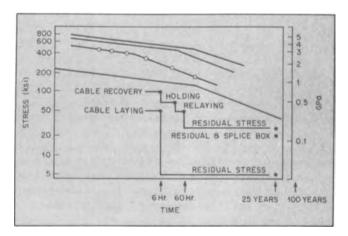

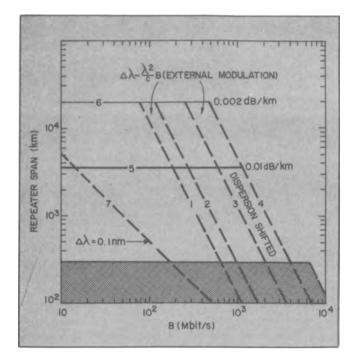

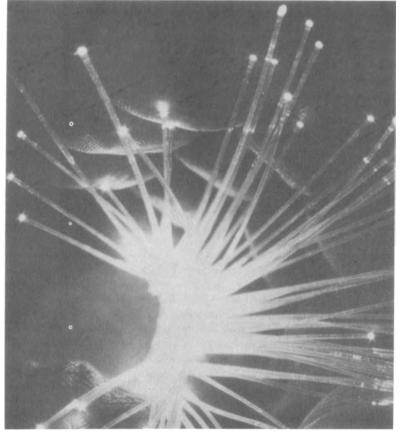

Silicon-on-insulator (SOI) materials provide an emerging technology for high-density, high-performance, special-purpose integrated circuits (ICs). These useful SOI properties are fundamentally derived from the capability of total electrical isolation of silicon areas and from the qualitative reduction of junction areas. We illustrate this in Fig. 1, where a bulk complementary MOS cross section is compared to an equivalent SOI structure. Bulk CMOS is used for comparison since the most likely initial impact of SOI is special-purpose integrated circuits, such as threedimensional circuits, high-voltage transistors, or radiationtolerant devices. The extraordinary success for dynamic RAM technology presents a formidable barrier for any new competitor in packing density, whereas, in other areas, SOI has special characteristics that will provide it with some advantage.