ELECTRICAL, ELECTRONICS, AND DIGITAL HARDWARE ESSENTIALS FOR SCIENTISTS AND ENGINEERS

# IEEE Press 445 Hoes Lane Piscataway, NJ 08855

# **IEEE Press Editorial Board**

John B. Anderson, Editor in Chief

R. Abhari D. Goldof M. Lanzerotti T. Samad G. W. Arnold B-M. Haemmerli O. P. Malik G. Zobrist F. Canavero D. Jacobson S. Nahavandi

Kenneth Moore, Director of IEEE Book and Information Services (BIS)

# ELECTRONICS, AND DIGITAL HARDWARE ESSENTIALS FOR SCIENTISTS AND ENGINEERS

Ed Lipiansky

Cisco Systems, Inc. San Jose, California, USA

IEEE PRESS SERIES ON MICROELECTRONIC SYSTEMS

A JOHN WILEY & SONS, INC., PUBLICATION

Cover Designer: Denise Lipiansky

Copyright © 2013 by The Institute of Electrical and Electronics Engineers, Inc.

Published by John Wiley & Sons, Inc., Hoboken, New Jersey. All rights reserved Published simultaneously in Canada

No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, scanning, or otherwise, except as permitted under Section 107 or 108 of the 1976 United States Copyright Act, without either the prior written permission of the Publisher, or authorization through payment of the appropriate per-copy fee to the Copyright Clearance Center, Inc., 222 Rosewood Drive, Danvers, MA 01923, (978) 750-8400, fax (978) 750-4470, or on the web at www.copyright.com. Requests to the Publisher for permission should be addressed to the Permissions Department, John Wiley & Sons, Inc., 111 River Street, Hoboken, NJ 07030, (201) 748-6011, fax (201) 748-6008, or online at http://www.wiley.com/go/permissions.

Limit of Liability/Disclaimer of Warranty: While the publisher and author have used their best efforts in preparing this book, they make no representations or warranties with respect to the accuracy or completeness of the contents of this book and specifically disclaim any implied warranties of merchantability or fitness for a particular purpose. No warranty may be created or extended by sales representatives or written sales materials. The advice and strategies contained herein may not be suitable for your situation. You should consult with a professional where appropriate. Neither the publisher nor author shall be liable for any loss of profit or any other commercial damages, including but not limited to special, incidental, consequential, or other damages.

For general information on our other products and services or for technical support, please contact our Customer Care Department within the United States at (800) 762-2974, outside the United States at (317) 572-3993 or fax (317) 572-4002.

Wiley also publishes its books in a variety of electronic formats. Some content that appears in print may not be available in electronic formats. For more information about Wiley products, visit our web site at www.wiley.com.

#### Library of Congress Cataloging-in-Publication Data:

Lipiansky, Ed.

Electrical, electronics, and digital hardware essentials for scientists and engineers / Ed Lipiansky.

p. cm. ISBN 978-1-118-30499-0 (hardback) 1. Electronic circuits. 2. Electronic apparatus and appliances. I. Title. TK7876.L484 2012 621.3–dc23

2012012321

Printed in the United States of America

10 9 8 7 6 5 4 3 2 1

To my lovely wife Ruty

# CONTENTS

| Pre | face              |                                                      | xvi                                                                                                                                                                                                 |

|-----|-------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Abo | out th            | e Auth                                               | or xiz                                                                                                                                                                                              |

| 1   |                   | n the B                                              | ottom Up: Voltages, Currents, and Electrical                                                                                                                                                        |

|     | 1.1<br>1.2<br>1.3 | Electr<br>1.2.1<br>1.2.2<br>1.2.3<br>Electr<br>1.3.1 | DC Voltage and Current Sources / 5<br>Sources Internal Resistance / 9<br>ic Components: Resistors, Inductors, and Capacitors / 12                                                                   |

|     | 1.4               | 1.3.3<br>1.3.4                                       | Resistivity: A Physical Interpretation / 23<br>Resistance of Conductors / 25<br>s Law, Power Delivered and Power Consumed / 25<br>Voltage Source Internal Resistance / 30                           |

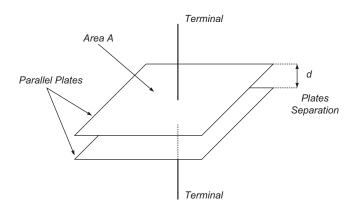

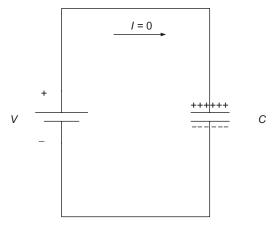

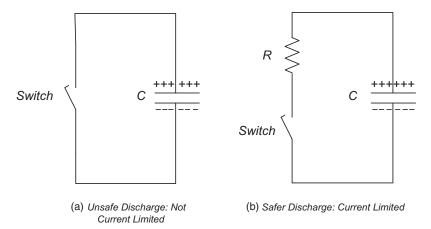

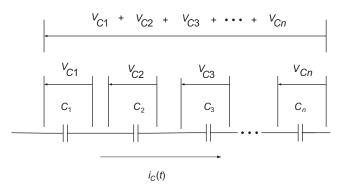

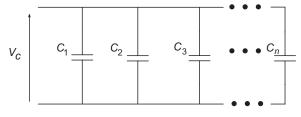

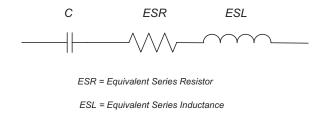

|     | 1.5               |                                                      | titors / 33<br>Physical Interpretation of a Parallel-Plate Capacitor<br>Capacitance / 35<br>Capacitor Voltage Current Relationship / 36<br>Capacitors in Series / 37<br>Capacitors in Parallel / 39 |

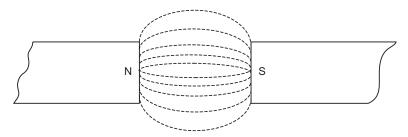

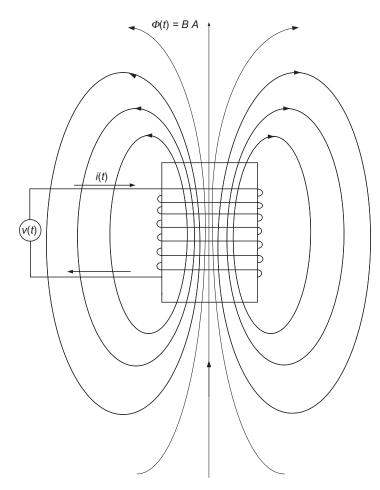

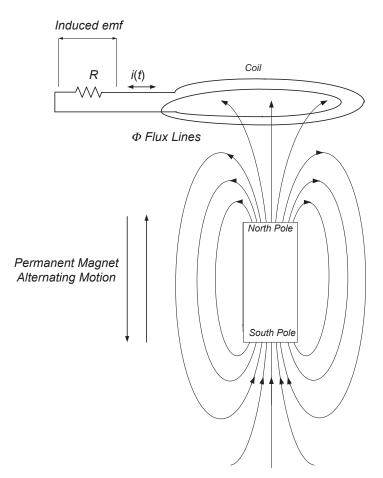

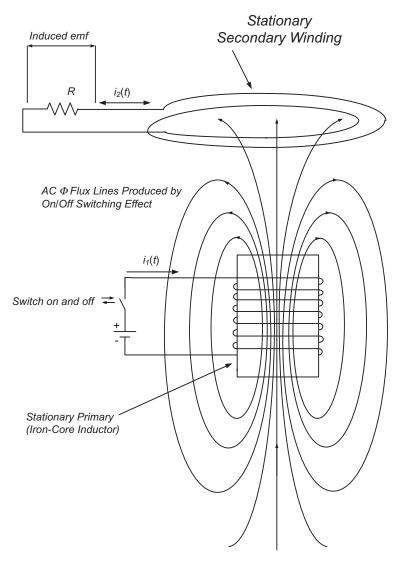

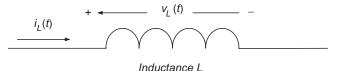

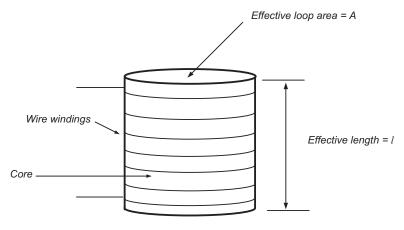

|     | 1.6               |                                                      | tors / 44<br>Magnetism / 45<br>Magnetic Field around a Coil / 49                                                                                                                                    |

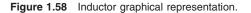

- 1.6.5 Inductors in Series / 58

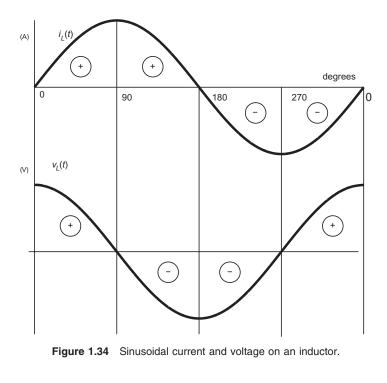

- 1.6.6 Inductors in Parallel / 60

- 1.6.7 Mutual Inductance / 62

- 1.6.8 Energy Stored by an Inductor / 69

- 1.6.9 Inductor Nonlinearity / 70

- 1.6.10 Inductor Component Selection / 71

- 1.7 Kirchhoff's Voltage Law (KVL) and Kirchhoff's Current Law (KCL) / 73

1.8 Summary / 87 Further Reading / 87 Problems / 88

# 2 Alternating Current Circuits

- 98

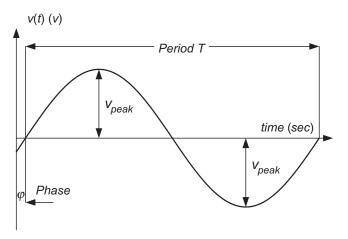

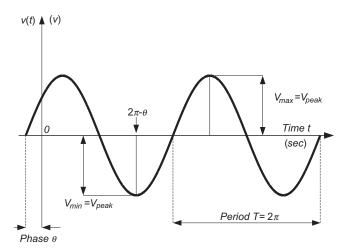

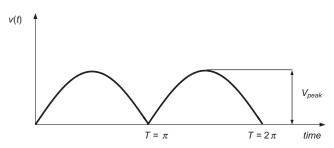

- 2.1 AC Voltage and Current Sources, Root Mean Square Values (RMS), and Power / 98

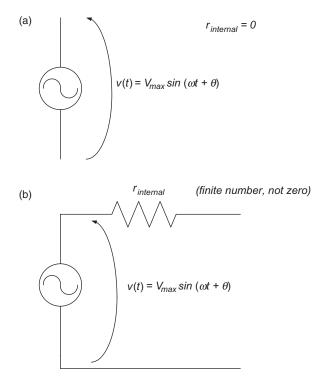

- 2.1.1 Ideal and Real AC Voltage Sources / 99

- 2.1.2 Ideal and Real AC Current Sources / 106

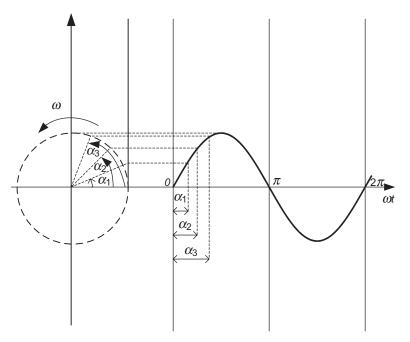

- 2.2 Sinusoidal Steady State: Time and Frequency Domains / 111

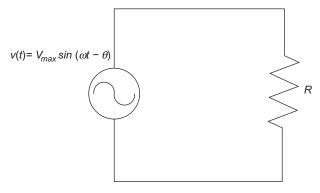

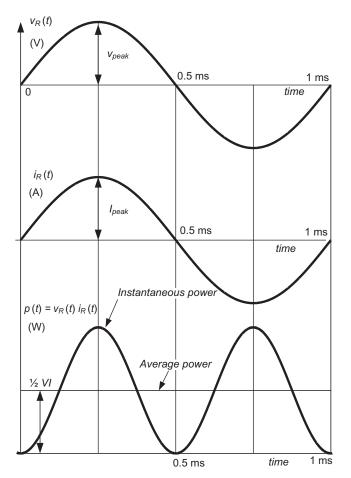

- 2.2.1 Resistor under Sinusoidal Steady State / 112

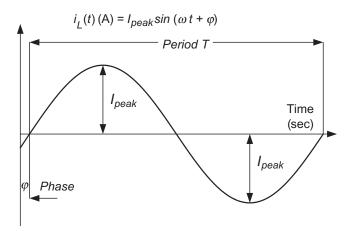

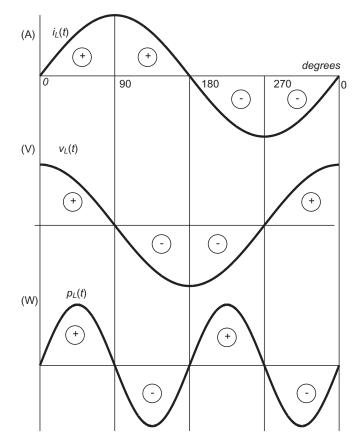

- 2.2.2 Inductor under Sinusoidal Steady State / 112

- 2.2.3 Capacitor under Sinusoidal Steady State / 113

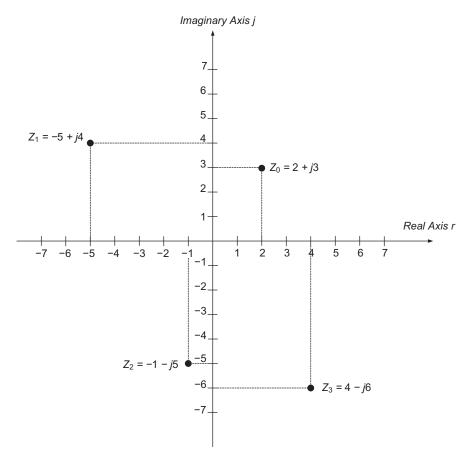

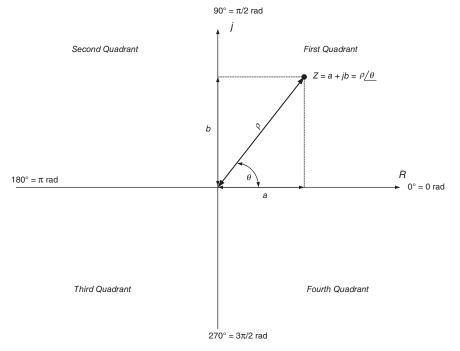

- 2.2.4 Brief Complex Number Theory Facts / 115

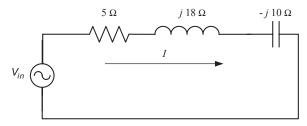

- 2.3 Time Domain Equations: Frequency Domain Impedance and Phasors / 123

- 2.3.1 Phasors / 123

- 2.3.2 The Impedance Concept / 124

- 2.3.3 Purely Resistive Impedance / 126

- 2.3.4 Inductive Impedance: Inductive Reactance / 127

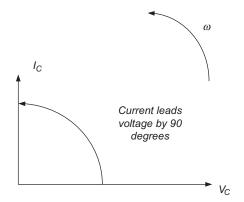

- 2.3.5 Purely Capacitive Impedance: Capacitive Reactance / 131

- 2.3.6 R, L, and C Impedances Combinations / 133

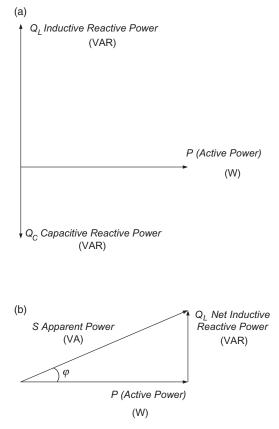

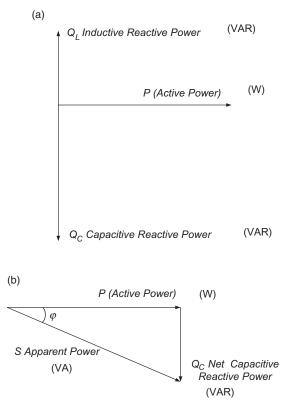

- 2.4 Power in AC Circuits / 136

- 2.4.1 AC Instantaneous Power Drawn by a Resistor / 137

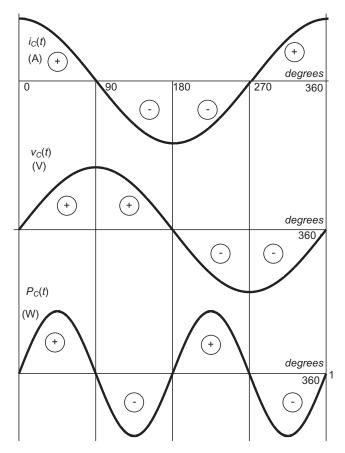

- 2.4.2 AC Instantaneous Power Drawn by a Capacitor / 137

- 2.4.3 AC Instantaneous Power Drawn by an Inductor / 139

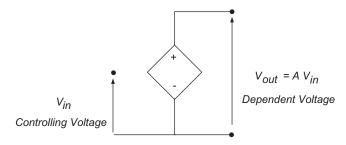

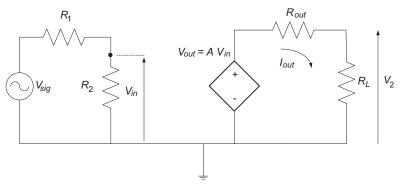

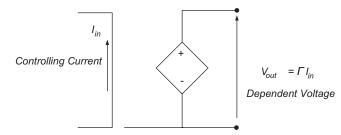

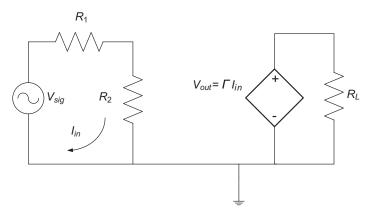

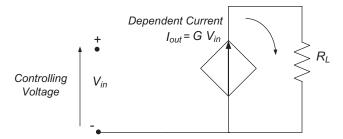

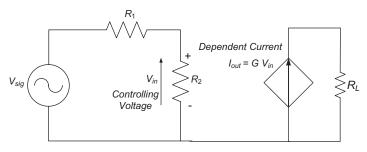

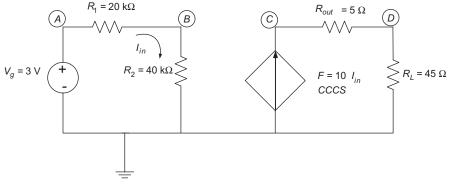

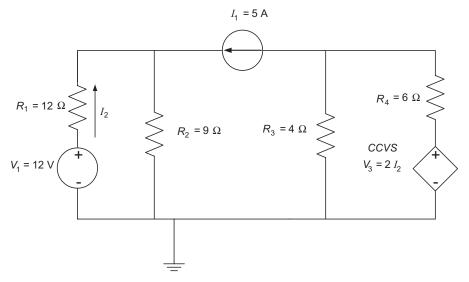

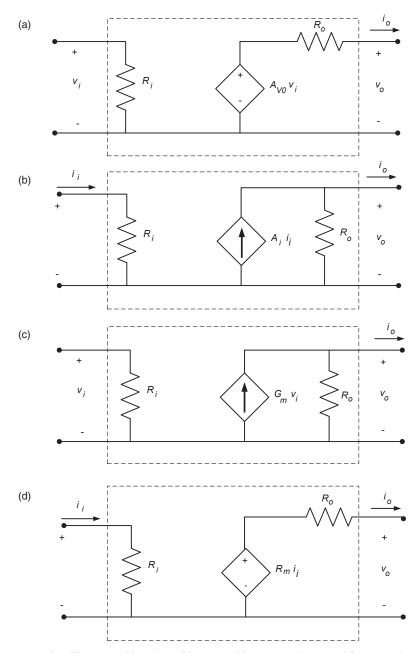

- 2.5 Dependent Voltage and Current Sources / 145

- 2.5.1 Voltage-Controlled Voltage Source (VCVS) / 145

- 2.5.2 Current-Controlled Voltage Source (CCVS) / 146

- 2.5.3 Voltage-Controlled Current Source (VCCS) / 147

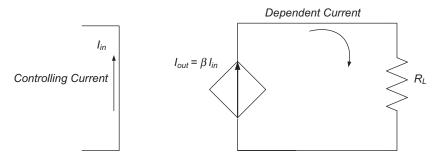

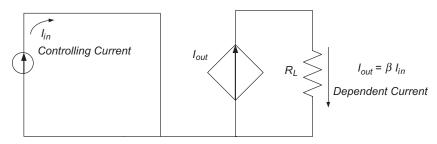

- 2.5.4 Current-Controlled Current Source (CCCS) / 148

- 2.6 Summary of Key Points / 149

- Further Reading / 149

- Problems / 150

# 3 Circuit Theorems and Methods of Circuit Analysis

- 3.1 Introduction / 155

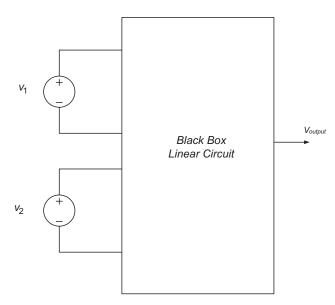

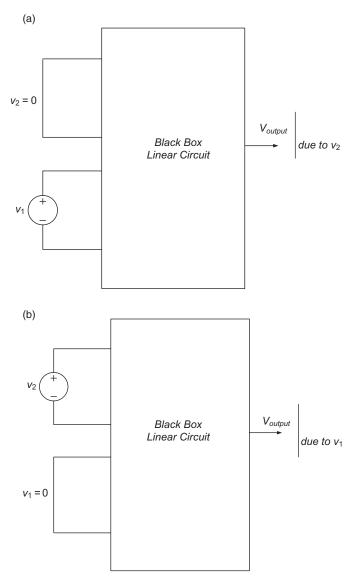

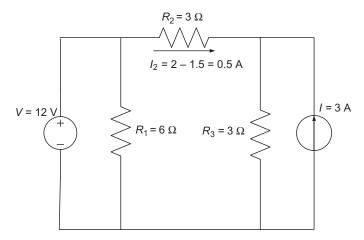

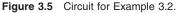

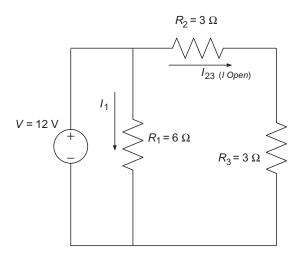

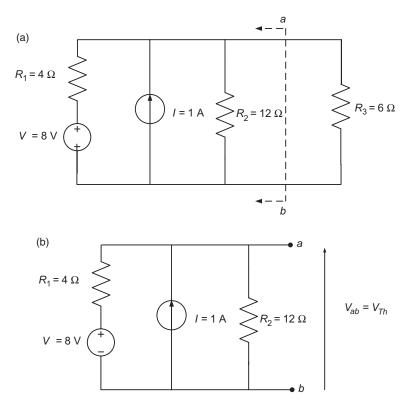

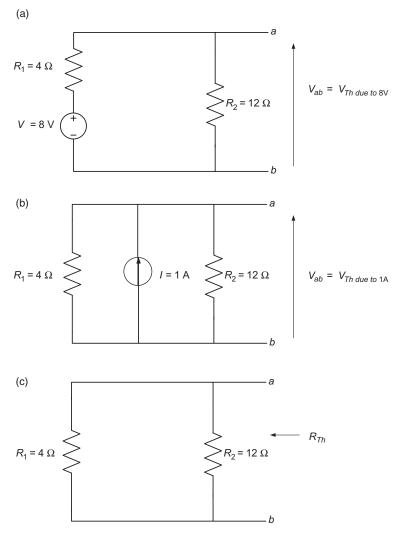

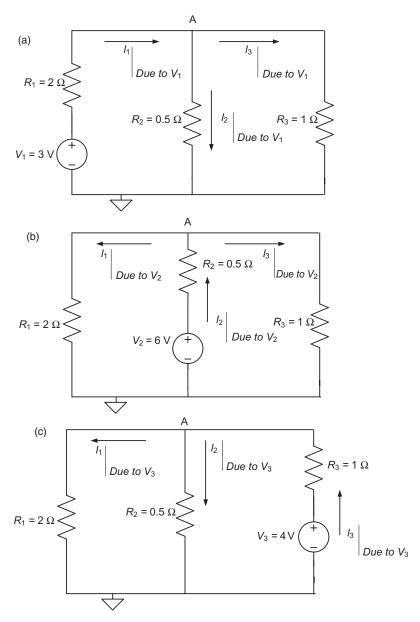

- 3.2 The Superposition Method / 156

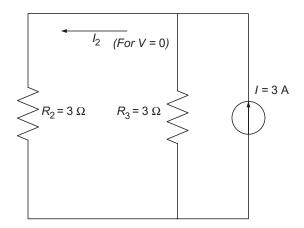

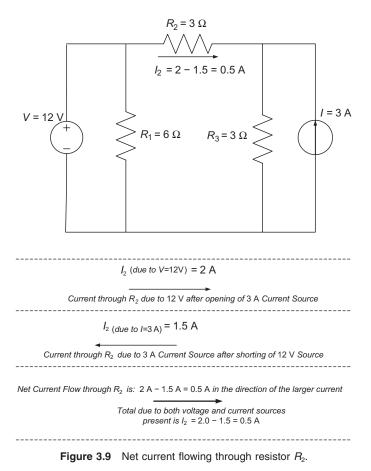

- 3.2.1 Circuits Superposition / 160

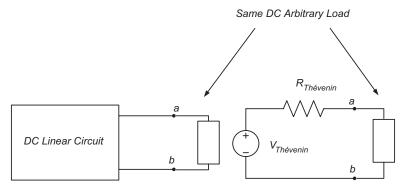

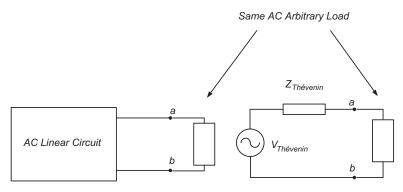

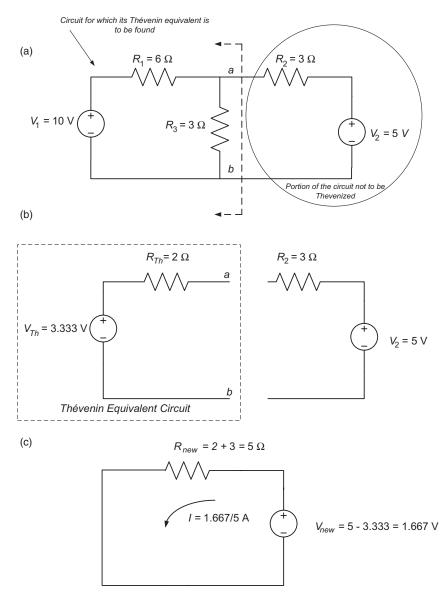

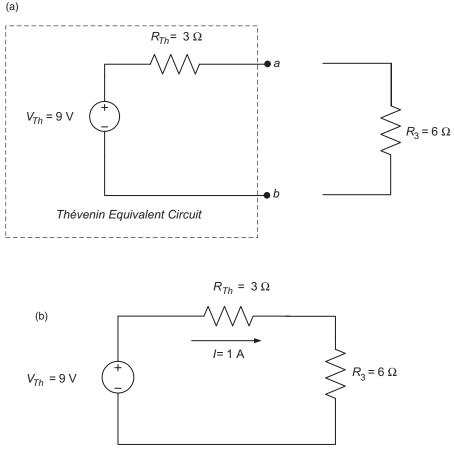

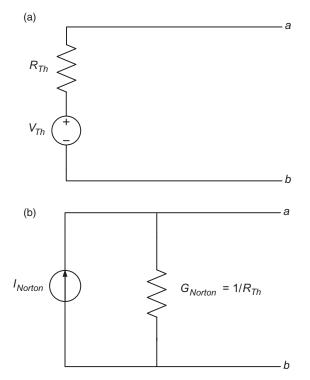

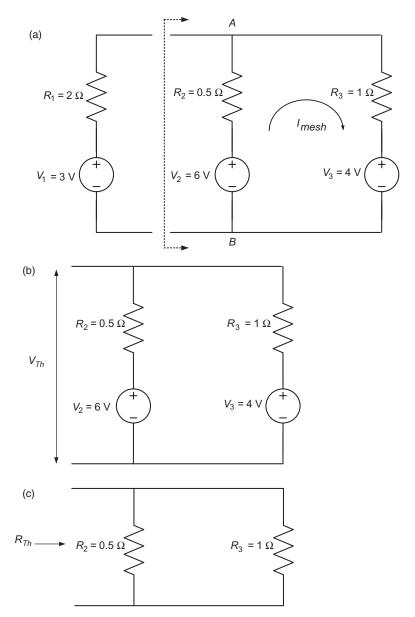

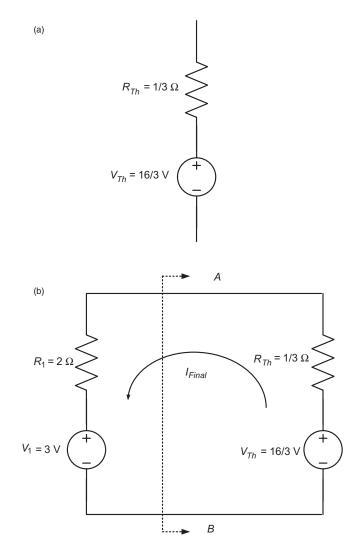

- 3.3 The Thévenin Method / 165

- 3.3.1 Application of the Thévenin Method / 167

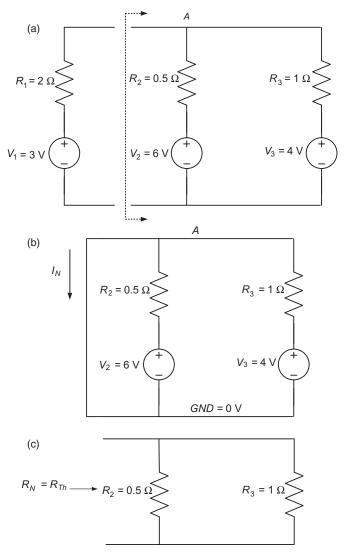

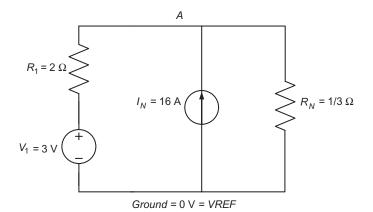

- 3.4 Norton's Method / 172

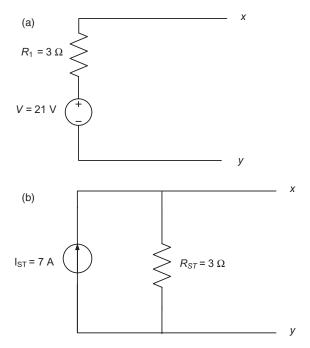

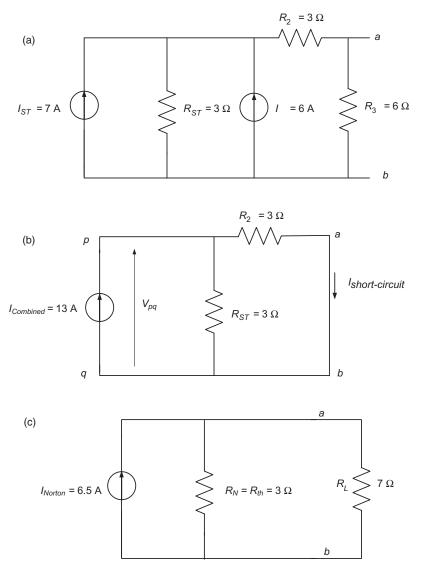

- 3.4.1 Source Transformations / 174

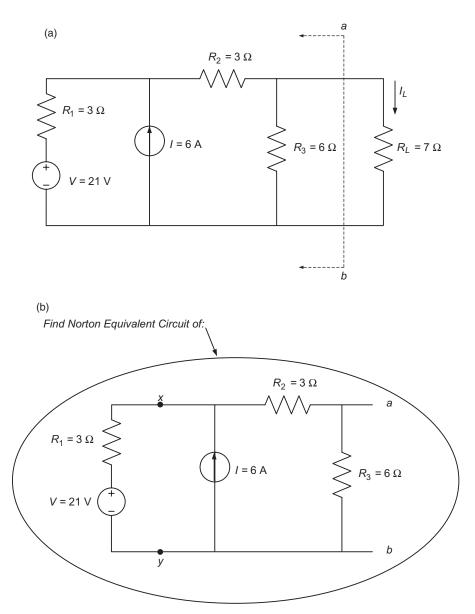

- 3.4.2 Finding the Norton Equivalent Circuit Directly from the Given Circuit / 175

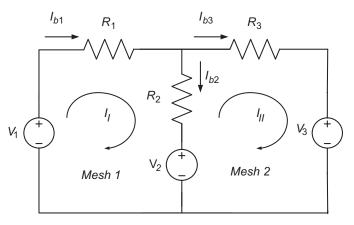

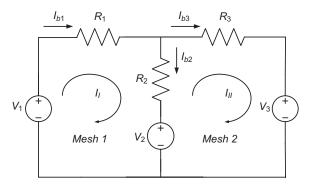

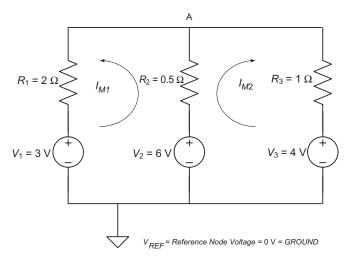

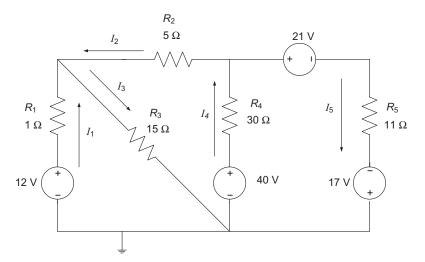

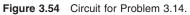

- 3.5 The Mesh Method of Analysis / 179

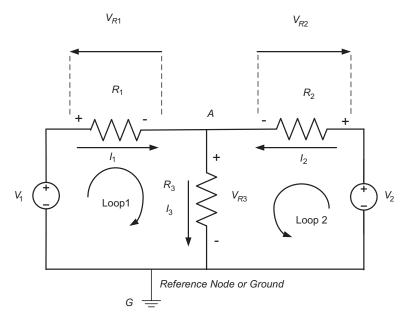

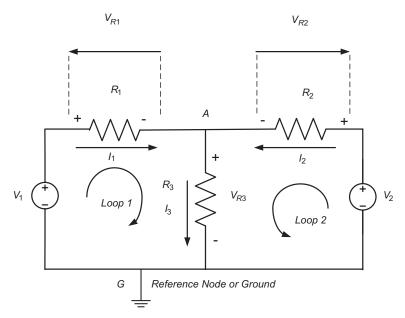

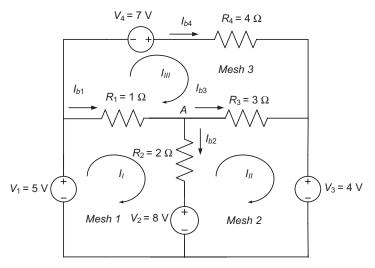

- 3.5.1 Establishing Mesh Equations. Circuits with Voltage Sources / 180

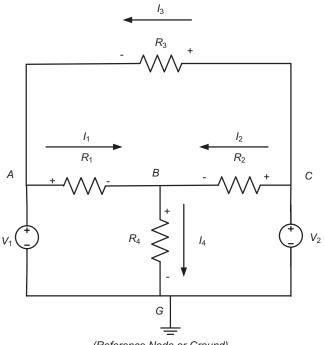

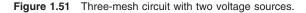

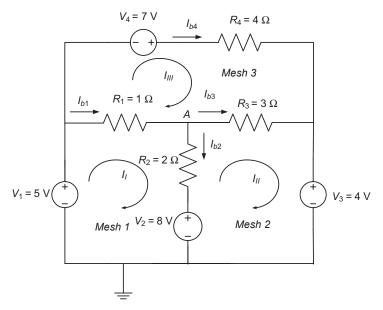

- 3.5.2 Establishing Mesh Equations by Inspection of the Circuit / 186

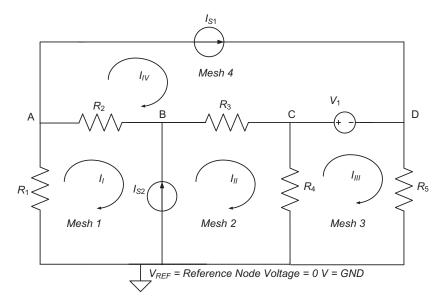

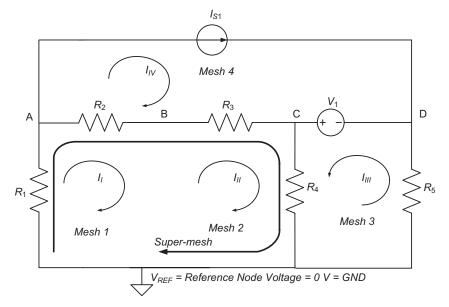

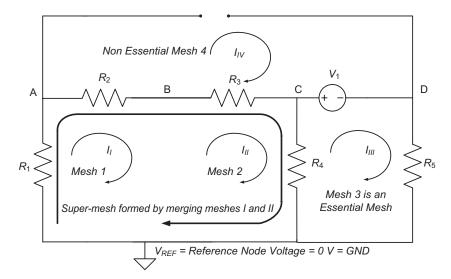

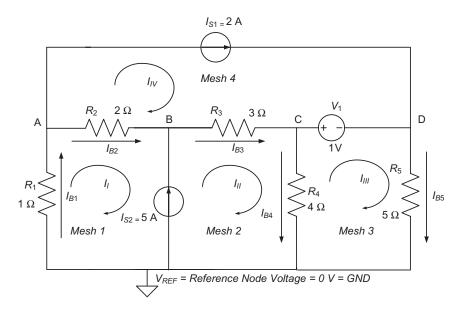

- 3.5.3 Establishing Mesh Equations When There Are also Current Sources / 189

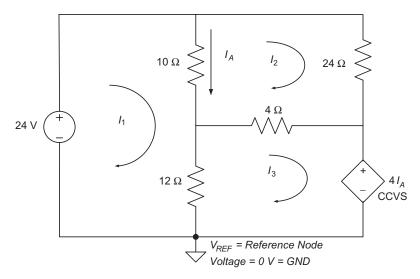

- 3.5.4 Establishing Mesh Equations When There Are also Dependent Sources / 196

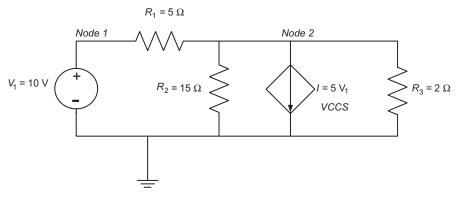

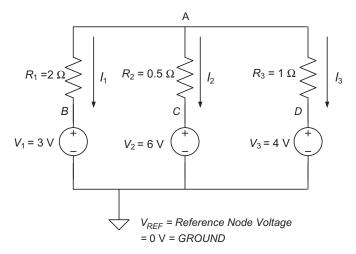

- 3.6 The Nodal Method of Analysis / 199

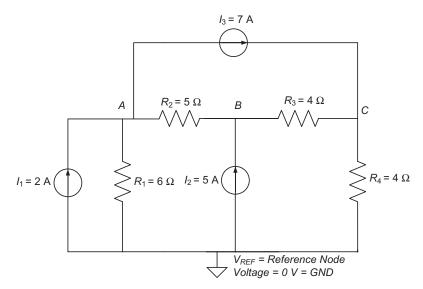

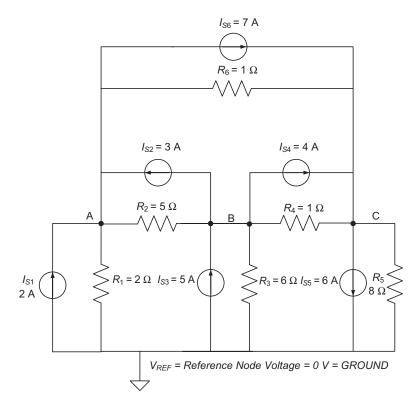

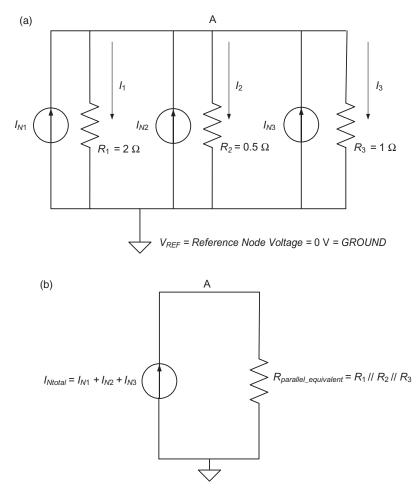

- 3.6.1 Establishing Nodal Equations: Circuits with Independent Current Sources / 199

- 3.6.2 Establishing Nodal Equations by Inspection: Circuits with Current Sources / 201

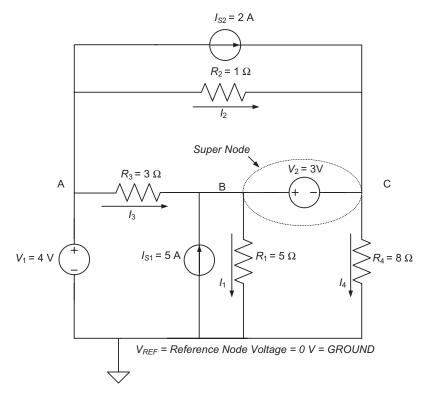

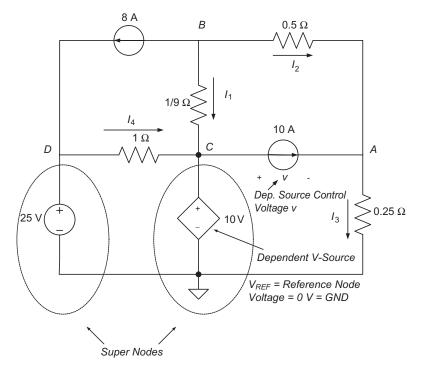

- 3.6.3 Establishing Nodal Equations When There Are also Voltage Sources / 205

- 3.6.4 Establishing Nodal Equations When There Are Dependent Sources / 207

- 3.7 Which One Is the Best Method? / 210

- 3.7.1 Superposition Theorem Highlights / 210

- 3.7.2 Thévenin Theorem Highlights / 211

- 3.7.3 Norton's Theorem Highlights / 211

- 3.7.4 Source Transformations Highlights / 212

- 3.7.5 Mesh Method of Analysis Highlights / 212

- 3.7.6 Nodal Method of Analysis Highlights / 212

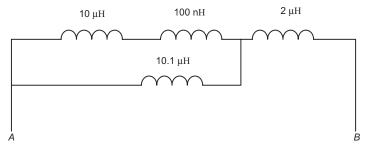

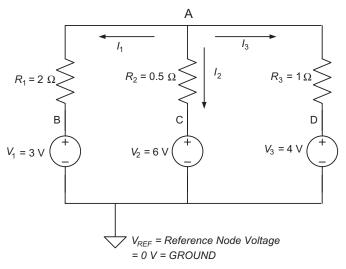

- 3.8 Using all the Methods / 213

- 3.8.1 Solving Using Superposition / 213

- 3.8.2 Example 3.21: Solving the Circuit of Figure 3.36 by Thévenin / 216

- 3.8.3 Example 3.22: Solving the Circuit of Figure 3.36 by Norton / 219

- 3.8.4 Example 3.23: Solving the Circuit of Figure 3.36 Using Source Transformations / 221

- 3.8.5 Example 3.24: Solving the Circuit of Figure 3.36 Using the Mesh Method / 223

- 3.8.6 Example 3.25: Solving the Circuit of Figure 3.36 Using the Nodal Method / 224

- 3.9 Summary and Conclusions / 225

Further Reading / 225

Problems / 226

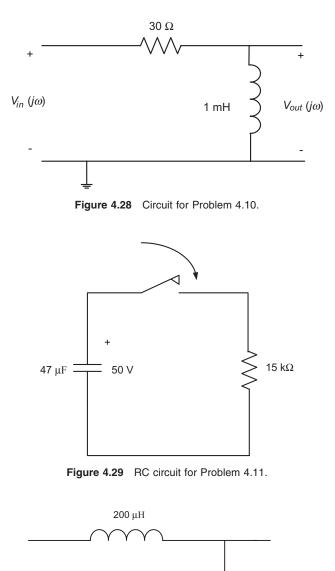

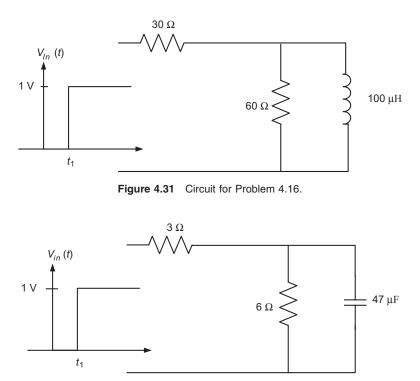

# 4 First- and Second-Order Circuits under Sinusoidal and Step Excitations

- 4.1 Introduction / 233

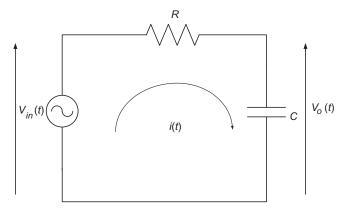

- 4.2 The First-Order RC Low-Pass Filter (LPF) / 235

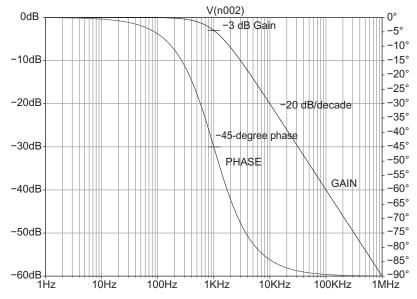

- 4.2.1 Frequency Domain Analysis / 235

- 4.2.2 Brief Introduction to Gain and the Decibel (dB) / 236

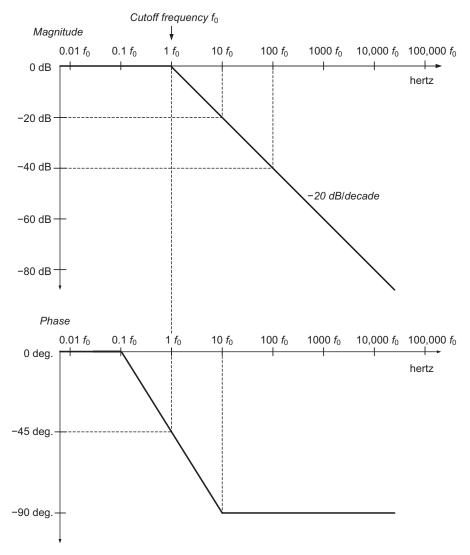

- 4.2.3 RC LPF Magnitude and Phase Bode Plots / 238

- 4.2.4 *RC* LPF Drawing a Bode Plot Using Just the Asymptotes / 241

- 4.2.5 Interpretation of the *RC* LPF Bode Plots in the Time Domain / 244

- 4.2.6 Why Do We Call This Circuit a LPF? / 245

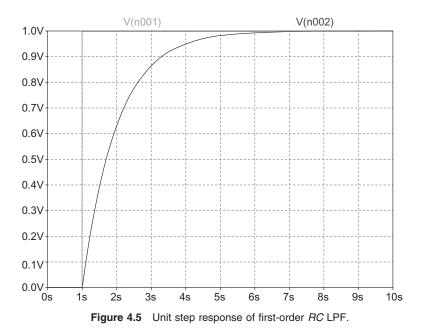

- 4.2.7 Time Domain Analysis of the RC LPF / 245

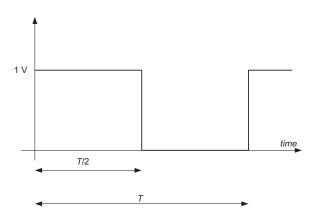

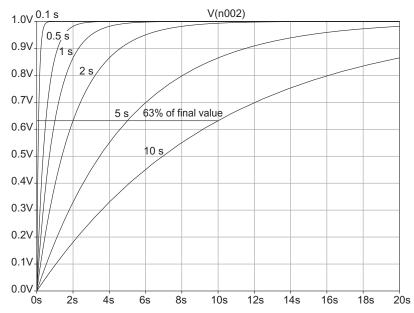

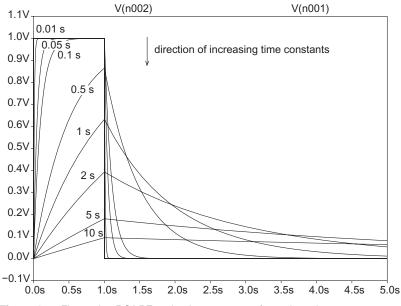

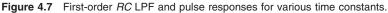

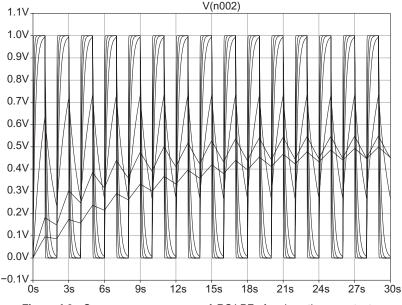

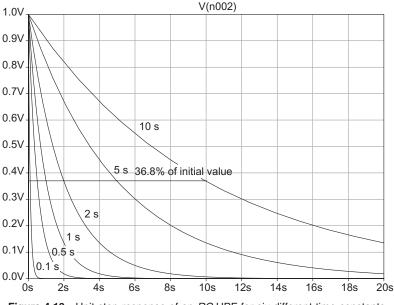

- 4.2.8 First-order *RC* LPF under Pulse and Square-Wave Excitation / 248

- 4.2.9 The *RC* LPF as an Integrator / 251

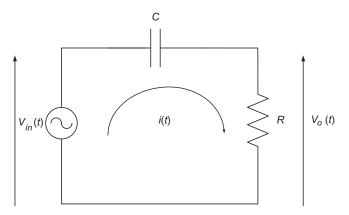

- 4.3 The First-Order RC High-Pass Filter (HPF) / 252

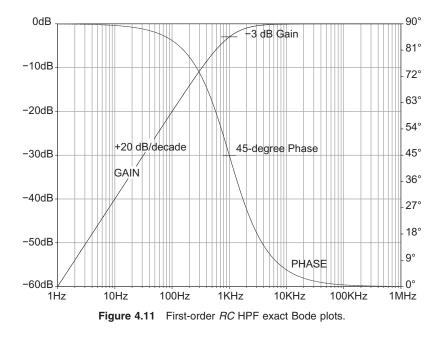

- 4.3.1 RC HPF Frequency Domain Analysis / 253

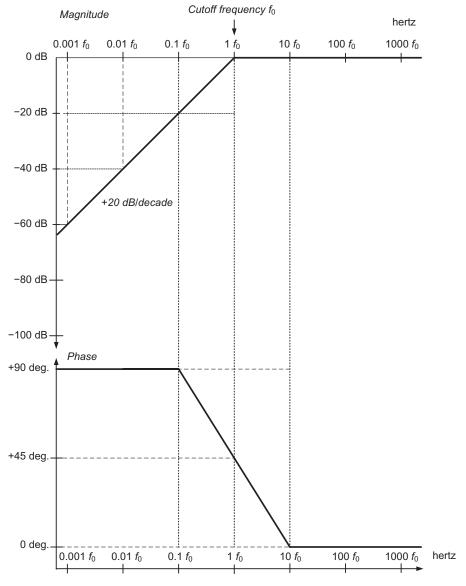

- 4.3.2 Drawing an *RC* HPF Bode Plot Using Just the Asymptotes / 254

- 4.3.3 Interpretation of the *RC* HPF Bode Plots in the Time Domain / 257

- 4.3.4 Why Do We Call This Circuit an HPF? / 258

- 4.3.5 Time Domain Analysis of the RC HPF / 258

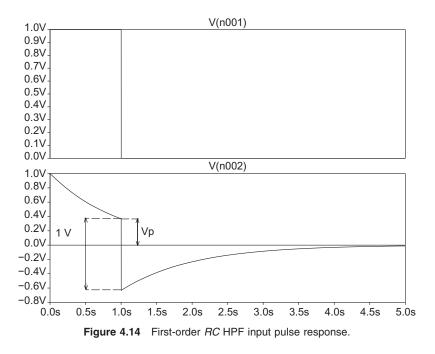

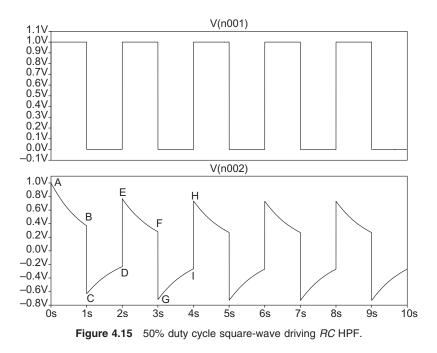

- 4.3.6 First-Order *RC* LPF under Pulse and Square-Wave Excitation / 260

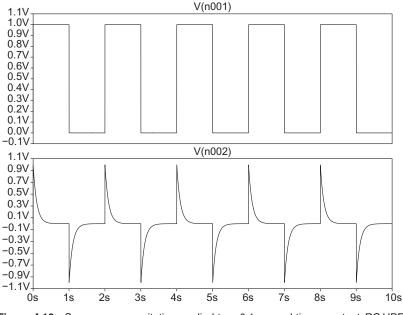

- 4.3.7 The RC HPF as a Differentiator / 263

- 4.4 Second-Order Circuits / 265

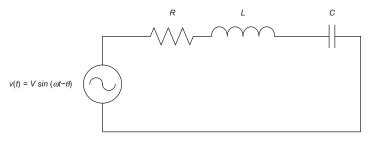

- 4.5 Series RLC Second-Order Circuit / 266

- 4.6 Second-Order Circuit in Sinusoidal Steady State: Bode Plots / 275

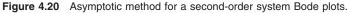

- 4.7 Drawing the Second-Order Bode Plots Using Asymptotic Approximations / 278

- 4.8 Summary / 279

- Further Reading / 279

- Problems / 280

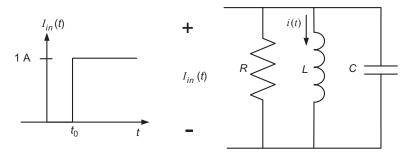

# 5 The Operational Amplifier as a Circuit Element

- 5.1 Introduction to the Operational Amplifier / 287

- 5.2 Ideal and Real Op Amps / 288

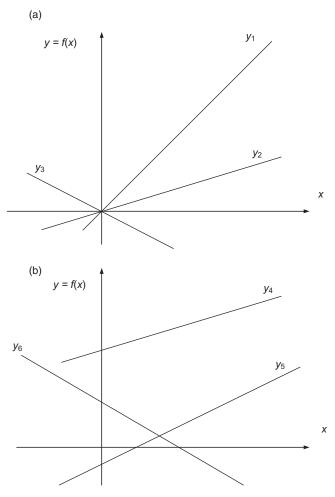

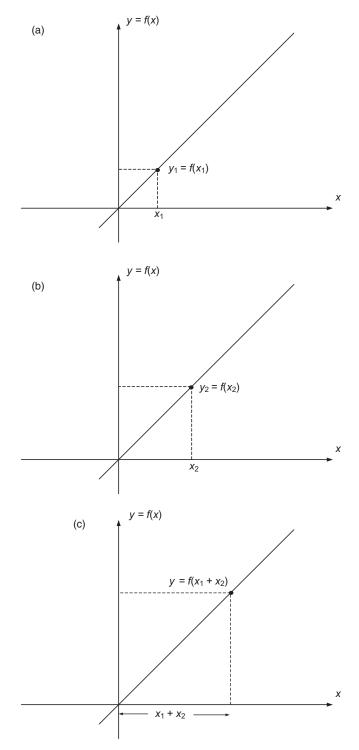

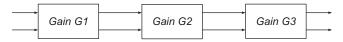

- 5.3 Brief Definition of Linear Amplifiers / 290

- 5.4 Linear Applications of Op Amps / 294

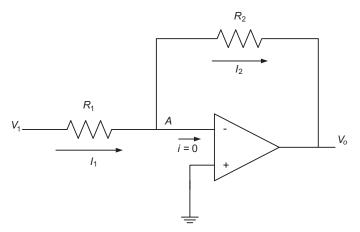

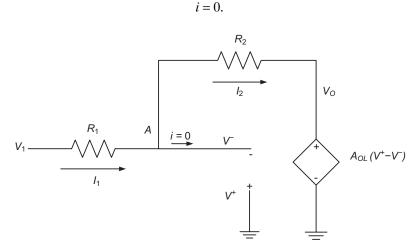

- 5.4.1 The Inverting Amplifier / 294

- 5.4.2 The Noninverting Amplifier / 306

- 5.4.3 The Buffer or Noninverting Amplifier of Unity Gain / 309

- 5.4.4 The Inverting Adder / 314

- 5.4.5 The Difference Amplifier / 316

- 5.4.6 The Inverting Integrator / 321

- 5.4.7 The Inverting Differentiator / 322

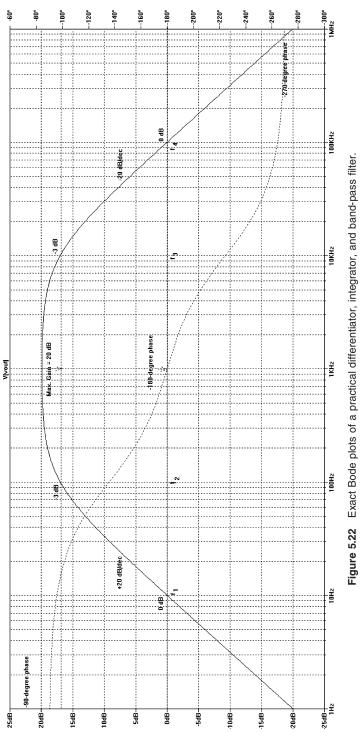

- 5.4.8 A Practical Integrator and Differentiator Circuit / 326

- 5.5 Op Amps Nonlinear Applications / 331

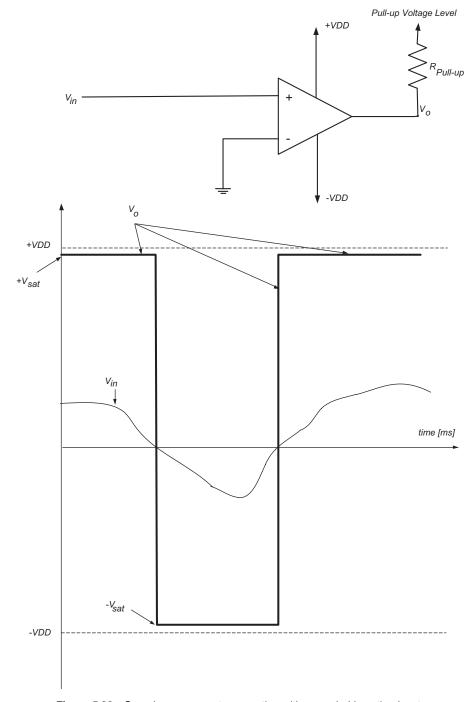

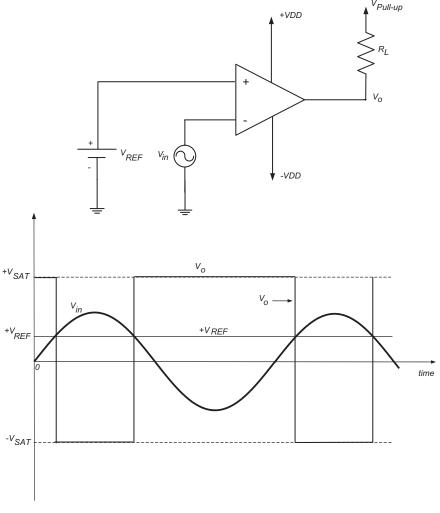

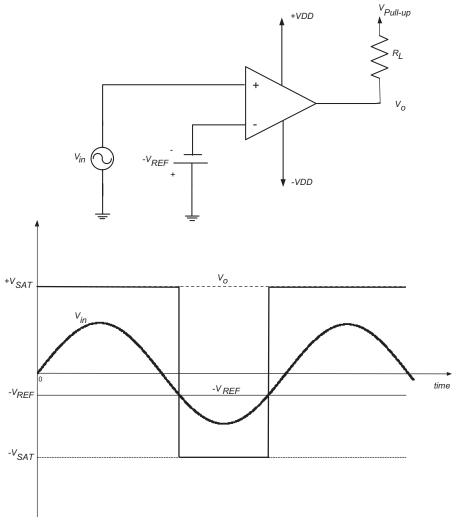

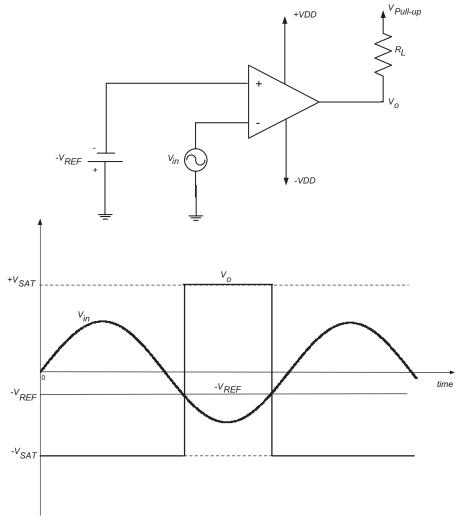

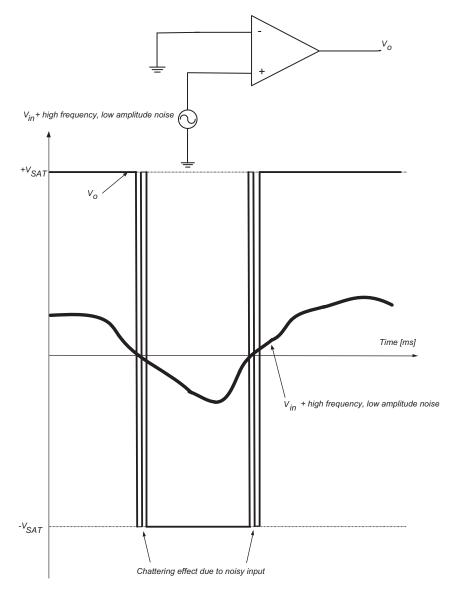

- 5.5.1 The Open-Loop Comparator / 332

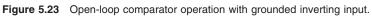

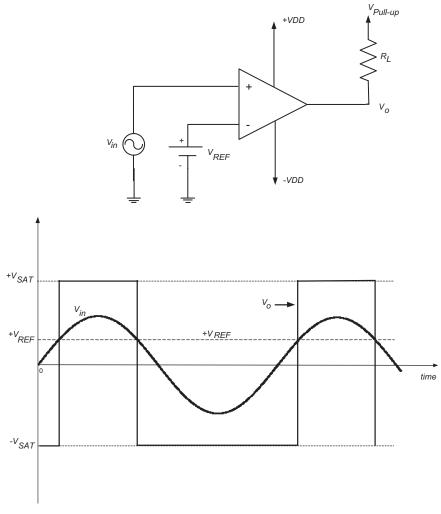

- 5.5.2 Positive and Negative Voltage-Level Detectors Using Comparators / 332

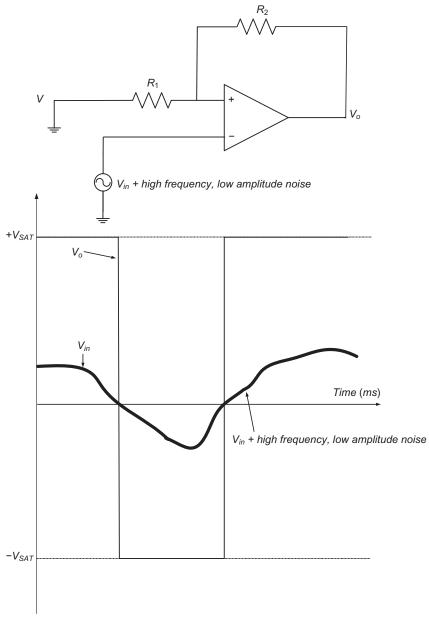

- 5.5.3 Comparator with Positive Feedback (Hysteresis) / 336

- 5.6 Operational Amplifiers Nonidealities / 341

- 5.7 Op Amp Selection Criteria / 343

- 5.8 Summary / 347

- Further Reading / 348

Problems / 348

Appendix to Chapter 5 / 353

# 6 Electronic Devices: Diodes, BJTs, and MOSFETs

- 6.1 Introduction to Electronic Devices / 354

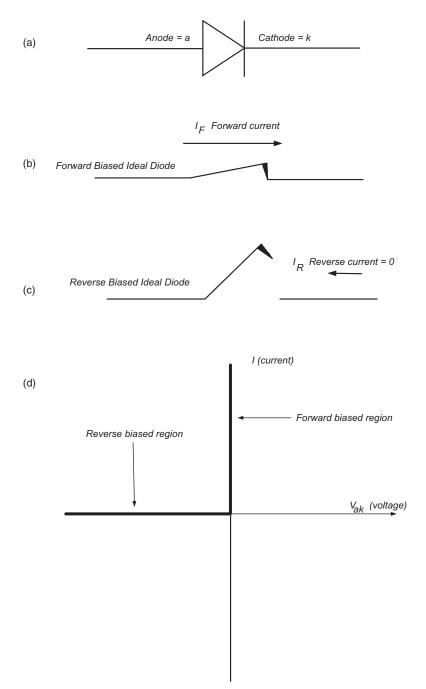

- 6.2 The Ideal Diode / 355

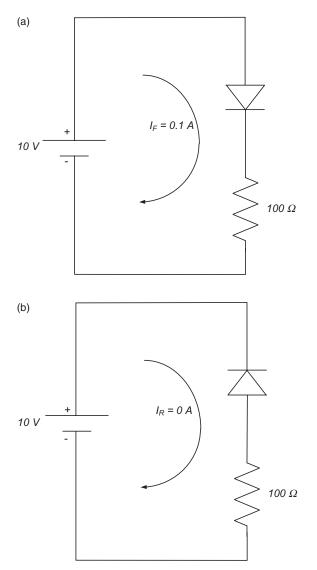

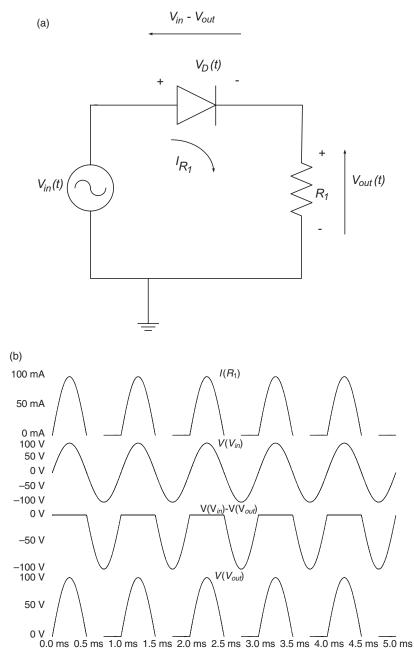

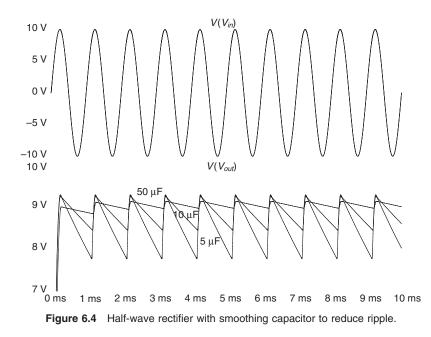

- 6.2.1 The Half-Wave Rectifier / 357

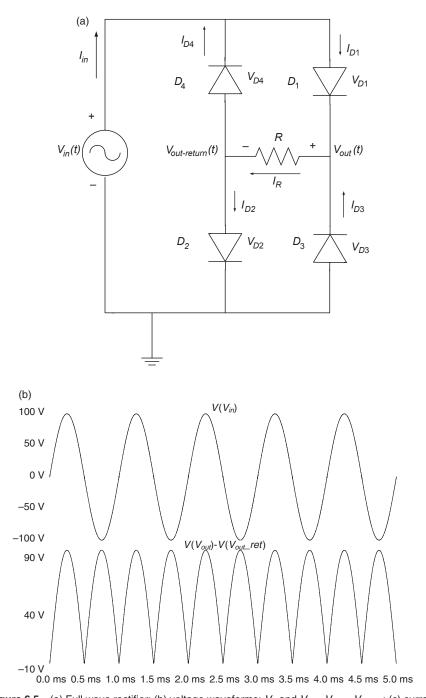

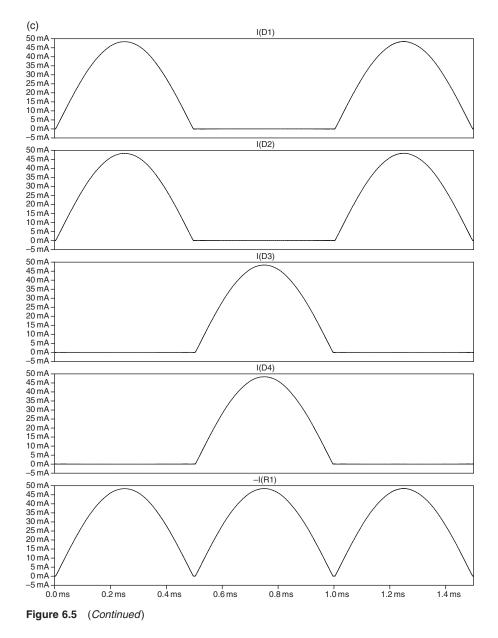

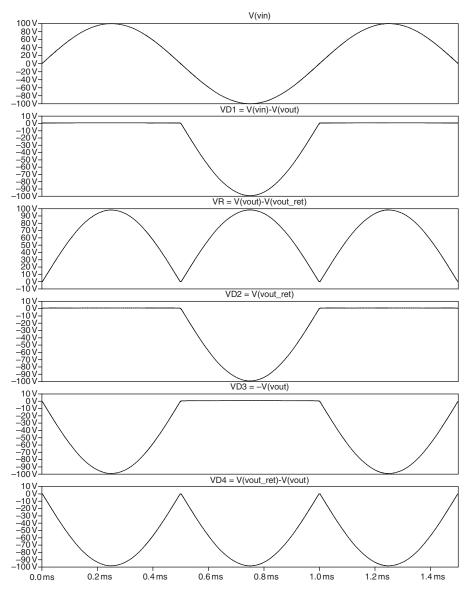

- 6.2.2 The Full-Wave Bridge Rectifier / 360

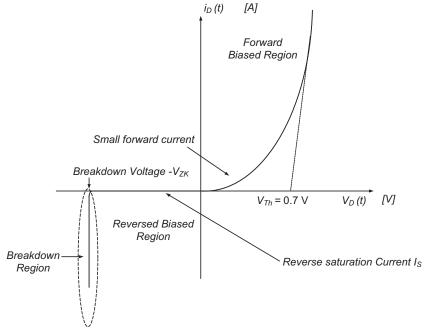

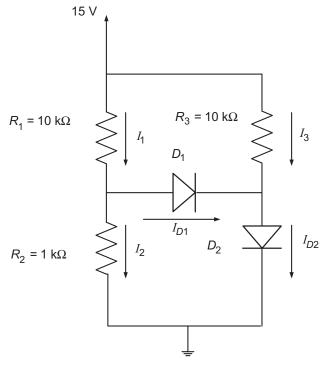

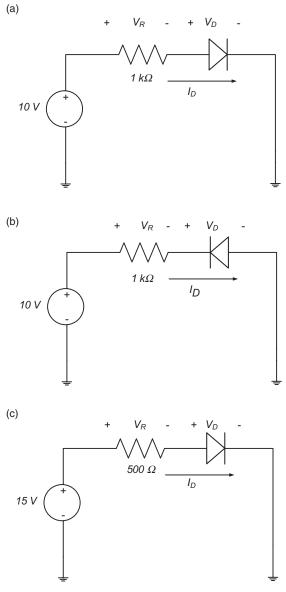

- 6.2.3 The Real Silicon Diode *I-V* Characteristics: Forward-Bias, Reverse-Bias, and Breakdown Regions / 363

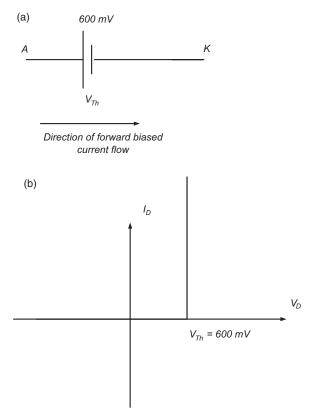

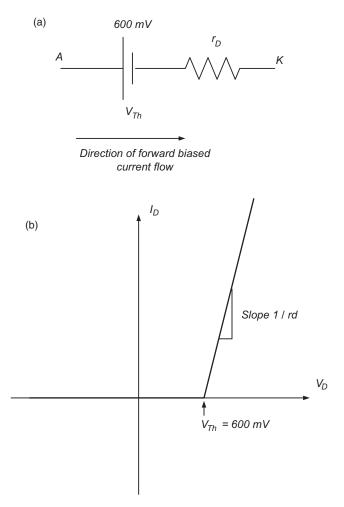

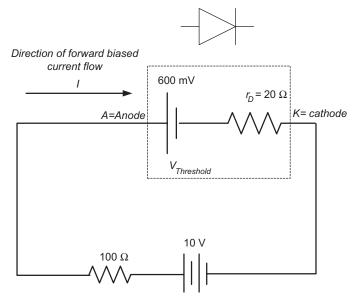

- 6.2.4 Two More Realistic Diode Models / 367

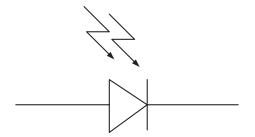

- 6.2.5 Photodiode / 369

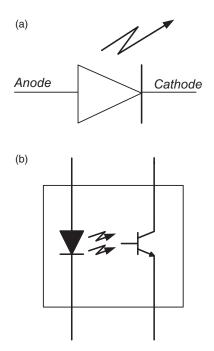

- 6.2.6 Light Emitting Diode (LED) / 369

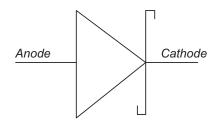

- 6.2.7 Schottky-Barrier Diode / 371

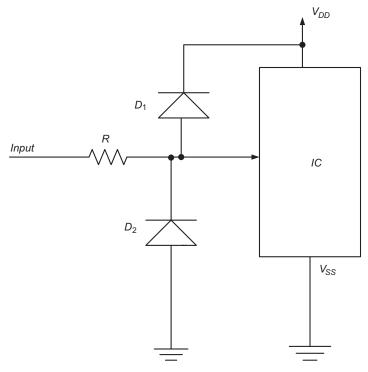

- 6.2.8 Another Diode Application: Limiting and Clamping Diodes / 371

- 6.2.9 Diode Selection / 372

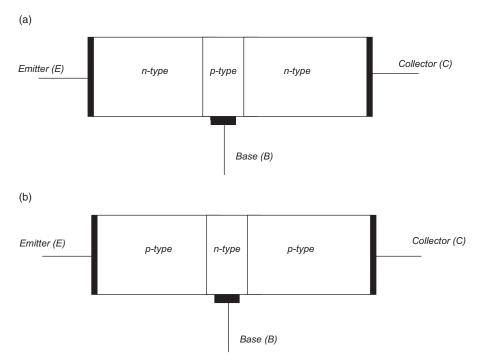

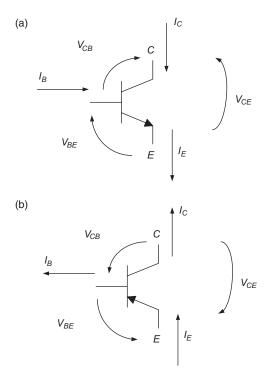

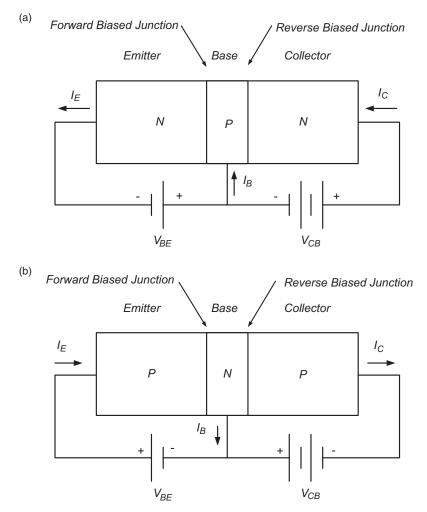

- 6.3 Bipolar Junction Transistors (BJT) / 374

- 6.3.1 Basic Concepts on Intrinsic, *n*-type and *p*-type Silicon Materials / 374

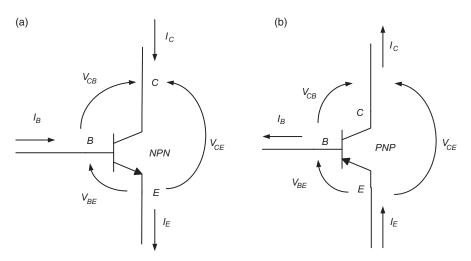

- 6.3.2 The BJT as a Circuit Element / 376

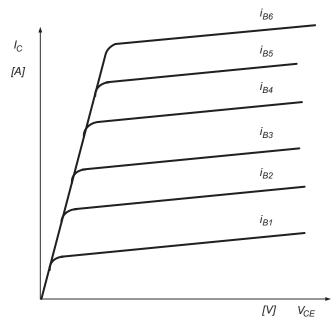

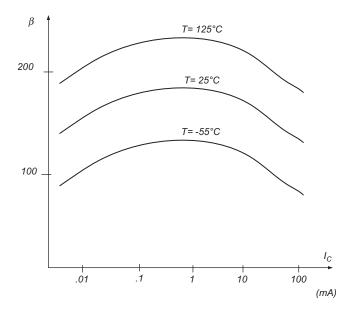

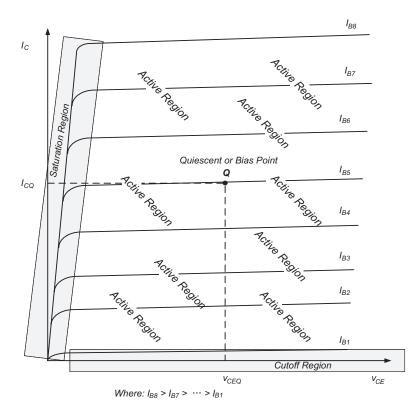

- 6.3.3 Bipolar Transistor *I-V* Characteristics / 377

- 6.3.4 Biasing Techniques of Bipolar Transistors / 382

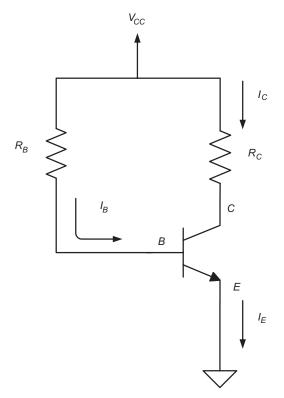

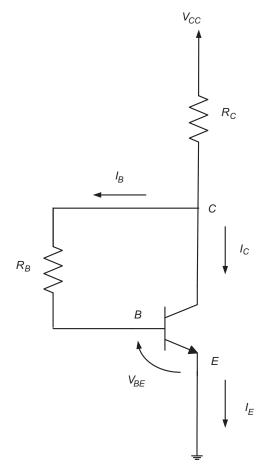

- 6.3.5 Very Simple Biasing / 385

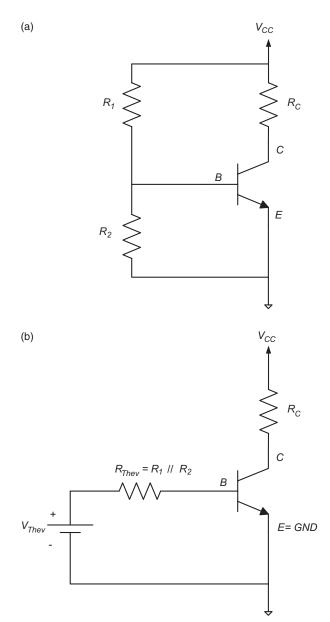

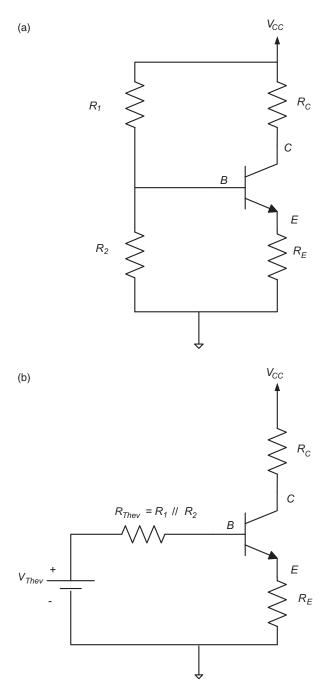

- 6.3.6 Resistor Divider Biasing / 387

- 6.3.7 Emitter Degeneration Resistor Biasing / 391

- 6.3.8 Self-Biased Staged / 394

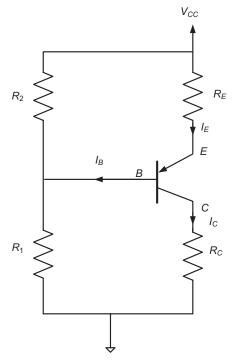

- 6.3.9 Biasing Techniques of PNP Bipolar Transistors / 396

- 6.3.10 Small Signal Model and Single-Stage Bipolar Amplifier Configurations / 397

- 6.3.11 Common Emitter ( $C_E$ ) Configuration / 399

- 6.3.12 Common Emitter ( $C_E$ ) Configuration with Emitter Degeneration / 404

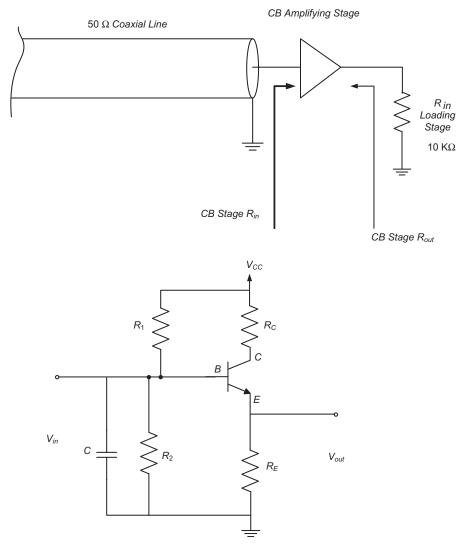

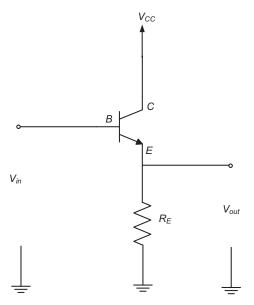

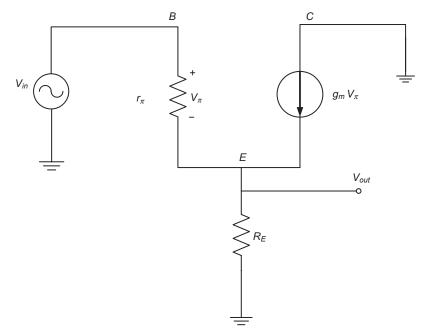

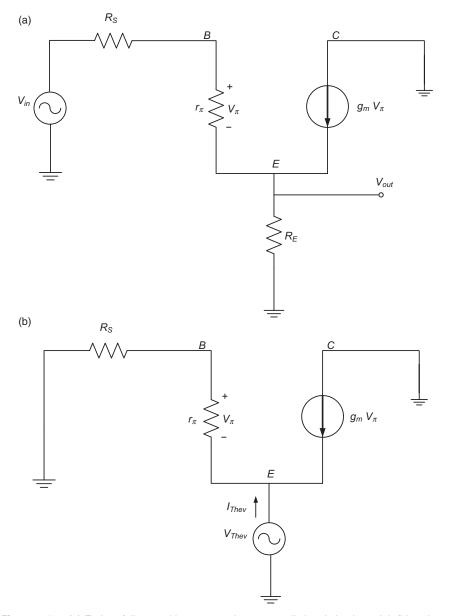

- 6.3.13 Common-Base (CB) Configuration / 407

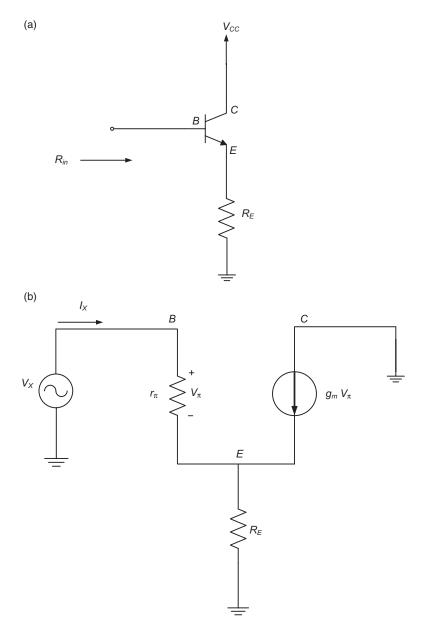

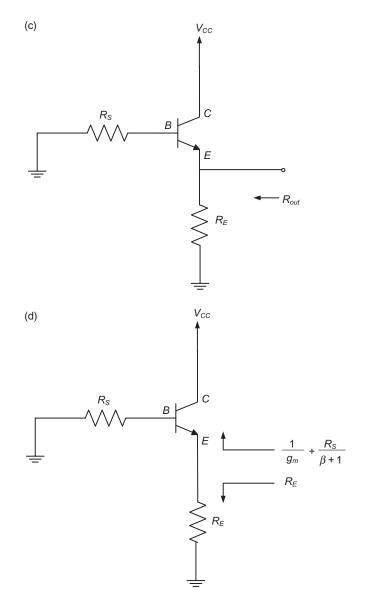

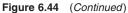

- 6.3.14 The Common-Collector (CC) Configuration / 415

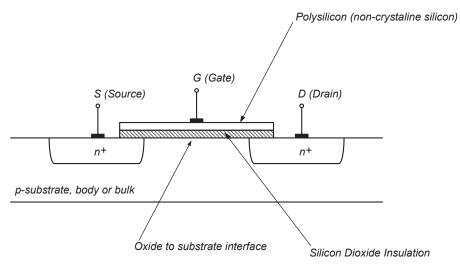

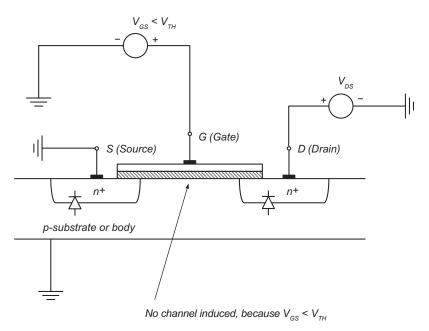

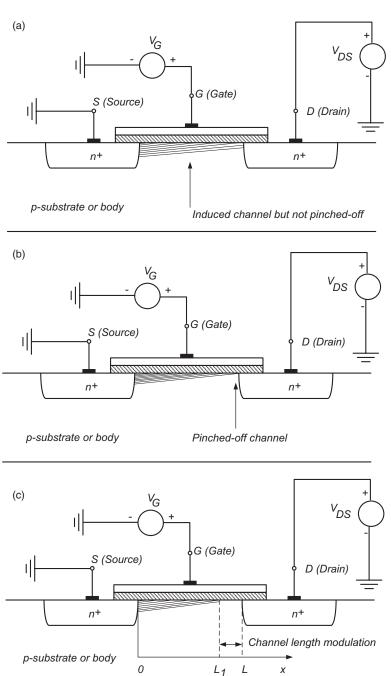

- 6.4 Metal Oxide Field Effect Transistor (MOSFET) / 420

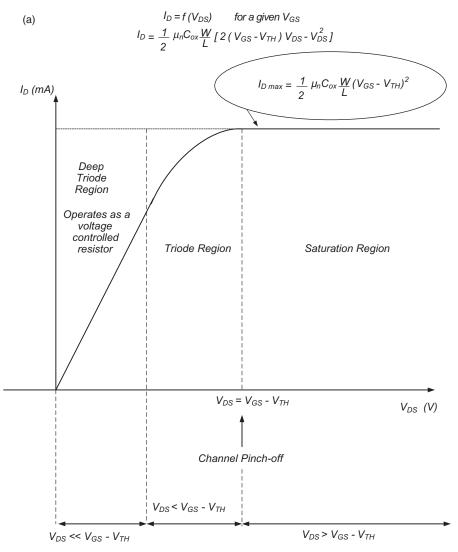

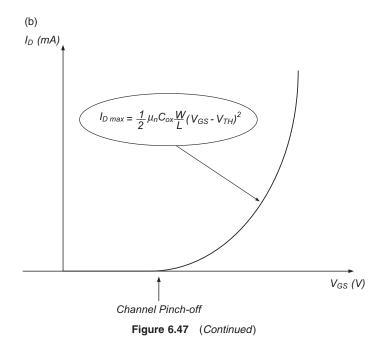

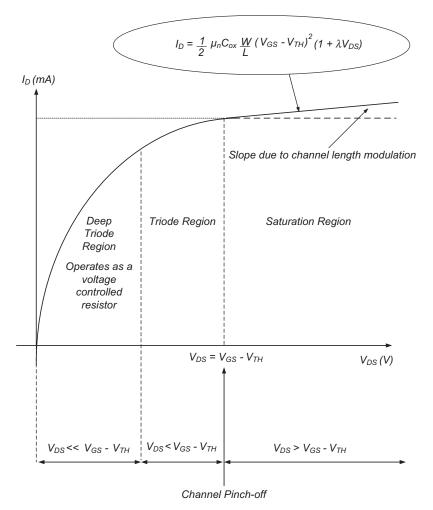

- 6.4.1 MOSFET I-V Characteristics / 424

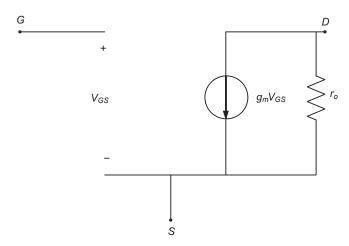

- 6.4.2 MOSFET Small Signal Model / 427

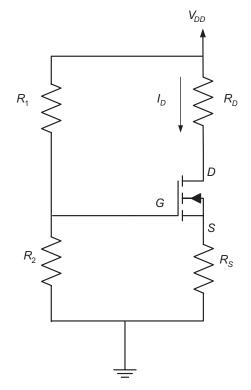

- 6.4.3 MOSFET Biasing Techniques / 428

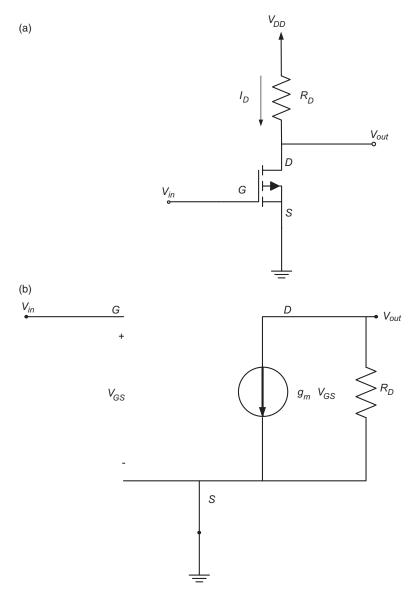

- 6.4.4 Common Source (CS) Configuration / 434

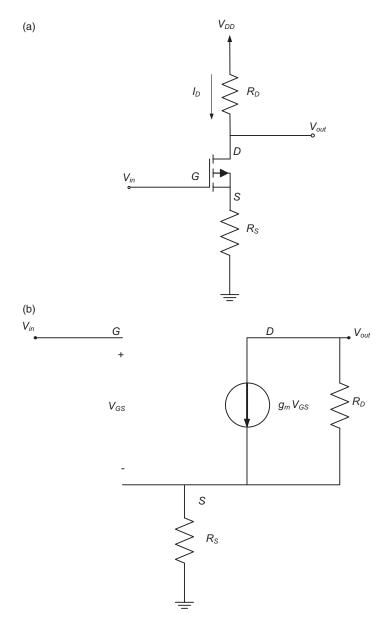

- 6.4.5 Common Source (CS) Configuration with Degeneration / 436

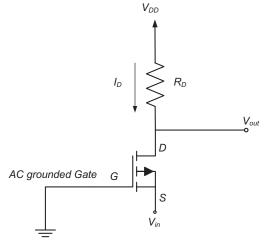

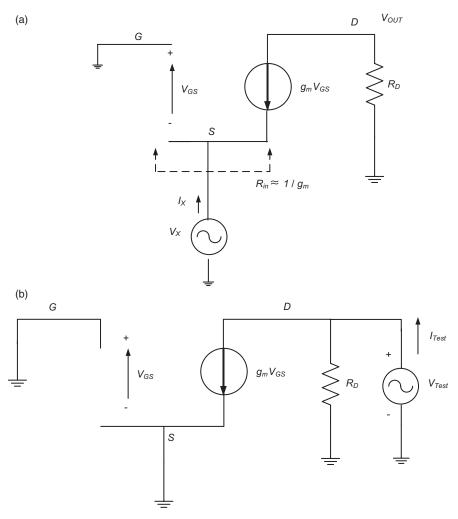

- 6.4.6 Common Gate (CG) Configuration / 437

- 6.4.7 Common Drain (CD) Configuration or Source Follower / 439

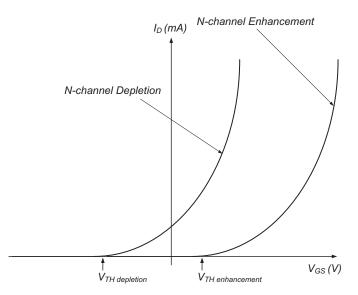

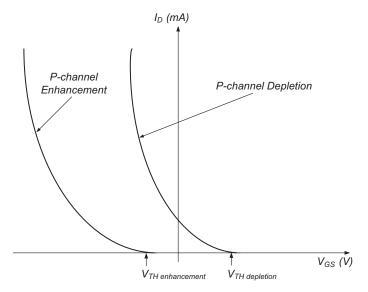

- 6.4.8 Other MOSFETs: Enhancement Mode *p*-Channel and Depletion Mode (*n*-Channel and *p*-Channel) / 439

456

6.5 Summary / 443 Further Reading / 446

Problems / 446

# 7 Combinational Circuits

- 7.1 Introduction to Digital Circuits / 456

- 7.2 Binary Numbers: a Quick Introduction / 456

- 7.3 Boolean Algebra / 460

- 7.3.1 AND Logic Operation 460

- 7.3.2 OR Logic Operation (Also Called Inclusive OR, or XNOR) / 461

- 7.3.3 NOT Logic Operation or Inversion—*NAND* and *NOR / 462*

- 7.3.4 Exclusive OR Logic Operation or XOR / 463

- 7.3.5 DeMorgan's Laws, Rules, and Theorems / 464

- 7.3.6 Other Boolean Algebra Postulates and Theorems / 465

- 7.3.7 The Duality Principle / 466

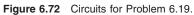

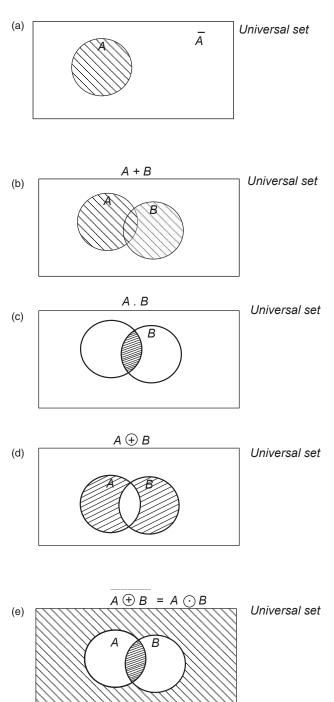

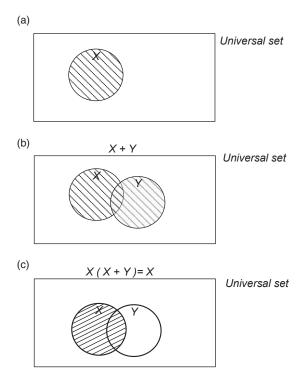

- 7.3.8 Venn Diagrams / 467

- 7.4 Minterms: Standard or Canonical Sum of Products (SOP) Form / 467

- 7.5 Maxterms: Standard or Canonical Product of Sums (POS) Form / 472

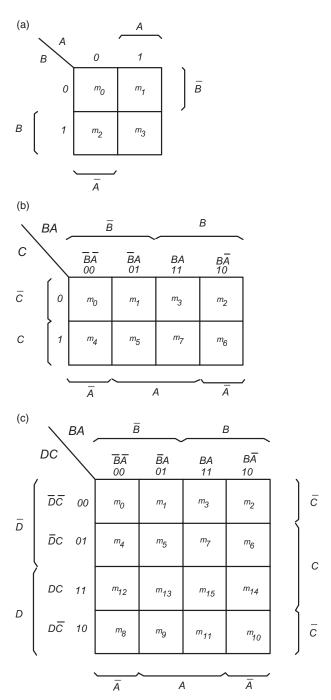

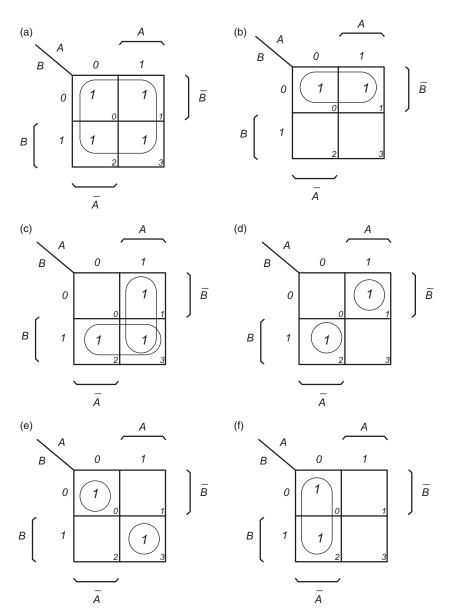

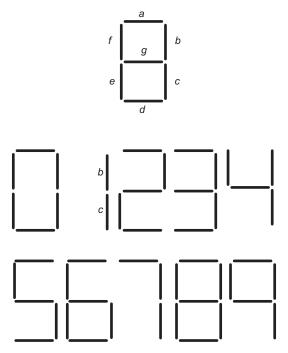

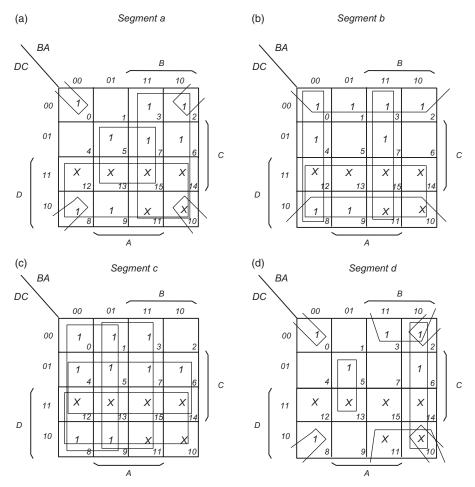

- 7.6 Karnaugh Maps and Design Examples / 473

- 7.6.1 Two-Variable Karnaugh Maps / 474

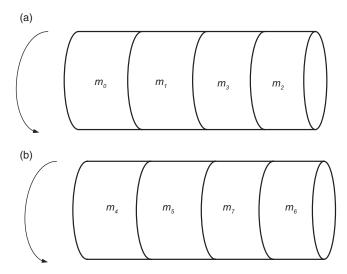

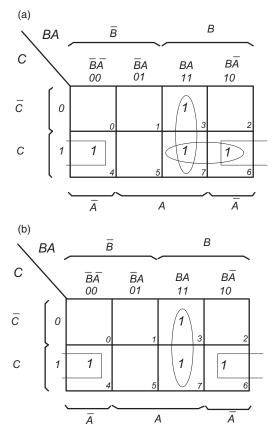

- 7.6.2 Three-Variable Karnaugh Maps / 479

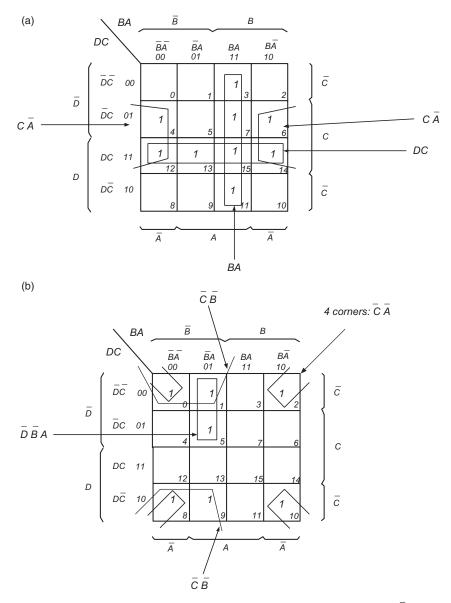

- 7.6.3 Four-Variable Karnaugh Maps / 484

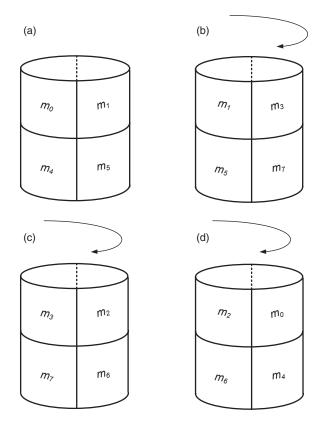

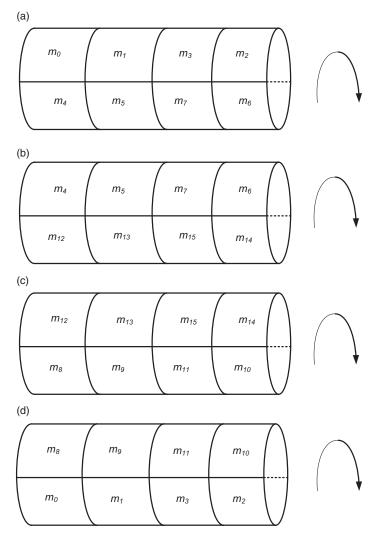

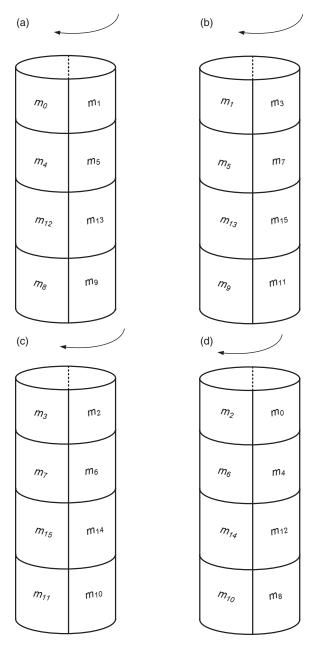

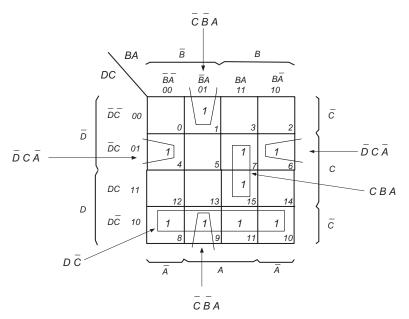

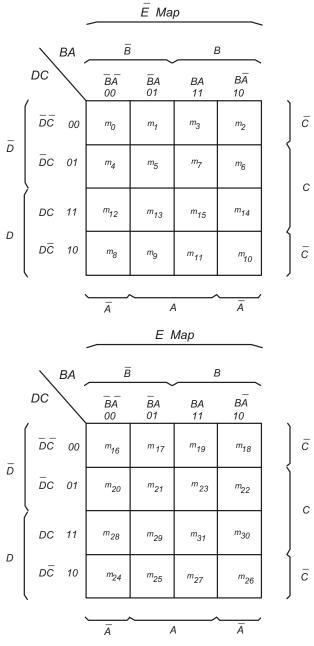

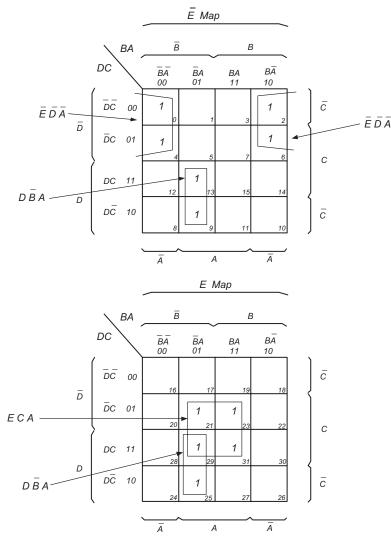

- 7.6.4 Five-Variable Karnaugh Maps / 487

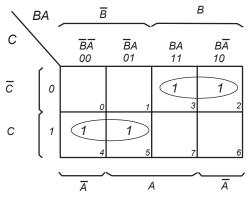

- 7.7 Product of Sums Simplifications / 490

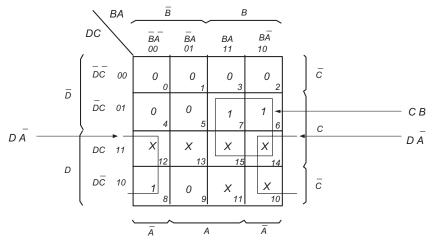

- 7.8 Don't Care Conditions / 491

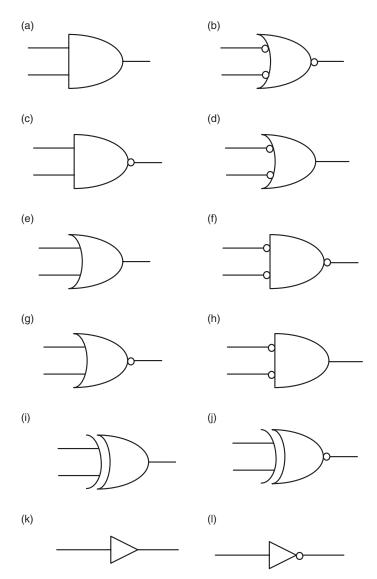

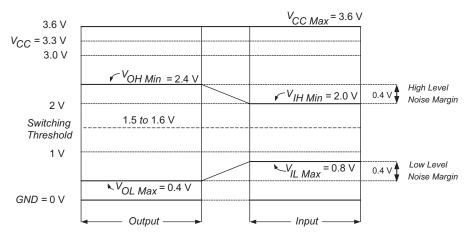

- 7.9 Logic Gates: Electrical and Timing Characteristics / 495

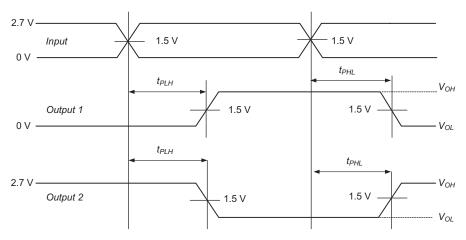

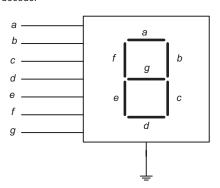

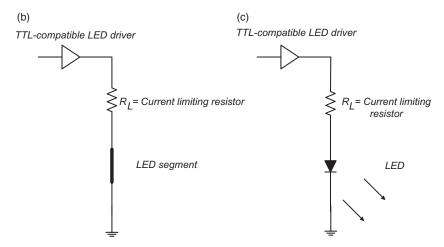

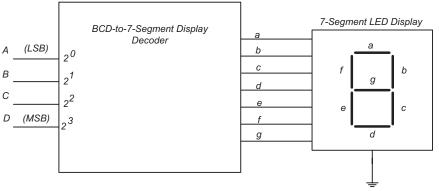

- 7.9.1 Gates Key Electrical Characteristics / 497

- 7.9.2 Gates Key Timing Characteristics / 499

- 7.10 Summary / 500

- Further Reading / 500

Problems / 500

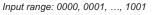

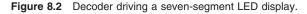

# 8 Digital Design Building Blocks and More Advanced Combinational Circuits

- 8.1 Combinational Circuits with More than One Output / 503

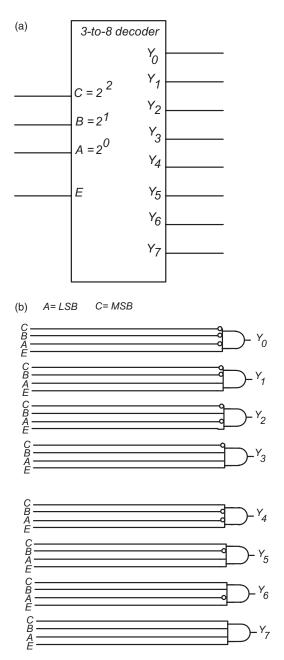

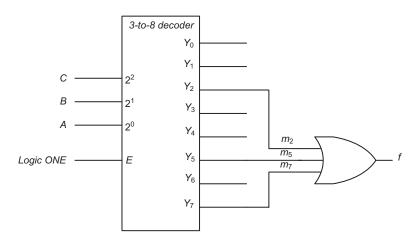

- 8.2 Decoders and Encoders / 510

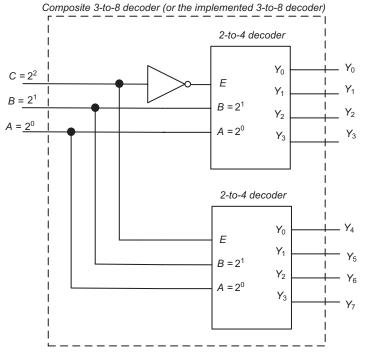

- 8.2.1 Making Larger Decoders with Smaller Ones / 515

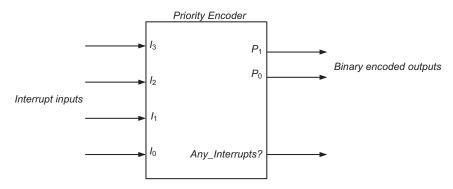

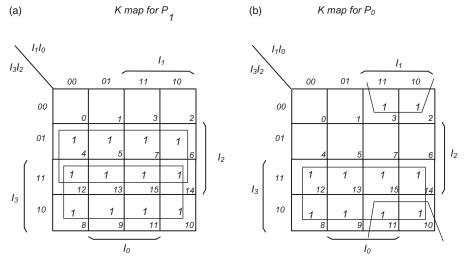

- 8.2.2 Encoders / 517

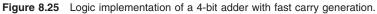

- 8.3 Multiplexers and Demultiplexers (MUXes and DEMUXes) / 519

- 8.3.1 Multiplexers / 521

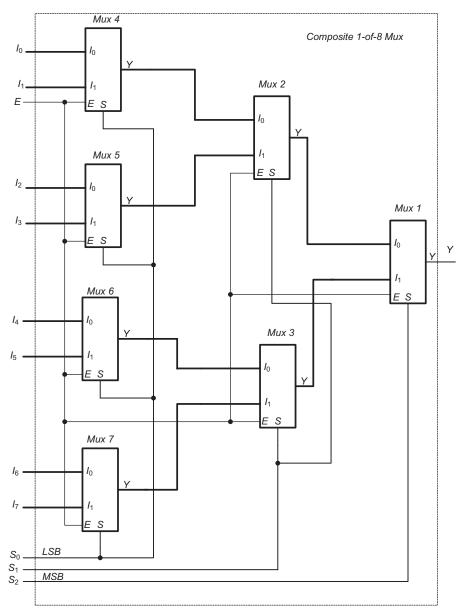

- 8.3.2 Building Larger Multiplexers / 522

- 8.3.3 De-Multiplexers / 526

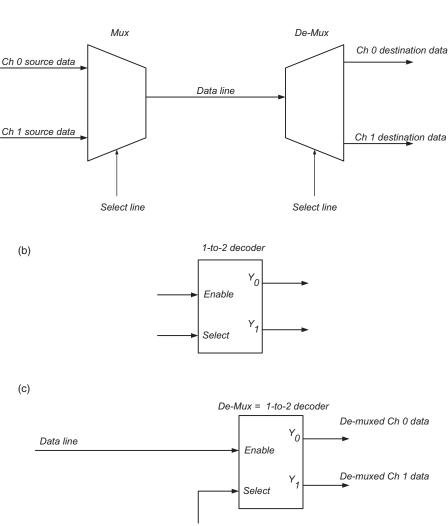

- 8.4 Signed and Unsigned Binary Numbers / 527

- 8.4.1 One's Complement Representation of Binary Numbers: Addition / 527

- 8.4.2 Two's Complement Representation of Binary Numbers: Addition / 531

- 8.4.3 Other Numbering Systems / 533

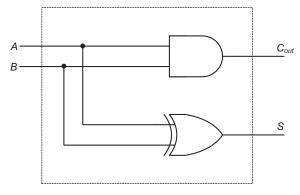

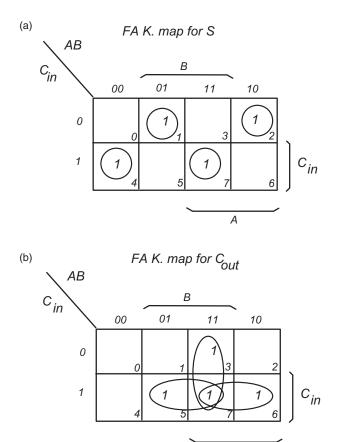

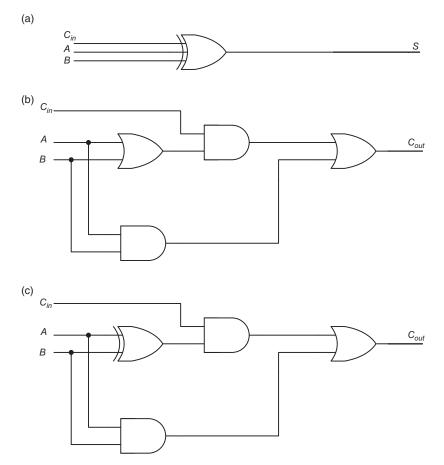

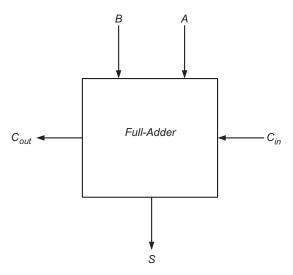

- 8.5 Arithmetic Circuits: Half-Adders (HA) and Full-Adders (FA) / 533

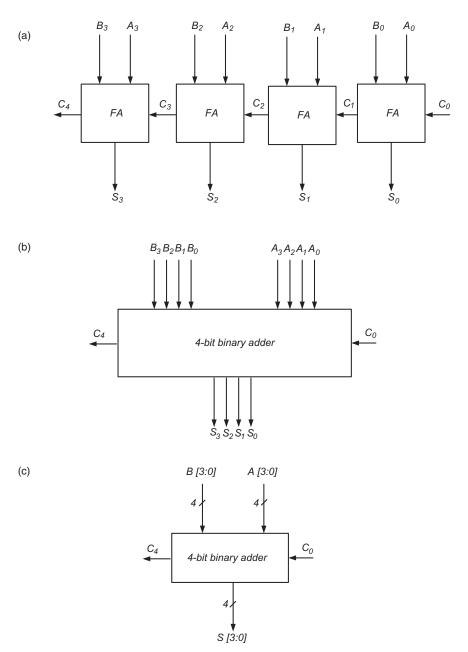

- 8.5.1 Building Larger Adders with Full-Adders / 536

- 8.5.2 Notes about Full-Adder Timing / 540

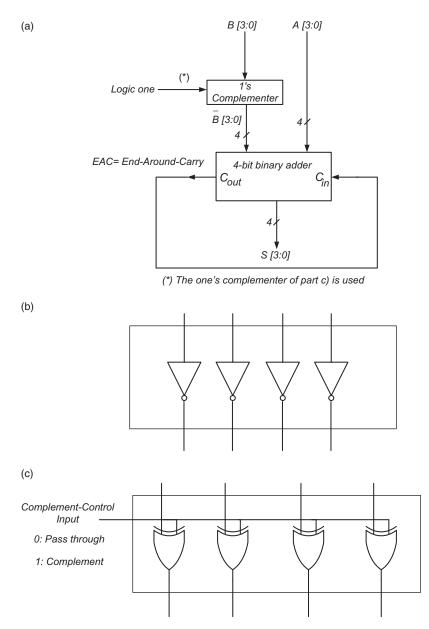

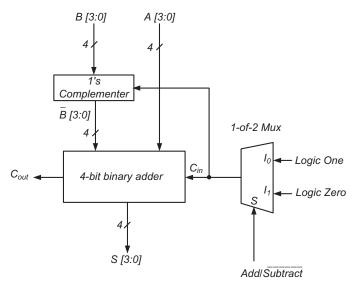

- 8.5.3 Subtracting with a 4-bit Adder Using 1's Complement Representation / 540

- 8.5.4 Subtracting with a 4-bit Adder Using 2's Complement Representation / 542

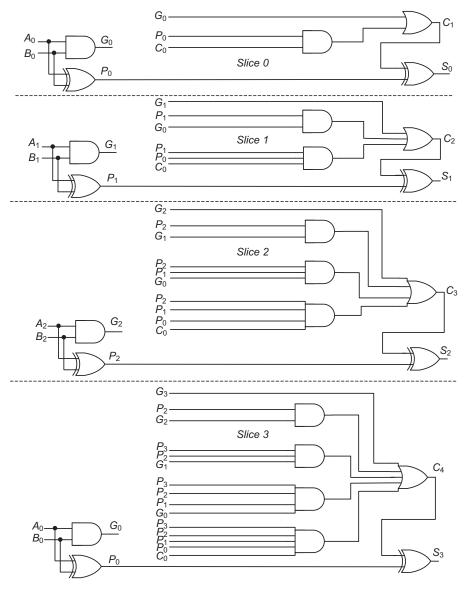

8.6 Carry Look Ahead (CLA) or Fast Carry Generation / 543

8.7 Some Short-Hand Notation for Large Logic Blocks / 546

8.8 Summary / 547

Further Reading / 548

Problems 548

# 9 Sequential Logic and State Machines

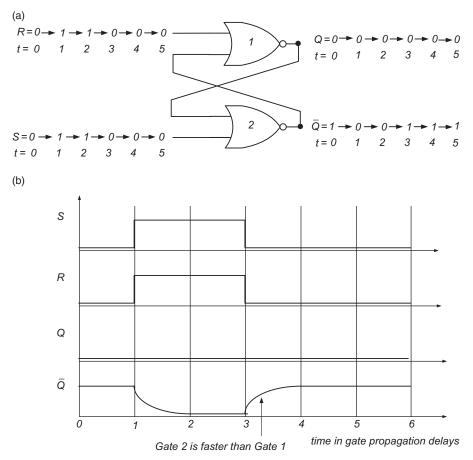

- 9.1 Introduction / 550

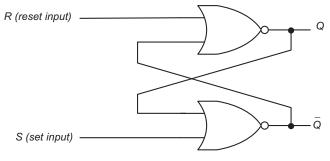

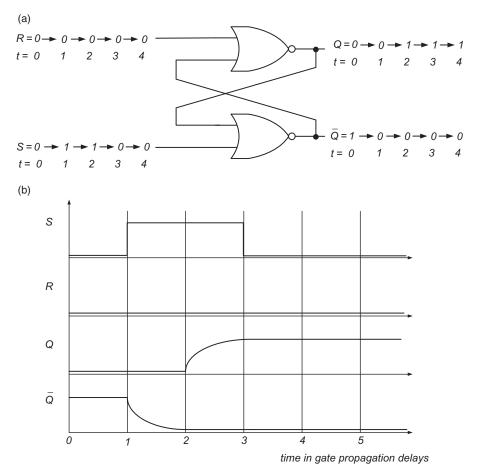

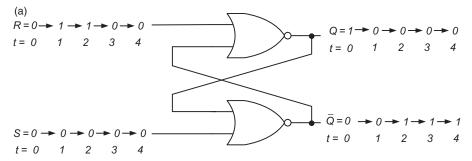

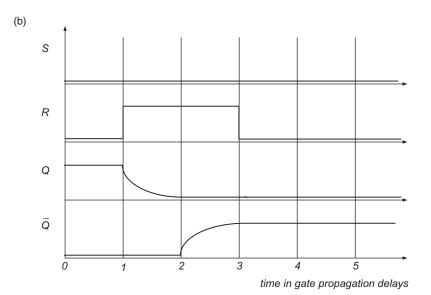

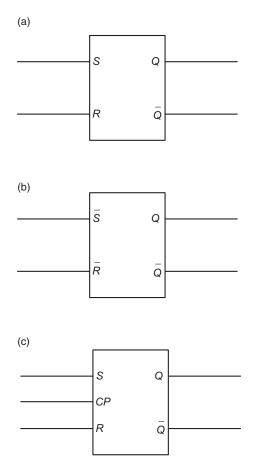

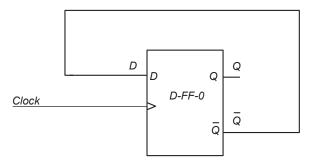

- 9.2 Latches and Flip-Flops (FF) / 552

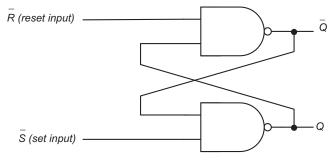

- 9.2.1 NAND-Implemented  $\overline{R} / \overline{S}$  Latch / 557

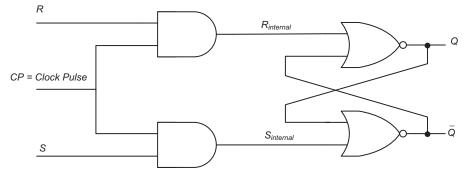

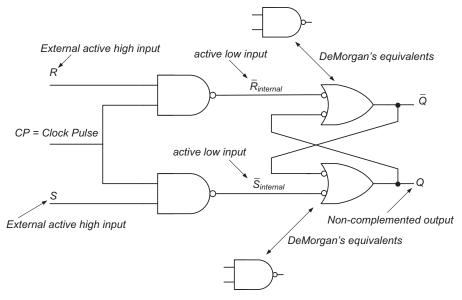

- 9.2.2 SR-Latch with Enable / 559

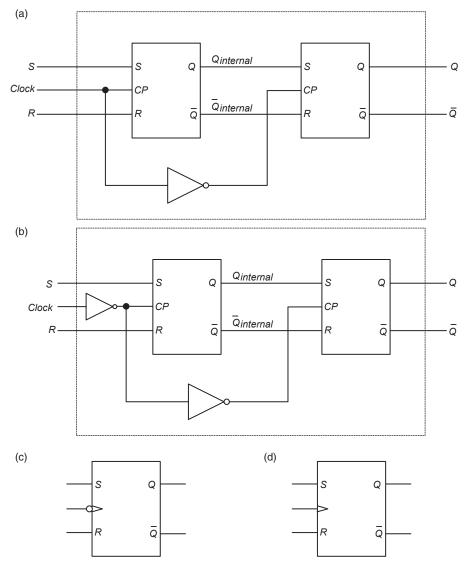

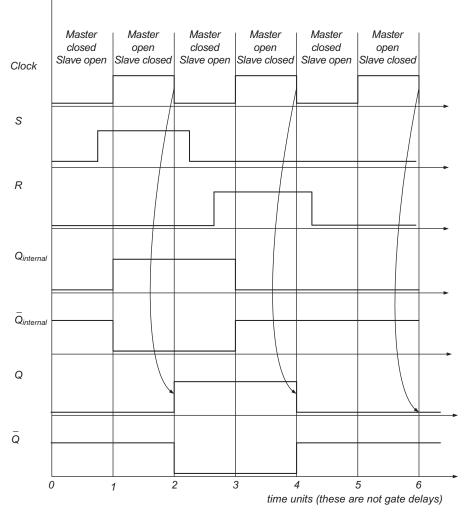

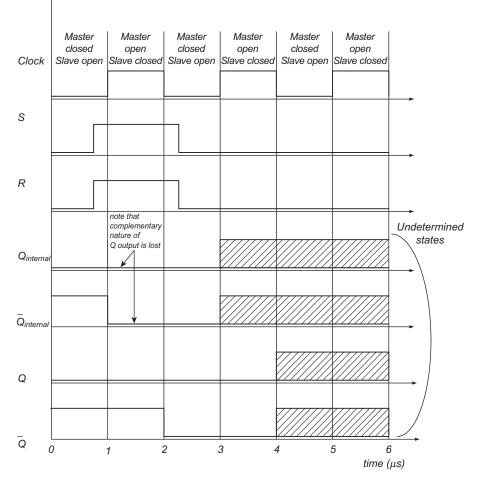

- 9.2.3 Master/Slave SR-Flip-Flop / 561

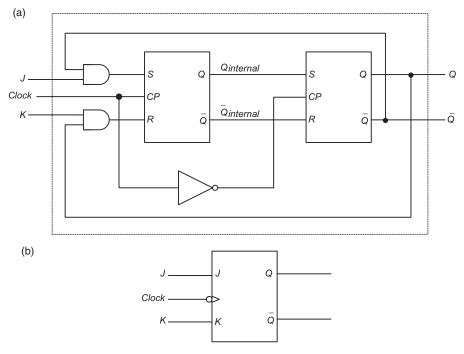

- 9.2.4 Master/Slave JK Flip-Flop / 565

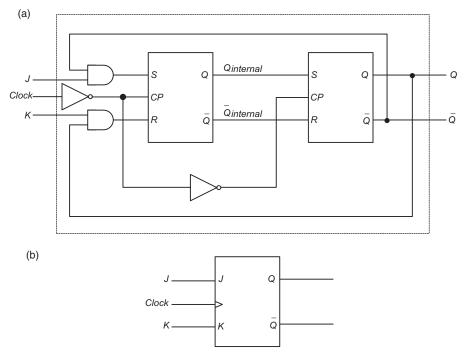

- 9.2.5 Master/Slave T and D Type Flip-Flops / 568

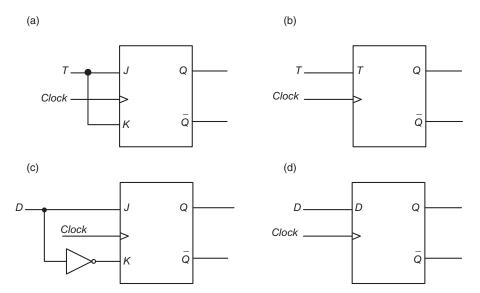

- 9.3 Timing Characteristics of Sequential Elements / 571

- 9.3.1 Timing of Flip-Flops with Additional Set and Reset Control Inputs / 571

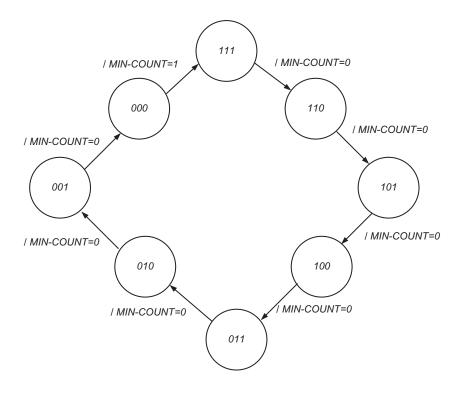

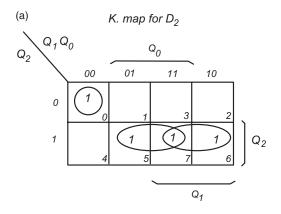

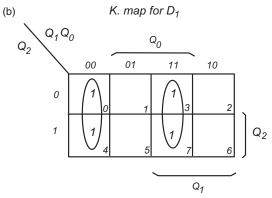

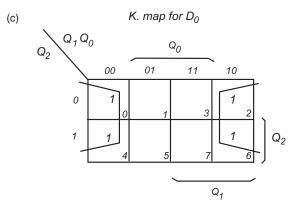

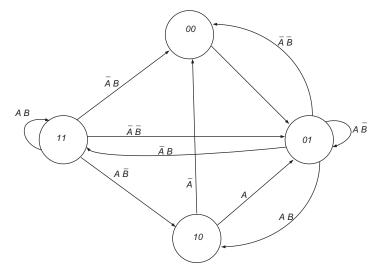

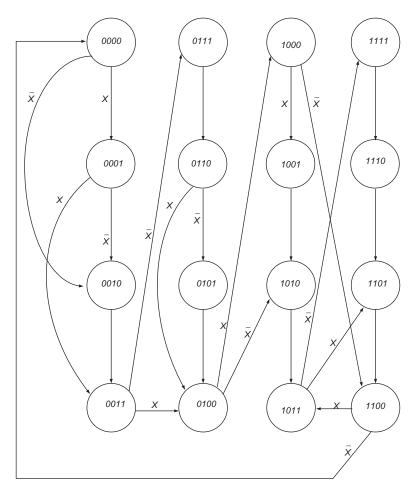

- 9.4 Simple State Machines / 574

- 9.4.1 SR Flip-Flop Excitation Table / 578

- 9.4.2 T Flip-Flop Excitation Table / 580

- 9.4.3 *D* Flip-Flop Excitation Table / 581

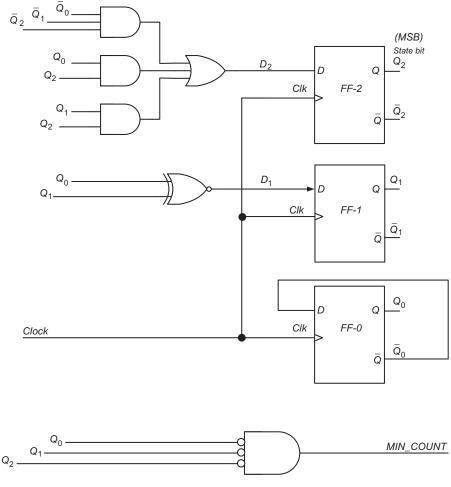

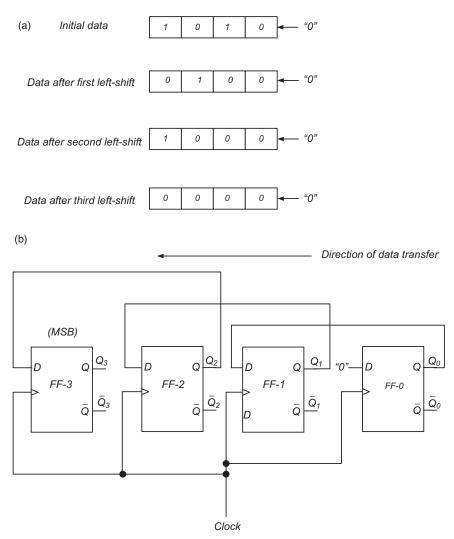

- 9.5 Synchronous State Machines General Considerations / 592

- 9.5.1 Synchronous State Machine Design Guidelines / 592

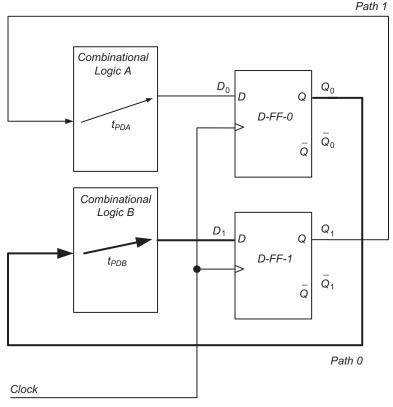

- 9.5.2 Timing Considerations: Long and Short Path Analyses / 595

9.6 Summary / 599

Further Reading / 600 Problems / 600

# 10 A Simple CPU Design

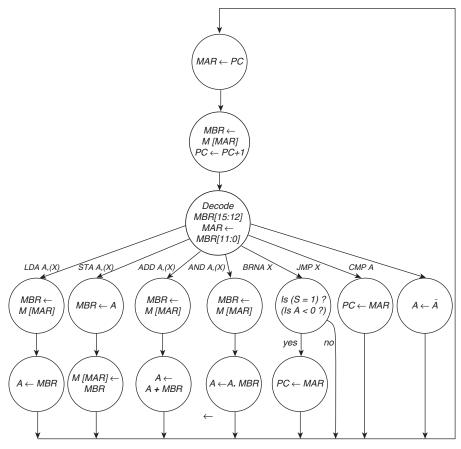

- 10.1 Our Simple CPU Instruction Set / 603

- 10.2 Instruction Set Details: Register Transfer Language (RTL) / 605

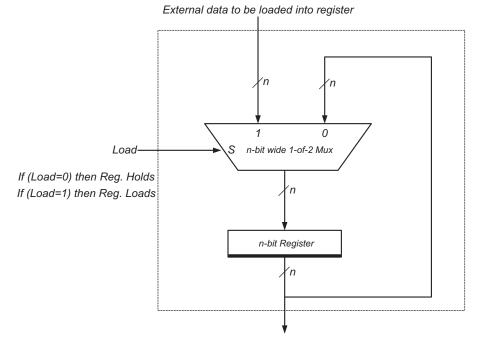

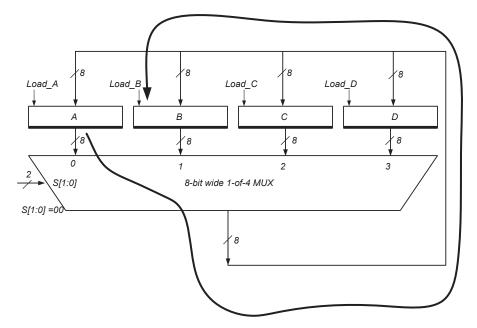

- 10.3 Building a Simple CPU: A Bottom-Up Approach / 607

- 10.3.1 The Registers / 607

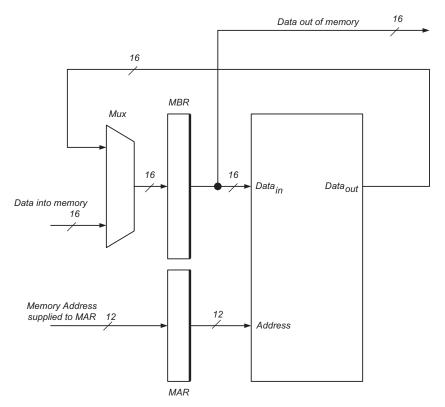

- 10.3.2 The Memory Access Path or Memory Interface / 610

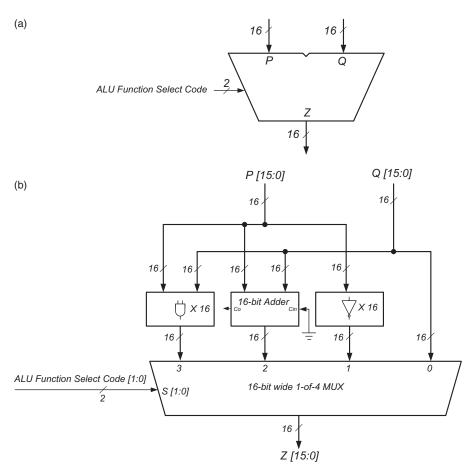

- 10.3.3 The Arithmetic and Logic Unit (ALU) / 611

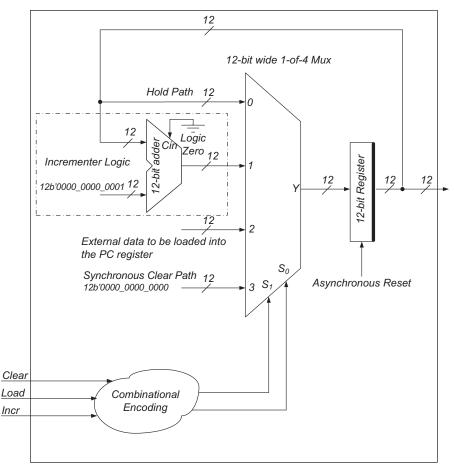

- 10.3.4 The Program Counter (PC) / 611

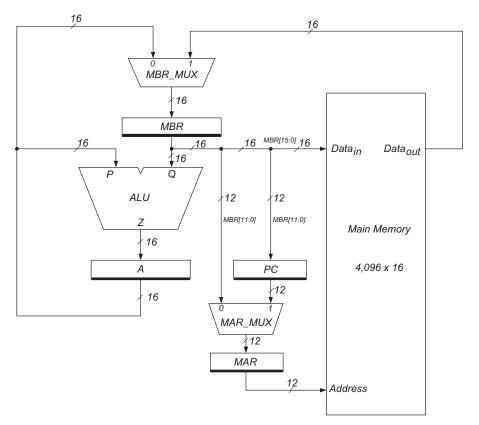

- 10.4 Data Path Architecture: Putting the Logic Blocks Together / 615

- 10.4.1 Data Path: *LDA* Instruction Fetch, Decode and Execution RTL / 615

- 10.4.2 All Other Instructions: Fetch, Decode and Execution: RTL / 618

#### 550

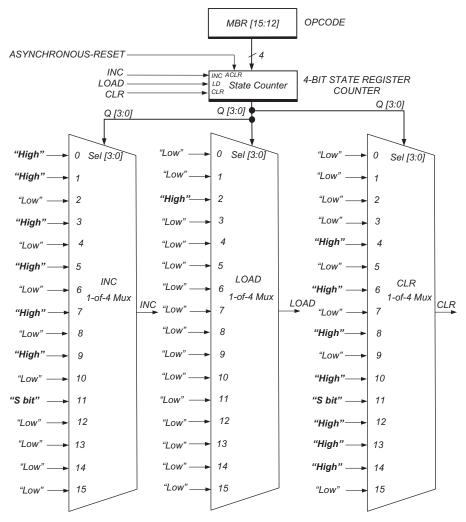

10.5 The Simple CPU Controller / 620

10.5.1 State Assignments and Controller Implementation / 622

- 10.6 CPU Timing Requirements / 626

- 10.7 Other System Pieces: Clock, Reset and Power Decoupling / 628

- 10.7.1 Clock / 628

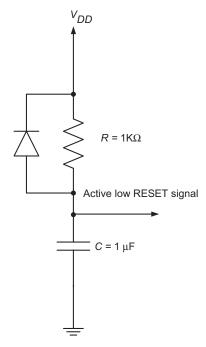

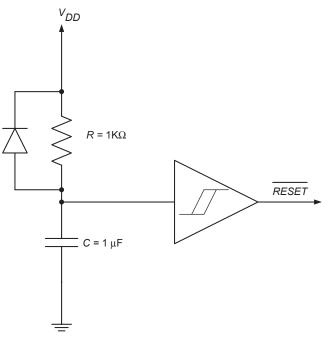

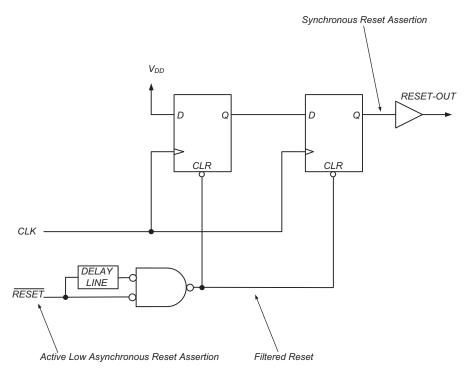

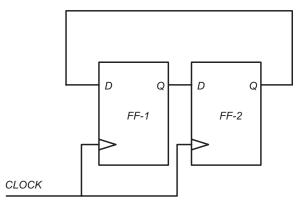

- 10.7.2 Reset / 628

- 10.7.3 Power Decoupling / 631

- 10.8 Summary / 633

Further Reading / 633

Problems / 633

Index

# PREFACE

For several years I taught an introductory analog and digital essentials course for the University of California Extensions at Berkeley and Santa Cruz. Teaching there motivated me to put together, under one cover, a textbook that contains fundamentals of electrical, electronics, analog, and digital circuits. That is the reason for the word "essentials" in the title. There are not that many books in the market that try to accomplish this task in about 600 pages.

The book is divided into 10 chapters. It is useful for surveys of electrical and electronics courses, for college students as well as practicing scientists and engineers; it is also useful for introductory circuit courses at the undergraduate level. The book provides many examples from beginning to end. Within the examples, specific components part numbers were avoided to prevent this book from becoming obsolete. The book can be used by students who have some to no previous knowledge of the material, and for graduate-level and working professionals' circuit courses. The prerequisites for using this book are freshman-level calculus and algebra. Nevertheless, the level of math needed is quite light. The book is a gentle introduction to electrical and electronic circuit analysis with many examples.

Physical concepts are emphasized not only with text but also with specially prepared figures that should help the first-time readers study the material.

This book emphasizes problem solving, using different circuit analysis methodologies. These techniques allow readers to understand when one method is more appropriate than another. Ultimately, it is the student who is responsible for adopting the methods that make the most sense. No one thinks exactly in the same way. An example is differentiation and integration. For some people, differentiation is simpler than integration; for others, is the other way around.

Chapter 1 covers the three basic circuit elements: resistors, inductors, and capacitors. Additionally, *ideal* and *real* independent DC current and voltage sources are addressed. Chapter 2 emphasizes AC circuits, as they are applied to the three basic circuit elements. Their *time-domain* and *frequency-domain* behavior is seen throughout examples. A brief refresher on *operations with complex numbers* is embedded in this chapter and not in an appendix for reasons of reading continuity. The concept of power drawn by a circuit and its different types are addressed. The chapter ends with the coverage of dependent

voltage and current sources. Chapter 3 addresses methods to solve circuits; it should be studied with the greatest attention and as many problems with different circuit analysis methods as possible should be solved. From a practical point of view, this is a core chapter to master.

Chapter 4 describes with plenty of detail the behavior of first-order and second-order circuits in the time and frequency domains. Many textbooks do not put as much emphasis on first-order circuits, because they are considered too simple. It has been my experience with students that first-order high-pass filters are particularly more difficult to understand than first-order low-pass filters. Chapter 5 is dedicated to *operational amplifiers*. Even though op amps consist of to-be-covered electronic components, it is useful to have the reader think with some high level of abstraction. Under some conditions op amps are seen as functional blocks and not as circuits with transistors and resistors. Linear and nonlinear applications with op amps are covered with many examples.

Chapter 6 covers electronic devices. Much information on devices is provided. One can say that entire books have been written just on the electronic components addressed by this chapter. The textbook takes a systematic approach to study the circuits using diodes and transistors, hardly dwelling on device physics. Chapter 7 begins with digital logic. Combinational (and not "combinatorial," as it is sometimes mistakenly called) logic circuits do not have any memory. Logic operations or Boolean algebra is presented, and logic simplification methods such as the Karnaugh map method are illustrated. Chapter 8 deals with more advanced combinational circuits such as multiplexers, decoders, and some arithmetic circuits. A method to produce a very fast arithmetic sum of two operands is covered. Chapter 9 is about state machine design or sequential logic. Sequential logic has memory, unlike combinational logic, and it is the core subject when designing logic circuits that perform useful and complete functions. Chapter 10 describes piece by piece the construction of a simple CPU. The CPU basic functional blocks, such as its instruction set, the data path architecture, its memory interface, and the control logic, are described step by step. Some insights into capacitor power decoupling and reliable reset circuits are also presented. The problems at the end of this chapter provide tremendous insight into the CPU functionality. This chapter can be thought as a very light introduction to a computer architecture course.

Writing this book has been a very rewarding experience for me. This book should be very useful to college students and those professionals who need an essential analog and digital source.

I want to thank my wife Ruty and daughter Denise for their infinite patience and support while I was preparing the manuscript.

Eduardo (Ed) M. Lipiansky

# ABOUT THE AUTHOR

Eduardo (Ed) Lipiansky received his undergraduate degree in electrical engineering from the National University of La Plata, Argentina (UNLP). He performed graduate studies at the University of California, Berkeley, obtaining a master of science degree in electrical engineering. Mr. Lipiansky has 25 years of industry experience, having worked at Varian Associates, Tandem Computer, Sun Microsystems, Cisco Systems, and Google.

He is author or co-author of six patents; four have been issued by the U.S. Patent Office, and two more have been submitted. Mr. Lipiansky's key interests are maintenance and diagnostics subsystems for servers, networking line cards, analog and digital electronic design for medical instrumentation and computers, and power engineering. Ed wrote *Embedded Systems Hardware for Software Engineers* (2011), which deals with more advanced hardware concepts and can be used as an add-on to the present textbook. For about 20 years, he taught a variety of courses such as circuit analysis, digital design, operational amplifiers, and microprocessor interfacing techniques at the University of California Berkeley and Santa Cruz Extensions. Mr. Lipiansky lives with his family in the San Francisco Bay area in northern California.

# 1

# FROM THE BOTTOM UP: VOLTAGES, CURRENTS, AND ELECTRICAL COMPONENTS

# 1.1 AN INTRODUCTION TO ELECTRIC CHARGES AND ATOMS

The ancient Greek philosophers knew that when amber was rubbed against wool, it would attract lightweight particles of other materials like small pieces of paper or lint. Also, little pieces of paper get attracted to a plastic comb when the weather is dry. These experiments reveal that electric charge exists. If we rub one end of a glass rod with silk, charges will move toward that end of the rod. Rubbing a second glass rod in the same fashion and placing it close to the rubbed end of the first glass rod will exhibit a repelling force between the rods. However, when a plastic rod is rubbed with fur and it is placed near the rubbed glass rod, the plastic and the glass rods will attract each other. These simple experiments prove the existence of two different types of charge. Benjamin Franklin\* called one of them positive and the other one negative. Most charge in an everyday object appears to be nonexistent because there is an equal amount of positive and negative charge. The word *electron* is derived from the Greek word "elektron," which means amber. From the above experiments the following can be asserted:

Charges of the same sign repel each other, while charges of opposite signs attract each other.

\* Benjamin Franklin: American scientist, writer, and politician (1706–1790).

*Electrical, Electronics, and Digital Hardware Essentials for Scientists and Engineers*, First Edition. Ed Lipiansky.

<sup>@</sup> 2013 The Institute of Electrical and Electronics Engineers, Inc. Published 2013 by John Wiley & Sons, Inc.

All matter is made of the basic elements, those elements listed in the periodic table of chemical elements. As of 2006, there are 117 elements of which 94 are found naturally on the Earth. The remaining elements are synthesized in particle accelerators. Loosely speaking, all matter is made of some combination of atoms, where an atom is the basic unit of matter. An atom contains a nucleus surrounded by a cloud of electrons. The nucleus consists of positively charged protons and electrically neutral neutrons. Neutrons have no electrical charge, but their mass is about 1800 times the mass of electrons. The electronic cloud around the nucleus is negatively charged, and an atom with an equal number of protons and electrons is said to be neutral. Protons have a positive charge and a mass about 1800 times larger than the mass of electrons. Different element atoms are different from each other because of the different numbers and arrangements of the atom's basic particles: electrons, neutrons, and protons. Traditionally in elementary physics and chemistry, the atom was compared to our planetary system. The nucleus is in the center of the atom, like the sun is the center of our system. The electrons are like the planets, orbiting around the sun. Electrons occupy different layers or shells that are at different distances away from nucleus. The outermost shell is referred to as the valence shell. The valence shell electrons determine the electrical characteristics of an atom.

Table 1.1 presents the elementary charge, which has a positive sign for a proton and a negative sign for an electron. Values for the mass of the electron, proton, and neutron are also tabulated.

From an electrical point of view, there are four main types of materials: conductors, nonconductors or insulators, semiconductors, and superconductors. The fourth type of material, the superconductor, is beyond the scope of this book.

Conductors are materials through which charge can move quite freely, such as copper or gold. Insulators are materials through which charge cannot move freely such as plastic or rubber. Semiconductors are materials that have an intermediate behavior between that of conductors and insulators. More on semiconductors will be covered in Chapter 6.

|                               | Abbreviation                                       | Mass Value                                                                                             | Units          | Relative Mass<br>to the Electron<br>Mass (m <sub>e</sub> ) | Charge in C<br>(coulombs)                                                          |

|-------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------|------------------------------------------------------------|------------------------------------------------------------------------------------|

| Elementary<br>charge          | e                                                  |                                                                                                        |                |                                                            | $1.602 \times 10^{-19}$                                                            |

| Electron<br>Proton<br>Neutron | m <sub>e</sub><br>m <sub>p</sub><br>m <sub>n</sub> | $\begin{array}{c} 9.109 \times 10^{-31} \\ 1.673 \times 10^{-27} \\ 1.675 \times 10^{-27} \end{array}$ | kg<br>kg<br>kg | 1<br>1800 (approx.)<br>1800 (approx.)                      | $\begin{array}{c} -1.602\times 10^{-19} \\ +1.602\times 10^{-19} \\ 0 \end{array}$ |

#### Table 1.1 Some atomic constants

# 1.2 ELECTRIC DC VOLTAGE AND CURRENT SOURCES

Two types of independent sources are available, voltage and current sources. A source is said to be independent when either its nominal voltage or current is constant and does not depend on any other voltage or current present in a circuit. In a later section, we will cover the concept of dependent sources. The ideal voltage source produces a constant voltage across its terminals, regardless of the current that is being drawn from it by a load. Conversely, an ideal current source produces a constant current to a load connected across its terminals regardless of the voltage that is developed across the load. Let us now address the concepts of electric current and voltage.

#### 1.2.1 Electric Current and Voltage

A net flow of electric charges through a circuit establishes an electric current. Note that conductors in isolation, such as a piece of copper not connected to anything else, contain free electrons or conduction electrons that randomly move. Such electrons do not constitute an electric current since in any cross section of the copper wire, the net amount of charge moved through the wire is zero. The emphasis here is on the word "net"; the net flow of charge constitutes an electric current. Current is defined as

$$i(t) = \frac{dq}{dt},\tag{1.1}$$

where i(t) represents electric current as a function of time and dq/dt is the net variation of charge with respect to time. Traditionally, electric current was referred to as current intensity. In most places, the term "current" is used, which is a short form of current intensity. The letter *i* denotes current, while dq differential of charge over dt differential of time refers to the net passage of charge during a time interval through a cross section of the conductor. On the other hand, a voltage can be interpreted as the "pressure" that needs to be asserted in a circuit in order to cause electric current to flow.

Throughout the book, we will assume that a conductor or a wire is ideal and will have zero resistance to the flow of current, unless it is stated otherwise. The unit of resistance is the ohm ( $\Omega$ ). Electric components that have greater than 0  $\Omega$  resistance are called resistors. The current that flows through a resistor times the resistance value equals the voltage drop that is produced across such resistor. Conventional current in a resistor flows from higher voltages or potentials to lower voltages or potentials.

Figure 1.1 depicts a resistor, a current flowing through it, and the voltage with its polarities that is produced across the resistor. The current through the resistor times its resistance value equals the voltage obtained across the resistor terminals. Mathematically,

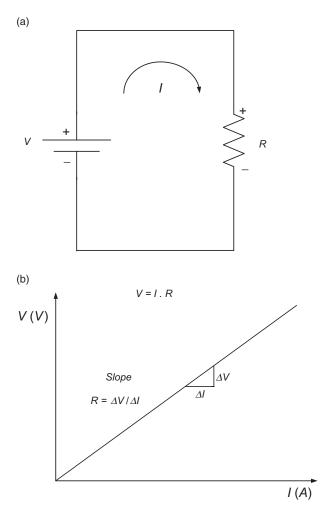

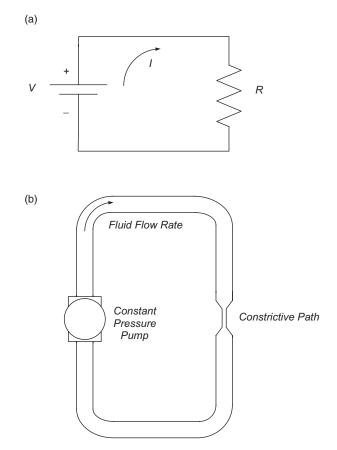

Figure 1.1 Ohm's Law: (a) DC voltage source powering a resistor; (b) linear variation of resistor voltage versus current.

$$V = IR. \tag{1.2}$$

Equation (1.2) states the voltage across a resistor is proportional to the current flowing through it. The constant of proportionality is the resistor value R. Equation (1.2) is *Ohm's Law*. In Figure 1.1a, a resistor powered by a DC source is shown; Figure 1.1b depicts the variation of resistor voltage versus current variation. The slope of the line V = I R is the resistance value. Ohm's law in Equation (1.2) denotes a linear variation of the voltage across the resistor versus the current flowing through it.

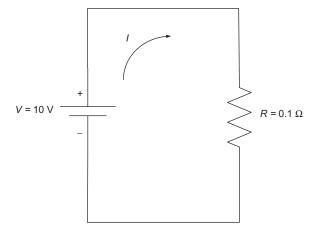

**Example 1.1** Given a 10-V DC voltage source that is connected across a  $0.1 \Omega$  resistor, calculate for the current that will flow through the resistor.

#### Solution to Example 1.1

From Equation (1.2),

$$V = IR.$$

And since

$$I = V/R,$$

$I = 10 \text{ V}/0.1 \Omega = 100 \text{ A}.$

#### 1.2.2 DC Voltage and Current Sources

We all have some familiarity with electricity and electronics. We have seen flashlights, batteries, battery chargers, lightbulbs, portable electronic devices, and electrical and electronic appliances such as toasters and microwave ovens.

Flashlight batteries, toy batteries, and automobile batteries are all examples of DC voltage sources. DC stands for direct current, and what this means is that the current polarity that the source supplies does not change; that is, the current always flows in the same direction through the load.

An idealization of the DC voltage source is that its DC voltage is always constant with respect to time and independent of the amount of current that it may supply. In practical devices such as batteries, that voltage is "somewhat" constant, and it varies based on factors such as temperature, environmental factors, mechanical vibration, age of the battery, and use of the battery. However, unless we state otherwise, the first-order approximation of a battery is that of a constant or DC voltage source.

Current sources are as also idealized like DC voltage sources. An everyday example of a current source is a battery charger. A battery charger provides a constant current to recharge a battery with rechargeable chemistry. Note that not all batteries are rechargeable. No attempt should be made to recharge batteries that are not of the rechargeable kind, since this causes a hazard to the user. Another example of a current source is that of a transistor hooked up to operate as a current source.

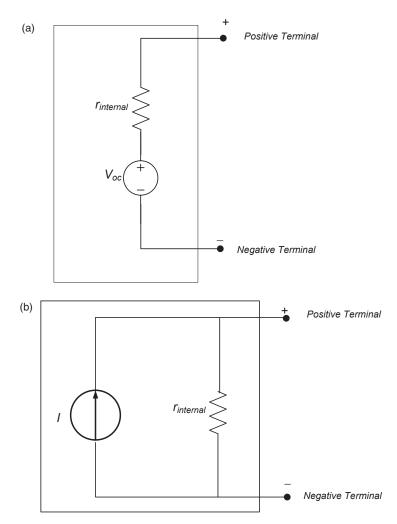

A DC voltage source may not always be a chemical battery. It may, for example, be built with electronic components that behave largely like a DC source. An example of this is a DC power supply (see Figure 1.2).

When a DC voltage source is not being used, it must be stored in an opencircuit condition (refer to Figure 1.3a). That means nothing is connected to the positive and the negative electrical terminals. Upon connecting an element

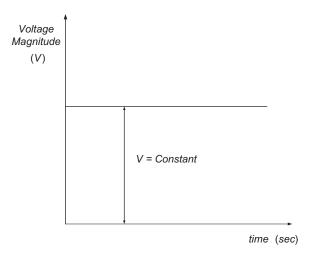

Figure 1.2 Mathematical representation of a DC voltage source as a function of time.

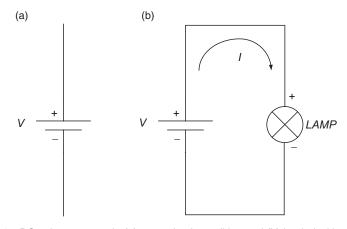

Figure 1.3 DC voltage source in (a) open-circuit condition and (b) loaded with a lightbulb.

such as a lightbulb across the voltage source terminals, a current flows through the circuit that was just established. Figure 1.3b shows a DC voltage source, which in this case is actually a battery connected with wires to a lightbulb.

The battery exerts "pressure" into the circuit by displacing charges. The net flow of charge with respect to time is called an electric current. Physically, an electric current consists of a net flow of electrons. That is, the electronic current leaves the negative terminal of the source, goes through the lightbulb, and returns back into the positive terminal of the source. However, the traditional interpretation is that current flows from the positive terminal of the source through the lightbulb and back into the negative terminal of the source. Throughout this book, the traditional or conventional current flow will be used. This is what most of the electrical engineering literature assumes. The lightbulb depicted in Figure 1.3 is in effect a resistor. The voltage applied and the resistance of the lightbulb determines the current that will be present in the closed circuit. Resistance is the opposition that a resistor presents to the net flow of current. In other words, the DC voltage source voltage is basically constant, regardless of the amount of current that is being drawn form the source. Naturally, this is an idealization of what a DC voltage source is, or what we would like it to be. Real voltage sources do not behave that way; their output voltage is quite constant as long as the current flowing through the circuit is considerably less than what the total current pumping capability of the source is. More details on this topic will be provided when the internal resistance of a source is addressed, later in this chapter.

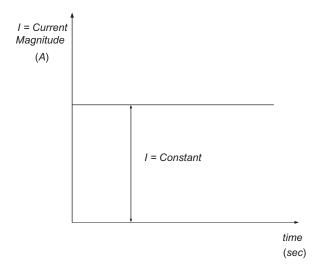

DC current sources, on the other hand, produce a constant current when a lightbulb or a resistive element establishes a closed loop circuit and the voltage across it will depend strictly on the resistive value placed across the current source and the current value. Just like with the DC voltage source, the DC current source is an idealization. Real current sources can provide a constant current as long as the voltage across the resistor does not produce an excessive voltage. Figure 1.4 depicts a constant DC current as a function of time.

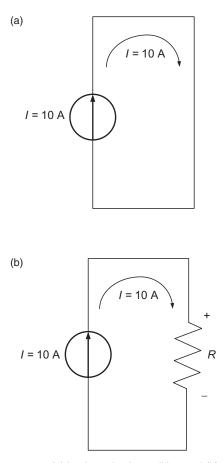

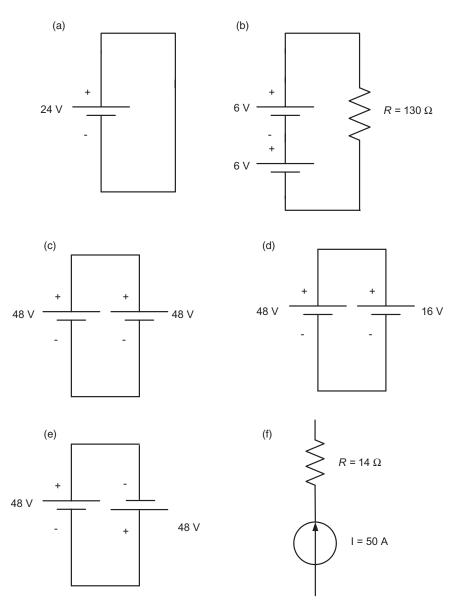

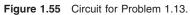

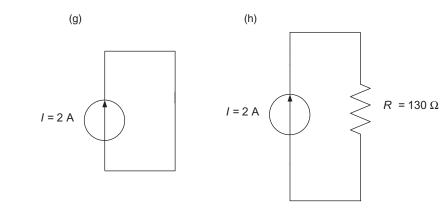

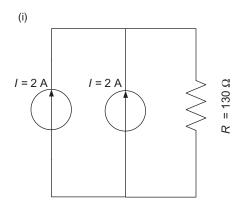

Figure 1.5a depicts a DC current source in a standby condition, that is, with its terminals short-circuited to each other. A current source should not be left open-circuited because the voltage that gets developed across its terminals would grow without bound. A real or physical current source would self-destruct or become severely damaged if its terminals were left in an open-circuit condition. Figure 1.5b depicts a DC current source with a resistor connected across its terminals. In Figure 1.5a,b, both states of the current source are benign states or normal states. In both cases, the current supplied by the current source is identical.

Figure 1.4 Mathematical representation of a DC current source as a function of time.

Figure 1.5 DC current source (a) in short-circuit condition and (b) loaded with a resistor.

The ideal current source with a resistive element in a closed circuit (Fig. 1.5) provides a constant current, and the voltage across the terminals of the current source depends on the value of the resistor across the current source times the current supplied by the source. Changes of the resistor values across the current source will produce proportional changes of the voltage across the current source. Note that the resistor (or load) across a current source produces higher voltages as the load resistor increases in value, because the current remains constant. For the case that the load resistor is very large, the voltage across the current sources will be very large. When current sources are in open-circuit condition, the voltage across its terminal grows without bound. Real current source must always be short-circuited when not in use (refer to Figure 1.5a). The voltage across a shorted current source is zero because the wire across the current source has zero resistance. However, the current

supplied by a shorted current source is its nominal value of current. For example, a 10 A current source must be shorted when not supplying any current to a load. This current has a value of 10 A. When the current source is loaded by a resistor (Fig. 1.5b), the 10 A times the value of the resistor determines the voltage across the resistor. Note that since the current supplied by a current source remains constant as the resistor becomes larger in value, the voltage becomes larger as well.

In the extreme case if the value of the resistor is an open circuit, or infinitely many ohms, the voltage developed across the ideal current source is infinite.

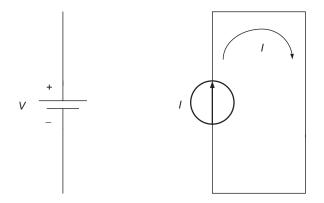

In mathematical terms, an open-circuit current source produces an indetermination. The voltage source on the other hand must never be short-circuited because if we did, the current that the voltage source would supply to the short circuit is infinitely large, that is, also an indetermination (unbounded current). A real or physical short-circuited voltage source would also self-destruct rather quickly. Figure 1.6 depicts an open-circuit voltage source and a shortcircuited current source. These are the benign or idle states for the voltage and the current sources. Figure 1.7 depicts ill-defined or undesirable states for a voltage and current source, respectively. A voltage source cannot survive short-circuited conditions, like a current source cannot survive an opencircuited condition. If they did, their reliability would be severely affected after that. Finally, let us be 100% clear about it: Figure 1.7 depicts circuits that fall under the "do-not-do-this-at-home-or-at-work" category.

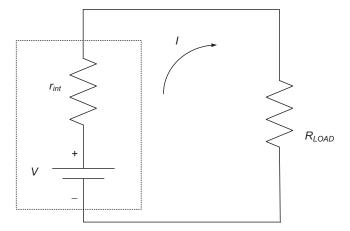

## 1.2.3 Sources Internal Resistance

No real voltage source has a capacity of generating an infinite current upon being short-circuited. Similarly, no real current source can produce an infinite voltage across its terminals if left open-circuited. Real sources have their

(a) Open-Circuited Voltage Source(b) Short-Circuited Current SourceFigure 1.6 Sources benign states: (a) for a voltage source; (b) for a current source.

Figure 1.7 Ill-defined (hazardous) states: (a) for a voltage source; (b) for a current source.

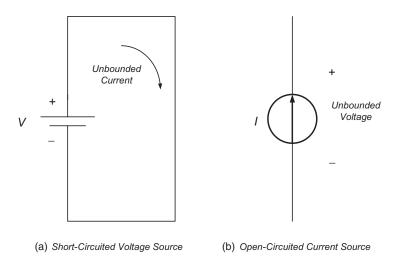

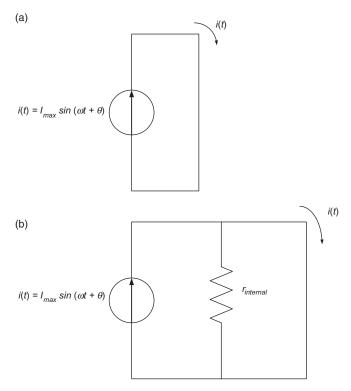

physical limitations. To account for these limitations, a voltage source is modeled with a current-limiting resistor in series, and a current source is modeled with a voltage-limiting resistor in parallel with the current source. Figure 1.8a,b depicts models of physical voltage and current sources with their respective series and parallel resistors. The series resistance in the voltage source represents the current limitation characteristic that a voltage source has. Note that if the voltage source of Figure 1.8a is 10 V and has an internal resistance of 1  $\Omega$ , the total short-circuit current capability of this source is its open-circuit voltage V divided by its internal resistance  $r_{internal}$ .

$$I_{short-circuit} = V_{constant\_source\_open-circuit\_voltage} / r_{internal}.$$

(1.3)

In particular for the example stated above, this short-circuit current is  $10 \text{ V}/1 \Omega = 1 \text{ A}$ . The internal resistance distinguishes a real voltage source from an ideal voltage source, which is assumed to have an infinite capability of generating current. Its internal resistance limits the current that can be drawn from a real or physical voltage source. This limitation is stated by Equation (1.3). When referring to Figure 1.8a, it is important to say that the internal resistance is an integral part of the real DC source, and the real DC source is modeled by an ideal DC source in series with the source internal resistance in series.

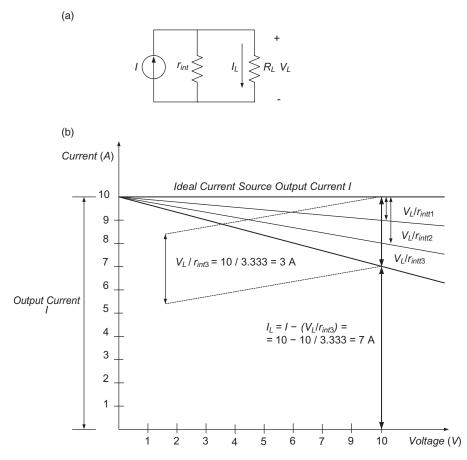

Similarly for the DC current source (refer to Figure 1.8b), the paralleled resistor with the current source represents or models the finite voltagegenerating capability that an open-circuited current source has. We can write the current voltage relationship for the real current source modeled in Figure 1.8b as follows:

Figure 1.8 Modeling of real sources: (a) voltage source; (b) current source.

$$I_{constant-source-current} = V_{current\ source} / r_{internal}$$

(1.4)

Note that Equations (1.3) and (1.4) are governed by Ohm's law.

So, if we have a 10 A current source with its internal resistance of 10  $\Omega$ , using Equation (1.4), we determine that the maximum output voltage that this current source produces is 10 A·10  $\Omega$  = 100 V. Note that the open-circuit voltage of a real current source cannot exceed the limits imposed by Equation (1.4). The open-circuited ideal current source would produce a very large voltage across its terminals.

# 1.3 ELECTRIC COMPONENTS: RESISTORS, INDUCTORS, AND CAPACITORS

There are three fundamental circuit elements in electric circuits. These are resistors, inductors, and capacitors. From a circuit analysis point of view, we are interested in the voltage versus current as well as the current versus voltage relationships that exist for every one of these circuit elements. All three components, resistors, inductors, and capacitors, are said to be passive elements to differentiate them from active elements. Passive components do not have *gain*, while active components do. Active components will be covered in Chapters 5 and 6.

## 1.3.1 Resistors

The resistor is an electric component usually made with some of the resistive materials such as carbon, metal film, or paste. Other materials are used, but the ones mentioned are the most common. Resistor technologies vary, and the most common are metal thin film and thick film, metal strip, wire wound, foil, and composition.

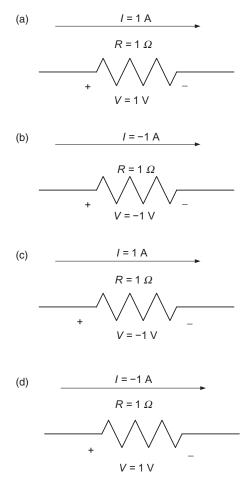

A resistor opposes the flow of electric current. As the current flows through the resistor, a voltage is developed across such resistor. The voltage drop across the resistor follows Ohm's law, which states that the voltage across the resistor equals the current flowing through it, times the resistance value. Figure 1.9 shows the circuit symbol that represents a resistor. Figure 1.9 depicts a positive current and a positive voltage on the resistor (a), a negative current and a negative voltage (b), a positive current and a negative voltage (c), and a negative current and a positive voltage (d).

The current voltage and voltage current relationship on a resistor is given by Ohm's law, Equation (1.2), which we repeat for the reader's convenience:

$$V = IR = f(I),$$

where f(I) is a linear function of I equal to I R.

And conversely,

$$I = V/R \tag{1.5}$$

$$I = g(V), \tag{1.6}$$

where g(V) is a linear function of V and equals V/R. The term 1/R, the inverse of the resistance, is called the conductance G. Using G in Equation (1.6), it becomes

$$I = GV. \tag{1.7}$$

Figure 1.9 Circuit symbol of a resistor showing current and voltage polarities.

In Equation (1.5), V is the voltage across the resistor in volts, I is the current flowing through the resistor in amperes, and R is the resistor value in ohms. In Equation (1.7), I is in amperes, G in siemens (or mho), and V in volts.

The unit of resistance is the  $\Omega$ , and *R* represents resistance. The inverse of the resistance (1/R) in DC circuit analysis is called conductance (G), and it is measured in siemens (S), where  $1 \text{ S} = \Omega^{-1}$ , formerly also referred to as a mho (ohm spelled backward). Common values of resistors range from very small fractions of an ohm up to several megaohms  $(1 \text{ M}\Omega = 10^6 \Omega)$ . This is a good point to introduce the most common prefixes used in the SI system of units.

Table 1.2 shows the internationally accepted power of 10 factors, their names, and their symbols. The most commonly used prefixes in electrical engineering and computer sciences range from  $10^{24}$  (yotta) down to  $10^{-24}$  (yocto). Within such range, some prefixes are more common than others.

|                 |       |        | -                |        |        |

|-----------------|-------|--------|------------------|--------|--------|

| Factor          | Name  | Symbol | Factor           | Name   | Symbol |

| 1024            | yotta | Y      | 10 <sup>-1</sup> | deci   | d      |

| $10^{21}$       | zetta | Z      | 10-2             | centi  | с      |

| $10^{18}$       | exa   | E      | $10^{-3}$        | milli  | m      |

| 1015            | peta  | Р      | $10^{-6}$        | micro  | μ      |

| 1012            | tera  | Т      | $10^{-9}$        | nano   | n      |

| $10^{9}$        | giga  | G      | $10^{-12}$       | pico   | р      |

| $10^{6}$        | mega  | Μ      | $10^{-15}$       | fempto | f      |

| $10^{3}$        | kilo  | k      | $10^{-18}$       | atto   | а      |

| 10 <sup>2</sup> | hecto | h      | $10^{-21}$       | zepto  | Z      |

| 10 <sup>1</sup> | deka  | da     | $10^{-24}$       | yocto  | У      |

Table 1.2 Prefixes used with the International System of Units (SI)

When selecting a resistor from a data sheet, there are key parameters that cannot be ignored to make a good component selection. Such resistor parameters are

- (a) Resistance value in  $\Omega$

- (b) Resistor power rating in W

- (c) Resistor tolerance in  $\pm\%$

- (d) Temperature coefficient of resistance in ±ppm/°C, which stands for parts per million per Celsius degree or 10<sup>-6</sup>/°C.

Other defined parameters that characterize resistors may vary a little bit from manufacturer to manufacturer. For a more complete list of precision resistor parameters, access the first reference of the Further Reading section at the end of the chapter.

Resistance values range from a small fraction of an ohm all the way up to a few M $\Omega$  (1 M = 10<sup>6</sup>  $\Omega$ ). The electronic industry standardized the resistor values based on the E-series according to Table 1.3. For example, for 1% tolerance resistors, 96 values per decade are chosen in an equally spaced basis. The resistor values follow the following geometric progression:

$$N = 10^{n-1/k}.$$

(1.8)

In Equation (1.8), N is the nominal resistance value at position n, and k is 96 for the E96 series. For example, for series E96, using Equation (1.8) for n = 1, 2, 3..., the progression of resistance values becomes

$$1.00, 1.02, 1.05 \dots$$

(1.9)

The resistor values of (1.9) have been rounded.

In Equation (1.8), k refers to a decade of resistors values such as 1  $\Omega$ , 10  $\Omega$ , 100  $\Omega$ , and so on, while "n" is the series number. For example, for the E96

| Series | Tolerance                      | Comments                                                                    |

|--------|--------------------------------|-----------------------------------------------------------------------------|

| E3     | 50%                            | 3 steps per decade. No longer used.                                         |

| E6     | 20%                            | 6 steps per decade. No longer used.                                         |

| E12    | 10%                            | 12 steps per decade. No longer used.                                        |

| E24    | 5%                             | 24 steps per decade. Not commonly used.                                     |

| E48    | 2%                             | 48 steps per decade. Commonly used.                                         |

| E96    | 1%                             | 96 steps per decade. Commonly used.                                         |

| E192   | 0.5%, 0.25%, 0.1%<br>or higher | 192 steps per decade. Commonly used in high accuracy and precision designs. |

Table 1.3 Common Values of Resistor Tolerances

series, there are 96 (i.e., the reason for Equation (1.8) is to obtain the same number of steps within each decade of resistor values). Ultimately, the goal is to limit the number of resistor values or the inventory that manufacturers and distributors would have to have to handle otherwise.

For example for the E48 series of standardized resistor values, using Equation (1.8), the first three values are 100, 105, and 110  $\Omega$ . E48 is the ±2% tolerance series. Note that each of the three values mentioned plus and minus their 2% tolerance are

98

$$\Omega < 100 \Omega < 102 \Omega.$$

(1.10)

$$102.9 \,\Omega < 105 \,\Omega < 107.1 \,\Omega. \tag{1.11}$$

$$107.8 \,\Omega < 110 \,\Omega < 112.2 \,\Omega.$$

(1.12)

It is easy to see that none of the values including their tolerance overlap. The same applies to all values for all ohmic decades of all other series. The tolerance of a resistor is the deviation in percent that the actual value of a resistor can deviate from its nominal value at room temperature. Room temperature for some manufacturers is defined as 20°C, for others is 25°C. However, when the resistor is in use, the temperature surrounding the resistor will cause its nominal value to increase or decrease. Resistor manufacturers specify the maximum/minimum resistance variation of their components for a certain temperature span.

**Example 1.2** Assume that a 1 M $\Omega$  resistor has a ±100 ppm/°C temperature coefficient within an operating temperature range of -25°C to +125°C. Further assume that the resistor is exactly 1 M $\Omega$  at 20°C (i.e., assume the resistor has zero tolerance ±0%):

- (a) What will the resistor value range be for the above temperature range?

- (b) What will the resistor value range be if in addition to the temperature range, a  $\pm 1\%$  tolerance is assumed?

## Solution to Example 1.2a

When the resistor operates at +125°C,

$$1 M\Omega \times [+100 \text{ ppm/°C}] \times (125^{\circ}\text{C} - 20^{\circ}\text{C}) = \pm 1 M\Omega \times 100 \times 10^{-6} \times 105$$

= ±10,500 \Omega = ±1.05% of the resistor nominal value 125°C. (1.13)

When the resistor operates at  $-25^{\circ}$ C,

$$1 \operatorname{M}\Omega \times [-100 \text{ ppm/°C}] \times (-25^{\circ}\text{C} - 20^{\circ}\text{C}) = \pm 1 \operatorname{M}\Omega \times 100 \times 10^{-6} \times 45$$

= ±4500 \Omega = ±0.45% of the resistor nominal value -25°C. (1.14)

From Equations (1.13) and (1.14), we conclude that for a  $-25^{\circ}$ C to  $+125^{\circ}$ C temperature range, the resistor varies from -0.45% up to 1.05% from its nominal value.

## Solution to Example 1.2b

In Example 1.2a, the resistance variation was just due to the resistor temperature coefficient over the operating temperature range. If in addition the resistor nominal value will be its value  $\pm$ tolerance (%). That means that if the resistor has a  $\pm 2\%$  tolerance, its value can vary between -2% (or 980,000  $\Omega$ ) to +2% (or 1,020,000  $\Omega$ ); a total of 1.05% due to its temperature coefficient operating in the  $-25^{\circ}$ C to  $+125^{\circ}$ C temperature range. Thus, at the high end the resistor value can be +1% due to tolerance and +1.05% operating at  $+125^{\circ}$ C; that is a total of 2.05%. At the low end, the resistor value can be -1% due to tolerance and -0.45% operating at  $-25^{\circ}$ C, that is, a total of -1.45% from its nominal value.

*Resistor Tolerances:* The most commonly used resistor tolerances for electrical and electronic applications are  $\pm 1\%$  and  $\pm 2\%$ . Many years ago,  $\pm 5\%$ ,  $\pm 10\%$ , and  $\pm 20\%$  were commonly used. When dealing with high precision analog electronics,  $\pm 0.1\%$  tolerance is available. When higher precision is required, metal foil resistors and ultrahigh precision metal film resistors are available. Metal foil resistor tolerances of up to  $\pm 0.005\%$  tolerance are available, and special metal film resistors of up to  $\pm 0.01\%$  are also available.

#### Example 1.3 Resistor Value, Tolerance, and Power Rating Selection

So let us assume that we need to select a resistor R to establish a constant current of 100 mA. The resistor will have 12 V DC ±120 mV applied across its terminals. Assume that the DC source and resistor R will always operate at 20°C and no temperature changes will occur. Determine (1) a reasonable resistor value, (2) its tolerance, and (3) its power rating that can keep the load current at 100 mA ±2% under all voltage variations and resistor variations due to its tolerance.

#### Solution to Example 1.3

If the voltage (V) were exactly 12 V without any variations and the resistor were exactly 120  $\Omega$ , the current would be, by virtue of Equation (1.2),

$$I = 12 \text{ V}/120 \ \Omega = 100 \text{ mA}. \tag{1.15}$$

The statement that the resistor will always operate at 20°C is equivalent to saying that its temperature coefficient is zero or that there are no resistor variations due to temperature changes.

Let us start adding the real requirements to the problem. We are told that the voltage can vary  $\pm 120 \text{ mV}$  or  $\pm 1\%$  from its nominal value of V = 12 V. Thus,

$$11.88 V < V < 12.12 V. \tag{1.16}$$

If we assume that we have a perfect resistor of  $120 \Omega$  with a 0% tolerance, then

which leads to

99 mA

$$\Omega$$

< I < 101 mA. (1.18)

From Equation (1.16) we can state that having a  $\pm 120 \text{ mV}$  voltage variation and a perfect resistor of 120  $\Omega$ , the current *I* will be bounded between 99 mA and 101 mA, or 100 mA  $\pm 1\%$ .

Now let us introduce the concept that the resistor R is not perfect, and let us assume that it has a tolerance of  $\pm 1\%$ .

Then the resistor value will range from

$$118.80 \, \Omega < R < 121.20 \, \Omega. \tag{1.19}$$

Using the resistor R range obtained in Equation (1.19) and combining it with all possible variation of the voltage V, it yields

$$V_{\rm max}/R_{\rm max} \tag{1.20}$$

$$V_{\min}/R_{\min} \tag{1.21}$$

$$V_{\max}/R_{\min} \tag{1.22}$$

$$V_{\min}/R_{\max} \tag{1.23}$$

where

$$V_{\text{max}} = V + (1\% \text{ of } V) = 12 \text{ V} + 0.12 \text{ V} = 12.12 \text{ V}.$$

(1.24)

$$V_{\min} = V - (1\% \text{ of } V) = 12 \text{ V} - 0.12 \text{ V} = 11.88 \text{ V}.$$

(1.25)

$$R_{\max} = R + (1\% \text{ of } R) = (120 \ \Omega + 1.2 \ \Omega) = 121.2 \ \Omega. \tag{1.26}$$

$$R_{\min} = R - (1\% \text{ of } R) = (120 \ \Omega - 1.2 \ \Omega) = 118.8 \ \Omega. \tag{1.27}$$

Using Equations (1.24) through (1.27) in Equations (1.20) through (1.23), we obtain

$$V_{\rm max}/R_{\rm max} = 12.12 \,{\rm V}/121.2 \,\Omega = 100.0 \,{\rm mA}.$$

(1.28)

$$V_{\min}/R_{\min} = 11.88 \text{ V}/118.8 \Omega = 100.0 \text{ mA}.$$

(1.29)

$$V_{\rm max}/R_{\rm min} = 12.12 \text{ V}/118.8 \,\Omega = 102.0 \text{ mA}.$$

(1.30)

$$V_{\min}/R_{\max} = 11.88 \text{ V}/121.2 \Omega = 98.0 \text{ mA}.$$

(1.31)

Equations (1.28) through (1.31) provide all the possible extreme variations of current *I*. And from Equations (1.22) and (1.21), it can be seen that current *I* varies approximately  $\pm 2\%$  from its nominal value of 100 mA.

Finally, the power dissipated by resistor *R* will be  $V^2/R$ . To account for voltage and resistor variations, we need to calculate

$$P_1 = V_{\text{max}}^2 / R_{\text{min}} = 1.236 \text{ W} \text{ (maximum)}.$$

(1.32)

$$P_2 = V_{\min}^2 / R_{\max} = 1.164 \text{ W} \text{ (minimum)}.$$

(1.33)

$$P_3 = V_{\rm max}^2 / R_{\rm max} = 1.212 \,\,{\rm W}. \tag{1.34}$$

$$P_4 = V_{\min}^2 / R_{\min} = 1.188 \text{ W.}$$

(1.35)

By inspection of Equations (1.32) through (1.35), Equation (1.32) shows the maximum dissipated power, and Equation (1.33) shows the smallest dissipated power.

Commonly available resistor power ratings are 0.063 W, 0.1 W, 0.125 W, 0.2 W, 0.25 W, 0.5 W, 1 W, 2 W, and 5 W for most electronic and some electrical applications. For special high-power electrical applications, the power ratings go well beyond 5 W, such as 10 W, 20 W, 50 W, 75 W, 100 W, 500 W, 1 kW, and above.

For our example, the most logical choice is to select a 2-W power-rated resistor.

#### Answers to Example 1.3

(a)  $R = 120 \Omega$ , (b)  $\pm 1\%$ , (c) 2 W.

*R* can be 120  $\Omega \pm 1\%$ , 2 W. When the voltage varies from 12 V  $\pm 1\%$ , current *I* remains within  $\pm 2\%$  of its nominal value of 100 mA. Note that choosing a 1 W resistor is not an option since the minimum power dissipation exceeds 1 W; 2 W resistor is the next given resistor power rating that provides a head-room of 0.764 W or 76.4% more with respect to 1 W.

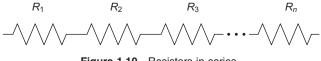

Figure 1.10 Resistors in series.

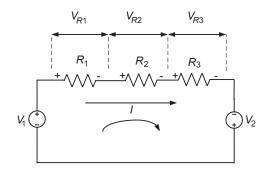

## 1.3.2 Resistors in Series and in Parallel

Two or more resistors are connected in series when the same current flows through all of them. Referring to Figure 1.10, resistors  $R_1$ ,  $R_2$ , and  $R_3$  are in series. Why? Because if a positive terminal of a voltage source is applied to the free end of one resistor in the series, and the negative terminal of the source is applied to the free terminal of the last resistor in the series, the current flowing through such circuit is identical for all resistors.

Generalizing the above concept, "n" resistors in series are equivalent to the sum of all n resistors. n is an integer and the total number of resistors in series.

$$R_1 + R_2 + R_3 + \ldots + R_n = \sum_{i}^{n} R_i.$$

(1.36)

Two resistors in series are equivalent to the sum of each of the resistors.

#### **Example 1.4 Resistors in Series**

Given a 1 k $\Omega$ , a 3 k $\Omega$ , and a 100  $\Omega$  resistor in series, find the series equivalent resistance.

#### Solution to Example 1.4

1000 Ω + 3000 Ω + 100 Ω = 4100 Ω = 4.1 kΩ.

#### **Example 1.5 Resistors of Significantly Different Values**

Given 1 M $\Omega$  and 1 k $\Omega$  resistors, find their series equivalent resistance.

#### Solution to Example 1.5

Not different from the previous example, the solution is 1,000,000  $\Omega$  + 1000  $\Omega$  = 1.001 M $\Omega$ .

**Example 1.6** Let us assume that both resistors of the previous example have  $\pm 1\%$  tolerance. What is the series equivalent resistance of both resistors with an error of approximately  $\pm 1\%$ ?

# Solution to Example 1.6

With  $\pm 1\%$  tolerance, it is easy to see that

$$\pm 1\% \text{ of } 1 \text{ M}\Omega = \pm 10,000 \Omega$$

(1.37)

and

$$\pm 1\% \text{ of } 1 \text{ k}\Omega = \pm 10 \Omega.$$

(1.38)

Since the value of the 1 k $\Omega$  resistor is much smaller than 1% of the value of the series equivalent resistor, found in the earlier part of this example to be 1.001 M $\Omega$ , the entire value of the small resistor can be neglected. The approximate answer is 1 M $\Omega$  ±10,000 k $\Omega$ , which is within a ±1% error. Note that a 1% error of 1 M $\Omega$  from Equation (1.37) is 10,000  $\Omega$ .

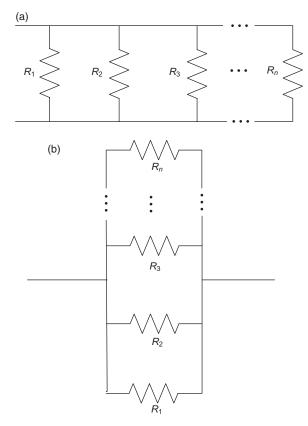

Resistors in parallel are those resistors that are connected such that the voltage across all of them is the same. Figure 1.11, depicts "n" resistors in

Figure 1.11 Resistors in parallel.

parallel. Note that part (a) and part (b) of the figure represent the exact same circuit.

Given two resistors  $R_1$  and  $R_2$  in parallel, the total parallel equivalent resistance  $(R_{parallel-equiv})$  is

$$R_{parallel-equiv} = \frac{product - of - both - resistor - values}{sum - of - both - resistor - values}.$$

(1.39)

**Example 1.7** Given two resistors in parallel,  $R_1 = 3 \Omega$  and  $R_2 = 6 \Omega$ , find the total equivalent resistance.

# Solution to Example 1.7

Applying Equation (1.39),

$$R_{parallel-equiv} = 3 \times 6/(3+6) = 2 \Omega.$$

(1.40)

Equation (1.39) can be arithmetically expressed as follows:

$$\frac{1}{R_{parallel-equiv}} = \frac{1}{R_1} + \frac{1}{R_2}$$

(1.41)

$$R_{parallel-equiv} = \frac{R_1 \cdot R_2}{R_1 + R_2},\tag{1.42}$$

where  $R_{parallel-equiv}$  refers to the parallel equivalent resistor of  $R_1$  and  $R_2$ . Note that Equations (1.41) and (1.42) are equivalent.

Generalizing from Equation (1.41), the parallel equivalent resistance of n (where n is an integer) that represents the number of resistors equals

$$1/R_{parallel-equiv} = 1/R_1 + 1/R_2 + 1/R_3 + \dots + 1/R_n.$$

(1.43)

Upon covering Kirchhoff's laws in the next section we will justify the computations to find series and parallel equivalent resistors.

**Example 1.8** Given three resistors in parallel, where  $R_1 = 3 \Omega$ ,  $R_2 = 6 \Omega$ , and  $R_3 = 2 \Omega$ , calculate the parallel equivalent resistor.

## Solution to Example 1.8

Using Equation (1.43), we obtain

$$\frac{1}{R_{parallel-equiv}} = \frac{1}{R_1} + \frac{1}{R_2} + \frac{1}{R_3},$$

(1.44)

and using the corresponding values for  $R_1$ ,  $R_2$ , and  $R_3$ , we get that

$$1/R_{parallel-equiv} = 1/3 + 1/6 + 1/2, \tag{1.45}$$

from where

$$R_{equiv} = 1\,\Omega. \tag{1.46}$$

**Example 1.9a** Given 10 resistors in parallel of equal value, find the parallel equivalent resistor of the group of 10.

# Solution to Example 1.9a

Using Equation (1.43) for "n = 10" resistors in parallel, we find that

$$1/R_{parallel-equiv} = 1/R + 1/R + 1/R + \dots + 1/R,$$

(1.47)

where Equation (1.43) has 10 equal terms because all 10 resistors have the same value.

From Equation (1.43), we obtain

$$1/R_{parallel-equiv} = 10/R \tag{1.48}$$

or

$$R_{parallel-equiv} = R/10. \tag{1.49}$$

**Example 1.9b** Given two resistors in parallel where one is  $1 \text{ k}\Omega$  and the other one is  $1 \Omega$ , find the total equivalent resistance.

# Solution to Example 1.9b

Using Equation (1.43) one more time, we obtain

$$1/R_{parallel-equiv} = 1/1 + 1/1000, \tag{1.50}$$

from where we obtain that

$$R_{parallel-equiv} = 1000/1001 = 0.999001 \,\Omega. \tag{1.51}$$

#### Corollary from Example 1.9

The parallel of one resistor with another one that is several orders of magnitude larger than the first one is approximately equal to the smaller resistor value. **Example 1.10** Given three resistors, where  $R_1 = 1 \Omega$ ,  $R_2 = 27 \Omega$ , and  $R_3 = 500 \Omega$ , calculate the parallel equivalent resistance of the three resistors.

#### Solution to Example 1.10

Using Equation (1.43) from above,

$$1/R_{parallel-equiv} = 1/R_1 + 1/R_2 + 1/R_3$$

$$1/R_{equiv} = 1/1 + 1/27 + 1/500 = 1/0.9624$$

$$R_{equiv} = 0.9624 \ \Omega$$

Note that the parallel equivalent resistor of 0.9624  $\Omega$  is smaller than the smallest given resistor, which is 1  $\Omega$ .

# Corollary from Example 1.10

The reader should be convinced that

Given n resistors,  $R_1$ ,  $R_2$ , ...,  $R_n$  where  $R_1 < R_2 < ... < R_n$ , the total parallel equivalent resistor is always smaller than  $R_1$ . In other words, a number of resistors in parallel has a parallel equivalent which is numerically smaller than the smallest resistor value.

# 1.3.3 Resistivity: A Physical Interpretation

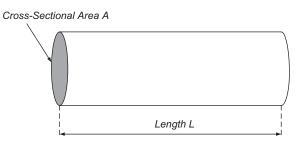

Figure 1.12 shows a conductor made of a conductive material. The most common conductive materials are metals; copper is the most abundant and the least expensive metal to mass-produce electrical wire. Although in many practical applications it is reasonable to assume that the total resistance of a conductor is close to 0  $\Omega$ , actually, it is not 0. So for some applications, the true resistance of a conductor needs to be taken into account.

The resistance of a conductor is given by

$$R = \rho L/A, \tag{1.52}$$

Figure 1.12 Conductor of length L and cross-section A.

| Material              | Resistivity $\rho$ in $(\Omega \cdot m)$ at 20°C | Conductor or Insulator? |

|-----------------------|--------------------------------------------------|-------------------------|

| Silver                | $1.62 \times 10^{-8}$                            | Conductor               |

| Copper                | $1.69 \times 10^{-8}$                            | Conductor               |

| Gold                  | $2.35 \times 10^{-8}$                            | Conductor               |

| Aluminum              | $2.75 \times 10^{-8}$                            | Conductor               |

| Magnanin <sup>a</sup> | $4.82 \times 10^{-8}$                            | Conductor               |

| Tungsten              | $5.25 \times 10^{-8}$                            | Conductor               |

| Iron                  | $9.68 \times 10^{-8}$                            | Conductor               |

| Platinum              | $10.6 \times 10^{-8}$                            | Conductor               |

| Glass                 | $10^{10}$ to $10^{14}$                           | Insulator               |

| Fused quartz          | ~10 <sup>16</sup>                                | Insulator               |

| Table 1.4 | Resistivity of | of some | materials at | room | temperature | (20°C) | ) [2 | 2] |

|-----------|----------------|---------|--------------|------|-------------|--------|------|----|

|           |                |         |              |      |             |        |      |    |

<sup>a</sup> Magnanin is an alloy with a very small temperature coefficient of resistivity.

where  $\rho$  (lowercase Greek letter rho) is the material resistivity in ohm meter ( $\Omega$ m), L is the length of the conductor in meters (m), and A is the cross-sectional area of the conductor in meters squared (m<sup>2</sup>).

Figure 1.12 depicts a conductor of length L and cross-section A. Resistivity  $\rho$  is an electric characteristic of the material used, and it varies with temperature. Most commonly, resistivity is specified at room temperature of 20°C.

Table 1.4 lists some of the most common conductor and insulator materials and their resistivity.

Note that the range in resistivity between a conductor and an insulator such as glass minimally ranges from  $10^{-8}$  to  $10^{10}$ ; this is 19 orders of magnitude!

**Example 1.11** Assume that we have a DC voltage source that can produce 100 A of current at a constant 12 V. What voltage level will be present across the resistive load, without neglecting the voltage drop across the copper wires? Assume that you are using 10 mm<sup>2</sup> cross-section copper wires and that the one-way wire length (from source to load) is 1 m and the ambient temperature is 20°C. For illustration purposes of this problem, the reader is strongly referred to the circuit diagram of Figure 1.1 at the beginning of this chapter.

# Solution to Example 1.11

If the resistance of the wires was 0  $\Omega$ , the load would see exactly 12 V at 100 A. We need to take into account the wire resistance, then:

From Equation (1.52),  $R = \rho L/A$ .

Since one-way length of the wire is 1 m, the round-trip length of the wire is 2 m. From Table 1.4, copper resistivity is  $1.69 \times 10^{-8} \Omega m$  at a room temperature of 20°C. A cross section of 10 mm<sup>2</sup> equals 0.0001 m<sup>2</sup>. Plugging all the values into Equation (1.52) yields

$$R_{wire} = (1.69 \times 10^{-8} \ \Omega m) \times 2 \ m/10^{-4} \ m^2 = 338 \ \mu \Omega.$$

(1.53)

Since the current flowing through the wires is 100 A, the voltage drop across the load wires is

$$V_{drop-across-wires} = IR_{wire} = 100 \times 338 \times 10^{-6} \text{ A} \cdot \Omega = 33.8 \text{ mV}.$$

(1.54)

#### Answer to Example 1.11

The voltage that the load resistor will see is 12 V - 0.0338 V = 11.9662 V.

#### 1.3.4 Resistance of Conductors

It is interesting to observe that for a given conductor material, for example, copper, the resistance of the conductor equals to its resistivity, which depends on the material, times the length of the conductor (L), and it is inversely proportional to the conductor cross-sectional area (A) according to Equation (1.52).

So if the length of a conductor is doubled, all other factors remaining equal, the resistance of such conductor doubles. If the thickness (i.e., cross section) of a conductor doubles, while all other factors remain equal, the resistance of the conductor becomes half of the original resistance.

Resistivity  $\rho$ , is a temperature-dependent parameter, and it is a characteristic of the material. A good empirical approximation of how resistivity varies with temperature is

$$\rho - \rho_0 = \rho_0 \alpha (T - T_0), \tag{1.55}$$

where  $\alpha$  is called the temperature coefficient of resistivity,  $\rho_0$  is the resistivity at the reference temperature, usually 20°C (or 293K [kelvin degrees]),  $T_0$  is the reference temperature (20°C in our case), and  $\rho$  and T are respectively the resistivity and the temperature of the conductor at the temperature of interest, or at the unknown temperature. Equation (1.55) is linear and remains linear for most engineering problems over a wide temperature range around 20°C. Table 1.5 lists the temperature coefficient of resistivity  $\alpha$  for some metals.

## 1.4 OHM'S LAW, POWER DELIVERED AND POWER CONSUMED

A voltage source happens to behave very much like a constant pressure water pump. The voltage source pushes the current through the electric circuit very much like a water pump pushes a volume of water through the closed-loop hydraulic case as depicted in Figure 1.13a, which shows an electrical circuit with a DC voltage source, a conductor or wire and a resistor, and Figure 1.13b

| Metal                 | ( $\alpha$ ) Temperature Coefficient of Resistivity [K <sup>-1</sup> ] |

|-----------------------|------------------------------------------------------------------------|

| Silver                | $4.1 \times 10^{-3}$                                                   |

| Copper                | $4.3 	imes 10^{-3}$                                                    |

| Gold                  | $4.0 	imes 10^{-3}$                                                    |

| Aluminum              | $4.4 	imes 10^{-3}$                                                    |

| Manganin <sup>a</sup> | $0.002 \times 10^{-3}$                                                 |

| Tungsten              | $4.5	imes10^{-3}$                                                      |

| Iron                  | $6.5 	imes 10^{-3}$                                                    |

| Platinum              | $3.9 \times 10^{-3}$                                                   |

Table 1.5 Temperature coefficients of resistivity for some metals [2]

<sup>*a*</sup> An alloy with an extremely low value of  $\alpha$ .

Figure 1.13 (a) An electric circuit and (b) its hydraulic analogy.

which depicts the hydraulic analogy of the electric circuit. The constant pressure pump is the analog to the electric voltage source. The pipe is analogous to the wiring, and the pipe with flow restriction is analogous to the resistor.

In Figure 1.13a, we can state that the current that flows through resistor R is proportional to the voltage applied across its terminals. Equation (1.2) is repeated here for the reader's convenience.

Ohm's Law

$$V = IR. \tag{1.56}$$

In Equation (1.56), V is the voltage across the resistor, I is the current flowing through resistor R, and R is the resistor value. Note from Figure 1.13a that V is the same as the voltage of the DC source applied.

The summary and a side-by-side comparison between the circuit elements and those of the hydraulic analogy in Figure 1.13 are presented in Table 1.6. Rearranging terms of Equation (1.56), it yields

$$I = V/R \tag{1.57}$$

and

$$R = V/I. \tag{1.58}$$

SI units in Table 1.1 refer to the international system of units (in French Le Système International d'Unités) that was established worldwide by the General Conference of Weights and Measures in 1960. Note that Ohm's law can be expressed in any of the three forms given by Equations (1.56), (1.57), or (1.58), where in all three equations, I is the current flowing through resistor R, and V is the voltage across resistor R terminals.

Now back to Joule's law, a resistor will consume or dissipate in the form of heat an amount of power given in watts (W) in the SI system. This power

| Electric Circuit  |                 | Hydra                     | aulic Analogy                                                            |

|-------------------|-----------------|---------------------------|--------------------------------------------------------------------------|

| Element           | SI Units        | Element                   | SI Units                                                                 |

| DC voltage source | V (volts)       | Constant<br>pressure pump | Kg/m <sup>2</sup>                                                        |

| Current           | A (coulomb/s)   | Volume flow rate          | Liter/s                                                                  |

| Resistor          | $\Omega$ (ohms) | Flow constrictive pipe    | There is no unit of<br>resistance for a water<br>flow constrictive pipe. |

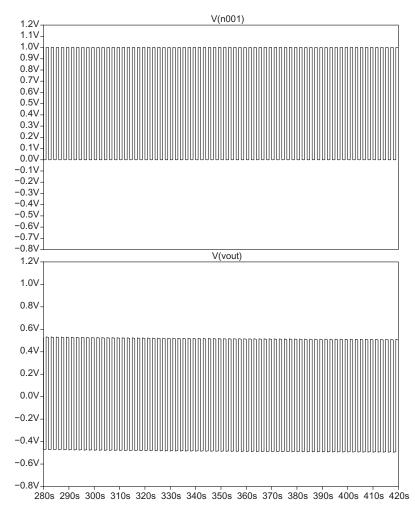

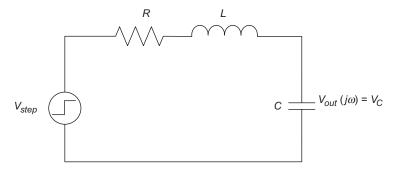

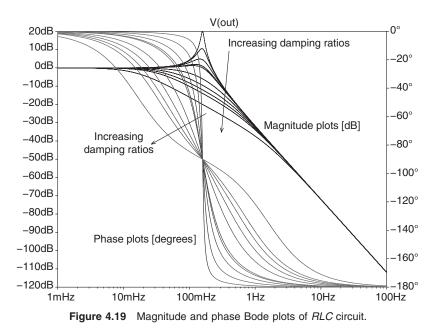

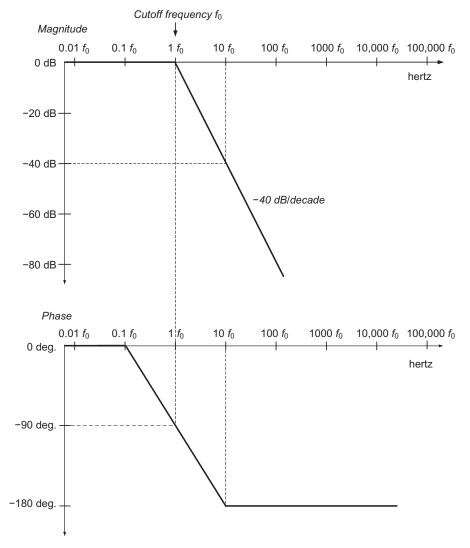

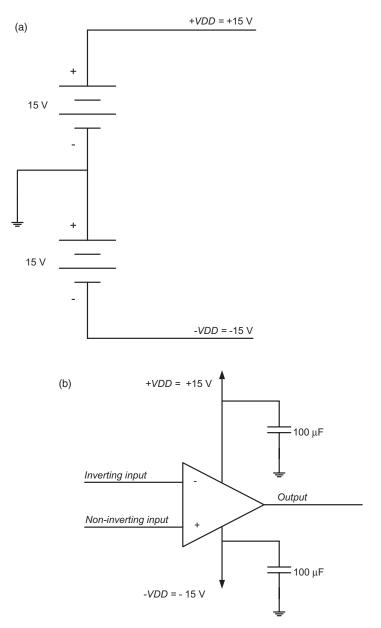

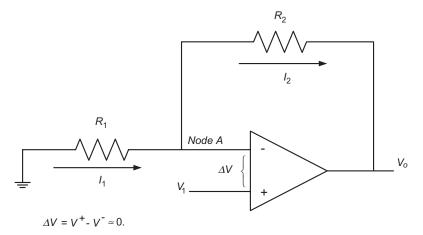

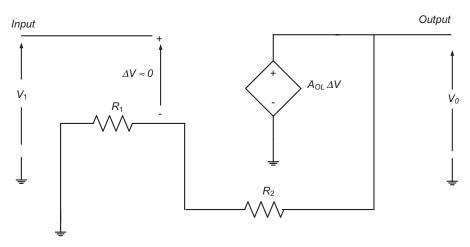

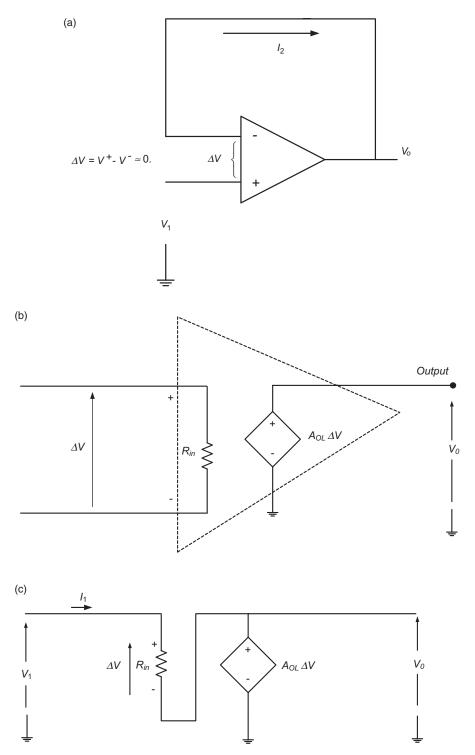

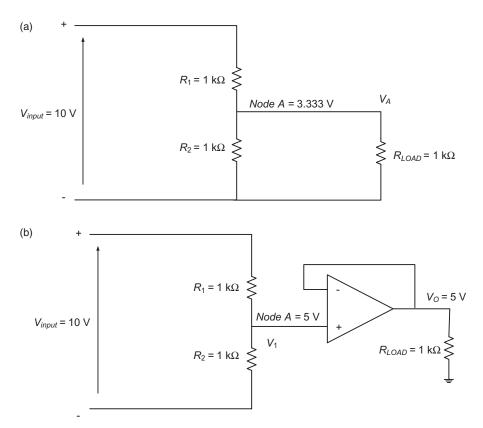

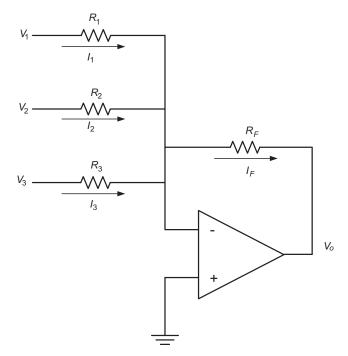

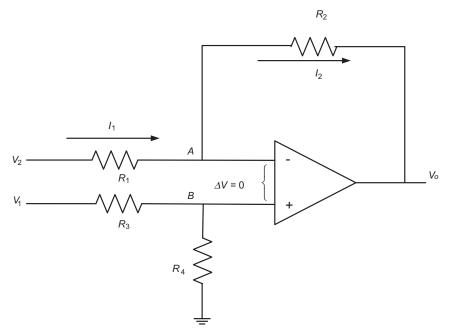

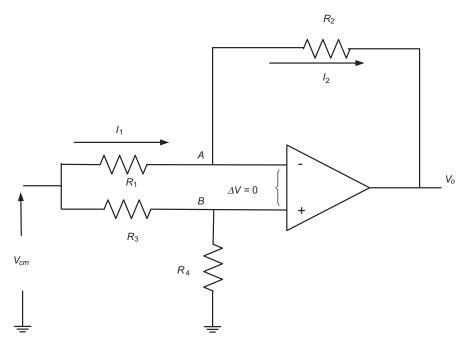

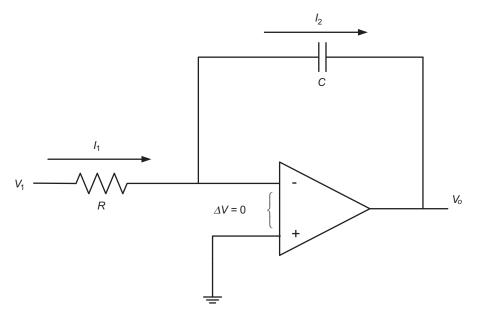

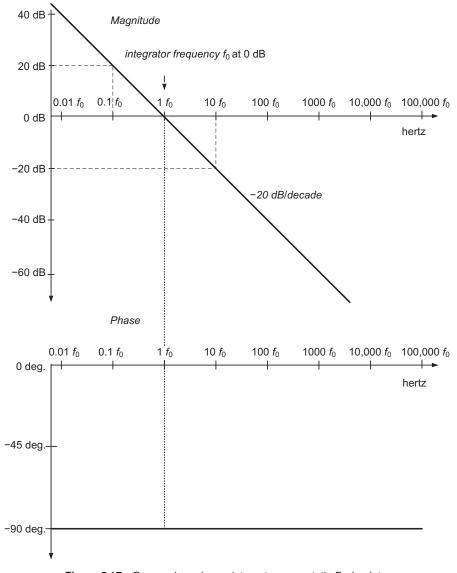

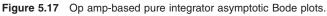

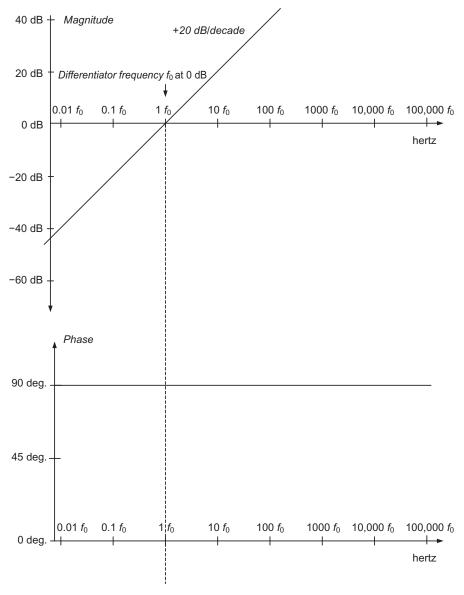

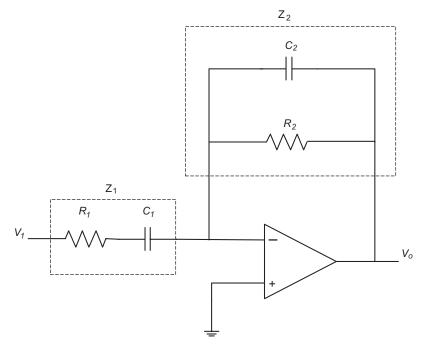

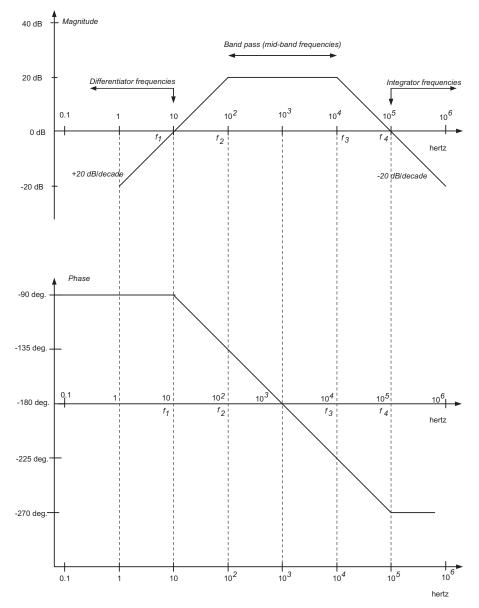

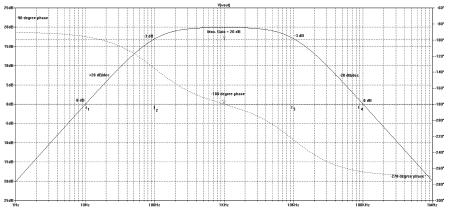

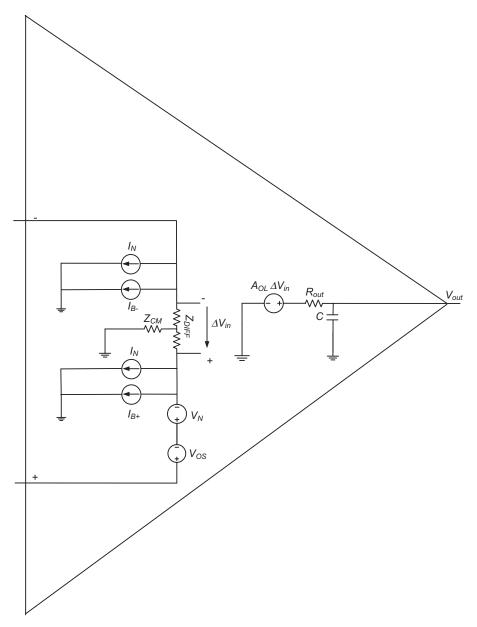

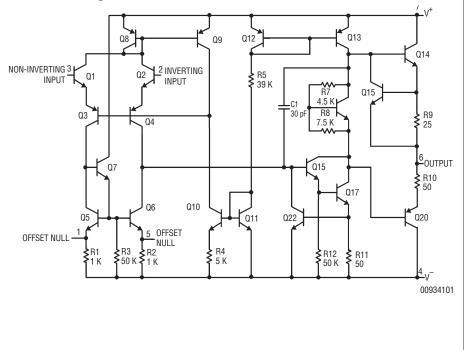

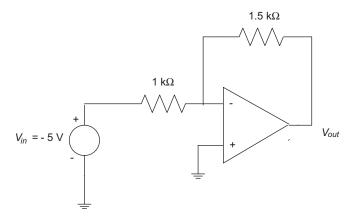

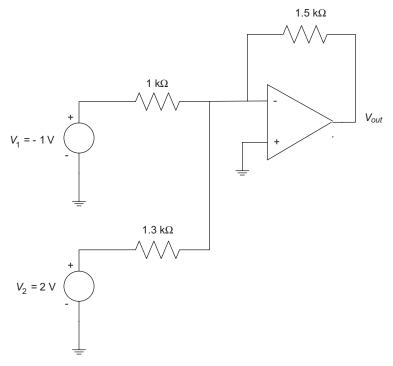

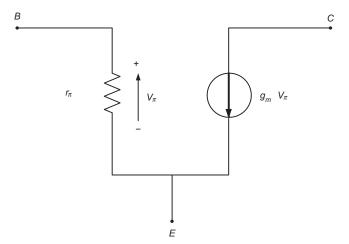

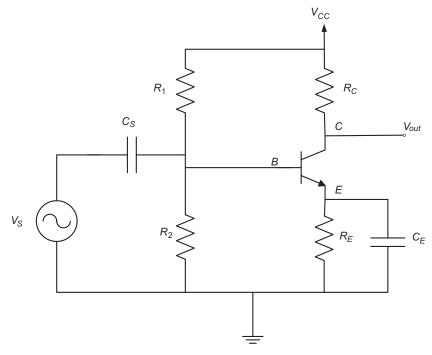

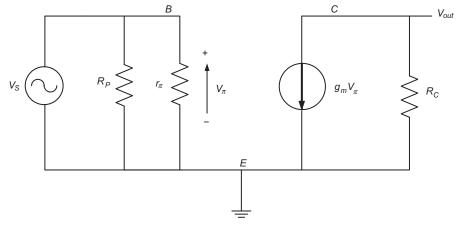

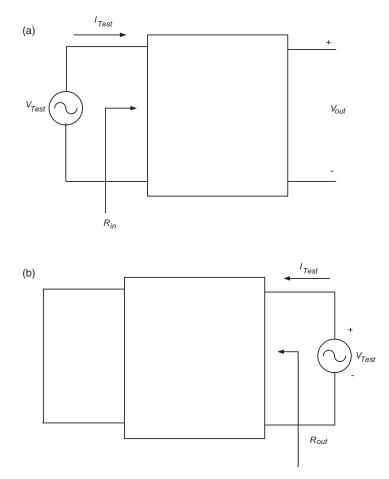

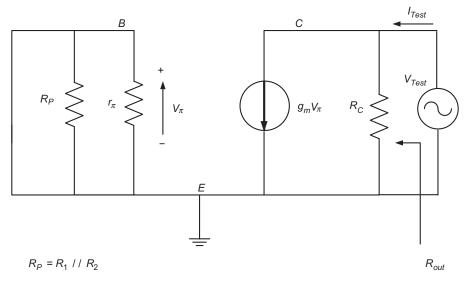

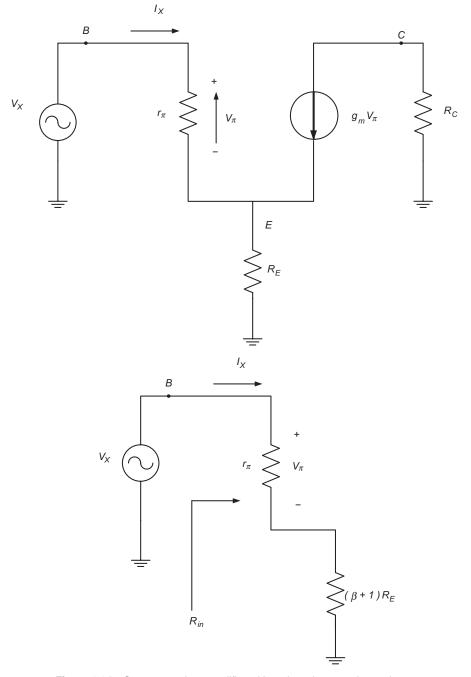

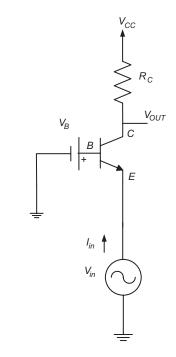

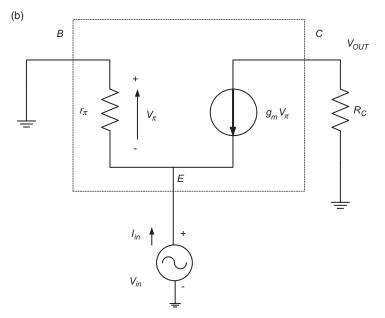

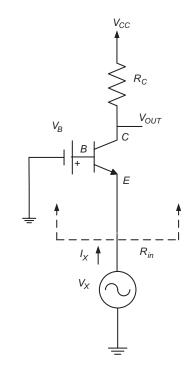

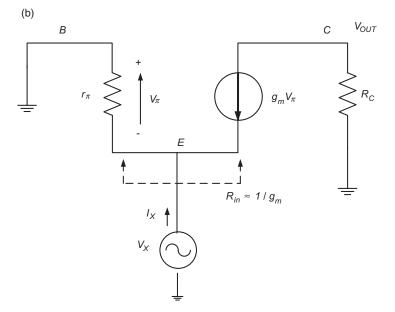

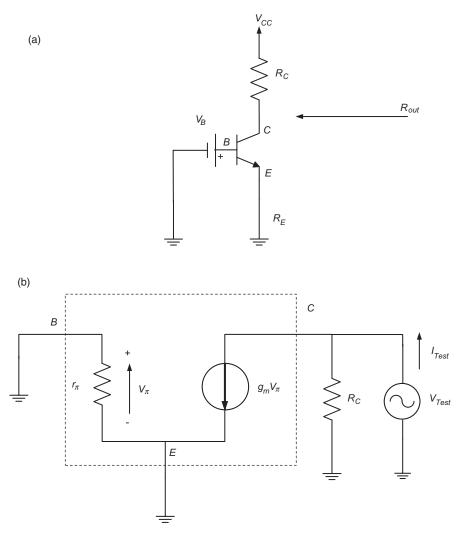

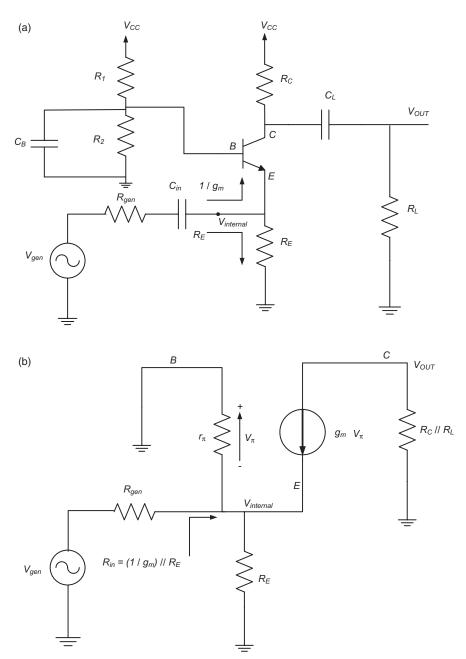

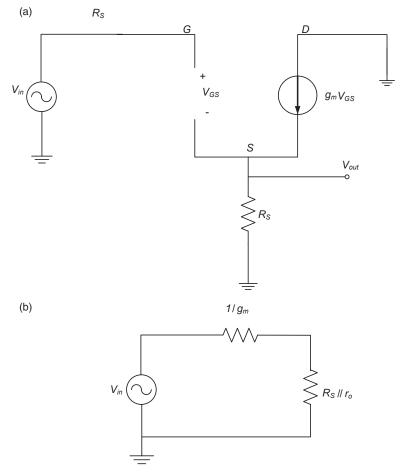

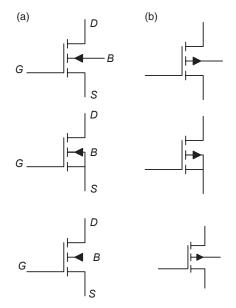

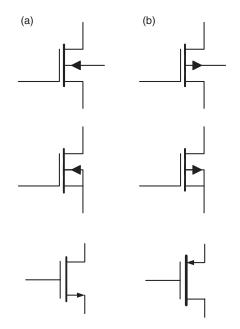

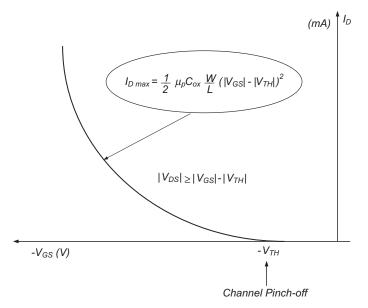

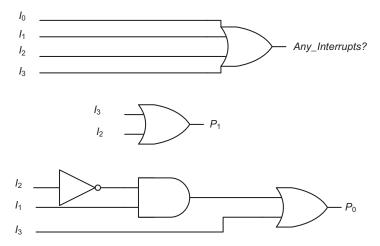

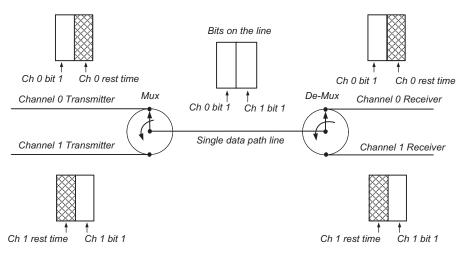

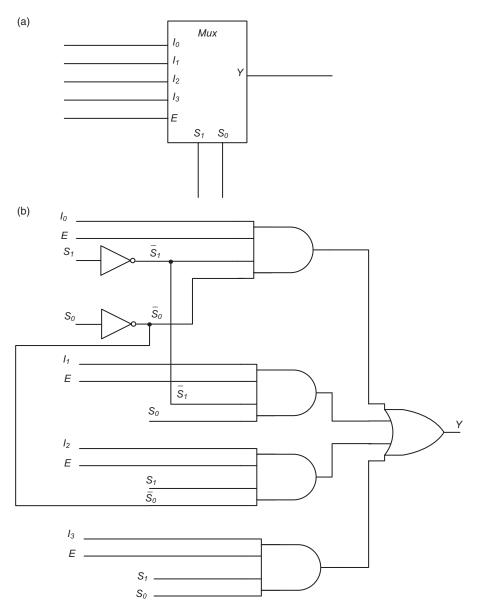

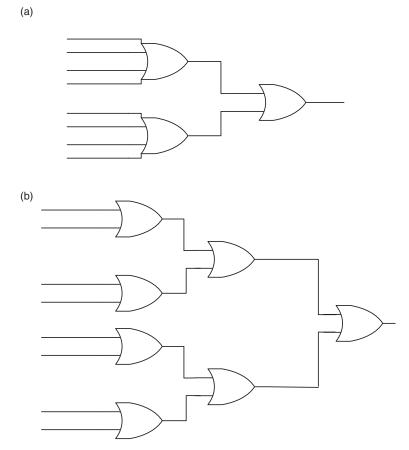

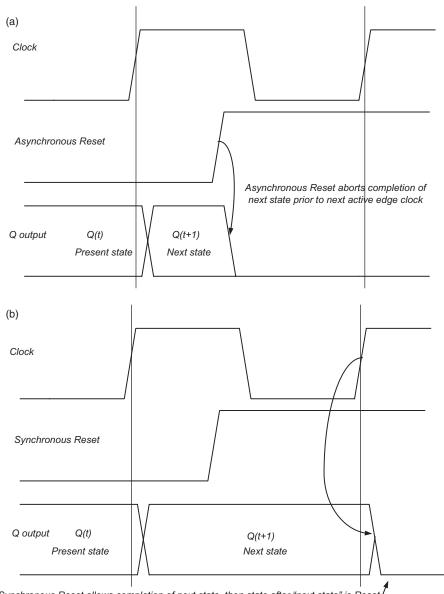

Table 1.6 Electrical and hydraulic analogies