## Digital Power Electronics and Applications

### Digital Power Electronics and Applications

# This page intentionally left blank

### Digital Power Electronics and Applications

Fang Lin Luo Hong Ye Muhammad Rashid

This book is printed on acid-free paper

Copyright © 2005, Elsevier (USA). All rights reserved

No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means electronic, mechanical, photocopying, recording or otherwise, without the prior written permission of the publisher

Permissions may be sought directly from Elsevier's Science & Technology Rights Department in Oxford, UK: phone: (+44) 1865 843830, fax: (+44) 1865 853333, e-mail: permissions@elsevier.co.uk. You may also complete your request on-line via the Elsevier homepage (http://elsevier.com), by selecting "Customer Support" and then "Obtaining Permissions."

Elsevier Academic Press 525 B Street, Suite 1900, San Diego, California 92101-4495, USA http://www.elsevier.com

Elsevier Academic Press 84 Theobald's Road, London WC1X 8RR, UK http://www.elsevier.com

Library of Congress Control Number: 2005929576

### **British Library Cataloguing-in-Publication Data**

A catalogue record for this book is available from the British Library.

ISBN: 0-1208-8757-6

Typeset by Charon Tec Pvt. Ltd, Chennai, India www.charontec.com

Printed and bound in United States

05 06 07 08 9 8 7 6 5 4 3 2 1

### Working together to grow libraries in developing countries

www.elsevier.com | www.bookaid.org | www.sabre.org

**ELSEVIER**

BOOK AID

Sabre Foundation

### **Contents**

| Pre | face   |                                                                  | ix  |

|-----|--------|------------------------------------------------------------------|-----|

| Au  | tobiog | raphy                                                            | xi  |

| 1.  | Intro  | duction                                                          |     |

|     | 1.1    | Historical review                                                | 1   |

|     | 1.2    | Traditional parameters                                           | 7   |

|     | 1.3    | Multiple-quadrant operations and choppers                        | 16  |

|     | 1.4    | Digital power electronics: pump circuits and conversion          |     |

|     |        | technology                                                       | 22  |

|     | 1.5    | Shortage of analog power electronics and conversion technology   | 31  |

|     | 1.6    | Power semiconductor devices applied in digital power electronics | 32  |

| 2.  | Ener   | gy Factor (EF) and Sub-sequential Parameters                     |     |

|     | 2.1    | Introduction                                                     | 34  |

|     | 2.2    | Pumping energy ( <i>PE</i> )                                     | 35  |

|     | 2.3    | Stored energy (SE)                                               | 36  |

|     | 2.4    | Energy factor (EF)                                               | 40  |

|     | 2.5    | Variation energy factor $(EF_{V})$                               | 41  |

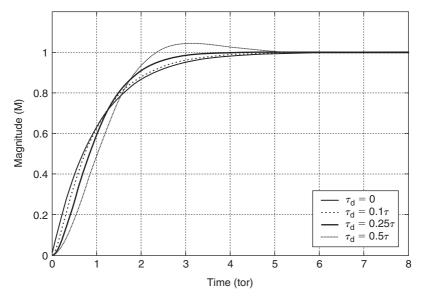

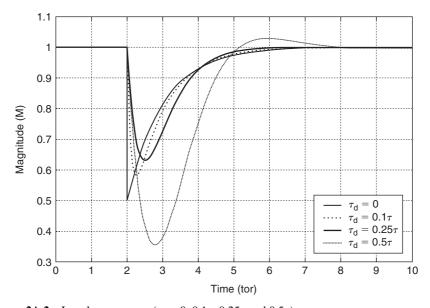

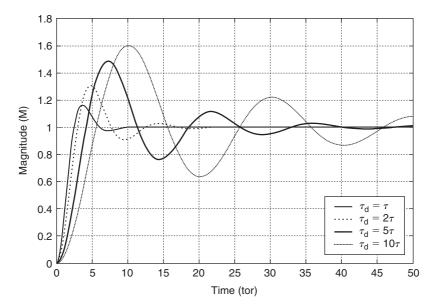

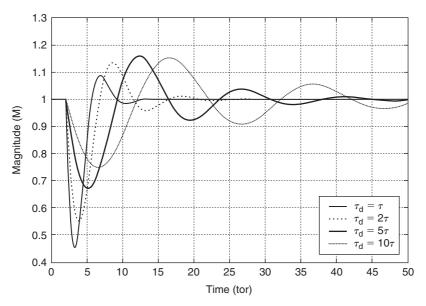

|     | 2.6    | Time constant, $\tau$ , and damping time constant, $\tau_d$      | 41  |

|     | 2.7    | Examples of applications                                         | 43  |

|     | 2.8    | Small signal analysis                                            | 65  |

| 3.  | Basic  | c Mathematics of Digital Control Systems                         |     |

|     | 3.1    | Introduction                                                     | 85  |

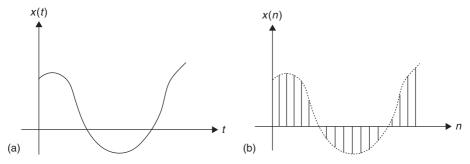

|     | 3.2    | Digital Signals and Coding                                       | 91  |

|     | 3.3    | Shannon's sampling theorem                                       | 94  |

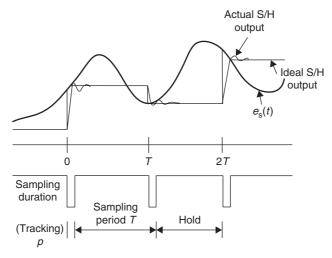

|     | 3.4    | Sample-and-hold devices                                          | 95  |

|     | 3.5    | Analog-to-digital conversion                                     | 99  |

|     | 3.6    | Digital-to-analog conversion                                     | 101 |

|     | 3.7    | Energy quantization                                              | 104 |

|     | 3.8    | Introduction to reconstruction of sampled signals                | 106 |

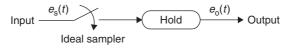

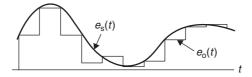

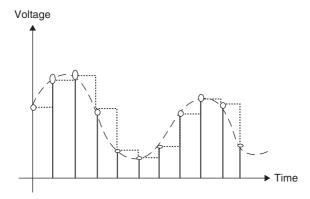

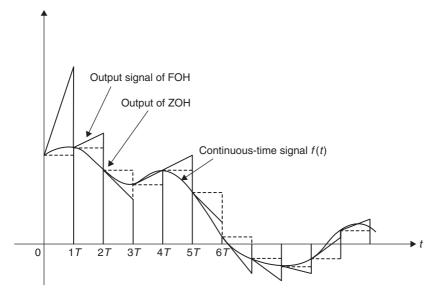

|     | 3.9    | Data conversion: the zero-order hold                             | 107 |

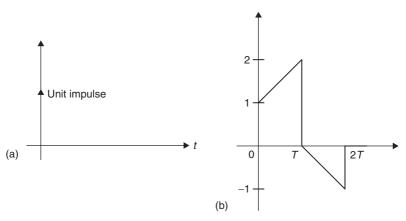

|     | 3.10   | The first-order hold                                             | 110 |

|     | 3.11   | The second-order hold                                            | 112 |

|     | 3.12   | The Laplace transform (the <i>s</i> -domain)                     | 118 |

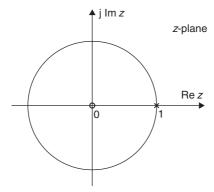

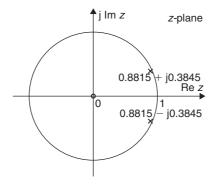

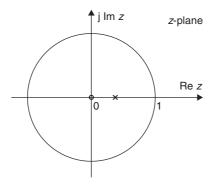

|     | 3.13   | The z-transform (the z-domain)                                   | 118 |

vi Contents

| 4. | Matl                                 | nematical Modeling of Digital Power Electronics                  |     |  |  |  |  |

|----|--------------------------------------|------------------------------------------------------------------|-----|--|--|--|--|

|    | 4.1                                  | Introduction                                                     | 123 |  |  |  |  |

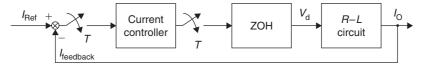

|    | 4.2                                  | A zero-order hold (ZOH) for AC/DC controlled rectifiers          | 125 |  |  |  |  |

|    | 4.3                                  | A first-order transfer function for DC/AC pulse-width-modulation |     |  |  |  |  |

|    |                                      | inverters                                                        | 128 |  |  |  |  |

|    | 4.4                                  | A second-order transfer function for DC/DC converters            | 132 |  |  |  |  |

|    | 4.5                                  | A first-order transfer function for AC/AC (AC/DC/AC) converters  | 136 |  |  |  |  |

| 5. | Digi                                 | tally Controlled AC/DC Rectifiers                                |     |  |  |  |  |

|    | 5.1                                  | Introduction                                                     | 142 |  |  |  |  |

|    | 5.2                                  | Mathematical modeling for AC/DC rectifiers                       | 151 |  |  |  |  |

|    | 5.3                                  | Single-phase half-wave controlled AC/DC rectifier                | 153 |  |  |  |  |

|    | 5.4                                  | Single-phase full-wave AC/DC rectifier                           | 154 |  |  |  |  |

|    | 5.5                                  | Three-phase half-wave controlled AC/DC rectifier                 | 155 |  |  |  |  |

|    | 5.6                                  | Three-phase full-wave controlled AC/DC rectifier                 | 155 |  |  |  |  |

|    | 5.7                                  | Three-phase double-anti-star with interphase-transformer         |     |  |  |  |  |

|    |                                      | controlled AC/DC rectifier                                       | 156 |  |  |  |  |

|    | 5.8                                  | Six-phase half-wave controlled AC/DC rectifier                   | 158 |  |  |  |  |

|    | 5.9                                  | Six-phase full-wave controlled AC/DC rectifier                   | 159 |  |  |  |  |

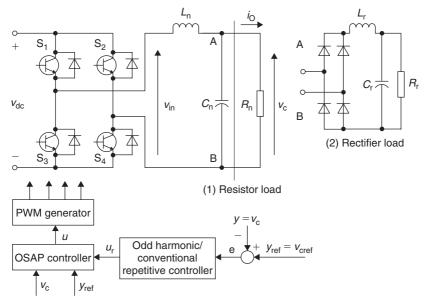

| 6. | Digitally Controlled DC/AC Inverters |                                                                  |     |  |  |  |  |

|    | 6.1                                  | Introduction                                                     | 162 |  |  |  |  |

|    | 6.2                                  | Mathematical modeling for DC/AC PWM inverters                    | 172 |  |  |  |  |

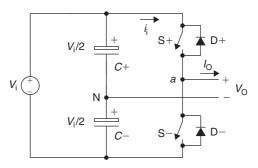

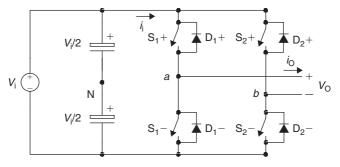

|    | 6.3                                  | Single-phase half-wave VSI                                       | 174 |  |  |  |  |

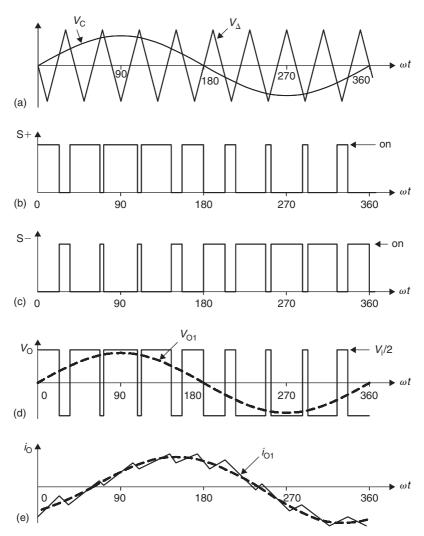

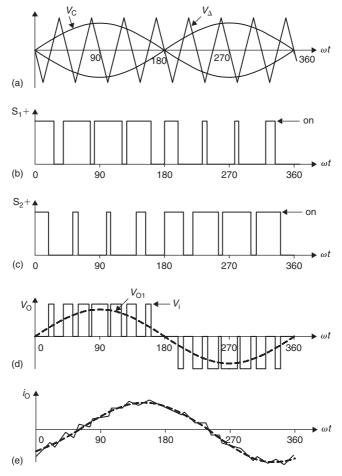

|    | 6.4                                  | Single-phase full-bridge PWM VSI                                 | 175 |  |  |  |  |

|    | 6.5                                  | Three-phase full-bridge PWM VSI                                  | 175 |  |  |  |  |

|    | 6.6                                  | Three-phase full-bridge PWM CSI                                  | 176 |  |  |  |  |

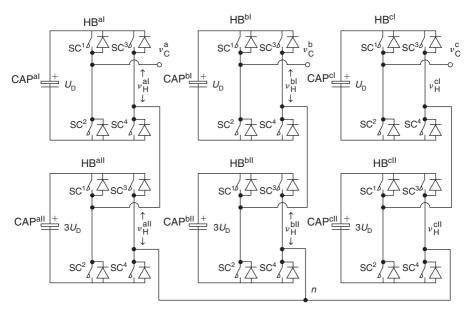

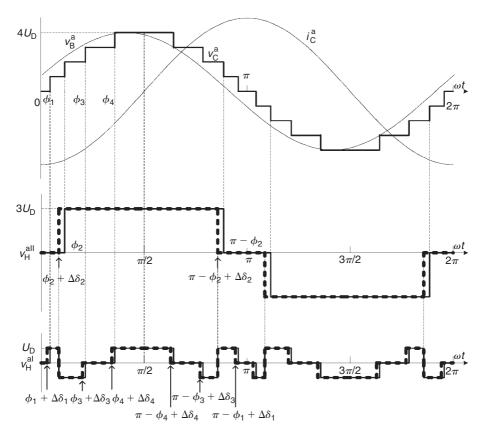

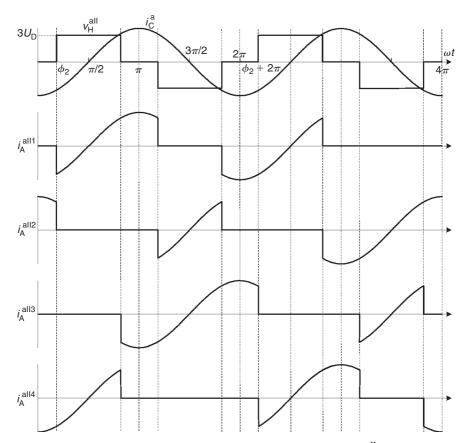

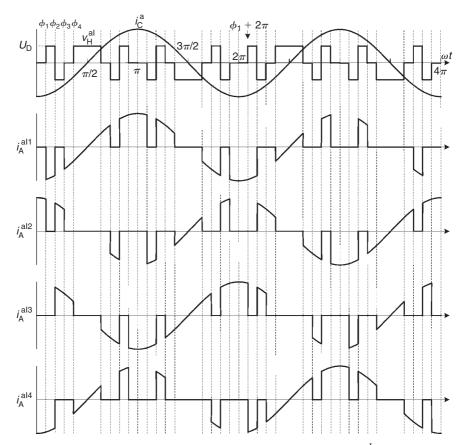

|    | 6.7                                  | Multistage PWM inverter                                          | 176 |  |  |  |  |

|    | 6.8                                  | Multilevel PWM inverter                                          | 176 |  |  |  |  |

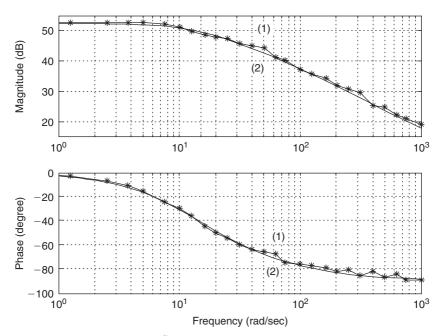

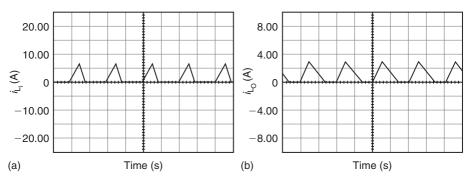

| 7. | Digi                                 | tally Controlled DC/DC Converters                                |     |  |  |  |  |

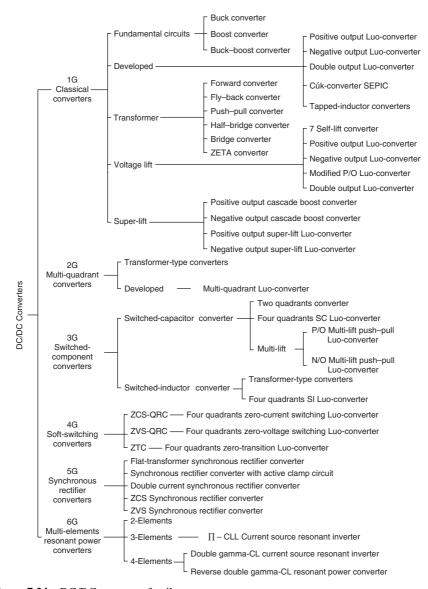

|    | 7.1                                  | Introduction                                                     | 178 |  |  |  |  |

|    | 7.2                                  | Mathematical Modeling for power DC/DC converters                 | 202 |  |  |  |  |

|    | 7.3                                  | Fundamental DC/DC converter                                      | 205 |  |  |  |  |

|    | 7.4                                  | Developed DC/DC converters                                       | 208 |  |  |  |  |

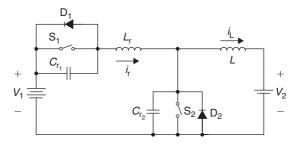

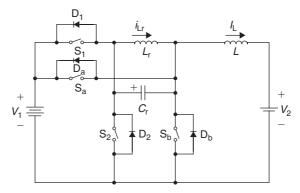

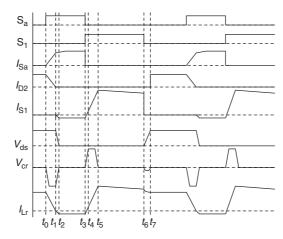

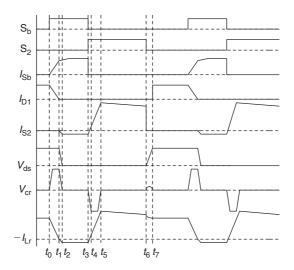

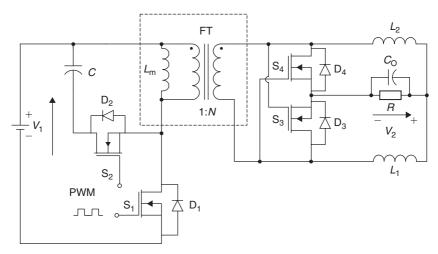

|    | 7.5                                  | Soft-switching converters                                        | 209 |  |  |  |  |

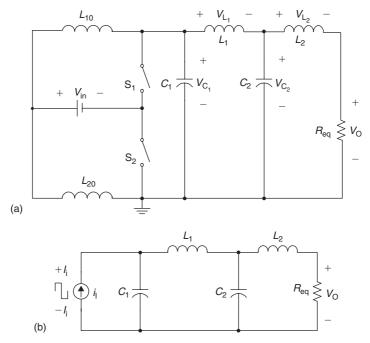

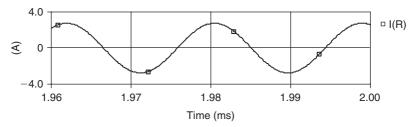

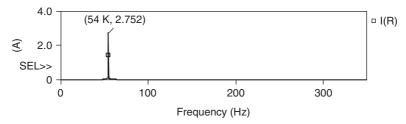

|    | 7.6                                  | Multi-element resonant power converters                          | 213 |  |  |  |  |

| 8. | Digi                                 | tally Controlled AC/AC Converters                                |     |  |  |  |  |

|    | 8.1                                  | Introduction                                                     | 221 |  |  |  |  |

|    | 8.2                                  | Traditional modeling for AC/AC (AC/DC/AC) converters             | 244 |  |  |  |  |

|    | 8.3                                  | Single-phase AC/AC converter                                     | 245 |  |  |  |  |

|    | 8.4                                  | Three-phase AC/AC voltage controllers                            | 245 |  |  |  |  |

|    | 8.5                                  | SISO cycloconverters                                             | 246 |  |  |  |  |

*Contents* vii

|      | 8.6   | TISO cycloconverters                                | 246 |

|------|-------|-----------------------------------------------------|-----|

|      | 8.7   | TITO cycloconverters                                | 246 |

|      | 8.8   | AC/DC/AC PWM converters                             | 246 |

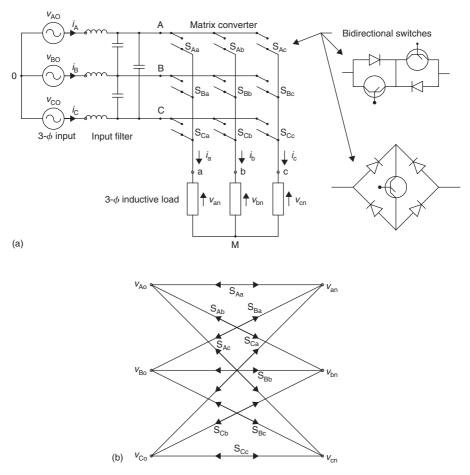

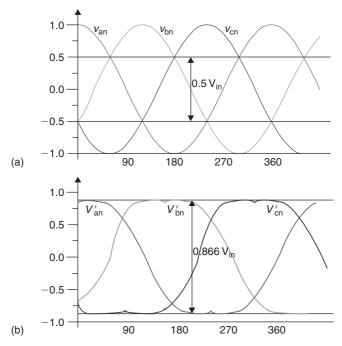

|      | 8.9   | Matrix converters                                   | 247 |

| 9.   | Oper  | n-loop Control for Digital Power Electronics        |     |

|      | 9.1   | Introduction                                        | 249 |

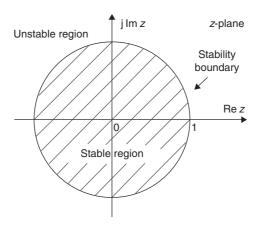

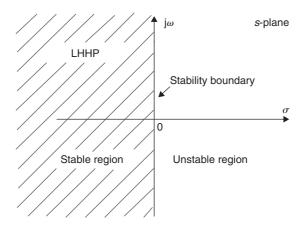

|      | 9.2   | Stability analysis                                  | 256 |

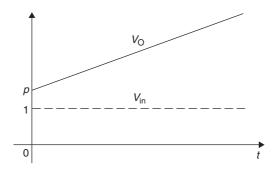

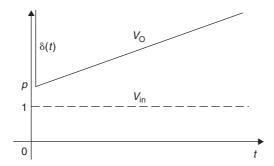

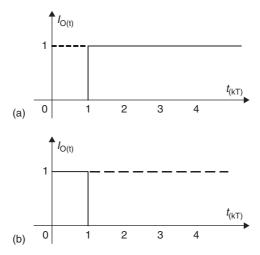

|      | 9.3   | Unit-step function responses                        | 269 |

|      | 9.4   | Impulse responses                                   | 280 |

|      | 9.5   | Summary                                             | 281 |

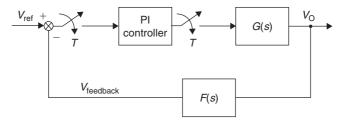

| 10.  | Close | ed-Loop Control for Digital Power Electronics       |     |

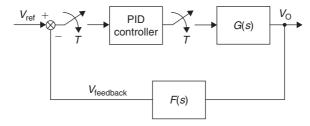

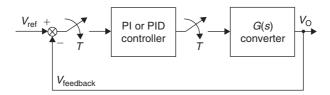

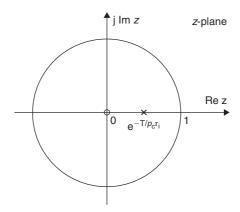

|      |       | Introduction                                        | 283 |

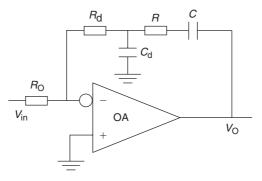

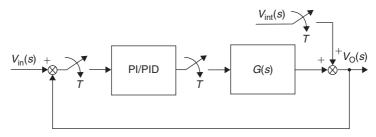

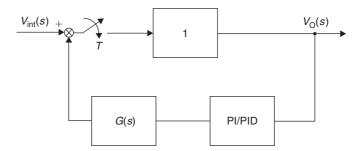

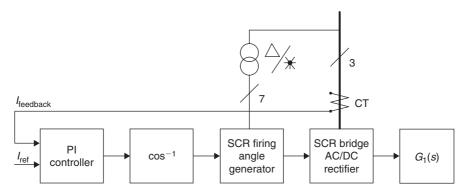

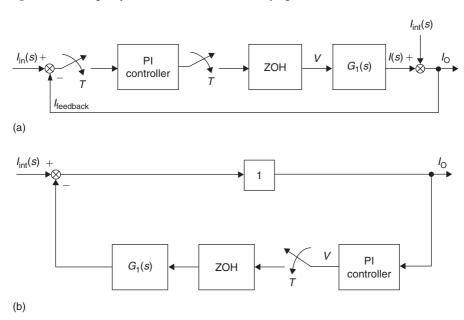

|      | 10.2  | PI control for AC/DC rectifiers                     | 288 |

|      | 10.3  | PI control for DC/AC inverters and AC/AC (AC/DC/AC) |     |

|      |       | converters                                          | 298 |

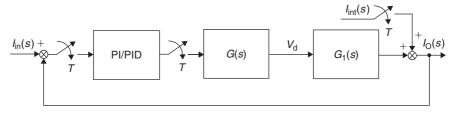

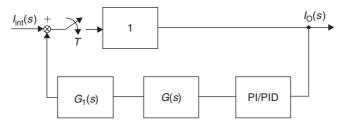

|      | 10.4  | PID control for DC/DC converters                    | 305 |

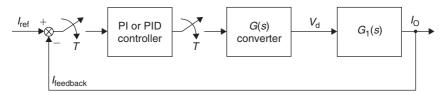

| 11.  | Ener  | gy Factor Application in AC and DC Motor Drives     |     |

|      |       | Introduction                                        | 314 |

|      | 11.2  | Energy storage in motors                            | 315 |

|      |       | A DC/AC voltage source                              | 317 |

|      | 11.4  | An AC/DC current source                             | 333 |

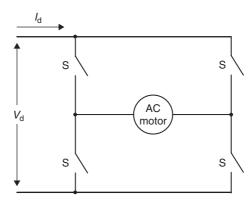

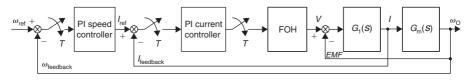

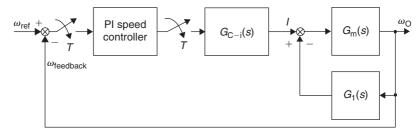

|      | 11.5  | AC motor drives                                     | 338 |

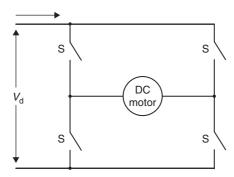

|      | 11.6  | DC motor drives                                     | 342 |

| 12.  | Appl  | ications in Other Branches of Power Electronics     |     |

|      |       | Introduction                                        | 348 |

|      |       | Power systems analysis                              | 349 |

|      |       | Power factor correction                             | 349 |

|      |       | Static compensation (STATCOM)                       | 363 |

| Inde | x     |                                                     | 401 |

# This page intentionally left blank

### **Preface**

The purpose of this book is to provide a theory of Digital Power Electronics and its applications. It is well organized in 400 pages and over 300 diagrams. Traditionally, Power Electronics is analyzed by the analog control theory. For over a century, people have enjoyed analog control in Power Electronics, and good results in the analog control and its applications in Power Electronics mislead people into an incorrect conclusion that Power Electronics **must** be in analog control scheme. The mature control results allowed people to think that Power Electronics is a sunset knowledge. We would like to change these incorrect conclusions, and confer new life onto the traditional Power Electronics. In this book the authors initially introduce the digital control theory applied to Power Electronics, which is completely different from the traditional control scheme.

Power Electronics supplies electrical energy from its source to its users. It is of vital importance to all of industry as well as the general public – just as the air that we breathe and water that we drink are taken for granted, until they are no longer available, so it is with Power Electronics. Therefore, we have to carefully investigate Power Electronics. Energy conversion technique is the main focus of Power Electronics. DC and AC motor drive systems convert the electrical energy to mechanical energy and vice versa. The corresponding equipment that drives DC and AC motors can be divided into four groups:

- AC/DC rectifiers:

- DC/AC inverters:

- DC/DC converters:

- AC/AC (AC/DC/AC) converters.

All of the above equipment are called power supplies. They are switching circuits working in a discrete state. High-frequency switch-on and switch-off semiconductor devices allow switching circuits to have the advantage of high power rate and efficiency, low cost, small size and high power density. The size of a flat-transformer working in 250 kHz is much less than 1% of the volume of a normal transformer working in 50 Hz with the same power rating. Switching circuits perform in switching-on and switching-off states periodically. The switching period, T, is the sampling interval (T = 1/f), where f is the switching frequency. Switching circuits, including all converters, transfer energy from a source to the end-users in discontinuous manner; i.e. the energy is not continuously flowing from a source to load. The energy is pumped by energy-quantization via certain energy-storage elements to load in a sampling interval.

x Preface

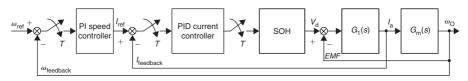

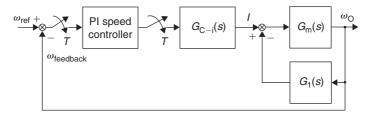

In order to apply digital control theory to Power Electronics, the authors define new parameters such as the energy factor (EF), pumping energy (PE), stored energy (SE), time constant,  $\tau$ , and damping time constant,  $\tau_d$ . These parameters are totally different from the traditional parameters such as the power factor (PF), power transfer efficiency ( $\eta$ ), ripple factor (RF) and total harmonic distortion (THD). Using the new parameters we successfully describe the characteristics of the converters' systems. Correspondingly, new mathematical modeling has been defined:

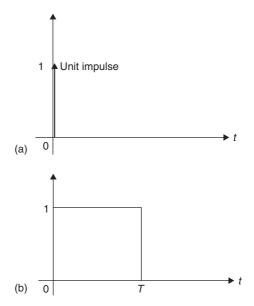

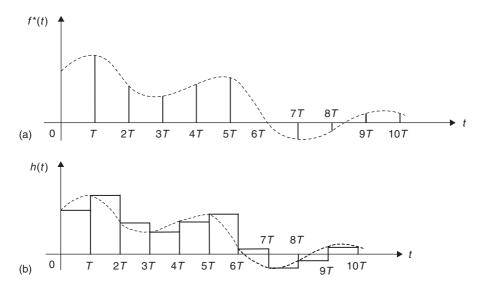

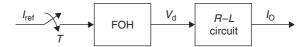

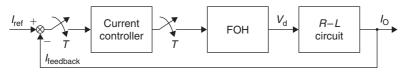

- A zero-order-hold (ZOH) is used to simulate all AC/DC rectifiers.

- A first-order-hold (FOH) is used to simulate all DC/AC inverters.

- A second-order-hold (SOH) is used to simulate all DC/DC converters.

- A first-order-hold (FOH) is used to simulate all AC/AC (AC/DC/AC) converters.

The authors had successfully applied the digital control theory in the AC/DC rectifiers in 1980s. The ZOH was discussed in digitally-controlled AC/DC current sources. Afterwards, the FOH was discussed in digitally-controlled DC/AC inverters and AC/AC converters. Finally, the SOH has been discussed in digitally-controlled DC/DC converters. The energy storage in power DC/DC converters have carefully been paid attention to and the system's characteristics have been discussed, including the fundamental features: system stability, unit-step response and impulse-response for disturbance.

These research results are available not only for all types of the converters, but for other branches in Power Electronics as well. We describe the digital control scheme in all types of the converters in this book, and some applications in other branches such as power factor correction (PFC) and power system synchronous static compensation (STATCOM). Digital Power Electronics is a fresh theory and novel research method.

We hope that our book attracts considerable attention from experts, engineers and university professors and students working in Power Electronics. This new control scheme could be described as fresh blood injected into the traditional Power Electronics field, and hopefully may generate new development. Therefore, this book is useful for both engineering students and research workers.

Fang Lin Luo Hong Ye Muhammad Rashid

### **Autobiography**

Dr. Fang Lin Luo (IEEE M'84, SM'95) received a Bachelor of Science Degree, First Class with Honours, in Radio-Electronic Physics at the Sichuan University, Chengdu, Sichuan, China and his Ph.D. Degree in Electrical Engineering and Computer Science (EE & CS) at Cambridge University, England, UK in 1986.

Dr. Luo was with the Chinese Automation Research Institute of Metallurgy (CARIM), Beijing, China as a Senior Engineer after his graduation from Sichuan University. In 1981 and 1982, he was with the Enterprises Saunier Duval,

Paris, France as a Project Engineer. Later, he worked with Hocking NDT Ltd, Allen-Bradley IAP Ltd and Simplatroll Ltd in England as a Senior Engineer, after he received his Ph.D. Degree from Cambridge University. He is with the School of Electrical and Electronic Engineering, Nanyang Technological University (NTU), Singapore, and is a Senior Member of IEEE.

Dr Luo has published seven teaching textbooks and 218 technical papers in IEEE-Transactions, IEE-Proceedings and other international journals, and various international conferences. His present research interest is in the Digital Power Electronics and DC and AC motor drives with computerized artificial intelligent control (AIC) and digital signal processing (DSP), and DC/AC inverters, AC/DC rectifiers, AC/AC and DC/DC converters.

Dr. Luo was the Chief Editor of the international journal, *Power Supply Technologies and Applications*. He is currently the Associate Editor of the *IEEE Transactions* on both *Power Electronics* and *Industrial Electronics*.

Dr. Hong Ye (IEEE S'00-M'03) received a Bachelor Degree (the first class with honors) in 1995 and a Master Engineering Degree from Xi'an Jiaotong University, China in 1999. She completed her Ph.D. degree in Nanyang Technological University (NTU), Singapore.

From 1995 to 1997, Dr. Ye was with the R&D Institute, XIYI Company Ltd, China, as a Research Engineer. She joined the NTU in 2003.

Dr. Ye is an IEEE Member and has authored seven teaching textbooks and written more than 48 technical papers published

xii Preface

in *IEEE-Transactions*, *IEE-Proceedings*, other international journals and various international conferences. Her research interests are in the areas of DC/DC converters, signal processing, operations research and structural biology.

Muhammad H. Rashid is employed by the University of Florida as Professor of Electrical and Computer Engineering, and Director of the UF/UWF Joint Program in Electrical and Computer Engineering. Dr. Rashid received a B.Sc. Degree in Electrical Engineering from the Bangladesh University of Engineering and Technology, and M.Sc. and Ph.D. Degrees from the University of Birmingham in the UK. Previously, he worked as Professor of Electrical Engineering and was the Chair of the Engineering Department at Indiana University, Purdue University at Fort Wayne. He has also worked as Visiting Assistant Professor of Electrical Engi-

neering at the University of Connecticut, Associate Professor of Electrical Engineering at Concordia University (Montreal, Canada), Professor of Electrical Engineering at Purdue University Calumet, Visiting Professor of Electrical Engineering at King Fahd University of Petroleum and Minerals (Saudi Arabia), as a Design and Development Engineer with Brush Electrical Machines Ltd (UK), a Research Engineer with Lucas Group Research Centre (UK), and as a Lecturer and Head of Control Engineering Department at the Higher Institute of Electronics (Malta).

Dr. Rashid is actively involved in teaching, researching, and lecturing in power electronics. He has published 14 books and more than 100 technical papers. He received the 2002 IEEE Educational Activity Award (EAB) Meritorious Achievement Award in Continuing Education with the following citation "for contributions to the design and delivery of continuing education in power electronics and computer-aided-simulation". From 1995 to 2002, Dr. Rashid was an ABET Program Evaluator for Electrical Engineering and he is currently an Engineering Evaluator for the Southern Association of Colleges and Schools (SACS, USA). He has been elected as an IEEE-Industry Applications Society (IAS) as a Distinguished Lecturer. He is the Editor-in-Chief of the *Power Electronics and Applications Series* with CRC Press.

Our acknowledgment goes to the executive editor for this book.

### Chapter 1

### Introduction

Power electronics and conversion technology are exciting and challenging professions for anyone who has a genuine interest in, and aptitude for, applied science and mathematics. Actually, the existing knowledge in power electronics is not completed. All switching power circuits including the power DC/DC converters and switched DC/AC pulse-width-modulation (PWM) inverters (DC: direct current; AC: alternative current) perform in high-frequency switching state. Traditional knowledge did not fully consider the pumping–filtering process, resonant process and voltage-lift operation. Therefore, the existing knowledge cannot well describe the characteristics of switching power circuits including the power DC/DC converters. To reveal the disadvantages of the existing knowledge, we have to review the traditional analog Power Electronics in this Chapter.

### 1.1 HISTORICAL REVIEW

Power Electronics and conversion technology are concerned to systems that produce, transmit, control and measure electric power and energy. To describe the characteristics of power systems, various measuring parameters so-called the factors are applied. These important concepts are the power factor (PF), power-transfer efficiency  $(\eta)$ , ripple factor (RF) and total harmonic distortion (THD). For long-time education and engineering practice, we know that the traditional power systems have been successfully described by these parameters.

These important concepts will be introduced in the following sections.

### 1.1.1 WORK, ENERGY AND HEAT

Work, W, and energy, E, are measured by the unit "**joule**". We usually call the kinetic energy "work", and the stored or static energy potential "energy". Work and energy

can be transferred to *heat*, which is measured by "calorie". Here is the relationship (Joule-Lenz law):

$$1 \text{ joule} = 0.24 \text{ calorie}$$

or

$$1 \text{ calorie} = 4.18 \text{ joules}$$

In this mechanism, there is a relationship between power, P, and work, W, and/or energy, E:

$$W = \int P \, \mathrm{d}t \quad E = \int P \, \mathrm{d}t$$

and

$$P = \frac{\mathrm{d}}{\mathrm{d}t}W$$

$P = \frac{\mathrm{d}}{\mathrm{d}t}E$

Power *P* is measured by the unit "watt", and

1 joule = 1 watt

$$\times$$

1 second

or

$$1 \text{ watt} = 1 \text{ joule}/1 \text{ second}$$

### 1.1.2 DC AND AC EQUIPMENT

Power supplies are sorted into two main groups: DC and AC. Corresponding equipment are sorted into DC and AC kinds as well, e.g. DC generators, AC generators, DC motors, AC motors, etc.

### **DC Power Supply**

A DC power supply has parameters: voltage (amplitude)  $V_{\rm dc}$  and ripple factor (RF). A DC power supply can be a battery, DC generator or DC/DC converter.

### **AC Power Supply**

An AC power supply has parameters: voltage (amplitude, root-mean-square (rms or RMS) value and average value), frequency (f or  $\omega$ ), phase angle ( $\phi$  or  $\theta$ ) and total harmonic distortion (THD). An AC power supply can be an AC generator, transformer or DC/AC inverter. An AC voltage can be presented as follows:

$$v(t) = V_{\rm p} \sin(\omega t - \theta) = \sqrt{2} V_{\rm rms} \sin(\omega t - \theta)$$

(1.1)

where v(t) is the measured AC instantaneous voltage;  $V_p$ , the peak value of the voltage;  $V_{rms}$ , the rms value of the voltage;  $\omega$ , the angular frequency,  $\omega = 2\pi f$ ; f, the supply frequency, e.g.  $f = 50 \,\text{Hz}$  and  $\theta$ , the delayed phase angle.

### **1.1.3** Loads

Power supply source transfers energy to load. If the characteristics of a load can be described by a linear differential equation, we call the load a linear load. Otherwise, we call the load a non-linear load (i.e. the diodes, relays and hysteresis-elements that cannot be described by a linear differential equation). Typical linear loads are sorted into two categories: passive and dynamic loads.

### **Linear Passive Loads**

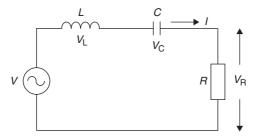

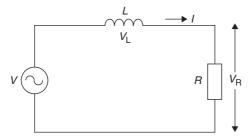

Linear passive loads are resistance (R), inductance (L) and capacitance (C). All these components satisfy linear differential equations. If the circuit current is I as shown in Figure 1.1, from Ohm's law we have:

$$V_{\rm R} = RI \tag{1.2}$$

$$V_{\rm L} = L \frac{\mathrm{d}I}{\mathrm{d}t} \tag{1.3}$$

$$V_{\rm C} = \frac{1}{C} \int I \, \mathrm{d}t \tag{1.4}$$

$$V = V_{R} + V_{L} + V_{C} = RI + L\frac{dI}{dt} + \frac{1}{C} \int I \, dt$$

(1.5)

Equations (1.2)–(1.5) are all linear differential equations.

### **Linear Dynamic Loads**

Linear dynamic loads are DC and AC back electromagnetic force (EMF). All these components satisfy differential equation operation.

The back EMF of a DC motor is DC back EMF with DC voltage that is proportional to the field flux and armature running speed:

$$EMF = k\Phi\omega \tag{1.6}$$

where k is the DC machine constant;  $\Phi$ , the field flux and  $\omega$ , the machine running speed in rad/s.

Figure 1.1 An L-R-C circuit.

The back EMF of an AC motor is AC back EMF with AC voltage that is proportional to the field flux and rotor running speed.

### 1.1.4 IMPEDANCE

If an R–L–C circuit supplied by a voltage source with mono-frequency ( $\omega = 2\pi f$ ) sinusoidal waveform as shown in Figure 1.1, we can simplify the differential equation (1.5) into an algebraic equation using the concept "impedance", Z:

$$V = ZI \tag{1.7}$$

We define impedance Z as follows:

$$Z = R + j\omega L - j\frac{1}{\omega C} = R + jX = |Z|\angle\theta$$

(1.8)

where

$$X = \omega L - \frac{1}{\omega C}$$

$$|Z| = \sqrt{R^2 + \left(\omega L - \frac{1}{\omega C}\right)^2} \tag{1.9}$$

$$\theta = \tan^{-1} \left( \frac{\omega L - \frac{1}{\omega C}}{R} \right) \tag{1.10}$$

in which  $\theta$  is the conjugation phase angle. The real part of an impedance Z is defined as resistance R, and the imaginary part of an impedance Z is defined as reactance X. The reactance has two components: the positive part is called *inductive reactance*  $j\omega L$  and the negative part is called *capacitive reactance*  $-j/\omega C$ . The power delivery has been completed only across resistance. The reactance can only store energy and shift phase angle. No power is consumed on reactance, which produces reactive power and spoils power delivery.

From Ohm's law, we can get the vector current (I) from vector voltage (V) and impedance (Z):

$$I = \frac{V}{Z} = \frac{V}{R + j\omega L - j\frac{1}{\omega C}} = |I|\angle\theta$$

(1.11)

Most industrial application equipment are of inductive load. For example, an R–L circuit is supplied by a sinusoidal voltage V, and it is shown in Figure 1.2. The impedance Z obtained is:

$$Z = R + j\omega L = R + jX = |Z| \angle \theta \tag{1.12}$$

**Figure 1.2** An L–R circuit.

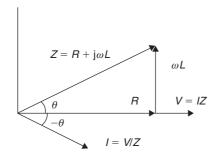

Figure 1.3 The vector diagram of an L-R circuit.

with

$$|Z| = \sqrt{R^2 + (\omega L)^2}$$

and  $\theta = \tan^{-1} \left(\frac{\omega L}{R}\right)$

The conjugation angle  $(\theta)$  is a positive value. The corresponding vector diagram is shown in Figure 1.3.

We also get the current as follows:

$$I = \frac{V}{Z} = \frac{V}{R + j\omega L} = |I| \angle -\theta \tag{1.13}$$

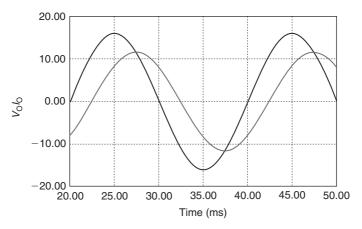

Select the supply voltage V as reference vector with phase angle zero. The current vector is delayed than the voltage by the conjugation angle  $\theta$ . The corresponding vector diagram is also shown in Figure 1.3. The voltage and current waveforms are shown in Figure 1.4.

### **1.1.5 Powers**

There are various powers such as apparent power (or complex power), S, power (or real power), P, and reactive power, Q.

Figure 1.4 The corresponding voltage and current waveforms.

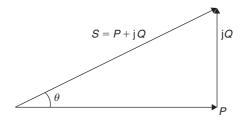

**Figure 1.5** The power vector diagram of an L–R circuit.

### **Apparent Power S**

We define the apparent power S as follows:

$$S = VI^* = P + jQ \tag{1.14}$$

### Power P

Power or real power *P* is the real part of the apparent power *S*:

$$P = S\cos\theta = I^2R \tag{1.15}$$

### Reactive Power Q

Reactive power Q is the imaginary part of the apparent power S:

$$Q = S\sin\theta = I^2X\tag{1.16}$$

Referring to the R-L circuit in Figure 1.2, we can show the corresponding power vectors in Figure 1.5.

### 1.2 TRADITIONAL PARAMETERS

Traditional parameters used in power electronics are the power factor (PF), power-transfer efficiency  $(\eta)$ , total harmonic distortion (THD) and ripple factor (RF). Using these parameters has successfully described the characteristics of power (generation, transmission, distribution, protection and harmonic analysis) systems and most drive (AC and DC motor drives) systems.

### 1.2.1 Power Factor (PF)

Power factor is defined by the ratio of real power *P* over the apparent power *S*:

$$PF = \frac{P}{S} = \cos \theta = \frac{I^2 R}{V I^*} = \frac{IR}{V}$$

(1.17)

Figure 1.5 is used to illustrate the power factor (PF).

### 1.2.2 Power-Transfer Efficiency $(\eta)$

Power-transfer efficiency ( $\eta$ ) is defined by the ratio of output power  $P_{\rm O}$  over the input power  $P_{\rm in}$ :

$$\eta = \frac{P_{\rm O}}{P_{\rm in}} \tag{1.18}$$

The output power  $P_{\rm O}$  is received by the load, end user. The input power  $P_{\rm in}$  is usually generated by the power supply source. Both the input power  $P_{\rm in}$  and output power  $P_{\rm O}$  are real power.

### 1.2.3 TOTAL HARMONIC DISTORTION (THD)

A periodical AC waveform usually possesses various order harmonics. Since the instantaneous value is periodically repeating in fundamental frequency f (or  $\omega = 2\pi f$ ), the corresponding spectrum in the frequency domain consists of discrete peaks at the frequencies nf (or  $n\omega = 2n\pi f$ ), where  $n = 1, 2, 3, ... \infty$ . The first-order component (n = 1) corresponds to the fundamental component  $V_1$ . The total harmonic distortion (THD) is defined by the ratio of the sum of all higher-order harmonics over the fundamental harmonic  $V_1$ :

$$THD = \frac{\sqrt{\sum_{n=2}^{\infty} V_n^2}}{V_1} \tag{1.19}$$

where all  $V_n$   $(n = 1, 2, 3, ... \infty)$  are the corresponding rms values.

### 1.2.4 RIPPLE FACTOR (RF)

A DC waveform usually possesses DC component  $V_{\rm dc}$  and various high-order harmonics. These harmonics make the variation (ripple) of the DC waveform. Since the instantaneous value is periodically repeating in fundamental frequency f (or  $\omega = 2\pi f$ ), the corresponding spectrum in the frequency domain consists of discrete peaks at the frequencies nf (or  $n\omega = 2n\pi f$ ), where  $n = 0, 1, 2, 3, ... \infty$ . The zeroth-order component (n = 0) corresponds to the DC component  $V_{\rm dc}$ . The ripple factor (RF) is defined by the ratio of the sum of all higher-order harmonics over the DC component  $V_{\rm dc}$ :

$$RF = \frac{\sqrt{\sum_{n=1}^{\infty} V_n^2}}{V_{\rm dc}} \tag{1.20}$$

where all  $V_n$   $(n = 1, 2, 3, ... \infty)$  are the corresponding rms values.

### 1.2.5 APPLICATION EXAMPLES

In order to describe the fundamental parameters better, we provide some examples as the application of these parameters in this section.

### Power and Efficiency $(\eta)$

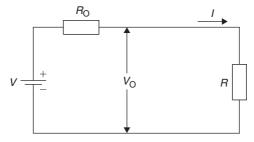

A pure resistive load R supplied by a DC voltage source V with internal resistance  $R_{\rm O}$  is shown in Figure 1.6. The current I is obtained by the calculation expression:

$$I = \frac{V}{R + R_{\rm O}} \tag{1.21}$$

The output voltage  $V_{\rm O}$  is:

$$V_{\rm O} = \frac{R}{R + R_{\rm O}} V \tag{1.22}$$

**Figure 1.6** A pure resistive load supplied by a DC source with internal resistance.

The output power  $P_{\rm O}$  is:

$$P_{\rm O} = I^2 R = \frac{R}{(R + R_{\rm O})^2} V^2 \tag{1.23}$$

The power-transfer efficiency  $(\eta)$  is:

$$\eta = \frac{P_{\rm O}}{P_{\rm in}} = \frac{I^2 R}{IV} = \frac{R}{R + R_{\rm O}} \tag{1.24}$$

In order to obtain maximum output power, we can determine the condition by differentiating Equation (1.23):

$$\frac{d}{dR}P_{O} = \frac{d}{dR} \left[ \frac{R}{(R+R_{O})^{2}} V^{2} \right] = 0$$

(1.25)

$$\frac{1}{(R+R_{\rm O})^2} - \frac{2R}{(R+R_{\rm O})^3} = 0$$

Hence,

$$R = R_{\rm O} \tag{1.26}$$

When  $R = R_0$ , we obtain the maximum output power:

$$P_{\text{O-max}} = \frac{V^2}{4R_{\text{O}}} \tag{1.27}$$

and the corresponding efficiency:

$$\eta = \frac{R}{R + R_{\rm O}}|_{R = R_{\rm O}} = 0.5 \tag{1.28}$$

This example shows that the power and efficiency are different concepts. When load R is equal to the internal resistance  $R_{\rm O}$ , maximum output power is obtained with the efficiency  $\eta = 50\%$ . Vice versa, if we would like to obtain maximum efficiency  $\eta = 1$  or 100%, it requires load R is equal to infinite (if the internal resistance  $R_{\rm O}$  cannot be equal to zero). It causes the output power, which is equal to zero. The interesting relation is listed below:

Maximum output power

$$\eta = 50\%$$

Output power = 0  $\eta = 100\%$

The second case corresponds to the open circuit. Although the theoretical calculation illustrates the efficiency  $\eta = 1$  or 100%, no power is delivered from source to load.

Another situation is R = 0 that causes the output current is its maximum value  $I_{\text{max}} = V/R_{\text{O}}$  as (1.21) and:

Output power =

$$0 \quad \eta = 0\%$$

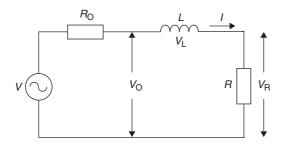

### An R-L Circuit Calculation

Figure 1.7 shows a single-phase sinusoidal power supply source with the internal resistance  $R_{\rm O} = 0.2 \,\Omega$ , supplying an R-L circuit with  $R = 1 \,\Omega$  and  $L = 3 \,\text{mH}$ . The source voltage is a sinusoidal waveform with the voltage 16 V (rms voltage) and frequency  $f = 50 \,\text{Hz}$ :

$$V = 16\sqrt{2}\sin 100\pi t \,V \tag{1.29}$$

The internal impedance is:

$$Z_{\rm O} = R_{\rm O} = 0.2 \,\Omega$$

(1.30)

The impedance of load is:

$$Z = 1 + j100\pi \times 3m = 1 + j0.94 = 1.3724 \angle 43.23^{\circ}\Omega$$

(1.31)

$$Z + Z_{\rm O} = 1.2 + j0.94 = 1.524 \angle 38.073^{\circ}\Omega$$

(1.32)

The current is:

$$I = \frac{V}{Z + Z_{\rm O}} = 10.5\sqrt{2}\sin(100\pi t - 38.073^{\circ})\,\text{A}$$

(1.33)

The output voltage across the R–L circuit is:

$$V_{\rm O} = ZI = 14.4\sqrt{2}\sin(100\pi t - 5.16^{\circ})\,\text{A} \tag{1.34}$$

The apparent power S across the load is:

$$S = V_0 I^* = 14.4 \times 10.5 = 151.3 \text{ VA}$$

(1.35)

The real output power  $P_{O}$  across the load is:

$$P_{\rm O} = P_{\rm R} = I^2 R = 10.5^2 \times 1 = 110.25 \,\text{W}$$

(1.36)

Figure 1.7 An R-L circuit supplied by an AC source with internal resistance.

The real input power  $P_{\text{in}}$  is:

$$P_{\rm in} = I^2 (R + R_{\rm O}) = 10.5^2 \times 1.2 = 132.3 \,\text{W}$$

(1.37)

Therefore, the power factor *PF* of the load is:

$$PF = \frac{P_0}{S} = \cos \theta = \cos 43.23 = 0.73 \text{ (lagging)}$$

(1.38)

The corresponding reactive power Q is:

$$Q = S \times \sin \theta = 151.3 \times \sin 43.23 = 103.63 \text{ VAR}$$

(1.39)

Thus, the power-transfer efficiency  $(\eta)$  is:

$$\eta = \frac{P_{\rm R}}{P_{\rm in}} = \frac{110.25}{132.3} = 0.833\tag{1.40}$$

Other way to calculate the efficiency  $(\eta)$  is:

$$\eta = \frac{R}{R + R_{\rm O}} = \frac{1}{1.2} = 0.833$$

To obtain the maximum output power we have to choose same condition as in Equation (1.26),

$$R = R_{\rm O} = 0.2\,\Omega\tag{1.41}$$

The maximum output power  $P_{\rm O}$  is:

$$P_{\text{O-max}} = \frac{V^2}{4R_{\text{O}}} = \frac{16^2}{4 \times 0.2} = 320 \,\text{W}$$

(1.42)

with the efficiency  $(\eta)$  is:

$$\eta = 0.5 \tag{1.43}$$

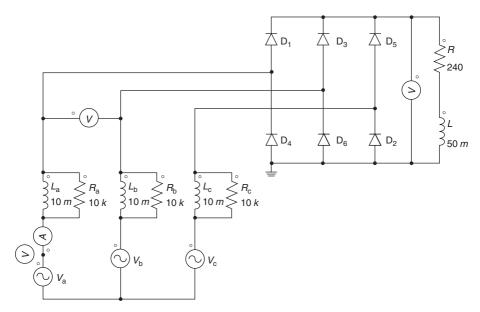

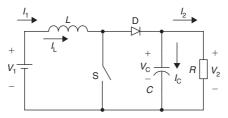

### A Three-Phase Circuit Calculation

Figure 1.8 shows a balanced three-phase sinusoidal power supply source supplying a full-wave diode-bridge rectifier to an R–L load. Each single-phase source is a sinusoidal voltage source with the internal impedance  $10 \, \mathrm{k}\Omega$  plus  $10 \, \mathrm{mH}$ . The load is an R–L circuit with  $R = 240 \, \Omega$  and  $L = 50 \, \mathrm{mH}$ . The source phase voltage has the amplitude  $16 \, \mathrm{V}$  (its rms value is  $16/\sqrt{2} = 11.3 \, \mathrm{V}$ ) and frequency  $f = 50 \, \mathrm{Hz}$ . It is presented as:

$$V = 16\sin 100\pi t \,V \tag{1.44}$$

**Figure 1.8** A three-phase source supplies a diode full-wave rectifier to an R–L load.

The internal impedance is:

$$Z_{\rm O} = \frac{10,000}{\rm j} = \frac{10,000 \times \rm j}{100\pi \times 10 \, m} = \frac{10,000 \times \rm j}{10,000 + \rm j} = \frac{10,000 \times \rm j}{10000 \times \rm j} = \frac{10,000 \times \rm j}{100000 \times \rm j} = \frac{10,000 \times \rm j}{100000 \times \rm j} = \frac{10,000 \times \rm j}{100000 \times \rm j$$

The impedance of the load is:

$$Z = 240 + j100\pi \times 50 \, m = 240 + j15.708 = 240.5 \angle 3.74^{\circ} \Omega \tag{1.46}$$

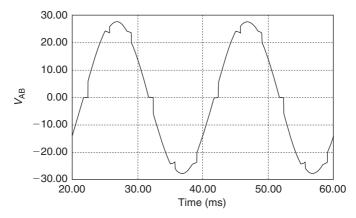

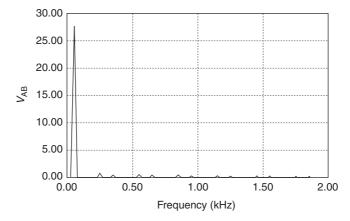

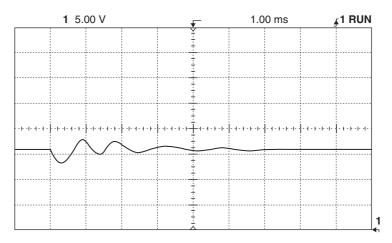

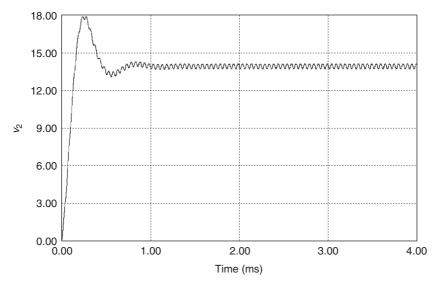

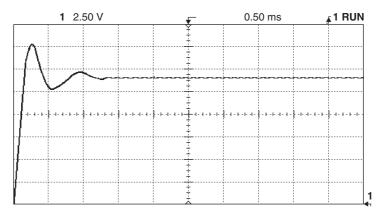

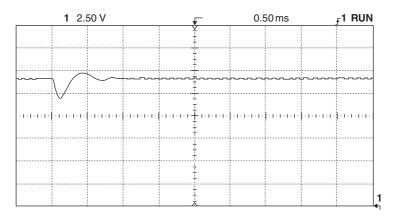

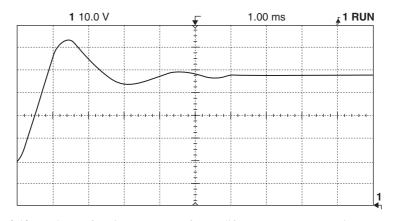

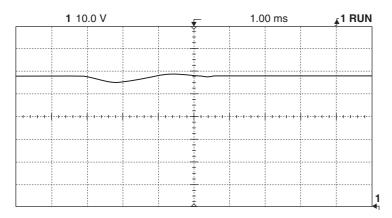

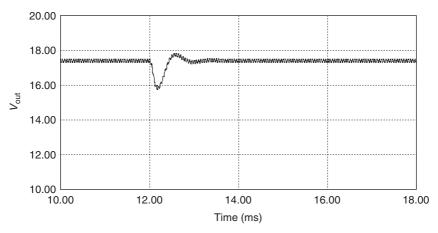

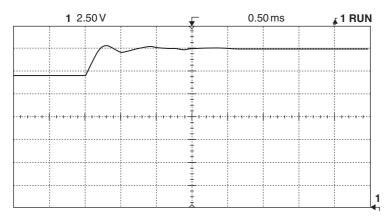

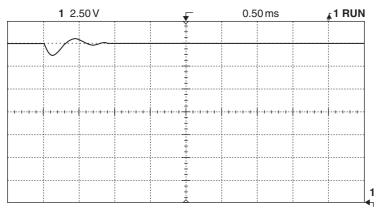

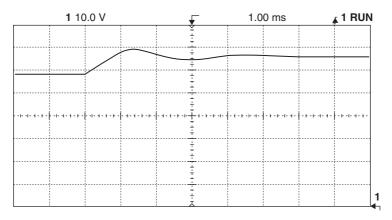

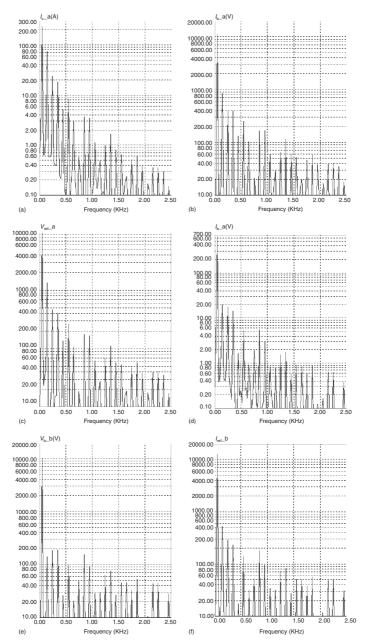

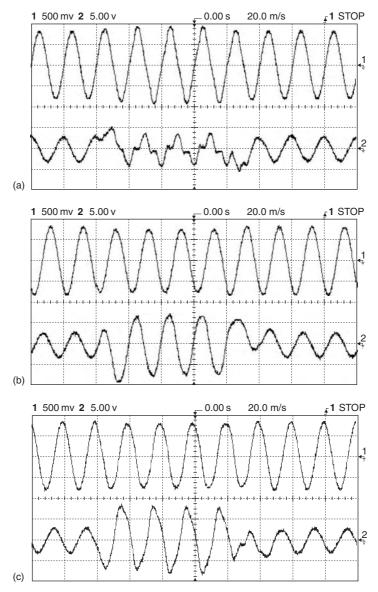

The bridge input AC line-to-line voltage is measured and shown in Figure 1.9. It can be seen that the input AC line voltage is distorted. After the fast Fourier transform (FFT) analysis, the corresponding spectrums can be obtained as shown in Figure 1.10 for the bridge input AC line voltage waveforms.

The input line–line voltage fundamental value and the harmonic peak voltages for *THD* calculation are listed in Table 1.1.

Using formula (1.19) to calculate the *THD*, we have,

$$THD = \frac{\sqrt{\sum_{n=2}^{\infty} v_{AB-n}^2}}{v_{AB-1}} = \frac{\sqrt{0.737^2 + 0.464^2 + 0.566^2 + 0.422^2 + \cdots}}{27.62} \times 100\% = 4.86\%$$

(1.47)

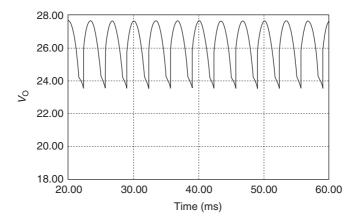

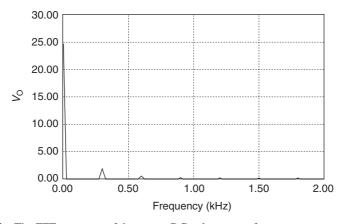

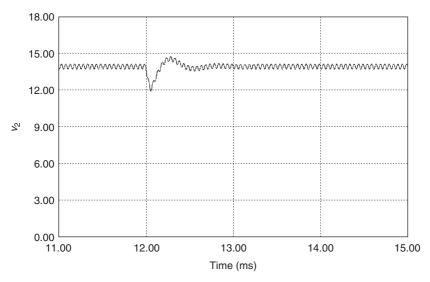

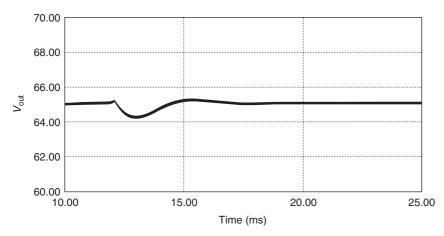

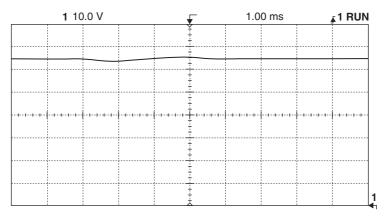

We measured the output DC voltage in Figure 1.11. It can be seen that the DC voltage has ripple. After FFT analysis, we obtain the corresponding spectrums as shown in Figure 1.12 for the output DC voltage waveforms.

**Figure 1.9** The input line AC voltage waveform.

**Figure 1.10** The FFT spectrum of the input line AC voltage waveform.

Table 1.1

The harmonic peak voltages of the distorted the input line-line voltage

| Order no. | Fundamental 27.62 | 5     | 7     | 11    | 13    | 17    | 19               |

|-----------|-------------------|-------|-------|-------|-------|-------|------------------|

| Volts     |                   | 0.737 | 0.464 | 0.566 | 0.422 | 0.426 | 0.34             |

| Order no. | 23                | 25    | 29    | 31    | 35    | 37    | <i>THD</i> 4.86% |

| Volts     | 0.297             | 0.245 | 0.196 | 0.164 | 0.143 | 0.119 |                  |

**Figure 1.11** The output DC voltage waveform.

**Figure 1.12** The FFT spectrum of the output DC voltage waveform.

The output DC load voltage and the harmonic peak voltages for *RF* calculation are listed in Table 1.2.

Using formula (1.20) to calculate the RF, we have,

$$RF = \frac{\sqrt{\sum_{n=1}^{\infty} v_{\text{O-n}}^2}}{v_{\text{O-dc}}} = \frac{\sqrt{1.841^2 + 0.5^2 + 0.212^2 + 0.156^2 + \cdots}}{26.15 \times \sqrt{2}} \times 100\% = 5.24\%$$

(1.48)

From input phase voltage and current, the partial power factor  $(PF_p)$  is obtained,

$$PF_{p} = \cos \theta = 0.9926 \tag{1.49}$$

Table 1.2

The harmonic peak voltages of the DC output voltage with ripple

| Order no.<br>Volts |       |       |       |       |       |       |       |       |

|--------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| VOITS              | 20.13 | 1.841 | 0.500 | 0.212 | 0.156 | 0.151 | 0.134 | 5.24% |

Table 1.3

The harmonic peak voltages of the input phase current

|                      | Fundamental 0.12024 | 5<br>2.7001e–2  |                 | 13<br>5.9472e-3 | 17<br>4.5805e-3 | 19<br>3.2942e-3       |

|----------------------|---------------------|-----------------|-----------------|-----------------|-----------------|-----------------------|

| Order no.<br>Amperes | 23<br>2.3524e-3     | 25<br>1.8161e-3 | 31<br>9.7928e–4 | 33              | 37<br>5.9850e–4 | Total <i>PF</i> 0.959 |

Table 1.4

The harmonic peak voltages of the output DC current

| Order no. | DC (0) | 6       | 12      | 18      | 24      | 30      | 36      | η     |

|-----------|--------|---------|---------|---------|---------|---------|---------|-------|

| Amperes   | 0.109  | 7.14e-3 | 1.64e-3 | 5.72e-4 | 3.49e-4 | 2.85e-4 | 2.19e-4 | 0.993 |

The input phase current peak value and the higher-order harmonic current peak values are listed in Table 1.3.

$$I_{\text{a-1}} = \frac{0.12024}{\sqrt{2}} = 0.085 \,\text{A}$$

$I_{\text{a-rms}} = \sqrt{\sum_{n=0}^{\infty} i_n^2} = 0.088 \,\text{A}$

Total power factor

$$PF_{\text{total}} = \frac{I_{\text{a-1}}}{I_{\text{a-rms}}} \cos \theta = \frac{0.085}{0.088} \times 0.9926 = 0.959$$

The average DC output load current and the higher-order harmonic current peak values are listed in Table 1.4.

$$V_{\text{O-rms}} = \sqrt{\sum_{n=0}^{\infty} v_n^2} = 26.186 \,\text{V}$$

$I_{\text{O-rms}} = \sqrt{\sum_{n=0}^{\infty} i_n^2} = 0.1096 \,\text{A}$

The efficiency  $(\eta)$  is:

$$\eta = \frac{P_{\rm dc}}{P_{\rm ac}} = \frac{V_{\rm O-dc}I_{\rm O-rms}}{V_{\rm O-rms}I_{\rm O-rms}} \times 100\% = \frac{26.15 \times 0.10896}{26.186 \times 0.1096} \times 100\% = 99.28\% \quad (1.50)$$

From this example, we fully demonstrated the four important parameters: power factor (PF), power-transfer efficiency  $(\eta)$ , total harmonic distortion (THD) and ripple factor (RF). Usually, these four parameters are enough to describe the characteristics of a power supply system.

### 1.3 MULTIPLE-QUADRANT OPERATIONS AND CHOPPERS

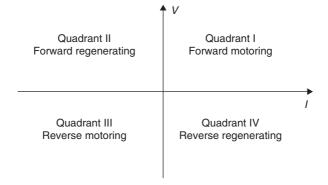

Multiple-quadrant operation is required in industrial applications. For example, a DC motor can perform forward running or reverse running. The motor armature voltage and armature current are both positive during forward starting process. We usually call it the forward motoring operation or "Quadrant I" operation. The motor armature voltage is still positive and its armature current is negative during forward braking process. This state is called the forward regenerative braking operation or "Quadrant II" operation.

Analogously, the motor armature voltage and current are both negative during reverse starting process. We usually call it the reverse motoring operation or "Quadrant III" operation. The motor armature voltage is still negative and its armature current is positive during reverse braking process. This state is called the reverse regenerative braking operation or "Quadrant IV" operation.

Referring to the DC motor operation states, we can define the multiple-quadrant operation as below:

Quadrant I operation: Forward motoring; voltage and current are positive;

Quadrant II operation: Forward regenerative braking; voltage is positive and

current is negative;

Quadrant III operation: Reverse motoring; voltage and current are negative;

Quadrant IV operation: Reverse regenerative braking; voltage is negative and current is positive.

The operation status is shown in the Figure 1.13. Choppers can convert a fixed DC voltage into various other voltages. The corresponding chopper is usually called which quadrant operation chopper, e.g. the first-quadrant chopper or "A"-type chopper. In the

**Figure 1.13** The four-quadrant operation.

following description we use the symbols  $V_{\rm in}$  for fixed voltage,  $V_{\rm p}$  for chopped voltage and  $V_{\rm O}$  for output voltage.

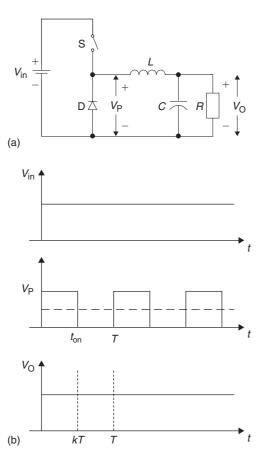

### 1.3.1 THE FIRST-QUADRANT CHOPPER

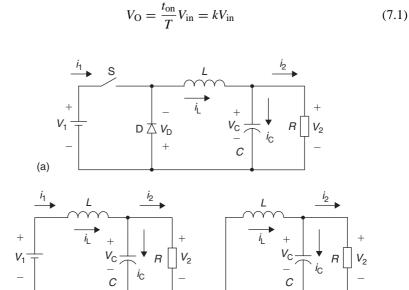

The first-quadrant chopper is also called "A"-type chopper and its circuit diagram is shown in Figure 1.14(a) and the corresponding waveforms are shown in Figure 1.14(b). The switch S can be some semiconductor devices such as BJT, integrated gate bipolar transistors (IGBT) and power MOS field effected transistors (MOSFET). Assuming all parts are ideal components, the output voltage is calculated by the formula:

Figure 1.14 The first-quadrant chopper. (a) Circuit diagram and (b) voltage waveforms.

where T is the repeating period (T = 1/f), in which f is the chopping frequency;  $t_{\rm on}$  is the switch-on time and k is the conduction duty cycle  $(k = t_{\rm on}/T)$ .

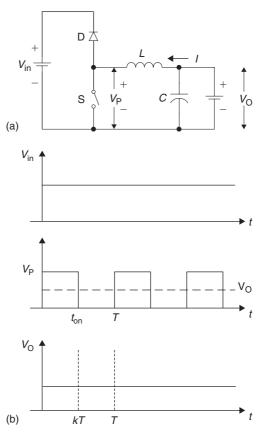

### 1.3.2 THE SECOND-QUADRANT CHOPPER

The second-quadrant chopper is also called "B"-type chopper and its circuit diagram is shown in Figure 1.15(a) and the corresponding waveforms are shown in Figure 1.15(b). The output voltage can be calculated by the formula:

$$V_{\rm O} = \frac{t_{\rm off}}{T} V_{\rm in} = (1 - k) V_{\rm in}$$

(1.52)

where T is the repeating period (T = 1/f), in which f is the chopping frequency;  $t_{\rm off}$  is the switch-off time  $(t_{\rm off} = T - t_{\rm on})$  and k is the conduction duty cycle  $(k = t_{\rm on}/T)$ .

**Figure 1.15** The second-quadrant chopper. (a) Circuit diagram and (b) voltage waveforms.

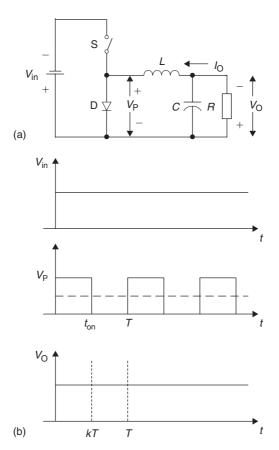

### 1.3.3 THE THIRD-QUADRANT CHOPPER

The third-quadrant chopper is shown in Figure 1.16(a) and the corresponding waveforms are shown in Figure 1.16(b). All voltage polarities are defined in the figure. The output voltage (absolute value) can be calculated by the formula:

$$V_{\rm O} = \frac{t_{\rm on}}{T} V_{\rm in} = k V_{\rm in} \tag{1.53}$$

where  $t_{\rm on}$  is the switch-on time and k is the conduction duty cycle  $(k = t_{\rm on}/T)$ .

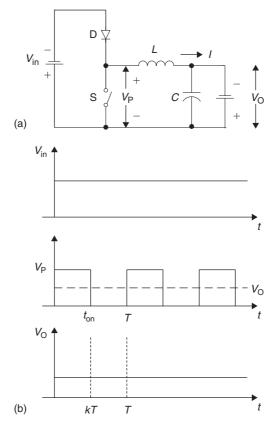

### 1.3.4 THE FOURTH-QUADRANT CHOPPER

The fourth-quadrant chopper is shown in Figure 1.17(a) and the corresponding waveforms are shown in Figure 1.17(b). All voltage polarities are defined in the figure.

Figure 1.16 The third-quadrant chopper. (a) Circuit diagram and (b) voltage waveforms.

Figure 1.17 The fourth-quadrant chopper. (a) Circuit diagram and (b) voltage waveforms.

The output voltage (absolute value) can be calculated by the formula:

$$V_{\rm O} = \frac{t_{\rm off}}{T} V_{\rm in} = (1 - k) V_{\rm in}$$

(1.54)

where  $t_{\rm off}$  is the switch-off time ( $t_{\rm off} = T - t_{\rm on}$ ) and k is the conduction duty cycle ( $k = t_{\rm on}/T$ ).

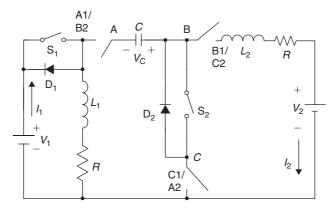

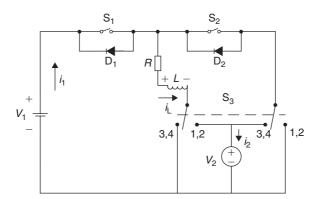

### 1.3.5 THE FIRST-SECOND-QUADRANT CHOPPER

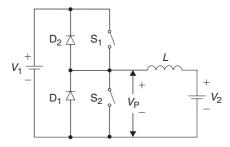

The first–second-quadrant chopper is shown in Figure 1.18. Dual-quadrant operation is usually requested in the system with two voltage sources  $V_1$  and  $V_2$ . Assume the condition  $V_1 > V_2$ , the inductor L is the ideal component. During Quadrant I operation,  $S_1$  and  $D_2$  work, and  $S_2$  and  $D_1$  are idle. Vice versa, during Quadrant II operation,  $S_2$  and  $S_1$  and  $S_2$  are idle. The relation between the two voltage sources can

Figure 1.18 The first–second quadrant chopper.

**Figure 1.19** The third–fourth quadrant chopper.

be calculated by the formula:

$$V_2 = \begin{cases} kV_1 & \text{Quadrant I operation} \\ (1-k)V_1 & \text{Quadrant II operation} \end{cases}$$

(1.55)

where *k* is the conduction duty cycle  $(k = t_{on}/T)$ .

### 1.3.6 THE THIRD-FOURTH-QUADRANT CHOPPER

The third–fourth-quadrant chopper is shown in Figure 1.19. Dual-quadrant operation is usually requested in the system with two voltage sources  $V_1$  and  $V_2$ . Both the voltage polarities are defined in the figure, we just concentrate on their absolute values in analysis and calculation. Assume the condition  $V_1 > V_2$ , the inductor L is the ideal component. During Quadrant III operation,  $S_1$  and  $D_2$  work, and  $S_2$  and  $D_1$  are idle. Vice versa, during Quadrant IV operation,  $S_2$  and  $D_1$  work, and  $S_1$  and  $D_2$  are idle. The relation between the two voltage sources can be calculated by the formula:

$$V_2 = \begin{cases} kV_1 & \text{Quadrant III operation} \\ (1-k)V_1 & \text{Quadrant IV operation} \end{cases}$$

(1.56)

where *k* is the conduction duty cycle ( $k = t_{on}/T$ ).

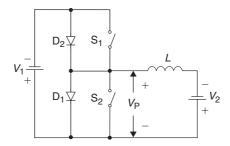

Figure 1.20 The four-quadrant chopper.

Table 1.5

The switches' and diodes' status for four-quadrant operation

| Switch or diode  | Quadrant I   | Quadrant II  | Quadrant III | Quadrant IV  |

|------------------|--------------|--------------|--------------|--------------|

| $\overline{S_1}$ | Works        | Idle         | Idle         | Works        |

| $D_1$            | Idle         | Works        | Works        | Idle         |

| $S_2$            | Idle         | Works        | Works        | Idle         |

| $D_2$            | Works        | Idle         | Idle         | Works        |

| $S_3$            | Idle         | Idle         | On           | Idle         |

| $D_3$            | Idle         | Idle         | Idle         | On           |

| $S_4$            | On           | Idle         | Idle         | Idle         |

| $D_4$            | Idle         | On           | Idle         | Idle         |

| Output           | $V_2+, I_2+$ | $V_2+, I_2-$ | $V_2-, I_2-$ | $V_2-, I_2+$ |

### 1.3.7 THE FOUR-QUADRANT CHOPPER

The four-quadrant chopper is shown in Figure 1.20. The input voltage is positive, output voltage can be either positive or negative. The status of switches and diodes for the operation are given in Table 1.5. The output voltage can be calculated by the formula:

$$V_{2} = \begin{cases} kV_{1} & \text{Quadrant I operation} \\ (1-k)V_{1} & \text{Quadrant II operation} \\ -kV_{1} & \text{Quadrant III operation} \\ -(1-k)V_{1} & \text{Quadrant IV operation} \end{cases}$$

(1.57)

### 1.4 DIGITAL POWER ELECTRONICS: PUMP CIRCUITS AND CONVERSION TECHNOLOGY

Besides choppers there are more and more switching circuits applied in industrial applications. These switching circuits work in discrete-time state. Since high-frequency switching circuits can transfer the energy in high power density and high efficiency, they have been applied on more and more branches of power electronics. The energy

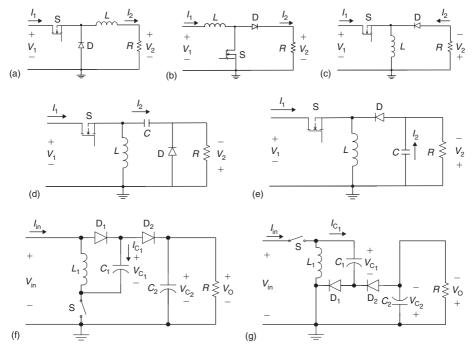

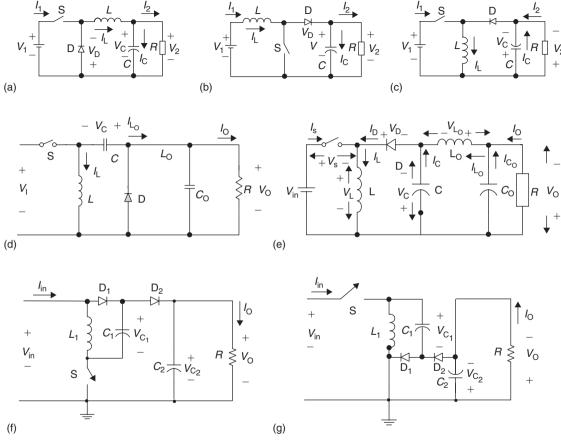

**Figure 1.21** Pumping circuits: (a) buck pump, (b) boost pump, (c) buck-boost pump, (d) positive Luo-pump, (e) negative Luo-pump, (f) positive super Luo-pump and (g) negative super Luo-pump.

and power delivery from source to the users are not in continuous mode. Therefore, digital control theory has to be applied in this area.

All conversion technologies (such as pumping circuits, AC/DC rectifiers, DC/AC inverters, DC/DC converters and AC/AC (and/or AC/DC/AC) converters) are theoretically based on the switching circuit. It is urgent to investigate the digital power electronics rather than the traditional analog control applied in analog power electronics. The following typical circuits are examples of switching circuits working in the discrete-time mode.

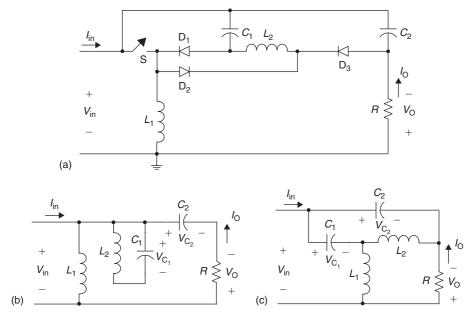

### 1.4.1 Fundamental Pump Circuits

All power DC/DC converters have pumping circuit. Pumping circuits are typical switching circuits to convert the energy from an energy source to energy-storage components in discrete state. Each pump has a switch S and an energy-storage component that can be an inductor L. The switch S turns on once in a period T=1/f, where f is the switching frequency. Therefore, the energy transferred in a period is a certain value that can be called energy quantum. Figure 1.21 shows seven (buck, boost, buck–boost, positive Luo, negative Luo, positive super Luo and negative super Luo) pumping circuits, which are used in the corresponding DC/DC converters.

All pumping circuits are switching circuits that convert the energy from source to load or certain energy-storage component in discrete state. Each pumping circuit has at least one switch and one energy-store element, for example an inductor. The switch is controlled by a PWM signal with the period T (T=1/f, where f is the switching frequency) and the conduction duty cycle k. The energy was absorbed from the energy source to the inductor during switching-on period kT. The energy stored in the inductor will be delivered to next stage during switching-off period (1-k)T. Therefore, the energy from the source to users is transferred in discrete-time mode.

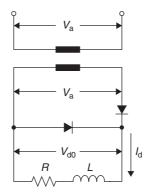

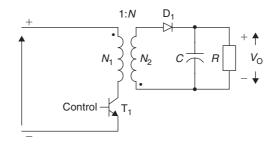

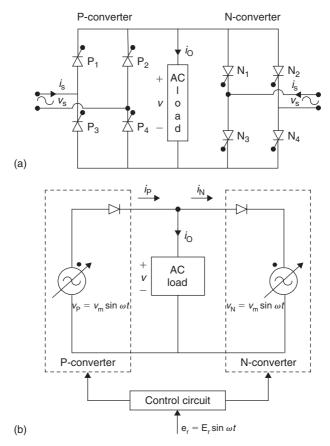

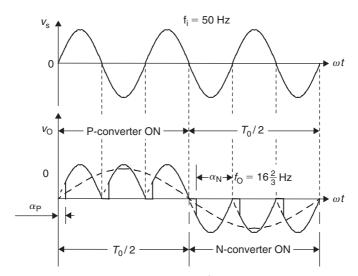

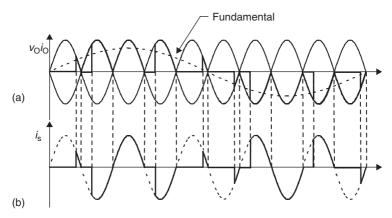

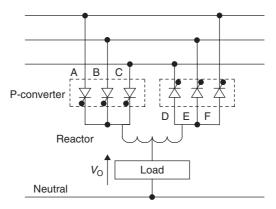

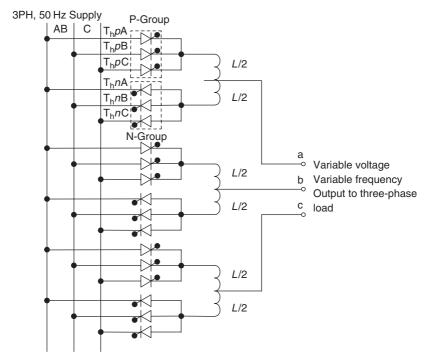

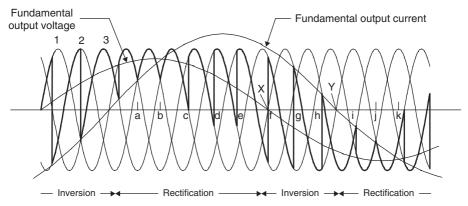

### 1.4.2 AC/DC RECTIFIERS

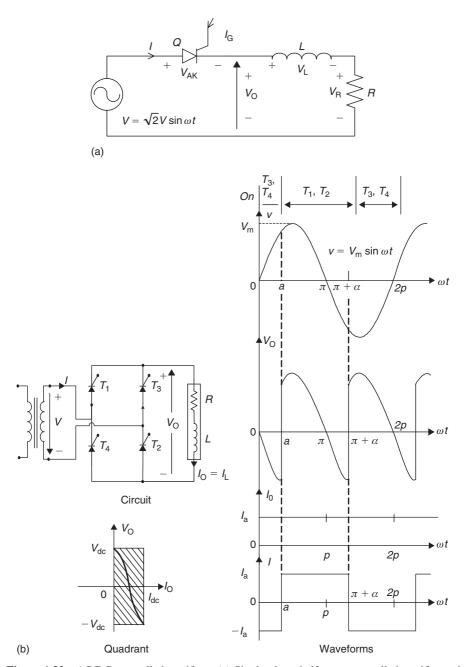

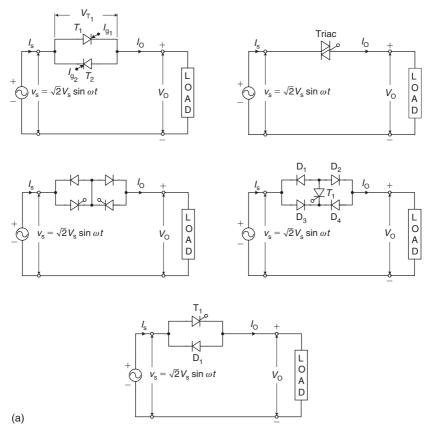

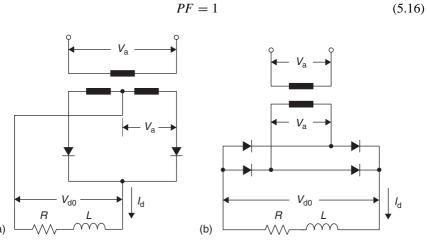

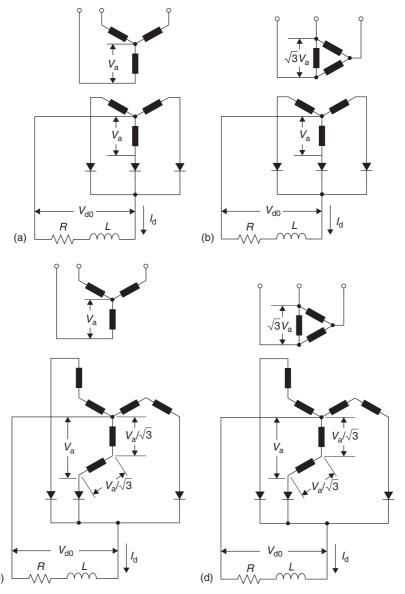

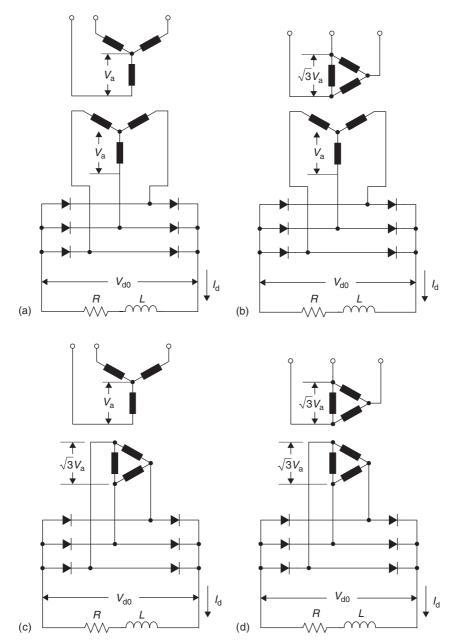

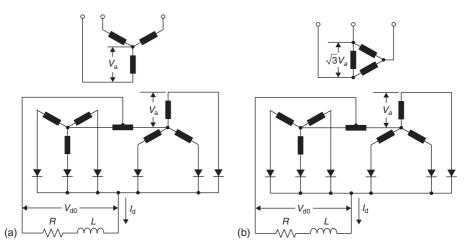

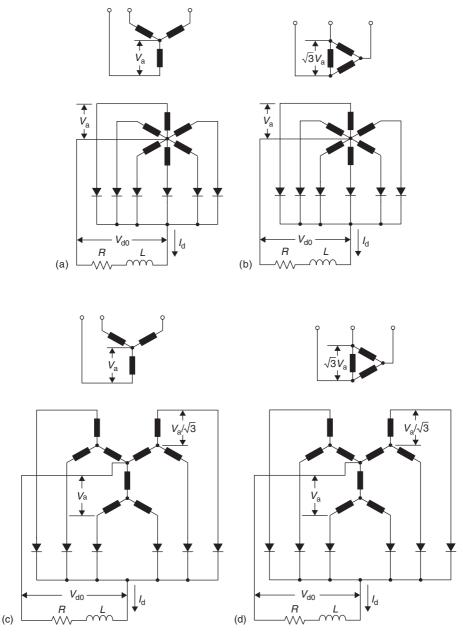

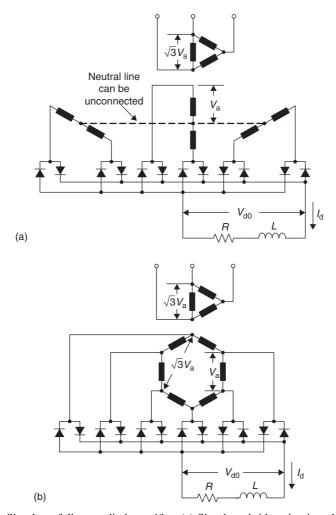

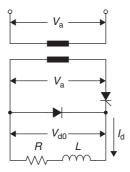

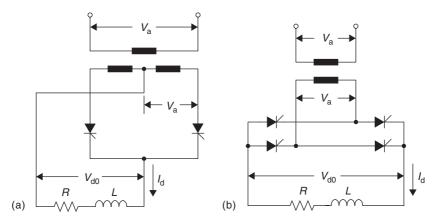

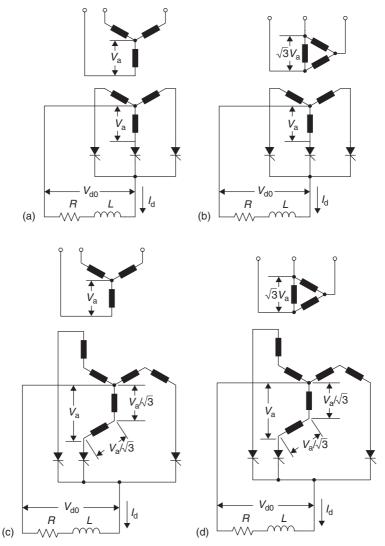

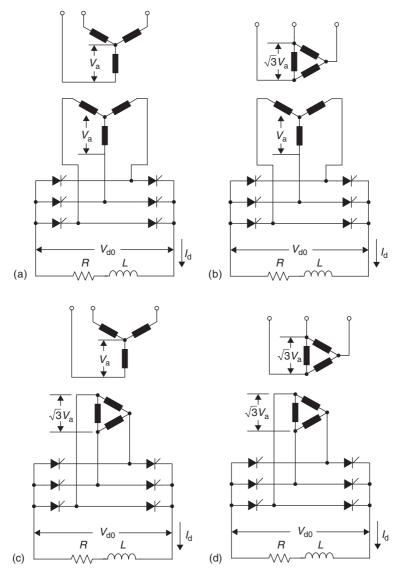

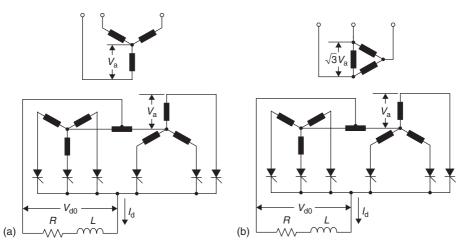

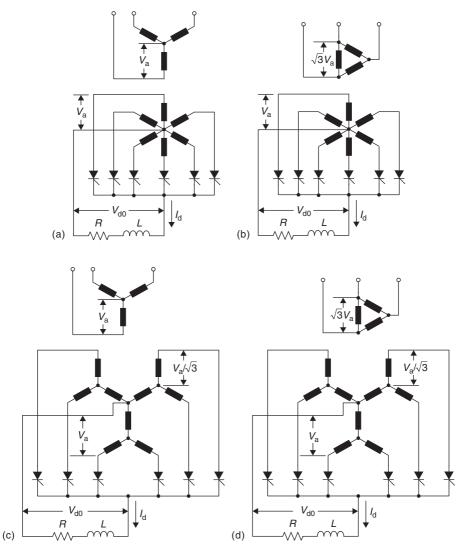

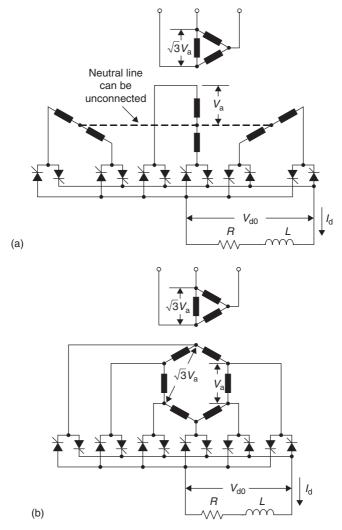

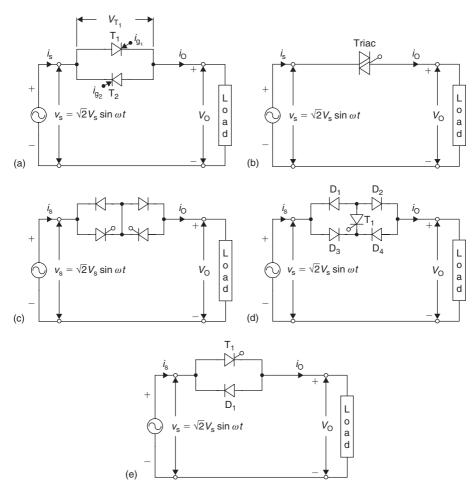

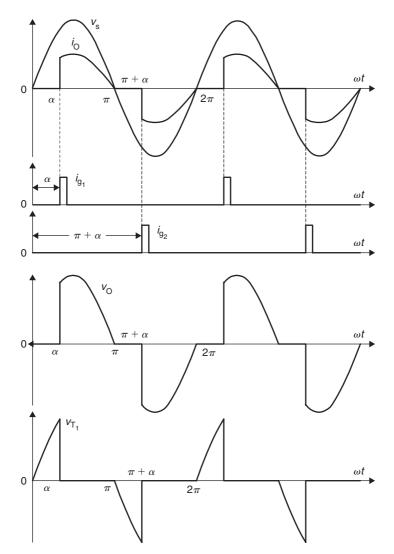

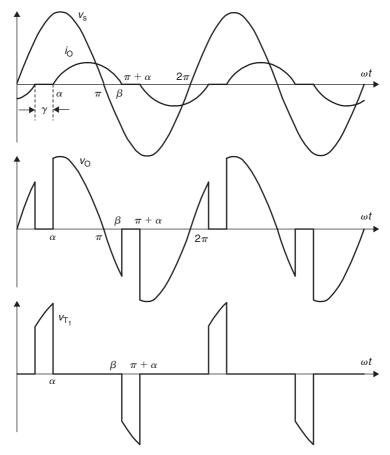

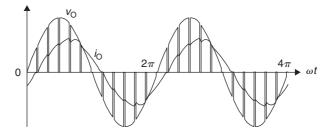

All AC/DC controlled rectifiers are switching circuits. Figure 1.22 shows few rectifier circuits (namely single-phase half-wave, single-phase full-wave, three-phase half-wave, and three-phase half-wave controlled rectifier), which are used in the corresponding AC/DC converters.

All AC/DC rectifier circuits are switching circuits that convert the energy from an AC source to load in discrete state. Each AC/DC controlled rectifier has at least one switch. For example, a half-wave controlled thyristor (silicon controlled rectifier, SCR) rectifier has one SCR switch. The switch is controlled by a firing pulse signal with the repeating period T (T = 1/f, where f is the switching frequency for the single-phase rectifiers) and the conduction period. The energy was delivered from the energy source to the load during switching-on period. The energy is blocked during switching-off period. Therefore, the energy from the source to loads is transferred in discrete-time mode.

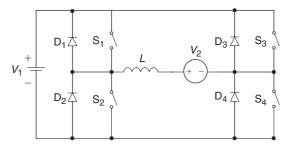

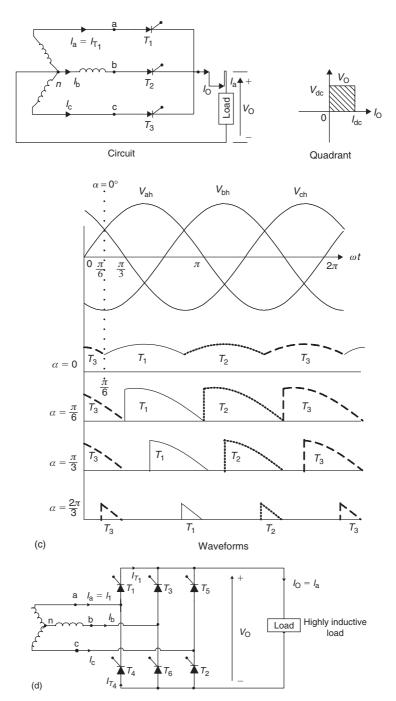

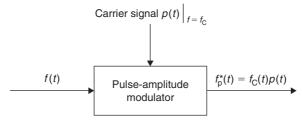

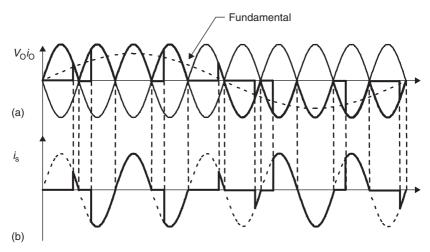

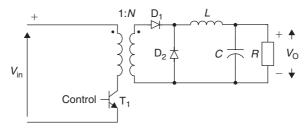

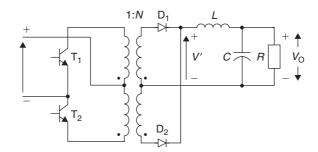

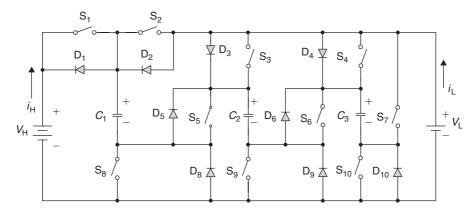

### 1.4.3 DC/AC PWM INVERTERS

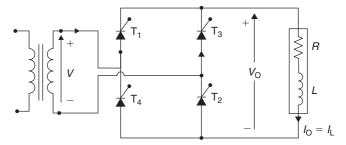

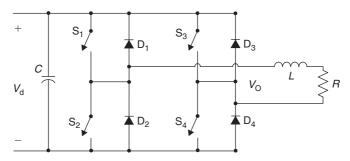

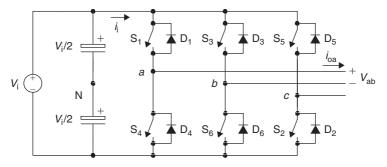

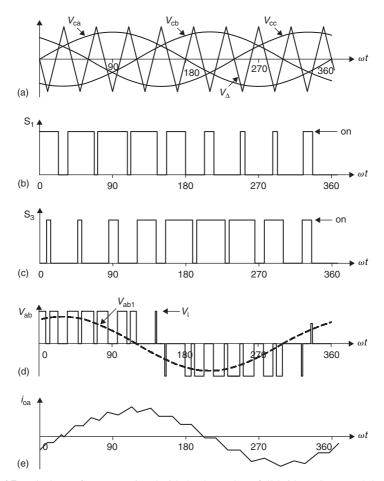

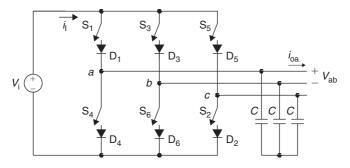

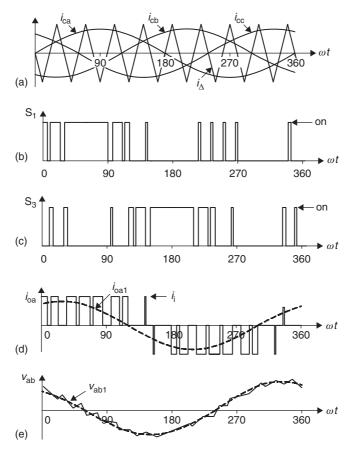

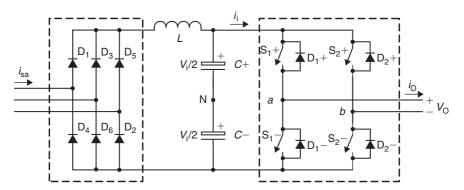

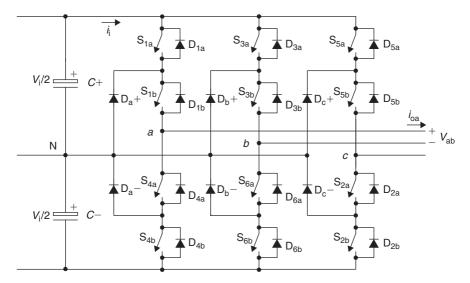

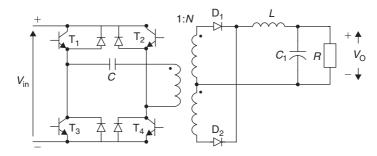

All DC/AC inverters are switching circuits. Figure 1.23 shows three (single-phase, three-phase, three-phase) DC/AC PWM inverter circuits, which are used in the corresponding DC/AC inverters.

All DC/AC PWM inverter circuits are switching circuits that convert the energy from a DC source to load in discrete state. Each DC/AC inverter has multiple switches. The switches are controlled by PWM signals with the repeating period T (T = 1/f, where f is the switching frequency for the single-phase rectifiers) and the modulation ratio m. The energy was delivered from the energy source to the load during switching-on period. The energy is blocked during switching-off period. Therefore, the energy from the source to loads is transferred in discrete-time mode.

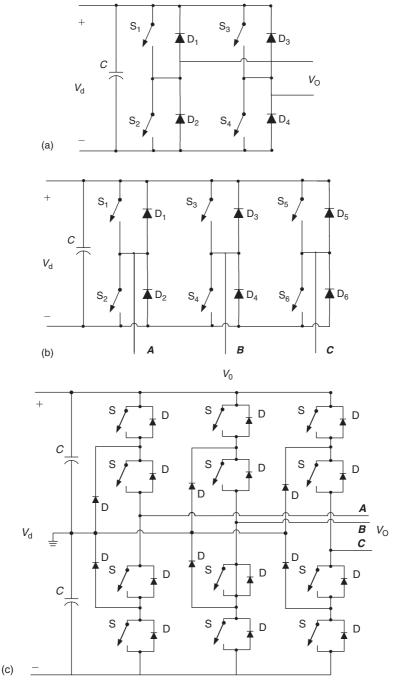

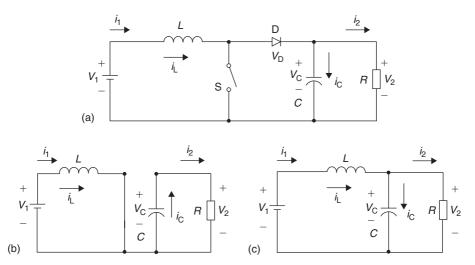

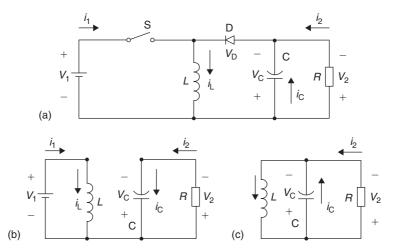

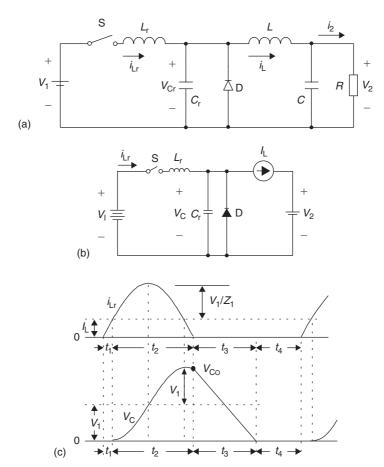

### 1.4.4 DC/DC CONVERTERS

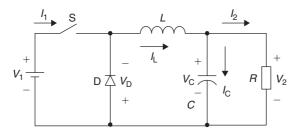

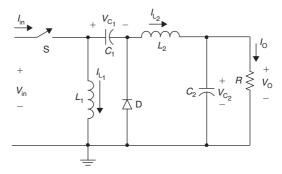

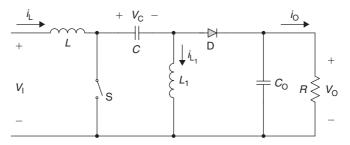

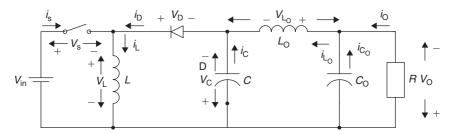

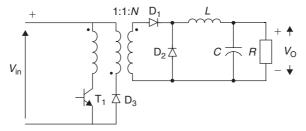

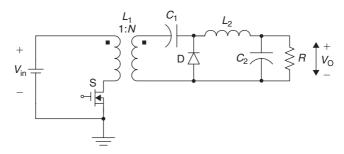

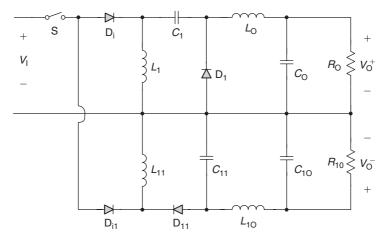

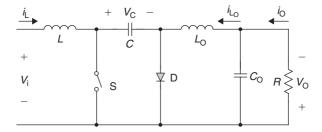

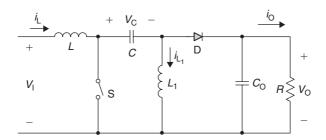

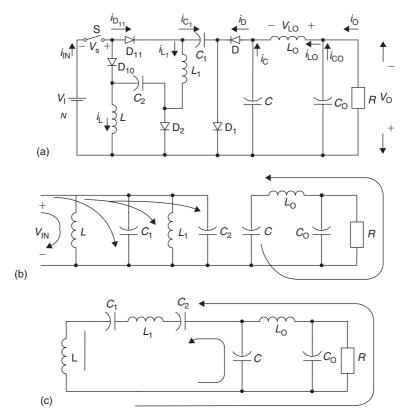

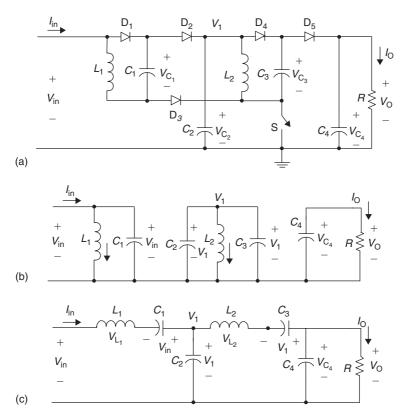

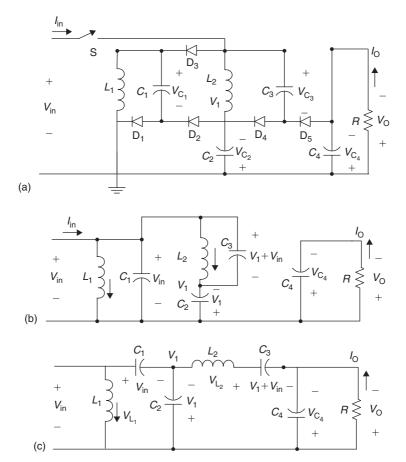

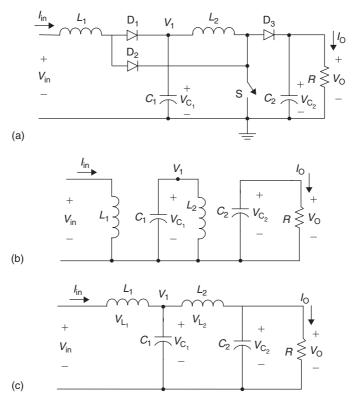

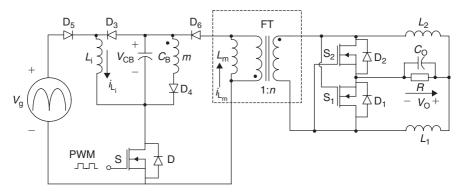

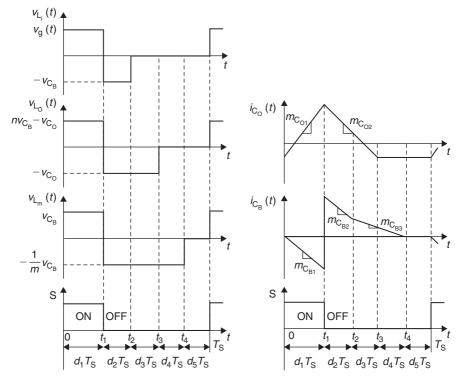

All DC/DC converters are switching circuits. Figure 1.24 shows seven (buck, boost, buck–boost, positive output Luo, negative output Luo, positive output super-lift Luo and negative output super-lift Luo converters) DC/DC converter circuits.

**Figure 1.22** AC/DC controlled rectifiers: (a) Single-phase half-wave controlled rectifier and (b) single-phase full-wave controlled rectifier.

Figure 1.22 (contd.) (c) Three-phase half-wave controlled rectifier and (d) three-phase half-wave controlled rectifier.

$\begin{tabular}{ll} Figure~1.23 & DC/AC~PWM~inverters:~(a)~single-phase,~(b)~three-phase~and~(c)~three-level three-phase. \end{tabular}$

**Figure 1.24** DC/DC converters: (a) buck converter, (b) boost converter, (c) buck—boost converter, (d) positive output Luo-converter, (e) negative output Luo-converter, (f) positive output super-lift Luo-converter and (g) negative output super-lift Luo-converter.

All DC/DC converters' circuits are switching circuits that convert the energy from a DC source to load in discrete state. Each power DC/DC converter has at least one pumping circuit and filter. The switch is controlled by a PWM signal with the repeating period T (T = 1/f, f is the switching frequency) and the conduction duty cycle k. The energy was delivered from the energy source to the load via the pumping circuit during switching-on period kT. The energy is blocked during switching-off period (1 - k)T. Therefore, the energy from the source to loads is transferred in discrete-time mode.

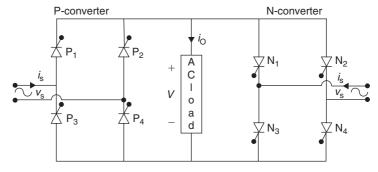

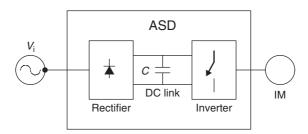

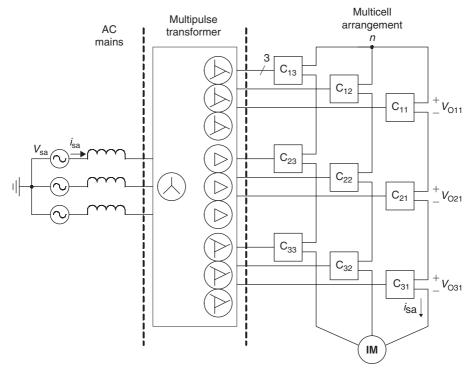

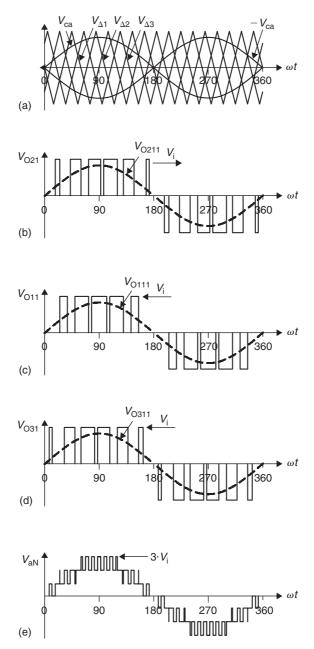

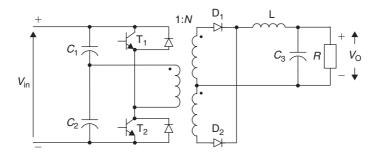

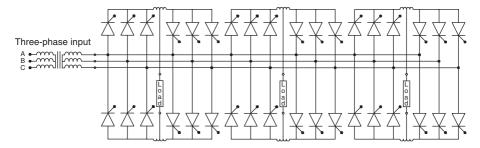

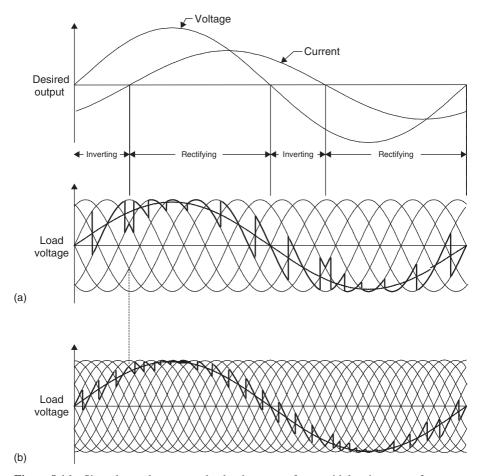

### 1.4.5 AC/AC CONVERTERS

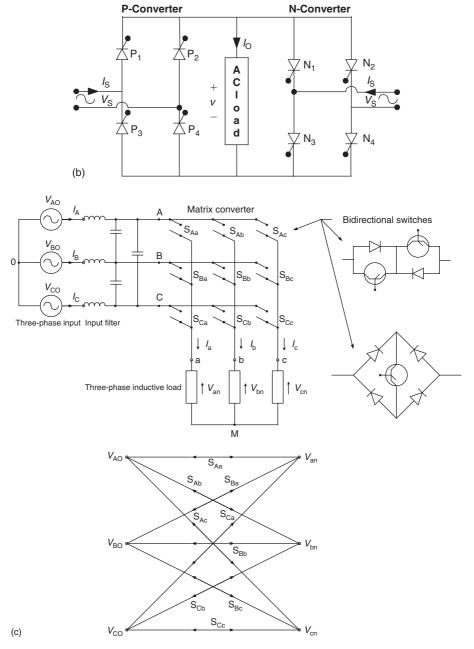

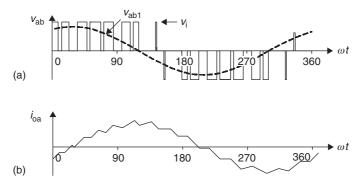

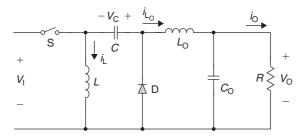

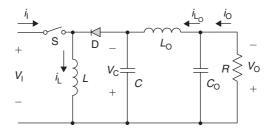

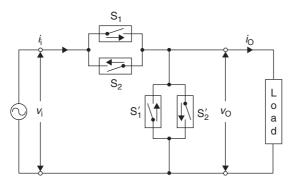

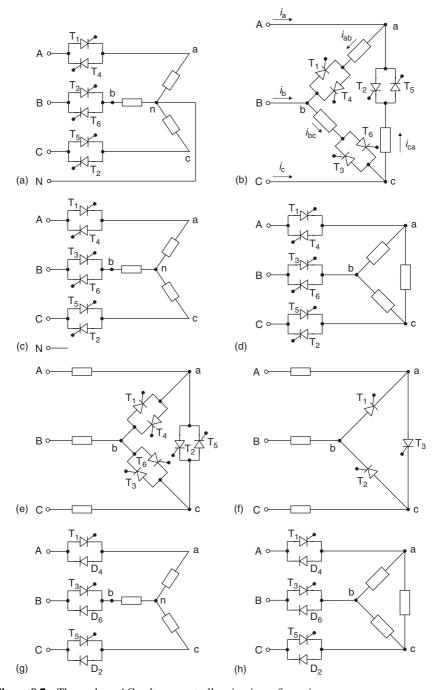

All AC/AC converters are switching circuits. Figure 1.25 shows three (single-phase amplitude regulation, single-phase and three-phase) AC/AC converter circuits.

All AC/AC converter circuits are switching circuits that convert the energy from an AC source to load in discrete state. Each AC/AC converter has multiple switches. The

**Figure 1.25** AC/AC converters. (a) Single-phase amplitude regulation.

**Figure 1.25** (contd.) (b) Single phase AC/AC cyclo converter and (c) three-phase AC/AC matrix converter.

switches are controlled by PWM signals with the repeating period T (T=1/f, where f is the switching frequency for the single-phase rectifiers) and the modulation factor. The energy was delivered from the energy AC source to the load during switching-on period. The energy is blocked during switching-off period. Therefore, the energy from the source to loads is transferred in discrete-time mode.

# 1.5 SHORTAGE OF ANALOG POWER ELECTRONICS AND CONVERSION TECHNOLOGY

Analog power electronics use the traditional parameters: power factor (PF), efficiency  $(\eta)$ , total harmonic distortion (THD) and ripple factor (RF) to describe the characteristics of a power system or drive system. It is successfully applied for more than a century. Unfortunately, all these factors are not available to be used to describe the characteristics of switching circuits: power DC/DC converters and other high-frequency switching circuits.

Power DC/DC converters have been usually equipped by a DC power supply source, pump circuit, filter and load. The load can be of any type, but most investigations are concerned to resistive load *R* and back EMF or battery. It means that the input and output voltages are nearly pure DC voltages with very small ripple, e.g. output voltage variation ratio is usually less than 1%. In this case, the corresponding *RF* is less than 0.001, which is always ignored.

Since all powers are real power without reactive power jQ, we cannot use power factor (PF) to describe the energy-transferring process.

As only DC components exists without harmonics in input and output voltage, *THD* is not available to be used to describe the energy-transferring process and waveform distortion.

To simplify the research and analysis, we usually assume the condition without power losses during power-transferring process to investigate power DC/DC converters. Consequently, the efficiency  $\eta=1$  or 100% for most of description of power DC/DC investigation. Otherwise, efficiency  $(\eta)$  must be considered for special investigations regarding the power losses.

In general conditions, all four factors are not available to apply in the analysis of power DC/DC converters. This situation lets the designers of power DC/DC converters confusing for very long time. People would like to find other new parameters to describe the characteristics of power DC/DC converters.

There is no correct theory and the corresponding parameters to be used for all switching circuits till 2004. Dr. Fang Lin Luo and Dr. Hong Ye firstly created new theory and parameters to describe the characteristics of all switching circuits in 2004.

Energy storage in power DC/DC converters has been paid attention long time ago. Unfortunately, there is no clear concept to describe the phenomena and reveal the relationship between the stored energy and the characteristics of power DC/DC converters. We have theoretically defined a new concept, energy factor (EF), and researched the relations between EF and the mathematical modeling of power DC/DC converters.

EF is a new concept in power electronics and conversion technology, which thoroughly differs from the traditional concepts such as power factor (PF), power-transfer efficiency  $(\eta)$ , total harmonic distortion (THD) and ripple factor (RF). EF and the subsequential other parameters can illustrate the system stability, reference response and interference recovery. This investigation is very helpful for system design and DC/DC converters characteristics foreseeing.

# 1.6 POWER SEMICONDUCTOR DEVICES APPLIED IN DIGITAL POWER ELECTRONICS

High-frequency switching equipment can convert high power, and its power density is proportional to the applying frequency. For example, the volume of a 1-kW transformer working in 50 Hz has the size 4 in.  $\times$  3 in.  $\times$  2.5 in. = 30 in.  $^3$  The volume of a 2.2-kW flat-transformer working in 50 kHz has the size 1.5 in.  $\times$  0.3 in.  $\times$  0.2 in. = 0.09 in.  $^3$  The difference between them is about 1000 times.

To be required by the industrial applications, power semiconductor devices applied in digital power electronics have been improved in recent decades. Their power, voltage and current rates increase in many times, the applying frequency is greatly enlarged. For example, the working frequency of an IGBT increases from 50 to 200 kHz, and the working frequency of a MOSFET increases from 5 to 20 MHz.

The power semiconductor devices usually applied in industrial applications are as follows:

- diodes:

- SCRs (thyristors);

- GTOs (gate turn-off thyristors);

- BTs (power bipolar transistors);

- IGBTs (insulated gate bipolar transistors);

- MOSFETs (power MOS field effected transistors);

- MSCs (MOS controlled thyristors).

All devices except diode are working in switching state. Therefore, the circuits consists them to be called switching circuits and work in discrete state.

### **FURTHER READING**

- Luo F. L. and Ye H., Advanced DC/DC Converters, CRC Press LLC, Boca Raton, Florida, USA, 2004. ISBN: 0-8493-1956-0.

- 2. Luo F. L., Ye H. and Rashid M. H., DC/DC conversion techniques and nine series luo-converters. In *Power Electronics Handbook*, Rashid M. H. and Luo F. L. *et al.* (Eds), Academic Press, San Diego, USA, 2001, pp. 335–406.

- 3. Mohan N., Undeland T. M. and Robbins W. P., *Power Electronics: Converters, Applications and Design*, 3rd edn., John Wiley & Sons, New York, USA, 2003.

Rashid, M. H., Power Electronics: Circuits, Devices and Applications, 2nd edn., Prentice-Hall, USA, 1993.

- Nilsson J. W. and Riedel S. A., *Electric Circuits*, 5th edn. Addison-Wesley Publishing Company, Inc., New York, USA, 1996.

- Irwin J. D. and Wu C. H., Basic Engineering Circuit Analysis, 6th edn., John Willey & Sons, Inc., New York, USA, 1999.

- 7. Carlson A. B., Circuits, Brooks/Cole Thomson Learning, New York, USA, 2000.

- 8. Johnson D. E., Hilburn J. L., Johnson J. R. and Scott P. D., *Basic Electric Circuit Analysis*, 5th edn., John Willey & Sons, Inc. New York, USA, 1999.

- 9. Grainger J. J. and Stevenson Jr. W. D., *Power System Analysis*, McGraw-Hill International Editions, New York, USA, 1994.

- Machowski J., Bialek J. W. and Bumby J. R., Power System Dynamics and Stability, John Wiley & Sons, New York, USA, 1997.

- 11. Luo F. L. and Ye H., Energy Factor and Mathematical Modelling for Power DC/DC Converters, IEE-Proceedings on EPA, vol. 152, No. 2, 2005, pp. 233–248.

- Luo F. L. and Ye H., Mathematical Modeling for Power DC/DC Converters, Proceedings of the IEEE International Conference POWERCON'2004, Singapore, 21–24/11/2004, pp. 323–328.

- Padiyar K. R., Power System Dynamics, Stability and Control, John Wiley & Sons, New York, USA, 1996.

# Chapter 2

# **Energy Factor** (*EF*) and **Sub-sequential Parameters**

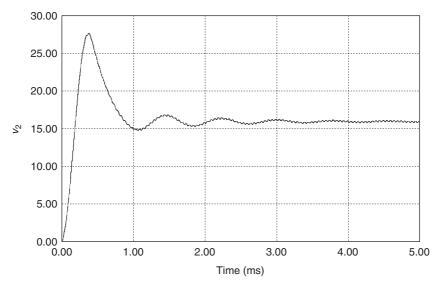

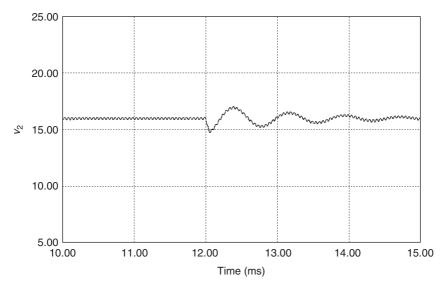

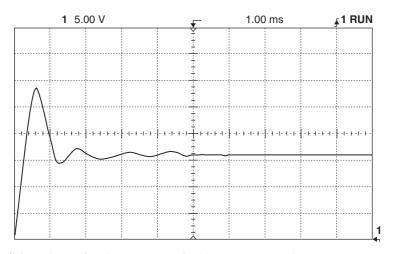

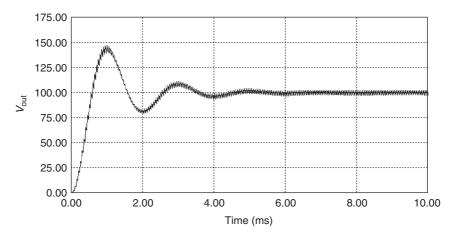

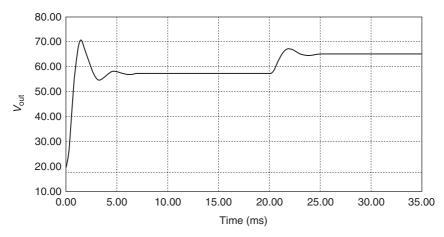

Switching power circuits, such as power DC/DC converters, power pulse-width-modulation (PWM) DC/AC inverters, soft-switching converters, resonant rectifiers and soft-switching AC/AC matrix converters, have pumping—filtering process, resonant process and/or voltage-lift operation. These circuits consist of several energy-storage elements. They are likely an energy container to store certain energy during performance. The stored energy will vary if the working condition changes. For example, once the power supply is on, the output voltage starts from zero since the container is not filled. The transient process from one steady state to another depends on the pumping energy and stored energy. Same reason affects the interference discovery process since the stored energy, similar to inertia, affects the impulse response.

All switching power circuits work under the switching condition with high frequency f. It is thoroughly different from traditional continuous work condition. The obvious technical feature is that all parameters perform in a period T=1/f, then gradually change period-by-period. The switching period T is the clue to investigate all switching power circuits. Catching the clue, we can define many brand new concepts (parameters) to describe the characteristics of switching power circuits. These new factors fill in the blanks of the knowledge in power electronics and conversion technology. We will carefully discuss the new concepts and their applications in this chapter.

### 2.1 INTRODUCTION

From the introduction in previous chapter, we have got the impression of the four important factors: power factor (PF), power transfer efficiency  $(\eta)$ , total harmonic distortion (THD) and ripple factor (RF) that well describe the characteristics of power

systems. Unfortunately, all these factors are not available to be used to describe the characteristics of power DC/DC converters and other high-frequency switching circuits.

Power DC/DC converters have usually equipped by a DC power supply source, pump circuit, filter and load. The load can be of any type, but most of the investigations are concerned with resistive load, R, and back electromagnetic force (EMF) or battery. It means that the input and output voltages are nearly pure DC voltages with very small ripple (e.g. output voltage variation ratio is usually less than 1%). In this case, the corresponding RF is less than 0.001, which is always ignored.

Since all power is real power without reactive power jQ, we cannot use power factor PF to describe the energy-transferring process.

Since DC components exist without harmonics in input and output voltage, *THD* is not available to be used to describe the energy-transferring process and waveform distortion.

To simplify the research and analysis, we usually assume the condition without power losses during power-transferring process to investigate power DC/DC converters. Consequently, the efficiency  $\eta=1$  is 100% for most of the description of power DC/DC investigation. Otherwise, efficiency  $\eta$  must be considered for special investigations regarding the power losses.

In general conditions, all four factors are not available to apply in the analysis of power DC/DC converters. This situation makes the designers of power DC/DC converters confusing for very long time. People would like to find other new parameters to describe the characteristics of power DC/DC converters.

Energy storage in power DC/DC converters has been paid attention long time ago. Unfortunately, there is no clear concept to describe the phenomena and reveal the relationship between the stored energy and the characteristics of power DC/DC converters. We have theoretically defined a new concept, "energy factor (EF)", and researched the relationship between EF and the mathematical modeling of power DC/DC converters. EF is a new concept in power electronics and conversion technology, which thoroughly differs from the traditional concepts such as power factor (PF), power transfer efficiency ( $\eta$ ), total harmonic distortion (THD) and ripple factor (RF). EF and the sub-sequential other parameters can illustrate the system stability, reference response and interference recovery. This investigation is very helpful for system design and DC/DC converters characteristics foreseeing.

Assuming the instantaneous input voltage and current of a DC/DC converter are,  $v_1(t)$  and  $i_1(t)$ , and their average values are  $V_1$  and  $I_1$ , respectively. The instantaneous output voltage and current of a DC/DC converter are, respectively,  $v_2(t)$  and  $i_2(t)$ , and their average values are  $V_2$  and  $I_2$ , respectively. The switching frequency is f, the switching period is T = 1/f, the conduction duty cycle is k and the voltage transfer gain is  $M = V_2/V_1$ .

# 2.2 PUMPING ENERGY (PE)

All power DC/DC converters have pumping circuit to transfer the energy from the source to some energy-storage passive elements, e.g. inductors and capacitors. The

pumping energy (PE) is used to count the input energy in a switching period T. Its calculation formula is:

$$PE = \int_0^T P_{\text{in}}(t) dt = \int_0^T V_1 i_1(t) dt = V_1 I_1 T$$

(2.1)

where  $I_1 = \int_0^T i_1(t) dt$  is the average value of the input current if the input voltage  $V_1$  is constant. Usually, the input average current  $I_1$  depends on the conduction duty cycle.

### 2.2.1 Energy Quantization

In switching power circuits the energy is not continuously flowing from source to actuator. The energy delivered in a switching period T from source to actuator is likely an energy quantum. Its value is the PE.

# 2.2.2 Energy Quantization Function

From Equation (2.1) it can be seen that the energy quantum (PE) is the function of switching frequency f or period T, conduction duty cycle k, input voltage  $v_1$  and current  $i_1$ . Since the variables T, k,  $v_1$  and  $i_1$  can vary on time, PE is the time function. Usually, in a steady state the variables T, k,  $v_1$  and  $i_1$  cannot vary, consequently PE is a constant value in a steady state.

# 2.3 STORED ENERGY (SE)

Energy storage in power DC/DC converters has been paid attention long time ago. Unfortunately, there is no clear concept to describe the phenomena and reveal the relationship between the stored energy and the characteristics of power DC/DC converters.

### 2.3.1 STORED ENERGY IN CONTINUOUS CONDUCTION MODE

If a power DC/DC converter works in the continuous conduction mode (CCM), then all inductor's currents and capacitor's voltages are continuous (not to be equal to zero).

### Stored Energy (SE)

The stored energy in an inductor is:

$$W_{\rm L} = \frac{1}{2} L I_{\rm L}^2 \tag{2.2}$$

The stored energy across a capacitor is.

$$W_{\rm C} = \frac{1}{2}CV_{\rm C}^2 \tag{2.3}$$

Therefore, if there are  $n_L$  inductors and  $n_C$  capacitors, the total stored energy in a DC/DC converter is:

$$SE = \sum_{j=1}^{n_{L}} W_{L_{j}} + \sum_{j=1}^{n_{C}} W_{C_{j}}$$

(2.4)

Usually, the stored energy (SE) is independent from the switching frequency f (as well as the switching period T). Since the inductor currents and the capacitor voltages rely on the conduction duty cycle k, the stored energy does also rely on the conduction duty cycle k. We use the stored energy (SE) as a new parameter in further description.

### Capacitor-Inductor Stored Energy Ratio (CIR)

Most power DC/DC converters consist of inductors and capacitors. Therefore, we can define the capacitor–inductor stored energy ratio (*CIR*) as follows:

$$CIR = \frac{\sum_{j=1}^{n_{\rm C}} W_{{\rm C}_j}}{\sum_{j=1}^{n_{\rm L}} W_{{\rm L}_j}}$$

(2.5)

### Energy Losses (EL)

Usually, most analyses applied in DC/DC converters are assuming no power losses, i.e. the input power is equal to the output power,  $P_{\rm in} = P_{\rm o}$  or  $V_1I_1 = V_2I_2$ , so that pumping energy is equal to output energy in a period  $PE = V_1I_1T = V_2I_2T$ . It corresponds to the efficiency  $\eta = V_2I_2T/PE = 100\%$ .

Particularly, power losses always exist during the conversion process. They are caused by the resistance of the connection cables, resistance of the inductor and capacitor wire, and power losses across the semiconductor devices (diode, integrated gate bipolar transistors (IGBT), power metal-oxide semiconductor field effected transistors (MOSFET) and so on). We can sort them as the resistance power losses  $P_{\rm r}$ , passive element power losses  $P_{\rm e}$  and device power losses  $P_{\rm d}$ . The total power losses are:

$$P_{\text{loss}} = P_{\text{r}} + P_{\text{e}} + P_{\text{d}}$$

and

$$P_{\text{in}} = P_{\text{O}} + P_{\text{loss}} = P_{\text{O}} + P_{\text{r}} + P_{\text{e}} + P_{\text{d}} = V_2 I_2 + P_{\text{r}} + P_{\text{e}} + P_{\text{d}}$$

Therefore,

$$EL = P_{loss} \times T = (P_r + P_e + P_d)T$$

The energy losses (EL) is in a period T:

$$EL = \int_0^T P_{\text{loss}} \, \mathrm{d}t = P_{\text{loss}} T \tag{2.6}$$

Since the output energy in a period T is (PE - EL)T, we can define the efficiency  $\eta$  to be:

$$\eta = \frac{P_{\rm O}}{P_{\rm in}} = \frac{P_{\rm in} - P_{\rm loss}}{P_{\rm in}} = \frac{PE - EL}{PE}$$

(2.7)

If there are some energy losses (EL > 0), then the efficiency  $\eta$  is smaller than unity. If there are no energy losses during conversion process (EL = 0), then the efficiency  $\eta$  is equal to unity.

### Stored Energy Variation on Inductors and Capacitors (VE)

The current flowing through an inductor has variation (ripple)  $\Delta i_L$ , the variation of stored energy in an inductor is:

$$\Delta W_{\rm L} = \frac{1}{2} L (I_{\rm max}^2 - I_{\rm min}^2) = L I_{\rm L} \Delta i_{\rm L}$$

(2.8)

where

$$I_{\text{max}} = (I_{\text{L}} + \Delta i_{\text{L}})/2$$

and  $I_{\text{min}} = (I_{\text{L}} - \Delta i_{\text{L}})/2$ .

The voltage across a capacitor has variation (ripple)  $\Delta v_{\rm C}$ , the variation of stored energy across a capacitor is:

$$\Delta W_{\rm C} = \frac{1}{2}C(V_{\rm max}^2 - V_{\rm min}^2) = CV_{\rm C}\Delta \nu_{\rm C}$$

(2.9)

where

$$V_{\text{max}} = (V_{\text{C}} + \Delta v_{\text{C}})/2$$

and  $V_{\text{min}} = (V_{\text{C}} - \Delta v_{\text{C}})/2$

In the steady state of CCM, the total variation of the stored energy (VE) is:

$$VE = \sum_{i=1}^{n_{L}} \Delta W_{L_{i}} + \sum_{i=1}^{n_{C}} \Delta W_{C_{i}}$$

(2.10)

# 2.3.2 STORED ENERGY IN DISCONTINUOUS CONDUCTION MODE (DCM)

If a power DC/DC converter works in the CCM, some component's voltage and current are discontinuous. In the steady state of the discontinuous conduction situation (DCM), some minimum currents through inductors and/or some minimum voltages across capacitors become zero. We define the **filling coefficients**  $m_{\rm L}$  and  $m_{\rm C}$  to describe the performance in DCM.

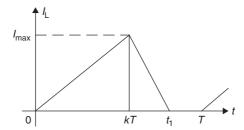

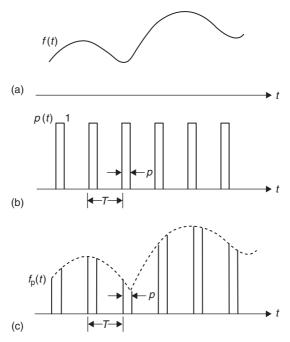

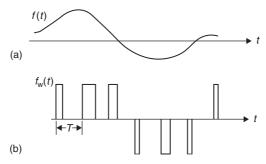

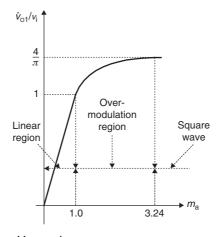

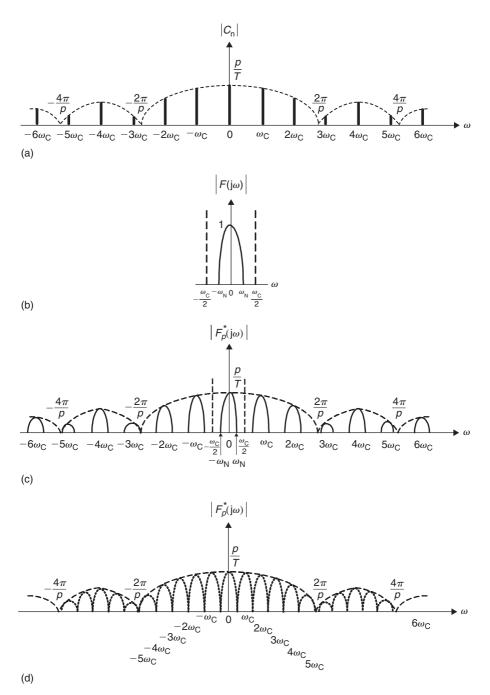

Usually, if the switching frequency f is high enough, the inductor's current is a triangle waveform. It increases and reaches  $I_{\text{max}}$  during the switching-on period kT, and it decreases and reaches  $I_{\text{min}}$  during the switching-off period (1-k)T. If it becomes zero at  $t=t_1$  before next switching-on, we call the converter works in DCM. The waveform of the inductor's current is shown in Figure 2.1. The time  $t_1$  should be in the range  $kT < t_1 < T$ , and the filling coefficient  $m_L$  is:

$$m_{\rm L} = \frac{t_1 - kT}{(1 - k)T} \tag{2.11}$$

where  $0 < m_{\rm L} < 1$ . It means the inductor's current only can fill the time period  $m_{\rm L}(1-k)T$  during switch-off period. In this case,  $I_{\rm min}$  is equal to zero and the average current  $I_{\rm L}$  is:

$$I_{\rm L} = \frac{1}{2} I_{\rm max} [m_{\rm L} + (1 - m_{\rm L})/k]$$

(2.12)

and

$$\Delta i_{\rm L} = I_{\rm max} \tag{2.13}$$

Therefore,

$$\Delta W_{\rm L} = LI_{\rm L} \Delta i_{\rm L} = \frac{1}{2} LI_{\rm max}^2 [m_{\rm L} + (1 - m_{\rm L})/k]$$

(2.14)

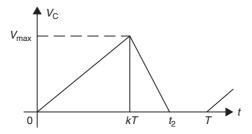

Analogously, we define the filling coefficient  $m_{\rm C}$  to describe the capacitor voltage discontinuity. The waveform is shown in Figure 2.2. Time  $t_2$  should be  $kT < t_2 < T$ , and the filling coefficient  $m_{\rm C}$  is:

$$m_{\rm C} = \frac{t_2 - kT}{(1 - k)T} \tag{2.15}$$

**Figure 2.1** Discontinuous inductor current.

Figure 2.2 Discontinuous capacitor voltage.

where  $0 < m_{\rm C} < 1$ . It means that the capacitor's voltage only can fill the time period  $m_{\rm C}(1-k)T$  during the switch-off period. In this case,  $V_{\rm min}$  is equal to zero and the average voltage  $V_{\rm C}$  is:

$$V_{\rm C} = \frac{1}{2} V_{\rm max} [m_{\rm C} + (1 - m_{\rm C})/k]$$

(2.16)

and

$$\Delta v_{\rm C} = V_{\rm max} \tag{2.17}$$

Therefore.

$$\Delta W_{\rm C} = CV_{\rm C} \Delta v_{\rm C} = \frac{1}{2} CV_{\rm max}^2 [m_{\rm C} + (1 - m_{\rm C})/k]$$

(2.18)

We consider a converter working in DCM; it usually means only one or two energy-storage elements' voltage/current are discontinuous, and not all elements. We use the parameter  $VE_D$  to present the total variation of the stored energy:

$$VE_{\rm D} = \sum_{j=1}^{n_{\rm L-d}} \Delta W_{\rm L_j} + \sum_{j=n_{\rm L-d}+1}^{n_{\rm L}} \Delta W_{\rm L_j} + \sum_{j=1}^{n_{\rm C-d}} \Delta W_{\rm C_j} + \sum_{j=n_{\rm C-d}+1}^{n_{\rm C}} \Delta W_{\rm C_j}$$

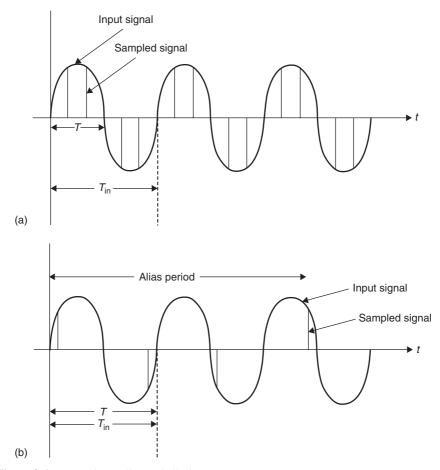

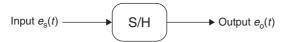

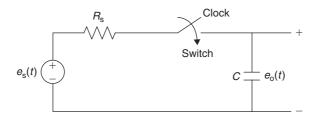

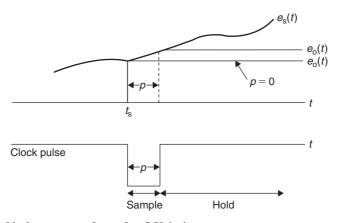

(2.19)