Digital Integrated

CIRCUITS

Analysis and Design

**John E. Ayers**

## Digital Integrated CIRCUITS

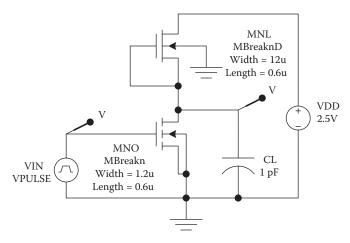

Analysis and Design

# Digital Integrated CIRCUITS

## **Analysis and Design**

**John E. Ayers**

CRC Press is an imprint of the Taylor & Francis Group, an **informa** business

CRC Press Taylor & Francis Group 6000 Broken Sound Parkway NW, Suite 300 Boca Raton, FL 33487-2742

© 2010 by Taylor & Francis Group, LLC CRC Press is an imprint of Taylor & Francis Group, an Informa business

No claim to original U.S. Government works Printed in the United States of America on acid-free paper 10 9 8 7 6 5 4 3 2 1

International Standard Book Number-13: 978-1-4200-6987-7 (Hardcover)

This book contains information obtained from authentic and highly regarded sources. Reasonable efforts have been made to publish reliable data and information, but the author and publisher cannot assume responsibility for the validity of all materials or the consequences of their use. The authors and publishers have attempted to trace the copyright holders of all material reproduced in this publication and apologize to copyright holders if permission to publish in this form has not been obtained. If any copyright material has not been acknowledged please write and let us know so we may rectify in any future reprint.

Except as permitted under U.S. Copyright Law, no part of this book may be reprinted, reproduced, transmitted, or utilized in any form by any electronic, mechanical, or other means, now known or hereafter invented, including photocopying, microfilming, and recording, or in any information storage or retrieval system, without written permission from the publishers.

For permission to photocopy or use material electronically from this work, please access www.copyright.com (http://www.copyright.com/) or contact the Copyright Clearance Center, Inc. (CCC), 222 Rosewood Drive, Danvers, MA 01923, 978-750-8400. CCC is a not-for-profit organization that provides licenses and registration for a variety of users. For organizations that have been granted a photocopy license by the CCC, a separate system of payment has been arranged.

**Trademark Notice:** Product or corporate names may be trademarks or registered trademarks, and are used only for identification and explanation without intent to infringe.

#### Library of Congress Cataloging-in-Publication Data

Ayers, John E.

Digital integrated circuits: analysis and design / by John E. Ayers. -- 2nd ed.

p. cm.

Includes bibliographical references and index.

ISBN-13: 978-1-4200-6987-7

ISBN-10: 1-4200-6987-X

1. Digital integrated circuits--Design and construction. I. Title.

TK7874.65.A94 2010 621.3815--dc22

2009010227

Visit the Taylor & Francis Web site at http://www.taylorandfrancis.com

and the CRC Press Web site at http://www.crcpress.com

To Kimberly, Jacob, Sarah, and Rachel.

Their patience and limitless support made this project possible.

### Contents

| re | тасе    |                                                      | XV   |

|----|---------|------------------------------------------------------|------|

| ٩b | out the | e Author                                             | xvii |

|    |         |                                                      |      |

| 1. | Intro   | duction                                              |      |

|    | 1.1     | Historical Perspective and Moore's Law               |      |

|    | 1.2     | Electrical Properties of Digital Integrated Circuits | 8    |

|    |         | 1.2.1 Logic Function                                 | 9    |

|    |         | 1.2.2 Static Voltage Transfer Characteristics        |      |

|    |         | 1.2.3 Transient Characteristics                      |      |

|    |         | 1.2.4 Fan-In and Fan-Out                             | 20   |

|    |         | 1.2.5 Dissipation                                    |      |

|    |         | 1.2.6 Power Delay Product                            |      |

|    | 1.3     | Computer-Aided Design and Verification               | 25   |

|    | 1.4     | Fabrication                                          |      |

|    | 1.5     | Semiconductors and Junctions                         | 27   |

|    | 1.6     | The MOS Transistor                                   | 28   |

|    | 1.7     | MOS Gate Circuits                                    | 29   |

|    | 1.8     | Interconnect                                         | 30   |

|    | 1.9     | Dynamic CMOS                                         | 31   |

|    | 1.10    | Low-Power CMOS                                       | 31   |

|    | 1.11    | Bistable Circuits                                    | 32   |

|    | 1.12    | Memories                                             | 33   |

|    | 1.13    | Input/Output and Interface Circuits                  | 33   |

|    | 1.14    | Practical Perspective                                | 34   |

|    | 1.15    | Summary                                              | 34   |

|    | 1.16    | Exercises                                            |      |

|    | Refer   | ences                                                | 38   |

| 2. | Fabri   | cation                                               | 39   |

|    | 2.1     | Introduction                                         | 39   |

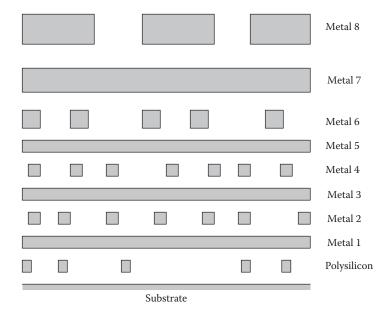

|    | 2.2     | Basic CMOS Fabrication Sequence                      |      |

|    | 2.3     | Advanced Processing for High-Performance CMOS        |      |

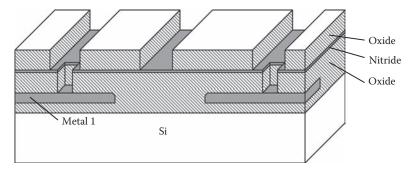

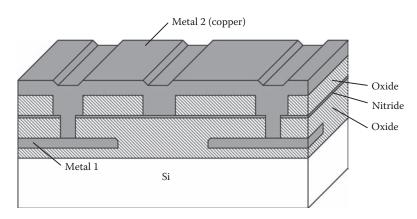

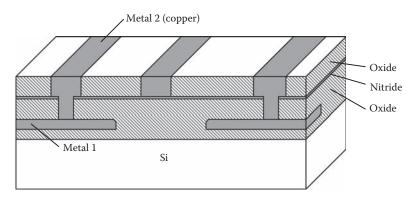

|    |         | 2.3.1 Copper Metal                                   | 45   |

|    |         | 2.3.2 Metal Gates                                    |      |

|    |         | 2.3.3 High-κ Gate Dielectric                         |      |

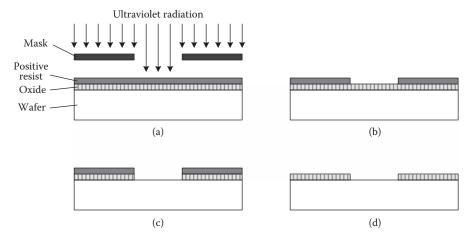

|    | 2.4     | Lithography and Masks                                |      |

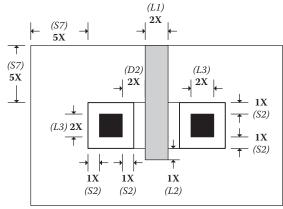

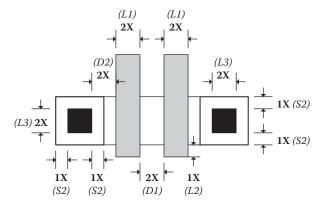

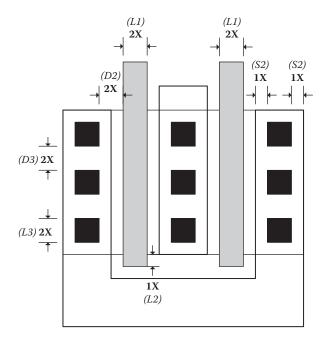

|    | 2.5     | Layout and Design Rules                              |      |

|    |         | 2.5.1 Minimum Line Widths and Spacings               |      |

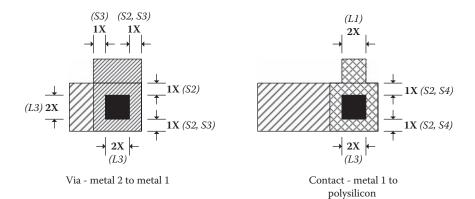

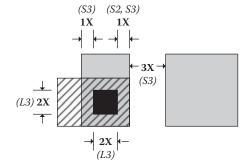

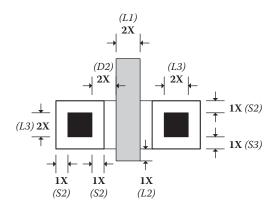

|    |         | 2.5.2 Contacts and Vias                              |      |

|    | 2.6    | Testin | ıg and Yie | eld                                   | 57  |

|----|--------|--------|------------|---------------------------------------|-----|

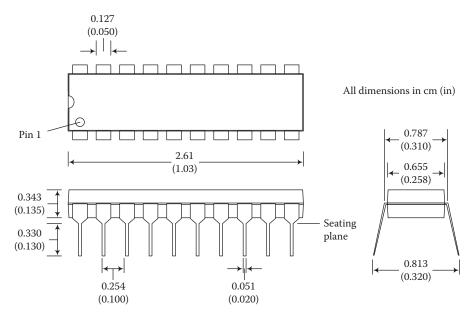

|    | 2.7    | Packa  | ging       |                                       | 61  |

|    | 2.8    | Burn-  | In and Ac  | celerated Testing                     | 63  |

|    | 2.9    |        |            | ective                                |     |

|    | 2.10   |        |            |                                       |     |

|    | 2.11   |        |            |                                       |     |

|    | Refere | nces   |            |                                       | 64  |

| 3. | Semic  | onduct | tors and p | o-n Junctions                         | 67  |

|    | 3.1    |        |            |                                       |     |

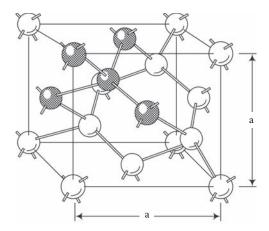

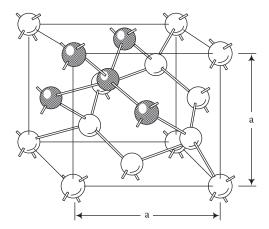

|    | 3.2    | Crysta | al Structu | re of Silicon                         | 67  |

|    | 3.3    | Energ  | y Bands    |                                       | 67  |

|    | 3.4    | Carrie | er Concen  | trations                              | 69  |

|    |        | 3.4.1  | Intrinsi   | c Silicon                             | 70  |

|    |        | 3.4.2  | n-Type S   | Silicon                               | 70  |

|    |        | 3.4.3  | p-Type S   | Silicon                               | 72  |

|    | 3.5    | Curre  |            | ort                                   |     |

|    | 3.6    |        |            | uity Equations                        |     |

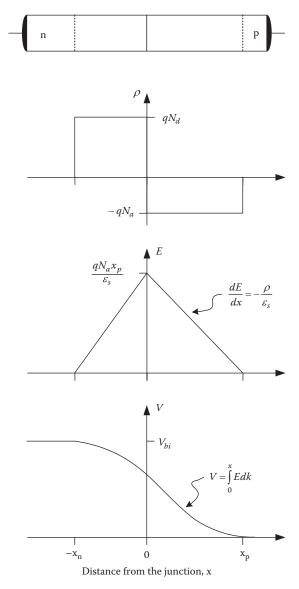

|    | 3.7    | Poisso | on's Equat | ion                                   | 75  |

|    | 3.8    |        |            | n                                     |     |

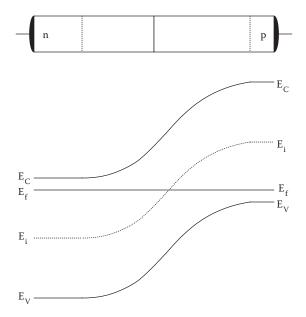

|    |        | 3.8.1  |            | as (Thermal Equilibrium)              |     |

|    |        |        | 3.8.1.1    | · · · · · · · · · · · · · · · · · · · |     |

|    |        |        | 3.8.1.2    |                                       |     |

|    |        | 3.8.2  | Depletion  | on Capacitance                        |     |

|    |        | 3.8.3  | Forward    | d Bias Current                        | 83  |

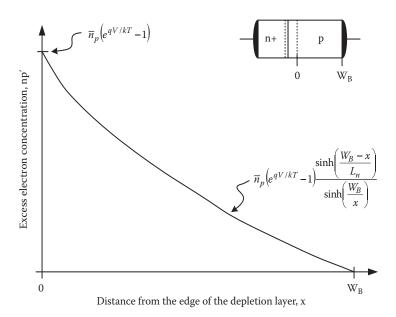

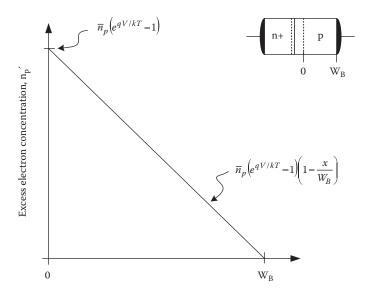

|    |        |        | 3.8.3.1    | Short-Base n+-p Junction              | 85  |

|    |        |        | 3.8.3.2    | *                                     |     |

|    |        | 3.8.4  | Reverse    | Bias                                  | 87  |

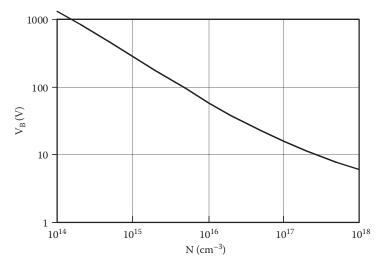

|    |        | 3.8.5  | Reverse    | Breakdown                             | 88  |

|    | 3.9    | Metal  | -Semicon   | ductor Junctions                      | 88  |

|    | 3.10   | SPICE  | Models .   |                                       | 90  |

|    | 3.11   | Practi | cal Perspe | ective                                | 91  |

|    | 3.12   |        |            |                                       |     |

|    | 3.13   | Exerci | ises       |                                       | 92  |

|    | Refere | nces   |            |                                       | 93  |

| 4. | The M  | IOS Tr | ansistor   |                                       | 95  |

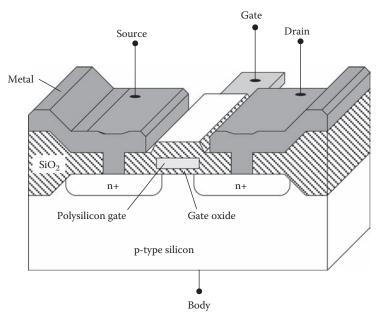

|    | 4.1    | Introd | luction    |                                       | 95  |

|    | 4.2    | The M  | 1OS Capa   | citor                                 | 97  |

|    | 4.3    | Thres  | hold Volta | age                                   | 100 |

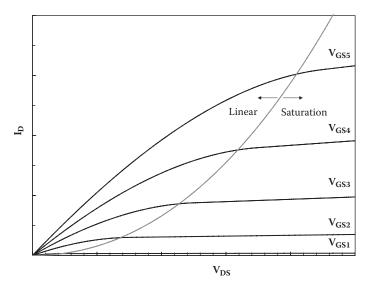

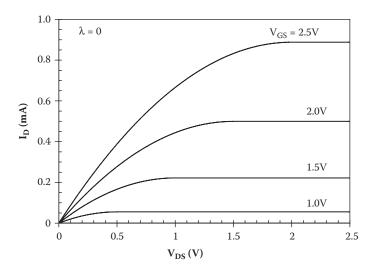

|    | 4.4    |        |            | ent-Voltage Characteristics           |     |

|    |        | 4.4.1  |            | Operation                             |     |

|    |        | 4.4.2  |            | on Operation                          |     |

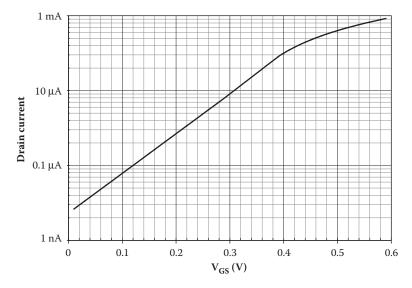

|    |        | 4.4.3  |            | shold Operation                       |     |

|    |        | 4.4.4  |            | Time                                  |     |

|    | 4.5    | Short-Channel MOSFETs                                       | 115        |

|----|--------|-------------------------------------------------------------|------------|

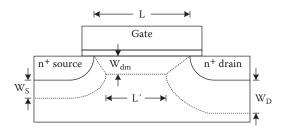

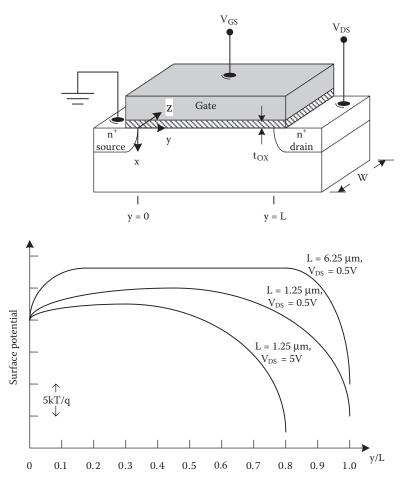

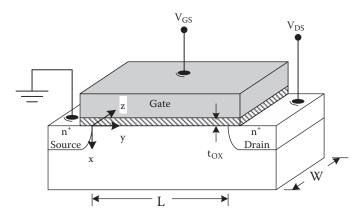

|    |        | 4.5.1 The Short-Channel Effect                              | 115        |

|    |        | 4.5.2 Narrow-Channel Effect                                 | 116        |

|    |        | 4.5.3 Drain-Induced Barrier Lowering                        | 117        |

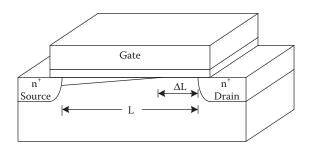

|    |        | 4.5.4 Channel Length Modulation                             |            |

|    |        | 4.5.5 Field-Dependent Mobility and Velocity Saturation      | n 119      |

|    |        | 4.5.6 Transit Time in Short-Channel MOSFETs                 | 125        |

|    | 4.6    | MOSFET Design                                               | 126        |

|    | 4.7    | MOSFET Capacitances                                         | 133        |

|    |        | 4.7.1 Oxide Capacitances                                    |            |

|    |        | 4.7.2 p-n Junction Capacitances                             |            |

|    |        | 4.7.3 The Miller Effect                                     |            |

|    | 4.8    | MOSFET Constant-Field Scaling                               |            |

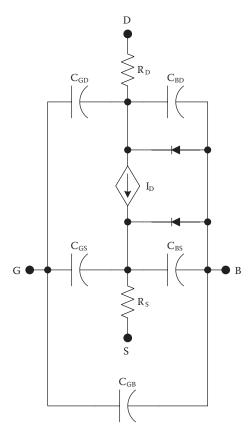

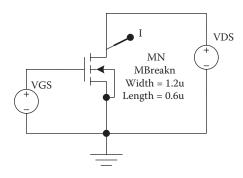

|    | 4.9    | SPICE MOSFET Models                                         |            |

|    |        | 4.9.1 MOSFET Level 1 Model                                  |            |

|    |        | 4.9.2 Berkeley Short-Channel Insulated Gate Field Effe      |            |

|    |        | Transistor Model                                            |            |

|    |        | 4.9.2.1 BSIM1 Parameters                                    |            |

|    |        | 4.9.2.2 BSIM1 Threshold Voltage                             |            |

|    |        | 4.9.2.3 BSIM1 Drain Current-Linear Region                   |            |

|    |        | 4.9.2.4 BSIM1 Drain Current-Saturation Region               | 150        |

|    |        | 4.9.2.5 BSIM1 Drain Current-Subthreshold                    | 4          |

|    |        | Region                                                      |            |

|    | 4.10   | 4.9.2.6 Hand Calculations Related to the BSIM1              |            |

|    | 4.10   | SPICE Demonstrations                                        |            |

|    | 4.11   | Practical Perspective                                       |            |

|    | 4.12   | Summary                                                     |            |

|    | 4.13   | Exercises                                                   |            |

|    | Kerere | ences                                                       | 160        |

| _  | MOS    | Gate Circuits                                               | 162        |

| э. | 5.1    | Inverter Static Characteristics                             |            |

|    | 5.2    | Critical Voltages                                           |            |

|    | 5.2    | 5.2.1 Output High-Voltage V <sub>OH</sub>                   |            |

|    |        | 5.2.2 Output Low-Voltage V <sub>OL</sub>                    |            |

|    |        | 5.2.3 Input Low-Voltage V <sub>IL</sub>                     | 160<br>169 |

|    |        | 5.2.4 Input High-Voltage V <sub>II</sub>                    | 107<br>170 |

|    |        | 5.2.5 Switching Threshold (Midpoint) Voltage V <sub>M</sub> | 171        |

|    | 5.2    | Dissipation                                                 |            |

|    | 5.4    | Propagation Delays                                          |            |

|    | 5.5    | Fan-Out.                                                    |            |

|    | 5.6    | NOR Circuits                                                |            |

|    | 5.7    | NAND Circuits                                               |            |

|    | 5.8    | Exclusive OR (XOR) Circuit                                  |            |

|    | 5.9    | General Logic Design                                        |            |

|    |        |                                                             |            |

x Contents

|    | 5.10   | Pass Tı      | ransistor Circuits                                 | 189 |

|----|--------|--------------|----------------------------------------------------|-----|

|    | 5.11   | <b>SPICE</b> | Demonstrations                                     | 191 |

|    | 5.12   | Practic      | al Perspective                                     | 195 |

|    | 5.13   |              | ary                                                |     |

|    | 5.14   |              | ses                                                |     |

| _  | Chalia | CMOS         |                                                    | 201 |

| υ. | 6.1    |              | uction                                             |     |

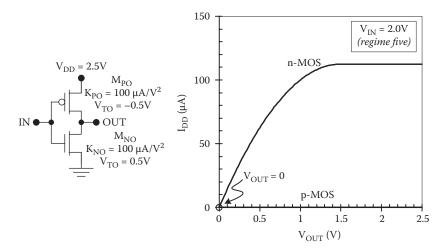

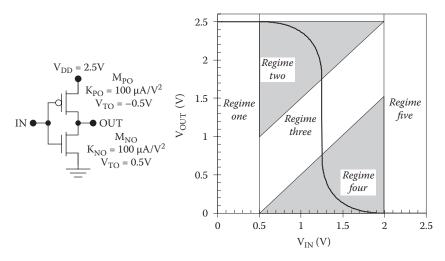

|    | 6.2    |              | e Transfer Characteristic                          |     |

|    | 0.2    | _            | Voltage Regime One: n-MOS Cutoff and               | 201 |

|    |        | 6.2.1        | p-MOS Linear                                       | 204 |

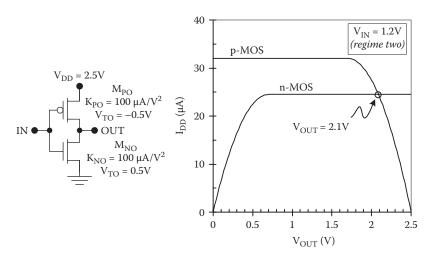

|    |        | 6.2.2        | Voltage Regime Two: n-MOS Saturated and            | 204 |

|    |        | 0.2.2        |                                                    | 204 |

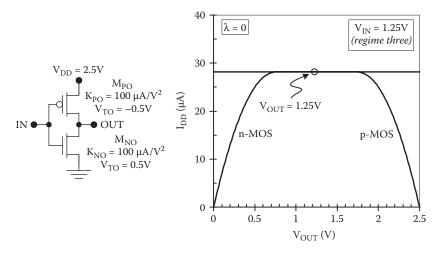

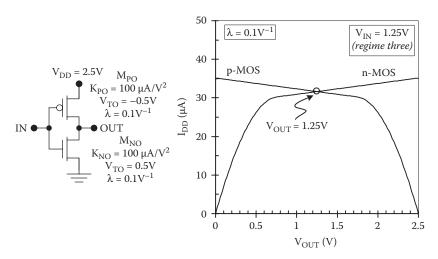

|    |        | 6.2.3        | p-MOS Linear                                       |     |

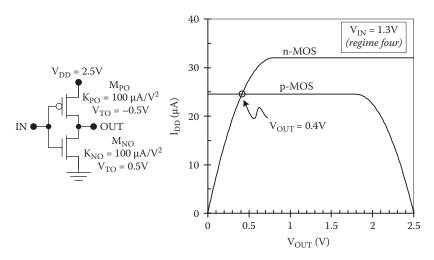

|    |        | 6.2.4        | Voltage Regime Four: n-MOS Linear and              | 200 |

|    |        | 0.2.4        | p-MOS Saturated                                    | 207 |

|    |        | 6.2.5        | Voltage Regime Five: n-MOS Linear and              | 207 |

|    |        | 0.2.3        | p-MOS Cutoff                                       | 208 |

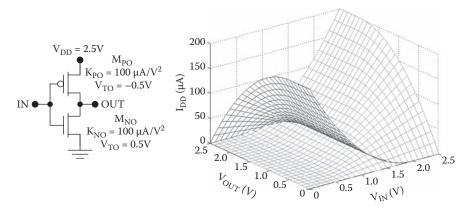

|    | 6.3    | LoadS        | burface Analysis                                   |     |

|    | 6.4    |              | l Voltages                                         |     |

|    | 0.1    | 6.4.1        | Input Low-Voltage V <sub>IL</sub>                  |     |

|    |        | 6.4.2        | Switching Threshold $V_M$                          |     |

|    |        | 6.4.3        | Input High-Voltage V <sub>IH</sub>                 |     |

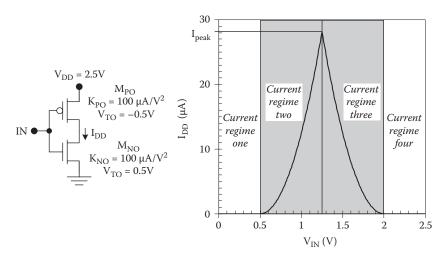

|    | 6.5    |              | ver (Short-Circuit) Current                        |     |

|    | 0.0    | 6.5.1        | Current Regime One: n-MOS Cutoff                   |     |

|    |        | 6.5.2        | Current Regime Two: n-MOS Saturated                |     |

|    |        | 6.5.3        | Current Regime Three: p-MOS Saturated              |     |

|    |        | 6.5.4        | Current Regime Four: p-MOS Cutoff                  |     |

|    |        | 6.5.5        | Unified Expression for the Crossover Current       |     |

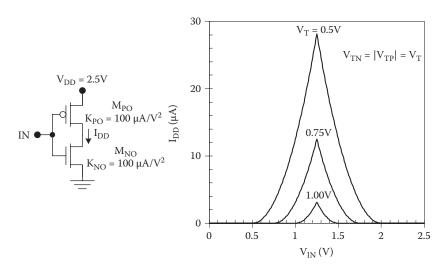

|    |        | 6.5.6        | Effect of Threshold Voltages                       |     |

|    | 6.6    |              | gation Delays                                      |     |

|    |        | 6.6.1        | High-to-Low Propagation Delay t <sub>PHL</sub>     |     |

|    |        | 6.6.2        | Low-to-High Propagation Delay t <sub>PLH</sub>     |     |

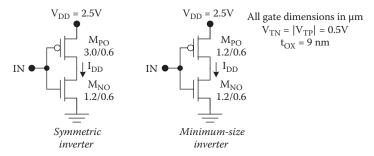

|    |        | 6.6.3        | Propagation Delay Design Equations                 |     |

|    |        | 6.6.4        | Propagation Delays in the Symmetric Inverter       |     |

|    |        | 6.6.5        | Approximate Expressions for the Propagation Delays |     |

|    |        | 6.6.6        | Effect of the Input Rise and Fall Time             |     |

|    | 6.7    | Inverte      | er Rise and Fall Times                             |     |

|    |        | 6.7.1        | Fall Time                                          | 230 |

|    |        | 6.7.2        | Rise Time                                          | 232 |

|    |        | 6.7.3        | Effect of the Input Rise and Fall Time on          |     |

|    |        |              | Output Rise and Fall Time                          | 234 |

|    | 6.8    | Propag       | gation Delays in Short-Channel CMOS                | 236 |

|    |        | 6.8.1        | High-to-Low Propagation Delay t <sub>PHL</sub> in  |     |

|    |        |              | Short-Channel CMOS                                 | 236 |

|    |         | 6.8.2       | Low-to-High Propagation Delay t <sub>PLH</sub> in | 225 |

|----|---------|-------------|---------------------------------------------------|-----|

|    |         | (02         | Short-Channel CMOS                                | 237 |

|    |         | 6.8.3       | Comparison of the Short-Channel and               | 220 |

|    |         | 6.0.4       | Long-Channel Delay Equations                      | 238 |

|    |         | 6.8.4       | Propagation Delay Design Equations for            | 220 |

|    |         | _           | Short-Channel CMOS                                |     |

|    | 6.9     |             | Dissipation                                       |     |

|    |         | 6.9.1       | Capacitance Switching Dissipation                 |     |

|    |         | 6.9.2       | Short-Circuit Dissipation                         |     |

|    |         | 6.9.3       | Leakage Current Dissipation                       |     |

|    | 6.10    |             | ut                                                |     |

|    | 6.11    |             | t Delays as Functions of Fan-Out                  |     |

|    | 6.12    |             | Ring Oscillator                                   |     |

|    | 6.13    |             | Inverter Design                                   |     |

|    | 6.14    |             | NAND Circuits                                     |     |

|    |         | 6.14.1      | Sizing of Transistors in a CMOS NAND Gate         | 256 |

|    |         | 6.14.2      | Static Characteristics of the CMOS NAND Gate      | 260 |

|    |         | 6.14.3      | Dynamic Characteristics of the CMOS               |     |

|    |         |             | NAND Gate                                         | 262 |

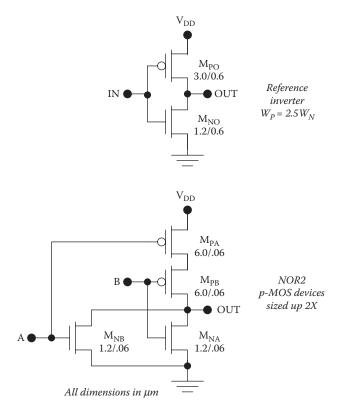

|    | 6.15    | <b>CMOS</b> | NOR Circuits                                      | 262 |

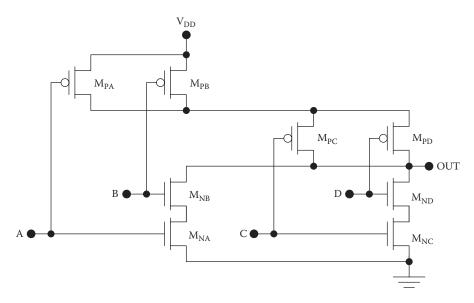

|    | 6.16    | Other 1     | Logic Functions in CMOS                           | 264 |

|    |         |             | Transistor Sizing in CMOS AND-OR-INVERT           |     |

|    |         |             | Gates                                             | 266 |

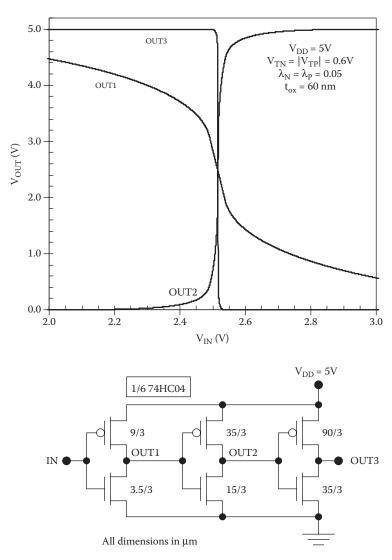

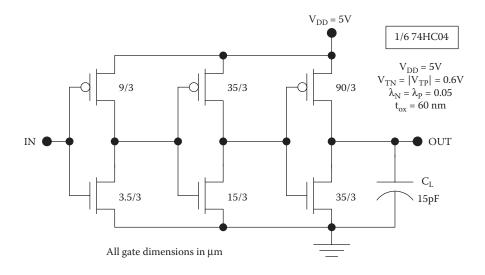

|    | 6.17    | 74HC S      | Series CMOS                                       | 267 |

|    | 6.18    | Pseudo      | NMOS Circuits                                     | 273 |

|    | 6.19    | Scaling     | g of CMOS                                         | 274 |

|    |         |             | Full Scaling of CMOS                              |     |

|    |         |             | Constant Voltage Scaling of CMOS                  |     |

|    | 6.20    |             | Up in CMOS                                        |     |

|    | 6.21    |             | Demonstrations                                    |     |

|    | 6.22    |             | ary                                               |     |

|    | 6.23    |             | al Perspective                                    |     |

|    | 6.24    |             | Ses                                               |     |

|    | 0.21    | 27101010    |                                                   | 207 |

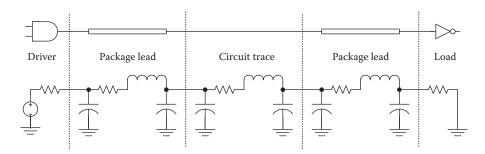

| 7. | Interco | onnect      |                                                   | 299 |

| •  | 7.1     |             | uction                                            |     |

|    | 7.2     |             | tance of Interconnect                             |     |

|    | 7.3     |             | ance of Interconnect                              |     |

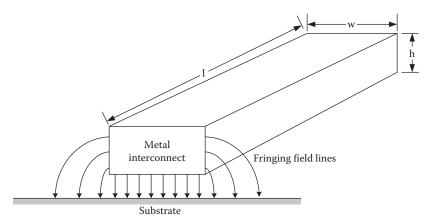

|    | 7.4     |             | ance of Interconnect                              |     |

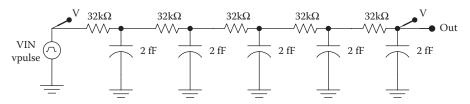

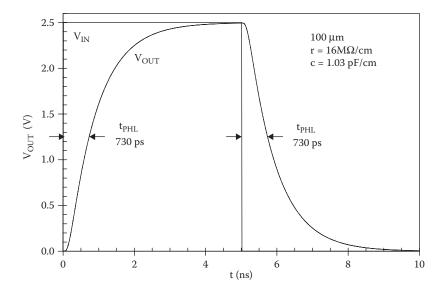

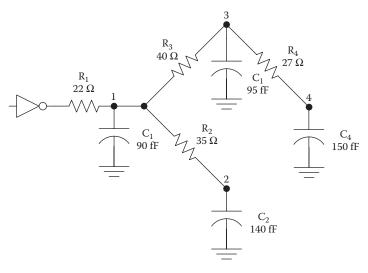

|    | 7.5     |             | ing Interconnect Delays                           |     |

|    | 7.5     | 7.5.1       | Lumped Capacitance Model                          |     |

|    |         | 7.5.1       | Distributed Models                                |     |

|    |         | 7.5.2       | Transmission Line Model                           |     |

|    | 7.6     |             |                                                   |     |

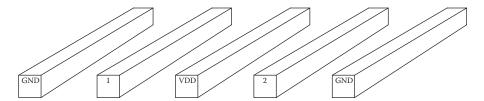

|    | 7.6     |             | alk                                               |     |

|    | 7.7     | 1'01YS11    | icon Interconnect                                 | 317 |

|    | 7.8    | SPICE Demons    | strations                           | 319 |

|----|--------|-----------------|-------------------------------------|-----|

|    | 7.9    | Practical Persp | ective                              | 326 |

|    | 7.10   | Summary         |                                     | 327 |

|    | 7.11   |                 |                                     |     |

|    | Refere | nces            |                                     | 331 |

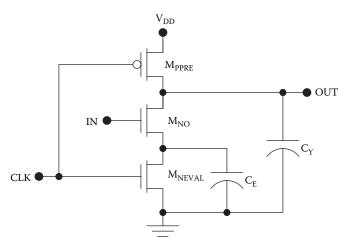

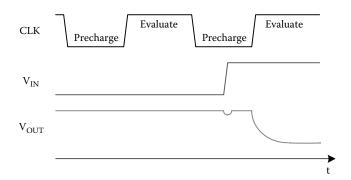

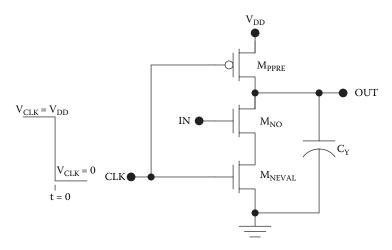

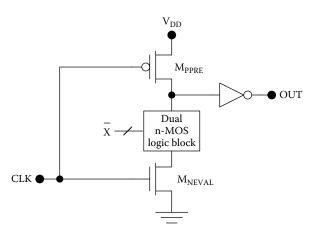

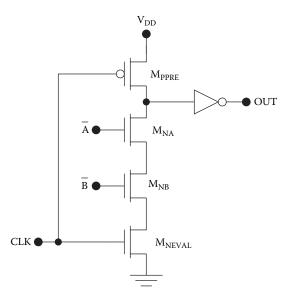

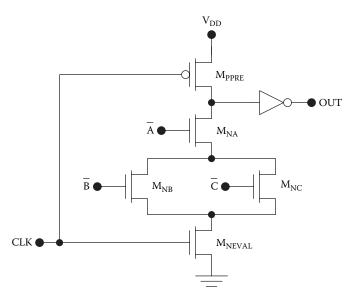

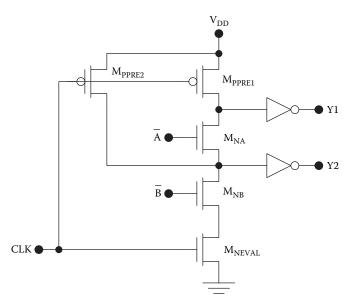

| 8. | Dvnaı  | nic CMOS        |                                     | 333 |

|    | 8.1    |                 |                                     |     |

|    | 8.2    |                 |                                     |     |

|    | 8.3    |                 |                                     |     |

|    | 8.4    |                 | g                                   |     |

|    | 8.5    |                 | ion                                 |     |

|    | 8.6    |                 |                                     |     |

|    | 8.7    |                 | rm Using a p-MOS Pull-Up Network    |     |

|    | 8.8    |                 | Dynamic Logic Circuits              |     |

|    | 8.9    |                 |                                     |     |

|    | 8.10   |                 | ut Domino Logic                     |     |

|    | 8.11   |                 |                                     |     |

|    | 8.12   |                 | Transistor Circuits                 |     |

|    |        |                 | 1" Transfer Delay t <sub>1</sub>    |     |

|    |        |                 | 0" Transfer Delay t <sub>0</sub>    |     |

|    | 8.13   |                 | ission Gate Circuits                |     |

|    | 8.14   |                 | strations                           |     |

|    | 8.15   |                 | ective                              |     |

|    | 8.16   |                 |                                     |     |

|    | 8.17   |                 |                                     |     |

|    | Refere | nces            |                                     | 371 |

| 9. | Low-P  | ower CMOS       |                                     | 373 |

|    | 9.1    |                 |                                     |     |

|    | 9.2    |                 | MOS                                 |     |

|    | 9.3    |                 | ge CMOS                             |     |

|    | 9.4    |                 | ge Scaling                          |     |

|    | 9.5    |                 | asing                               |     |

|    | 9.6    |                 | shold CMOS                          |     |

|    | 9.7    |                 | C                                   |     |

|    | 9.8    |                 | ılator                              |     |

|    |        |                 | chnologies: SIMOX and Wafer Bonding |     |

|    |        |                 | OSFETs: Fully Depleted or Partially |     |

|    |        |                 | ed                                  | 393 |

|    |        | 9.8.3 SOI for   | Low-Power CMOS                      |     |

|    | 9.9    |                 | ective                              |     |

|    | 9.10   |                 |                                     |     |

|    | 9.11   |                 |                                     |     |

|    | Roforo |                 |                                     | 400 |

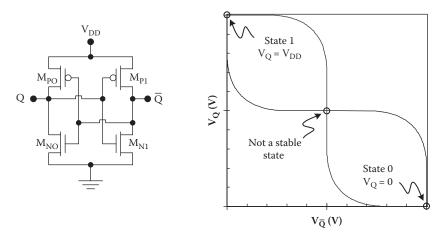

| 10. | Bistab | le Circuits                                         |     |

|-----|--------|-----------------------------------------------------|-----|

|     | 10.1   | Introduction                                        |     |

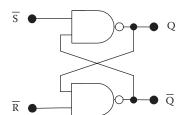

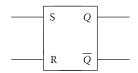

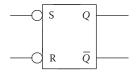

|     | 10.2   | Set-Reset Latch                                     | 408 |

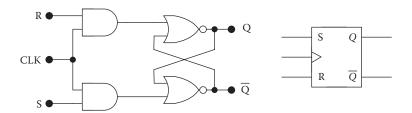

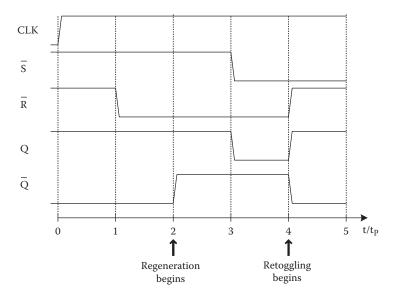

|     | 10.3   | SR Flip-Flop                                        | 410 |

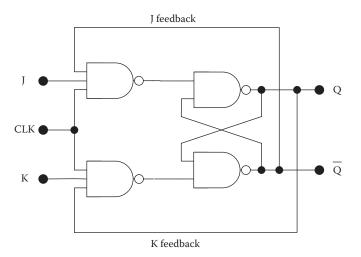

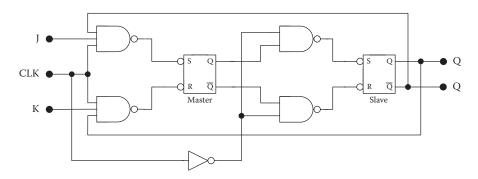

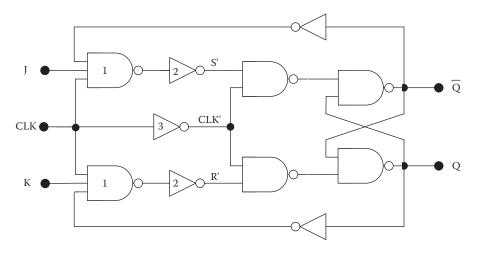

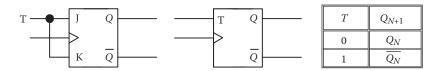

|     | 10.4   | JK Flip-Flops                                       | 410 |

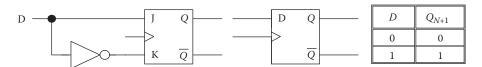

|     | 10.5   | Other Flip-Flops                                    | 415 |

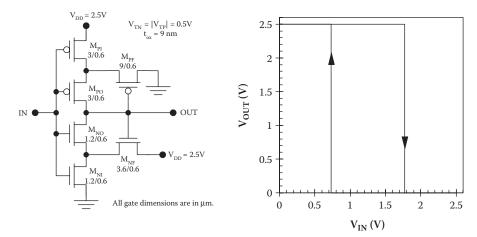

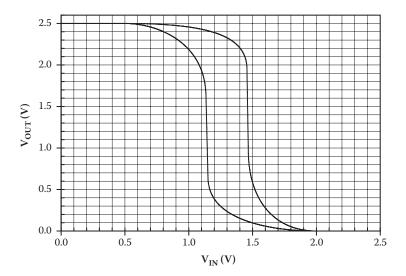

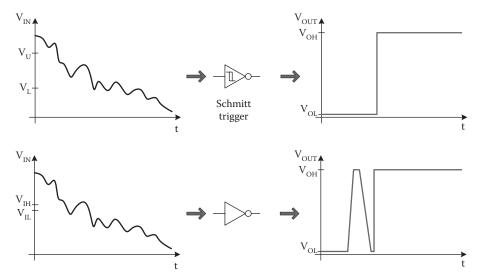

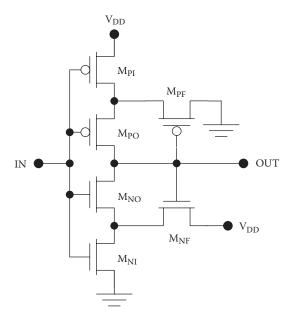

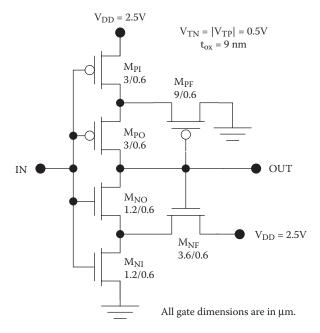

|     | 10.6   | Schmitt Triggers                                    | 416 |

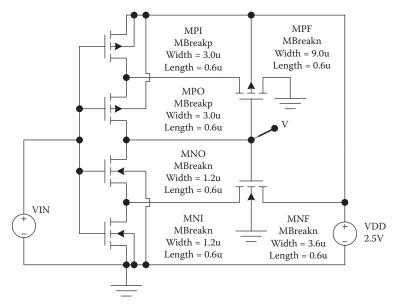

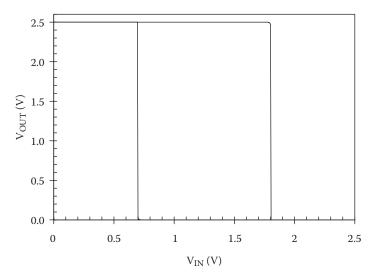

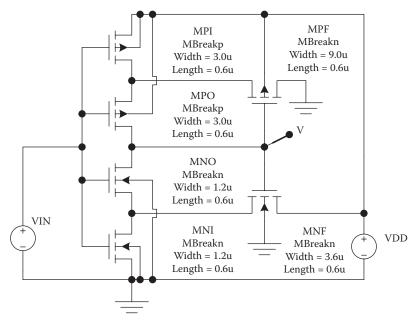

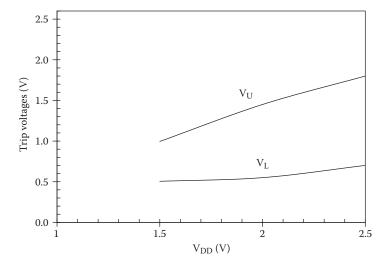

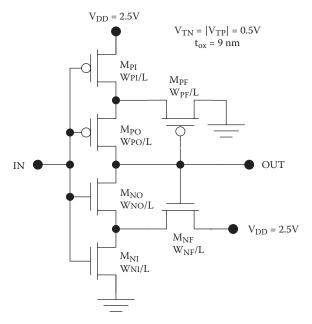

|     |        | 10.6.1 CMOS Schmitt Trigger                         |     |

|     | 10.7   | SPICE Demonstrations                                | 425 |

|     | 10.8   | Practical Perspective                               |     |

|     | 10.9   | Summary                                             | 432 |

|     | 10.10  | Exercises                                           | 432 |

|     | Refere | nces                                                | 434 |

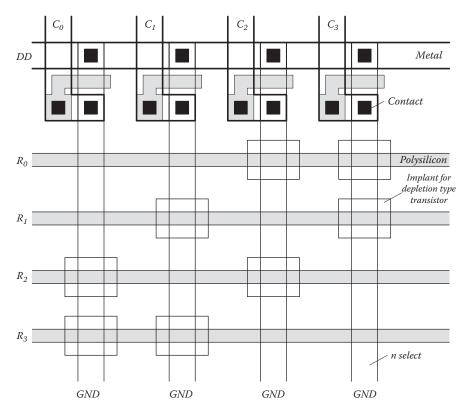

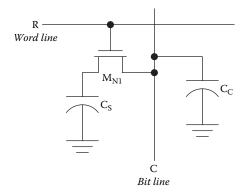

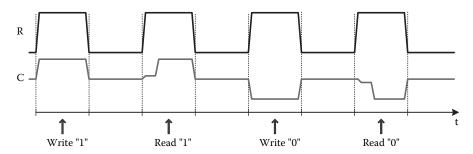

| 11. | Digita | l Memories                                          | 435 |

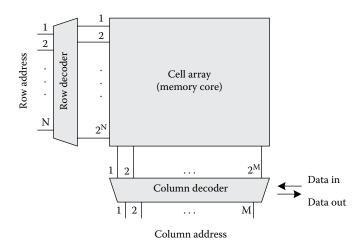

|     | 11.1   | Introduction                                        | 435 |

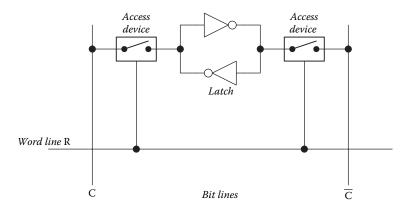

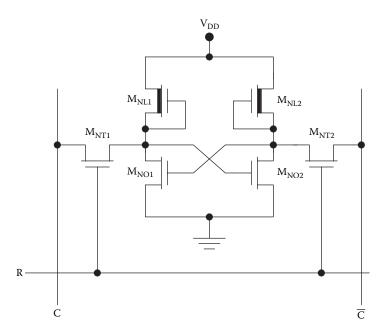

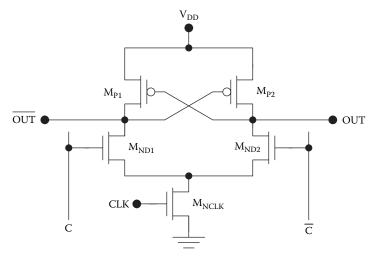

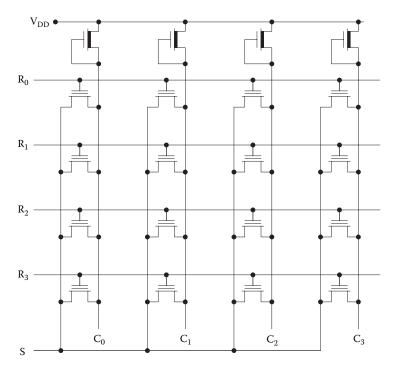

|     | 11.2   | Static Random Access Memory                         | 437 |

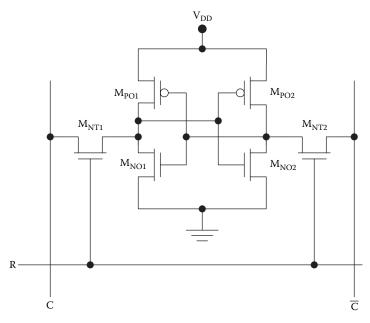

|     |        | 11.2.1 CMOS SRAM Cell                               | 438 |

|     |        | 11.2.2 NMOS SRAM Cell                               | 439 |

|     |        | 11.2.3 SRAM Sense Amplifiers                        | 439 |

|     | 11.3   | Dynamic Random Access Memory                        |     |

|     | 11.4   | Read-Only Memory                                    |     |

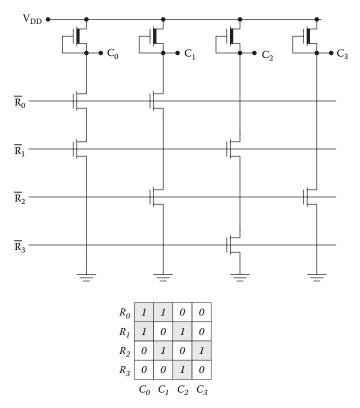

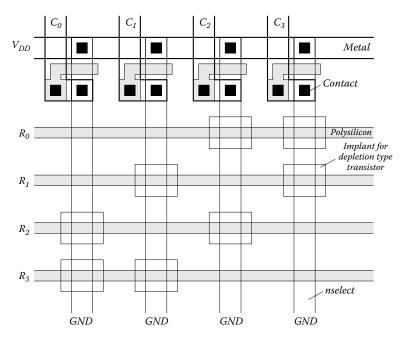

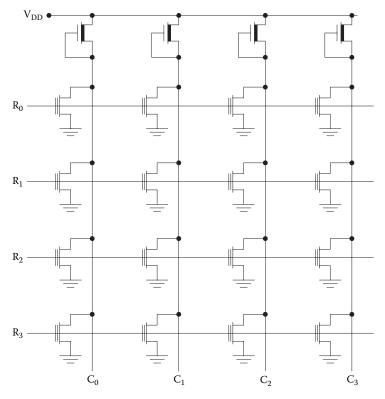

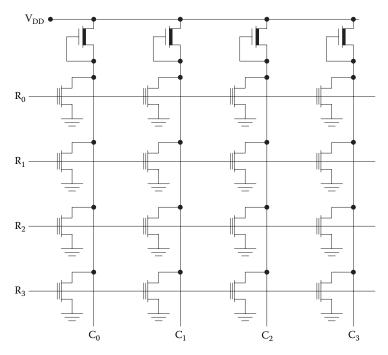

|     |        | 11.4.1 NOR Read-Only Memory                         |     |

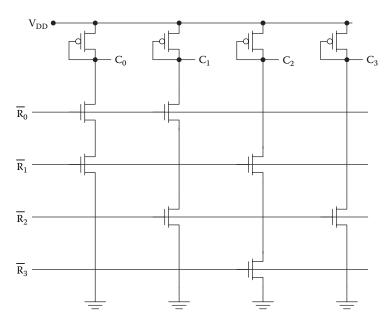

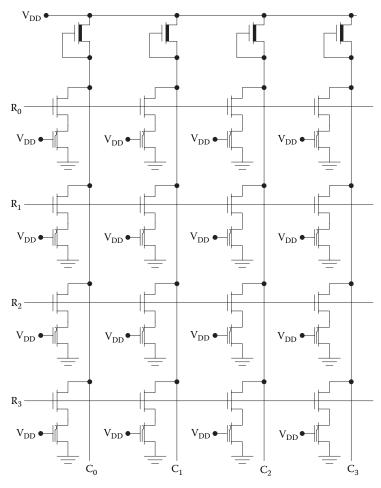

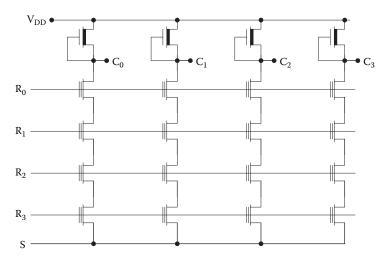

|     |        | 11.4.2 NAND Read-Only Memory                        | 445 |

|     | 11.5   | Programmable Read-Only Memory                       |     |

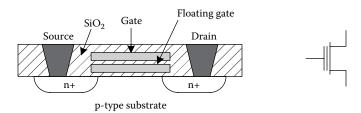

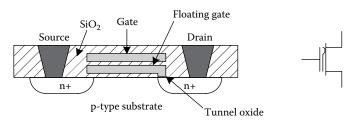

|     | 11.6   | Erasable Programmable Read-Only Memory              | 448 |

|     | 11.7   | Electrically Erasable Programmable Read-Only Memory |     |

|     | 11.8   | Flash Memory                                        | 453 |

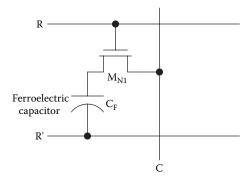

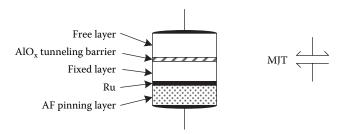

|     | 11.9   | Other Nonvolatile Memories                          | 455 |

|     | 11.10  | Access Times in Digital Memories                    | 459 |

|     | 11.11  | Row and Column Decoder Design                       |     |

|     | 11.12  | Practical Perspective                               | 462 |

|     | 11.13  | Summary                                             | 462 |

|     | 11.14  | Exercises                                           | 465 |

|     | Refere | nces                                                | 466 |

| 12. | Input/ | Output and Interface Circuits                       | 471 |

|     | 12.1   | Introduction                                        | 471 |

|     | 12.2   | Input Electrostatic Discharge Protection            | 471 |

|     | 12.3   | Input Enable Circuits                               |     |

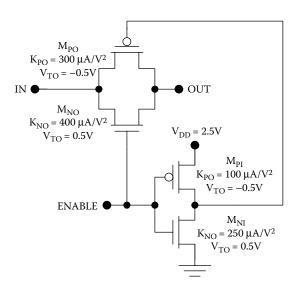

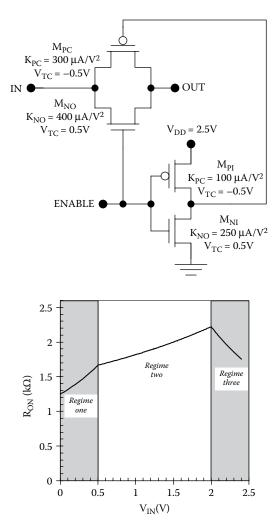

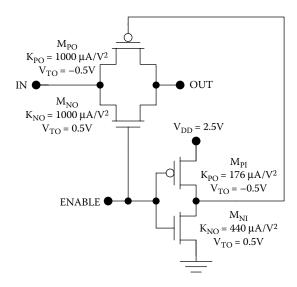

|     |        | 12.3.1 CMOS Transmission Gate                       | 473 |

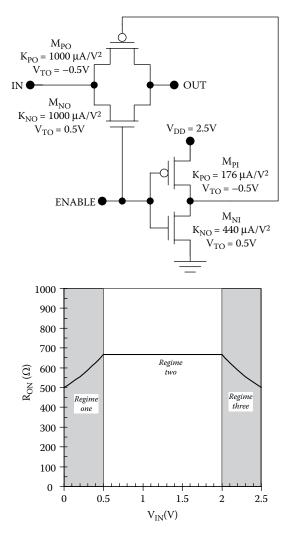

|     |        | 12.3.1.1 Regime One: n-MOS Linear and               |     |

|     |        | p-MOS Cutoff                                        | 475 |

|     |        | 12.3.1.2 Regime Two: n-MOS Linear and               |     |

|     |        | p-MOS Linear                                        | 475 |

xiv Contents

|           | 12.3.1.3 Regin                   | ne Three: n-MOS Cutoff and |     |

|-----------|----------------------------------|----------------------------|-----|

|           | p-MC                             | OS Linear                  | 475 |

|           | 12.3.1.4 Overa                   | all Characteristic of CMOS |     |

|           |                                  | mission Gate               | 476 |

| 12.4      | <b>CMOS Output Buffers</b>       | ·                          | 478 |

| 12.5      |                                  |                            |     |

| 12.6      |                                  |                            |     |

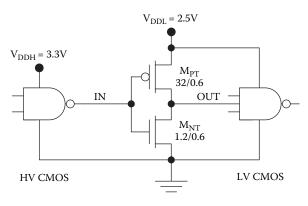

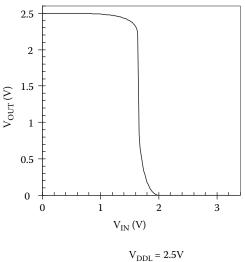

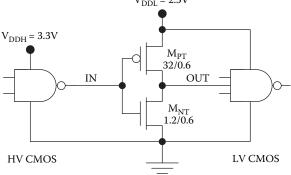

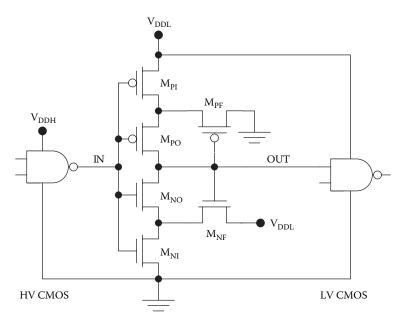

|           | 12.6.1 High-Voltage C            | CMOS to Low-Voltage CMOS   | 487 |

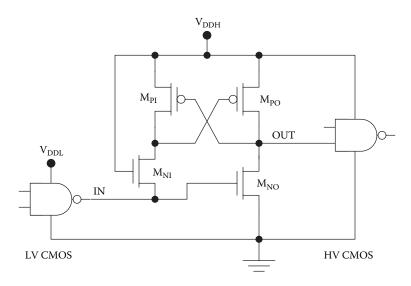

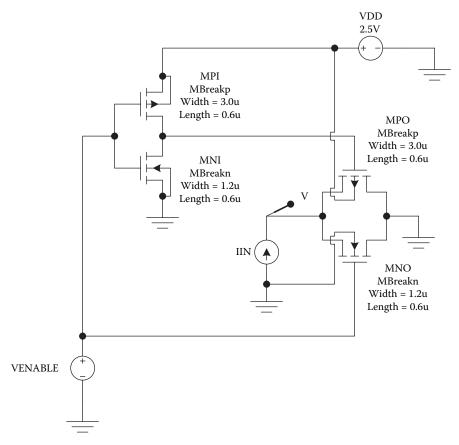

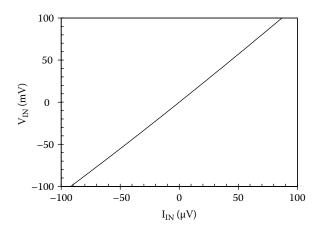

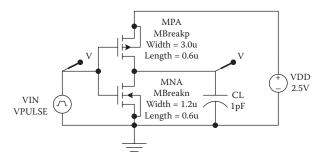

|           |                                  | MOS to High-Voltage CMOS   |     |

| 12.7      |                                  | S                          |     |

| 12.8      |                                  |                            |     |

| 12.9      |                                  |                            |     |

| 12.10     |                                  |                            |     |

| Refere    |                                  |                            |     |

|           |                                  |                            |     |

| Annondiv  | A List of Symbols                |                            | 503 |

| Appendix  | A List of Symbols                |                            |     |

| Annondiv  | R International Syste            | m of Units                 | 511 |

| Appendix  | D International Syste            | III OI CIIIts              |     |

| Annendix  | C Unit Profixes                  |                            | 513 |

| трренил   | C OIIIt I Tellacs                |                            |     |

| Annendix  | D Greek Alphabet                 |                            | 515 |

| - ppenuix | D Greek mpnubet                  |                            |     |

| Appendix  | E Physical Constants             |                            | 517 |

| - ppenuix | 2 Thyorean Constants             |                            |     |

| Appendix  | F Properties of Si and           | l Ge at 300 K              | 519 |

|           | r                                |                            |     |

| Appendix  | G Properties of SiO <sub>2</sub> | at 300 K                   | 521 |

|           | 2 F                              |                            |     |

| Appendix  | H Important Equation             | ns                         | 523 |

| I I       | 1                                |                            |     |

| Appendix  | I Design Rules                   |                            | 525 |

| 11        | 0                                |                            |     |

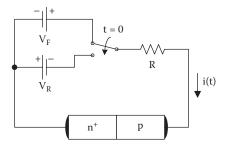

| Appendix  | J p-n Junction Switch            | ing Transients             | 535 |

| 11        | , ,                              | 8                          |     |

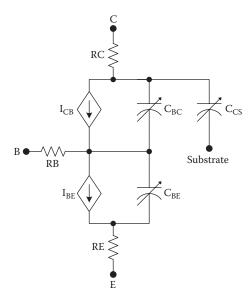

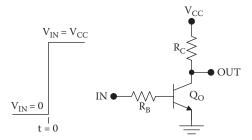

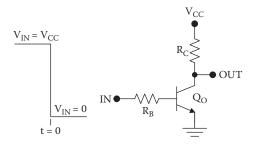

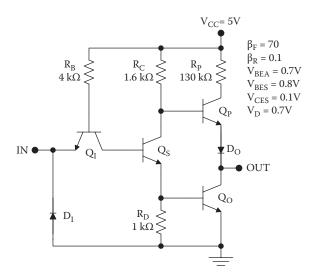

| Appendix  | K Bipolar and BiCMO              | OS Circuits                | 539 |

|           |                                  |                            |     |

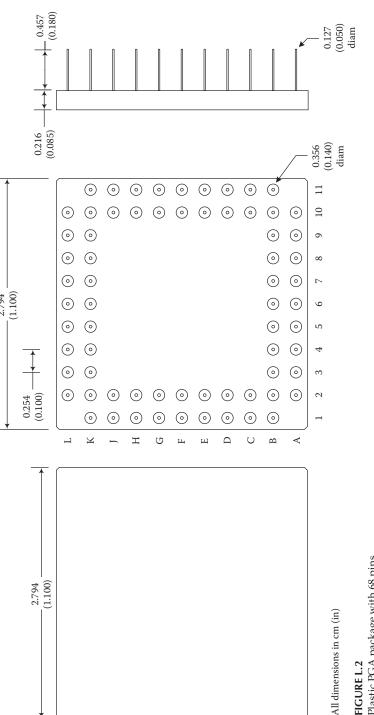

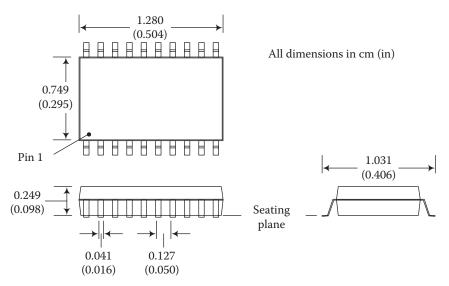

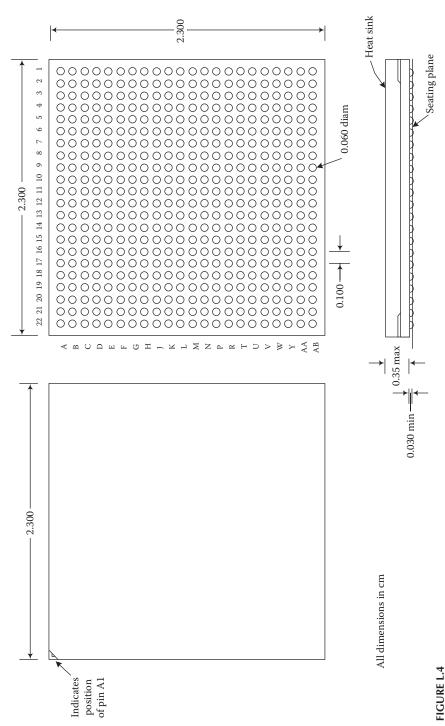

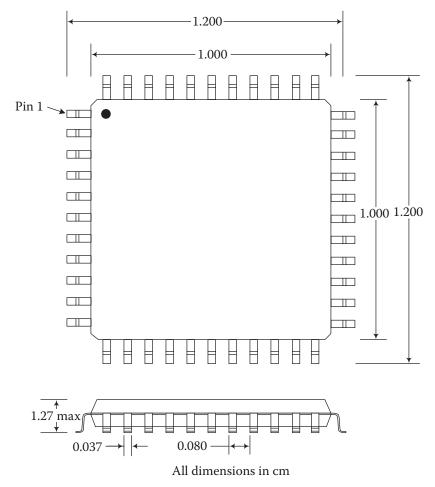

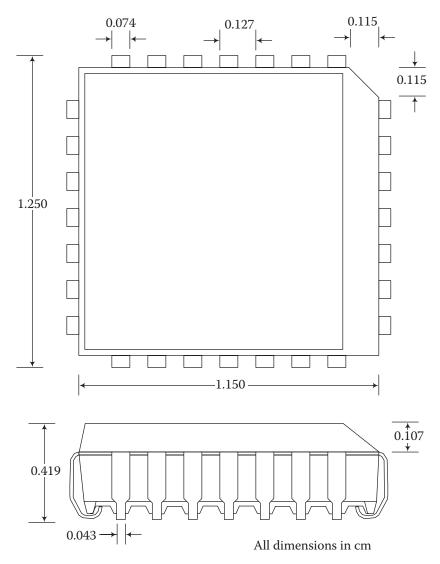

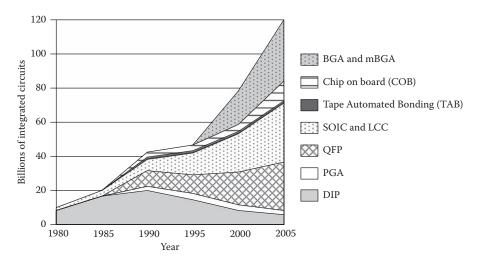

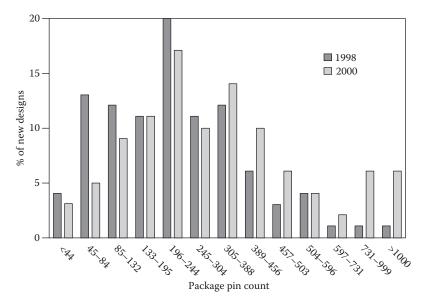

| Appendix  | L Integrated Circuit I           | Package                    | 559 |

|           | <u> </u>                         |                            |     |

| Index     |                                  |                            | 585 |

#### Preface

Today, there is no field of enterprise more dynamic or challenging than digital integrated circuits. Since the invention of the integrated circuit in 1958, our ability to pack transistors on a single chip of silicon has doubled roughly every 18–24 months, as described by Moore's law. As a consequence, the functionality and performance of digital integrated circuits have improved geometrically with time. This exponential progress is unmatched in any endeavor of mankind and has revolutionized the way we live and work.

The rapid progress in digital circuitry, and the relentless scaling of MOS transistors that brought it about, have broadened the interdisciplinary reach of the field. More than ever, the materials, processing, device physics, and circuit performance characteristics are inseparably linked. The original book, conceived in this interdisciplinary spirit and with a strong focus on principles, bridged a void that had existed between books on transistor electronics and those treating VLSI design and fabrication as a separate topic.

This second edition adheres to this same successful concept but is significantly improved in nearly every way, with four new chapters, more than 200 new illustrations, and support provided on a dynamic website (http://www.engr.uconn.edu/ece/books/ayers), including a section for instructors. An all-new chapter describes the integrated circuit fabrication process with detailed illustrations and discussions of the dual damascene process for copper interconnect, metal gates, and high-κ gate dielectric. The expanded chapter on the MOS transistor includes new material on the physics of short-channel devices. CMOS circuitry has been covered in greater detail by incorporating numerous new examples and short-channel behavior.

Like the first edition, this book bridges the gap between courses in transistor electronics and VLSI design or fabrication. It serves as a crucial link for integrated circuit engineers, because they make the cross-disciplinary connections to guide them in more advanced work. For pedagogical reasons, this book uses SPICE level 1 models (similar to the transistor electronics courses) but introduces BSIM models that are indispensable for VLSI design. This approach makes it possible to draw direct connections between the hand analysis and the SPICE models for the development of a strong and intuitive sense of device and circuit design. Once these connections are made, the BSIM device models can be better appreciated as incorporating many second-order and empirical corrections to the predictions of the level 1 model.

Digital Integrated Circuits, Second Edition, focusing on principles and presented from a modern interdisciplinary view, should serve integrated circuits engineers from all disciplines for years to come.

#### About the Author

John E. Ayers grew up eight miles from an integrated circuit design and fabrication facility, where he worked as a technician and first developed his passionate interest in the topic. After earning a BSEE degree from the University of Maine (Orono, Maine) in 1984, he worked as an integrated circuit test engineer for National Semiconductor (South Portland, Maine). He worked for six years at Rensselaer Polytechnic Institute (Troy, New York) and Philips Laboratories (Briarcliff, New York) on semiconductor material growth and characterization, earning the MSEE in 1987 and the PhDEE in 1990, both from Rensselaer Polytechnic Institute. Since then, he has been employed in academic research and teaching at the University of Connecticut (Storrs, Connecticut), where he has taught the course on digital integrated circuits for a number of years. He has been honored with the Electrical and Computer Engineering Best Teacher Award (2003–2004 and 2004–2005) and the School of Engineering Outstanding Teaching Award (2000–2001) and is a University of Connecticut Teaching Fellow (1999–2000). Ayers has authored more than 60 journal and conference papers as well as three books. He is a member of Eta Kappa Nu, Tau Beta Pi, and Phi Kappa Phi and is a senior member of the Institute of Electrical and Electronics Engineers. He lives in Ashford, Connecticut, and enjoys running, hiking, and bicycling with his wife and three children.

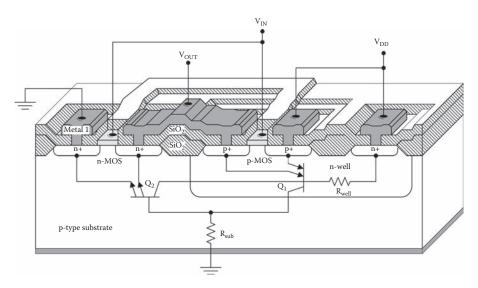

#### 1.1 Historical Perspective and Moore's Law

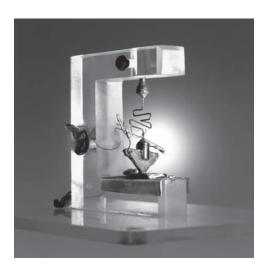

Since the demonstration of the first transistor [1–4] at Bell Laboratories in 1947 (Figure 1.1), rapid progress in the design and manufacture of semi-conductors has led to gigahertz microprocessors and gigabit memories today. The invention of the integrated circuit (Figure 1.2) in 1958 [5, 6], and subsequent improvements on the concept in the 1960s, made it possible to combine multiple devices on a single chip of silicon instead of wiring together devices on a circuit board. Thus, it was possible to reduce the size, weight, and cost of a circuit even while increasing its functionality. These breakthroughs eventually allowed the fabrication of billions of transistors in a single chip of silicon, enabling computing power far

**FIGURE 1.1** The first transistor, invented at Bell Laboratories in 1947. (From Lucent Technologies Inc./Bell Labs. With permission.)

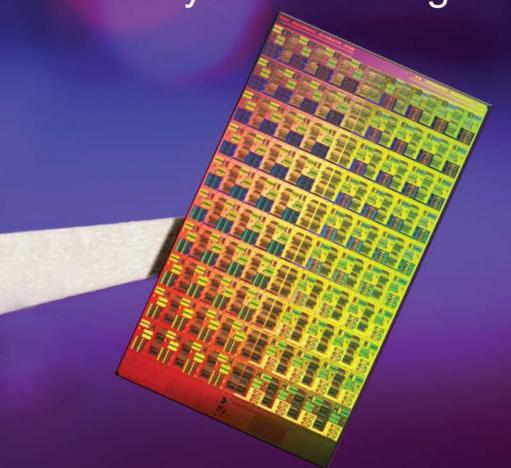

#### FIGURE 1.2

The first commercial integrated circuit, developed by Robert Noyce at Fairchild Semiconductor. The integrated circuit was invented by Robert Noyce of Fairchild Semiconductor and Jack Kilby of Texas Instruments at about the same time. (From Fairchild Semiconductor. With permission.)

beyond that achievable by wiring together discrete transistors. At the present time, state-of-the-art microprocessor chips contain hundreds of millions of transistors, whereas memory chips contain up to several billion transistors.

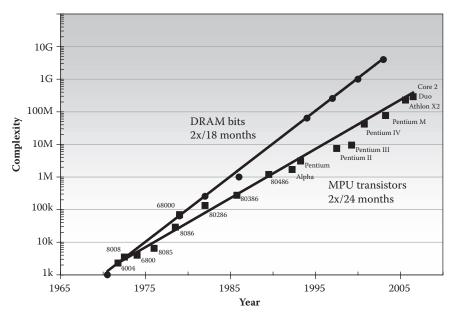

Soon after the realization of integrated circuits, Intel cofounder Gordon Moore noted that the complexity of integrated circuits was increasing exponentially with time. Moore stated that the "complexity" of integrated circuits with "minimum component costs" was doubling every 12 months [7]. Since that time, several variations of "Moore's law" have been stated. Usually, it is noted that the number of transistors per microprocessor chip doubles every 24 months, whereas the number of bits per dynamic random access memory (DRAM) chip doubles every 18 months. Remarkably, this rate of progress has been maintained for more than three decades! Figure 1.3 illustrates this exponential progress for microprocessors and DRAMs. Similar exponential trends have been established for flash memories and application-specific integrated circuits (ASICs). However, memory chips have outpaced microprocessors because of their simpler designs and built-in redundancy.

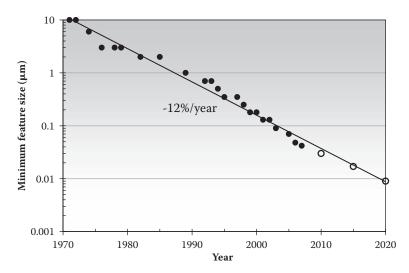

Industry has kept pace with Moore's law primarily by scaling down the dimensions of transistors through improved lithography [8, 9], but chip size has also been increased. Transistor miniaturization has been pursued aggressively and has brought about improvements in circuit performance and cost as well as density. A key parameter describing this scaling is the "minimum feature size" for the transfer of circuit patterns from a computer design to the semiconductor wafer. Figure 1.4 shows the historical evolution

**FIGURE 1.3** According to Moore's law, the complexity of integrated circuits has increased exponentially with time. Historically, the number of transistors per microprocessor unit (MPU) doubles every 24 months; the number of bits per DRAM chip doubles every 18 months.

of the minimum feature size, along with projections out to the year 2020. Historically, much of the progress shown in Figure 1.4 was achieved by decreasing the wavelength used in lithographic tools. However, at the present time, technical solutions for the lithographic requirements of 2020 and beyond have not been found.

With the goal of extending the historic trends in integrated circuit technology, the Semiconductor Industry Association in the United States [10] produced the National Technology Roadmap for Semiconductors in 1992. This roadmap defined industry-wide technology goals with a 15-year horizon and was revised in 1994 and 1997. In 1998, after the globalization of the semiconductor industry, an International Technology Roadmap for Semiconductors (ITRS) was developed with participation from the semiconductor industries in Europe, Japan, Korea, and Taiwan [11]. Full ITRS reports are published biannually, in odd years, and update reports are published in even years.

Each ITRS report projects industry trends 15 years into the future. What, then, is the digital integrated circuit industry expected to look like in 2020? According to the 2007 ITRS, the starting silicon wafers will grow to 450 mm in diameter, whereas transistor gate lengths will diminish to 5.6 nm. As a consequence of these developments, flash memory will be able to

**FIGURE 1.4** Minimum feature size for the fabrication of integrated circuits as a function of time.

store one terabit on a single chip, and you will be able to purchase a 12.4 GHz processor with 6.1 billion transistors and 7902 pins for about 0.24 microcents per transistor! These and other important trends are charted in Table 1.1.

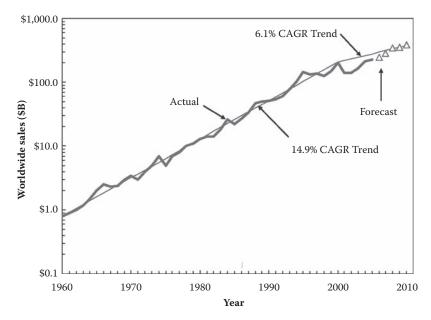

The rapid progress in digital integrated circuits has been fueled by strong demand from a number of driving force applications. During the first decade after the invention of the integrated circuit, mainframe computers represented the driving application. In the 1980s, there was a shift to personal computers, consumer electronics, and digital communication. During the 1990s, wireless communication, portable computers, and handheld devices came into play. Today, video-on-demand, multimedia applications, and network computing are some of the driving forces behind the technology. Sales of semiconductors have increased at a 14.9% compound annual growth rate since the invention of the integrated circuit (see Figure 1.5), now making up 20% of the world electronics market and 2% of the gross world product (GWP).

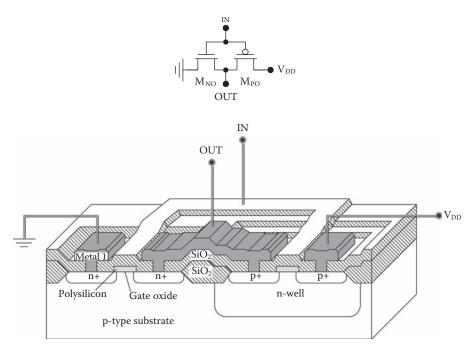

At the present time, most digital integrated circuits use the CMOS circuit family, so named because it uses complementary metal oxide semiconductor transistors (MOS transistors, or MOSFETs). However, this hasn't always been the case. The first integrated circuit was based on bipolar junction transistors (BJTs), and numerous families of digital integrated circuits have been realized using BJTs; these include resistor transistor logic, diode transistor logic, transistor transistor logic (TTL), integrated injection logic, and emitter coupled logic (ECL). New bipolar circuit families were still being developed in the 1980s, because BJTs provided a speed advantage over metal oxide semiconductor field effect transistors (MOSFETs) using the lithographic design

**TABLE 1.1**Semiconductor Technology Trends

| Year of production                                      | 2007 | 2010  | 2015    | 2020   |

|---------------------------------------------------------|------|-------|---------|--------|

| Lithography                                             |      |       |         |        |

| DRAM stagger-contacted metal ½ pitch (nm)*              | 65   | 45    | 25      | 14     |

| MPU/ASIC stagger-contacted metal ½ pitch (nm)*          | 68   | 45    | 25      | 14     |

| Flash uncontacted poly Si ½ pitch*                      | 54   | 36    | 20      | 11     |

| MPU printed gate length (nm)                            | 42   | 30    | 17      | 9      |

| MPU physical gate length (nm)                           | 25   | 18    | 10      | 5.6    |

| # mask levels, MPU                                      | 33   | 35    | 37      | 39     |

| # mask levels, DRAM                                     | 24   | 26    | 26      | 26     |

| Maximum number of wiring levels                         | 11   | 12    | 13      | 14     |

| MPU high performance                                    |      |       |         |        |

| MPU transistors per chip (millions)                     | 386  | 773   | 1546    | 6184   |

| MPU chip size (mm²)                                     | 140  | 140   | 88      | 111    |

| MPU cost per transistor (microcents) (high performance) | 12.2 | 4.3   | 0.76    | 0.24   |

| MPU total package pins (high performance)               | 4000 | 4851  | 6191    | 7902   |

| Clock frequency (GHz)                                   | 4.70 | 5.875 | 8.522   | 12.361 |

| DRAM                                                    |      |       |         |        |

| DRAM bits per chip (billions)                           | 2G   | 4G    | 8G      | 32G    |

| DRAM chip size (mm²)                                    | 93   | 93    | 59      | 74     |

| DRAM cost per bit (microcents)                          | 0.96 | 0.34  | 0.06    | 0.01   |

| Flash memory                                            |      |       |         |        |

| Flash bits per chip (four level cell)                   | 32G  | 64G   | 128G    | 1024G  |

| Flash chip size (mm²)                                   | 144  | 128   | 81      | 102    |

| ASICs                                                   |      |       |         |        |

| ASIC package pins (high performance)                    | 4000 | 4851  | 6191    | 7902   |

| General                                                 |      |       |         |        |

| On-chip clock frequency (GHz)                           | 4.70 | 5.875 | 8.522   | 12.361 |

| Supply voltage $V_{DD}(V)$ (high performance)           | 1.1  | 1.0   | 0.80    | 0.65   |

| Chip power dissipation (W) (high performance)           | 189  | 198   | 198     | 198    |

| Silicon wafer diameter (mm)                             | 300  | 300   | 300/450 | 450    |

Source: The International Technology Roadmap for Semiconductors, http://public.itrs.net.

rules in place at that time. By the 1990s, CMOS had become the dominant technology, but bipolar circuits, and also bipolar-CMOS (BiCMOS) circuits, remained commercially important into the beginning of the 21st century.

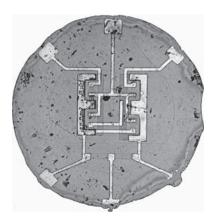

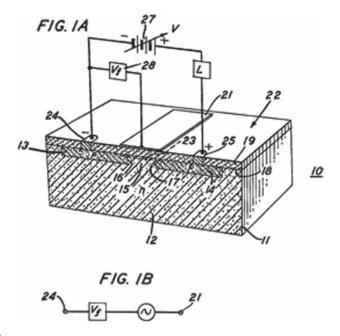

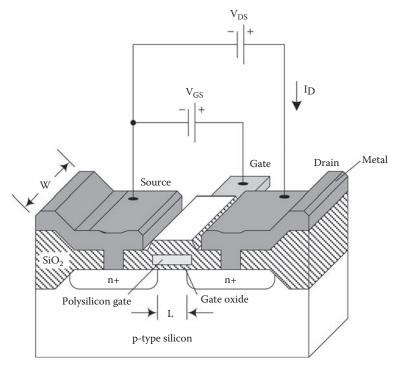

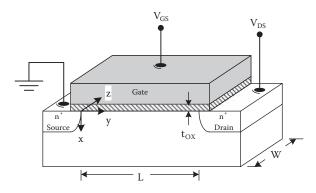

The MOSFET was invented in 1930 by Lilienfeld [12], but the first working device was not demonstrated until 1960 by Kahng and Atalla (see Figure 1.6) [13, 14]. MOS transistors allowed the integration of more functionality on an integrated circuit than BJTs for two reasons. First, MOSFETs are

<sup>\*</sup> The half-pitch is defined as one-half of the center-to-center distance for two wires defined on the chip surface.

**FIGURE 1.5** Worldwide sales of integrated circuits have increased with a 14.9% compound annual growth rate since 1960 and now account for 2% of the gross world product. (From Kumar, R., *IEEE Solid-State Circuits* 12, 22–27, 2007. With permission.)

**FIGURE 1.6** The first MOSFET. Electric field controlled semiconductor device. (From Kahng, D., and Atalla, M.M., U.S. Patent 3,102,230, filed May 31, 1960, and issued Aug. 27, 1963.)

inherently smaller than BJTs using the same set of layout design rules. Second, MOSFETs are voltage controlled and require no biasing resistors like BJTs, which are current controlled. Integrated resistors take up considerable chip area, because they are typically much larger than either BJTs or MOSFETs.

The first microprocessor was the 4004, introduced by Intel in 1971 (see Figure 1.7). It was realized using the PMOS circuit family and included 2300 p-channel MOSFETs. PMOS was used because, at that time, the repeatable manufacture of enhancement type (normally off) n-channel MOSFETs was not possible because of oxide and contamination-related problems. For these reasons, PMOS was used for microprocessors and their associated components such as memories and peripheral interfaces for a short time.

By 1974, with the problems of n-channel transistors solved, PMOS circuits were replaced by superior NMOS (n-channel MOSFETs) circuits. Notable examples were the 6800 and 8080 microprocessors.

Soon thereafter, the ability to manufacture both n-MOS and p-MOS transistors on the same wafer enabled the development of CMOS digital integrated circuits. The key advantage of this circuit family, relative to PMOS and NMOS, is its low static power dissipation. After the invention of CMOS in 1963, the 4000 series of CMOS logic gates was developed in 1968, and CMOS microprocessors emerged in the mid-1970s.

Even after the establishment of CMOS as a mainstream digital integrated circuit technology, bipolar circuits temporarily maintained their edge in critical high-speed applications. This is because bipolar transistors exhibited much higher transconductance values than MOSFETs, for a given device size, and could therefore drive high-capacitance off-chip loads at higher data rates. Bipolar circuit families, such as ECL and Schottky transistor-transistor logic (STTL), found use in high-performance computing, supercomputers, and high bit rate communication. Even nonsilicon integrated circuits, such as direct coupled FET logic circuits

FIGURE 1.7

The Intel 4004 microprocessor. (From Intel. With permission.)

fabricated in gallium arsenide or indium phosphide, were used in high-end microprocessor and digital communication applications. Eventually, however, the relentless scaling of transistor dimensions helped CMOS overtake bipolar circuit families in terms of on-chip switching speed *and* off-chip data rates.

There are limits to the scaling and performance of CMOS circuits, however. At some point in time, it will be necessary to make the transition to a new, higher-density, higher-performance circuit family. We cannot be sure when this will happen or what types of devices might replace MOSFETs, but it is sure to happen. It is important to study digital integrated circuits in this light, with an emphasis on general principles, but the examples are oriented to the CMOS circuit family.

#### 1.2 Electrical Properties of Digital Integrated Circuits

In digital circuitry, voltage signals take on one of two (or possibly more) discrete levels. This contrasts with the case of analog circuits and systems, in which signals can take on any value in a continuous range. In the binary digital systems commonly in use today, signals exist as sequences of ones and zeroes. The advantage of digitizing analog signals is that they can be stored, duplicated, and transmitted repeatedly without any loss in quality.

Digital circuits use semiconductor electronic devices to process or combine binary signals in a desired manner. These digital circuits are called logic gates, and, in practice, the two binary values are represented by two distinct voltage levels.

Digital integrated circuits involve the fabrication of many different electronic devices in one chip of silicon (or some other semiconductor crystal). The level of integration is classified according to the number of gates that have been integrated on a single chip. The various levels of integration have been called small scale integration (SSI), medium scale integration (MSI), large scale integration (LSI), very large scale integration (VLSI), and ultra large scale integration (ULSI) and are listed in Table 1.2. At the present time, integrated circuits at all of these levels of complexity are manufactured and used for various applications. Often, the distinction between VLSI and ULSI is not made, so that state-of-the art circuits are often referred to as "VLSI" even today.

Another level of integration, called "wafer scale integration," was proposed some years ago. The idea was to fabricate a single integrated circuit using an entire silicon wafer. This goal turned out to be far too ambitious because the size of silicon wafers grew to 200 mm and then 300 mm. Nonetheless, it has become feasible to implement "system on a chip" designs, in which an entire

| TABLE 1.2             |

|-----------------------|

| Levels of Integration |

| Level of integration         | Gates/chip |  |

|------------------------------|------------|--|

| Small scale integration      | 1–10       |  |

| Medium scale integration     | 10-100     |  |

| Large scale integration      | $100-10^4$ |  |

| Very large scale integration | >104       |  |

computer system is built in a single chip of silicon. It goes without saying that this approach is superior in size, cost, and performance compared with the traditional approach of wiring together many integrated circuits on a printed circuit board.

In this section, we will describe the electrical properties of digital integrated circuits at the gate level. Ideally, a logic gate should process an infinite number of inputs, perform some logic function with zero time delay, be completely immune to the effects of loading by other gates, and consume zero power. Although this goal has not been achieved, it serves as a starting point for discussing the properties of real logic gates.

#### 1.2.1 Logic Function

To be useful, a logic gate must perform some Boolean logic function. Boolean algebra, named after mathematician George Boole, is a system of mathematics based on the binary number system. In this number system, each binary digit, or bit, takes on a value of "0" or "1." Sometimes a 1 is referred to as a "true" result, whereas a 0 is referred to as a "false" result.

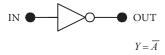

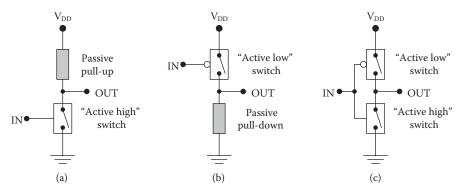

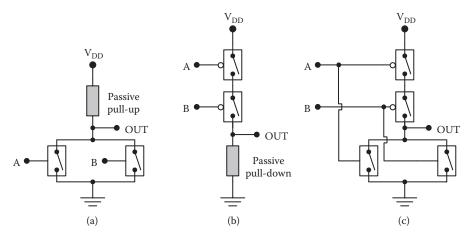

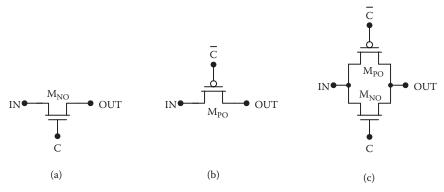

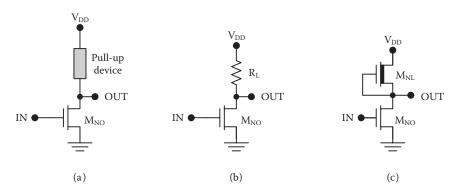

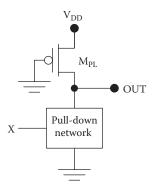

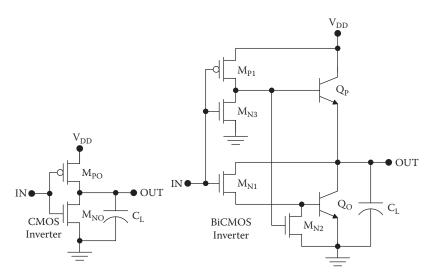

A commonly used logic gate is the one-input inverter, or NOT gate, shown in Figure 1.8. If the input A is true, then the output Y is not true and vice versa. The implementation of an inverter requires one or more switching devices. Three possible implementations are shown in Figure 1.9. Here, the switches are assumed to be three-terminal devices, but nonlinear two-terminal devices can also act as switches.

The active pull-down implementation of Figure 1.9a uses a single switch device connected between the output and ground. With a low (logic zero)

| IN | OUT |

|----|-----|

| 0  | 1   |

| 1  | 0   |

FIGURE 1.8 Inverter.

**FIGURE 1.9** Inverter circuit designs: (a), Active pull-down design, (b) active pull-up design, and (c) fully active design.

input, the switch is "off" (open) and the output is brought high by the passive pull-up device. (The passive pull-up device can be a resistor, but other devices may be used as well.) With a high (logic one) input, the switch is "on" (closed) and the output goes low. Therefore, the circuit functions as an inverter, and this type of switch is called an "active high" device. The active pull-down circuit design dissipates steady power under the low output condition, in which both the switch and the passive design are conducting.

In the active pull-up design of Figure 1.9b, the switch is connected between the supply voltage  $V_{\rm DD}$  and the output, and a passive pull-down device is used. The circuit still functions as an inverter, as long as an "active low" switch is used. Steady power dissipation occurs in this circuit with the high output condition, as a result of the simultaneous conduction of the switch and the passive design.

The fully active inverter design of Figure 1.9c uses two switch devices; the pull-down switch is active high, whereas the pull-up switch has active low character. It is possible to design this circuit so that the two switches do not conduct simultaneously under static conditions, so the average dissipation can be reduced dramatically.

The switch devices in Figure 1.9 may be any three-terminal active devices. If current-controlled devices are used, such as bipolar junction transistors, it is necessary to include biasing circuitry. Simpler implementations stem from the use of voltage-controlled devices such as MOS transistors.

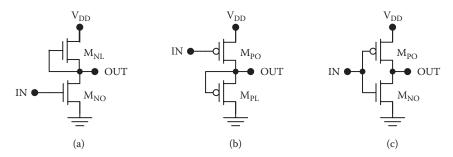

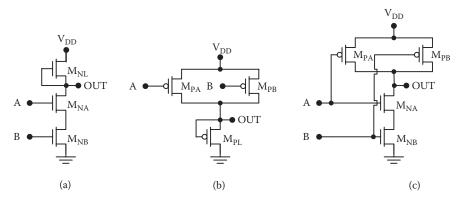

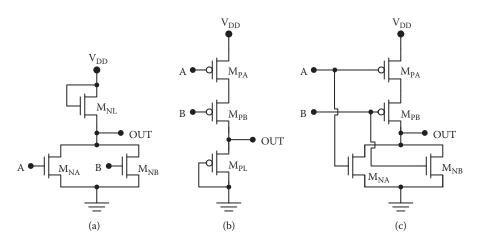

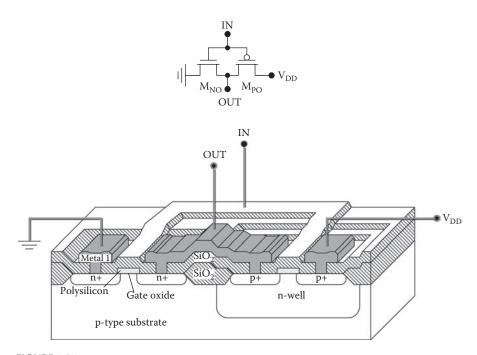

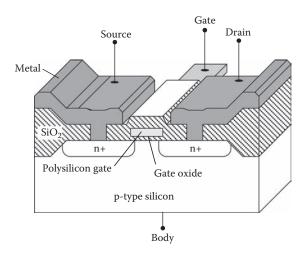

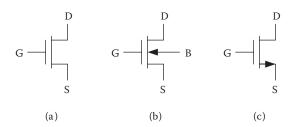

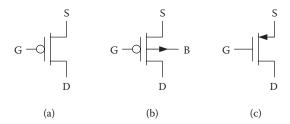

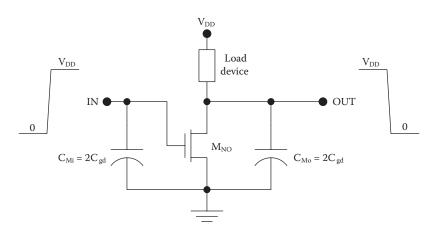

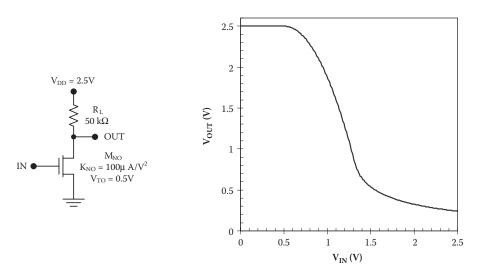

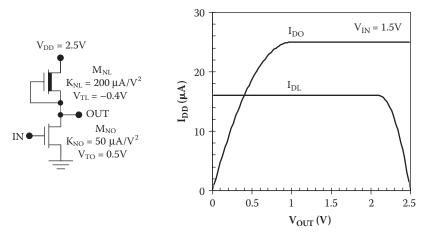

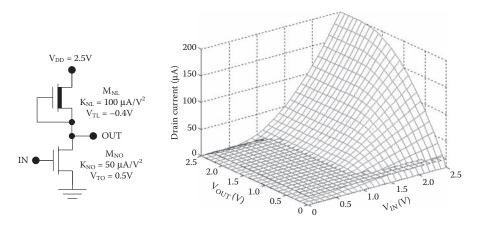

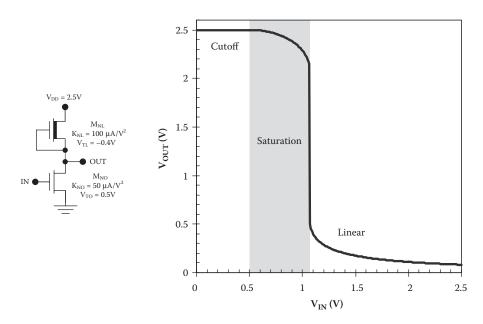

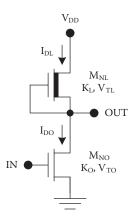

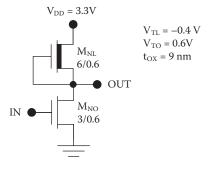

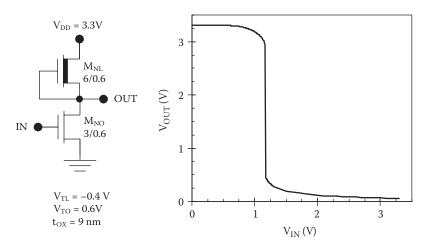

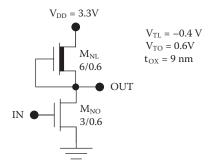

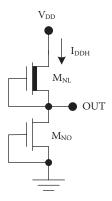

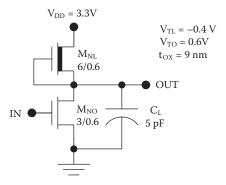

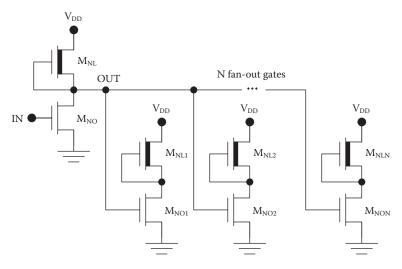

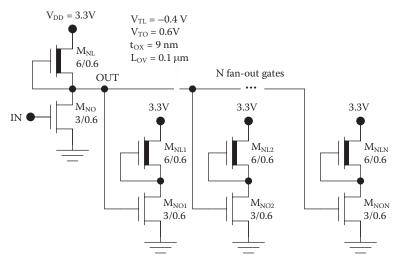

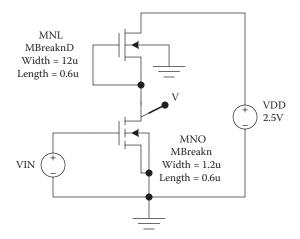

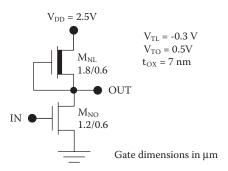

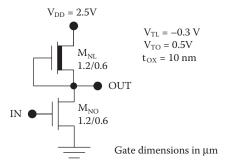

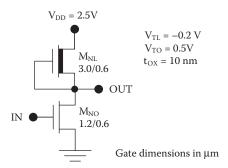

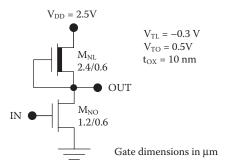

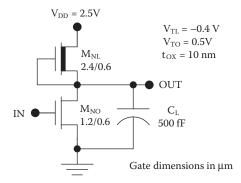

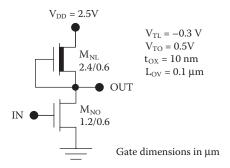

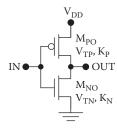

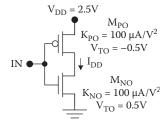

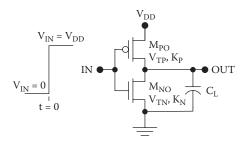

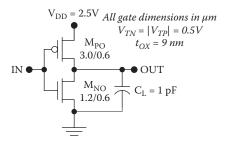

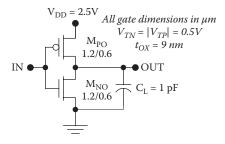

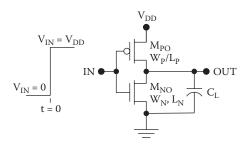

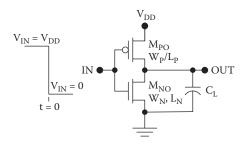

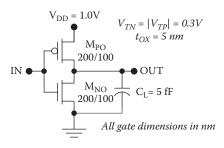

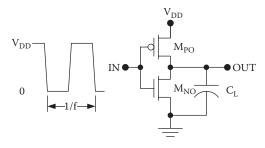

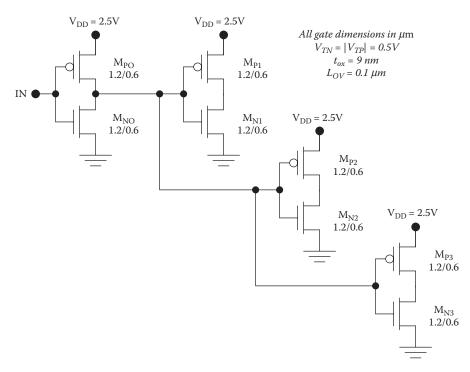

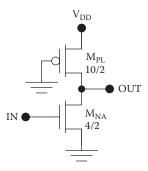

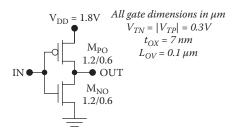

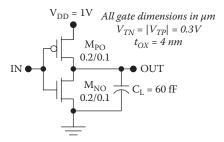

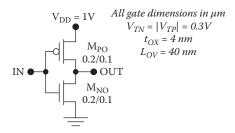

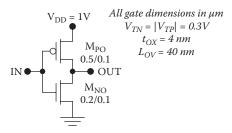

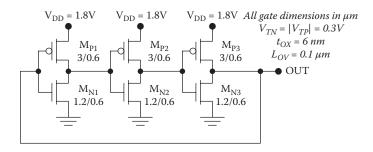

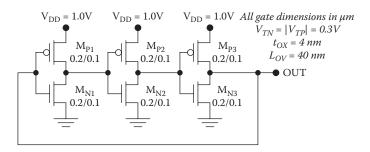

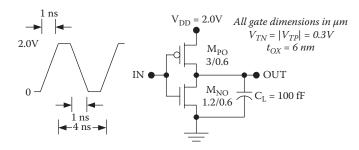

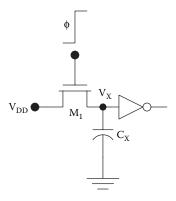

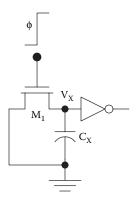

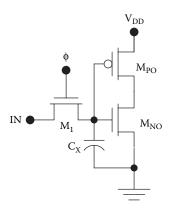

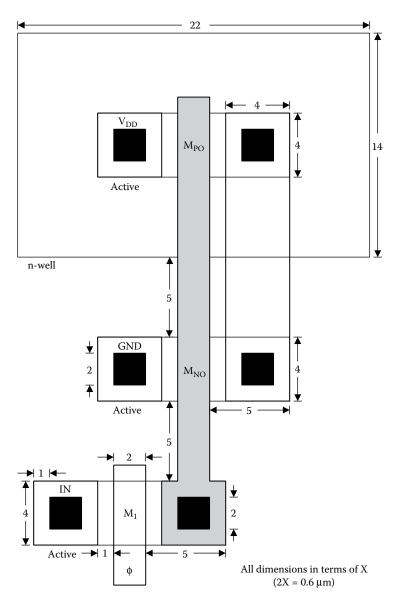

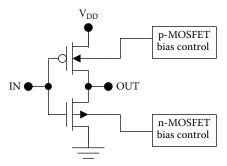

Figure 1.10 shows inverter circuit implementations based on the use of MOSFETs. The active pull-down design of Figure 1.10a uses all n-channel MOSFETs, the active pull-up design of Figure 1.10b uses all p-channel MOSFETs, and the fully active design of Figure 1.10c uses complementary n-channel and p-channel MOSFETs. These three circuit families are referred to as NMOS, PMOS, and CMOS, respectively.

FIGURE 1.10

Inverter circuit implementations using MOSFETs: (a) Active pull-down circuit constructed with n-channel MOSFETs, (b) active pull-up circuit using p-channel MOSFETs, and (c) fully active circuit using complementary MOSFETs.

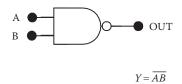

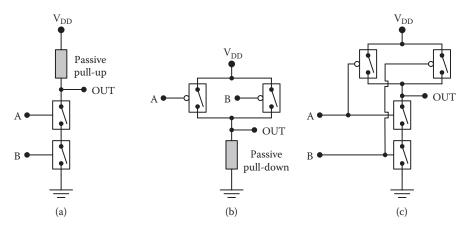

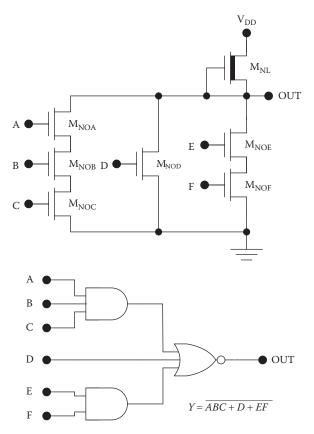

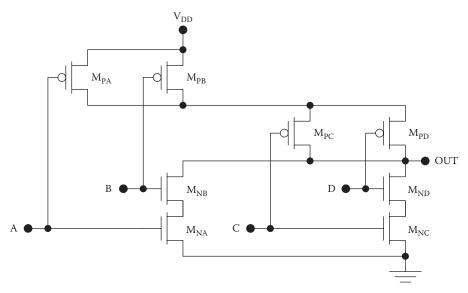

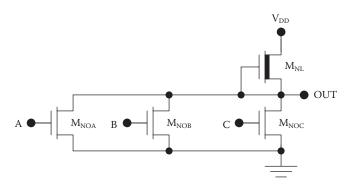

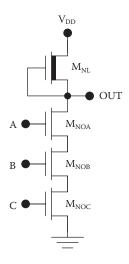

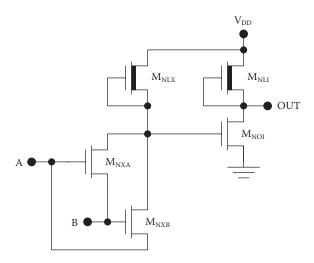

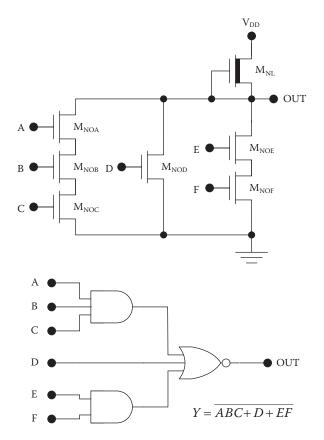

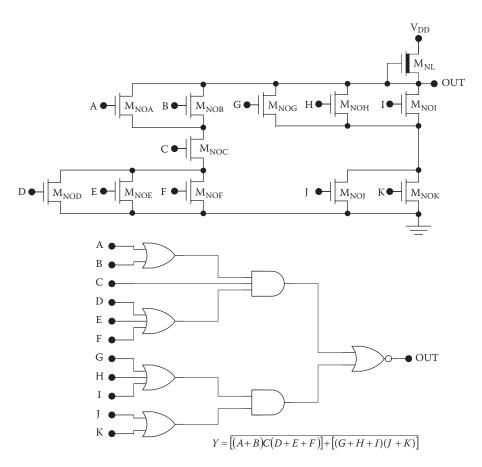

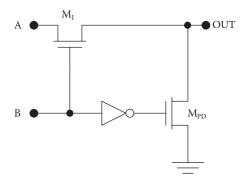

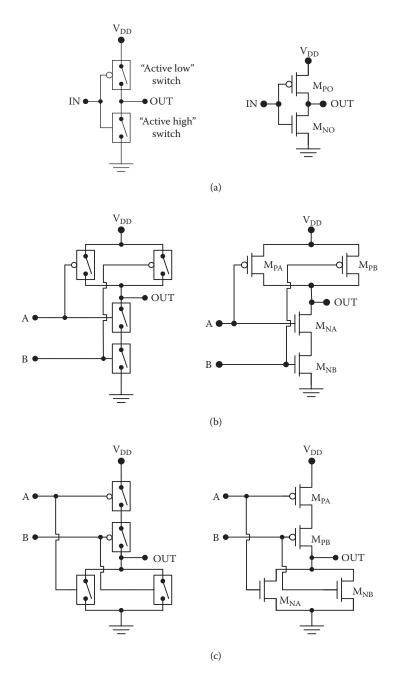

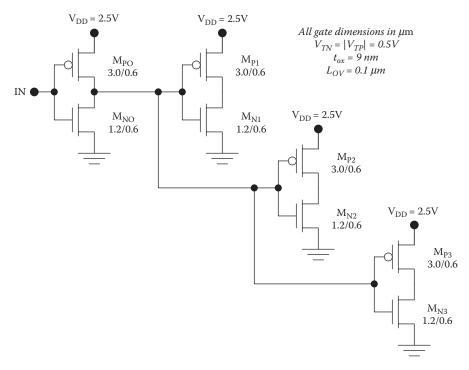

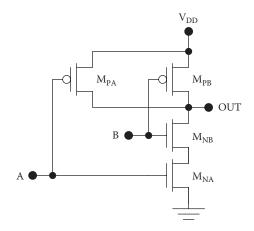

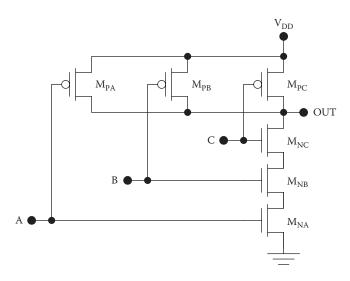

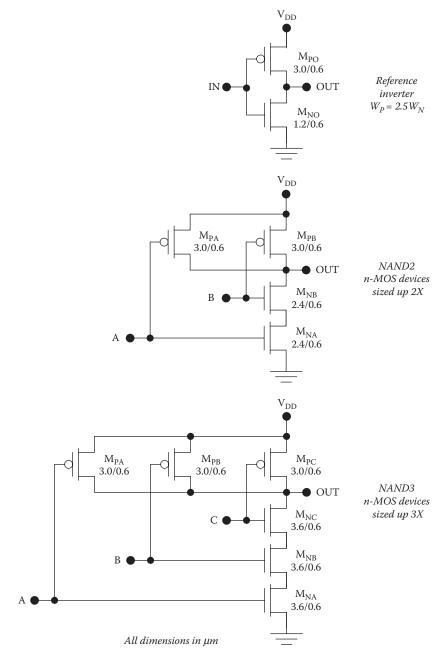

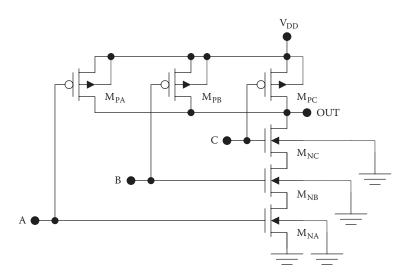

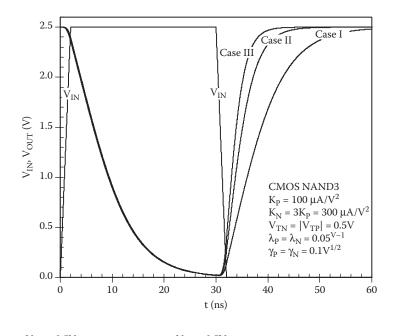

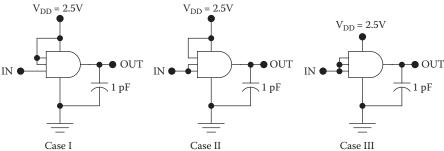

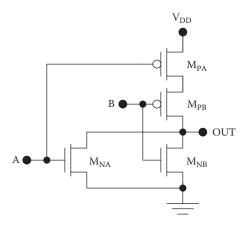

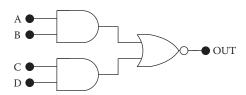

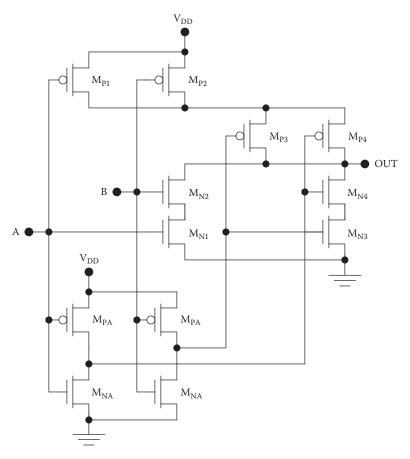

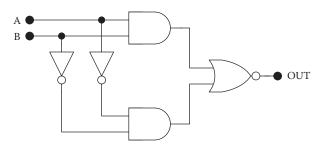

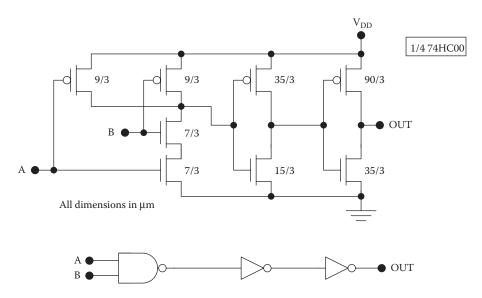

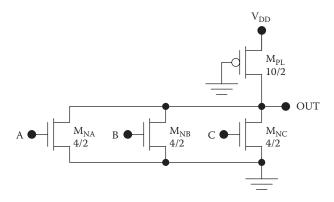

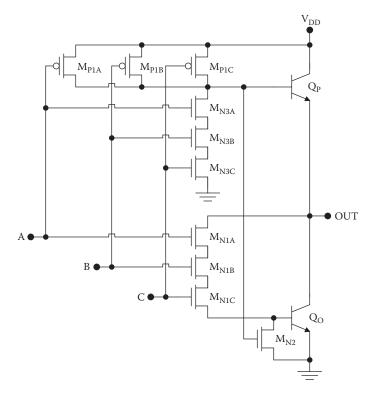

Other important logic functions include NAND and NOR. These can also be implemented in circuits using active pull down, active pull up, or both. Figure 1.11 shows the NAND (Not AND) gate with its truth table. Three possible circuit designs are provided in Figure 1.12. In the active pull-down circuit of Figure 1.12a, the active high switches are placed in series. Therefore, the output goes low if both inputs are high, causing both switches to turn "on." The active pull-up circuit of Figure 1.12b uses active low switches in parallel. In this case, the output goes high if either input goes low. The fully active circuit of Figure 1.12(c) uses both active high switches in series and active low switches in parallel. Figure 1.13 shows MOSFET-based two-input NAND gates designed using these three basic approaches.

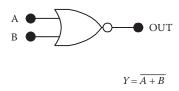

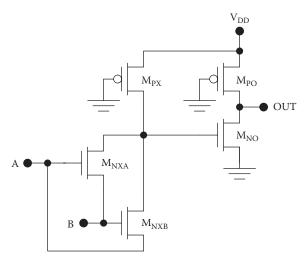

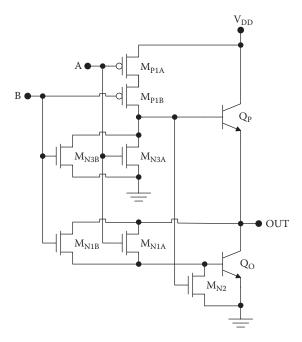

The two-input NOR (Not OR) gate is shown in Figure 1.14 with its truth table. The active pull-down design of Figure 1.15a uses two active high switches in parallel. If either input goes high, the associated switch turns on and brings the output low. The active pull-down design of Figure 1.15b uses two active low switches in series so that, if both inputs go low, the output goes high. The fully active design uses active high pull-down devices and active low pull-up devices. These three designs may be implemented using

| A | В | OUT |

|---|---|-----|

| 0 | 0 | 1   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 0   |

FIGURE 1.11 Two-input NAND gate.

**FIGURE 1.12**Design of two-input NAND gates: (a) Active pull-down circuit, (b) active pull-up circuit, and (c) completely active circuit design.

n-channel MOSFETs as the active high devices and p-channel MOSFETs as the active low devices as shown in Figure 1.16.

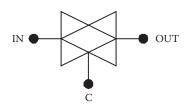

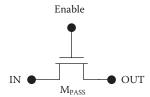

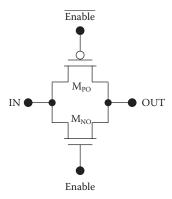

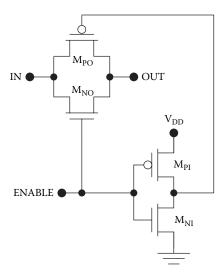

Another noteworthy circuit is the transmission gate, although it does not perform a Boolean algebraic function; this circuit is shown in Figure 1.17. With logic one applied to the control input, the transmission gate is enabled and the output follows the input. If logic zero is applied to the control input, the gate is disabled and the output is in the high impedance ("High Z") state regardless of the value of the input. With the output in the High Z state, the voltage at the output will float to whatever voltage is imposed by other

#### FIGURE 1.13

Two-input NAND circuit implementations using MOSFETs: (a) Active pull-down circuit constructed with n-channel MOSFETs, (b) active pull-up circuit using p-channel MOSFETs, and (c) fully active circuit using complementary MOSFETs.

| A | В | OUT |

|---|---|-----|

| 0 | 0 | 1   |

| 0 | 1 | 0   |

| 1 | 0 | 0   |

| 1 | 1 | 0   |

FIGURE 1.14 Two-input NOR gate.

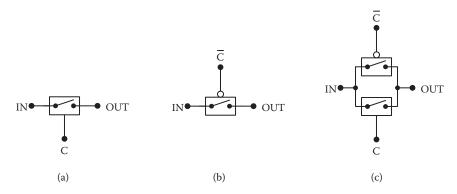

circuitry connected to the node. Therefore, transmission gates can be used to connect/disconnect logic blocks in a system. This is useful in bus-based systems and power-managed digital systems. Figure 1.18 illustrates possible designs for the transmission gate, and MOS circuit implementations are given in Figure 1.19.

Practical digital systems involve complex functions of many inputs. However, these complex functions can be realized using the basic functions described above. In fact, it is possible to realize any arbitrary logic function with any arbitrary number of inputs using just the NOT and OR functions or just the NOT and AND functions. There are a number of techniques available for the simplification of complex logic functions that make it possible to realize the necessary logic functions with maximum efficiency.

It is important to note that the circuits described in this section are all *static* logic gates. That is, they are designed to operate with steady (static) input and output voltages. *Dynamic* logic gates are also of tremendous importance in

**FIGURE 1.15**Design of two-input NOR gates: (a) Active pull-down design, (b) active pull-up design, and (c) fully active design.

FIGURE 1.16

Two-input NOR circuit implementations using MOSFETs: (a) Active pull-down circuit constructed with n-channel MOSFETs, (b) active pull-up circuit using p-channel MOSFETs, and (c) fully active circuit using complementary MOSFETs.

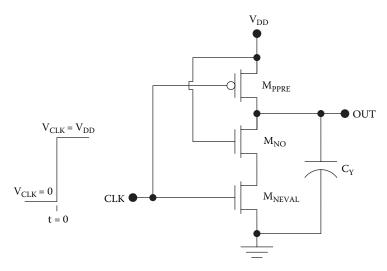

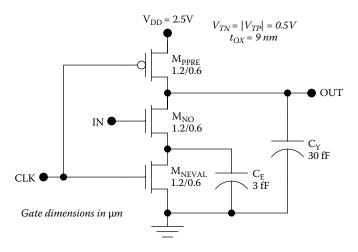

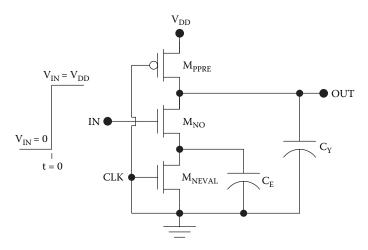

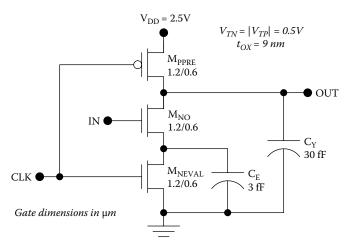

modern VLSI circuits. This type of gate circuit is controlled by a clock signal, and the output must be evaluated at particular points in the clock cycle. The principles underlying dynamic logic gates will be described in Chapter 8.

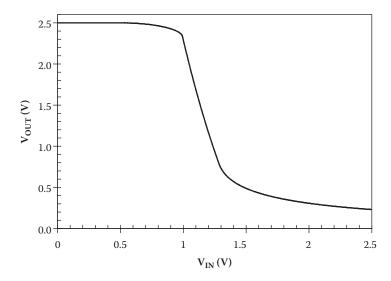

#### 1.2.2 Static Voltage Transfer Characteristics

An important electrical characteristic of any static logic gate is the *voltage transfer characteristic* (VTC). This is the steady-state output voltage versus input voltage characteristic. It is usually measured under low-frequency, quasi-static conditions.

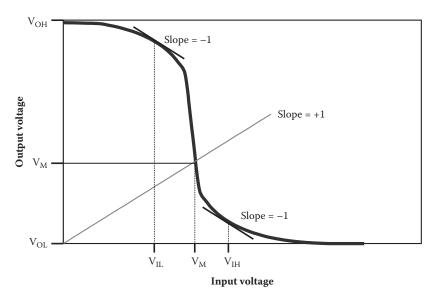

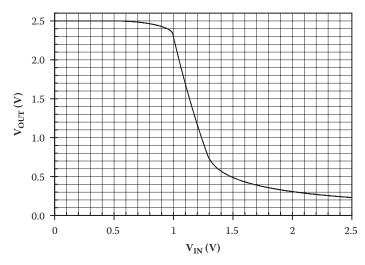

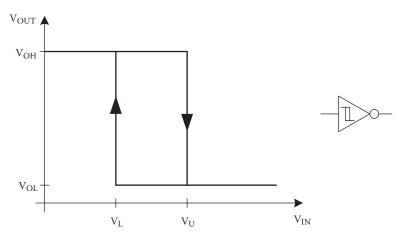

The important features of the VTC can be seen in Figure 1.20, which is a generic characteristic for an inverter. There are five critical voltages for the inverter:  $V_{\text{OL}}$ ,  $V_{\text{OH}}$ ,  $V_{\text{IL}}$ ,  $V_{\text{IH}}$ , and  $V_{\text{M}}$ .

| С | IN | OUT    |

|---|----|--------|

| 0 | 0  | High Z |

| 0 | 1  | High Z |

| 1 | 0  | 0      |

| 1 | 1  | 1      |

FIGURE 1.17 Transmission gate.

FIGURE 1.18

Design of transmission gates using three-terminal switch devices: (a) Active high design, (b) active low design, and (c) active high-active low design.

The output low voltage  $V_{OL}$  is the voltage output corresponding to logic zero, and the output high voltage  $V_{OH}$  is the value of the output corresponding to logic one. The difference between the two output levels is called the *logic swing* LS:

$$LS = V_{OH} - V_{OL}. (1.1)$$

The *input low voltage*  $V_{IL}$  is the maximum input voltage that will be interpreted as logic zero, and the *input high voltage*  $V_{IH}$  is the minimum value that will be interpreted as logic one. Input values between  $V_{IL}$  and  $V_{IH}$  are ambiguous and should be avoided, so it is desirable to minimize this voltage

#### **FIGURE 1.19**

MOS transmission gate circuits: (a) Active high design using an n-channel MOSFET, (b) active low design using a p-channel MOSFET, and (c) active high-active low design using complementary MOSFETs.

**FIGURE 1.20** Voltage transfer characteristic for an inverter.

range. By definition,  $V_{IL}$  and  $V_{IH}$  are the input voltages for which the slope of the transfer characteristic is minus one (plus one for a noninverting gate):

$$\left. \frac{dV_{OUT}}{dV_{IN}} \right|_{V_{IN} = V_{IL}} = -1. \tag{1.2}$$

and

$$\frac{dV_{OUT}}{dV_{IN}}\Big|_{V_{IN}=V_{IJ}} = -1. \tag{1.3}$$

The *noise margins* are important with regard to bit error rates in the presence of electrical noise. They are defined by

$$V_{NML} = V_{IL} - V_{OL} \tag{1.4}$$

and

$$V_{NMH} = V_{OH} - V_{IH} , \qquad (1.5)$$

where  $V_{\text{NML}}$  and  $V_{\text{NMH}}$  are the low noise margin and the high noise margin, respectively. Electrical noise with a peak-to-peak amplitude less than the

noise margin is attenuated, whereas noise of greater amplitude can create a bit error. It is therefore desirable to maximize the noise margins.

The midpoint voltage  $V_M$ , sometimes also called the switching threshold, is the value of the input voltage for which  $V_{OUT} = V_{IN} = V_M$ . Ideally, the midpoint voltage should be halfway between the logic zero and logic one input voltages. Therefore, its value is often used in the design of level translators to interface between circuits operating with different supply voltages.

Static voltage transfer characteristics are measured using the x-y feature of a storage oscilloscope or a computer-based virtual instrument. The measurement is straightforward in the case of an inverter. The situation is more complicated with multiple inputs, and the usual approach is to tie all but one input to logic zero or logic one, thus avoiding the need for a multidimensional plot. For example, with a NAND gate, all inputs are tied to the positive supply voltage except one, and the transfer characteristic is measured for this one input. For an NOR gate, all inputs but one are grounded for the measurement. Usually, it is assumed that all inputs behave in identical manner, although there may be subtle differences as shown in Chapter 6.

For an ideal logic gate, the output high voltage is equal to the positive supply voltage ( $V_{OH} = V_{DD}$ ), and the output low voltage is equal to the negative supply voltage ( $V_{OL} = V_{SS}$  and usually  $V_{SS} = 0$ ). This results in the maximum possible logic swing, called "rail-to-rail." The ideal logic gate also exhibits a voltage transfer characteristic with an abrupt transition midway between the supply voltages ( $V_{M} = (V_{DD} + V_{SS})/2$ ). Together, these conditions maximize the noise margins.

#### 1.2.3 Transient Characteristics

Transient characteristics are of great importance because of their bearing on the speed characteristics of digital circuits, such as the clock frequency and off-chip data rates.

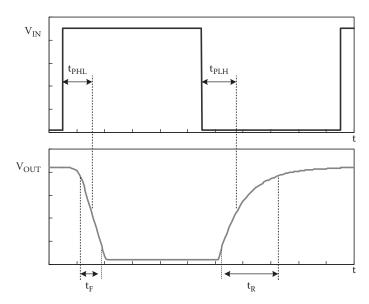

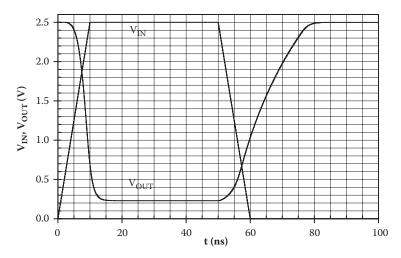

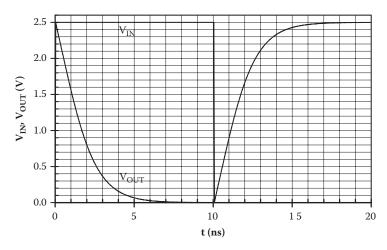

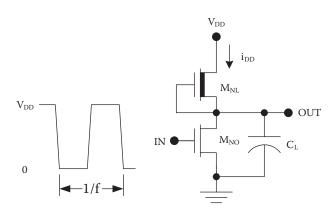

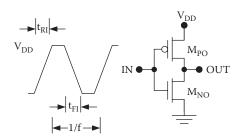

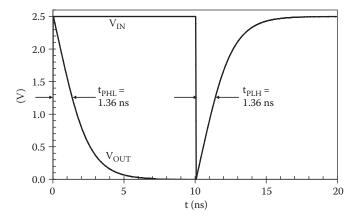

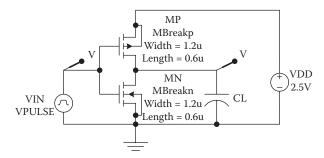

Consider Figure 1.21, which shows the transient behavior for an inverter with a rectangular wave applied at the input. There are four important transient parameters for the inverter. These are the low-to-high propagation delay  $t_{\rm PLH}$ , the high-to-low propagation delay  $t_{\rm PHL}$ , the output rise time  $t_{\rm R}$ , and the output fall time  $t_{\rm F}$ .

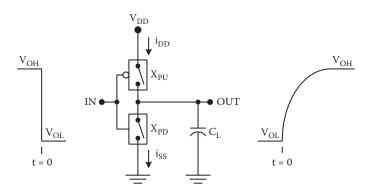

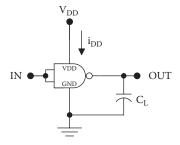

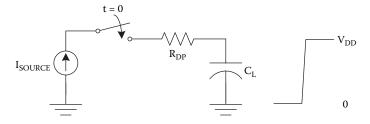

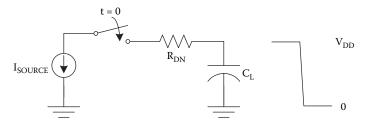

The propagation delays are measured between the 50% points on the input and output waveforms. By this, we mean the points at which the voltage is midway between the two limiting values. As a matter of nomenclature, the low-to-high propagation delay  $t_{\rm PLH}$  refers to the low-to-high transition at the *output node*. For an inverter, this corresponds to the opposite transition at the input node. Similarly,  $t_{\rm PHL}$  refers to the high-to-low transition at the output node. The estimation of the propagation delay  $t_{\rm PLH}$  may be understood with the aid of Figure 1.22. Here, it has been assumed that a signal

**FIGURE 1.21** Transient response of an inverter with a rectangular input waveform.

with an abrupt high-to-low transition has been applied to the input of an inverter with a capacitive load  $C_L$ . If the currents in the pull-up and pull-down devices are  $i_{DD}$  and  $i_{SS}$ , respectively, then  $t_{PLH}$  may be found from

$$\frac{1}{2}(V_{OH} + V_{OL}) - V_{OL} = \int_{0}^{t_{PLH}} \frac{i_{DD} - i_{SS}}{C_L} dt .$$

(1.6)

**FIGURE 1.22** Determination of the propagation delay  $t_{\text{PLH}}$  for an inverter.

Introduction 19

In general, both  $i_{DD}$  and  $i_{SS}$  are functions of the output voltage, so they will vary with time. If the pull-down device turns off abruptly at t=0 and the inverter exhibits rail-to-rail swing at the output, then Equation 1.6 simplifies to

$$\frac{V_{DD}}{2} = \frac{1}{C_L} \int_{0}^{t_{PLH}} i_{DD} dt . {(1.7)}$$

The estimation of  $t_{PHL}$  is similar. Here it is assumed that the input signal makes an abrupt transition from  $V_{OL}$  to  $V_{OH}$  at t=0. If the pull-up device switches off abruptly and if the circuit exhibits rail-to-rail swing, then the high-to-low propagation delay can be estimated from

$$\frac{V_{DD}}{2} = \frac{1}{C_L} \int_{0}^{t_{PHL}} i_{SS} dt . {1.8}$$

For some digital gate circuits, the two propagation delays  $t_{PLH}$  and  $t_{PHL}$  are very different so that both should be specified. Often, an average propagation delay  $t_P$  is used:

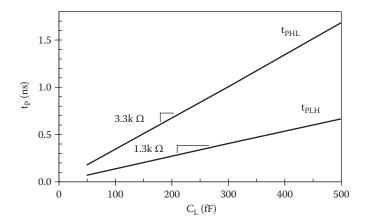

$$t_P = \frac{t_{PLH} + t_{PHL}}{2} \,. \tag{1.9}$$

For a gate circuit with perfectly symmetric transient characteristics,  $t_{PLH} = t_{PHL} = t_P$ . In practice, the input waveforms to digital gates do not make abrupt transitions but have finite rise and fall times. These are important because they modify the time dependences of the currents  $i_{DD}$  and  $i_{SS}$  flowing in the gate circuit and therefore the propagation delays. The rise time is measured between the 10 and 90% points on the waveform, and the fall time is measured between the 90 and 10% points. The rise and fall times may be estimated using a similar approach to that applied for the propagation delays.

There is an inverse relationship between the worst-case propagation delay and the maximum achievable system clock frequency:

$$f_{CLK} < \frac{1}{N_s t_P} \,, \tag{1.10}$$

where  $f_{\rm CLK}$  is the clock frequency, and  $N_{\rm S}$  is the number of cascaded logic stages in the critical (longest) path in the digital system. Therefore, system performance is affected critically by both the system design and the performances of the individual of the logic building blocks. For an otherwise similar design, halving the gate propagation delays will allow a doubling of the clock frequency.

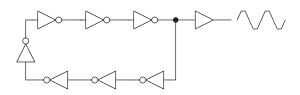

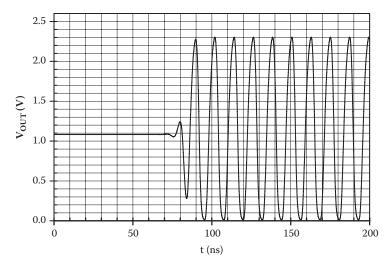

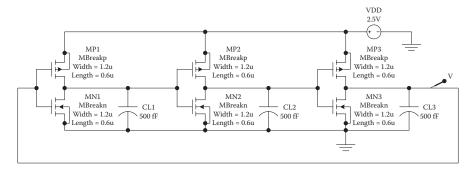

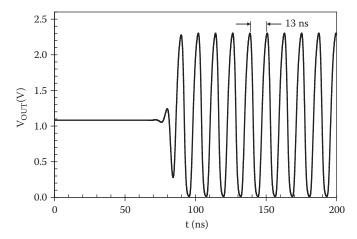

Propagation delays are determined experimentally using ring oscillators such as the one shown in Figure 1.23. A ring oscillator comprises an odd number of inverters, so that the voltage at any connection node will oscillate with time. During one period of the oscillation, each gate switches from low to high and then back to low again. Therefore, the period is given by

$$T = \sum_{n=1}^{M} (t_{PLH} + t_{PHL}), \qquad (1.11)$$

where M is the (odd) number of inverters in the ring. If the inverters in the ring are all identical, with identical loading, then the frequency of oscillation is given by

$$f_M = \frac{1}{M(t_{PLH} + t_{PHL})} = \frac{1}{2Mt_P}$$

(1.12)

#### 1.2.4 Fan-In and Fan-Out

Fan-in and fan-out refer to the connectivity of a logic gate. Fan-in is simply the number of input connections, and fan-out is the maximum number of load gates that can be connected to the output (without undesirable degradation in performance).

The fan-in may be unity, as in the case of an inverter. However, general system design requires gates with at least two inputs, and gates with higher fan-in may simplify the implementation and improve the overall performance of complex systems. Generally, the maximum practical fan-in is limited by device or circuit performance considerations.

The maximum fan-out  $N_{\text{MAX}}$  will be determined by loading considerations and is usually estimated using the assumption that the load gates are identical to the driving gates. For MOS-based logic gates, dynamic loading considerations prevail because the loading is primarily capacitive. In this case, increasing the number of load gates decreases the switching speed of the driving gate. As a consequence, there is a maximum number of load gates that can be connected without an unacceptable degradation in the switching

**FIGURE 1.23** Seven-stage ring oscillator with a buffered output.

Introduction 21

speed. If  $t_{P, \text{max}}$  is the maximum allowable propagation delay, then this can be used to determine the maximum allowable load capacitance:

$$C_{L,\max} = f(t_{P,\max}). \tag{1.13}$$

If the load gates each have an input capacitance  $C_{in}$  and other loading effects (self loading, interconnect loading) may be neglected, then the maximum fan-out can be estimated from

$$N_{\text{max}} \le \frac{C_{L,\text{max}}}{C_{in}} \,. \tag{1.14}$$

The direct current (DC) fan-out consideration is based on current loading. Suppose that  $I_{OL}$  is the maximum current that can be sunk at the output with a logic zero output (the output low current). If  $I_{IL}$  is the current that flows out of an input lead when logic zero is applied (the input low current), then

$$N_{MAX} < \frac{I_{OL}}{I_{IL}}. \tag{1.15}$$

Suppose also that  $I_{OH}$  is the maximum current that can be sourced with a logic one output (the output high current). If  $I_{IH}$  is the amount of current that is sunk by an input with logic one applied, then

$$N_{MAX} < \frac{I_{OH}}{I_{IH}}. \tag{1.16}$$

Typically, the constraints imposed by Equations 1.15 and 1.16 are very different so that the more stringent one prevails.

For CMOS circuits, the dynamic fan-out consideration is prevalent. This leads to an engineering trade-off between fan-out and switching speed. However, system design aspects dictate that the fan-out should generally be greater than 3.

## 1.2.5 Dissipation

The power dissipation is an important consideration for nearly all applications of digital integrated circuits. In portable devices, the power dissipation must be minimized to prolong battery life. For all digital equipment, portable or stationary, the power dissipation must be minimized because of the associated heat that must be removed. The cooling of integrated circuits often requires specially designed packages with heat sinking and fans for more efficient heat removal. For VLSI circuits, dissipation considerations may limit the number or density of gates that can be put on a chip.

The dissipation may be dominated by the static component or the dynamic contribution. In some cases, both contributions may be similar in magnitude so that both must be considered.

The dynamic or alternating current (AC) dissipation is associated with charging and discharging of the load capacitance and is called the capacitance switching dissipation. Consider the gate of Figure 1.24 with a lumped capacitive load. The energy associated with one switching cycle (a low-to-high transition at the output, followed by a high-to-low transition at the output) is

$$J = V_{DD} \int_{\substack{clock \\ cucle}} i_{DD} dt . {(1.17)}$$

If there is negligible current flowing from the supply voltage to the ground through the logic gate itself, then during the low-to-high transition at the output, the supply current is given by

$$i_{DD} = C_L \frac{dV_{OUT}}{dt} \,. \tag{1.18}$$

During the high-to-low transition of the output, the load capacitor is discharged through the logic gate but no additional current flows from the supply voltage. Therefore, the energy (in joules) dissipated during one switching cycle is

$$J = V_{DD} \int_{0}^{V_{DD}} C_L dV_{OUT} = C_L V_{DD}^2 . {(1.19)}$$

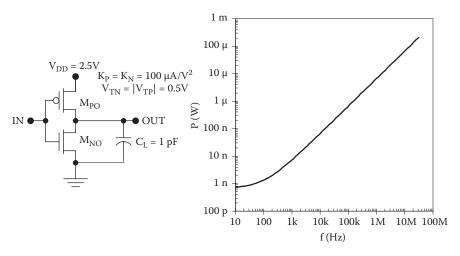

The dynamic dissipation (in watts) is therefore

$$P_{switch} = fC_L V_{DD}^2 = \alpha f_{CLK} C_L V_{DD}^2, \qquad (1.20)$$

#### **FIGURE 1.24**

A logic gate with a lumped capacitive load for the calculation of the dynamic power dissipation.

Introduction 23

where f is the switching frequency,  $f_{CLK}$  is the clock frequency, and  $\alpha$  is the switching activity factor. The activity factor is less than unity, because the actual switching frequency for any particular gate will be less than the system clock frequency. In general, there may be internal nodes of the logic gate, each with its own load capacitance, and these may not all switch at the same frequency as the output node. In that case, the switching power dissipation with K nodes can be estimated from

$$P_{switch} = f_{CLK} \sum_{n=1}^{K} \alpha_n C_{Ln} V_{DD}^2 , \qquad (1.21)$$

where  $\alpha_n$  and  $C_{Ln}$  are the switching activity factor and the load capacitance for the nth node, respectively.

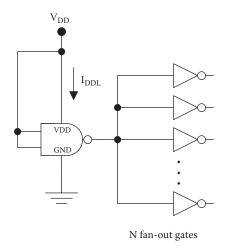

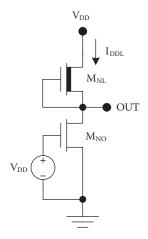

In general, the DC (static) dissipation is dependent on the output state and the fan-out.\* In the case of MOS logic gates, the DC load currents are attributable to leakage currents in oxides and p-n junctions as well as subthreshold currents in MOS transistors. Referring to Figure 1.25, the power with a logic zero output state (the "output low power") is

$$P_{L} = V_{DD}I_{DDL}, \qquad (1.22)$$

where  $V_{DD}$  is the supply voltage, and  $I_{DDL}$  is the supply current that flows with a low output. For the case shown, the gate under consideration is a two-input NAND gate. Therefore, the output low condition exists with both inputs tied to the supply voltage.

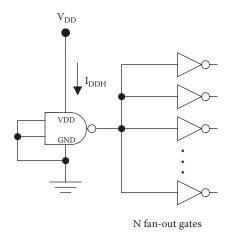

Referring to Figure 1.26, the power with a logic one output state (the "output high power") is

$$P_H = V_{DD}I_{DDH} \,, \tag{1.23}$$

where  $I_{\text{DDH}}$  is the current that flows from the supply to the gate under the condition of a logic one output. For the two-input NAND gate shown in the figure, the output high condition exists with both inputs tied to ground. In general,  $I_{\text{DDH}}$  and  $P_{\text{H}}$  are a function of N, the number of fan-out gates.

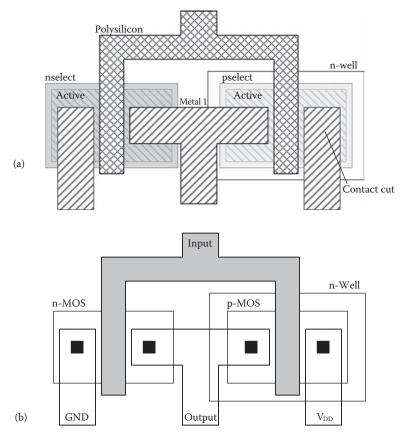

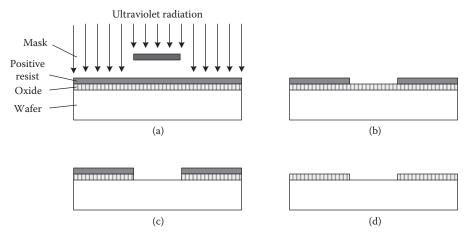

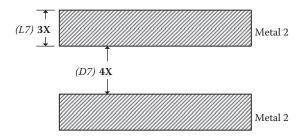

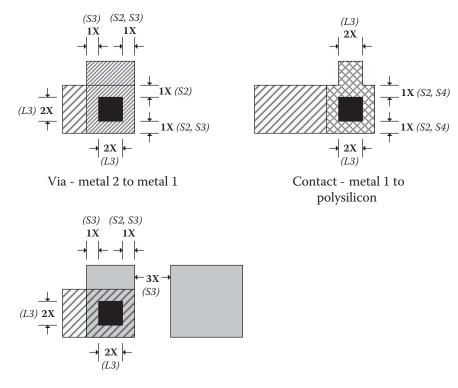

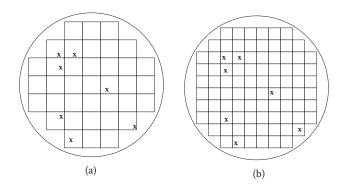

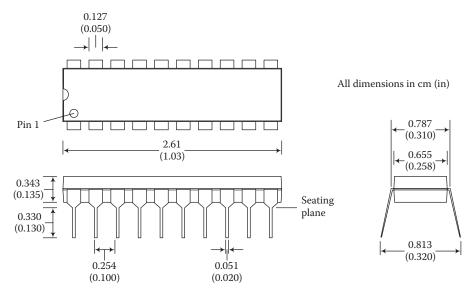

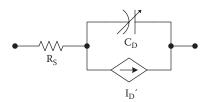

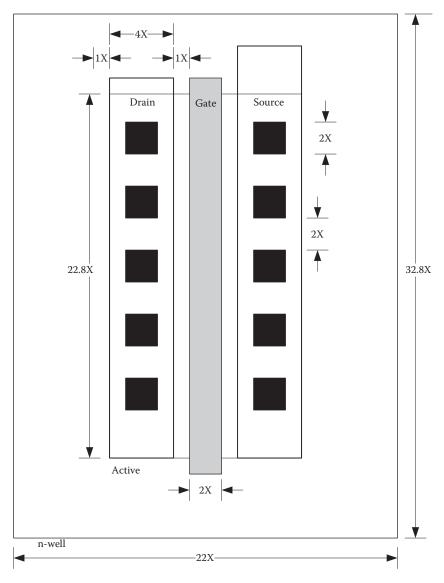

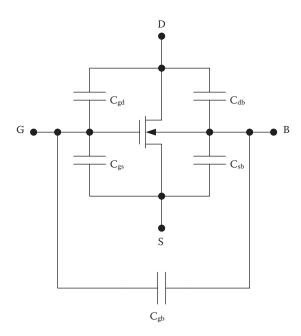

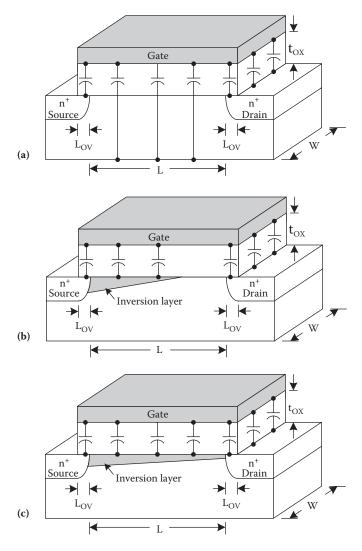

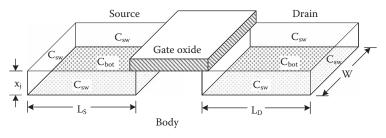

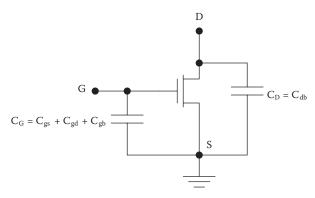

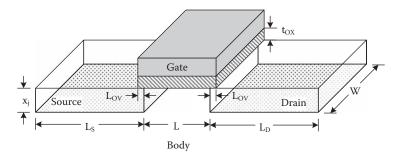

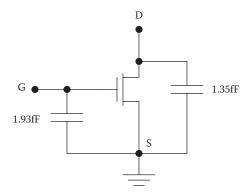

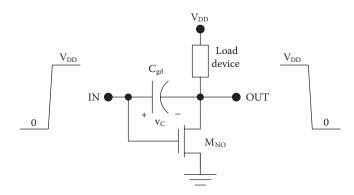

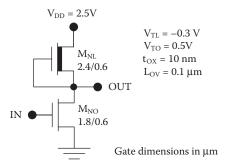

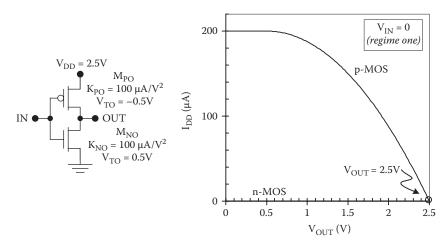

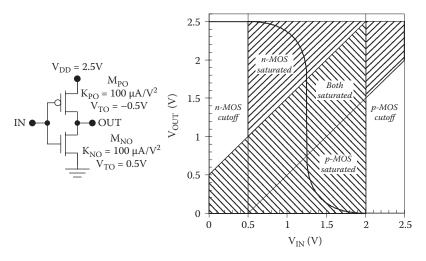

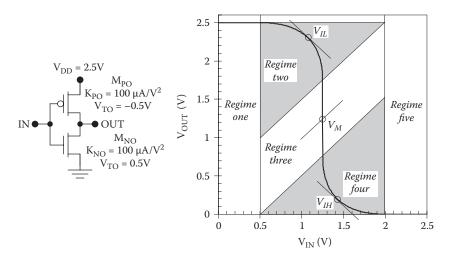

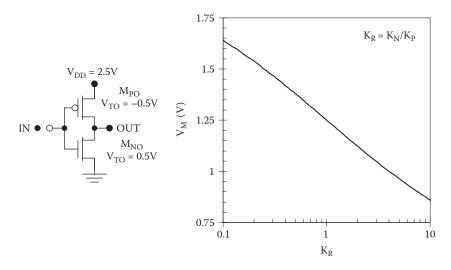

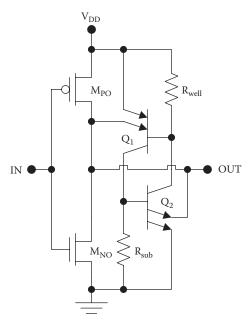

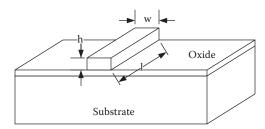

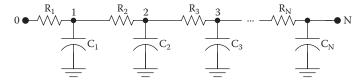

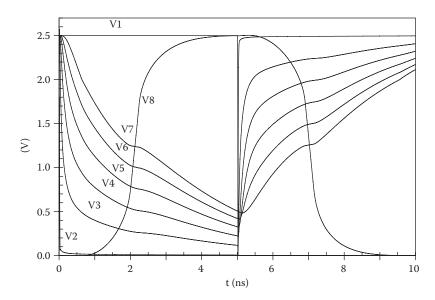

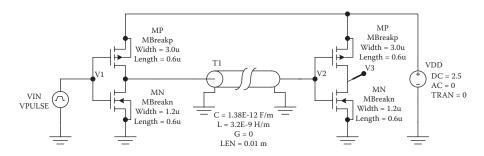

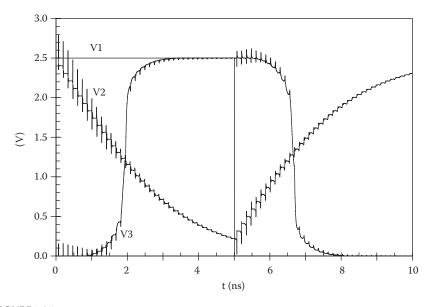

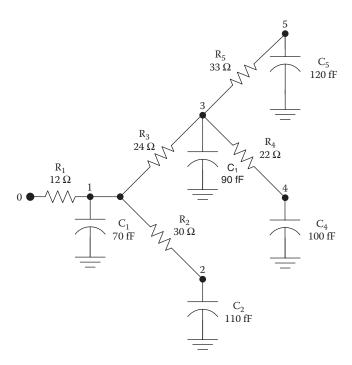

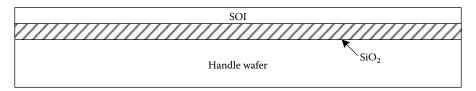

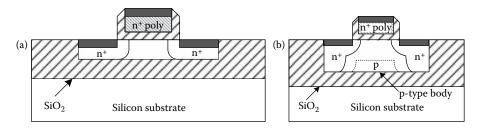

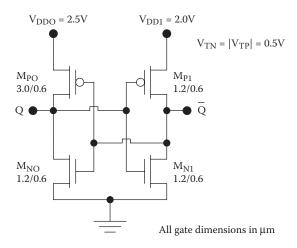

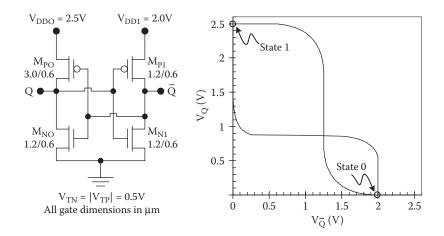

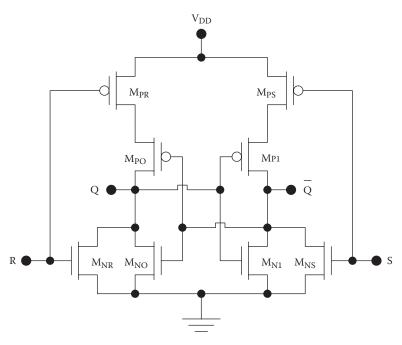

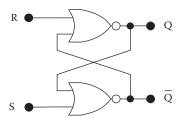

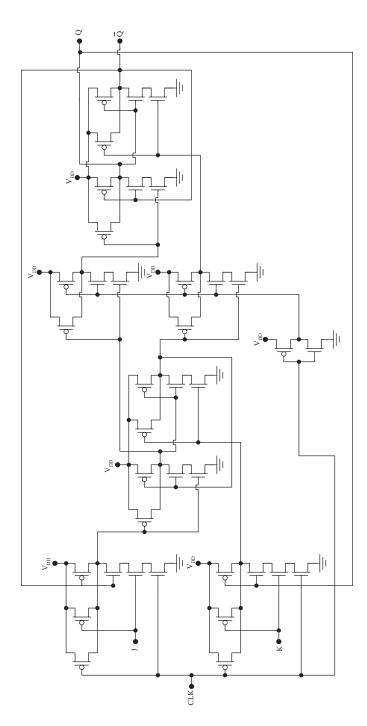

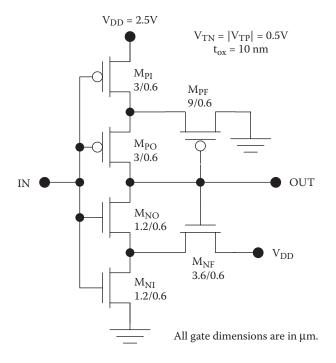

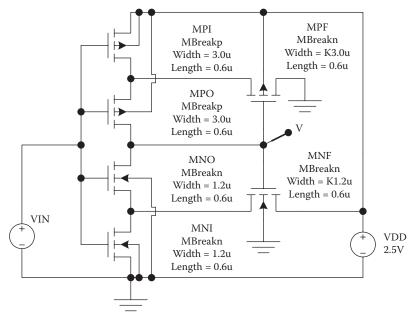

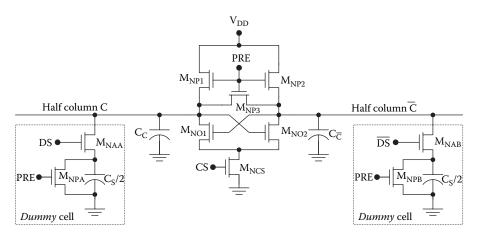

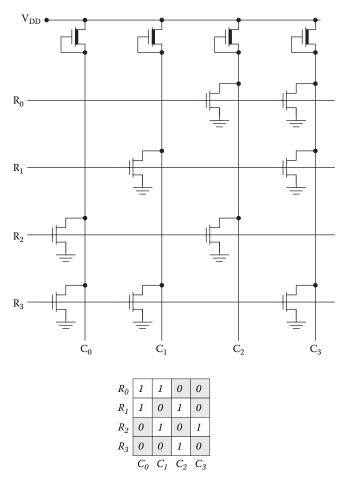

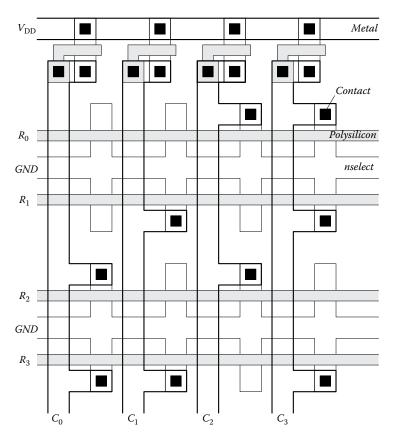

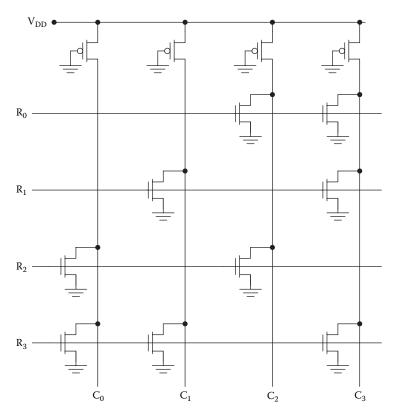

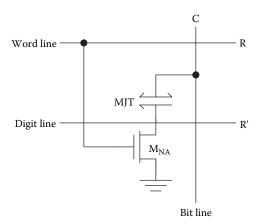

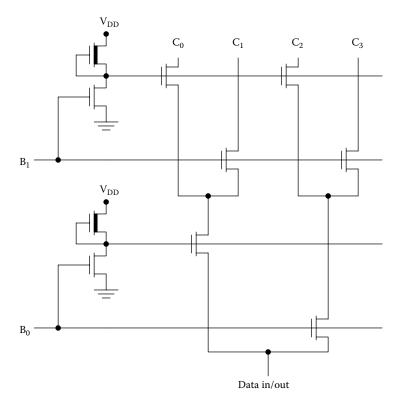

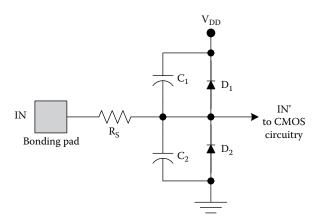

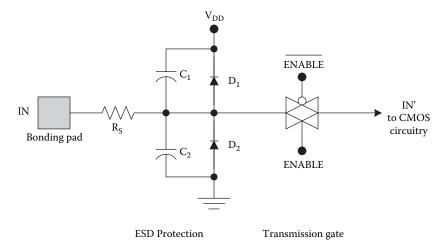

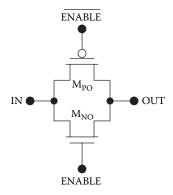

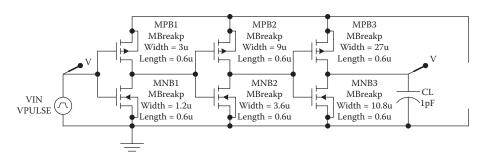

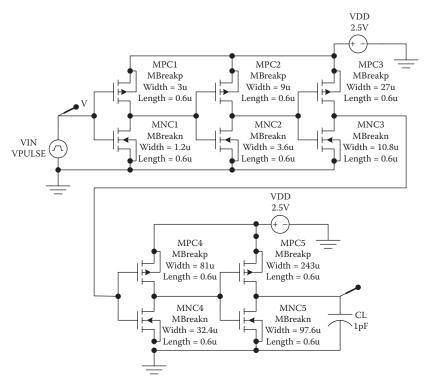

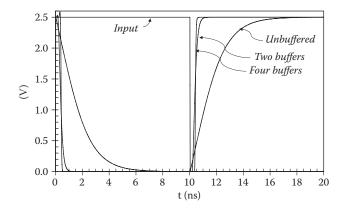

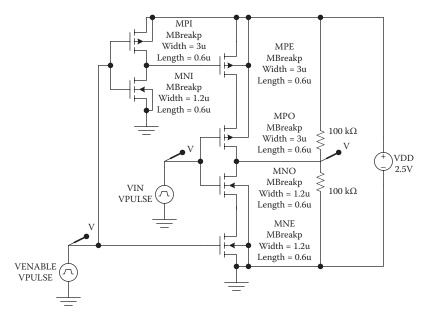

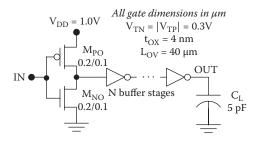

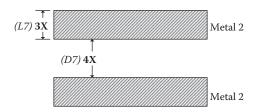

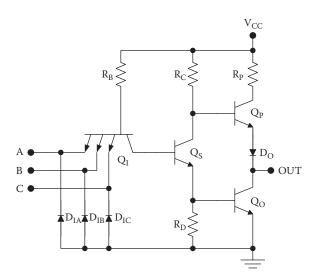

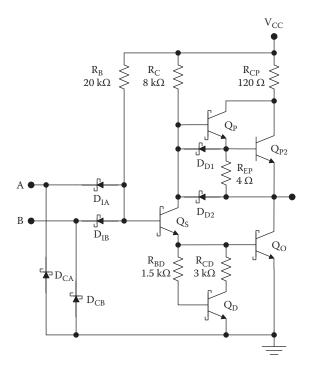

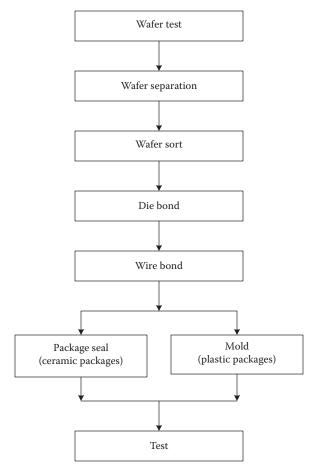

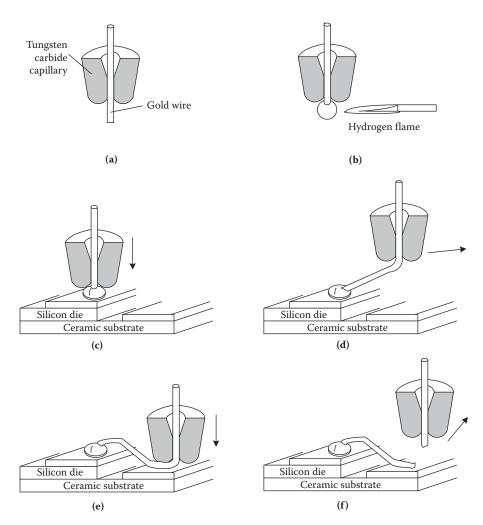

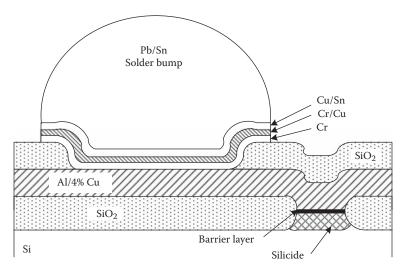

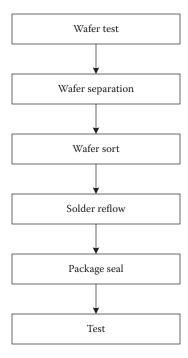

The average DC dissipation can be calculated by