**Copyrighted Material**

Donald G. Bailey

# Design for Embedded Image Processing on FPGAS

COMPANY AND DESCRIPTION OF

## DESIGN FOR EMBEDDED IMAGE PROCESSING ON FPGAS

# DESIGN FOR EMBEDDED IMAGE PROCESSING ON FPGAS

Donald G. Bailey

Massey University, New Zealand

John Wiley & Sons (Asia) Pte Ltd

This edition first published 2011 © 2011 John Wiley & Sons (Asia) Pte Ltd

#### **Registered** office

John Wiley & Sons (Asia) Pte Ltd, 1 Fusionopolis Walk, #07-01 Solaris South Tower, Singapore 138628

For details of our global editorial offices, for customer services and for information about how to apply for permission to reuse the copyright material in this book please see our website at www.wiley.com.

All Rights Reserved. No part of this publication may be reproduced, stored in a retrieval system or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, scanning, or otherwise, except as expressly permitted by law, without either the prior written permission of the Publisher, or authorization through payment of the appropriate photocopy fee to the Copyright Clearance Center. Requests for permission should be addressed to the Publisher, John Wiley & Sons (Asia) Pte Ltd, 1 Fusionopolis Walk, #07-01 Solaris South Tower, Singapore 138628, tel: 65-66438000, fax: 65-66438008, email: enquiry@wiley.com.

Wiley also publishes its books in a variety of electronic formats. Some content that appears in print may not be available in electronic books.

Designations used by companies to distinguish their products are often claimed as trademarks. All brand names and product names used in this book are trade names, service marks, trademarks or registered trademarks of their respective owners. The Publisher is not associated with any product or vendor mentioned in this book. This publication is designed to provide accurate and authoritative information in regard to the subject matter covered. It is sold on the understanding that the Publisher is not engaged in rendering professional services. If professional advice or other expert assistance is required, the services of a competent professional should be sought.

#### Library of Congress Cataloging-in-Publication Data

Bailey, Donald G. (Donald Graeme), 1962Design for embedded image processing on FPGAs / Donald G. Bailey.

p. cm.

Includes bibliographical references and index.

ISBN 978-0-470-82849-6 (hardback)

1. Embedded computer systems. 2. Field programmable gate arrays. I. Title.

TK7895.E42B3264 2011

621.39'9 dc22

2011002991

Print ISBN: 978-0-470-82849-6 ePDF ISBN: 978-0-470-82850-2 oBook ISBN: 978-0-470-82851-9 ePub ISBN: 978-0-470-82852-6 Mobi ISBN: 978-1-118-07331-5

Set in 9/11 pt Times New Roman by Thomson Digital, Noida, India

## Contents

| Preface          |       |                                   | xi   |

|------------------|-------|-----------------------------------|------|

| Acknowledgements |       |                                   | xvii |

| 1                | Imag  | e Processing                      | 1    |

|                  | 1.1   | Basic Definitions                 | 2    |

|                  | 1.2   | Image Formation                   | 3    |

|                  | 1.3   | Image Processing Operations       | 7    |

|                  | 1.4   | Example Application               | 9    |

|                  | 1.5   | e e                               | 11   |

|                  | 1.6   | Embedded Image Processing         | 12   |

|                  | 1.7   | 8                                 | 12   |

|                  |       | Parallelism                       | 14   |

|                  | 1.9   | Hardware Image Processing Systems | 18   |

| 2                | Field | Programmable Gate Arrays          | 21   |

|                  | 2.1   | Programmable Logic                | 21   |

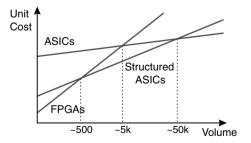

|                  |       | 2.1.1 FPGAs vs. ASICs             | 24   |

|                  | 2.2   | FPGAs and Image Processing        | 25   |

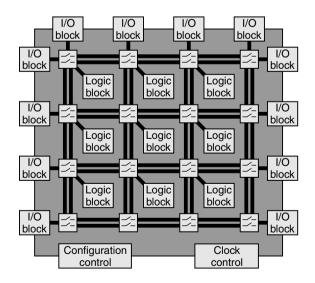

|                  | 2.3   | Inside an FPGA                    | 26   |

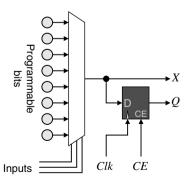

|                  |       | 2.3.1 Logic                       | 27   |

|                  |       | 2.3.2 Interconnect                | 28   |

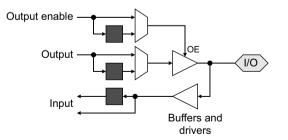

|                  |       | 2.3.3 Input and Output            | 29   |

|                  |       | 2.3.4 Clocking                    | 30   |

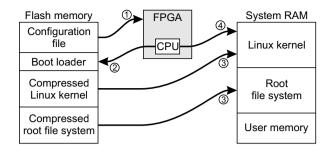

|                  |       | 2.3.5 Configuration               | 31   |

|                  |       | 2.3.6 Power Consumption           | 32   |

|                  | 2.4   |                                   | 33   |

|                  |       | 2.4.1 Xilinx                      | 33   |

|                  |       | 2.4.2 Altera                      | 38   |

|                  |       | 2.4.3 Lattice Semiconductor       | 44   |

|                  |       | 2.4.4 Achronix                    | 46   |

|                  |       | 2.4.5 SiliconBlue                 | 47   |

|                  |       | 2.4.6 Tabula                      | 47   |

|                  |       | 2.4.7 Actel                       | 48   |

|                  |       | 2.4.8 Atmel                       | 49   |

|   |       | <ul><li>2.4.9 QuickLogic</li><li>2.4.10 MathStar</li></ul> | 50<br>50 |

|---|-------|------------------------------------------------------------|----------|

|   |       | 2.4.10 Mathstar<br>2.4.11 Cypress                          | 51       |

|   | 2.5   | Choosing an FPGA or Development Board                      | 51       |

|   | 2.5   | choosing an IT ON of Development Dourd                     | 51       |

| 3 | Lang  | uages                                                      | 53       |

|   | 3.1   | Hardware Description Languages                             | 56       |

|   | 3.2   | Software-Based Languages                                   | 61       |

|   |       | 3.2.1 Structural Approaches                                | 63       |

|   |       | 3.2.2 Augmented Languages                                  | 64       |

|   |       | 3.2.3 Native Compilation Techniques                        | 69       |

|   | 3.3   | Visual Languages                                           | 72       |

|   |       | 3.3.1 Behavioural                                          | 73       |

|   |       | 3.3.2 Dataflow                                             | 73       |

|   |       | 3.3.3 Hybrid                                               | 74       |

|   | 3.4   | Summary                                                    | 77       |

| 4 | Desig | n Process                                                  | 79       |

|   | 4.1   | Problem Specification                                      | 79       |

|   | 4.2   | Algorithm Development                                      | 81       |

|   |       | 4.2.1 Algorithm Development Process                        | 82       |

|   |       | 4.2.2 Algorithm Structure                                  | 83       |

|   |       | 4.2.3 FPGA Development Issues                              | 86       |

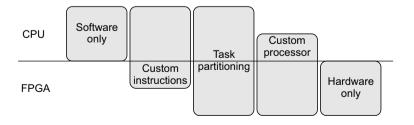

|   | 4.3   | Architecture Selection                                     | 86       |

|   |       | 4.3.1 System Level Architecture                            | 87       |

|   |       | 4.3.2 Computational Architecture                           | 89       |

|   |       | 4.3.3 Partitioning between Hardware and Software           | 93       |

|   | 4.4   | System Implementation                                      | 96       |

|   |       | 4.4.1 Mapping to FPGA Resources                            | 97       |

|   |       | 4.4.2 Algorithm Mapping Issues                             | 100      |

|   |       | 4.4.3 Design Flow                                          | 101      |

|   | 4.5   | Designing for Tuning and Debugging                         | 102      |

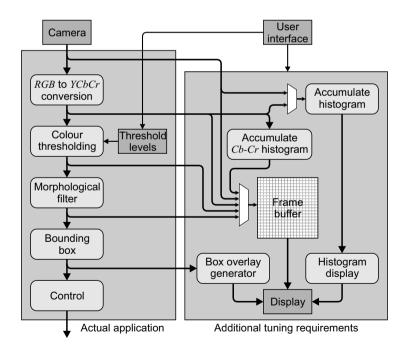

|   |       | 4.5.1 Algorithm Tuning                                     | 102      |

|   |       | 4.5.2 System Debugging                                     | 104      |

| 5 | Мар   | ping Techniques                                            | 107      |

|   | 5.1   | Timing Constraints                                         | 107      |

|   |       | 5.1.1 Low Level Pipelining                                 | 107      |

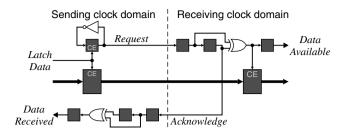

|   |       | 5.1.2 Process Synchronisation                              | 110      |

|   |       | 5.1.3 Multiple Clock Domains                               | 111      |

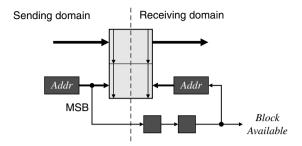

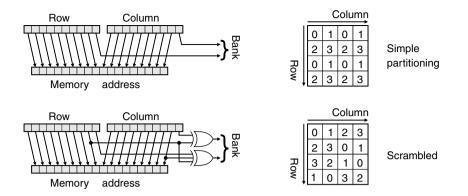

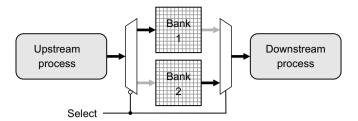

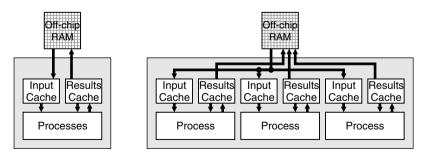

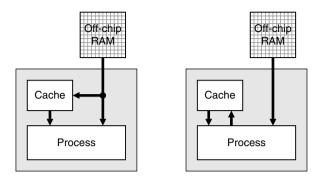

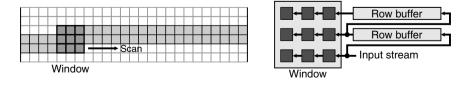

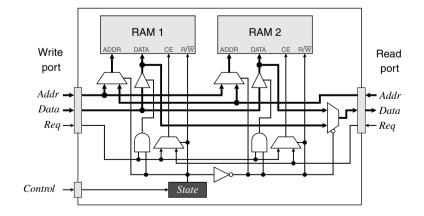

|   | 5.2   | Memory Bandwidth Constraints                               | 113      |

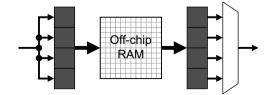

|   |       | 5.2.1 Memory Architectures                                 | 113      |

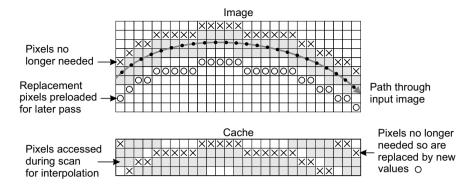

|   |       | 5.2.2 Caching                                              | 116      |

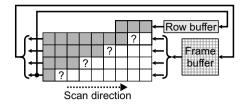

|   |       | 5.2.3 Row Buffering                                        | 117      |

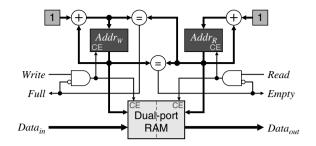

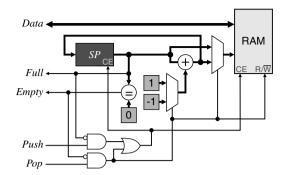

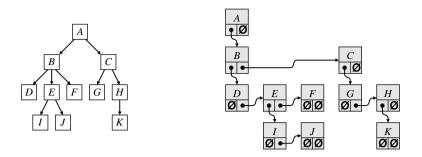

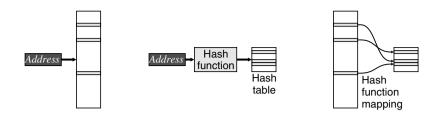

|   |       | 5.2.4 Other Memory Structures                              | 118      |

|   |       |                                                            |          |

|   | 5.3              | Resour  | ce Constraints                     | 122 |

|---|------------------|---------|------------------------------------|-----|

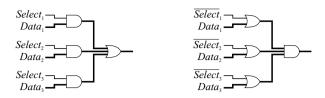

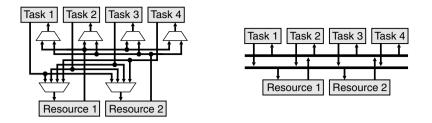

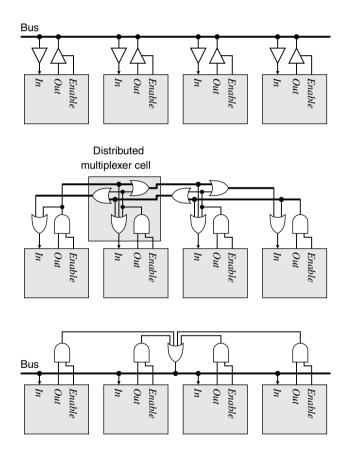

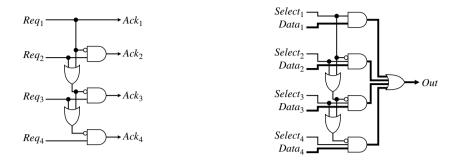

|   |                  | 5.3.1   | Resource Multiplexing              | 122 |

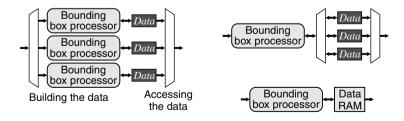

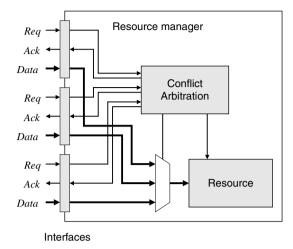

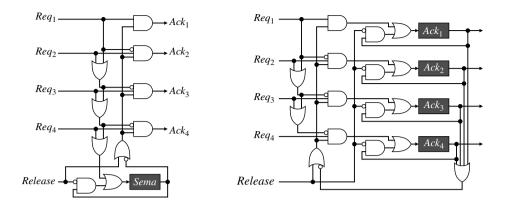

|   |                  | 5.3.2   | Resource Controllers               | 125 |

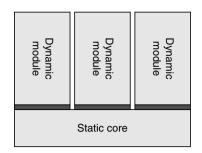

|   |                  | 5.3.3   | Reconfigurability                  | 130 |

|   | 5.4              | Compu   | itational Techniques               | 132 |

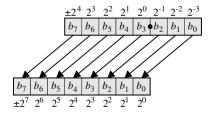

|   |                  | 5.4.1   | Number Systems                     | 132 |

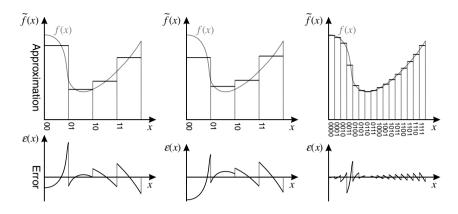

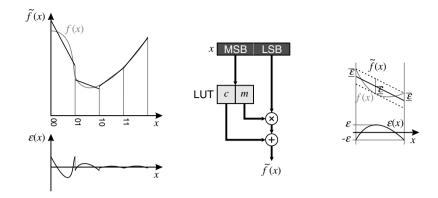

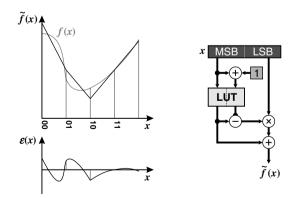

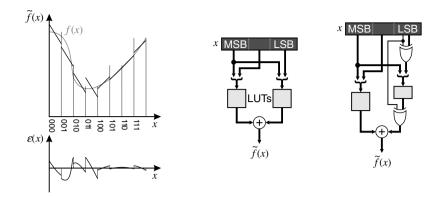

|   |                  | 5.4.2   | Lookup Tables                      | 138 |

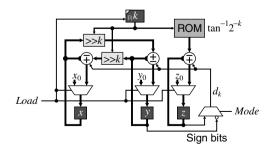

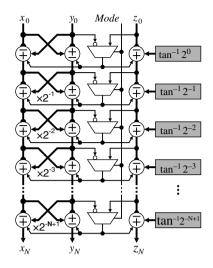

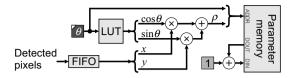

|   |                  | 5.4.3   | CORDIC                             | 142 |

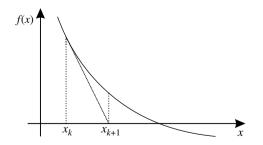

|   |                  | 5.4.4   | Approximations                     | 150 |

|   |                  | 5.4.5   | Other Techniques                   | 152 |

|   | 5.5              | Summa   | ary                                | 154 |

| 6 | Point Operations |         |                                    |     |

|   | 6.1              | Point C | Dperations on a Single Image       | 155 |

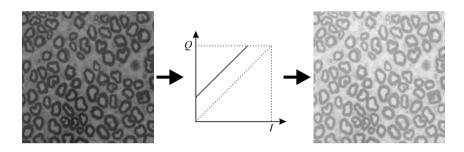

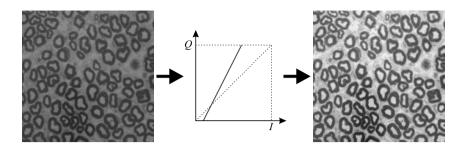

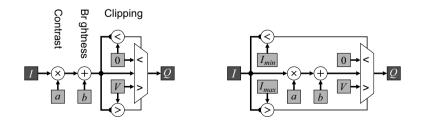

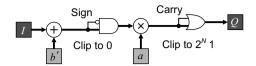

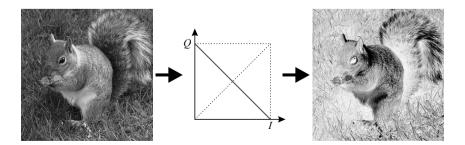

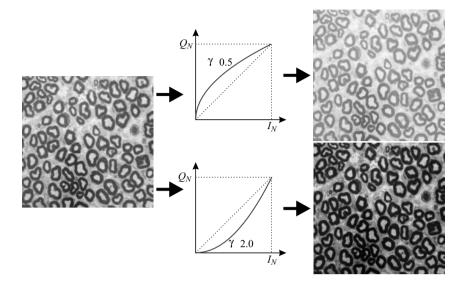

|   |                  | 6.1.1   | Contrast and Brightness Adjustment | 155 |

|   |                  | 6.1.2   | Global Thresholding and Contouring | 159 |

|   |                  | 6.1.3   | Lookup Table Implementation        | 162 |

|   | 6.2              | Point C | Dperations on Multiple Images      | 163 |

|   |                  |         | Image Averaging                    | 164 |

|   |                  |         | Image Subtraction                  | 166 |

|   |                  | 6.2.3   | Image Comparison                   | 170 |

|   |                  | 6.2.4   | Intensity Scaling                  | 171 |

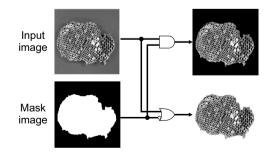

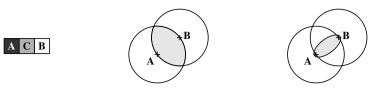

|   |                  | 6.2.5   | Masking                            | 173 |

|   | 6.3              | Colour  | Image Processing                   | 175 |

|   |                  | 6.3.1   | False Colouring                    | 175 |

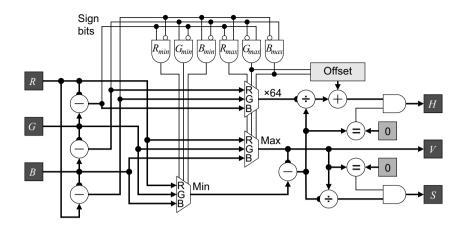

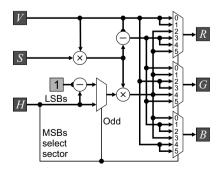

|   |                  | 6.3.2   | Colour Space Conversion            | 176 |

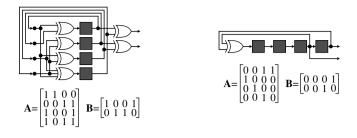

|   |                  | 6.3.3   | e                                  | 192 |

|   |                  | 6.3.4   | Colour Correction                  | 193 |

|   |                  | 6.3.5   | Colour Enhancement                 | 197 |

|   | 6.4              | Summa   | 197                                |     |

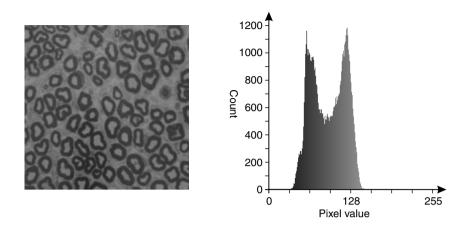

| 7 | Histo            | ogram O | perations                          | 199 |

|   | 7.1              | Greysc  | ale Histogram                      | 199 |

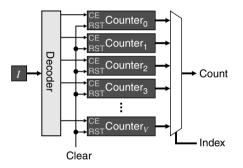

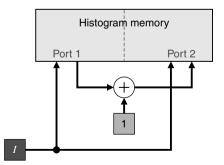

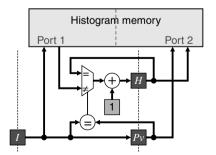

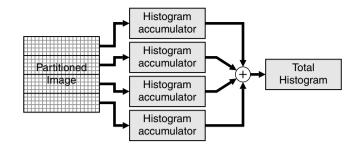

|   |                  | 7.1.1   | Data Gathering                     | 201 |

|   |                  | 7.1.2   | Histogram Equalisation             | 206 |

|   |                  | 7.1.3   | Automatic Exposure                 | 210 |

|   |                  | 7.1.4   | Threshold Selection                | 211 |

|   |                  | 7.1.5   | Histogram Similarity               | 219 |

|   | 7.2              |         | imensional Histograms              | 219 |

|   |                  | 7.2.1   | Triangular Arrays                  | 220 |

|   |                  | 7.2.2   | Multidimensional Statistics        | 222 |

|   |                  | 7.2.3   | Colour Segmentation                | 226 |

|   |                  | 7.2.4   | Colour Indexing                    | 229 |

|   |                  | 7.2.5   | Texture Analysis                   | 231 |

|   |                  |         |                                    |     |

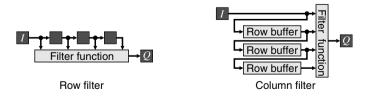

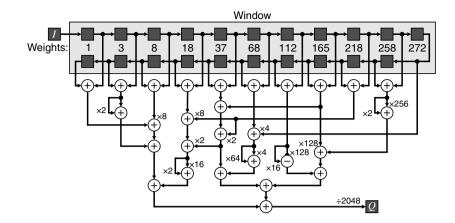

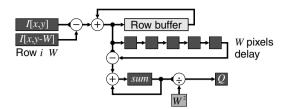

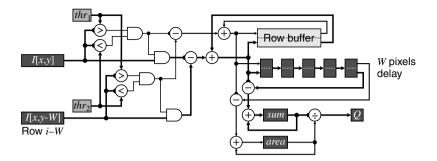

| 8  | Local Filters          |                           |                                 | 233 |  |

|----|------------------------|---------------------------|---------------------------------|-----|--|

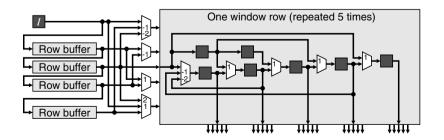

|    | 8.1 Caching            |                           | 233                             |     |  |

|    | 8.2                    | Linear Filters            |                                 | 239 |  |

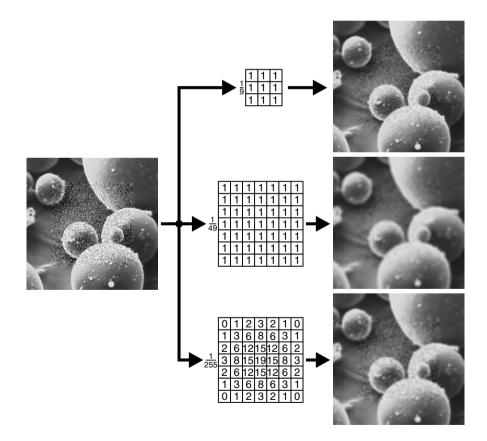

|    |                        | 8.2.1                     | Noise Smoothing                 | 239 |  |

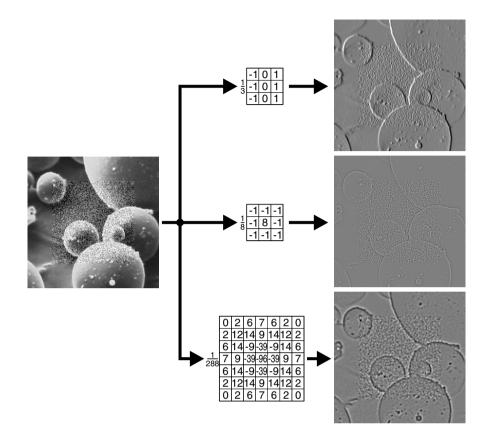

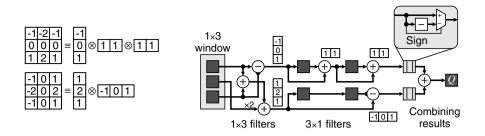

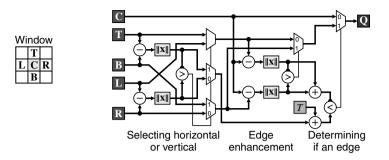

|    |                        | 8.2.2                     | Edge Detection                  | 241 |  |

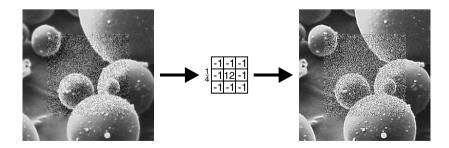

|    |                        | 8.2.3                     | Edge Enhancement                | 243 |  |

|    |                        |                           | Linear Filter Techniques        | 243 |  |

|    | 8.3                    | Nonlin                    | ear Filters                     | 248 |  |

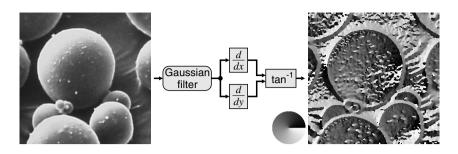

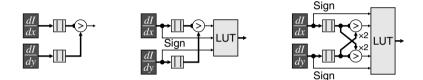

|    |                        | 8.3.1                     | Edge Orientation                | 250 |  |

|    |                        | 8.3.2                     | Non-maximal Suppression         | 251 |  |

|    |                        | 8.3.3                     | Zero-Crossing Detection         | 252 |  |

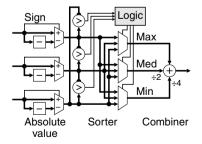

|    | 8.4                    | Rank F                    |                                 | 252 |  |

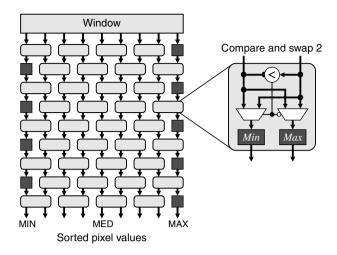

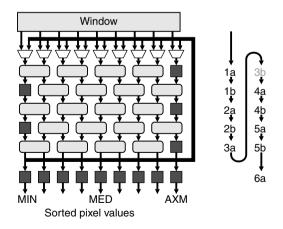

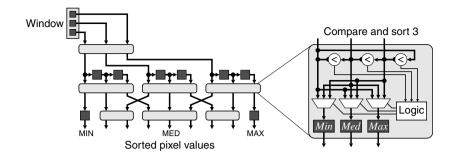

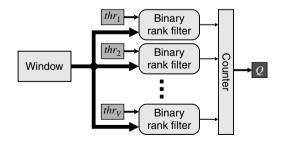

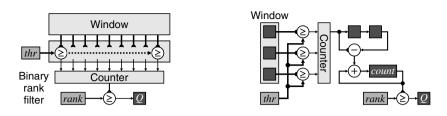

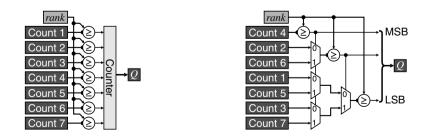

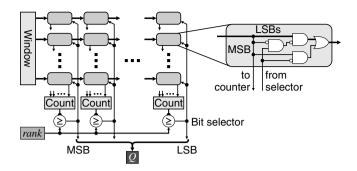

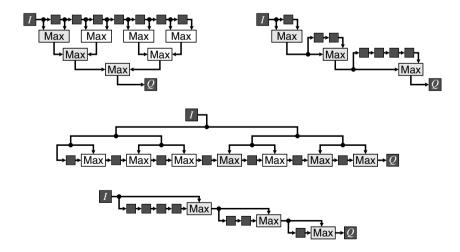

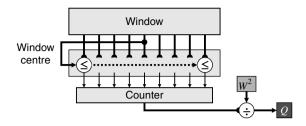

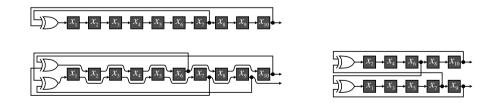

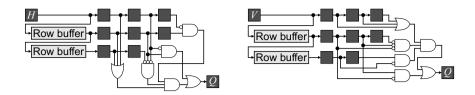

|    |                        | 8.4.1                     | Rank Filter Sorting Networks    | 255 |  |

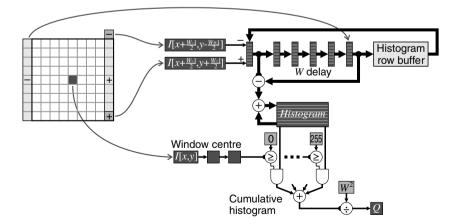

|    |                        | 8.4.2                     | Adaptive Histogram Equalisation | 260 |  |

|    | 8.5                    |                           | Filters                         | 261 |  |

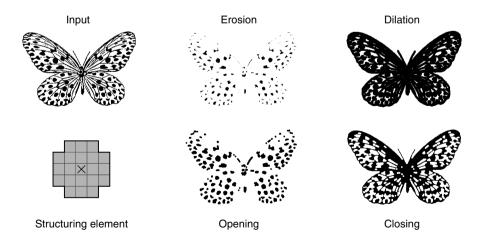

|    | 8.6                    | -                         | ological Filters                | 264 |  |

|    |                        |                           | Binary Morphology               | 264 |  |

|    |                        |                           | Greyscale Morphology            | 269 |  |

|    |                        |                           | Colour Morphology               | 270 |  |

|    | 8.7                    |                           | ve Thresholding                 | 271 |  |

|    |                        |                           | Error Diffusion                 | 271 |  |

|    | 8.8                    | Summa                     | ary                             | 273 |  |

| 9  | Geom                   | etric T                   | ransformations                  | 275 |  |

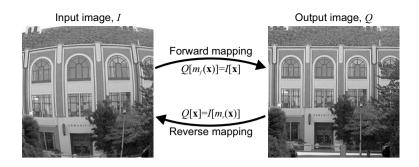

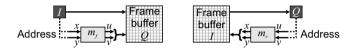

|    | 9.1 Forward Mapping    |                           | 276                             |     |  |

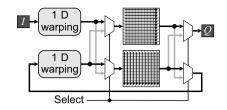

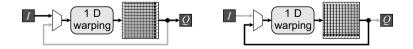

|    |                        |                           | Separable Mapping               | 277 |  |

|    | 9.2                    | Reverse Mapping           |                                 | 282 |  |

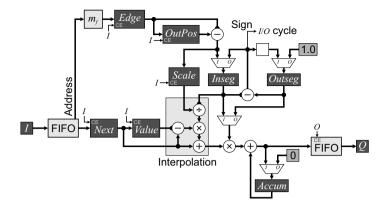

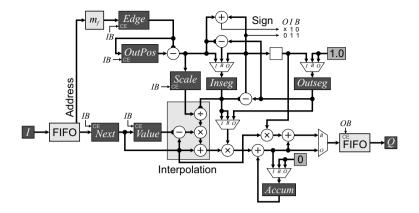

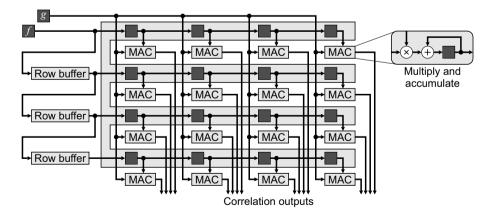

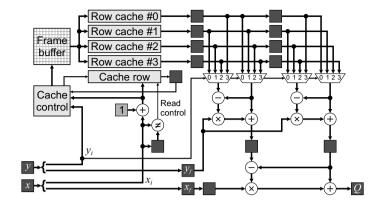

|    | 9.3                    | Interpolation             |                                 | 285 |  |

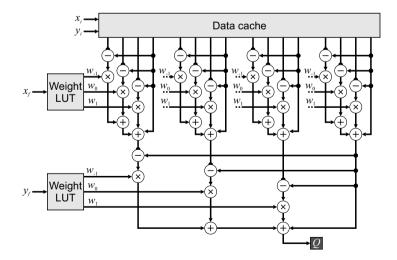

|    |                        | 9.3.1                     | Bilinear Interpolation          | 286 |  |

|    |                        | 9.3.2                     | Bicubic Interpolation           | 288 |  |

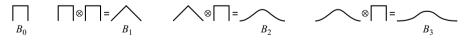

|    |                        | 9.3.3                     | Splines                         | 290 |  |

|    |                        | 9.3.4                     | Interpolating Compressed Data   | 292 |  |

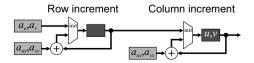

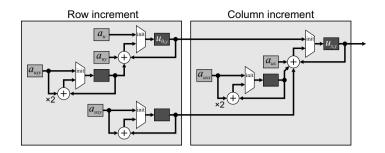

|    | 9.4                    | 9.4 Mapping Optimisations |                                 | 292 |  |

|    | 9.5                    | 6 6                       |                                 | 294 |  |

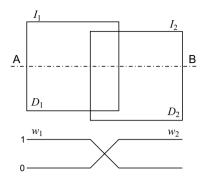

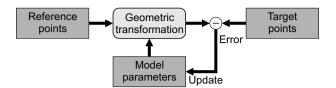

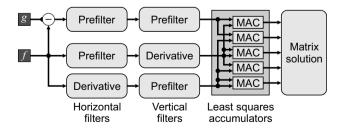

|    |                        | 9.5.1                     | Feature-Based Methods           | 295 |  |

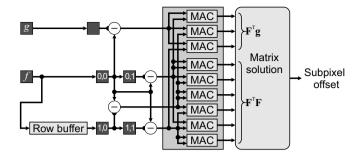

|    |                        | 9.5.2                     | Area-Based Methods              | 299 |  |

|    |                        | 9.5.3                     | Applications                    | 305 |  |

| 10 | Linear Transforms      |                           | 309                             |     |  |

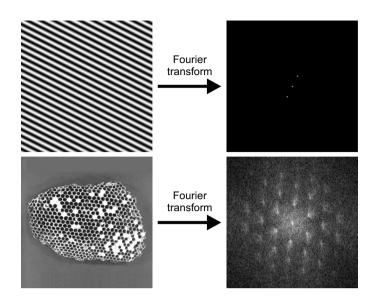

|    | 10.1 Fourier Transform |                           |                                 | 310 |  |

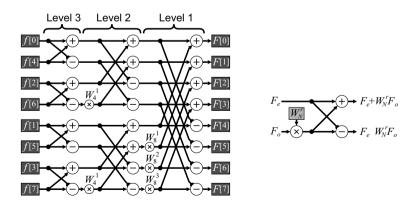

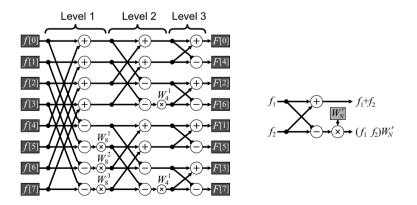

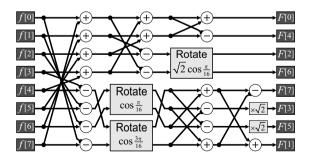

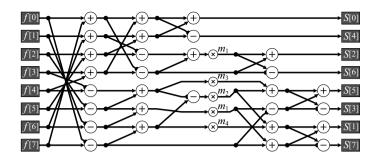

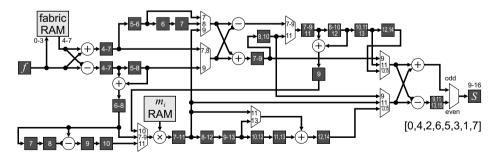

|    |                        | 10.1.1                    | Fast Fourier Transform          | 311 |  |

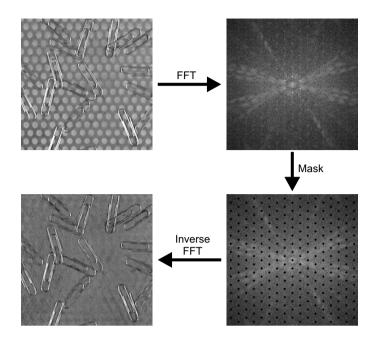

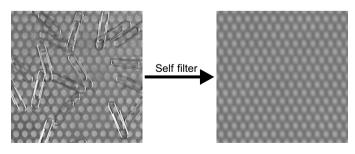

|    |                        |                           | Filtering                       | 318 |  |

|    |                        | 10.1.3                    | •                               | 320 |  |

|    |                        | 10.1.4                    | e                               | 321 |  |

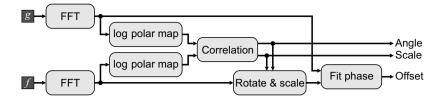

|    |                        | 10.1.5                    | Registration                    | 322 |  |

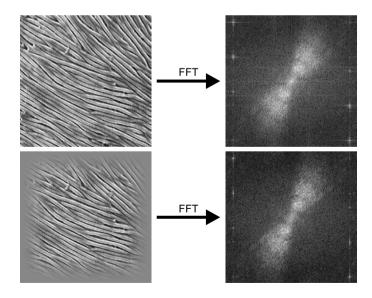

|    |                              | 10.1.6  | Feature Extraction                    | 323 |

|----|------------------------------|---------|---------------------------------------|-----|

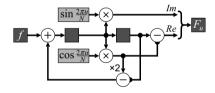

|    |                              | 10.1.7  | Goertzel's Algorithm                  | 324 |

|    | 10.2                         | Discret | te Cosine Transform                   | 325 |

|    | 10.3                         | Wavele  | et Transform                          | 328 |

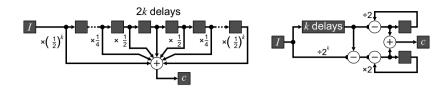

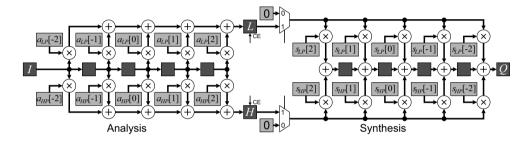

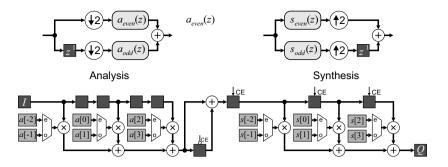

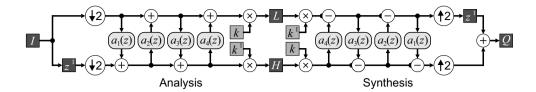

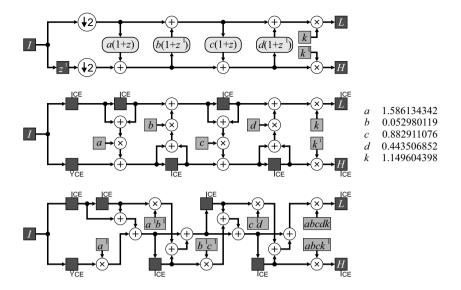

|    |                              | 10.3.1  | Filter Implementations                | 330 |

|    |                              | 10.3.2  | Applications of the Wavelet Transform | 335 |

|    | 10.4                         | Image   | and Video Coding                      | 336 |

| 11 | Blob Detection and Labelling |         |                                       | 343 |

|    |                              | Bound   |                                       | 343 |

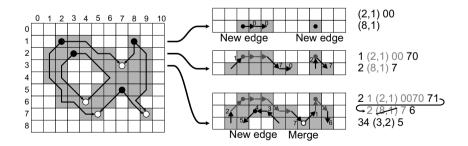

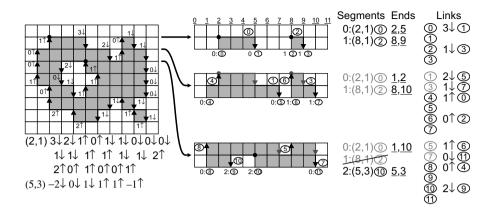

|    |                              |         | ength Coding                          | 346 |

|    | 11.3                         | Chain   |                                       | 347 |

|    |                              | 11.3.1  | 1 1                                   | 347 |

|    |                              |         | Single Pass Algorithms                | 348 |

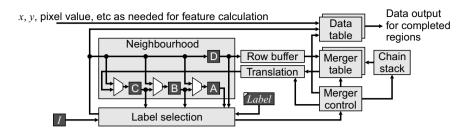

|    |                              | 11.3.3  | Feature Extraction                    | 350 |

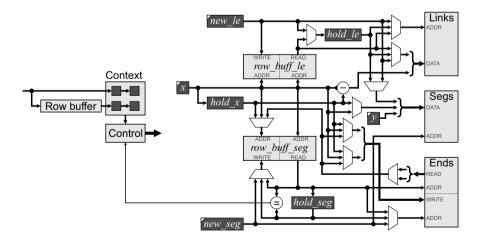

|    | 11.4                         |         | cted Component Labelling              | 352 |

|    |                              |         | Random Access Algorithms              | 353 |

|    |                              |         | Multiple-Pass Algorithms              | 353 |

|    |                              |         | Two-Pass Algorithms                   | 354 |

|    |                              |         | Single-Pass Algorithms                | 356 |

|    |                              |         | Multiple Input Labels                 | 358 |

|    |                              |         | Further Optimisations                 | 358 |

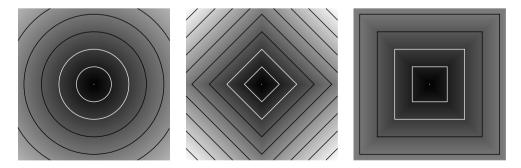

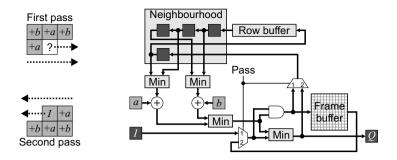

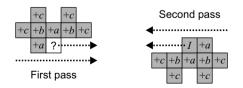

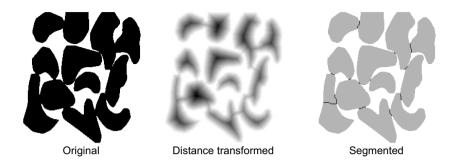

|    | 11.5                         |         | ce Transform                          | 359 |

|    |                              |         | Morphological Approaches              | 360 |

|    |                              |         | Chamfer Distance                      | 360 |

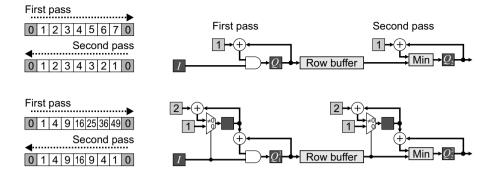

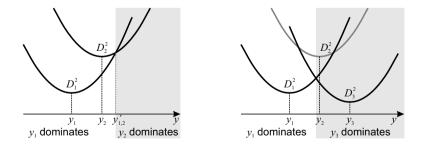

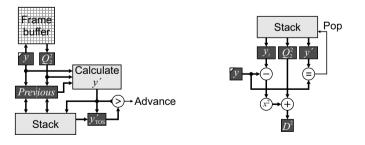

|    |                              |         | Separable Transform                   | 362 |

|    |                              |         | Applications                          | 365 |

|    |                              |         | Geodesic Distance Transform           | 365 |

|    | 11.6                         |         | shed Transform                        | 366 |

|    |                              |         | Flow Algorithms                       | 366 |

|    |                              | 11.6.2  | Immersion Algorithms                  | 367 |

|    |                              | 11.6.3  | 11                                    | 369 |

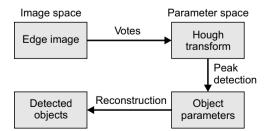

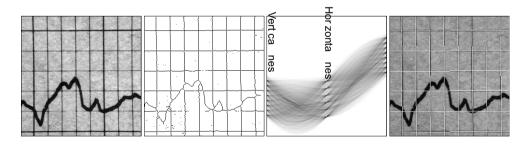

|    | 11.7                         |         | Transform                             | 370 |

|    |                              |         | Line Hough Transform                  | 371 |

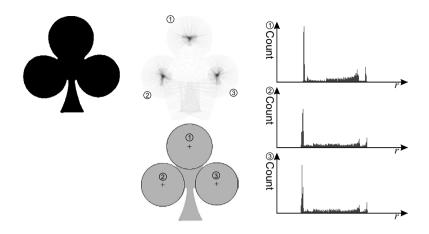

|    |                              | 11.7.2  | Circle Hough Transform                | 373 |

|    |                              | 11.7.3  | Generalised Hough Transform           | 374 |

|    | 11.8                         | Summa   | ary                                   | 375 |

| 12 | Inter                        | 377     |                                       |     |

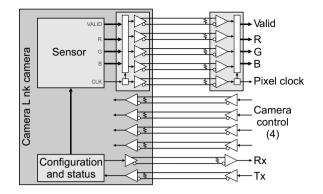

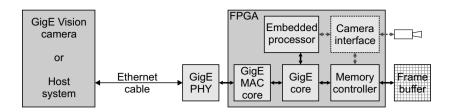

|    | 12.1                         | Camer   | a Input                               | 378 |

|    |                              | 12.1.1  | Camera Interface Standards            | 378 |

|    |                              | 12.1.2  | Deinterlacing                         | 383 |

|    |                              | 12.1.3  | Global and Rolling Shutter Correction | 384 |

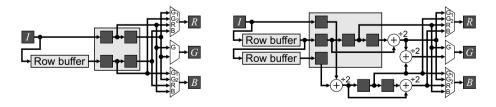

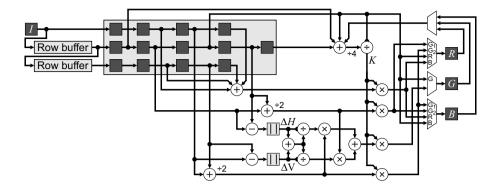

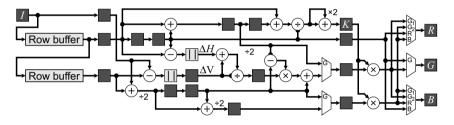

|    |                              | 12.1.4  | Bayer Pattern Processing              | 384 |

|    |                              |         |                                       |     |

|       | 12.2   | Display Output                         | 387 |  |

|-------|--------|----------------------------------------|-----|--|

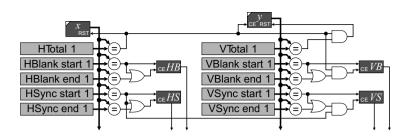

|       |        | 12.2.1 Display Driver                  | 387 |  |

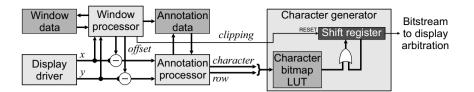

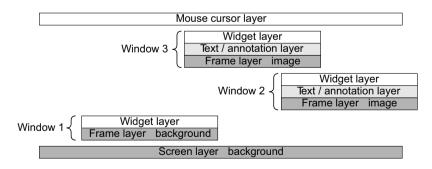

|       |        | 12.2.2 Display Content                 | 390 |  |

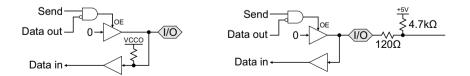

|       | 12.3   | Serial Communication                   | 393 |  |

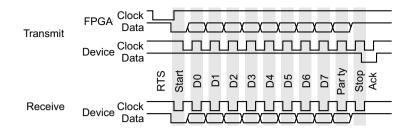

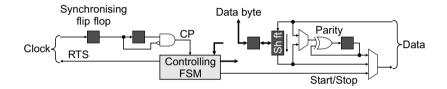

|       |        | 12.3.1 PS2 Interface                   | 393 |  |

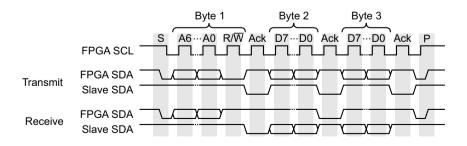

|       |        | 12.3.2 $I^2C$                          | 395 |  |

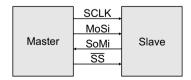

|       |        | 12.3.3 SPI                             | 397 |  |

|       |        | 12.3.4 RS-232                          | 397 |  |

|       |        | 12.3.5 USB                             | 398 |  |

|       |        | 12.3.6 Ethernet                        | 398 |  |

|       |        | 12.3.7 PCI Express                     | 399 |  |

|       | 12.4   | Memory                                 | 400 |  |

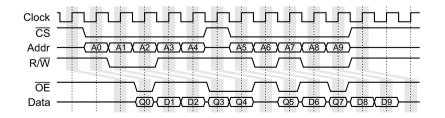

|       |        | 12.4.1 Static RAM                      | 400 |  |

|       |        | 12.4.2 Dynamic RAM                     | 401 |  |

|       |        | 12.4.3 Flash Memory                    | 402 |  |

|       | 12.5   | Summary                                | 402 |  |

| 13    | Testi  | Testing, Tuning and Debugging          |     |  |

|       | 13.1   | Design                                 | 405 |  |

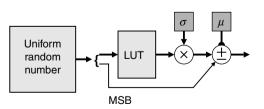

|       |        | 13.1.1 Random Noise Sources            | 406 |  |

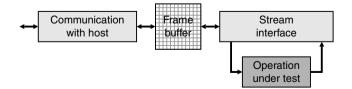

|       | 13.2   | Implementation                         | 409 |  |

|       |        | 13.2.1 Common Implementation Bugs      | 410 |  |

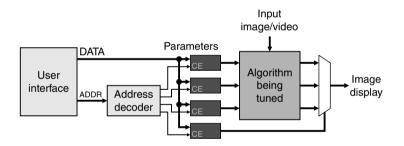

|       | 13.3   | Tuning                                 | 412 |  |

|       | 13.4   | Timing Closure                         | 412 |  |

| 14    | Exan   | nple Applications                      | 415 |  |

|       | 14.1   |                                        | 415 |  |

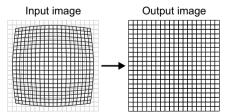

|       | 14.2   | Lens Distortion Correction             | 418 |  |

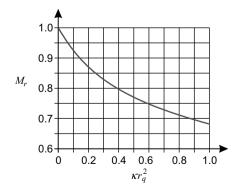

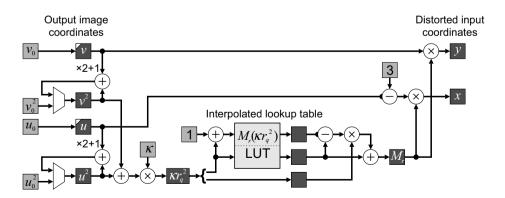

|       |        | 14.2.1 Characterising the Distortion   | 419 |  |

|       |        | 14.2.2 Correcting the Distortion       | 421 |  |

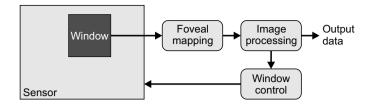

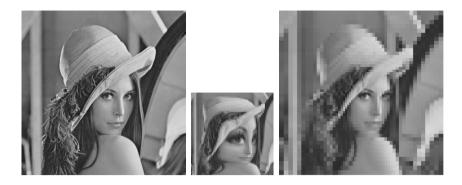

|       | 14.3   | Foveal Sensor                          | 424 |  |

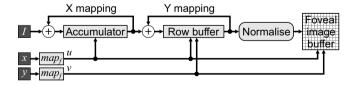

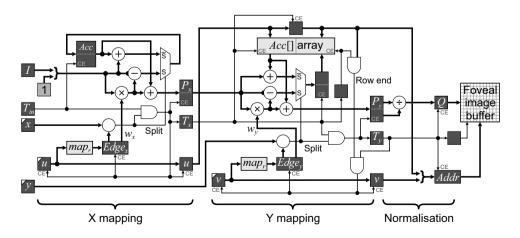

|       |        | 14.3.1 Foveal Mapping                  | 425 |  |

|       |        | 14.3.2 Using the Sensor                | 429 |  |

|       | 14.4   | Range Imaging                          | 429 |  |

|       |        | 14.4.1 Extending the Unambiguous Range | 431 |  |

|       | 14.5   | Real-Time Produce Grading              | 433 |  |

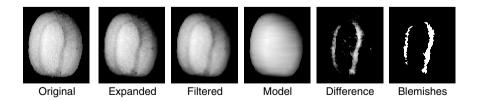

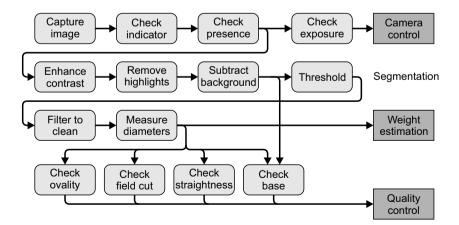

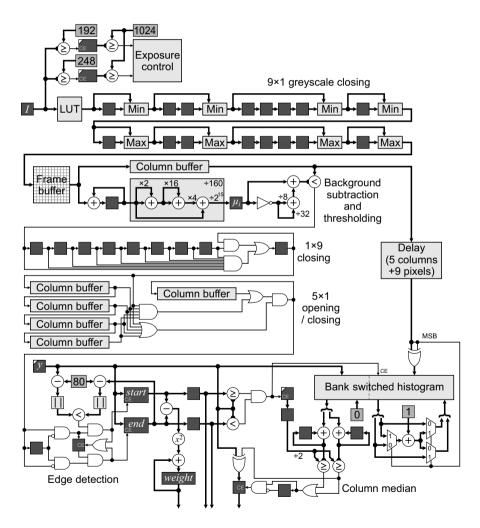

|       |        | 14.5.1 Software Algorithm              | 434 |  |

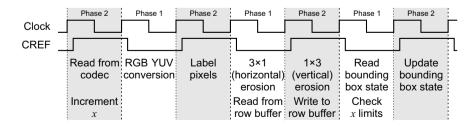

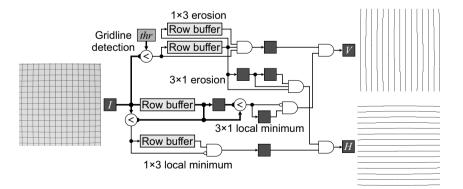

|       |        | 14.5.2 Hardware Implementation         | 436 |  |

|       | 14.6   | Summary                                | 439 |  |

| Ref   | erence | es                                     | 441 |  |

| Index |        |                                        | 475 |  |

### Preface

I think it is useful to provide a little background as to why and how this book came into being. This will perhaps provide some insight into the way the material is structured, and why it is presented in the way that it is.

#### Background

Firstly, a little bit of history. I have an extensive background in image processing, particularly in the areas of image analysis, machine vision and robot vision, all strongly application orientated areas. With over 25 years of applying image processing techniques to a wide range of problems, I have gained considerable experience in algorithm development. This is not only at the image processing application level but also at the image processing operation level. My approach to an application has usually been more pragmatic than theoretical I have focussed on developing image processing algorithms that solved the problem at hand. Often this involved assembling sequences of existing image processing operations, but occasionally it required developing new algorithms and techniques to solve particular aspects of the problem. Through work on machine vision and robotics applications, I have become aware of some of the limitations of software based solutions, particularly in terms of speed and algorithm efficiency.

This led naturally to considering FPGAs as an implementation platform for embedded imaging applications. Many image processing operations are inherently parallel and FPGAs provide program mable hardware, also inherently parallel. Therefore, it should be as simple as mapping one onto the other, right? Well, when I started implementing image processing algorithms on FPGAs, I had lots of ideas, but very little knowledge. I very soon found that there were a lot of tricks that were needed to create an efficient design. Consequently, my students and I learned many of these the hard way, through trial and error.

With my basic training as an electronics engineer, I was readily able to adapt to the hardware mindset. I have since discovered through observing my students, both at the undergraduate and postgraduate level, that this is perhaps the biggest hurdle to an efficient implementation. Image processing is traditionally thought of as a software domain task, whereas FPGA based design is firmly in the hardware domain. To bridge the gap, it is necessary to think of algorithms not on their own but more in terms of their underlying computational architecture.

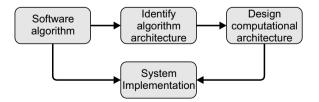

Implementing an image processing algorithm (or indeed any algorithm) on an FPGA, therefore, consists of determining the underlying architecture of an algorithm, mapping that architecture onto the resources available within an FPGA and finally mapping the algorithm onto the hardware architecture. Unfortunately, there is very little material available to help those new to the area to get started. Even this insight into the process is not actually stated anywhere, although it is implicitly followed (whether consciously or not) by most people working in this area.

### **Available Literature**

While there are many research papers published in conference proceedings and journals, there are only a few that focus specifically on how to map image processing algorithms onto FPGAs. The research papers found in the literature can be classified into several broad groups.

The first focuses on the FPGA architecture itself. Most of these provide an analysis of a range of techniques relating to the structure and granularity of logic blocks, the routing networks and embedded memories. As well as the FPGA structure, a wide range of topics is covered, including underlying technology, power issues, the effects of process variability and dynamic reconfigurability. Many of these papers are purely proposals or relate to prototype FPGAs rather than commercially available chips. Although such papers are interesting in their own right and represent perfectly legitimate research topics, very few of these papers are directly useful from an applications point of view. While they provide insights into some of the features which might be available in the next generation of devices, most of the topics within this group are at too low a level.

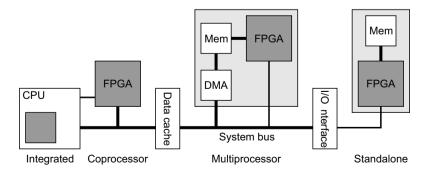

A second group of papers investigates the topic of reconfigurable computing. Here the focus is on how an FPGA can be used to accelerate some computationally intensive task or range of tasks. While image processing is one such task considered, most of the research relates more to high performance (and high power) computing rather than low power embedded systems. Topics within this group include hardware and software partitioning, hardware and software co design, dynamic reconfigurability, communication between an FPGA and CPU, comparisons between the performance of FPGAs, GPUs and CPUs, and the design of operating systems and specific platforms for both reconfigurable computing applications and research. Important principles and techniques can be gleaned from many of these papers, even though this may not be their primary focus.

The next group of papers is closely related to the previous group and considers tools for programming FPGAs and applications. The focus here is more on improving the productivity of the development process. A wide range of hardware description languages have been proposed, with many modelled after software languages such as C, Java and even Prolog. Many of these are developed as research tools, with very few making it out of the laboratory to commercial availability. There has also been considerable research on compilation techniques for mapping standard software languages to hardware. Such compilers attempt to exploit techniques such as loop unrolling, strip mining and pipelining to produce parallel hardware. Again, many of these papers describe important principles and techniques that can result in more efficient hardware designs. However, current compilers are still relatively immature in the level and kinds of parallelism that they can automatically exploit. They are also limited in that they can only perform relatively simple transformations to the algorithm provided; they cannot redesign the underlying algorithm.

The final group of papers focuses on a range of applications, including image processing and the implementation of both image processing operations and systems. Unfortunately, as a result of page limits and space constraints, many of these papers give the results of the implementation of various systems, but present relatively few design details. Often the final product is described, without describing many of the reasons or decisions that led to that design. Many of these designs cannot be recreated without acquiring the specific platform and tools that were used, or inferring a lot of the missing details. While some of these details may appear obvious in hindsight, without this knowledge many were far from obvious just from reading the papers. The better papers in this group tended to have a tighter focus, considering the implementation of a single image processing operation.

So while there may be a reasonable amount of material available, it is quite diffuse. In many cases, it is necessary to know exactly what you are looking for, or just be lucky to find it.

Shortly after beginning in this area, my research students and I wrote down a list of topics and techniques that we would have liked to have known when we started. As we progressed, our list grew. Our intention from the start was to compile this material into a book to help others who, like us, were having to learn things the hard way by themselves. Essentially, this book reflects our distilled experiences in this

field, combined with techniques (both FPGA design and image processing) that have been gleaned from the literature.

#### **Intended Audience**

This book is written primarily for those who are familiar with the basics of image processing and want to consider implementing image processing using FPGAs. It accomplishes this by presenting the techniques and approaches that we wished we knew when we were starting in this area. Perhaps the biggest hurdle is switching from a software mindset to a hardware way of thinking. Very often, when programming software, we do so without great consideration of the underlying architecture. Perhaps this is because the architecture of most software processors is sufficiently similar that any differences are really only a second order effect, regardless of how significant they may appear to a computer engineer. A good compiler is able to map the algorithm in the programming language onto the architecture relatively efficiently, so we can get away without thinking too much about such things. When programming hardware though, architecture is everything. It is not simply a matter of porting the software onto hardware. The underlying hardware architecture needs to be designed as well. In particular, programming hardware usually requires transforming the algorithm into an appropriate parallel architecture, often with significant changes to the algorithm itself. This is not something that the current generation of compilers is able to do because it requires significant design rather than just decomposition of the dataflow. This book addresses this issue by providing not only algorithms for image processing operations, but also underlying architectures that can be used to implement them efficiently.

This book would also be useful to those who are familiar with programming and applying FPGAs to other problems and are considering image processing applications. While many of the techniques are relevant and applicable to a wide range of application areas, most of the focus and examples are taken from image processing applications. Sufficient detail is given to make many of the algorithms and their implementation clear. However, I would argue that learning image processing is more than just collecting a set of algorithms, and there are any number of excellent image processing texts that provide these. Imaging is a practical discipline that can be learned most effectively by doing, and a software environment provides a significantly greater flexibility and interactivity than learning image processing via FPGAs.

That said, it is in the domain of embedded image processing where FPGAs come into their own. An efficient, low power design requires that the techniques of both the hardware engineer and the software engineer be integrated tightly within the final solution.

#### **Outline of the Contents**

This book aims to provide a comprehensive overview of algorithms and techniques for implementing image processing algorithms on FPGAs, particularly for low and intermediate level vision. However, as with design in any field, there is more than one way of achieving a particular task. Much of the emphasis has been placed on stream based approaches to implementing image processing, as these can efficiently exploit parallelism when they can be used. This emphasis reflects my background and experience in the area, and is not intended to be the last word on the topic.

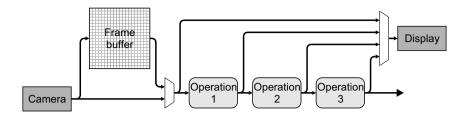

A broad overview of image processing is presented in Chapter 1, with a brief historical context. Many of the basic image processing terms are defined and the different stages of an image processing algorithm are identified and illustrated with an example algorithm. The problem of real time embedded image processing is introduced, and the limitations of conventional serial processors for tackling this problem are identified. High speed image processing must exploit the parallelism inherent in the processing of images. A brief history of parallel image processing systems is reviewed to provide the context of using FPGAs for image processing. FPGAs combine the advantages of both hardware and software systems, by providing reprogrammable (hence flexible) hardware. Chapter 2 provides an introduction to FPGA technology. While some of this will be more detailed than is necessary to implement algorithms, a basic knowledge of the building blocks and underlying architecture is important to developing resource efficient solutions. The key features of currently available FPGAs are reviewed in the context of implementing image processing algorithms.

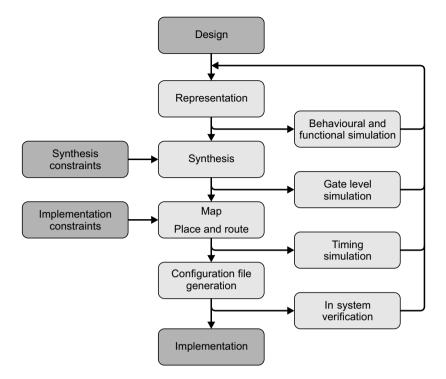

FPGA based design is hardware design, and this hardware needs to be represented using some form of hardware description language. Some of the main languages are reviewed in Chapter 3, with particular emphasis on the design flow for implementing algorithms. Traditional hardware description languages such as VHDL and Verilog are quite low level in that all of the control has to be explicitly programmed. The last 15 years has seen considerable research into more algorithm approaches to programming hardware, based primarily on C. An overview of some of this research is presented, finishing with a brief description of a number of commercial offerings.

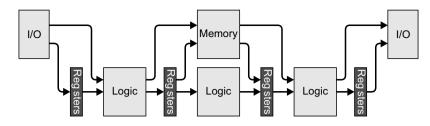

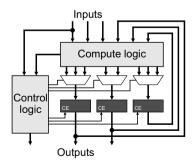

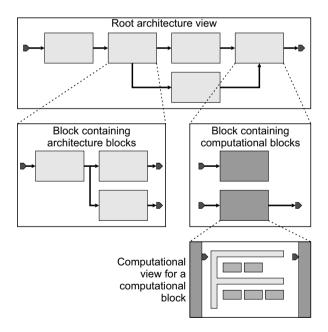

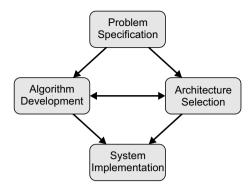

The process of designing and implementing an image processing application on an FPGA is described in detail in Chapter 4. Particular emphasis is given to the differences between designing for an FPGA based implementation and a standard software implementation. The critical initial step is to clearly define the image processing problem that is being tackled. This must be in sufficient detail to provide a specification that may be used to evaluate the solution. The procedure for developing the image processing algorithm is described in detail, outlining the common stages within many image processing algorithms. The resulting algorithm must then be used to define the system and computational architectures. The mapping from an algorithm is more than simply porting the algorithm to a hardware description language. It is necessary to transform the algorithm to make efficient use of the resources available on the FPGA. The final stage is to implement the algorithm by mapping it onto the computational architecture.

Three types of constraints on the mapping process are: limited processing time, limited access to data and limited system resources. Chapter 5 describes several techniques for overcoming or alleviating these constraints. Possible FPGA implementations are described of several data structures commonly found in computer vision algorithms. These help to bridge the gap between a software and hardware implementation. Number representation and number systems are described within the context of image processing. A range of efficient hardware computational techniques is discussed. Some of these techniques could be considered the hardware equivalent of software libraries for efficiently implementing common functions.

The next section of this book describes the implementation of many common image processing operations. Some of the design decisions and alternative ways of mapping the operations onto FPGAs are considered. While reasonably comprehensive, particularly for low level image to image transformations, it is impossible to cover every possible design. The examples discussed are intended to provide the foundation for many other related operations.

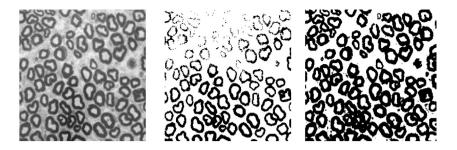

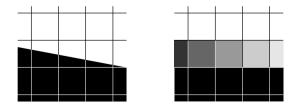

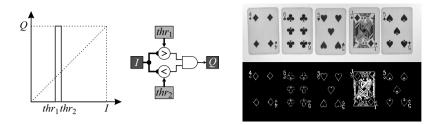

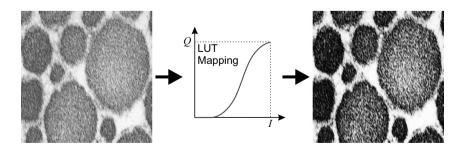

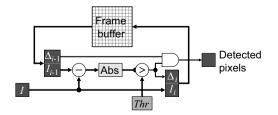

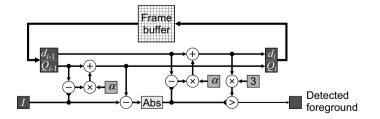

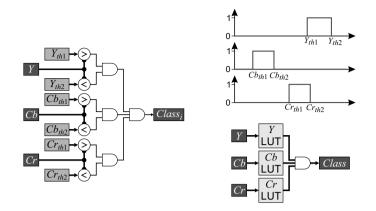

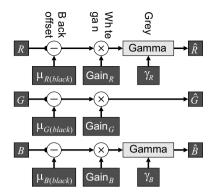

Chapter 6 considers point operations, where the output depends only on the corresponding input pixel in the input image(s). Both direct computation and lookup table approaches are described. With multiple input images, techniques such as image averaging and background subtraction are discussed in detail. The final section in this chapter extends the earlier discussion to the processing of colour images. Particular topics given emphasis are colour space conversion, colour segmentation and colour balancing.

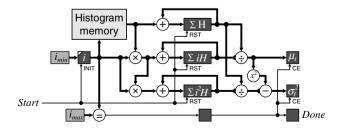

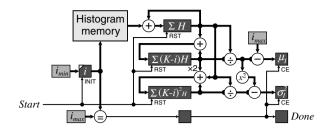

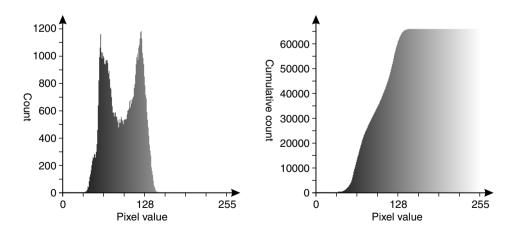

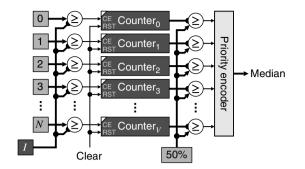

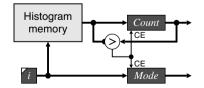

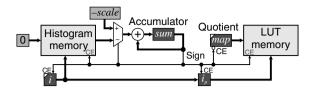

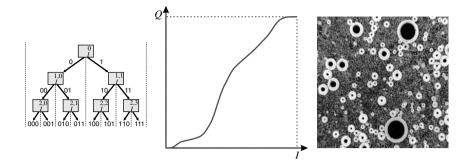

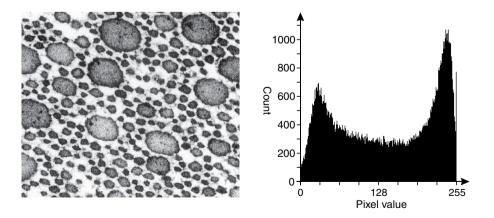

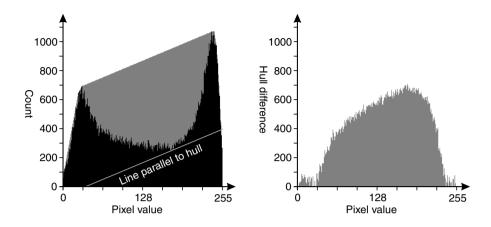

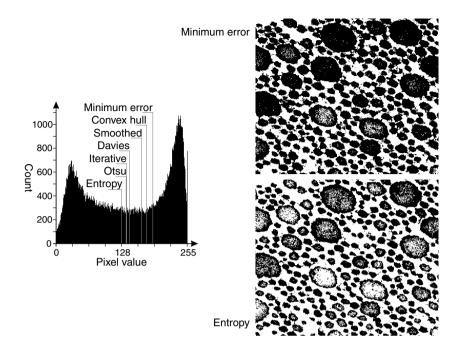

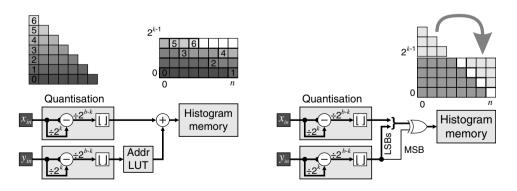

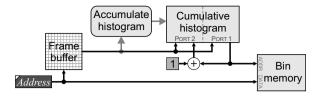

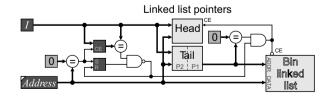

The implementation of histograms and histogram based processing are discussed in Chapter 7. Techniques of accumulating a histogram and then extracting data from the histogram are described in some detail. Particular tasks are histogram equalisation, threshold selection and using histograms for image matching. The concepts of standard one dimensional histograms are extended to multidimensional histograms. The use of clustering for colour segmentation and classification is discussed in some detail. The chapter concludes with the use of features extracted from multidimensional histograms for texture analysis.

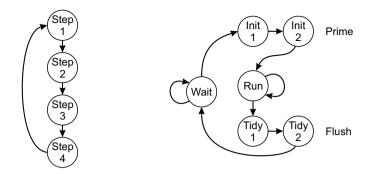

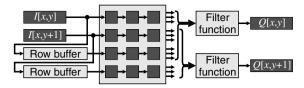

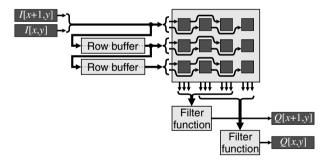

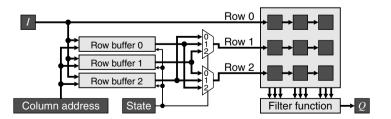

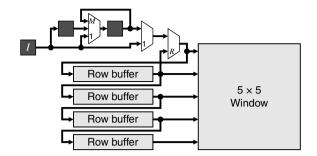

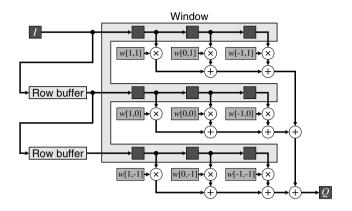

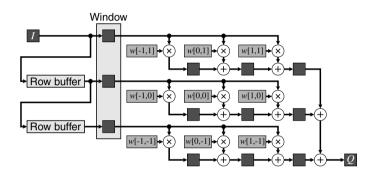

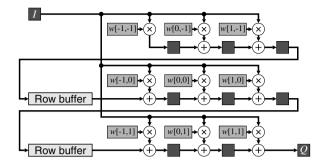

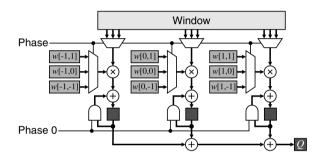

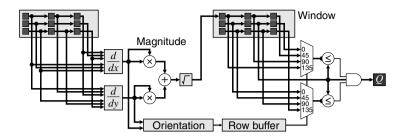

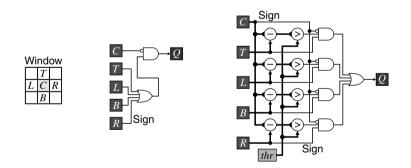

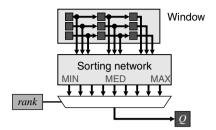

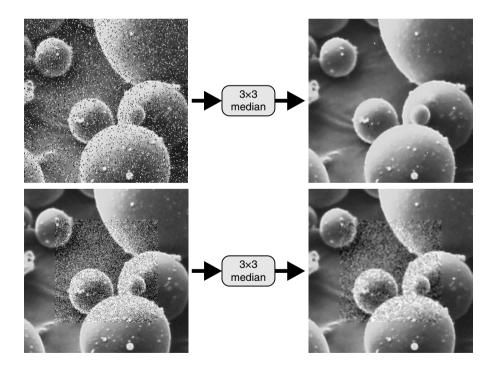

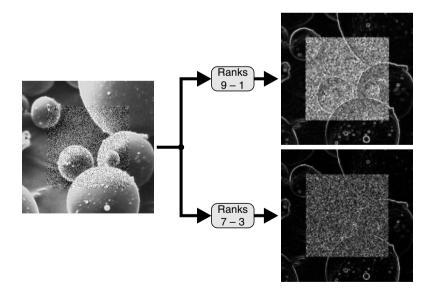

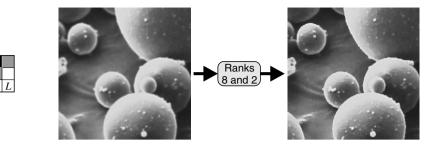

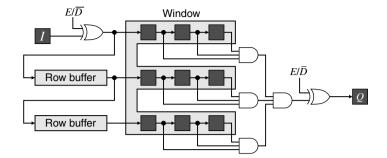

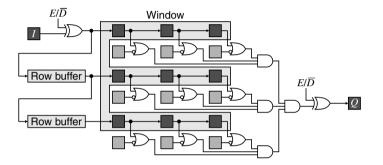

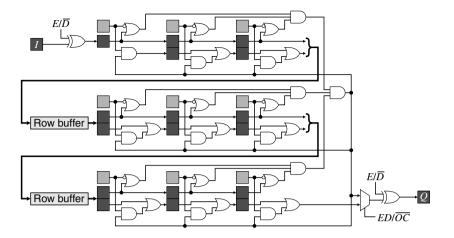

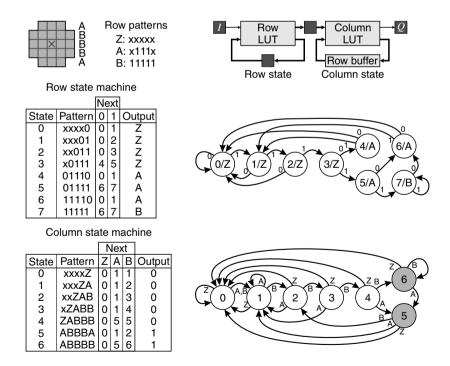

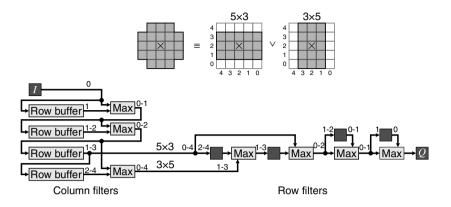

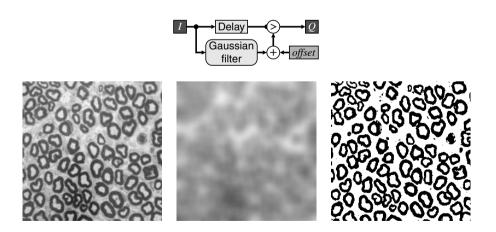

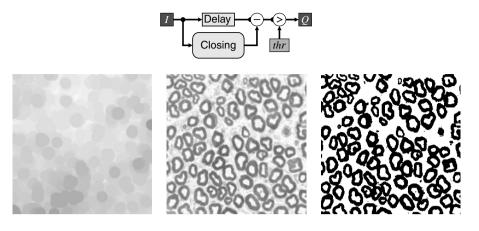

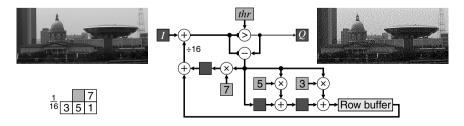

Chapter 8 focuses considers a wide range of local filters, both linear and nonlinear. Particular emphasis is given to caching techniques for a stream based implementation and methods for efficiently handling the processing around the image borders. Rank filters are described and a selection of associated sorting network architectures reviewed. Morphological filters are another important class of filters. State machine

implementations of morphological filtering provide an alternative to the classic filter implementation. Separability and both serial and parallel decomposition techniques are described that enable more efficient implementations.

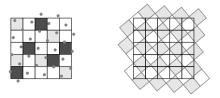

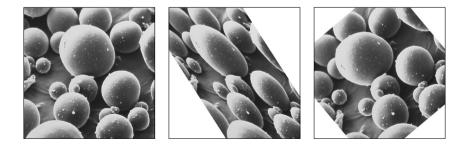

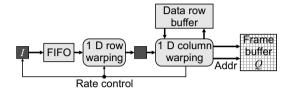

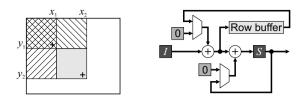

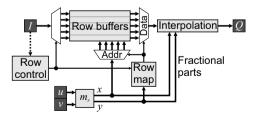

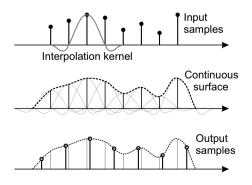

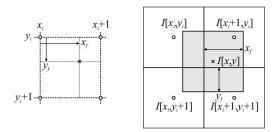

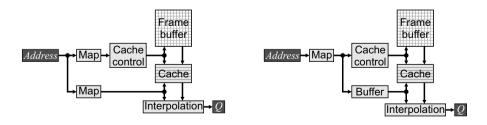

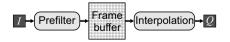

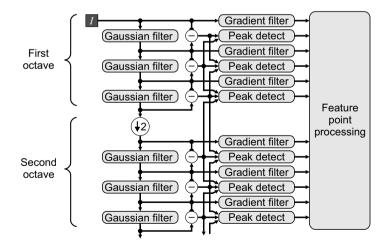

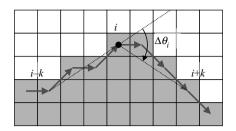

Image warping and related techniques are covered in Chapter 9. The forward and reverse mapping approaches to geometric transformation are compared in some detail, with particular emphasis on techniques for stream processing implementations. Interpolation is frequently associated with geometric transformation. Hardware based algorithms for bilinear, bicubic and spline based interpolation are described. Related techniques of image registration are also described at the end of this chapter, including a discussion of the scale invariant feature transform and super resolution.

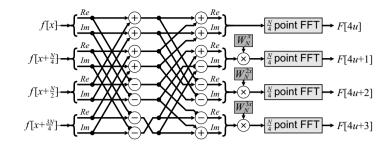

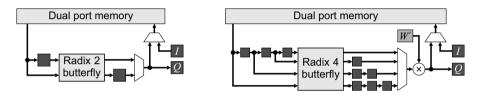

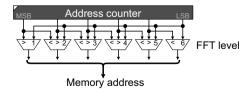

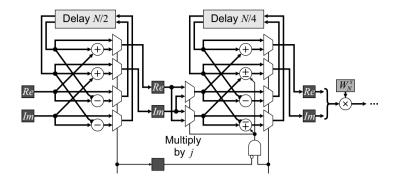

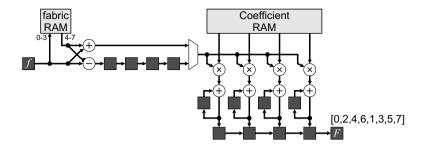

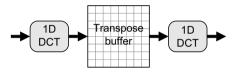

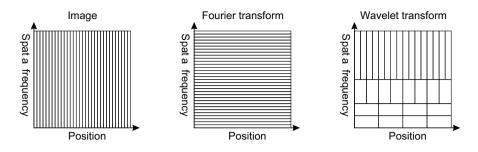

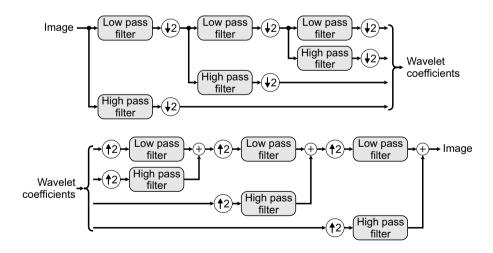

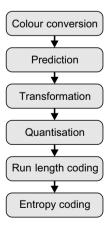

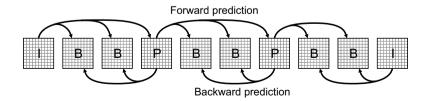

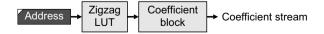

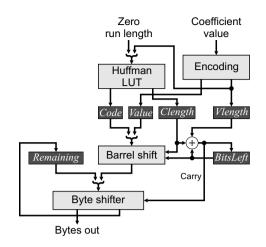

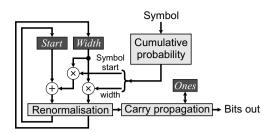

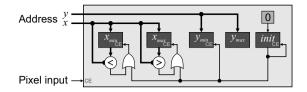

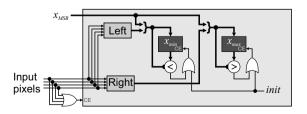

Chapter 10 introduces linear transforms, with a particular focus on the fast Fourier transform, the discrete cosine transform and the wavelet transform. Both parallel and pipelined implementations of the FFT and DCT are described. Filtering and inverse filtering in the frequency domain are discussed in some detail. Lifting based filtering is developed for the wavelet transform. This can reduce the logic requirements by up to a factor of four over a direct finite impulse response implementation. The final section in this chapter discusses the stages within image and video coding, and outlines some of the techniques that can be used at each stage.

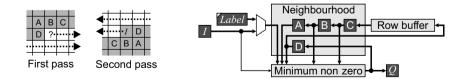

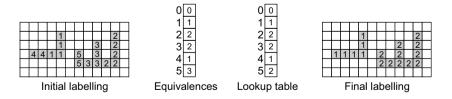

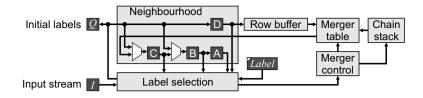

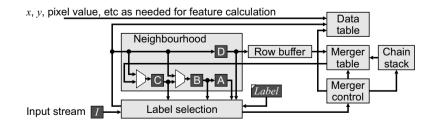

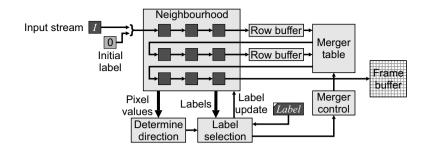

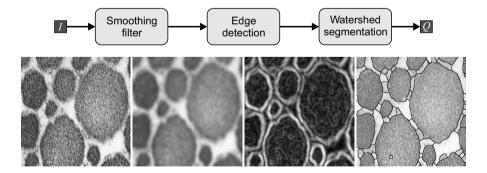

A selection of intermediate level operations relating to region detection and labelling is presented in Chapter 11. Standard software algorithms for chain coding and connected component labelling are adapted to give efficient streamed implementation. These can significantly reduce both the latency and memory requirements of an application. Hardware implementations of the distance transform, the watershed transform and the Hough transform are also described.

Any embedded application must interface with the real world. A range of common peripherals is described in Chapter 12, with suggestions on how they may be interfaced to an FPGA. Particular attention is given to interfacing cameras and video output devices, although several other user interface and memory devices are described. Image processing techniques for deinterlacing and Bayer pattern demosaicing are reviewed.

The next chapter expands some of the issues with regard to testing and tuning that were introduced earlier. Four areas are identified where an implementation might not behave in the intended manner. These are faults in the design, bugs in the implementation, incorrect parameter selection and not meeting timing constraints. Several checklists provide a guide and hints for testing and debugging an algorithm on an FPGA.

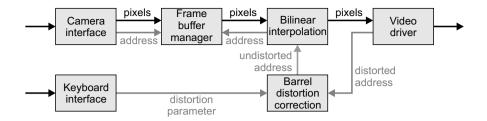

Finally, a selection of case studies shows how the material and techniques described in the previous chapters can be integrated within a complete application. These applications briefly show the design steps and illustrate the mapping process at the whole algorithm level rather than purely at the operation level. Many gains can be made by combining operations together within a compatible overall architecture. The applications described are coloured region tracking for a gesture based user interface, calibrating and correcting barrel distortion in lenses, development of a foveal image sensor inspired by some of the attributes of the human visual system, the processing to extract the range from a time of flight range imaging system, and a machine vision system for real time produce grading.

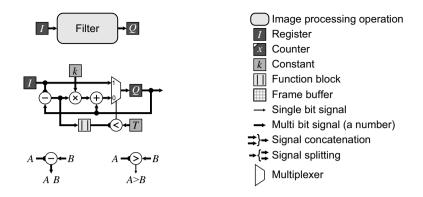

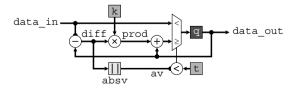

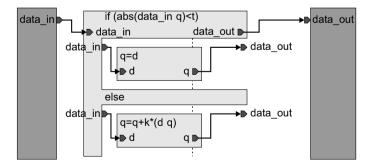

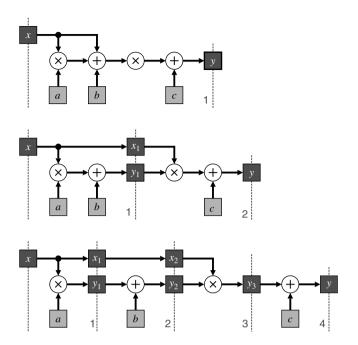

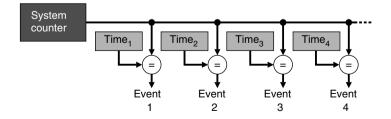

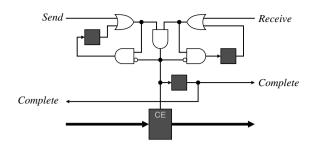

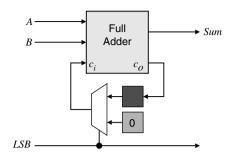

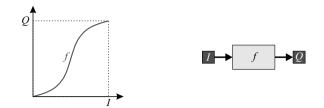

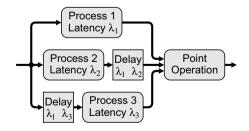

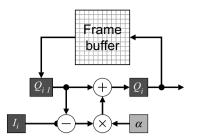

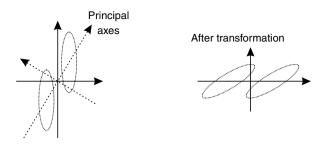

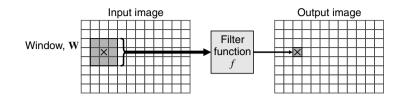

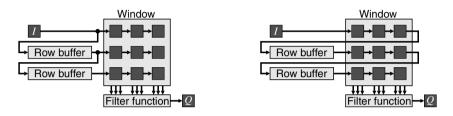

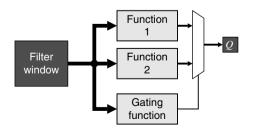

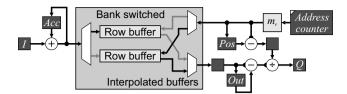

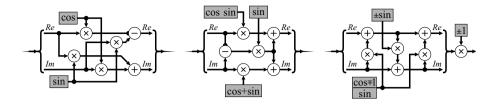

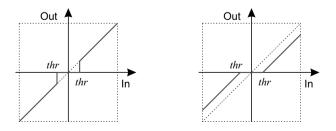

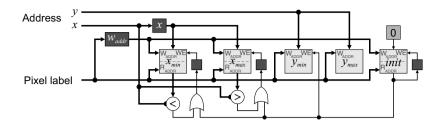

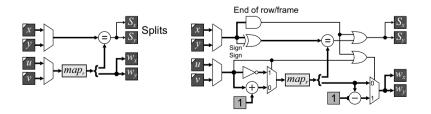

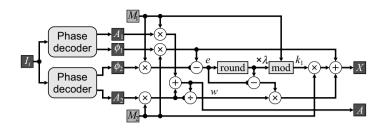

**Figure P.1** Conventions used in this book. Top left: representation of an image processing operation; middle left: a block schematic representation of the function given by Equation P.1; bottom left: representation of operators where the order of operands is important. Right: symbols used for various blocks within block schematics.

#### **Conventions Used**

The contents of this book are independent of any particular FPGA or FPGA vendor, or any particular hardware description language. The topic is already sufficiently specialised without narrowing the audience further! As a result, many of the functions and operations are represented in block schematic form. This enables a language independent representation, and places emphasis on a particular hardware implementation of the algorithm in a way that is portable. The basic elements of these schematics are illustrated in Figure P.1. *I* is generally used as the input of an image processing operation, with the output image represented by *Q*.

With some mathematical operations, such as subtraction and comparison, the order of the operands is important. In such cases, the first operand is indicated with a blob rather than an arrow, as shown on the bottom in Figure P.1.

Consider a recursive filter operating on streamed data:

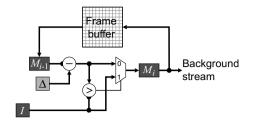

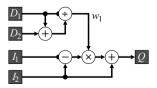

$$Q_{n} = \begin{cases} I_{n}, & |I_{n} \ Q_{n-1}| < T \\ Q_{n-1} + k(I_{n} \ Q_{n-1}), & \text{otherwise} \end{cases}$$

(P.1)

where the subscript in this instance refers to the *n*th pixel in the streamed image. At a high level, this can be considered as an image processing operation and represented by a single block, as shown in the top left of Figure P.1. The low level implementation is given in the middle left panel. The input and output, I and Q, are represented by registers dark blocks, with optional register names in white; the subscripts have been dropped because they are implicit with streamed operation. In some instances additional control inputs may be shown: CE for clock enable, RST for reset, and so on. Constants are represented as mid grey blocks and other function blocks with light grey background.

When representing logic functions in equations,  $\lor$  is used for logical OR and  $\land$  for logical AND. This is to avoid confusion with addition and multiplication.

### Acknowledgements

I would like to acknowledge all those who have helped me to get me where I currently am in my understanding of FPGA based design. In particular, I would like to thank my research students (David Johnson, Kim Gribbon, Chris Johnston, Aaron Bishell, Andreas Buhler and Ni Ma) who helped to shape my thinking and approach to FPGA development as we struggled together to work out efficient ways of implementing image processing algorithms. This book is as much a reflection of their work as it is of mine.

Most of our algorithms were programmed for FPGAs using Handel C and were tested on boards provided by Celoxica Ltd. I would like to acknowledge the support provided by Roger Gook and his team, originally with the Celoxica University Programme, and later with Agility Design Solutions. Roger provided heavily discounted licences for the DK development suite, without which many of the ideas presented in this book would not have been as fully explored.

Massey University has provided a supportive environment and the freedom for me to explore this field. In particular, Serge Demidenko gave me the encouragement and the push to begin playing with FPGAs. Since that time, he has been a source of both inspiration and challenging questions. Other colleagues who have been of particular encouragement are Gourab Sen Gupta and Richard Harris. I would also like to acknowledge Paul Lyons, who co supervised a number of my students.

Early versions of some of the material in this book were presented as half day tutorials at the IEEE Region 10 Conference (TenCon) in 2005 in Melbourne, Australia, the IEEE International Conference on Image Processing (ICIP) in 2007 in San Antonio, Texas, USA, and the 2010 Asian Conference on Computer Vision (ACCV) in Queenstown, New Zealand. I would like to thank attendees at these workshops for providing valuable feedback and stimulating discussion.

During 2008, I spent a sabbatical with the Circuits and Systems Group at Imperial College London, UK. I am grateful to Peter Cheung, who hosted my visit, and provided a quiet office, free from distractions and interruptions. It was here that I actually began writing, and got most of the text outlined at least. I would particularly like to thank Peter Cheung, Christos Bouganis, Peter Sedcole and George Constantinides for discussions and opportunities to bounce ideas off.

My wife, Robyn, has given me the freedom of many evenings and weekends over the two years since then to complete this manuscript. I am grateful for both her patience and her support. She now knows that field programmable gate arrays are not alligators with ray guns stalking the swamp. This book is dedicated to her.

Donald Bailey

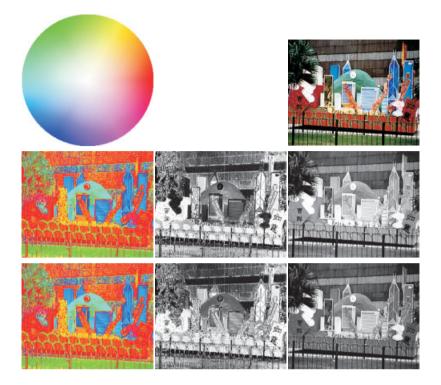

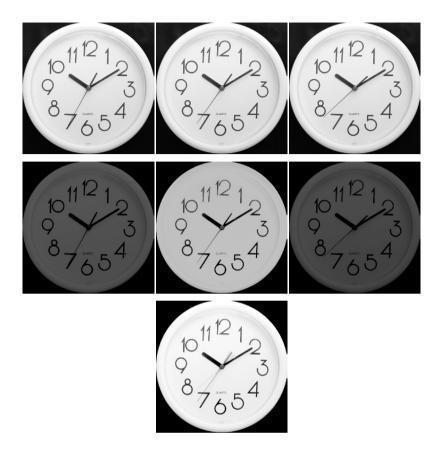

Figure 6.28 Temporal false colouring. Images taken at different times are assigned to different channels, with the resultant output showing coloured regions where there are temporal differences.

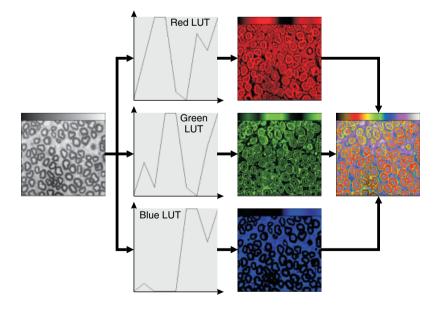

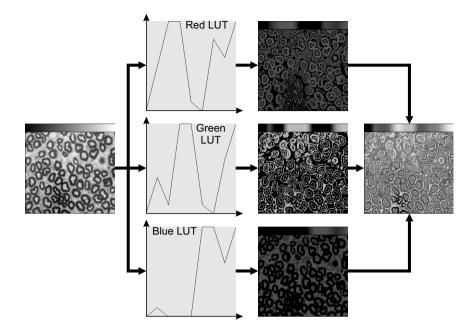

Figure 6.29 Pseudocolour or false colour mapping using lookup tables.

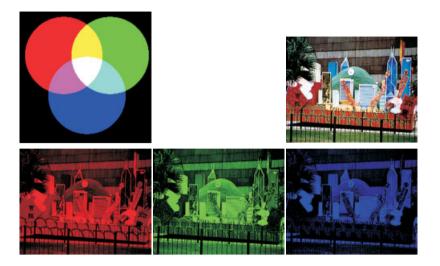

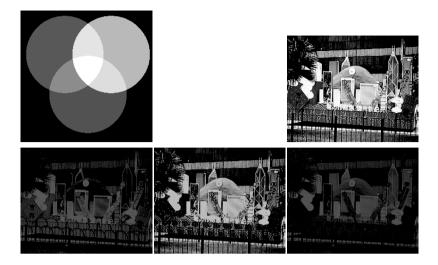

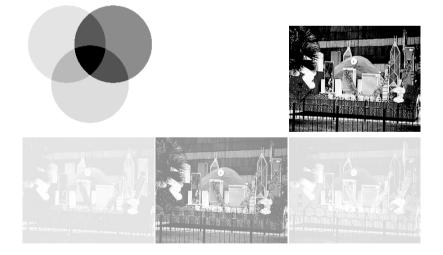

**Figure 6.30** RGB colour space. Top left: combining red, green and blue primary colours; bottom: the red, green and blue components of the colour image on the top right.

**Figure 6.32** CMY colour space. Top left: combining yellow, magenta and cyan secondary colours; bottom: the yellow, magenta and cyan components of the colour image on the top right.

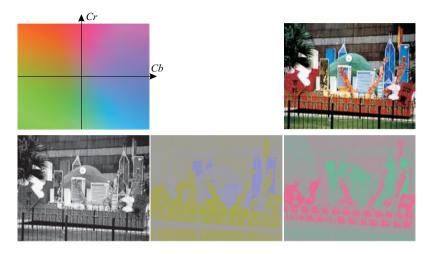

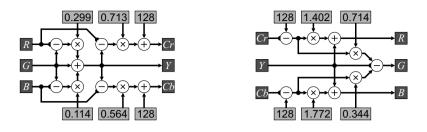

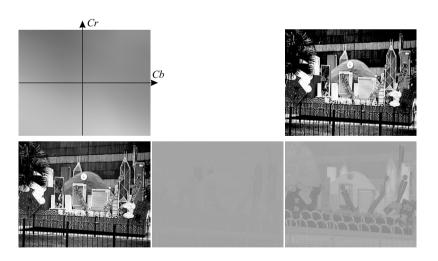

**Figure 6.34** YCbCr colour space. Top left: the Cb-Cr colour plane at mid luminance; bottom: the luminance and chrominance components of the colour image on the top right.

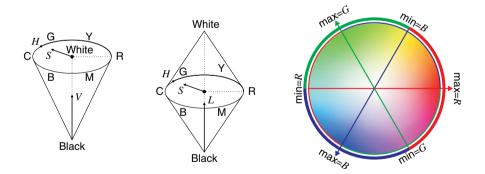

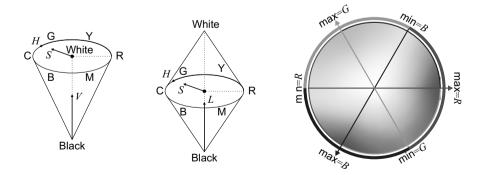

Figure 6.36 HSV and HLS colour spaces. Left: the HSV cone; centre: the HLS bi cone; right: the hue colour wheel.

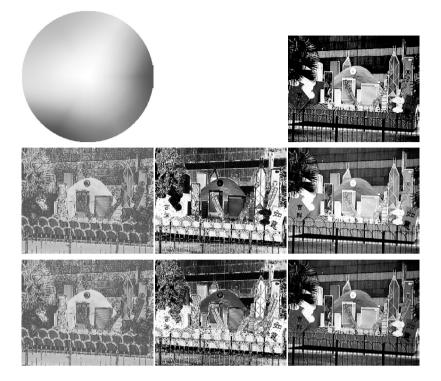

**Figure 6.37** HSV and HLS colour spaces. Top left: HSV hue colour wheel, with saturation increasing with radius; middle row: the HSV hue, saturation and value components of the colour image on the top right; bottom row: the HLS hue, saturation and lightness components.

Figure 6.40 Chromaticity diagram. The numbers are wavelengths of monochromatic light in nanometres.

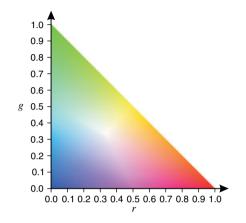

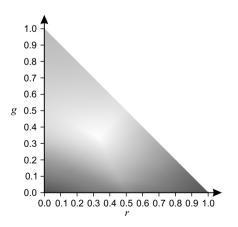

**Figure 6.41** Device dependent r-g chromaticity.

**Figure 6.43** Simple colour correction. Left: original image captured under incandescent lights, resulting in a yellowish red cast; centre: correcting assuming the average is grey, using Equation 6.86; right: correcting assuming the brightest pixel is white, using Equation 6.88.

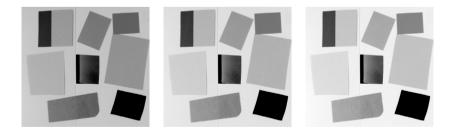

**Figure 6.44** Correcting using black, white and grey patches. Left: original image with the patches marked; centre: stretching each channel to correct for black and white, using Equation 6.90; right: adjusting the gamma of the red and blue channels using Equation 6.91 to make the grey patch grey.

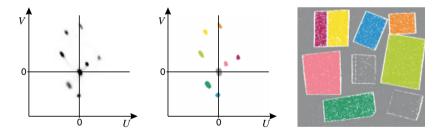

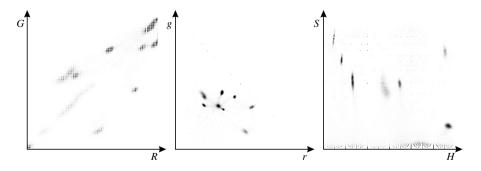

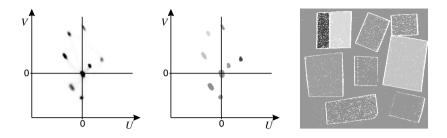

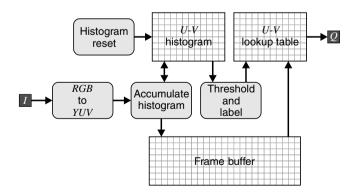

**Figure 7.24** Using a two dimensional histogram for colour segmentation. Left: U-V histogram using Equation 6.61; centre: after thresholding and labelling, used as a two dimensional lookup table; right: segmented image.

1

## Image Processing

Vision is arguably the most important human sense. The processing and recording of visual data therefore has significant importance. The earliest images are from prehistoric drawings on cave walls or carved on stone monuments commonly associated with burial tombs. (It is not so much the medium that is important here anything else would not have survived to today). Such images consist of a mixture of both pictorial and abstract representations. Improvements in technology enabled images to be recorded with more realism, such as paintings by the masters. Images recorded in this manner are indirect in the sense that the light intensity pattern is not used directly to produce the image. The development of chemical photography in the early 1800s enabled direct image recording. This trend has continued with electronic recording, first with analogue sensors, and subsequently with digital sensors, which include the analogue to digital (A/D) conversion on the sensor chip.

Imaging sensors have not been restricted to the portion of the electromagnetic spectrum visible to the human eye. Sensors have been developed to cover much of the electromagnetic spectrum from radio waves through to X rays and gamma rays. Other imaging modalities have been developed, including ultrasound, and magnetic resonance imaging. In principle, any quantity that can be sensed can be used for imaging even dust rays (Auer, 1982).

Since vision is such an important sense, the processing of images has become important too, to augment or enhance human vision. Images can be processed to enhance their subjective content, or to extract useful information. While it is possible to process the optical signals that produce the images directly by using lenses and optical filters, it is digital image processing the processing of images by computer that is the focus of this book.

One of the earliest applications of digital image processing was for transmitting digitised newspaper pictures across the Atlantic Ocean in the early 1920s (McFarlane, 1972). However, it was only with the advent of digital computers with sufficient memory and processing power that digital image processing became more widespread. The earliest recorded computer based image processing was from 1957, when a scanner was added to a computer at the National Bureau of Standards in the USA (Kirsch, 1998). It was used for some of the early research on edge enhancement and pattern recognition. In the 1960s, the need for processing large numbers of large images obtained from satellites and space exploration stimulated image processing research at NASA's Jet Propulsion Laboratory (Castleman, 1979). In parallel with this, research in high energy particle physics led to a large number of cloud chamber photographs that had to be interpreted to detect interesting events (Duff, 2000). As computers grew in power and reduced in cost, there was an explosion in the range of applications for digital image processing, from industrial inspection, to medical imaging.

Design for Embedded Image Processing on FPGAs, First Edition. Donald G. Bailey.

© 2011 John Wiley & Sons (Asia) Pte Ltd. Published 2011 by John Wiley & Sons (Asia) Pte Ltd.

### **1.1 Basic Definitions**

More formally, an *image* is a spatial representation of an object, scene or other phenomenon (Haralick and Shapiro, 1991). Examples of images include: a photograph, which is a pictorial record formed from the light intensity pattern on an optical sensor; a radiograph, which is a representation of density formed through exposure to X rays transmitted through an object; a map, which is a spatial representation of physical or cultural features; a video, which is a sequence of two dimensional images through time. More rigorously, an image is any continuous function of two or more variables defined on some bounded region of a plane.

Such a definition is not particularly useful in terms of computer manipulation. A *digital image* is an image in digital format, so that it is suitable for processing by computer. There are two important characteristics of digital images. The first is spatial quantisation. Computers are unable to easily represent arbitrary continuous functions, so the continuous function is sampled. The result is a series of discrete picture elements, or *pixels*, for two dimensional images, or volume elements, *voxels*, for three dimensional images. Sampling can result in an exact representation (in the sense that the underlying continuous function may be recovered exactly) given a band limited image and a sufficiently high sample rate. The second characteristic of digital images is sample quantisation. This results in discrete values for each pixel, enabling an integer representation. Common bit widths per pixel are 1 (binary images), 8 (greyscale images), and 24 ( $3 \times 8$  bits for colour images). Unlike sampling, value quantisation will always result in an error between the representation and true value. In many circumstances, however, this *quantisation error* or *quantisation noise* may be made smaller than the uncertainty in the true value resulting from inevitable measurement noise.

In its basic form, a digital image is simply a two (or higher) dimensional array of numbers (usually integers) which represents an object, or scene. Once in this form, an image may be readily manipulated by a digital computer. It does not matter what the numbers represent, whether light intensity, reflectance, distance to a point (or range), temperature, population density, elevation, rainfall, or any other numerical quantity.

*Image processing* can therefore be defined as subjecting such an image to a series of mathematical operations in order to obtain a desired result. This may be an enhanced image; the detection of some critical feature or event; a measurement of an object or key feature within the image; a classification or grading of objects within the image into one of two or more categories; or a description of the scene.

Image processing techniques are used in a number of related fields. While the principle focus of the fields often differs, at the fundamental level many of the techniques remain the same. Some of the distinctive characteristics are briefly outlined here.

- *Digital image processing* is the general term used for the processing of images by computer in some way or another.

- *Image enhancement* involves improving the subjective quality of an image, or the detectability of objects within the image (Haralick and Shapiro, 1991). The information that is enhanced is usually apparent in the original image, but may not be clear. Examples of image enhancement include noise reduction, contrast enhancement, edge sharpening and colour correction.

- *Image restoration* goes one step further than image enhancement. It uses knowledge of the causes of the degradation present in an image to create a model of the degradation process. This model is then used to derive an inverse process that is used to restore the image. In many cases, the information in the image has been degraded to the extent of being unrecognisable, for example severe blurring.

- *Image reconstruction* involves restructuring the data that a available into a more useful form. Examples are image super resolution (reconstructing a high resolution image from a series of low resolution images) and tomography (reconstructing a cross section of an object from a series of projections).

- Image analysis refers specifically to using computers to extract data from images. The result is usually some form of measurement. In the past, this was almost exclusively two dimensional imaging,

although with the advent of confocal microscopy and other advanced imaging techniques, this has extended to three dimensions.

- *Pattern recognition* is concerned with the identification of objects based on patterns in the measurements (Haralick and Shapiro, 1991). There is a strong focus on statistical approaches, although syntactic and structural methods are also used.

- *Computer vision* tends to use a model based approach to image processing. Mathematical models of both the scene and the imaging process are used to derive a three dimensional representation based on one or more two dimensional images of a scene. The use of models implicitly provides an interpretation of the contents of the images obtained.

The fields are sometimes distinguished based on application:

- *Machine vision* is using image processing as part of the control system for a machine (Schaffer, 1984). Images are captured and analysed, and the results are used directly for controlling the machine while performing a specific task. Real time processing is often emphasised.

- *Remote sensing* usually refers to the use of image analysis for obtaining geographical information, either using satellite images or aerial photography.

- *Medical imaging* encompasses a wide range of imaging modalities (X ray, ultrasound, magnetic resonance, etc.) concerned primarily with medical diagnosis and other medical applications. It involves both image reconstruction to create meaningful images from the raw data gathered from the sensors, and image analysis to extract useful information from the images.

- *Image and video coding* focuses on the compression of an image or image sequence so that it occupies less storage space or takes less time to transmit from one location to another. Compression is possible because many images contain significant redundant information. In the reverse step, image decoding, the full image or video is reconstructed from the compressed data.

#### **1.2 Image Formation**

While there are many possible sensors that can be used for imaging, the focus in this section is on optical images, within the visible region of the electromagnetic spectrum. While the sensing technology may differ significantly for other types of imaging, many of the imaging principles will be similar.

The first requirement to obtaining an image is some form of sensor to detect and quantify the incoming light. In most applications, it is also necessary for the sensor to be directional, so that it responds primarily to light arriving at the sensor from a particular direction. Without this direction sensitivity, the sensor will effectively integrate the light arriving at the sensor from all directions. While such sensors do have their applications, the directionality of a sensor enables a spatial distribution to be captured more easily.

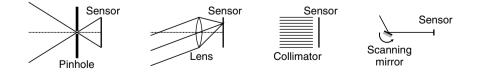

The classic approach to obtain directionality is through a pinhole as shown in Figure 1.1, where light coming through the pinhole at some angle maps to a position on the sensor. If the sensor is an array then a particular sensing element (a pixel) will collect light coming from a particular direction. The biggest

Figure 1.1 Different image formation mechanisms: pinhole, lens, collimator, scanning mirror.

limitation of a pinhole is that only limited light can pass through. This may be overcome using a lens, which focuses the light coming from a particular direction to a point on the sensor. A similar focussing effect may also be obtained by using an appropriately shaped concave mirror.

Two other approaches for constraining the directionality are also shown in Figure 1.1. A collimator allows light from only one direction to pass through. Each channel through the collimator is effectively two pinholes, one at the entrance, and one at the exit. Only light aligned with both the entrance and the exit will pass through to the sensor. The collimator can be constructed mechanically, as illustrated in Figure 1.1, or through a combination of lenses. Mechanical collimation is particularly useful for imaging modalities such as X rays, where diffraction through a lens is difficult or impossible. Another sensing arrangement is to have a single sensing element, rather than an array. To form a two dimensional image, the single element must be mechanically scanned in the focal plane, or alternatively have light from a different direction reflected towards the sensor using a scanning mirror. This latter approach is commonly used with time of flight laser range scanners (Jarvis, 1983).

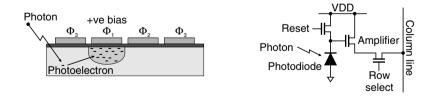

The sensor, or sensor array, converts the light intensity pattern into an electrical signal. The two most common solid state sensor technologies are charge coupled device (CCD) and complementary metal oxide semiconductor (CMOS) active pixel sensors (Fossum, 1993). The basic light sensing principle is the same: an incoming photon liberates an electron within the silicon semiconductor through the photoelectric effect. These photoelectrons are then accumulated during the exposure time before being converted into a voltage for reading out.

Within the CCD sensor (Figure 1.2) a bias voltage is applied to one of the three phases of gate, creating a potential well in the silicon substrate beneath the biased gates (MOS capacitors). These attract and store the photoelectrons until they are read out. By biasing the next phase and reducing the bias on the current phase, the charge is transferred to the next cell. This process is repeated, successively transferring the charge from each pixel to a readout amplifier where it is converted to a voltage signal. The nature of the readout process means that the pixels must be read out sequentially.

A CMOS sensor detects the light using a photodiode. However, rather than transferring the charge all the way to the output, each pixel has a built in amplifier that amplifies the signal locally. This means that the charge remains local to the sensing element, requiring a reset transistor to reset the accumulated charge at the start of each integration cycle. The amplified signal is connected to the output via a row select transistor and column lines. These make the pixels individually addressable, making it easier to read sections of the array, or even accessing the pixels randomly.

Although the active pixel sensor technology was developed before CCDs, the need for local transistors made early CMOS sensors impractical because the transistors consumed most of the area of the device (Fossum, 1993). Therefore, CCD sensors gained early dominance in the market. However, the continual reduction of feature sizes has meant that CMOS sensors became practical from the early 1990s. The early CMOS sensors had lower sensitivity and higher noise than a similar format CCD sensor, although with recent technological improvements there is now very little difference between the two families (Litwiller, 2005). Since they use the same process technology as standard CMOS devices, CMOS sensors also enable other functions, such as A/D conversion, to be directly integrated on the same chip.

**Figure 1.2** Sensor types. Left: the MOS capacitor sensor used by CCD cameras; right: a three transistor active pixel sensor used by CMOS cameras.

Humans are able to see in colour. There are three different types of colour receptors (cones) in the human eye that respond differently to different wavelengths of light. If the wavelength dependence of a receptor is  $S_k(\lambda)$ , and the light falling on the receptor contains a mix of light of different wavelengths,  $C(\lambda)$ , then the response of that receptor will be given by the combination of the responses of all different wavelengths:

$$R_k = \int C(\lambda) S_k(\lambda) d\lambda \tag{1.1}$$

What is perceived as colour is the particular combination of responses from the three different types of receptor. Many different wavelength distributions produce the same responses from the receptors, and therefore are perceived as the same colour. In practise, it is a little more complicated than this. The incoming light depends on the wavelength distribution of the source of the illumination,  $I(\lambda)$ , and the wavelength dependent reflectivity,  $\rho(\lambda)$ , of the object being looked at. So Equation 1.1 becomes:

$$R_k = \int I(\lambda)\rho(\lambda)S_k(\lambda)d\lambda$$

(1.2)

To reproduce a colour, it is only necessary to reproduce the associated combination of receptor responses. This is accomplished in a television monitor by producing the corresponding mixture of red, green and blue light.

To capture a colour image for human viewing, it is necessary to have three different colour receptors in the sensor. Ideally, these should correspond to the spectral responses of the cones. However, since most of what is seen has broad spectral characteristics, a precise match is not critical except when the illumination source has a narrow spectral content (for example sodium vapour lamps or LED based illumination sources). Silicon has a broad spectral response, with a peak in the near infrared. Therefore, to obtain a colour image, this response must be modified through appropriate colour filters.

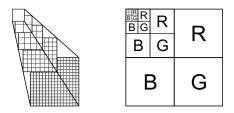

Two approaches are commonly used to obtain a full colour image. The first is to separate the red, green and blue components of the image using a prism and with dichroic filters. These components are then captured using three separate sensor chips, one for each component. The need for three chips with precise alignment makes such cameras relatively expensive. An alternative approach is to use a single chip, with small filters integrated with each pixel. Since each pixel senses only one colour, the effective resolution of the sensor is decreased. A full colour image is created by interpolating between the pixels of a component. The most commonly used colour filter array is the Bayer pattern (Bayer, 1976), with filters to select the red, green and blue primary colours. Other patterns are also possible, for example filtering the yellow, magenta and cyan secondary colours (Parulski, 1985). Cameras using the secondary colours have better low light sensitivity because the filters absorb less of the incoming light. However, the processing required to produce the output gives a better signal to noise ratio from the primary filters than from secondary filters (Parulski, 1985; Baer *et al.*, 1999).

One further possibility that has been considered is to stack the red, green and blue sensors one on top of the other (Lyon and Hubel, 2002; Gilblom *et al.*, 2003). This relies on the fact that longer wavelengths of light penetrate further into the silicon before being absorbed. Thus, by using photodiodes at different depths, a full colour pixel may be obtained without explicit filtering.

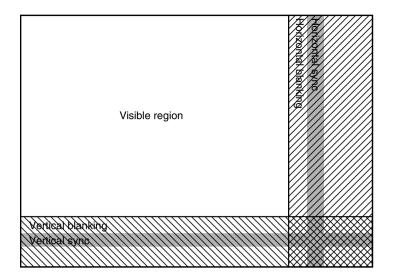

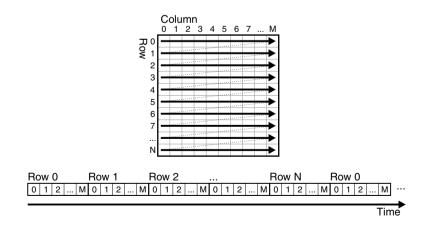

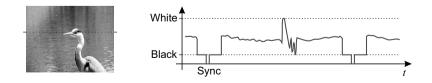

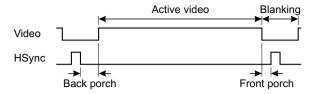

Since most cameras produce video output signals, the most common format is the same as that of television signals. A two dimensional representation of the timing is illustrated in Figure 1.3. The image is read out in raster format, with a horizontal blanking period at the end of each line. This was to turn off the cathode ray tube (CRT) electron beam while it retraced to the start of the next line. During the horizontal blanking, a horizontal synchronisation pulse controlled the timing. Similarly, after the last line is displayed there is a vertical blanking period to turn off the CRT beam while it is retraced vertically. Again, during the vertical blanking there is a vertical synchronisation pulse to control the vertical timing.

Figure 1.3 Regions within a scanned video image.

While such timing is not strictly necessary for digital cameras, at the sensor level there can also be blanking periods at the end of each line and frame.

Television signals are interlaced. The scan lines for a frame are split into two fields, with the odd and even lines produced and displayed in alternate fields. This effectively reduces the bandwidth required by halving the frame rate without producing the associated annoying flicker. From an image processing perspective, if every field is processed separately, this doubles the frame rate, albeit with reduced vertical resolution. To process the whole frame, it is necessary to re interlace the fields. This can produce artefacts; when objects are moving within the scene, their location will be different in each of the two fields. Cameras designed for imaging purposes (rather than consumer video) avoid this by producing a non interlaced or progressive scan output.

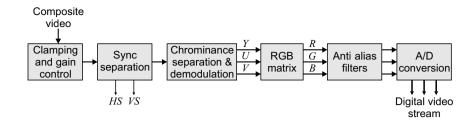

Cameras producing an analogue video signal require a *frame grabber* to capture digital images. A frame grabber preprocesses the signal from the camera, amplifying it, separating the synchronisation signals, and if necessary decoding the composite colour signal into its components. The analogue video signal is digitised by an A/D converter (or three A/D converters for colour) and stored in memory for later processing.

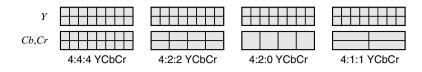

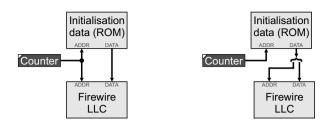

Digital cameras do much of this processing internally, directly producing a digital output. A digital sensor chip will usually provide the video data and synchronisation signals in parallel. Cameras with a low level interface will often serialise these signals (for example the Camera Link interface; AIA, 2004). Higher level interfaces will sometimes compress and will usually split the data into packets for transmission from the camera. The *raw* format is simply the digitised pixels; the colour filter array processing is not performed for single chip cameras. Another common format is RGB; for single chip sensors with a colour filter array, the pixels are interpolated to give a full colour value for each pixel. As the human eye has a higher spatial resolution to brightness than to colour, it is common to convert the image to YCbCr (Brown and Shepherd, 1995):

$$\begin{bmatrix} Y\\Cb\\Cr \end{bmatrix} = \begin{bmatrix} 65.481 & 128.553 & 24.966\\37.797 & 74.203 & 112.0\\112.0 & 93.786 & 18.214 \end{bmatrix} \begin{bmatrix} R\\G\\B \end{bmatrix} + \begin{bmatrix} 16\\128\\128 \end{bmatrix}$$

(1.3)

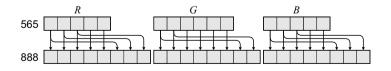

Figure 1.4 Common YCbCr subsampling formats.

where the RGB components are normalised between 0 and 1, and the YCbCr components are 8 bit integer values. The luminance component, Y, is always provided at the full sample rate, with the colour difference signals, Cb and Cr provided at a reduced resolution. Several common subsampling formats are shown in Figure 1.4. These show the size or resolution of each Cb and Cr pixel in terms of the Y pixels. For example, in the 4:2:0 format, there is a single Cb and Cr value for each  $2 \times 2$  block of Y values. To reproduce the colour signal, the lower resolution Cb and Cr values are combined with multiple luminance values. For image processing, it is usual to convert these back to RGB values using the inverse of Equation 1.3.

#### **1.3 Image Processing Operations**

After capturing the image, the next step is to process the image to achieve the desired result.

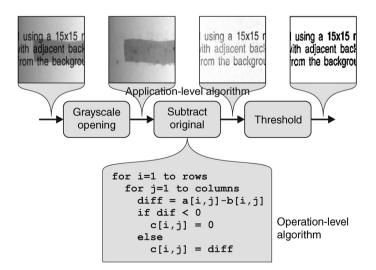

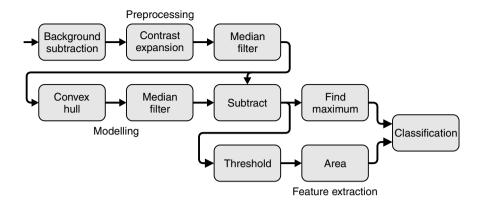

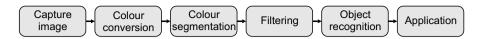

The sequence of image processing operations used to process an image from one state to another is called an *image processing algorithm*. The term algorithm is sometimes a cause of confusion, since each operation is also implemented through an algorithm in some programming language. This distinction between application level algorithms and operation level algorithms is illustrated in Figure 1.5. Usually the context will indicate in which sense the term is used.

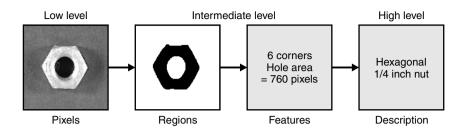

As the input image is processed by the application level algorithm, it undergoes a series of transformations. These are illustrated for a simple example in Figure 1.6. The input image consists of an array of pixels. Each pixel, on its own, carries very little information, but there are a large number of pixels. The individual pixel values represent high volume, but low value data. As the image is processed, collections of pixels are grouped together. At this intermediate level, the data may still be represented in

Figure 1.5 Algorithms at two levels: application level and operation level.

Figure 1.6 Image transformations.

terms of pixels, but the pixel values usually have more meaning; for example, they may represent a label associated with a region. At this intermediate level, the representation may depart from an explicit image representation, with the regions represented by their boundaries (for example as a chain code or a set of line segments) or their structure (for example as a quad tree). From each region, a set of features may be extracted that characterise the region. Generally, there are a small number of features (relative to the number of pixels within the region) and each feature contains significant information that can be used to distinguish it from other regions or other objects that may be encountered. At the intermediate level, the data becomes significantly lower in volume but higher in quality. Finally, at the high level, the feature data is used to classify the object or scene into one of several categories, or to derive a description of the object or scene.

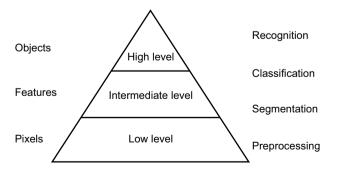

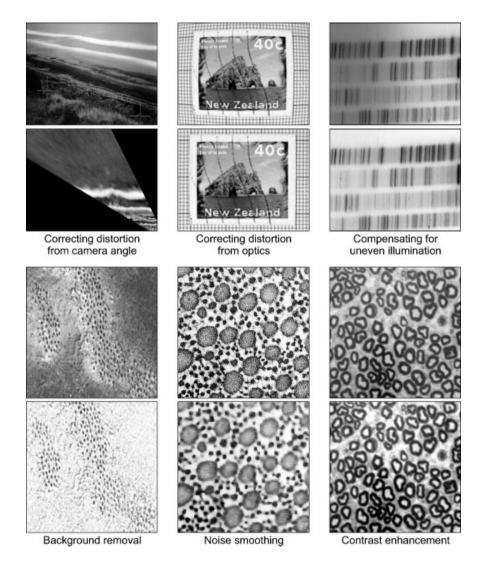

Rather than focussing on the data, it is also possible to focus on the image processing operations. The operations can be grouped according to the type of data that they process (Weems, 1991). This grouping is sometimes referred to as an image processing pyramid (Downton and Crookes, 1998; Ratha and Jain, 1999), as represented in Figure 1.7. At the lowest level of the pyramid are preprocessing operations. These are image to image transformations, with the purpose of enhancing the relevant information within the image, while suppressing any irrelevant information. Examples of preprocessing operations are distortion correction, contrast enhancement and filtering for noise reduction or edge detection. Segmentation operations such as thresholding, colour detection, region growing and connected components labelling occur at the boundary between the low and intermediate levels. The purpose of segmentation is to detect objects or regions in an image, which have some common property. Segmentation is therefore an image to identify objects or parts of objects, or to classify an object into one of several predefined categories. Classification transforms the data from regions to features, and then to labels. The data is no longer image based, but position information may be contained within the features, or be associated with the labels. At the highest level is recognition, which derives a description or some other interpretation of the scene.

Figure 1.7 Image processing pyramid.

#### **1.4 Example Application**