# Springer Series on SIGNALS AND COMMUNICATION TECHNOLOGY

## SIGNALS AND COMMUNICATION TECHNOLOGY

### **Functional Structures in Networks**

AMLn - A Language for Model Driven Development of Telecom Systems T. Muth

ISBN 3-540-22545-5

### Radio Wave Propagation

for Telecommunication Applications H. Sizun

3-540-40758-8 ISBN

### Electronic Noise and Interfering Signals

Principles and Applications G. Vasilescu

ISBN 3-540-40741-3

The Family of International Standards for Digital Video Broadcasting, 2nd ed. U. Reimers

ISBN 3-540-43545-X

### Digital Interactive TV and Metadata

Future Broadcast Multimedia A. Lugmayr, S. Niiranen, and S. Kalli ISBN 0-387-20843-7

### Adaptive Antenna Arrays

Trends and Applications S. Chandran (Ed.) ISBN 3-540-20199-8

# **Digital Signal Processing**

### with Field Programmable Gate Arrays

U. Meyer-Baese ISBN 3-540-21119-5

# Neuro-Fuzzy and Fuzzy-Neural Applications

in Telecommunications

P. Stavroulakis (Ed.) ISBN 3-540-40759-6

### SDMA for Multipath Wireless Channels

Limiting Characteristics and Stochastic Models I.P. Kovalyov

ISBN 3-540-40225-X

### **Digital Television**

A Practical Guide for Engineers W. Fischer ISBN 3-540-01155-2

### Multimedia Communication Technology

Representation, Transmission and Identification of Multimedia Signals J.R. Ohm ISBN 3-540-01249-4

### Information Measures

Information and its Description in Science and Engineering C. Arndt ISBN 3-540-40855-X

### Processing of SAR Data

Fundamentals, Signal Processing, Interferometry A. Hein ISBN 3-540-05043-4

### Chaos-Based Digital Communication Systems

Operating Principles, Analysis Methods, and Performance Evaluation F.C.M. Lau and C.K. Tse ISBN 3-540-00602-8

### **Adaptive Signal Processing**

Applications to Real-World Problems J. Benesty and Y. Huang (Eds.) ISBN 3-540-00051-8

### Multimedia Information Retrieval and Management

Technological Fundamentals and Applications D. Feng, W.C. Siu, and H.J. Zhang (Eds.) ISBN 3-540-00244-8

### Structured Cable Systems

A.B. Semenov, S.K. Strizhakov, and I.R. Suncheley ISBN 3-540-43000-8

### **UMTS**

The Physical Layer of the Universal Mobile Telecommunications System A. Springer and R. Weigel ISBN 3-540-42162-9

### Advanced Theory of Signal Detection

Weak Signal Detection in Generalized Observations I. Song, J. Bae, and S.Y. Kim ISBN 3-540-43064-4

### Wireless Internet Access over GSM and UMTS

M. Taferner and E. Bonek ISBN 3-540-42551-9

# Circuits and Systems Based on Delta Modulation

Linear, Nonlinear, and Mixed Mode Processing

With 130 Figures

Prof. Dr. Djuro G. Zrilic Department of Engineering New Mexiko Highlands University National Ave. 803 Las Vegas, NM 87701 U.S.A.

### ISBN 3-540-23751-8 Springer Berlin Heidelberg New York

Library of Congress Control Number: 2005921900

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilm or in other ways, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer-Verlag. Violations are liable to prosecution under German Copyright Law.

### Springer is a part of Springer Science+Business Media

springeronline.com

© Springer-Verlag Berlin Heidelberg 2005 Printed in The Netherlands

The use of general descriptive names, registered names, trademarks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

Typesetting: Data conversion by author.

Final processing by PTP-Berlin Protago-TEX-Production GmbH, Germany Cover-Design: design & production GmbH, Heidelberg

Printed on acid-free paper 62/3141/Yu - 5 4 3 2 1 0

# **PREFACE**

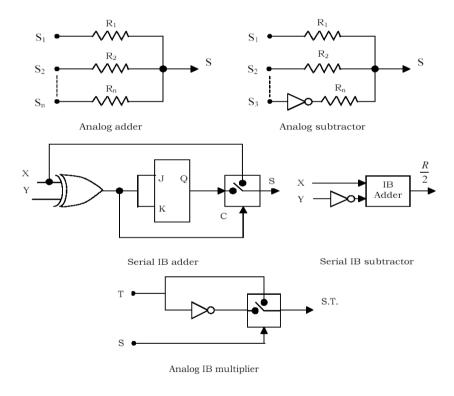

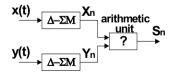

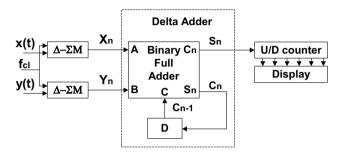

This book has the distinction of being the pioneering work on the subject of arithmetic operations of multi-valued delta modulated pulse density streams. Its focus is on both theoretical and practical aspects of different applications of linear, nonlinear, and mixed mode processing. The idea stems from a digital differential analyzer (DDA). Intensive design studies of DDA were undertaken during the 1950s in the Soviet Union, the USA, and the UK. The underlying aim was to replace software with hardware to perform real-time operations. The operation of DDA is based on the method of delta-modulation, where the idea is to build a functional arithmetic unit whose input and output is a delta modulated pulse density stream consisting of both negative and positive pulses. The instantaneous analog values are obtained by continuously averaging (demodulating) the polarities of pulses while a particular problem is being solved. Depending on the problem, individual functional units are interconnected in a similar manner to that in analog computers.

This book presents a number of such functional units for linear, nonlinear, and mixed mode processing of delta modulated pulse streams. We hope that this text provides a basis for a complementary approach to real time signal processing where traditional methods are losing their practical and economical significance.

A number of people have contributed to this text. I am grateful to Prof. Georgie Lukatela, Prof. Grozdan Petrovic, Prof. Savo Leonardis, and Prof. Lewis Franks, who in my youth introduced me to the ideas of pulse code modulation, delta modulation, digital communication, and the digital revolution in general. I am also grateful to my colleagues, Dr. Rade Majkic, Dr. Vojin Senk, Mr. Milan Narandzic, Mr. Nebojsa Pjevalica, and Dr. Danilo Mandic for their valuable comments and suggestions. A landmark paper by Dr. Nik Kouvaras, which was published in 1978 had significant influence on my work. I would like to express my gratitude to Dr. Gilbert Sanchez, my former president, who is a great proponent of science and engineering. I would also like to thank Mr. Umesh Dole, who is a graduate student at the University of New Mexico, and who helped me generate the simulation results in the text. I would also like to thank Dr. Glen W. Davidson and Mr. Tim Ames of Santa Fe, who edited the text.

Finally, I wish to express my deepest gratitude for the steadfast support of the late Dr. Dan C. Ross and Dr. Tomislav Tomic.

Djuro G. Zrilic Santa Fe, NM.

# INTRODUCTION

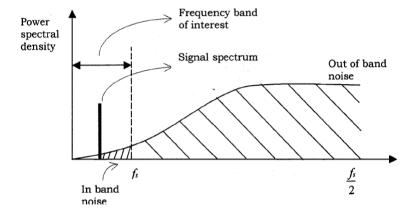

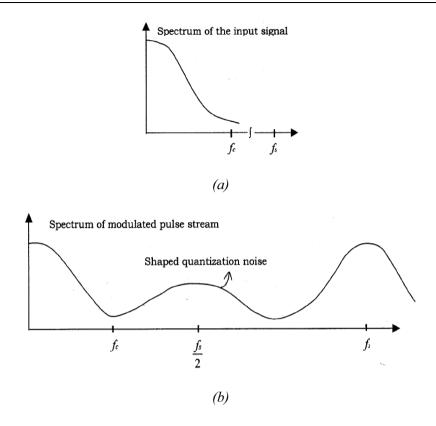

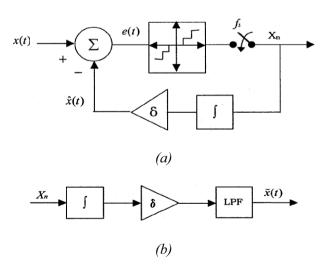

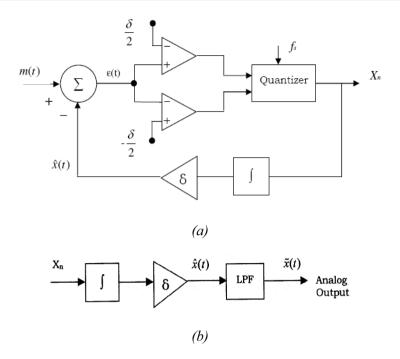

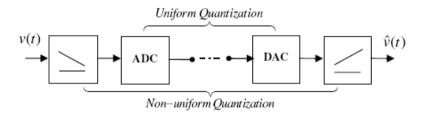

This book presents a collection of published and ongoing research work of the author over the past two decades in the area of delta modulation. Delta-sigma modulation ( $\Delta$ - $\Sigma$ M) is a very attractive, high resolution serial analog-to-digital converter (ADC). The output of a  $\Delta$ - $\Sigma$ M is a high rate, one bit, serial pulse density stream. There exists many different  $\Delta$ - $\Sigma$  modulation architectures. The bandwidth of an analog signal to be converted into a  $\Delta$ - $\Sigma$  modulator is much smaller compared to the bandwidth of the digital format of the  $\Delta$ - $\Sigma$  modulator output. Delta-sigma data converters exploit coarse quantization, which introduces quantization noise. This error is suppressed using negative feedback around the quantizer within some frequency band of interest.  $\Delta$ - $\Sigma$  ADCs are known as noise-shaping converters and they are characterized by high sampling rates, high resolution, and high signal-to-noise ratios (SNRs) over a wide dynamic range.

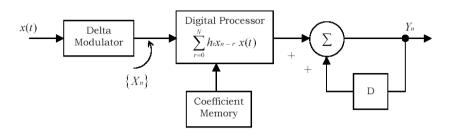

This book focuses on the processing aspects of a delta modulated pulse density stream. There exists two different approaches in this field. The traditional approach is to convert the  $\Delta$ - $\Sigma$  pulse density stream to a pulse code modulated (PCM) signal by means of decimation, and then process the multi-bit PCM word using ordinary digital signal processing (DSP) hardware. The second approach involves direct processing of a delta modulated pulse stream. To achieve this, a number of circuits have to be synthesized to perform linear, nonlinear and mixed mode arithmetic operations on a delta modulated pulse density stream. Due to over-sampling, the interface of a  $\Delta$ - $\Sigma$ M with the analog world is not expensive and is not complex compared to practical PCM interfaces. There are a number of applications where a  $\Delta$ - $\Sigma$  modulator is integrated with different types of sensors, thus eliminating the need for special types of additional interfacing circuits. Our goal is to add more functions on the same  $\Delta$ - $\Sigma$ M Integrated Circuit (IC). To implement this, additional novel circuits for direct processing of a  $\Delta$ - $\Sigma$ modulated pulse density stream have been developed.

In the following chapters, we have synthesized a number of circuits and systems for linear, nonlinear, and mixed mode processing of a  $\Delta$ - $\Sigma$  pulse density stream. The first three chapters of this book serve as a general introduction, and present a compilation of the existing literature. The first Chapter covers the basics of binary and multi-valued delta modulation. In

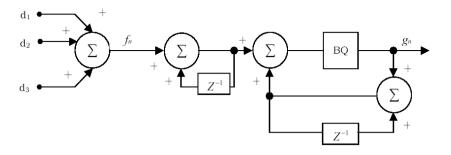

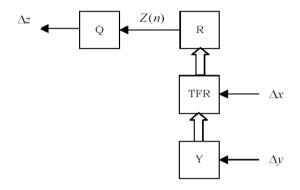

Chapter 2, some existing approaches of linear processing of a deltamodulated pulse density stream are presented. In Chapter 3, some basics of multi-valued logic are given. This introduction is needed for understanding Chapter 4, where the possibility of arithmetic operations on multi-valued delta modulation pulse density streams is examined. In fact, Chapter 4 presents a generalization of the existing binary arithmetic approaches performed on a binary delta modulated pulse density stream. In Chapter 5, we have shown the possibility of direct nonlinear processing on a delta modulated pulse density stream. In Chapter 6, the specific applications of a delta modulated pulse density stream are explored for mixed analog/digital processing. In Chapter 7, performance of two types of linear decoders are analyzed and compared to nonlinear decoders in the presence of channel errors. In Chapter 8, two different methods of direct conversion of a PCM binary word into a  $\Delta$ - $\Sigma$ M 1 bit pulse density stream are presented. In Chapter 9, two examples of stochastic processing of a  $\Delta$ - $\Sigma$ M pulse density stream are given. An example of using binary  $\Delta$ - $\Sigma$  arithmetic in measurement and instrumentation is elaborated in Chapter 10. Chapter 11 gives examples of compression of low-pass and band-pass  $\Delta$ - $\Sigma$ M pulse density streams. In addition, possibility of arithmetic operations on band-pass Δ- $\Sigma$ M pulse density streams is demonstrated.

# **CONTENTS**

| PREFACE                                         | VII |

|-------------------------------------------------|-----|

| INTRODUCTION                                    | IX  |

| CHAPTER 1 DELTA MODULATION SYSTEMS              | 1   |

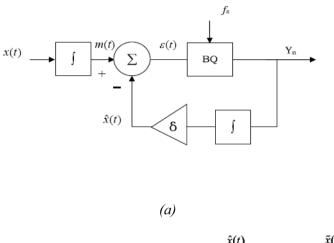

| 1.1 LINEAR DELTA MODULATION SYSTEMS             | 1   |

| 1.1.1 The Principle of LΔM                      | 1   |

| 1.1.2 Basic Parameters of LΔM                   |     |

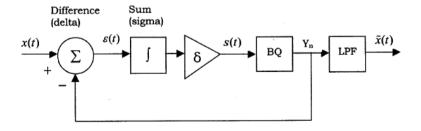

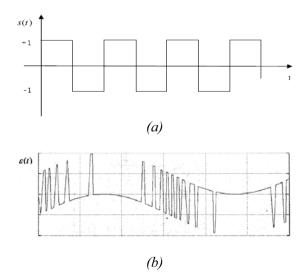

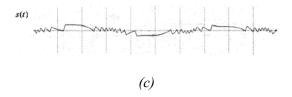

| 1.2 DELTA-SIGMA MODULATION SYSTEMS              | 9   |

| 1.2.1 The Principle of $\Delta$ – $\Sigma$ M    | 9   |

| 1.2.2 Basic Parameters of $\Delta$ – $\Sigma M$ | 13  |

| 1.2.3 Linear model of $\Delta$ – $\Sigma$ M     | 16  |

| 1.2.4 Anti-Aliasing Requirements                | 18  |

| 1.3 MULTI-LEVEL DELTA MODULATION SYSTEMS        |     |

| 1.3.1 Signal-to-Noise Ratio                     | 20  |

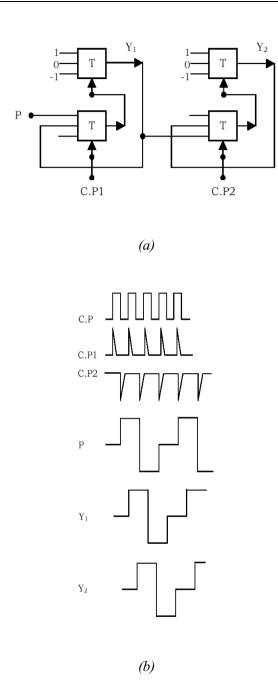

| 1.3.2 Ternary ΔM System (TΔM)                   |     |

| 1.3.3 Tri-level Delta-Sigma Modulation          |     |

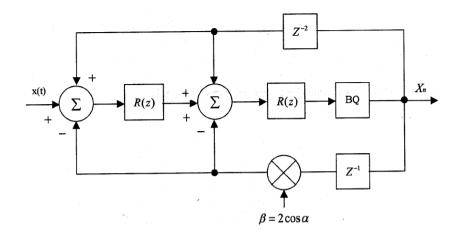

| 1.4 BAND-PASS DELTA-SIGMA MODULATION            |     |

| 1.4.1 Band-pass Sampling Theorem                | 24  |

| 1.5 CONCLUSION                                  |     |

| REFERENCES                                      | 28  |

| CHAPTER 2 LINEAR ARITHMETIC OPERATIONS          | 29  |

| 2.1 INTRODUCTION                                |     |

| 2.2 EXISTING ARITHMETIC CIRCUITS SOLUTIONS      | 30  |

| 2.2.1 The Approach of Kouvaras                  | 35  |

| 2.3 CONCLUSION                                  | 38  |

| REFERENCES                                      | 39  |

| CHAPTER 3 BASIC TERNARY LOGIC CIRCUITS          | 41  |

| 3.1 INTRODUCTION                                |     |

| 3.2 M           | ULTI-VALUED ALGEBRA AND FUNCTIONAL                                                      |      |

|-----------------|-----------------------------------------------------------------------------------------|------|

| CC              | OMPLETENESS                                                                             | 43   |

|                 | IPLEMENTATION OF TERNARY FULL ADDER                                                     |      |

| 3.4 M           | EMORY ELEMENT BASED ON T-GATE                                                           | 46   |

|                 | ONCLUSION                                                                               |      |

|                 | RENCES                                                                                  |      |

|                 |                                                                                         |      |

|                 | CR 4 MULTIVALUED ARITHMETIC                                                             |      |

|                 | TIONS                                                                                   |      |

|                 | TRODUCTION                                                                              |      |

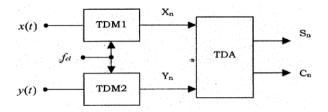

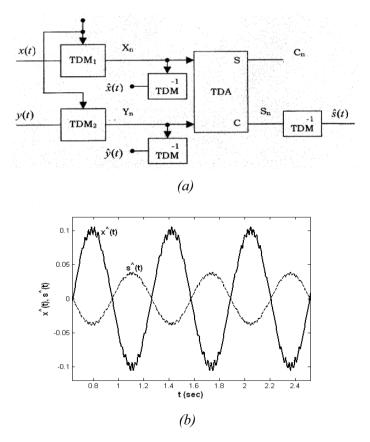

|                 | DDITION OF TWO OR MORE TAM SEQUENCES.                                                   |      |

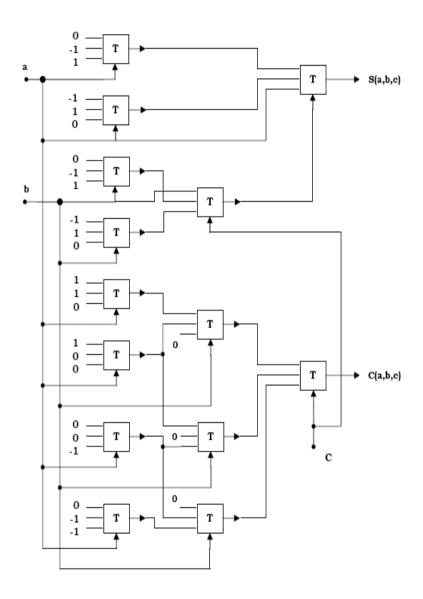

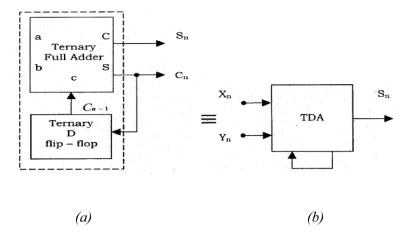

|                 | Addition of Two Ternary ΔM Sequences                                                    |      |

| 4.2.2           | <b>1</b>                                                                                |      |

|                 | Multiplication of $T\Delta M$ Signal With a Constant                                    |      |

|                 | Synthesis of Ternary Delta Multiplier                                                   |      |

|                 | Ternary Delta Tripler                                                                   |      |

|                 | DDITION OF MULTIVALUED TAM SEQUENCES                                                    |      |

|                 | ESULTS OF SIMULATION                                                                    |      |

| 4.5 CC          | ONCLUSION                                                                               | 71   |

| REFE            | RENCES                                                                                  | 72   |

| СНАРТЕ          | CR 5 NONLINEAR ARITHMETIC OPERATIONS                                                    | S 73 |

|                 | ASIC $\Delta$ - $\Sigma$ M CONCEPT                                                      |      |

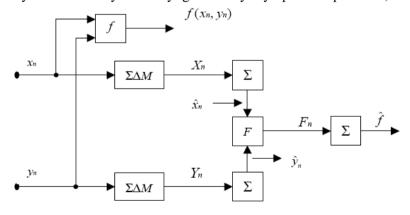

|                 | ASIC A=2M CONCEPTASIC A=2M CONCEPTASIC A=2M CONCEPTASIC A=2M CONCEPT                    |      |

|                 | ONSTRUCTION OF NONLINEAR MEMORYLESS                                                     |      |

|                 | EVICES                                                                                  |      |

|                 | OME SIMULATION RESULTS                                                                  |      |

| 5.4.3C<br>5.4.1 |                                                                                         |      |

|                 |                                                                                         |      |

| 5.4.2           | Mapping Of Boolean Functions                                                            | 8 /  |

| 5.4.3           | Multiplication by A Constant Greater than One<br>Addition of Several Δ-ΣM Pulse Streams | 88   |

|                 |                                                                                         |      |

|                 | ONCLUSION                                                                               |      |

| REFER           | RENCES                                                                                  | 92   |

| CHAPTE          | CR 6 MIXED PROCESSING OF Δ-ΣM                                                           |      |

|                 | ICES                                                                                    | 93   |

| _               | TRODUCTION                                                                              |      |

|                 | IRTHER RESULTS                                                                          |      |

| 63 OPT    | IMIZATION                                        | 98  |

|-----------|--------------------------------------------------|-----|

|           | ME SIMULATION RESULTS                            |     |

|           | Mixed Mode Multiplication                        |     |

|           | •                                                |     |

|           | Mixed Mode Multiplication of an Arbitrary Analog |     |

|           | A Robust Amplitude Modulation System             |     |

|           | NCLUSION                                         |     |

|           | ENCES                                            |     |

| KEFEKE    | INCES                                            | 112 |

| CHAPTER   | 7 DECODING OF FIRST-ORDER Δ-ΣΜ                   |     |

|           | ES                                               | 113 |

| -         | CODING OF FIRST-ORDER Δ-ΣM SEQUENCES .           |     |

| 7.1.1     | Introduction                                     |     |

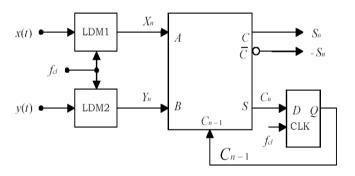

| , , , , , | Delta-Sigma Communication Model                  |     |

|           | Delta-Sigma Decoder                              |     |

| 7.1.3     | <u> </u>                                         |     |

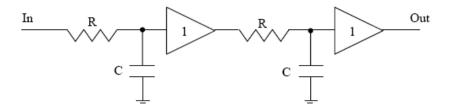

|           | PLIFIED IMPLEMENTATION OF Δ-ΣΜ                   | 110 |

|           | CODERSCODERS                                     | 110 |

| 7.2.1     |                                                  |     |

|           | Implementation of the Delta-Sigma Decoder        |     |

|           |                                                  |     |

|           | Proposed Implementation NCLUSION                 |     |

|           | NCES                                             |     |

| KEFEKE    | INCES                                            | 124 |

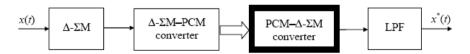

| CHAPTER   | 8 PCM – Δ-ΣM CONVERTERS                          | 125 |

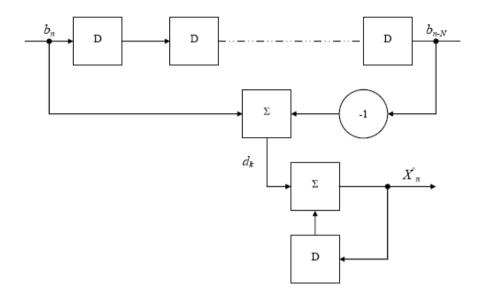

|           | $M - \Delta - \Sigma M$ CONVERTERS               |     |

| 8.1.1     | Introduction                                     |     |

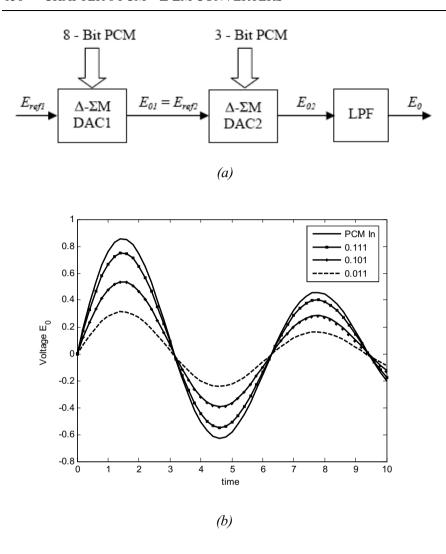

| 8.1.2     |                                                  |     |

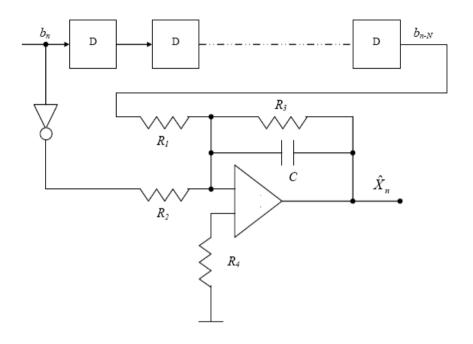

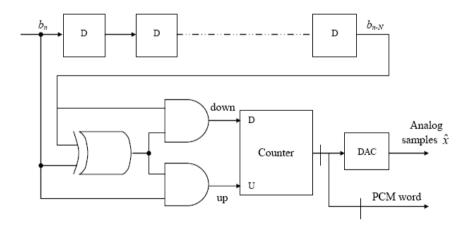

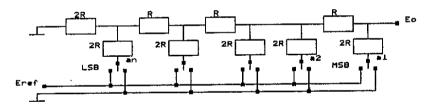

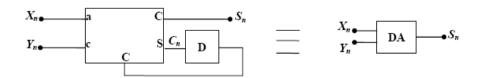

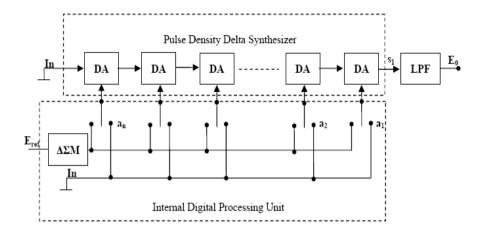

|           | ITAL-TO-ANALOG CONVERTER BASED ON                | 120 |

|           | TIME TO MINIEGO CONVENTENCIMBED ON               | 129 |

|           | Introduction                                     |     |

|           | A New DAC                                        |     |

|           | Simulation Results                               |     |

|           | VCLUSION                                         |     |

|           | ENCES                                            |     |

| KLFEKE    | INCES                                            | 140 |

| CHAPTER   | 9 STOCHASTIC PROCESSING USING                    |     |

|           |                                                  | 141 |

|           | PODICTION                                        |     |

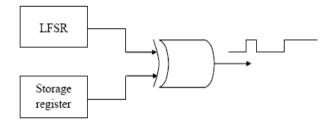

| 9.2 EXIS  | STING APPROACH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 142 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

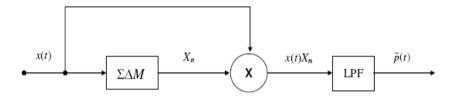

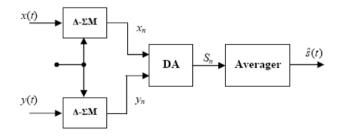

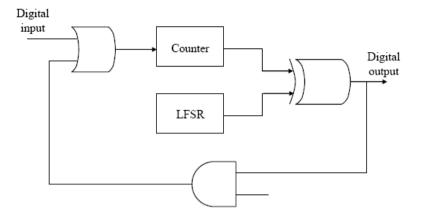

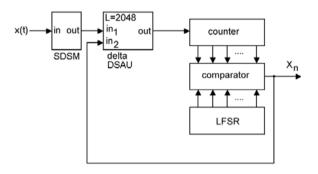

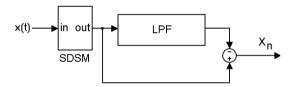

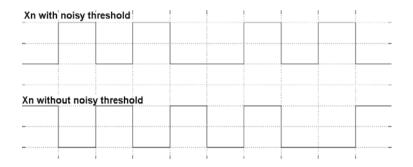

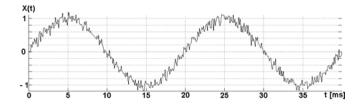

| 9.3 STO   | CHASTIC Δ-ΣM ANALOG-TO-DIGITAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

| CON       | IVERTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 144   |

| 9.4 UNI   | VERSAL Δ-ΣM ARITHMETIC UNIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 145   |

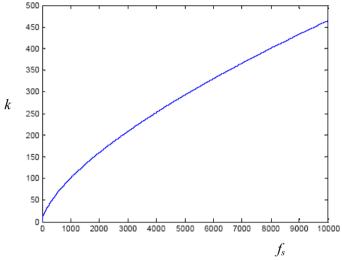

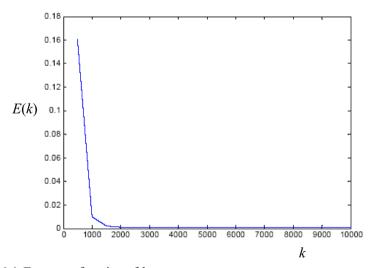

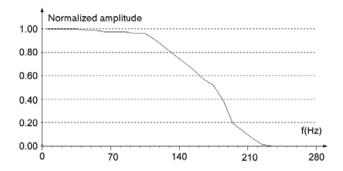

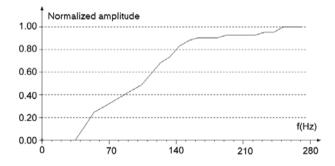

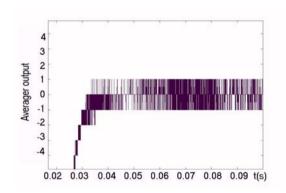

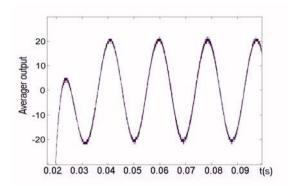

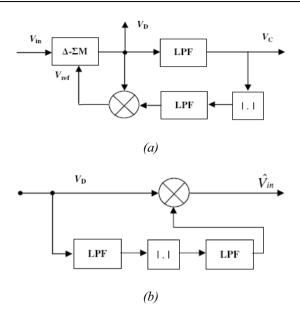

| 9.5 SIM   | ULATION RESULTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 146   |

| 9.6 CON   | ICLUSION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 148   |

| REFERE    | NCES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 149 |

| CHAPTER   | 10 MEASUREMENTS BASED ON Δ-ΣM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 151 |

| 10.1 DIRI | ECT DYNAMIC MEASUREMENT WITH INTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | VAL   |

|           | CERTAINTY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |

| 10.2THE   | MAIN IDEA BEHIND DELTA-MODULATION .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 152   |

| 10.3 DIRI | ECT DYNAMIC MEASUREMENT AND ITS ERF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ROS   |

|           | IMATE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

| 10.4DEL   | TA MODULATION: FORMAL DEFINITION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 156   |

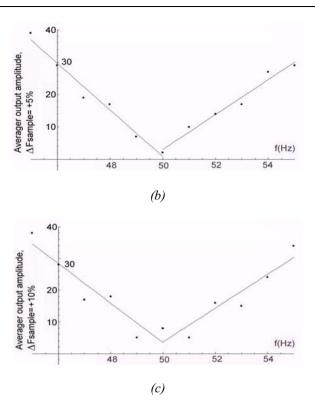

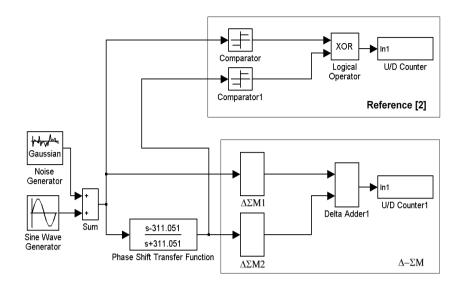

| 10.5FRE   | QUENCY DEVIATION MEASUREMENT BASE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | D     |

| ON A      | Δ-ΣΜ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 159   |

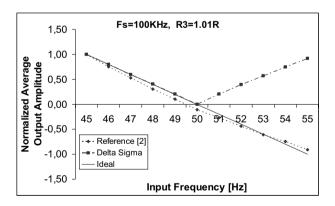

| 10.5.1    | Problem Statement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 159   |

| 10.5.2    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| 10.5.3    | Implementation Method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 163   |

| 10.5.4    | Performance Comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

| 10.6CON   | ICLUSION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 171   |

| REFERE    | NCES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 172   |

| CHAPTER   | 11 LPΔ-ΣΜ AND ΒΡΔ-ΣΜ CIRCUITS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 173   |

| 11.1INTI  | RODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 173   |

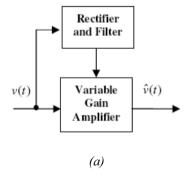

| 11.2TRA   | DITIONAL APPROACH OF COMPANDING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 174   |

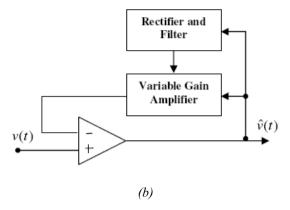

| 11.3A M   | IXED MODE COMPANDER APPROACH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 175   |

| 11.4A DI  | GITAL SQUARE-LAW COMPANDER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |