Ideal for a one-semester course, this concise textbook covers basic electronics for undergraduate students in science and engineering.

Beginning with the basics of general circuit laws and resistor circuits to ease students into the subject, the textbook then covers a wide range of topics, from passive circuits through to semiconductor-based analog circuits and basic digital circuits. Using a balance of thorough analysis and insight, readers are shown how to work with electronic circuits and apply the techniques they have learnt. The textbook's structure makes it useful as a self-study introduction to the subject. All mathematics is kept to a suitable level, and there are several exercises throughout the book. Solutions for instructors and laboratory exercises are available online at www.cambridge.org/eggleston.

"... an example of how the most important material in the introduction to electronics can be presented within a one-semester time frame. The text is written in a nice logical sequence and is beneficial for students majoring in all areas of the Natural Science ... Overall, the effort of the author is thrilling and, definitely, this text will be popular among many instructors and students."

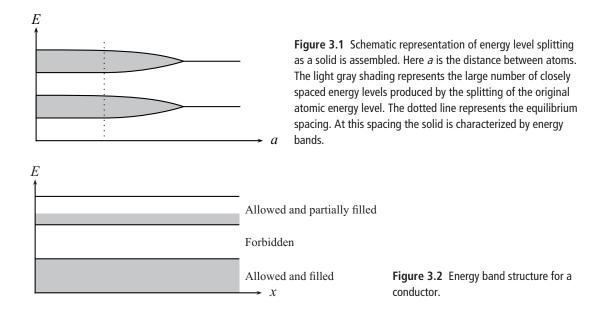

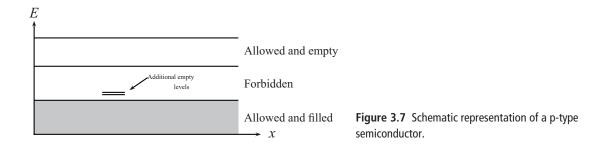

Anatoliy Glushchenko, Department of Physics and Energy Science, University of Colorado at Colorado Springs

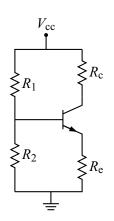

"... an excellent choice for undergraduates majoring in physics. It covers the basics, running from passive components through diodes, transistors and op-amps to digital electronics ... self-contained and a one-stop reference for the student. A brief treatment of the semiconductor physics of silicon devices provides a good basis for understanding the mathematical models of their behaviour and the end-of-chapter problems help with the learning process."

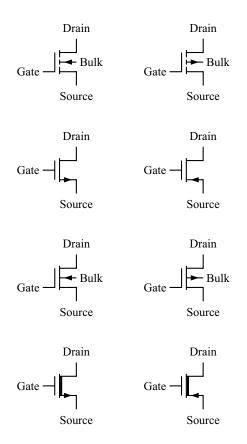

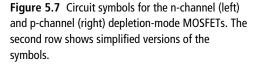

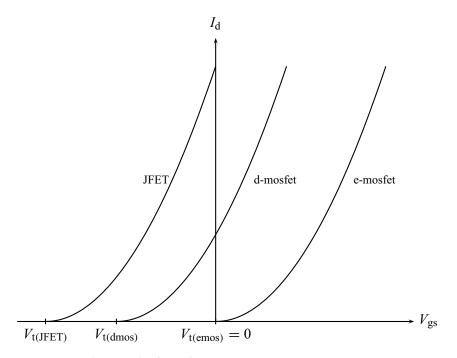

David Hanna, W C Macdonald Professor of Physics, McGill University

"I have been frustrated in the past by my inability to find a suitable book for a one-semester electronics course that starts with analog and progresses to basic digital circuits ... Eggleston's book is exactly what I was looking for ... Written concisely and clearly, the book emphasizes many practical applications, but with sufficient theoretical explanation so that the results don't simply appear out of thin air." Susan Lehman, Clare Boothe Luce Associate Professor and Chair of Physics, The College of Wooster

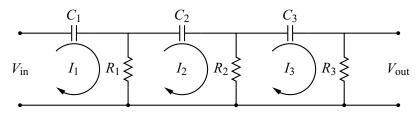

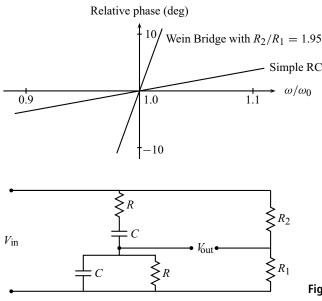

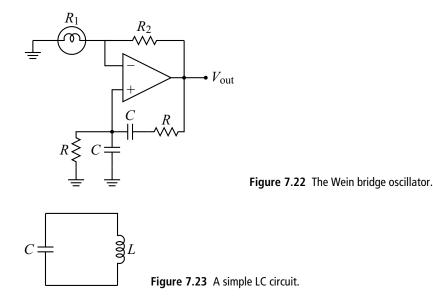

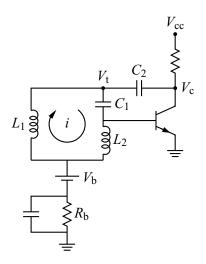

0

resources@ cambridge www.cambridge.org/eggleston

solutions for instructors

eight laboratory exercises that parallel the text

electronic version of figures

· electronic version of lightes

CAMBRIDGE UNIVERSITY PRESS www.cambridge.org Dennis

Eggleston

CAMBRIDGE

BASIC Dennis L. Eggleston ELECTRONICS for scientists and engineers

## **Basic Electronics for Scientists and Engineers**

Ideal for a one-semester course, this concise textbook covers basic electronics for undergraduate students in science and engineering.

Beginning with basics of general circuit laws and resistor circuits to ease students into the subject, the textbook then covers a wide range of topics, from passive circuits through to semiconductor-based analog circuits and basic digital circuits. Using a balance of thorough analysis and insight, readers are shown how to work with electronic circuits and apply the techniques they have learnt. The textbook's structure makes it useful as a self-study introduction to the subject. All mathematics is kept to a suitable level, and there are several exercises throughout the book. Solutions for instructors, together with eight laboratory exercises that parallel the text, are available online at www.cambridge.org/Eggleston.

**Dennis L. Eggleston** is Professor of Physics at Occidental College, Los Angeles, where he teaches undergraduate courses and labs at all levels (including the course on which this textbook is based). He has also established an active research program in plasma physics and, together with his undergraduate assistants, he has designed and constructed three plasma devices which form the basis for the research program.

## **Dennis L. Eggleston**

Occidental College, Los Angeles

CAMBRIDGE UNIVERSITY PRESS Cambridge, New York, Melbourne, Madrid, Cape Town, Singapore, São Paulo, Delhi, Dubai, Tokyo, Mexico City

Cambridge University Press The Edinburgh Building, Cambridge CB2 8RU, UK

Published in the United States of America by Cambridge University Press, New York

www.cambridge.org Information on this title: www.cambridge.org/Eggleston

© D. Eggleston 2011

This publication is in copyright. Subject to statutory exception and to the provisions of relevant collective licensing agreements, no reproduction of any part may take place without the written permission of Cambridge University Press.

First published 2011

Printed in the United Kingdom at the University Press, Cambridge

A catalog record for this publication is available from the British Library

Library of Congress Cataloging-in-Publication Data

Eggleston, Dennis L. (Dennis Lee), 1953-Basic Electronics for Scientists and Engineers / by Dennis L. Eggleston. p. cm Includes bibliographical references and index. ISBN 978-0-521-76970-9 (Hardback) – ISBN 978-0-521-15430-7 (Paperback) 1. Electronics. I. Title. TK7816.E35 2011 621.381-dc22

2010050327

ISBN 978-0-521-76970-9 Hardback ISBN 978-0-521-15430-7 Paperback

Additional resources for this publication at www.cambridge.org/Eggleston

Cambridge University Press has no responsibility for the persistence or accuracy of URLs for external or third-party internet websites referred to in this publication, and does not guarantee that any content on such websites is, or will remain, accurate or appropriate. To my wife Lynne

# Contents

|   | Preta | ice                                                          | page X1 |

|---|-------|--------------------------------------------------------------|---------|

| 1 | Basi  | c concepts and resistor circuits                             | 1       |

|   | 1.1   | Basics                                                       | 1       |

|   | 1.2   | Resistors                                                    | 4       |

|   | 1.3   | AC signals                                                   | 19      |

|   |       | Exercises                                                    | 23      |

|   |       | Further reading                                              | 26      |

| 2 | AC o  | ircuits                                                      | 27      |

|   | 2.1   | Introduction                                                 | 27      |

|   | 2.2   | Capacitors                                                   | 27      |

|   | 2.3   | Inductors                                                    | 29      |

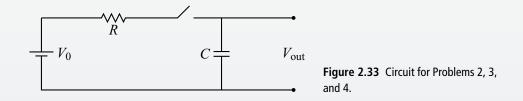

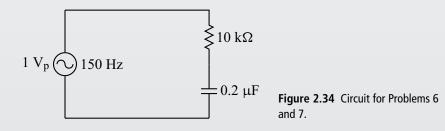

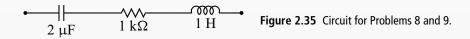

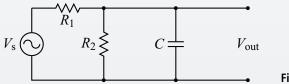

|   | 2.4   | RC circuits                                                  | 30      |

|   | 2.5   | Response to a sine wave                                      | 37      |

|   | 2.6   | Using complex numbers in electronics                         | 43      |

|   | 2.7   | Using the complex exponential method for a switching problem | 54      |

|   | 2.8   | Fourier analysis                                             | 58      |

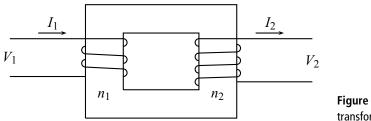

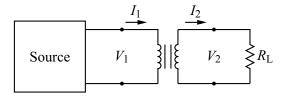

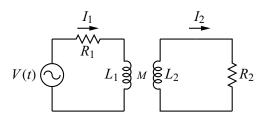

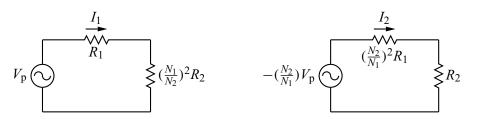

|   | 2.9   | Transformers                                                 | 61      |

|   |       | Exercises                                                    | 65      |

|   |       | Further reading                                              | 67      |

| 3 | Ban   | d theory and diode circuits                                  | 68      |

|   | 3.1   | The band theory of solids                                    | 68      |

|   | 3.2   | Diode circuits                                               | 80      |

|   |       | Exercises                                                    | 101     |

|   |       | Further reading                                              | 103     |

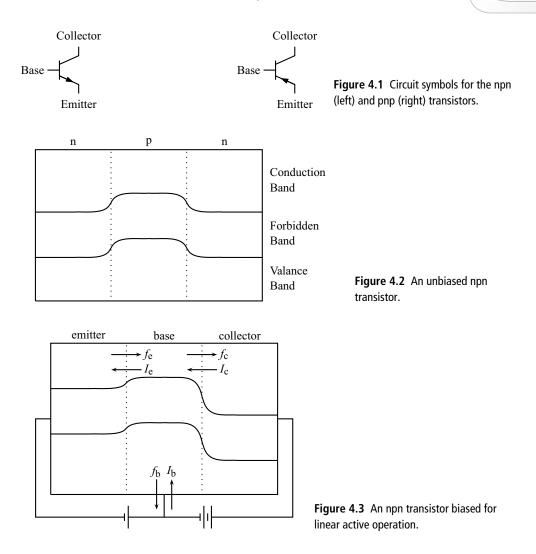

| 4 | Bipo  | lar junction transistors                                     | 104     |

|   | 4.1   | Introduction                                                 | 104     |

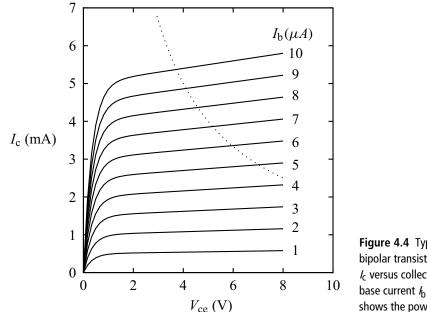

|   | 4.2   | Bipolar transistor fundamentals                              | 104     |

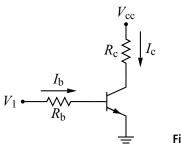

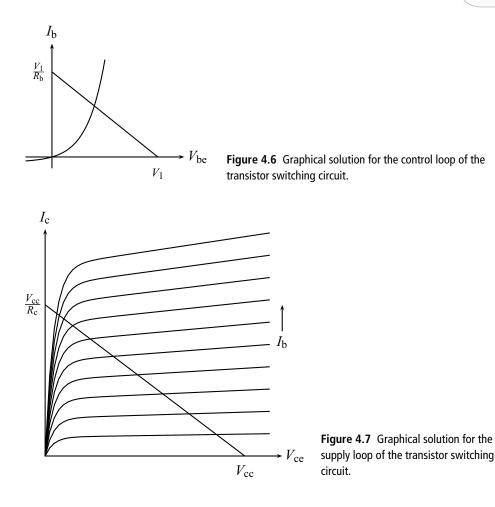

|   | 4.3  | DC and switching applications             | 108 |

|---|------|-------------------------------------------|-----|

|   | 4.4  | Amplifiers                                | 110 |

|   |      | Exercises                                 | 131 |

|   |      | Further reading                           | 132 |

| 5 | Fiel | d-effect transistors                      | 133 |

|   | 5.1  | Introduction                              | 133 |

|   | 5.2  | Field-effect transistor fundamentals      | 134 |

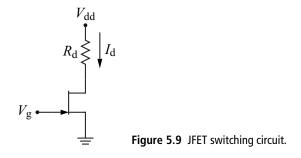

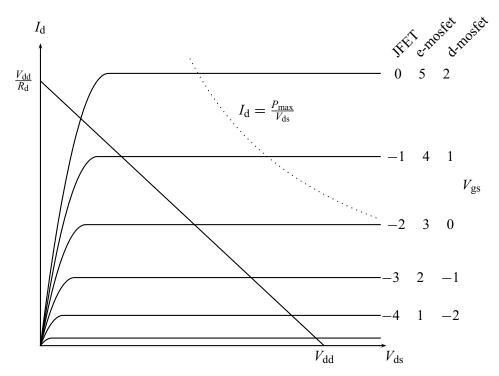

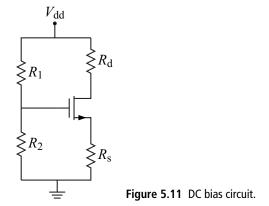

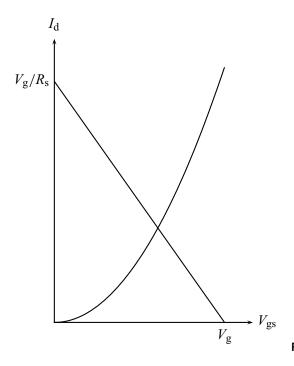

|   | 5.3  | DC and switching applications             | 140 |

|   | 5.4  | Amplifiers                                | 141 |

|   |      | Exercises                                 | 150 |

|   |      | Further reading                           | 151 |

| 6 | Оре  | erational amplifiers                      | 152 |

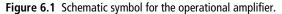

|   | 6.1  | Introduction                              | 152 |

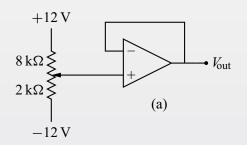

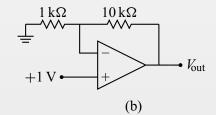

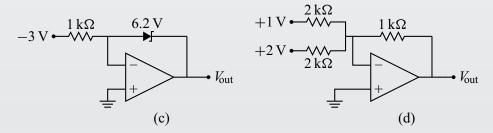

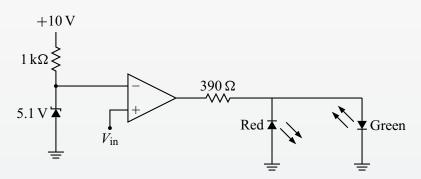

|   | 6.2  | Non-linear applications I                 | 153 |

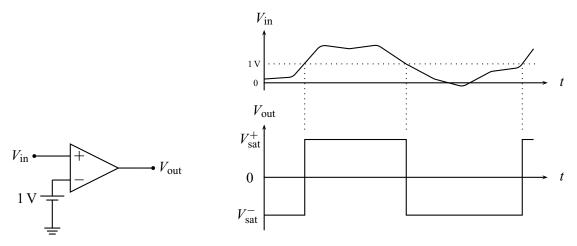

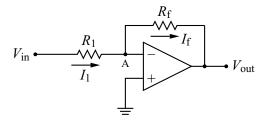

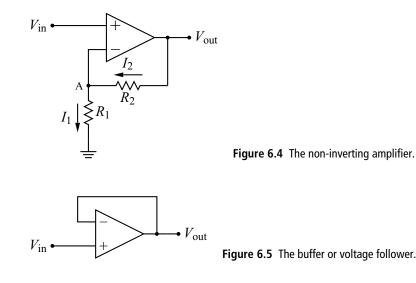

|   | 6.3  | Linear applications                       | 154 |

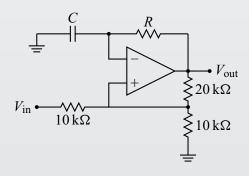

|   | 6.4  | Practical considerations for real op-amps | 159 |

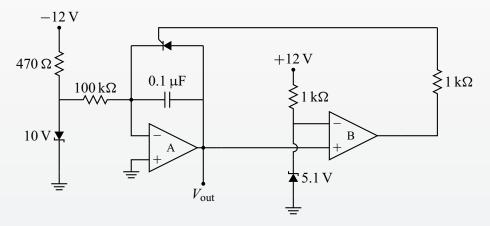

|   | 6.5  | Non-linear applications II                | 165 |

|   |      | Exercises                                 | 168 |

|   |      | Further reading                           | 170 |

| 7 | Osc  | illators                                  | 171 |

|   | 7.1  | Introduction                              | 171 |

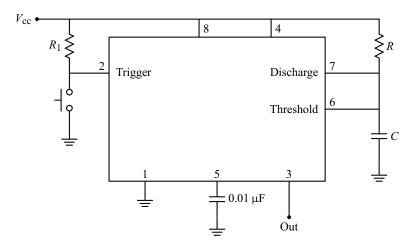

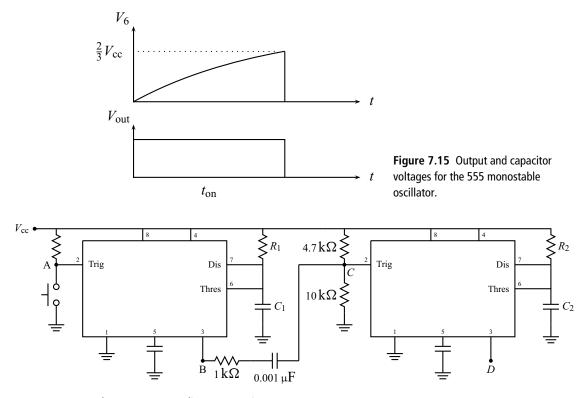

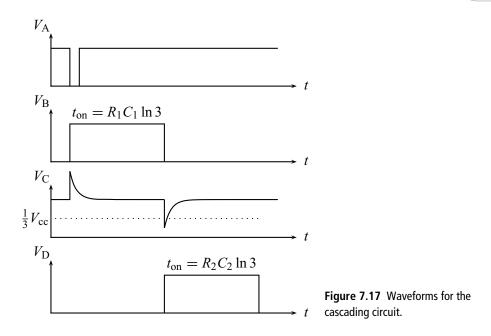

|   | 7.2  | Relaxation oscillators                    | 171 |

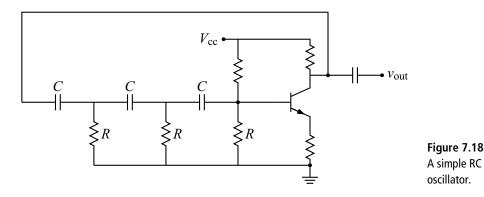

|   | 7.3  | Sinusoidal oscillators                    | 185 |

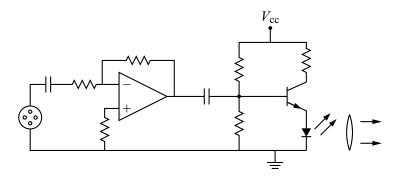

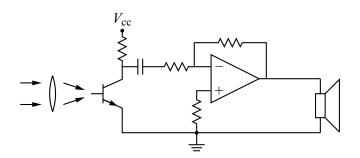

|   | 7.4  | Oscillator application: EM communications | 193 |

|   |      | Exercises                                 | 198 |

|   |      | Further reading                           | 199 |

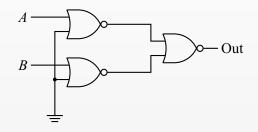

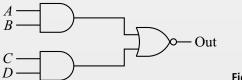

| 8 | Digi | ital circuits and devices                 | 200 |

|   | 8.1  | Introduction                              | 200 |

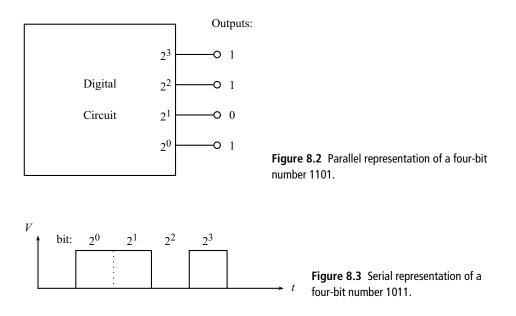

|   | 8.2  | Binary numbers                            | 200 |

|   | 8.3  | Representing binary numbers in a circuit  | 202 |

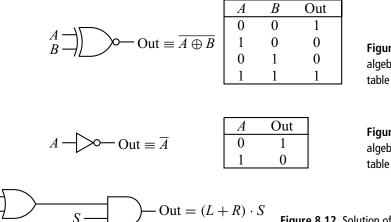

|   | 8.4  | Logic gates                               | 204 |

|   | 8.5  | Implementing logical functions            | 206 |

|   | 8.6  | Boolean algebra                           | 208 |

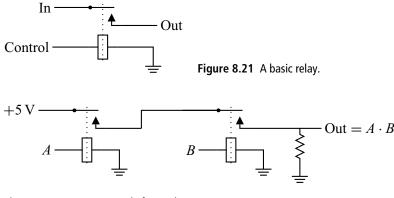

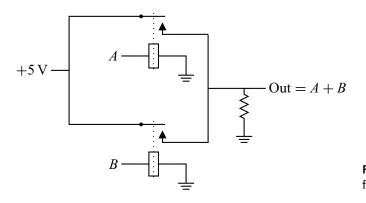

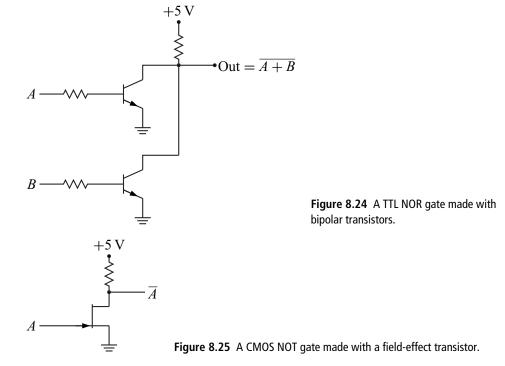

|   | 8.7  | Making logic gates                        | 211 |

viii

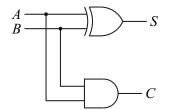

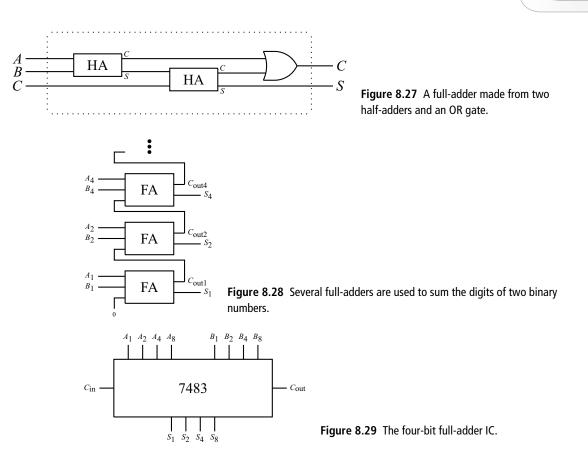

| 8.8 Adders                                              | 213 |

|---------------------------------------------------------|-----|

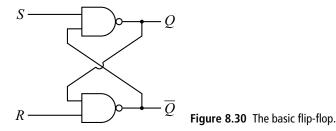

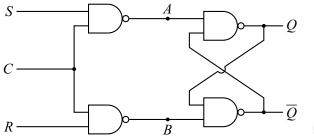

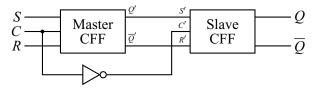

| 8.9 Information registers                               | 216 |

| 8.10 Counters                                           | 220 |

| 8.11 Displays and decoders                              | 223 |

| 8.12 Shift registers                                    | 224 |

| 8.13 Digital to analog converters                       | 227 |

| 8.14 Analog to digital converters                       | 228 |

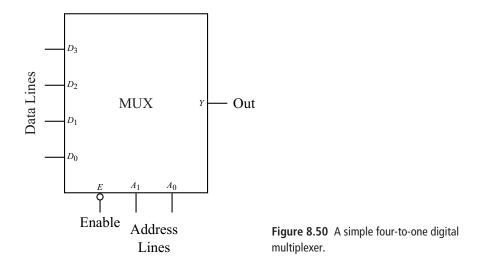

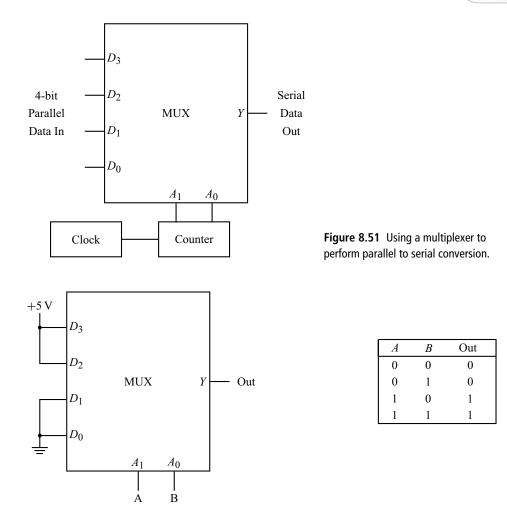

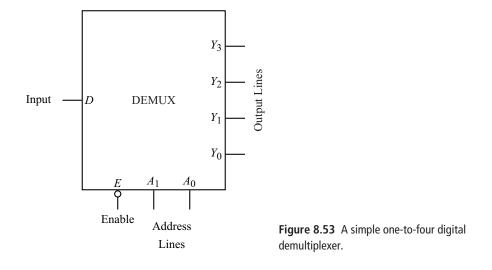

| 8.15 Multiplexers and demultiplexers                    | 229 |

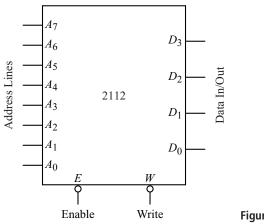

| 8.16 Memory chips                                       | 232 |

| Exercises                                               | 234 |

| Further reading                                         | 235 |

| Appendix A: Selected answers to exercises               | 236 |

| Appendix B: Solving a set of linear algebraic equations | 238 |

| Appendix C: Inductively coupled circuits                | 230 |

| References                                              | 245 |

| Index                                                   | 247 |

| HIQUA                                                   | 27/ |

## Preface

A professor of mine once opined that the best working experimentalists tended to have a good grasp of basic electronics. Experimental data often come in the form of electronic signals, and one needs to understand how to acquire and manipulate such signals properly. Indeed, in graduate school, everyone had a story about a budding scientist who got very excited about some new result, only to later discover that the result was just an artifact of the electronics they were using (or misusing!). In addition, most research labs these days have at least a few homemade circuits, often because the desired electronic function is either not available commercially or is prohibitively expensive. Other anecdotes could be added, but these suffice to illustrate the utility of understanding basic electronics for the working scientist.

On the other hand, the sheer volume of information on electronics makes learning the subject a daunting task. Electronics is a multi-hundred billion dollar a year industry, and new products of ever-increasing specialization are developed regularly. Some introductory electronics texts are longer than introductory physics texts, and the print catalog for one national electronic parts distributor exceeds two thousand pages (with tiny fonts!).

Finally, the undergraduate curriculum for most science and engineering majors (excepting, of course, electrical engineering) does not have much space for the study of electronics. For many science students, formal study of electronics is limited to the coverage of voltage, current, and passive components (resistors, capacitors, and inductors) in introductory physics. A dedicated course in electronics, if it exists, is usually limited to one semester.

This text grew out of my attempts to deal with this three-fold challenge. It is based on my notes for a one-semester course on electronics I have taught for many years in the Physics Department of Occidental College. The students in the course are typically sophomore, junior, or senior students majoring in physics or pre-engineering, with some from the other sciences and mathematics. The students have usually had at least two introductory physics courses and two semesters of calculus.

The primary challenge of such a course is to select the topics to include. My choices for this text have been guided by several principles: I wanted the text to be a rigorous, self-contained, one-semester introduction to basic analog and digital electronics. It should start with basic concepts and at least touch upon the major topics. I also let the choice of material be guided by those topics I thought were fundamental or have found useful during my career as a researcher in experimental plasma physics. Finally,

#### Preface

I wanted the text to emphasize learning how to work with electronics through analysis rather than copying examples.

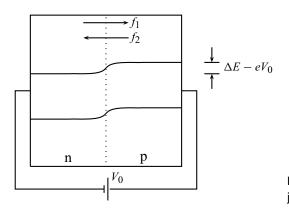

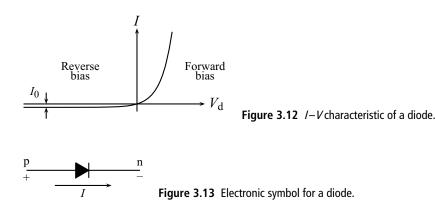

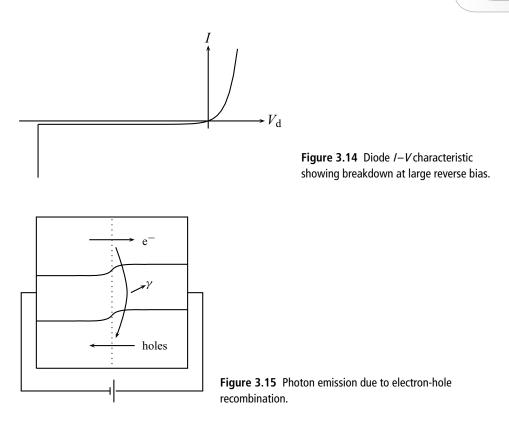

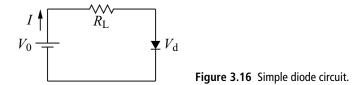

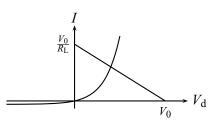

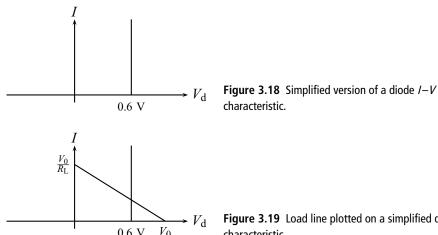

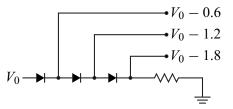

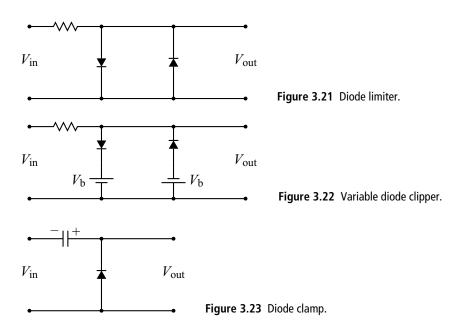

Chapters 1 and 2 start with basic concepts and cover the three passive components. Key concepts such as Thevenin's theorem, time- and frequency-domain analysis, and complex impedances are introduced. Chapter 3 uses the band theory of solids to explain semiconductor diode operation and shows how the diode and its cousins can be used in circuits. The use of the load line to solve the transcendental equations arising from the diode's non-linear I-V characteristic is introduced, as well as common approximation techniques. The fundamentals of power supply construction are also introduced in this chapter.

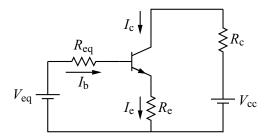

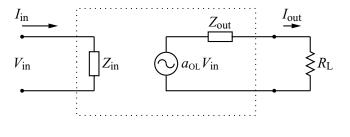

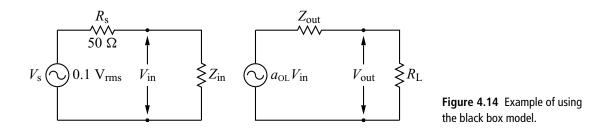

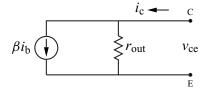

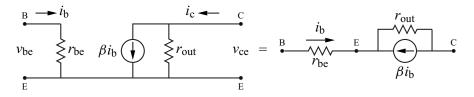

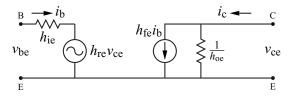

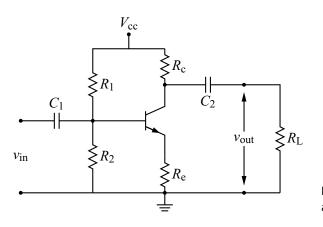

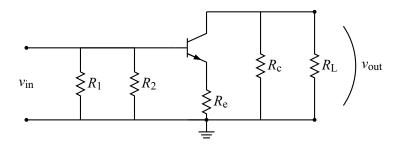

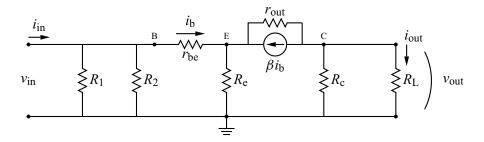

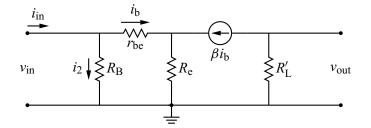

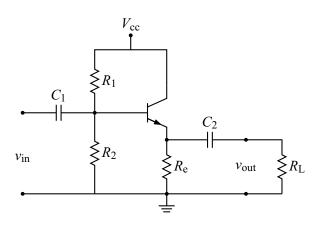

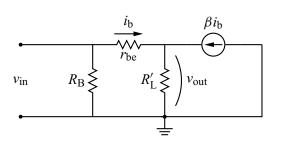

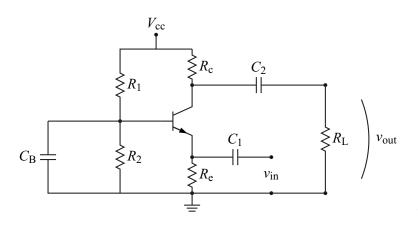

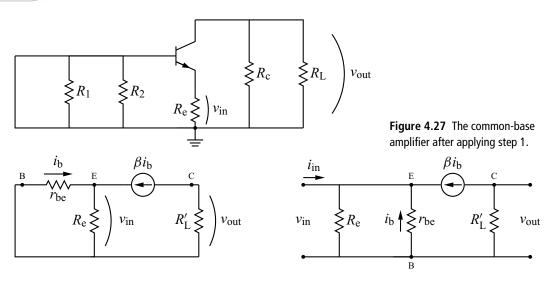

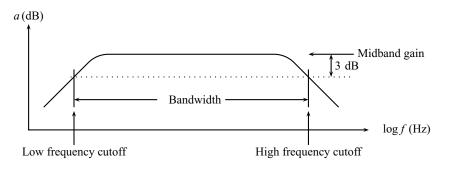

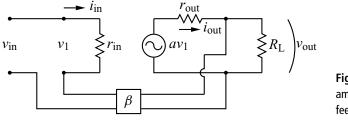

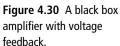

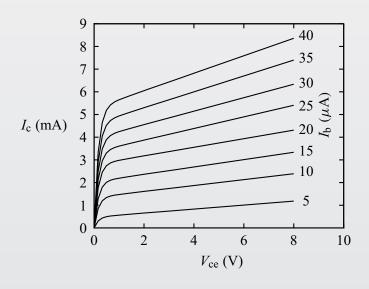

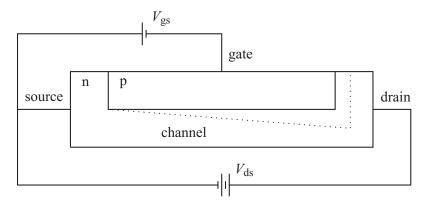

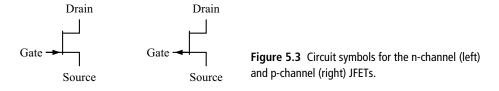

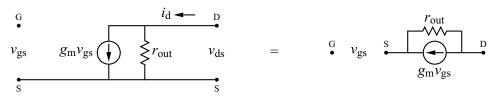

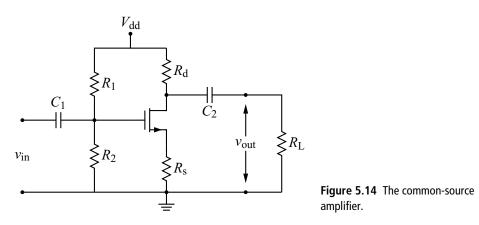

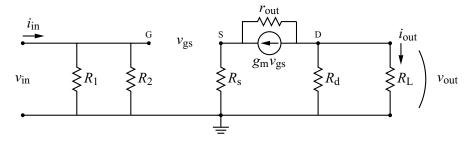

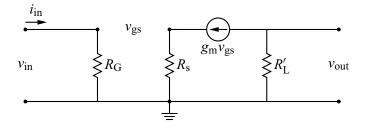

Bipolar junction transistors and field-effect transistors are covered in Chapters 4 and 5. Basic switching and amplifier circuits are analyzed and transistor AC equivalents are used to derive the voltage and current gain as well as the input and output impedance of the amplifiers. A discussion of feedback in Chapter 4 leads into the study of operational amplifiers in Chapter 6. Linear and non-linear circuits are analyzed and the limitations of real op-amps detailed.

Several examples of relaxation and sinusoidal oscillators are studied in Chapter 7, with time-domain analysis used for the former and frequency-domain analysis used for the latter. Amplitude- and frequency-modulation are introduced as oscillator applications. Finally, a number of basic digital circuits and devices are discussed in Chapter 8. These include the logic gates, flip-flops, counters, shift-registers, A/D and D/A converters, multiplexers, and memory chips. Although the digital universe is much larger than this (and expanding!), these seem sufficient to give a laboratory scientist a working knowledge of this universe and lay the foundation for further study.

Exercises are given at the end of each chapter along with texts for further study. I recommend doing all of the exercises. While simple plug-in problems are avoided, I have found that most students will rise to the challenge of applying the techniques studied in the text to non-trivial problems. Answers to some of the problems are given in Appendix A, and a solution manual is available to instructors.

At Occidental this course is accompanied by a laboratory, and I enthusiastically recommend such a structure. In addition to teaching a variety of laboratory skills, an instructional laboratory in electronics allows the student to connect the analytical approach of the text to the real world. A set of laboratory exercises that I have used is available from the publisher.

The original manuscript was typeset using LaTeX and the figures constructed using *PSTricks: Postscript macros for Generic TeX* by Timothy Van Zandt and *M4 Macros for Electric Circuit Diagrams in Latex Documents* by Dwight Aplevich. I am indebted to the makers of these products and would not have attempted this project without them.

Dennis L. Eggleston

Los Angeles, California, USA

#### Preface

xiii

*"Basic Electronics for Scientists and Engineers* by Dennis Eggleston is an example of how the most important material in the introduction to electronics can be presented within a one-semester time frame. The text is written in a nice logical sequence and is beneficial for students majoring in all areas of the Natural Science. In addition, many examples and detailed introduction of all equations allows this course to be taught to students of different background – sophomores, juniors, and seniors. Overall, the effort of the author is thrilling and, definitely, this text will be popular among many instructors and students."

Anatoliy Glushchenko, Department of Physics and Energy Science, University of Colorado at Colorado Springs

"This text is an excellent choice for undergraduates majoring in physics. It covers the basics, running from passive components through diodes, transistors and op-amps to digital electronics. This makes it self-contained and a one-stop reference for the student. A brief treatment of the semiconductor physics of silicon devices provides a good basis for understanding the mathematical models of their behaviour and the end-of-chapter problems help with the learning process. The concise and sequential nature of the book makes it easier to teach (and study) from than the venerable but somewhat overwhelming Art of Electronics by Horowitz and Hill." *David Hanna, W C Macdonald Professor of Physics, McGill University*

"I have been frustrated in the past by my inability to find a suitable book for a onesemester Electronics course that starts with analog and progresses to basic digital circuits. Most available books seem to be out of date or aimed at electrical engineers rather than scientists. Eggleston's book is exactly what I was looking for – a basic course ideal for science students needing a practical introduction to electronics. Written concisely and clearly, the book emphasizes many practical applications, but with sufficient theoretical explanation so that the results don't simply appear out of thin air." *Susan Lehman, Clare Boothe Luce Associate Professor and Chair of Physics, The College of Wooster*

## **Basic concepts and resistor circuits**

#### 1.1 Basics

We start our study of electronics with definitions and the basic laws that apply to *all* circuits. This is followed by an introduction to our first circuit element – the resistor.

In electronics, we are interested in keeping track of two basic quantities: the *currents* and *voltages* in a circuit. If you can make these quantities behave like you want, you have succeeded.

*Current* measures the flow of charge past a point in the circuit. The units of current are thus coulombs per second or *amperes*, abbreviated as A. In this text we will use the symbol *I* or *i* for current.

As charges move in circuits, they undergo collisions with atoms and lose some of their energy. It thus takes some work to move charges around a circuit. The work per unit charge required to move some charge between two points is called the *voltage* between those points. (In physics, this work per unit charge is equivalent to the difference in electrostatic potential between the two points, so the term *potential difference* is sometimes used for voltage.) The units of voltage are thus joules per coulomb or *volts*, abbreviated V. In this text we will use the symbol V or v for voltage.

In a circuit, there are sources and sinks of energy. Some sources of energy (or voltage) include batteries (which convert chemical energy to electrical energy), generators (mechanical to electrical energy), solar cells (radiant to electrical energy), and power supplies and signal generators (electrical to electrical energy). All other electrical components are sinks of energy.

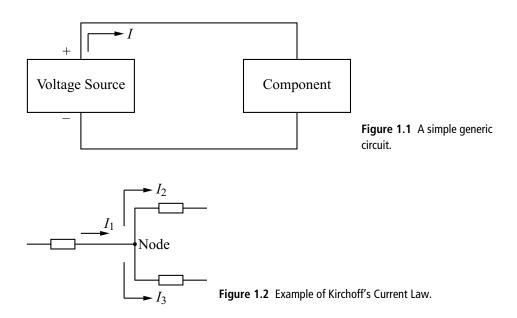

Let's see how this works. The simplest circuit will involve one voltage source and one sink, with connecting wires as shown in Fig. 1.1. By convention, we denote the two sides of the voltage source as + and -. A positive charge moving from the - side to the + side of the source gains energy. Thus we say that the voltage across the source is positive. When the circuit is complete, current flows out of the + side of the source, as shown. The voltage across the component is negative when we

cross it in the direction of the current. We say there is a *voltage drop* across the component. Note that while we can speak of the current at any point in the circuit, the voltage is always between two points. It makes no sense to speak of the voltage at a point (remember, the voltage is a potential *difference*).

We can now write down some general rules about voltage and current.

1. The sum of the currents into a node (i.e. any point on the circuit) equals the sum of the currents flowing out of the node. This is Kirchoff's Current Law (KCL) and expresses conservation of charge. For example, in Fig. 1.2,  $I_1 = I_2 + I_3$ . If we use the sign convention that currents into a node are positive and currents out of a node are negative, then we can express this law in the compact form

$$\sum_{k}^{\text{node}} I_k = 0 \tag{1.1}$$

where the sum is over all currents into or out of the node.

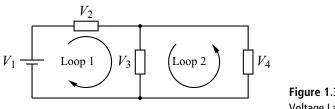

**2.** The sum of the voltages around any closed circuit is zero. This is Kirchoff's Voltage Law (KVL) and expresses conservation of energy. In equation form,

$$\sum_{k}^{\text{loop}} V_k = 0. \tag{1.2}$$

Here we must use the convention that the voltage across a source is positive when we move across the source in the direction of the current and the voltage

across a sink is negative when we move across the component in the direction of the current. If we traverse a source or sink in the direction opposite to the direction of the current, the signs are reversed. Figure 1.3 gives an example. Here we introduce the circuit symbol for an ideal battery, labeled with voltage  $V_1$ . The top of this symbol represents the positive side of the battery. The current (not shown) flows up out of the battery, through the component labeled  $V_2$  and down through the components labeled  $V_3$  and  $V_4$ . Looping around the left side of the circuit in the direction shown gives  $V_1 - V_2 - V_3 = 0$  or  $V_1 = V_2 + V_3$ . Here we take  $V_2$  and  $V_3$  to be positive numbers and include the sign explicitly. Going around the right portion of the circuit as shown gives  $-V_3 + V_4 = 0$ or  $V_3 = V_4$ . This last equality expresses the important result that components connected in parallel have the same voltage across them.

3. The power P provided or consumed by a circuit device is given by

$$P = VI \tag{1.3}$$

where V is the voltage across the device and I is the current through the device. This follows from the definitions:

$$VI = \left(\frac{\text{work}}{\text{charge}}\right) \left(\frac{\text{charge}}{\text{time}}\right) = \frac{\text{work}}{\text{time}} = \text{power.}$$

(1.4)

The units of power are thus joules per second or *watts*, abbreviated W. This law is of considerable practical importance since a key part of designing a circuit is to employ components with the proper power rating. A component with an insufficient power rating will quickly overheat and fail when the circuit is operated.

Finally, a word about prefixes and nomenclature. Some common prefixes and their meanings are shown in Table 1.1. As an example, recall that the unit *volts* is abbreviated as V, and *amperes* or *amps* is abbreviated as A. Thus  $10^6$  volts = 1 MV and  $10^{-3}$  amps = 1 mA. Notice that case matters: 1 MA  $\neq$  1 mA.

#### Basic concepts and resistor circuits

Table 1.1

Some common prefixes used in electronics

| Multiple         | Prefix | Symbol |

|------------------|--------|--------|

| 10 <sup>12</sup> | tera   | Т      |

| 10 <sup>9</sup>  | giga   | G      |

| 10 <sup>6</sup>  | mega   | М      |

| 10 <sup>3</sup>  | kilo   | k      |

| $10^{-3}$        | milli  | m      |

| $10^{-6}$        | micro  | μ      |

| $10^{-9}$        | nano   | n      |

| $10^{-12}$       | pico   | р      |

| $10^{-15}$       | femto  | f      |

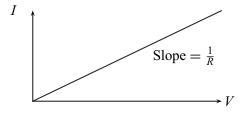

**Figure 1.4** I - V curve for a resistor.

#### **1.2 Resistors**

A common way to represent the behavior of a circuit device is the I-V characteristic. This is a plot of the current I through the device as a function of applied voltage V across the device. Our first device, the resistor, has the simple linear I-V characteristic shown in Fig. 1.4. This linear relationship is expressed by Ohm's Law:

$$V = IR. \tag{1.5}$$

The constant of proportionality, R, is called the *resistance* of the device and is equal to one over the slope of the I-V characteristic. The units of resistance are *ohms*, abbreviated as  $\Omega$ . Any device with a linear I-V characteristic is called a resistor.

The resistance of the device depends only on its physical properties – its size and composition. More specifically:

$$R = \rho \frac{L}{A} \tag{1.6}$$

| Table | 1.2    | The   | resistivity | of | some |

|-------|--------|-------|-------------|----|------|

| commo | on ele | ectro | nic materia | ls |      |

| Material | ρ (10 <sup>-8</sup> Ωm) |

|----------|-------------------------|

| Silver   | 1.6                     |

| Copper   | 1.7                     |

| Nichrome | 100                     |

| Carbon   | 3500                    |

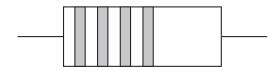

**Figure 1.5** Value and tolerance bands on a resistor.

where  $\rho$  is the resistivity, *L* is the length, and *A* is the cross-sectional area of the material. The resistivity of some representative materials is given in Table 1.2.

The interconnecting wires or circuit board paths are typically made of copper or some other low resistivity material, so for most cases their resistance can be ignored. If we want resistance in a circuit we will use a discrete device made of some high resistivity material (e.g., carbon). Such resistors are widely used and can be obtained in a variety of values and power ratings. The low power rating resistors typically used in circuits are marked with color coded bands that give the resistance and the tolerance (i.e., the uncertainty in the resistance value) as shown schematically in Fig. 1.5.

As shown in the figure, the bands are usually grouped toward one end of the resistor. The band closest to the end is read as the first digit of the value. The next band is the second digit, the next band is the multiplier, and the last band is the tolerance value. The values associated with the various colors are shown in Table 1.3. For example, a resistor code having colors red, violet, orange, and gold corresponds to a value of  $27 \times 10^3 \Omega \pm 5\%$ .

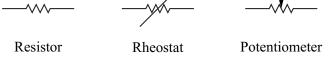

Resistors also come in variable forms. If the variable device has two leads, it is called a *rheostat*. The more common and versatile type with three leads is called a *potentiometer* or a "pot." Schematic symbols for resistors are shown in Fig. 1.6.

One must also select the proper power rating for a resistor. The power rating of common carbon resistors is indicated by the size of the device. Typical values are  $\frac{1}{8}$ ,  $\frac{1}{4}$ ,  $\frac{1}{2}$ , 1, and 2 watts.

| Color       | Digit | Multiplier      | Tolerance (%) |

|-------------|-------|-----------------|---------------|

| none        | -     | •               | 20            |

| silver      |       | 0.01            | 10            |

| gold        |       | 0.1             | 5             |

| black       | 0     | 1               |               |

| brown       | 1     | 10              |               |

| red         | 2     | 100             | 2             |

| orange      | 3     | 10 <sup>3</sup> |               |

| yellow      | 4     | 10 <sup>4</sup> |               |

| green       | 5     | 10 <sup>5</sup> |               |

| blue        | 6     | $10^{6}$        |               |

| violet      | 7     | 10 <sup>7</sup> |               |

| gray        | 8     |                 |               |

| white       | 9     |                 |               |

|             |       |                 |               |

|             |       |                 |               |

| —— <u> </u> |       |                 |               |

|             |       |                 |               |

|             |       |                 |               |

Table 1.3 Standard color scheme for resistors

Figure 1.6 Schematic symbols for a fixed resistor and two types of variable resistors.

As noted in Eq. (1.3), the power consumed by a device is given by P = VI, but for resistors we also have the relation V = IR. Combining these we obtain two power relations specific to resistors:

$$P = I^2 R \tag{1.7}$$

and

$$P = V^2/R. (1.8)$$

### 1.2.1 Equivalent circuit laws for resistors

It is common practice in electronics to replace a portion of a circuit with its functional equivalent. This often simplifies the circuit analysis for the remaining portion of the circuit. The following are some equivalent circuit laws for resistors.

#### 1.2.1.1 Resistors in series

Components connected in series are connected in a head-to-tail fashion, thus forming a line or series of components. When forming equivalent circuits, any

Figure 1.7 Equivalent circuit for resistors in series.

number of resistors in series may be replaced by a single equivalent resistor given by:

$$R_{\rm eq} = \sum_{i} R_i \tag{1.9}$$

where the sum is over all the resistors in series. To see this, consider the circuit shown in Fig. 1.7. We would like to replace the circuit on the left by the equivalent circuit on the right. The circuit on the right will be equivalent if the current supplied by the battery is the same.

By KCL, the current in each resistor is the same. Applying KVL around the circuit loop and Ohm's Law for the drop across the resistors, we obtain

$$V = IR_1 + IR_2 + IR_3$$

=  $I(R_1 + R_2 + R_3)$

=  $IR_{eq}$  (1.10)

where

$$R_{\rm eq} = R_1 + R_2 + R_3. \tag{1.11}$$

This derivation can be extended to any number of resistors in series, hence Eq. (1.9).

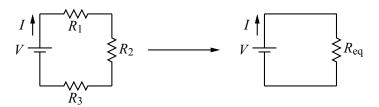

#### 1.2.1.2 Resistors in parallel

Components connected in parallel are connected in a head-to-head and tail-to-tail fashion. The components are often drawn in parallel lines, hence the name. When forming equivalent circuits, any number of resistors in parallel may be replaced by a single equivalent resistor given by:

$$\frac{1}{R_{\rm eq}} = \sum_{i} \frac{1}{R_i} \tag{1.12}$$

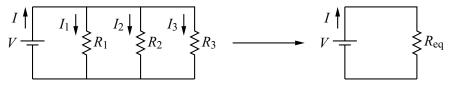

where the sum is over all the resistors in parallel. To see this, consider the circuit shown in Fig. 1.8. Again, we would like to replace the circuit on the left by the equivalent circuit on the right.

Figure 1.8 Equivalent circuit for resistors in parallel.

First, note that KCL requires

$$I = I_1 + I_2 + I_3. \tag{1.13}$$

Since the resistors are connected in parallel, the voltage across each one is the same, and, by KVL is equal to the battery voltage:  $V = I_1R_1$ ,  $V = I_2R_2$ ,  $V = I_3R_3$ . Solving these for the three currents and substituting in Eq. (1.13) gives

$$I = \frac{V}{R_1} + \frac{V}{R_2} + \frac{V}{R_3} = V\left(\frac{1}{R_1} + \frac{1}{R_2} + \frac{1}{R_3}\right) = \frac{V}{R_{eq}}$$

(1.14)

where

$$\frac{1}{R_{\rm eq}} = \frac{1}{R_1} + \frac{1}{R_2} + \frac{1}{R_3}.$$

(1.15)

Again, this derivation can be extended to any number of resistors in parallel, hence Eq. (1.12).

A frequent task is to analyze two resistors in parallel. Of course, for this special case of Eq. (1.12) we get  $\frac{1}{R_{eq}} = \frac{1}{R_1} + \frac{1}{R_2}$ . It is often more illuminating to write this as an equation for  $R_{eq}$  rather than  $\frac{1}{R_{eq}}$ . After some algebra, we get

$$R_{\rm eq} = \frac{R_1 R_2}{R_1 + R_2}.$$

(1.16)

This special case is worth memorizing.

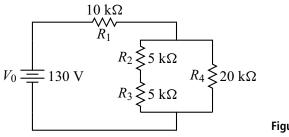

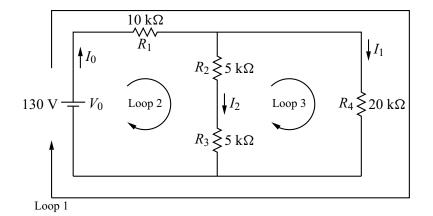

**Example** For the circuit shown in Fig. 1.9, how much current flows through the 20 k $\Omega$  resistor? What must its power rating be?

**Solution** As we will see, there is more than one way to solve this problem. Here we use a method that relies on basic electronics reasoning and our resistor equivalent circuit laws. We want the current through the 20 k $\Omega$  resistor. If we knew the voltage across this resistor (call this voltage  $V_{20k}$ ), we could then get the current from Ohm's Law. In order to get the voltage across the 20 k $\Omega$  resistor, we need the voltage across the 10 k $\Omega$  resistor since, by KVL,  $V_{20k} = 130 - V_{10k}$ . In order to get the voltage across the 10 k $\Omega$  resistor, we need to know the current through

#### 1.2 Resistors

it, which is the same as the current supplied by the battery. Thus, if we can get the current supplied by the battery we can solve the problem. To get the battery current, we combine all our resistors into one equivalent resistor. The implementation of this strategy goes as follows.

- 1. Combine the two 5 k $\Omega$  series resistors into a 10 k $\Omega$  resistor.

- **2.** This 10 kΩ resistor is then in parallel with the 20 kΩ resistor. Combining these we get (using Eq. (1.16))

$$R_{\rm eq} = \frac{R_1 R_2}{R_1 + R_2} = \frac{(10 \,\mathrm{k}\Omega)(20 \,\mathrm{k}\Omega)}{10 \,\mathrm{k}\Omega + 20 \,\mathrm{k}\Omega} = 6.67 \,\mathrm{k}\Omega. \tag{1.17}$$

- **3.** This 6.67 k $\Omega$  resistor is then in series with a 10 k $\Omega$  resistor, giving a total equivalent circuit resistance  $R_{eq} = 16.67 \text{ k}\Omega$ .

- 4. The current supplied by the battery is then

$$I = \frac{V_0}{R_{\rm eq}} = \frac{130 \,\mathrm{V}}{16.67 \times 10^3 \,\Omega} = 7.8 \times 10^{-3} \,\mathrm{A} = 7.8 \,\mathrm{mA}. \tag{1.18}$$

- 5. KVL then gives 130 V (7.8 mA)(10 k $\Omega$ ) V<sub>20k</sub> = 0. Solving this gives  $V_{20k} = 52$  V.

- 6. Ohm's Law then gives  $I_{20k} = \frac{52 \text{ V}}{20 \text{ k}\Omega} = 2.6 \text{ mA}$ , which is the solution to the first part of our problem. As a check, it is comforting to note that this current is less than the total battery current, as it must be. The remainder goes through the two 5 k $\Omega$  resistors.

- 7. The power consumed by the 20 k $\Omega$  resistor is  $P = I^2 R = (2.6 \times 10^{-3} \text{ A})^2 (2 \times 10^4 \Omega) = 0.135 \text{ W}$ . This is too much for a  $\frac{1}{8}$  W resistor, so we must use at least a  $\frac{1}{4}$  W resistor.

Figure 1.10 Representation of Thevenin's theorem.

#### 1.2.1.3 Thevenin's theorem and Norton's theorem

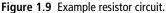

The third of our equivalent circuit laws, Thevenin's theorem, is a more general result that actually includes the first two laws as special cases. The theorem states that any two-terminal network of sources and resistors can be replaced by a series combination of a single resistor  $R_{\text{th}}$  and voltage source  $V_{\text{th}}$ . This is represented by the example in Fig. 1.10. The sources can include both voltage and current sources (the current source is described below). A more general version of the theorem replaces the word *resistor* with *impedance*, a concept we will develop in Chapter 2.

The point of Thevenin's theorem is that when we connect a component to the terminals, it is much easier to analyze the circuit on the right than the circuit on the left. But there is no free lunch – we must first determine the values of  $V_{\text{th}}$  and  $R_{\text{th}}$ .

$V_{\text{th}}$  is the voltage across the circuit terminals when nothing is connected to the terminals. This is clear from the equivalent circuit: if nothing is connected to the terminals, then no current flows in the circuit and there is no voltage drop across  $R_{\text{th}}$ . The voltage across the terminals is thus the same as  $V_{\text{th}}$ . In practice, the voltage across the terminals must be calculated by analyzing the original circuit.

There are two methods for calculating  $R_{\text{th}}$ ; you can use whichever is easiest. In the first method, you start by short circuiting all the voltage sources and open circuiting all the current sources in the original circuit. This means that you replace the voltage sources by a wire and disconnect the current sources. Now only resistors are left in the circuit. These are then combined into one resistor using the resistor equivalent circuit laws. This one resistor then gives the value of  $R_{\text{th}}$ . In the second method, we calculate the current that would flow in the circuit if we shorted (placed a wire across) the terminals. Call this the short circuit current  $I_{\text{sc}}$ . Then from the Thevenin equivalent circuit it is clear that  $R_{\text{th}} = \frac{V_{\text{th}}}{I_{\text{sc}}}$ .

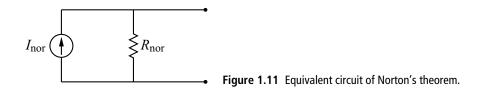

There is also a similar result known as Norton's theorem. This theorem states that any two-terminal network of sources and resistors can be replaced by a parallel

combination of a single resistor  $R_{nor}$  and current source  $I_{nor}$ . This equivalent circuit is shown in Fig. 1.11.

The current source is usually less familiar that the voltage source, but the two can be viewed as complements of one another. An ideal voltage source will maintain a constant voltage across it and will provide whatever current is required by the rest of the circuit. Similarly, an ideal current source will maintain a constant current through it while the voltage across it will be set by the rest of the circuit.

Returning now to the equivalent circuit, let's determine  $R_{nor}$  and  $I_{nor}$ . If we short the terminals, it is clear from the Norton equivalent circuit that all of  $I_{nor}$  will pass through the shorting wire. Thus  $I_{nor} = I_{sc}$ . We have seen previously that the voltage across the terminals when nothing is connected is equal to  $V_{th}$ . From the Norton equivalent circuit we then see that  $V_{th} = I_{nor}R_{nor}$ , so

$$R_{\rm nor} = \frac{V_{\rm th}}{I_{\rm nor}} = \frac{V_{\rm th}}{I_{\rm sc}} = R_{\rm th}.$$

(1.19)

## 1.2.2 Applications for resistors

Resistors are probably the most common circuit element and can be used in a variety of simple circuits. Here are a few examples.

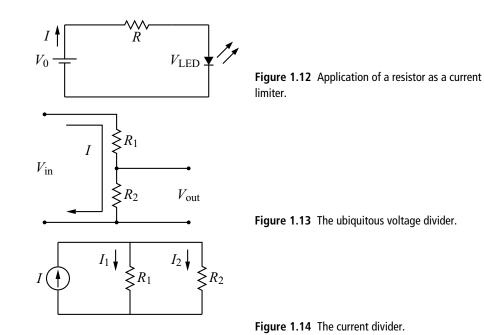

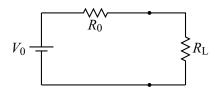

1. Current limiting. Many electronic devices come with operating specifications. For example, the ubiquitous LED (light emitting diode) typically operates with a voltage drop of 1.7 V and a current of 20 mA. Suppose you have a 9 V battery and wish to light the LED. How can you operate the 1.7 V LED with a 9 V battery? By the discriminating use of a resistor! Consider the circuit in Fig. 1.12. KVL gives  $V_0 - IR - V_{\text{LED}} = 0$ , where  $V_{\text{LED}}$  is the voltage across the LED. We know that  $V_0 = 9$  V,  $V_{\text{LED}} = 1.7$  V, and we want I = 20 mA for proper operation. Solving for *R* gives

$$R = \frac{V_0 - V_{\text{LED}}}{I} = \frac{9 - 1.7 \text{ V}}{20 \times 10^{-3} \text{ A}} = 365 \ \Omega.$$

(1.20)

This is an example of using a resistor as a current limiter. Without it, the LED would burn out immediately.

2. Voltage divider. Another very common resistor circuit is shown in Fig. 1.13. Some voltage  $V_{in}$  is applied to the input and the circuit provides a lower voltage at the output. The analysis is simple. KVL gives  $V_{in} = I(R_1 + R_2)$  and Ohm's Law gives  $V_{out} = IR_2$ . Solving for I from the first equation and substituting in the second gives

$$V_{\text{out}} = IR_2 = \left(\frac{V_{\text{in}}}{R_1 + R_2}\right)R_2 = V_{\text{in}}\left(\frac{R_2}{R_1 + R_2}\right)$$

(1.21)

where this last form emphasizes that  $V_{\text{out}} < V_{\text{in}}$  since  $\frac{R_2}{R_1+R_2} < 1$ . This equation is used so frequently it is worth memorizing.

3. The current divider circuit is shown in Fig. 1.14. A current source is applied to two resistors in parallel and we would like to obtain an expression that tells us how the current is divided between the two. By KCL,  $I = I_1 + I_2$ . Since the two resistors are in parallel, the voltage across them must be the same. Hence,  $I_1R_1 = I_2R_2$ . Solving this latter equation for  $I_2$  and plugging into the first gives

$$I = I_1 + I_1\left(\frac{R_1}{R_2}\right) = I_1\left(\frac{R_1 + R_2}{R_2}\right)$$

(1.22)

or

$$I_1 = \left(\frac{R_2}{R_1 + R_2}\right)I.$$

(1.23)

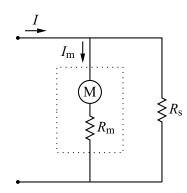

**Figure 1.15** Using a resistor to extend the range of a current meter.

4. Multi-range analog voltmeter/ammeter. In electronics, one frequently has the need to measure voltage and current. The instrument of choice for many experimentalists is the multimeter, which can measure voltage, current, and resistance. The analog version of the multimeter uses a simple meter as a display. If you tear one of these multimeters apart, you find that the meter is a current measuring device that gives a full scale deflection of the needle for a given, small current, typically 50  $\mu$ A. This is fine if you want to measure currents from zero to 50  $\mu$ A, but what if you have a larger current to measure, or want to measure a voltage instead?

Both of these can be accomplished by judicious use of resistors. The circuit in Fig. 1.15 shows a meter in parallel with a so-called shunt resistor  $R_s$ . The physical meter (within the dotted lines) is represented by an ideal current measuring meter in series with a resistor  $R_m$ . When a current *I* is applied to the terminals, part goes through the meter and part through the shunt. The circuit is simply a current divider, so we have (cf. Eq. (1.22))

$$I = I_{\rm m} \left( 1 + \frac{R_{\rm m}}{R_{\rm s}} \right). \tag{1.24}$$

A full scale deflection of the meter will always occur when  $I_{\rm m} = 50 \,\mu\text{A}$ , and  $R_{\rm m}$  is also set at the construction of the meter, but by adjusting the shunt resistance  $R_{\rm s}$  we can make this full scale deflection occur for any input current *I* we choose.

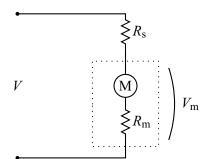

Another simple addition will allow us to use our meter to measure voltage. Placing a resistor  $R_s$  in series with the meter gives the configuration in Fig. 1.16. It is convenient here to define the voltage  $V_m = I_m R_m$  that will produce a full scale deflection when applied across the physical meter. This circuit is then seen to be a voltage divider. Inverting Eq. (1.21) then gives

**Figure 1.16** Using a resistor to measure voltage with a current meter.

Figure 1.17 The standard method of solving circuit problems.

$$V = V_{\rm m} \left( 1 + \frac{R_{\rm s}}{R_{\rm m}} \right) \tag{1.25}$$

so by varying  $R_s$  we can make the full scale deflection of the meter correspond to any input voltage.

### 1.2.3 Techniques for solving circuit problems

We list here three methods for solving circuit problems, and illustrate the use of these techniques on the same problem that we solved previously using equivalent circuit laws for resistors. Our goal is to solve for the current through resistor  $R_4$  in Fig. 1.17.

**The standard method** This method involves assigning currents to each branch of the circuit and then applying KVL and KCL. In Fig. 1.17 we have assigned currents  $I_0$ ,  $I_1$ , and  $I_2$ . In this case, the application of KCL gives a single equation

$$I_0 = I_1 + I_2 \tag{1.26}$$

but in circuits with more than three branches KCL gives additional relations. Next we use KVL around the loops indicated in the figure. For Loop 1 we get

$$V_0 - I_0 R_1 - I_1 R_4 = 0 (1.27)$$

while Loop 2 gives

$$V_0 - I_0 R_1 - I_2 (R_2 + R_3) = 0 (1.28)$$

and finally

$$-I_1R_4 + I_2(R_2 + R_3) = 0 (1.29)$$

for Loop 3. We thus have four equations relating the three unknown currents  $I_0$ ,  $I_1$ , and  $I_2$  and need to solve for  $I_1$ . In practice we need only three independent equations to solve for the currents, but we have given all four here to illustrate the method. Solving Eq. (1.26) for  $I_2$  (one of the currents we are not interested in) and plugging into Eq. (1.29) gives

$$-I_1R_4 + (I_0 - I_1)(R_2 + R_3) = 0 (1.30)$$

and solving Eq. (1.27) for  $I_0$  gives

$$I_0 = \frac{V_0 - I_1 R_4}{R_1}.$$

(1.31)

Plugging Eq. (1.31) into Eq. (1.30) and solving for  $I_1$  gives, after some algebra,

$$I_1 = \frac{V_0(R_2 + R_3)}{R_1 R_4 + (R_1 + R_4)(R_2 + R_3)}.$$

(1.32)

Plugging the circuit values into this equation gives  $I_1 = 2.6$  mA, our former answer.

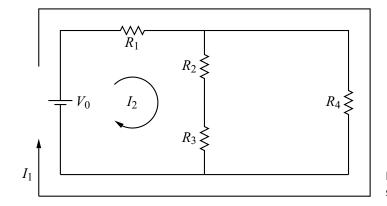

The mesh loop method Our second method for solving circuit problems is the mesh loop method. In this method, currents are assigned to the circuit loops rather than the actual physical branches of the circuit. This is shown in Fig. 1.18 where we assign current  $I_1$  to the outer loop and  $I_2$  to the inner loop.

We then move around these loops, applying KVL, but including contributions from both loop currents. The outer loop then gives

$$V_0 - (I_1 + I_2)R_1 - I_1R_4 = 0 (1.33)$$

while the inner loop gives

$$V_0 - (I_1 + I_2)R_1 - I_2(R_2 + R_3) = 0.$$

(1.34)

Basic concepts and resistor circuits

**Figure 1.18** The mesh loop method of solving circuit problems.

Note that the resulting set of equations is simpler in this method: two equations in two unknowns  $I_1$  and  $I_2$ . For this reason the mesh loop method is usually preferable for more complicated circuits. Furthermore, our equations can be rearranged into the conventional form of a system of linear algebraic equations. Thus Eq. (1.33) becomes

$$(R_1 + R_4)I_1 + R_1I_2 = V_0 \tag{1.35}$$

while Eq. (1.34) gives

$$R_1I_1 + (R_1 + R_2 + R_3)I_2 = V_0. (1.36)$$

Students of linear algebra may wish to solve these using Cramer's Method of Determinants or with the built-in capabilities of many hand-held calculators (see Appendix B). The usual brute force method also works: solving Eq. (1.36) for  $I_2$ , plugging this into Eq. (1.35), and solving for  $I_1$  produces (again, after some algebra),

$$I_1 = \frac{V_0(R_2 + R_3)}{(R_1 + R_4)(R_2 + R_3) + R_1R_4},$$

(1.37)

the same expression obtained with the standard method.

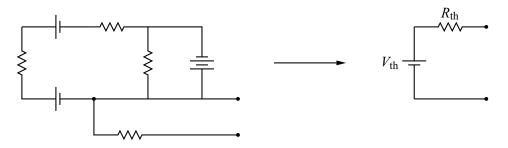

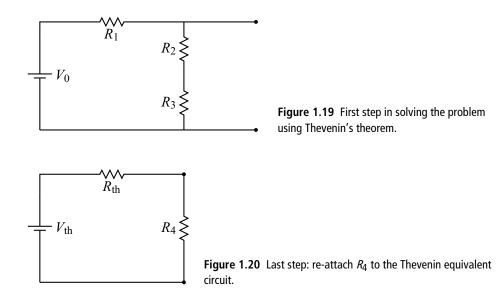

**Thevenin's theorem** Finally, we solve this problem by using Thevenin's theorem. We form the required two terminal network by removing  $R_4$  and taking the two terminals at the points where  $R_4$  was attached. This is shown in Fig. 1.19.

The remaining circuit should look familiar – if we combine  $R_2$  and  $R_3$  it is the previously considered voltage divider. Thus

$$V_{\rm th} = V_0 \left( \frac{R_2 + R_3}{R_1 + R_2 + R_3} \right) = 65 \,\mathrm{V}.$$

(1.38)

Shorting out the battery leaves  $R_1$  in parallel with  $R_2 + R_3$  so

$$R_{\rm th} = \frac{R_1(R_2 + R_3)}{R_1 + R_2 + R_3} = 5 \,\mathrm{k}\Omega. \tag{1.39}$$

Reattaching  $R_4$  then gives the simple circuit of Fig. 1.20 with the current through  $R_4$  given by

$$I_1 = \frac{V_{\rm th}}{R_{\rm th} + R_4} = \frac{65 \,\mathrm{V}}{25 \,\mathrm{k}\Omega} = 2.6 \,\mathrm{mA} \tag{1.40}$$

as before.

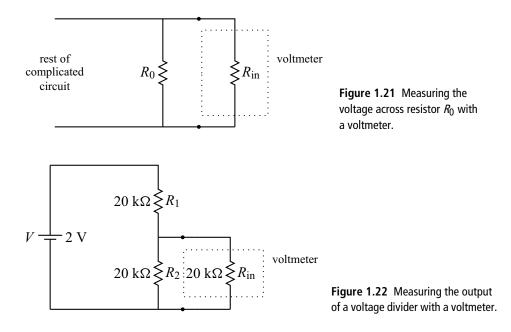

### 1.2.4 Input resistance

A common measurement in the electronics lab is the voltage across a component. An important fact to keep in mind when making such measurements is that *the measuring instrument becomes part of the circuit*. The act of measuring thus inevitably changes the thing we are trying to measure because we are adding circuitry to the original circuit. To help us cope with this problem, test instrument manufacturers specify a quantity called the *input resistance*  $R_{in}$  (or, as we will see later, the *input impedance*). The effect of attaching the instrument is the same as attaching a resistor with value  $R_{in}$ . To see how this helps, suppose we are measuring the voltage across some resistor  $R_0$  in a complicated circuit, as depicted in Fig. 1.21.

If we know the input resistance of our measuring device we see that the effect of making the measurement is to replace the original resistor  $R_0$  with the parallel combination of  $R_0$  with  $R_{in}$

$$R_0 \to R_0 \parallel R_{\rm in} = \frac{R_0 R_{\rm in}}{R_0 + R_{\rm in}}$$

(1.41)

where  $R_0 \parallel R_{in}$  is shorthand for the parallel combination. From this, one can see that the circuit-altering effect of attaching the measuring instrument is mitigated by making the input resistance as high as possible, because

$$\frac{R_0 R_{\rm in}}{R_0 + R_{\rm in}} \to R_0 \tag{1.42}$$

as  $R_{in} \rightarrow \infty$ .

As an example of what happens when  $R_{in}$  is not large, consider the circuit in Fig. 1.22. Ignoring the meter for a moment we see that the original circuit is a voltage divider, and application of Eq. (1.21) gives  $V_{out} = 1$  V. But the effect of the meter's input resistance is to change  $R_2$  to  $R_2 \parallel R_{in} = 10$  k $\Omega$ . Using this in Eq. (1.21) gives  $V_{out} = \frac{2}{3}$  V, and this is what the meter will indicate. So, unless we are aware of the effect of input resistance, we run the danger of making a false measurement. On the other hand, if we are aware of this effect, we can analyze the effect and determine the true value of our voltage when the meter is unattached.

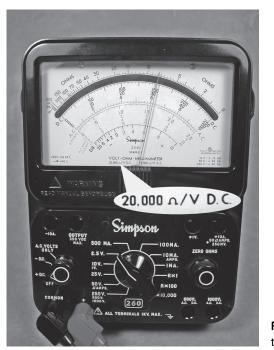

**Figure 1.23** Impedance specification for a typical analog meter.

How does one determine the value of the input resistance for a given instrument? Here are some common ways.

- **1.** Look in the instrument manual under *input resistance* or *input impedance*. The value should be in ohms.

- 2. For analog voltmeters, look for a specification with units of ohms per volt  $(\Omega/V)$ . This is usually printed on the face of the meter itself, as shown in Fig. 1.23. To get  $R_{\rm in}$ , multiply this number by the full scale voltage selected. For example, suppose your meter is specified as 20000  $\Omega/V$  and you have selected the 2.5 V full scale setting. The input resistance is then  $20000 \times 2.5 = 50 \text{ k}\Omega$ .

- **3.** You may have to analyze the instrument circuitry itself. The relevant question is: when a voltage is applied to the input of the instrument, how much current flows into the instrument? Then, by Ohm's Law, the input resistance is just the ratio of this voltage and current.

### 1.3 AC signals

So far our examples have used constant voltage sources such as batteries. Constant voltages and currents are described as DC quantities in electronics. On the other

Figure 1.24 A sine wave.

hand, voltages and currents that vary in time are called AC quantities. For future reference, we list here some of the most common AC signals.

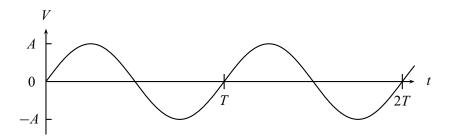

Sinusoidal signals. This is probably the most fundamental signal in electronics since, as we will see later, any signal can be constructed from sinusoidal signals. A typical sinusoidal voltage is shown in Fig. 1.24.

Sinusoidal voltages can be written

$$V = A\sin(2\pi ft + \phi) = A\sin(\omega t + \phi) \tag{1.43}$$

where *A* is the amplitude, *f* is the frequency in cycles/second or hertz (abbreviated Hz),  $\phi$  is the phase, and  $\omega$  is the angular frequency (in radians/second). The repetition time  $t_{rep}$  is also called the period *T* of the signal, and this is related to the frequency of the signal by  $T = \frac{1}{f}$ .

There are several ways to specify the amplitude of a sinusoidal signal that are in common use. These include the following.

- (a) The peak amplitude A or  $A_p$ .

- (b) The peak-to-peak amplitude  $A_{pp} = 2A$ .

- (c) The rms amplitude  $A_{\rm rms} = A/\sqrt{2}$ . This is useful for power calculations involving sinusoidal waves. For example, suppose we want the power dissipated in a resistor given the sinusoidally varying voltage across it. We cannot simply use Eq. (1.8) since our voltage is varying in time (what V would we use?). Instead, we calculate the time average of the power over one period:

$$P = \frac{1}{T} \int_0^T \frac{V^2}{R} dt = \frac{1}{TR} \int_0^T A^2 \sin^2(\omega t + \phi) dt = \frac{A^2}{2R} = \frac{A_{\text{rms}}^2}{R}.$$

(1.44)

This last form shows that we *can* use Eq. (1.8) to calculate the power as long as we use the rms amplitude of the sinusoidal signal in the formula. The same argument applies to Eq. (1.7) for sinusoidal currents.

(d) Decibels (abbreviated dB) are used to compare the amplitude of two signals, say  $A_1$  and  $A_2$ :

$$dB = 20 \log_{10} \frac{A_2}{A_1} = 10 \log_{10} \left(\frac{A_2}{A_1}\right)^2 = 10 \log_{10} \frac{P_2}{P_1}$$

(1.45)

where this last expression uses the power level of the two signals. So, for example, if  $A_2 = 2A_1$ , then we get  $20 \log 2 \approx 6$ , so we say  $A_2$  is 6 dB higher than  $A_1$ . Various related schemes specify the decibel level relative to a fixed standard. So dBV is the dB relative to a 1 V<sub>rms</sub> signal and dBm is the dB relative to a 0.78 V<sub>rms</sub> signal. For the curious, this latter voltage standard is 1 mW into a 600  $\Omega$  resistor.

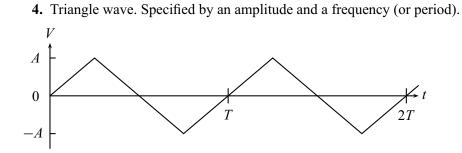

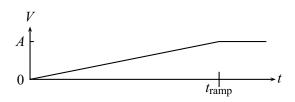

Some other typical waveforms of electronics are shown in Figs. 1.25 through 1.30.

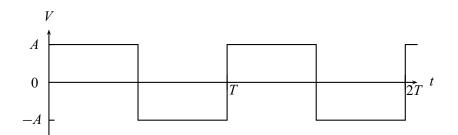

2. Square wave. Specified by an amplitude and a frequency (or period).

Figure 1.25 The square wave.

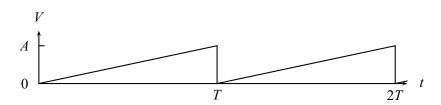

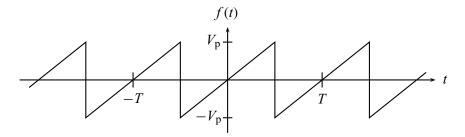

3. Sawtooth wave. Specified by an amplitude and a frequency (or period).

Figure 1.26 The sawtooth wave.

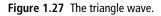

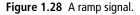

5. Ramp. Specified by an amplitude and a ramp time.

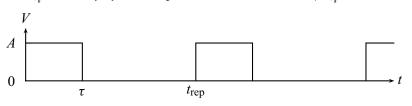

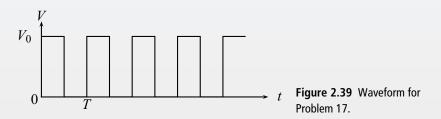

6. Pulse train. Specified by an amplitude, a pulse width  $\tau$ , and a repetition time  $t_{\text{rep}}$ . The *duty cycle* of a pulse train is defined as  $\tau/t_{\text{rep}}$ .

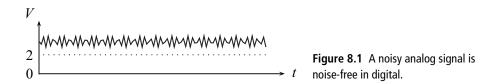

7. Noise. These are random signals of thermal origin or simply unwanted signals coupled into the circuit. Noise is usually described by its frequency content, but that is a more advanced topic.

Figure 1.30 Noise.

#### EXERCISES

- 1. What is the resistance of a nichrome wire 1 mm in diameter and 1 m in length?

- 2. What is the maximum allowable current through a  $10 \text{ k}\Omega$ , 10 W resistor? Through a  $10 \text{ k}\Omega$ , 1/4 W resistor?

- 3. (a) What power rating is needed for a 100  $\Omega$  resistor if 100 V is to be applied to it? (b) For a 100 k $\Omega$  resistor?

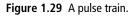

- **4.** Compute the current through  $R_3$  of Fig. 1.31.

- **5.** Compute the current through  $R_1$  and  $R_2$  of Fig. 1.31.

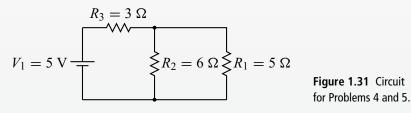

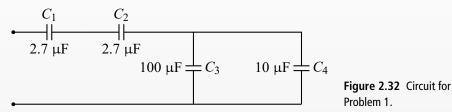

- 6. The output of the voltage divider of Fig. 1.32 is to be measured with voltmeters with input resistances of 100  $\Omega$ , 1 k $\Omega$ , 50 k $\Omega$ , and 1 M $\Omega$ . What voltage will each indicate?

- 7. A real battery can be modeled as an ideal voltage source in series with a resistor (the *internal resistance*). A voltmeter with input resistance of  $1000 \Omega$  measures the voltage of a worn-out 1.5 V flashlight battery as 0.9 V. What is the internal resistance of the battery?

- 8. If the flashlight battery of the preceding problem had been measured with a voltmeter with input resistance of  $10 \text{ M}\Omega$ , what would the reading be?

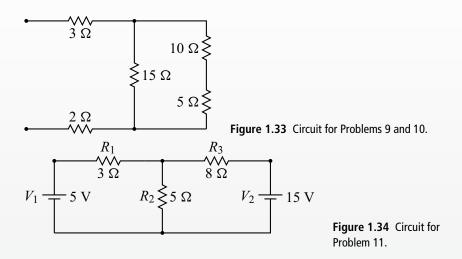

- 9. What is the resistance across the terminals of Fig. 1.33?

- 10. Suppose that a 25 V battery is connected to the terminals of Fig. 1.33. Find the current in the 10  $\Omega$  resistor.

- **11.** Compute the current through  $R_2$  and  $R_3$  of Fig. 1.34.

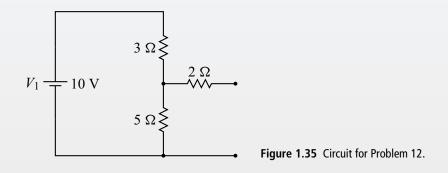

**12.** Find the Thevenin voltage and Thevenin resistance of the circuit shown in Fig. 1.35.

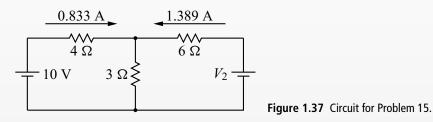

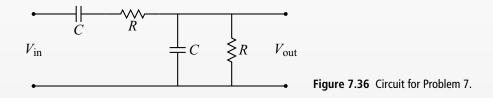

13. Find the Thevenin voltage and Thevenin resistance of the circuit shown in Fig. 1.36 with  $R_5$  removed. The two terminals for this problem are the points where  $R_5$  was connected.

#### Exercises

- 14. Using the result of the previous problem, find the current through  $R_5$  of Fig. 1.36.

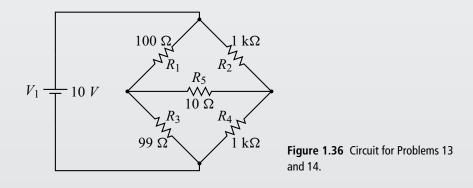

- 15. In the circuit of Fig. 1.37, compute the current in the 3  $\Omega$  resistor and find the value of  $V_2$ .

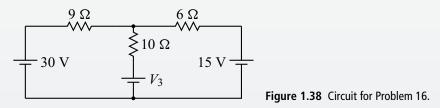

16. In the circuit of Fig. 1.38, find the value of  $V_3$  such that the current in the 10  $\Omega$  resistor is zero.

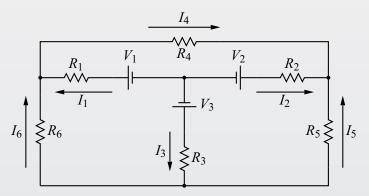

17. Compute all the currents labeled in the circuit of Fig. 1.39 assuming the following values: V<sub>1</sub> = 5 V, V<sub>2</sub> = 10 V, V<sub>3</sub> = 15 V, R<sub>1</sub> = 2 Ω, R<sub>2</sub> = 4 Ω, R<sub>3</sub> = 6 Ω, R<sub>4</sub> = 7 Ω, R<sub>5</sub> = 5 Ω, R<sub>6</sub> = 3 Ω. Suggestion: use the mesh loop method.

Figure 1.39 Circuit for Problem 17.

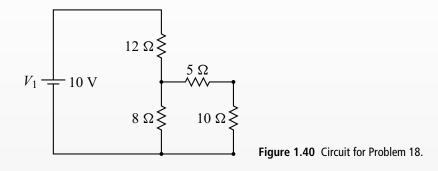

**18.** (a) Compute the current through the  $10 \Omega$  resistor in the circuit of Fig. 1.40. Do not use Thevenin's or Norton's theorems for this computation. (b) Now

find the Thevenin voltage, the Thevenin resistance, and the Norton current when the  $10 \Omega$  resistor is removed. The two terminals for this problem are the points where the  $10 \Omega$  resistor was connected. (c) Show that, if the  $10 \Omega$  resistor is connected to the Thevenin equivalent circuit, the current through the  $10 \Omega$  resistor matches the value found in part (a). Do the same for the Norton equivalent circuit.

#### FURTHER READING

- Charles K. Alexander and Matthew N. O. Sadiku, *Fundamentals of Electric Circuits*, 2nd edition (New York: McGraw-Hill, 2004).

- L. W. Anderson and W. W. Beeman, *Electric Circuits and Modern Electronics* (New York: Holt, Rinehart, and Winston, 1973).

- Dennis Barnaal, *Analog Electronics for Scientific Application* (Prospect Heights, IL: Waveland Press, 1989).

- James J. Brophy, *Basic Electronics for Scientists*, 5th edition (New York: McGraw-Hill, 1990).

- A. James Diefenderfer and Brian E. Holton, *Principles of Electronic Instrumentation*, 3rd edition (Philadelphia, PA: Saunders, 1994).

- Robert E. Simpson, *Introductory Electronics for Scientists and Engineers*, 2nd edition (Boston, MA: Allyn and Bacon, 1987).

## 2.1 Introduction

Currents and voltages that vary in time are called AC quantities. When analyzing circuits where the current and voltage change in time, the treatment of resistors is unchanged: they still obey Ohm's Law. In this chapter we introduce two other basic circuit components, the capacitor and the inductor. The treatment of these components depends on the details of how things are changing in time, and this will require the development of some new analysis techniques.

## 2.2 Capacitors

Another basic circuit component is the capacitor. A capacitor is formed by any pair of conductors, but the usual form is two parallel plates. For this case, the capacitance C is given by

$$C = \epsilon \frac{A}{d} \tag{2.1}$$

where A is the area of a plate, d is the distance between plates, and  $\epsilon$  is the dielectric constant of the material between the plates. Note that, like the resistance, the capacitance depends only on the physical characteristics of the device. The unit of capacitance is coulombs per volt or *farads*, abbreviated F. Typical capacitor values are in a range such that  $\mu$ F or pF are convenient units. When purchasing a capacitor, you must specify its *voltage rating* in addition to its capacitance value. This rating tells you the maximum voltage you can apply across the capacitor before there is electrical breakdown through the dielectric material.

So what does a capacitor do? One answer is that it is a charge storage device. When a voltage V is applied to a capacitor, a charge of magnitude Q will be stored on each plate. Q is given by

$$Q = CV. \tag{2.2}$$

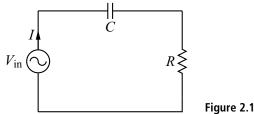

Figure 2.1 Equivalent circuit for capacitors in series.

In electronics, we are usually concerned with currents (the *flow* of charge) rather than charge. If we take the time derivative of Eq. (2.2) and note that, by definition,  $I = \frac{dQ}{dt}$  we get

$$I = C \frac{\mathrm{d}V}{\mathrm{d}t}.\tag{2.3}$$

Viewed from this perspective, C is the constant relating a time-varying voltage across the capacitor to the AC current through the capacitor.

## 2.2.1 Equivalent circuit laws for capacitors

As with resistors, capacitors in series and parallel can be combined to form simpler equivalent circuits.

#### 2.2.1.1 Series capacitors

Consider, for example, three capacitors in series as shown in Fig. 2.1. We wish to combine the capacitors to form the equivalent circuit on the right.

Let  $Q_1$  be the charge on capacitor  $C_1$  and so on. Applying KVL and Eq. (2.2) we obtain

$$V - \frac{Q_1}{C_1} - \frac{Q_2}{C_2} - \frac{Q_3}{C_3} = 0.$$

(2.4)

By charge conservation, the charge on each capacitor is the same, so  $Q_1 = Q_2 = Q_3 \equiv Q$  and

$$V = Q\left(\frac{1}{C_1} + \frac{1}{C_2} + \frac{1}{C_3}\right).$$

(2.5)

Comparing this with Eq. (2.2), we see that the equivalent capacitance  $C_{eq}$  will be given by

$$\frac{1}{C_{\rm eq}} = \frac{1}{C_1} + \frac{1}{C_2} + \frac{1}{C_3}$$

(2.6)

Figure 2.2 Equivalent circuit for capacitors in parallel.

or, generalizing this to any number of capacitors in series,

$$\frac{1}{C_{\rm eq}} = \sum_{i} \frac{1}{C_i}.$$

(2.7)

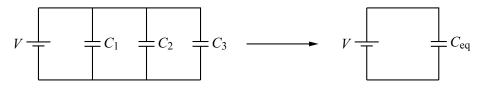

#### 2.2.1.2 Parallel capacitors

Now consider three capacitors in parallel as shown in Fig. 2.2. Again, let  $Q_1$  be the charge on capacitor  $C_1$  and so on. Because the capacitors are connected in parallel, the voltage across them must be the same

$$V = \frac{Q_1}{C_1} = \frac{Q_2}{C_2} = \frac{Q_3}{C_3}.$$

(2.8)

If we add the three charges and apply Eq. (2.8) to each term, we get

$$Q_1 + Q_2 + Q_3 = V(C_1 + C_2 + C_3).$$

(2.9)

If we are to form an equivalent capacitor the battery must supply the same amount of charge in both cases. Thus  $Q_{eq} = Q_1 + Q_2 + Q_3$  and, from Eq. (2.9),  $Q_{eq} = V(C_1 + C_2 + C_3)$ . Comparing this with Eq. (2.2), we see that

$$C_{\rm eq} = C_1 + C_2 + C_3 \tag{2.10}$$

or, generalizing this to any number of capacitors in parallel,

$$C_{\rm eq} = \sum_{i} C_i. \tag{2.11}$$

Note that capacitors combine opposite to the way resistors combine: *series* resistors add up directly while *parallel* capacitors add up directly.

#### 2.3 Inductors

We learn in introductory physics that currents produce magnetic fields (Ampère's Law) and that time-varying magnetic fields can induce a voltage in a circuit

(Faraday's Law). Putting these together means that time-varying currents in a circuit induce voltages. This is expressed in equation form by

$$V = L \frac{\mathrm{d}I}{\mathrm{d}t} \tag{2.12}$$

where the constant L is called the *self-inductance* or simply the inductance. While any circuit loop has inductance, we usually ignore this (like we ignore the small resistance of connecting wires) and, if inductance is required in a circuit, add discrete inductors made of coils of wire. For a long coil (i.e., a solenoid), this inductance is given by

$$L = \frac{\mu N^2 \pi R^2}{l} \tag{2.13}$$

where  $\mu$  is the permeability of the material on which the coil is wound, *N* is the number of turns in the coil, *R* is the radius of the coil, and *l* is the length of the coil. The unit of inductance is volts times seconds per amp or *henries* (abbreviated H).

The derivation of the equivalent circuit laws for inductors in series and parallel is similar to that for resistors, and we leave the details to the reader. The result for inductors in series is

$$L_{\rm eq} = \sum_{i} L_i \tag{2.14}$$

and for inductors in parallel

$$\frac{1}{L_{\rm eq}} = \sum_{i} \frac{1}{L_{i}}.$$

(2.15)

Note that inductors combine the same way that resistors do.

#### 2.4 RC circuits

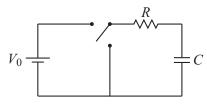

Now we turn to our first circuit that combines components - in this case a resistor and capacitor in series. Consider the circuit in Fig. 2.3.

Figure 2.3 A switched RC circuit.

2.4 RC circuits

The resistor-capacitor combination is connected to a switch which can be positioned to connect to the battery  $V_0$  or to a short. We can analyze both cases at once: applying KVL we obtain

$$V = IR + \frac{Q}{C} \tag{2.16}$$

where V is equal to  $V_0$  when the switch connects to the battery and is equal to zero when the switch is down. We next take the derivative of Eq. (2.16) in order to remove Q in favor of the current I. Since V is constant for either switch position, we obtain for both cases

$$0 = R\frac{\mathrm{d}I}{\mathrm{d}t} + \frac{I}{C}.\tag{2.17}$$

We thus have a first order differential equation for the current I that must be solved to complete the analysis of the circuit. Rearranging Eq. (2.17), we obtain

$$\frac{\mathrm{d}I}{I} = -\frac{\mathrm{d}t}{RC}.\tag{2.18}$$

Integrating both sides gives

$$\ln I = -\frac{t}{RC} + K \tag{2.19}$$

where K is the constant of integration. Finally, we exponentiate both sides

$$I = \exp\left(-\frac{t}{RC} + K\right) = I_0 \exp\left(-\frac{t}{RC}\right).$$

(2.20)

In this last step we have introduced a new constant  $I_0$  in place of the constant exp(K). Equation (2.20) is the general solution for the current as a function of time. We will see how to determine the constant  $I_0$  in a moment.

The voltage across the resistor is just *IR*. Let's also determine the voltage across the capacitor,  $V_c$ . KVL gives (for either switch position)  $V_c = V - IR$ . Employing Eq. (2.20) we obtain

$$V_{\rm c} = V - I_0 R \exp\left(-\frac{t}{RC}\right). \tag{2.21}$$

For future reference, we note that, since V and  $I_0R$  are constants, we can write a general solution for  $V_c$  as

$$V_{\rm c} = V_1 \exp\left(-\frac{t}{RC}\right) + V_2 \tag{2.22}$$

where  $V_1$  and  $V_2$  are constants.

#### 2.4.1 Charging

To further determine the behavior of the circuit, we need to specify the conditions when the switch is thrown (i.e., the *initial conditions*). Suppose we assemble the circuit with an uncharged capacitor so that  $V_c$  is initially zero. We define t = 0 at the instant we throw the switch to connect the battery. Thus, at t = 0,  $V_c = 0$  and  $V = V_0$ . Using this information in Eq. (2.21), we obtain:

$$0 = V_0 - I_0 R \tag{2.23}$$

which then gives us the unknown constant  $I_0 = \frac{V_0}{R}$ . Using this information in Eqs. (2.20) and (2.21) gives us our specific solutions:

$$I = \frac{V_0}{R} \exp\left(-\frac{t}{RC}\right) \tag{2.24}$$

and

$$V_{\rm c} = V_0 \left[ 1 - \exp\left(-\frac{t}{RC}\right) \right]. \tag{2.25}$$

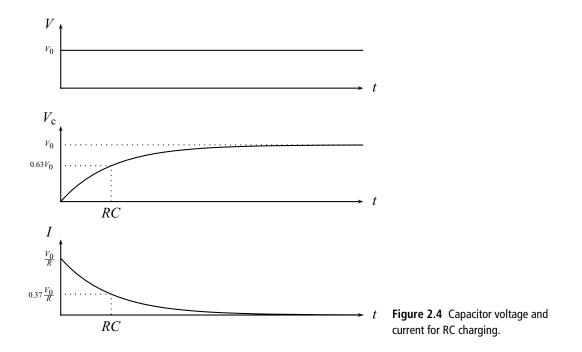

These solutions are plotted in Fig. 2.4. It is worth noting some of the key features. The current starts at its maximum value  $V_0/R$  and then falls toward zero. The capacitor starts (as we specified) with zero voltage and approaches the battery voltage  $V_0$  as it charges up. Each solution has an exponential term with a decay that depends on the ratio t/RC. The product RC, which has units of time, is called the *time constant* of the decay. It determines how long it takes for the circuit to approach its final state. When t = RC, the current has dropped to about 37% of its initial value and the capacitor has reached roughly 63% of its final value. This notion of time constant makes physical sense, too: a larger capacitor will take longer to fill with charge; a larger resistor will limit the flow of charge, thus increasing the time it takes to charge up the capacitor.

### 2.4.2 Discharging

Suppose that we have waited long enough that the capacitor has become fully charged. We now throw the switch to the down position. Resetting our clock to t = 0, our initial conditions are now  $V_c = V_0$  and V = 0. Using this information in Eq. (2.21) gives:

$$V_0 = 0 - I_0 R \to I_0 = -\frac{V_0}{R}$$

(2.26)

so our specific solutions become

$$I = -\frac{V_0}{R} \exp\left(-\frac{t}{RC}\right) \tag{2.27}$$

and

$$V_{\rm c} = V_0 \exp\left(-\frac{t}{RC}\right). \tag{2.28}$$

These solutions are plotted in Fig. 2.5. As the capacitor discharges, the capacitor voltage decays exponentially with a time constant RC and approaches zero (the voltage level it is now attached to). The current is negative because it flows in the opposite direction during discharge; it also decays exponentially with the same time constant.

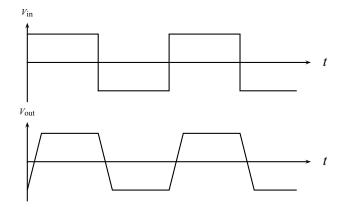

#### 2.4.3 Response to a square wave

We can use the insight we have obtained from our study of the switched RC circuit to sketch out the response of an RC circuit to a square wave drive. The square wave is a little different than our switch problem in that the voltage switches between  $V_0$  and  $-V_0$  rather than  $V_0$  and zero, so in the square wave case the discharge will approach  $-V_0$ .

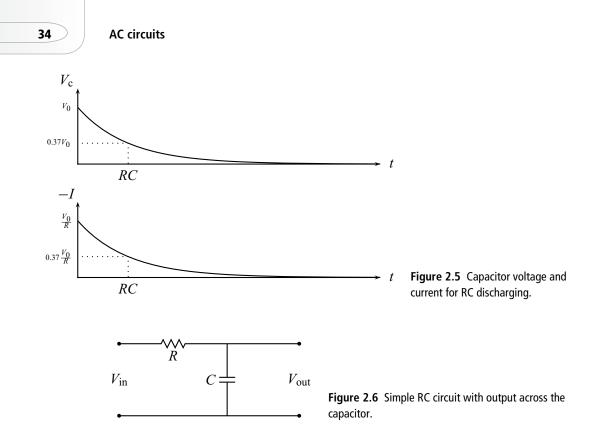

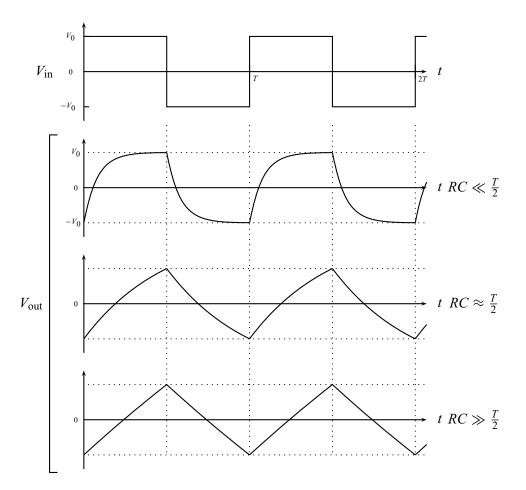

Let's first examine the case where the output of the circuit is the voltage across the capacitor. We can represent this case with the circuit diagram of Fig. 2.6 where  $V_{in}$  is a square wave of amplitude  $V_0$  and period T. The shape of the output voltage will depend on the relative size of RC and T/2. Some representative cases are shown in Fig. 2.7.

If  $RC \ll T/2$ , the capacitor has plenty of time to charge up fully while the square wave voltage stays constant. We thus see the same shape waveform as we saw in the switch problem. When the input voltage switches from  $V_0$  to  $-V_0$ , the capacitor discharges (or charges to the opposite polarity) and approaches the new input voltage. Note that for this case, the output voltage looks like a square wave with rounded leading edges.

If  $RC \approx T/2$ , the capacitor initially charges toward  $V_0$ , but only gets part of the way there before the input switches to  $-V_0$ . It now tries to charge to this input voltage, but, again, does not have the time to get there. Now the output voltage is quite different from a square wave. The maximum and minimum voltages are not shown for this case since they depend on the exact relationship between RC and T/2, but we can say that the maximum voltage is less than  $V_0$  and the minimum voltage is greater than  $-V_0$ .

Figure 2.7 Output of the circuit of Fig. 2.6 for a square-wave input voltage.

If  $RC \gg T/2$ , the capacitor has even less time to charge and discharge before the input voltage switches. In this case, the waveform is a series of rising and falling lines forming a triangle wave. This reflects the fact that the first term in the expansion of  $[1 - \exp(-t/RC)]$  for small t/RC is linear in time.

## 2.4.4 Voltage across the resistor

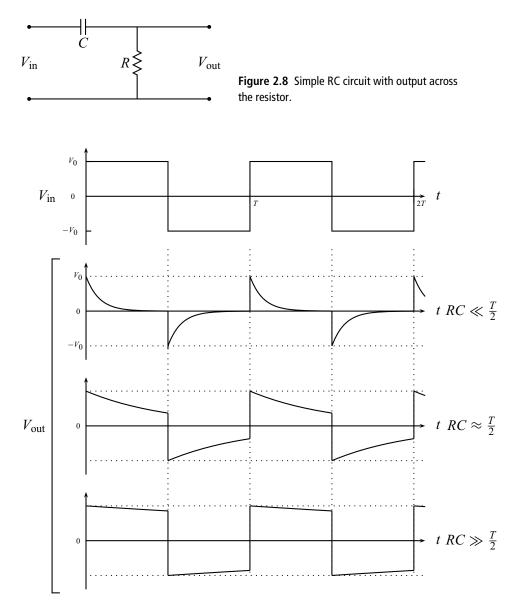

Having put so much work into our analysis of the RC circuit, let's squeeze out another result. Suppose we apply our square wave to the rearranged circuit of Fig. 2.8. Now our output voltage is the voltage across the resistor. This may seem like new territory, but it really is not since  $V_{\text{out}} = IR$  and we already solved the

Figure 2.9 Output of the circuit of Fig. 2.8 for a square-wave input voltage.

problem for *I*. Again, the shape of the output voltage depends on the relative size of RC and T/2 as shown in Fig. 2.9.

When  $RC \ll T/2$ , we have the case that is most like our switching problem. The current (and thus the output voltage) starts at its maximum value and decays exponentially toward zero. Since  $RC \ll T/2$ , there is plenty of time to decay all the way to zero. When the input voltage switches polarity, the current goes negative and again decays toward zero. The output voltage resembles a series of positive and negative spikes.

As the *RC* time constant becomes larger with respect to T/2, there is not enough time for the current to decay all the way to zero before the input switches, so the output voltage waveforms take on the shapes shown in the figure. When  $RC \gg T/2$ , the spiky behavior is gone and the output looks like a distorted square wave.

#### 2.5 Response to a sine wave

We now consider the response of an RC circuit to a sine wave drive. While it may appear that we are just making a minor change to the input waveform, the change is actually much more profound. For the switching case (or the square wave), the input voltage was, at each instant of time, constant. This allowed us to solve the differential equation (Eq. (2.17)) resulting from the circuit analysis, producing simple functions of time for I and  $V_c$ . This approach is called a *time domain analysis*. For more complicated input voltages, time domain analysis is not always possible because we cannot solve the resulting differential equation. In these cases, it is sometimes useful to analyze the circuit in terms of its sine wave response, which we will call a *frequency domain analysis*.

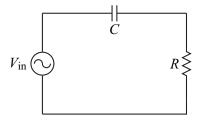

The relevant RC circuit is shown in Fig. 2.10, where now the voltage source is a sine wave input  $V_{in}$ . As usual, KVL gives

$$V_{\rm in} = \frac{Q}{C} + IR \tag{2.29}$$

and taking the time derivative of this and rearranging yields

$$R\frac{\mathrm{d}I}{\mathrm{d}t} + \frac{I}{C} = \frac{\mathrm{d}V_{\mathrm{in}}}{\mathrm{d}t}.$$

(2.30)

Note that, unlike the switching problem, the derivative of the input voltage is not zero. To proceed, we now specify the input voltage as  $V_{in} = V_p \sin \omega t$  and assume

**Figure 2.10** Simple RC circuit driven by a sinusoidal voltage.

the current has the form  $I = I_p \sin(\omega t + \phi)$ , where  $I_p$  and  $\phi$  are constants to be determined. Plugging into Eq. (2.30) results in

$$R\omega I_{\rm p}\cos\left(\omega t + \phi\right) + \frac{I_{\rm p}}{C}\sin\left(\omega t + \phi\right) = \omega V_{\rm p}\cos\omega t.$$

(2.31)

Note that our approach has allowed us to turn a differential equation (2.30) into an algebraic equation (2.31). We now proceed to solve for  $I_p$  and  $\phi$ .

In order to isolate the unknown constants  $\phi$  and  $I_p$ , we employ the following trig identities:

$$\sin(\omega t + \phi) = \sin \omega t \cos \phi + \cos \omega t \sin \phi \qquad (2.32)$$

and

$$\cos\left(\omega t + \phi\right) = \cos\omega t \cos\phi - \sin\omega t \sin\phi. \tag{2.33}$$

Dividing Eq. (2.31) by  $R\omega I_p$  and applying these identities gives

$$(\cos \omega t \cos \phi - \sin \omega t \sin \phi) + \frac{1}{\omega RC} (\sin \omega t \cos \phi + \cos \omega t \sin \phi) = \frac{V_{\rm p}}{I_{\rm p}R} \cos \omega t.$$

(2.34)

Rearranging, we get

$$\left(\cos\phi + \frac{1}{\omega RC}\sin\phi - \frac{V_{\rm p}}{I_{\rm p}R}\right)\cos\omega t + \left(-\sin\phi + \frac{1}{\omega RC}\cos\phi\right)\sin\omega t = 0.$$

(2.35)

In order to proceed in our quest for  $I_p$  and  $\phi$ , we make the following argument: Eq. (2.35) is valid for all times t, and thus must be valid for any particular time we choose. If we choose t = 0, then  $\sin \omega t = 0$  and  $\cos \omega t = 1$ , and Eq. (2.35) reduces to

$$\cos\phi + \frac{1}{\omega RC}\sin\phi - \frac{V_{\rm p}}{I_{\rm p}R} = 0.$$

(2.36)

Alternatively, if we choose t such that  $\omega t = \frac{\pi}{2}$ , then  $\sin \omega t = 1$  and  $\cos \omega t = 0$  and we obtain

$$-\sin\phi + \frac{1}{\omega RC}\cos\phi = 0. \tag{2.37}$$

This last equation can now be solved for  $\phi$ :

$$\frac{\sin\phi}{\cos\phi} = \tan\phi = \frac{1}{\omega RC} \to \phi = \tan^{-1}\left(\frac{1}{\omega RC}\right).$$

(2.38)

Figure 2.11 Right triangle satisfying Eq. (2.38).

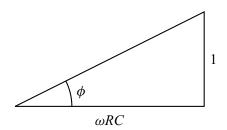

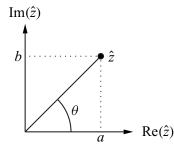

Equation (2.36) requires  $\sin \phi$  and  $\cos \phi$  in order to solve for  $I_p$ . If we have values for  $\omega$ , R, and C then, of course, we can obtain a number for  $\phi$  from Eq. (2.38) and simply plug-in to get  $\sin \phi$  and  $\cos \phi$ . But we prefer to obtain general algebraic results, so we use the following trick. A right triangle satisfying Eq. (2.38) is shown in Fig. 2.11. It thus follows that  $\sin \phi$  and  $\cos \phi$  are given by

$$\sin\phi = \frac{1}{\sqrt{1 + (\omega R C)^2}} \tag{2.39}$$

and

$$\cos\phi = \frac{\omega RC}{\sqrt{1 + (\omega RC)^2}}.$$

(2.40)

Using these expressions in Eq. (2.36),

$$\frac{\omega RC}{\sqrt{1 + (\omega RC)^2}} + \frac{1}{\omega RC} \frac{1}{\sqrt{1 + (\omega RC)^2}} = \frac{V_p}{I_p R}$$

(2.41)

which gives, after some algebra,

$$I_{\rm p} = \frac{\omega C}{\sqrt{1 + (\omega R C)^2}} V_{\rm p}.$$

(2.42)

Recalling the form we assumed for the current at the beginning, our final solution is

$$I = \frac{\omega C V_{\rm p}}{\sqrt{1 + (\omega R C)^2}} \sin(\omega t + \phi), \qquad (2.43)$$

where  $\phi$  is given by

$$\phi = \tan^{-1} \left( \frac{1}{\omega RC} \right). \tag{2.44}$$

Figure 2.12 A high-pass RC filter.

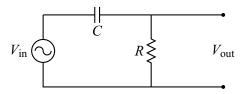

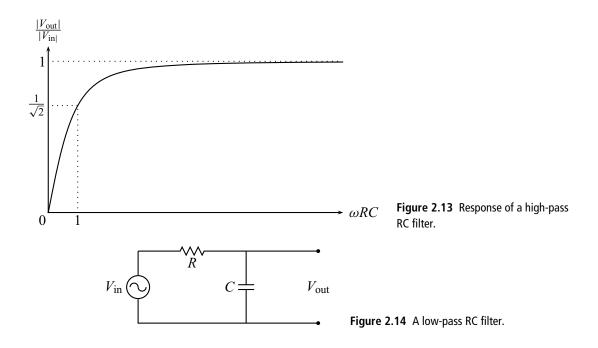

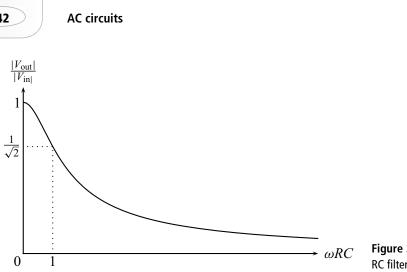

#### 2.5.1 RC positive phase shifter and high-pass filter

We can now apply our result to two common circuits. The first, shown in Fig. 2.12, takes the output voltage  $V_{\text{out}}$  across the resistor.

Since we have already solved for the current, getting this output voltage is easy:

$$V_{\text{out}} = IR = \frac{\omega R C V_{\text{p}}}{\sqrt{1 + (\omega R C)^2}} \sin(\omega t + \phi).$$

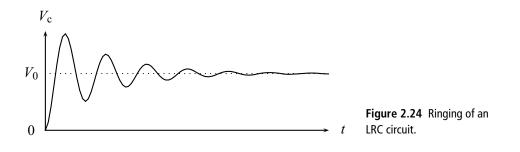

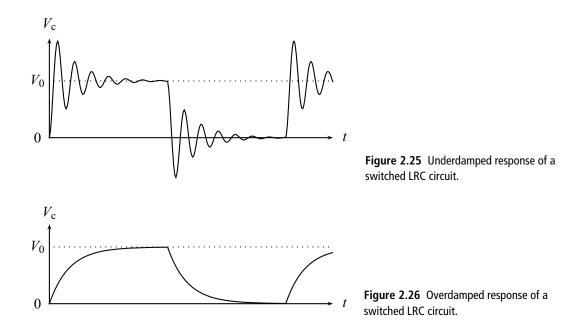

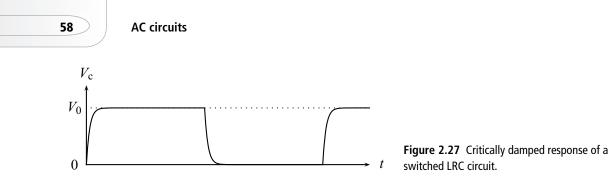

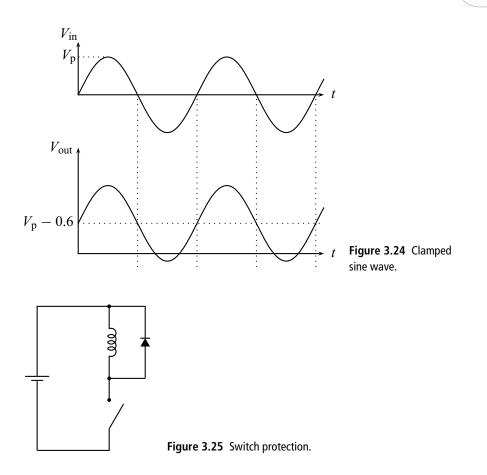

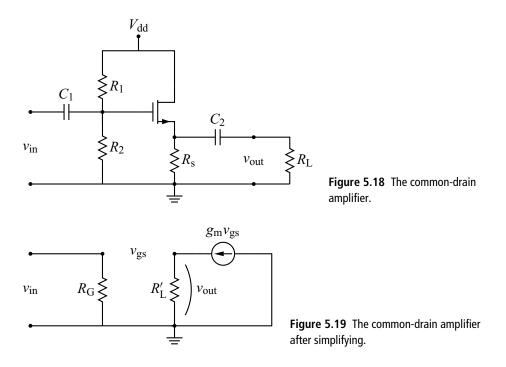

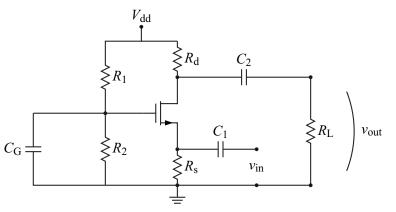

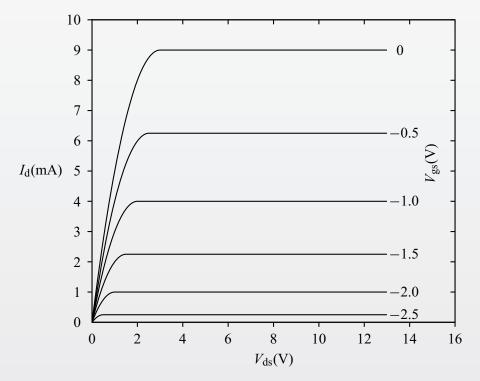

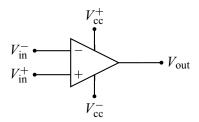

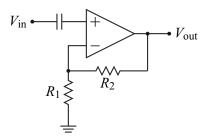

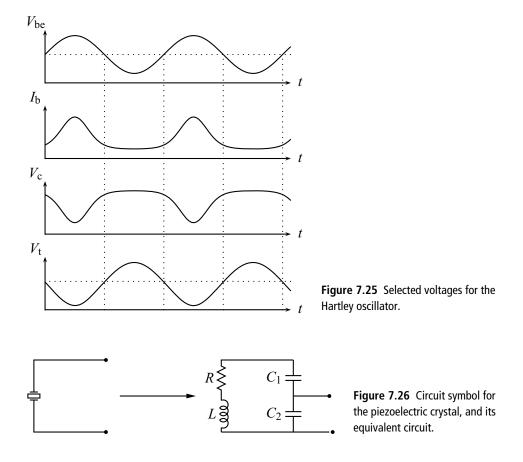

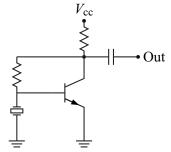

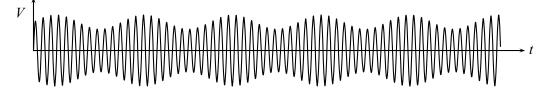

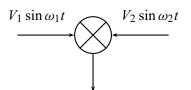

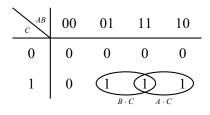

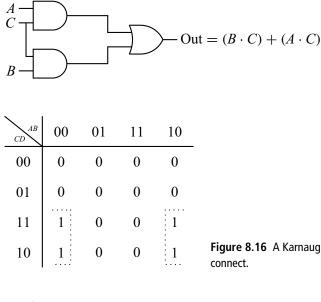

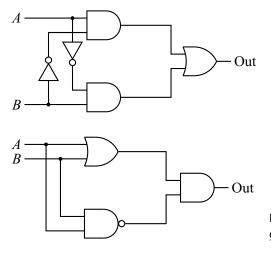

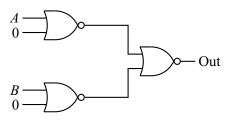

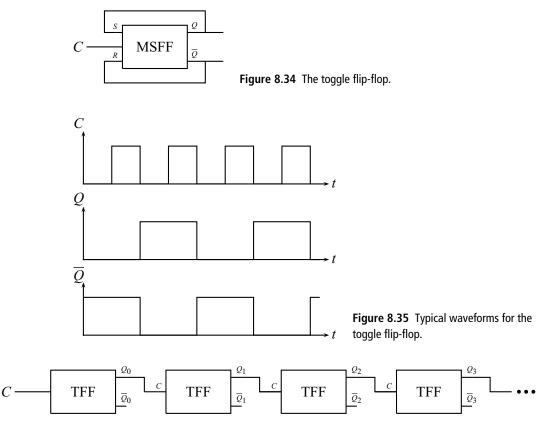

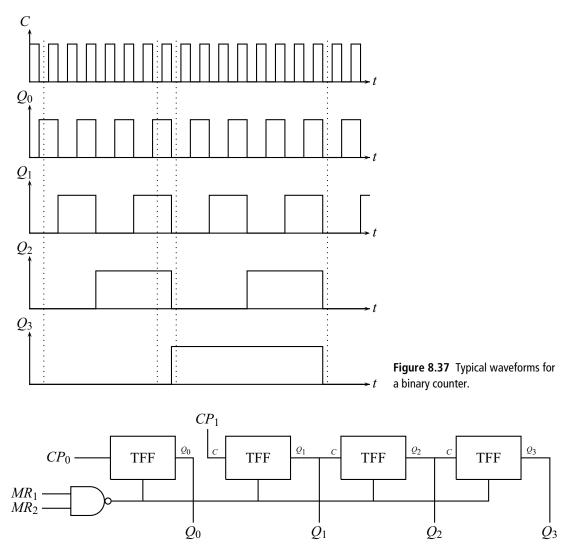

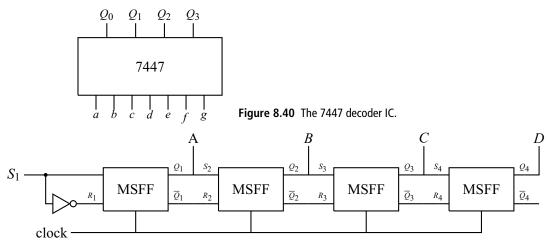

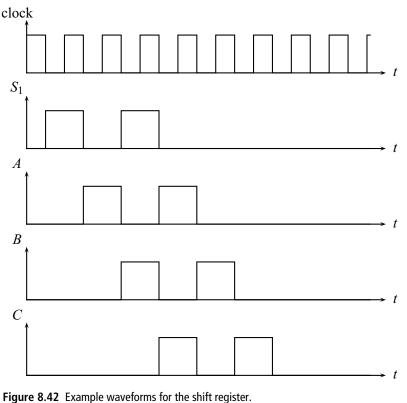

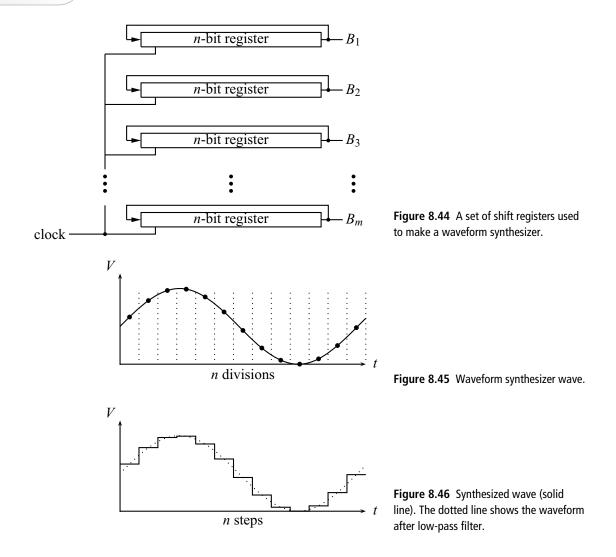

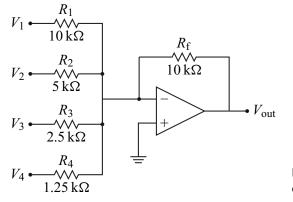

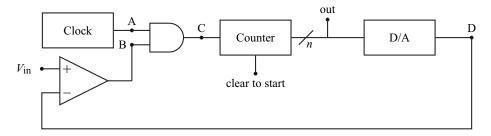

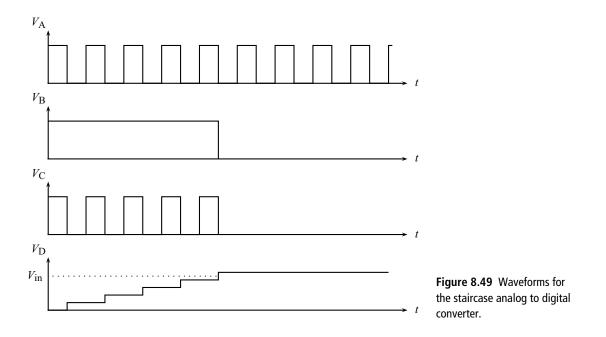

(2.45)