# **Springer Theses** Recognizing Outstanding Ph.D. Research

# Piotr Antonik

# Application of FPGA to Real-Time Machine Learning

Hardware Reservoir Computersand Software Image Processing

# **Springer Theses**

Recognizing Outstanding Ph.D. Research

# Aims and Scope

The series "Springer Theses" brings together a selection of the very best Ph.D. theses from around the world and across the physical sciences. Nominated and endorsed by two recognized specialists, each published volume has been selected for its scientific excellence and the high impact of its contents for the pertinent field of research. For greater accessibility to non-specialists, the published versions include an extended introduction, as well as a foreword by the student's supervisor explaining the special relevance of the work for the field. As a whole, the series will provide a valuable resource both for newcomers to the research fields described, and for other scientists seeking detailed background information on special questions. Finally, it provides an accredited documentation of the valuable contributions made by today's younger generation of scientists.

# Theses are accepted into the series by invited nomination only and must fulfill all of the following criteria

- They must be written in good English.

- The topic should fall within the confines of Chemistry, Physics, Earth Sciences, Engineering and related interdisciplinary fields such as Materials, Nanoscience, Chemical Engineering, Complex Systems and Biophysics.

- The work reported in the thesis must represent a significant scientific advance.

- If the thesis includes previously published material, permission to reproduce this must be gained from the respective copyright holder.

- They must have been examined and passed during the 12 months prior to nomination.

- Each thesis should include a foreword by the supervisor outlining the significance of its content.

- The theses should have a clearly defined structure including an introduction accessible to scientists not expert in that particular field.

More information about this series at http://www.springer.com/series/8790

Piotr Antonik

# Application of FPGA to Real-Time Machine Learning

Hardware Reservoir Computers and Software Image Processing

Doctoral Thesis accepted by the Université libre de Bruxelles, Brussels, Belgium

Author Dr. Piotr Antonik CentraleSupélec Metz France Supervisor Prof. Serge Massar Université libre de Bruxelles Brussels Belgium

ISSN 2190-5053 ISSN 2190-5061 (electronic) Springer Theses ISBN 978-3-319-91052-9 ISBN 978-3-319-91053-6 (eBook) https://doi.org/10.1007/978-3-319-91053-6

Library of Congress Control Number: 2018940427

© Springer International Publishing AG, part of Springer Nature 2018

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Printed on acid-free paper

This Springer imprint is published by the registered company Springer International Publishing AG part of Springer Nature

The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

To my Dad

# **Supervisor's Foreword**

Today, we have two completely different examples of computing systems. The first is our digital electronic computers that represent information using binary signals, 0 and 1, and process the information sequentially at a very high rate (GHz). The second is the biological brain that represents information in an analogue way (time and intensity of spikes) that processes the information in parallel, but rather slowly (kHz).

We do not really understand how the brain processes information. But the booming field of artificial intelligence and artificial neural networks tries to emulate the brain (if not in detail, at least imitating in some aspects how it processes information) using digital computers.

An alternative approach is to develop analogue hardware information processing systems that imitate, again only in some aspects, how the brain processes information. This line of research has a long history. It is closely related to advances in machine learning, as novel algorithms in machine learning can lead to novel hardware architectures.

In parallel with the above, photonics has developed into a major industry, which underlies many aspects of our information-driven society. But it remains extremely challenging to process information in the optical domain, and one is almost always obliged to carry out costly optical to electronic conversion whenever optical information must be processed (e.g. for routing).

A recent development in machine learning is the algorithm known as 'reservoir computing'. This algorithm turns out to be very well suited to experimental implementation, as there is a lot of flexibility how exactly it is implemented. This led to a number of photonic implementations that go beyond what had been achieved previously in optical computing. Photonic reservoir computing is a growing research field. The most important question in the area is whether these systems can be brought to the level where they can compete with existing solutions for optical information processing.

In his thesis, Piotr Antonik pushed the performance of these photonic reservoir computers considerably beyond what had been realised before, thereby expanding their capabilities and the range of possible applications. This was achieved by interfacing a photonic reservoir computer with a high-speed electronic device, a Field-Programmable Gate Array (FPGA), enabling interactions with the reservoir computer in real time.

The main results obtained during the thesis are:

- (1) The experimental demonstration that photonic reservoir computers can solve tasks that change in time, which is important for some applications, particularly in telecommunications. For this, Piotr had to adapt the method known as online training to photonic reservoir computers.

- (2) The experimental demonstration of a reservoir computing system whose hardware is used both for computing and for optimising its internal parameters, thereby considerably improving performance. By carrying out the optimisation in hardware, this work demonstrated that one could potentially circumvent the difficulties of previous work that relied on detailed numerical models of the experiment to realise the optimisation.

- (3) The experimental demonstration that photonic reservoir computers with output feedback could produce periodic time series and emulate chaotic dynamical systems. This opens up a whole new area of applications of analogue reservoir computers, as well as novel conceptual questions about chaotic dynamics.

- (4) The numerical demonstration (which Piotr Antonik hopes to soon confirm in hardware) that the performance and robustness of the output layer of reservoir computers could be considerably improved by online training.

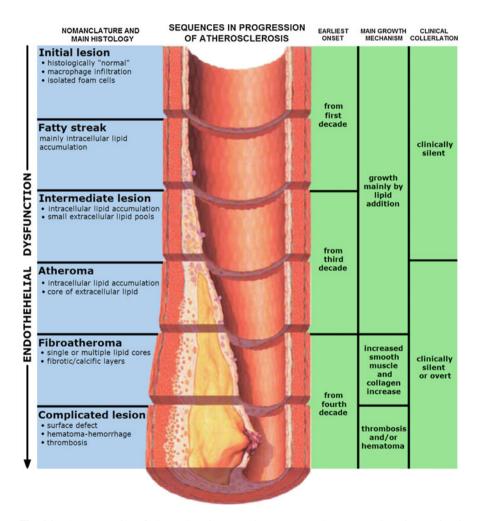

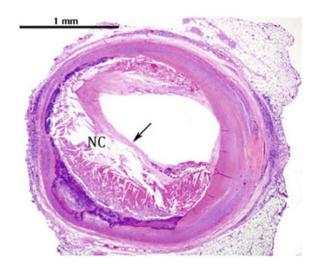

- (5) Real-time image analysis of optical coherence tomography of atherosclerotic arteries, using methods from artificial intelligence and FPGA programming. (In this chapter, Piotr Antonik used his expertise in machine learning and FPGA programming to make progress on a very different problem, namely real-time image analysis of optical coherence tomography of atherosclerotic arteries).

The thesis may give rise to industrial valorisation. First, reservoir computing is simple, flexible, easy to train and can be implemented in optics. It is believed that the most promising area of application in the short term is telecommunication through optical fibres, and in particular equalisation of optical communication channels (i.e. corrections of the distortions that occur during transmission). Second, Piotrs work on optical coherence tomography may give rise to applications on a short timescale. Indeed real-time image analysis of optical coherence tomography of atherosclerotic arteries may help expand the use of this technique in hospitals.

Piotr Antoniks thesis is highly interdisciplinary. The theory on how to design, train, exploit and benchmark the experiments was supplied by ideas from machine learning, and in particular from the topic of reservoir computing. The experiments themselves were built from photonic and electronic components. Understanding how they would perform required extensive numerical simulations. To develop new features, Piotr used an advanced tool from the electronics world—a FPGA chip. Programming of such a chip is a complex task that requires in-depth expertise of analogue and digital electronics.

Photonic reservoir computing is a rapidly developing area. Piotr Antoniks thesis is very clearly written. It gives a snapshot of some of the latest advances in the area. I hope that its publication in the 'Springer Theses' series will help spread knowledge and interest about this area.

Brussels, Belgium March 2018 Prof. Serge Massar

# Abstract

Computers have gained a cardinal place in modern societies, thanks to higher efficiencies and miniaturisation. However, their dramatic progress will soon have to stop as the limits of miniaturisation are being reached. Furthermore, few people realise that those computers are, in fact, not as powerful as they seem to be. And while the world champion at Go lost to a computer, an average human still beats a computer at relatively easy tasks such as recognising an object in a picture. Artificial intelligence is the key to more versatile computing machines capable of solving such challenging tasks.

My Ph.D. research lies in the intersection of artificial intelligence—the science of solving complex problems in a smart way, and photonics—the science of light that offers the potential to design ultra-fast and energy efficient processing devices. Photonics, and in particular optical telecommunications, underlies much of our information society, allowing information transmission at unprecedented rates through optical fibres. Recent optical realisations of simple artificial neural networks, also known as reservoir computers, have allowed a breakthrough in optical computing. I have pushed the performance of these systems significantly beyond what was achieved before. By interfacing a photonic reservoir computer with a high-speed electronic device, a FPGA, I could interact with the reservoir computer in real time, and thereby considerably expand its capabilities, and therefore the range of possible applications.

Specifically, we demonstrated experimentally that (1) photonic reservoir computers could solve tasks that change in time, which is important for some applications, particularly in telecommunications, (2) reservoir computing systems could use their hardware both for computation and for optimising its internal parameters, thereby considerably improving their performance, (3) photonic reservoir computers with output feedback could produce periodic time series and truthfully emulate chaotic dynamical systems. Furthermore, we presented a numerical demonstration (which we soon hope to confirm experimentally) that the performance and robustness of the output layer of reservoir computers could be considerably improved by online training. Finally, I used my expertise in machine learning and FPGA programming to make progress on a very different problem, namely real-time image analysis of optical coherence tomography of atherosclerotic arteries.

# Preface

This dissertation contains the full story of the 4 years of my Ph.D. The structure of the document is quite simple. The first chapter explains the theoretical and experimental basics. Throughout my thesis, I worked on four distinctive experiments. Some of them were my own projects, others were collaborations with other researchers in our group. They will be described in four separate chapters (Chaps. 2–5). By the end of my Ph.D., I took a 5-month internship at the University of Texas at Austin, that will be covered in Chap. 6. Finally, Chap. 7 concludes the story with a few ideas for future research.

Before writing this thesis, I had to make a crucial choice: either spend 3 to 5 months writing an original dissertation from scratch, or fill the thesis with my publications and spend the remaining time on another experiment. Without much hesitation, I chose the second option. In other words, this thesis compiles the work presented in these journal papers, properly integrating them to form a continuous story. This is a somewhat lazy approach—I do not deny it. But I believe the importance of a thesis consists of its scientific value. And those extra 5 months allowed me to complete another interesting project, thus increasing the significance of my work.

Another word of warning should be written concerning the style of the present thesis. Scientific English is a very clear and concise communication tool, but may seem somewhat boring. And after writing a few journal papers and a dozen of conference proceedings, I wanted to add some colours to the final publication of my Ph.D. Therefore, while its tone remains scientific most of the time, I allowed myself a few minor digressions. The reader will notice that from the very first lines of the first chapter.

Final remark, most chapters contain a 'bonus' section, describing the challenges encountered during the realisation of a particular project. These sections contain the back story of each experiment. In most fields of science, positive results are published, and the negative remain in the shadows. However, knowing what has been tried but did not work may save time in some cases, or even inspire new ideas. For this reason, I decided to include in this dissertation some facts that did not make it to the journal papers.

Brussels, Belgium

Piotr Antonik

# Acknowledgements

It is an immense pleasure to thank the numerous people who made this thesis possible.

First and foremost, it is difficult to overstate my gratitude to my Ph.D. supervisor, Prof. Serge Massar. There are two things I long for the most—freedom and support—and Serge gave me both. While freedom gives birth to that spark that ignites new ideas, support is the fuel that turns ideas into projects and, ultimately, results and publications. So thank you, Serge, for being the best supervisor I could ever wish for. This paragraph would be dramatically incomplete without a big thanks to Prof. Marc Haelterman, my co-supervisor, for his everlasting support.

The next hat tip goes to the team of awesome postdocs I had a great pleasure of working with. I could never complete this thesis alone, and these are the people who took direct part in some of my projects. Starting with Dr. François Duport, who took me under his wing right from the start, before I even started as a Ph.D. student, and taught me everything I needed to work independently in the lab, and even more. Greeting François in the office as early as 7 a.m. and regularly seeing him in the lab after 9 p.m. constantly reminded me that the only time success comes before work is in the dictionary.<sup>1</sup> Following with Dr. Anteo Smerieri, who 'basically' guided me through the complex theory of reservoir computing and learning methods. Few people can speak of intricate algorithms with simple words, and even less could turn it into an enjoyable show, with particularly well-placed jokes—as was demonstrated on numerous occasions. Last (chronologically) but not least, comes Dr. Michiel Hermans, from whom I acquired a much deeper understanding of the machine learning field in general, and reservoir computing in particular. And on top of that, the idea of taking an internship abroad was inspired by Michiel, which ultimately led to an amazing experience in Texas (more on that in Chap. 6). Thank you very much for that!

I am particularly grateful to Prof. Thomas Milner for offering me the life-changing opportunity to join his research team at the University of Texas.

<sup>&</sup>lt;sup>1</sup>Quote credited to Stubby Currence by Quote Investigator.

Working with Prof. Milner was a very inspiring experience, and I appreciate how much I could learn in so little time about various aspects of scientific life.

I would like to thank all the Jury members for their valuable comments on the present thesis and, in particular, Dr. Daniel Brunner for his in-depth proofreading of the manuscript and the long list of questions and comments, that made this work more accurate and complete.

Debuting in electronics, and especially in FPGA design, is all but an easy task. Fortunately, I could benefit from valuable help from several people well skilled in this art. Thus, I would like to express my very great appreciation to Benoit Denègre for providing a solid starting point, as well as Colin Fera, Matthew Luscher, Ashkan Ashrafi and Arnaud from 4DSP for providing precious documentation and technical support.

The working environment is only as good as the people who surround you. In that sense, OPERA-Photonique is the second best thing that happened to me on this journey. Never before could I imagine that scientific research could be accompanied by numerous fun parties, uncountable pies, video games and movie nights. Therefore, an enormous shout-out goes to my co-workers, in alphabetical order: Akram Akrout, Marc Bauduin, Serena Bolis, Arno Bouwens, Thomas Bury, Ali Chichebor, Charles Ciret, Robin De Gernier, Rima Dadoune, Evangelia Dimitriadou, Evdokia Dremetsika, Michael Fita Codina, Simon-Pierre Gorza, Wosen Kassa, Pascal Kockaert, Virginie Lecocq, François Leo, Anh-Dung Nguyen, Laurent Olislager, Nicolas Poulvellarie, Maïté Swaelens, Guillaume Tillema and Quentin Vinckier. Very special thanks to Prof. Philippe Emplit for creating and maintaining such a productive environment, and to our awesome secretaries, Ibtissame Malouli and Alexandra Peereboom, who just took care of everything.

And when I could not stand the guys from OPERA anymore (just kidding), I could always join my always welcoming colleagues at LIQ, again in alphabetical order: Cédric Bamps, Olmo Nieto Sileras, Jonathan Silman, Tom Van Himbeeck and Erik Woodhead. And again, warm thanks to the secretaries, Sabrina Serrano Alvarez and David Houssart, for handling my orders, travel documents, and, most importantly, reimbursing me for all my expensive conference trips.

The one thing I benefited the most from scientific conferences—besides the chance to travel to some exotic places on the globe—is the opportunity to interact with scholars and industry experts, absorbing as much knowledge from them as possible. My first ICONIP conference in Istanbul, and long discussions with Prof. João Paulo P. Gomes were a particular revelation. I wish to acknowledge here their valuable help.

Most of the first chapter of this thesis, as well as one or two papers were written in various hospitals, clinics and medical centres. I very much appreciate the efforts of the staff who made the task of writing in waiting halls quite a comfortable exercise.

I have composed quite a long list so far, but still I have the impression that I missed someone. To those people I offer my sincere apologies—for my poor memory, and my gratitude—for their valuable help.

I would like to conclude with people who made a rather indirect contribution to this work. My big thanks go to my school teachers for letting me do what I really wanted (that is, solving mathematical, and later, physical problems) and not paying much attention in class, my school and university buddies for helping me get through the education process with that much fun, my close friends Nicolas De Groote, Livio Filippin, Jonathan Bloch and Anton Leonov for their support and inspiration. And of course, many sweet thanks go to my dear Luda, and her sister Sveta, for taking such good care of my new hairstyle.

Most appreciation and gratitude usually goes to people for their positive contributions. However, as an old saying goes—there can be no evil without good—I would like to make an exception and express my gratitude to all people who managed to hurt me, deeply or not, intentionally or not. Thank you for making me that much stronger!

Family is a true masterpiece of nature, and undoubtedly the most precious treasure one gets to cherish. And while most of my family lives abroad and quite far away, I felt a very positive lift every time I went to visit them. Thank you for filling me with confidence, love and kindness! And what a person would I be if I failed to mention my beloved sister Maria for her artistic touch and a very special character. You rock!

And as the best is usually saved for the end, my warmest thanks go to my parents. This is where words begin to fall short, but I will try my best anyway. To my mum, thank you for being such a positive, dynamic, kind, caring and forgiving person. Few grown-ups think twice before leaving their parent's home these days, but somehow, you made me think and rethink a gazillion times. And to my dad, thank you for being a model to me for so many years, a friend and guide I could follow anytime with my eyes closed. Thank you for introducing me to arithmetic and basic algebra at the age of six, and for directing me straight into my current scientific life. There are few things one has the luxury of being certain of. But for me, not for a second did I doubt that one day I would be here, preparing the defence of my Ph.D. thesis. And although I can no longer learn from you as I used to, I can still follow that bright star in the night sky you turned into.

# Contents

| 1 | Intr       | oductio | n                                                   | 1  |  |  |

|---|------------|---------|-----------------------------------------------------|----|--|--|

|   | 1.1        | From    | Machine Learning to Reservoir Computing             | 1  |  |  |

|   |            | 1.1.1   | Machine Learning Algorithms                         | 2  |  |  |

|   |            | 1.1.2   | Artificial Neural Networks                          | 4  |  |  |

|   |            | 1.1.3   | Reservoir Computing                                 | 7  |  |  |

|   |            | 1.1.4   | Benchmark Tasks                                     | 12 |  |  |

|   | 1.2        | Hardw   | vare Implementations: Opto-Electronic Delay Systems | 15 |  |  |

|   |            | 1.2.1   | Time-Multiplexing                                   | 16 |  |  |

|   |            | 1.2.2   | Conceptual Setup                                    | 17 |  |  |

|   |            | 1.2.3   | Desynchronisation                                   | 19 |  |  |

|   |            | 1.2.4   | Experimental Setup                                  | 19 |  |  |

|   | 1.3        | Field-  | Programmable Gate Arrays                            | 24 |  |  |

|   |            | 1.3.1   | History                                             | 24 |  |  |

|   |            | 1.3.2   | Market and Applications                             | 27 |  |  |

|   |            | 1.3.3   | Xilinx Virtex 6: Architecture and Operation         | 28 |  |  |

|   |            | 1.3.4   | Design Flow and Implementation Tools                | 30 |  |  |

|   | References |         |                                                     |    |  |  |

| 2 | Onli       | ine Tra | ining of a Photonic Reservoir Computer              | 39 |  |  |

|   | 2.1        |         | uction                                              | 39 |  |  |

|   | 2.2        | Equali  | isation of Non-stationary Channels                  | 41 |  |  |

|   |            | 2.2.1   | Influence of Channel Model Parameters               |    |  |  |

|   |            |         | on Equaliser Performance                            | 41 |  |  |

|   |            | 2.2.2   | Slowly Drifting Channel                             | 42 |  |  |

|   |            | 2.2.3   | Switching Channel                                   | 42 |  |  |

|   | 2.3        | Online  | e Training                                          | 43 |  |  |

|   |            | 2.3.1   | Gradient Descent Algorithm                          | 44 |  |  |

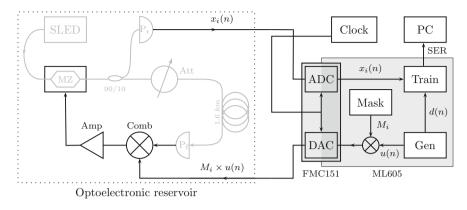

|   | 2.4        | Experi  | imental Setup                                       | 45 |  |  |

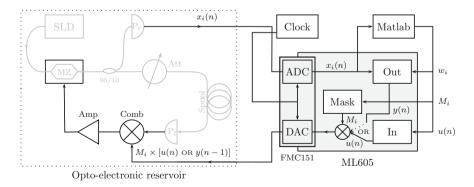

|   |            | 2.4.1   | Input and Readout                                   | 46 |  |  |

|   |      | 2.4.2     | Experimental Parameters                            | 47 |

|---|------|-----------|----------------------------------------------------|----|

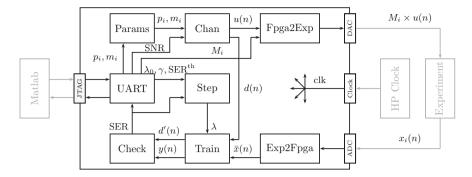

|   |      | 2.4.3     | Experiment Automation                              | 48 |

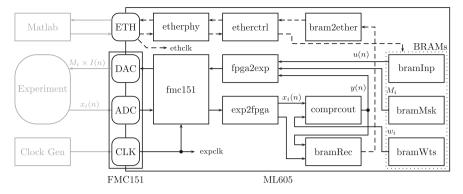

|   | 2.5  | FPGA      | Design                                             | 48 |

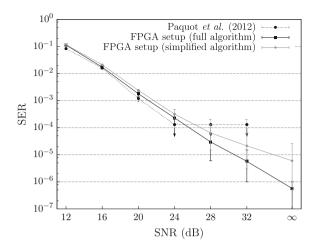

|   | 2.6  | Results   | -<br>3                                             | 51 |

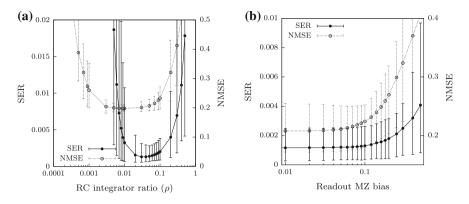

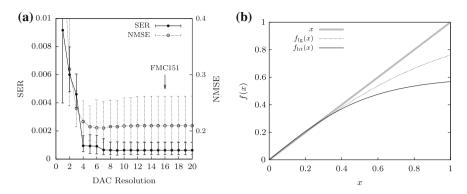

|   |      | 2.6.1     | Improved Equalisation Error Rate                   | 51 |

|   |      | 2.6.2     | Simplified Training Algorithm                      | 53 |

|   |      | 2.6.3     | Equalisation of a Slowly Drifting Channel          | 54 |

|   |      | 2.6.4     | Equalisation of a Switching Channel                | 55 |

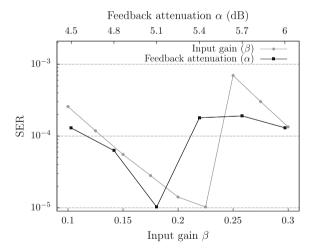

|   |      | 2.6.5     | Influence of Channel Model Parameters on Equaliser |    |

|   |      |           | Performance                                        | 57 |

|   | 2.7  |           | nges and Solutions                                 | 59 |

|   | 2.8  | Conclu    | sion                                               | 60 |

|   | Refe | erences . |                                                    | 61 |

| 3 | Bac  | kpropag   | ation with Photonics                               | 63 |

|   | 3.1  |           | iction                                             | 63 |

|   | 3.2  |           | opagation Through Time                             | 64 |

|   |      | 3.2.1     | General Idea and New Notations                     | 65 |

|   |      | 3.2.2     | Setting Up the Problem                             | 66 |

|   |      | 3.2.3     | Output Mask Gradient                               | 68 |

|   |      | 3.2.4     | Input Mask Gradient                                | 69 |

|   |      | 3.2.5     | Multiple Inputs/Outputs                            | 72 |

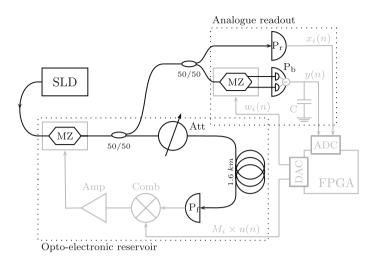

|   | 3.3  | Experii   | mental Setup                                       | 73 |

|   |      | 3.3.1     | Online Multiplication Using Cascaded MZMs          | 75 |

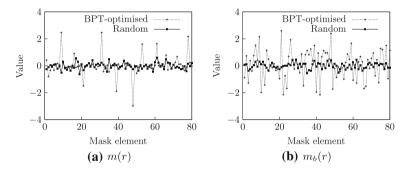

|   |      | 3.3.2     | Mask Parametrisation                               | 77 |

|   | 3.4  | FPGA      | Design                                             | 78 |

|   | 3.5  |           | 3                                                  | 80 |

|   |      | 3.5.1     | Tasks                                              | 80 |

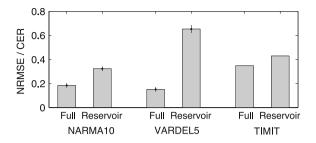

|   |      | 3.5.2     | NARMA10 and VARDEL5                                | 81 |

|   |      | 3.5.3     | TIMIT                                              | 83 |

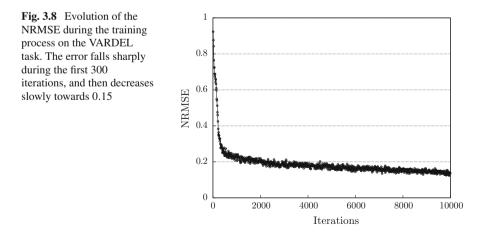

|   |      | 3.5.4     | Gradient Descent                                   | 84 |

|   |      |           | Robustness                                         | 85 |

|   | 3.6  |           | nges and Solutions                                 | 86 |

|   | 3.7  |           | sion                                               | 87 |

|   | Refe | erences . |                                                    | 88 |

| 4 | Pho  | tonic Re  | eservoir Computer with Output Feedback             | 91 |

|   | 4.1  |           | ction                                              | 91 |

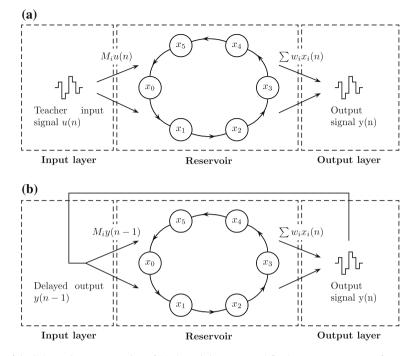

|   | 4.2  |           | oir Computing with Output Feedback                 | 93 |

|   | 4.3  |           | Series Generation Tasks                            | 95 |

|   |      |           | Frequency Generation                               | 95 |

|   |      |           | Random Pattern Generation                          | 95 |

|   |      | 4.3.3     | Mackey-Glass Chaotic Series Prediction             | 96 |

|   |      | 4.3.4     | Lorenz Chaotic Series Prediction                   | 96 |

| <ul> <li>4.5 FPGA Design</li></ul>                                                                                                                                                                                                                                               | · · · · 10<br>· · · · 10<br>· · · · 10<br>· · · · 10<br>· · · · 10                                                                                                                                                                                                                                                                                 | 98<br>01<br>01<br>01                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| <ul> <li>4.7 Results</li></ul>                                                                                                                                                                                                                                                   | · · · · 10<br>· · · · 10<br>· · · · 10<br>· · · · 10                                                                                                                                                                                                                                                                                               | 01<br>01                                                             |

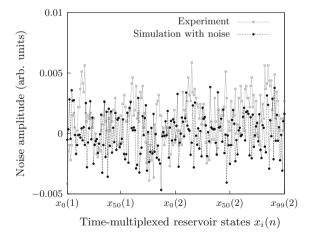

| <ul> <li>4.7.1 Noisy Reservoir.</li> <li>4.7.2 Frequency Generation</li> <li>4.7.3 Random Pattern Generation</li> <li>4.7.4 Mackey-Glass Series Prediction</li> </ul>                                                                                                            | 10<br>10<br>10                                                                                                                                                                                                                                                                                                                                     | 01                                                                   |

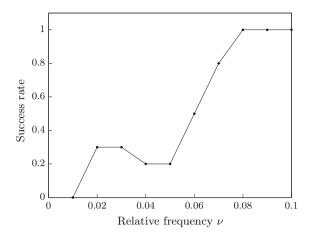

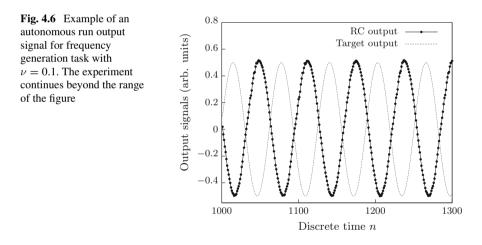

| <ul> <li>4.7.2 Frequency Generation</li></ul>                                                                                                                                                                                                                                    | 10<br>10                                                                                                                                                                                                                                                                                                                                           |                                                                      |

| 4.7.3Random Pattern Generation4.7.4Mackey-Glass Series Prediction                                                                                                                                                                                                                | 10                                                                                                                                                                                                                                                                                                                                                 | 02                                                                   |

| 4.7.4 Mackey-Glass Series Prediction                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                    | 03                                                                   |

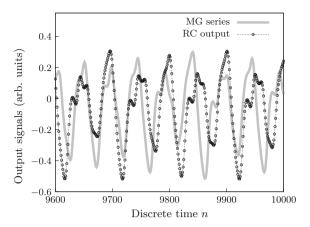

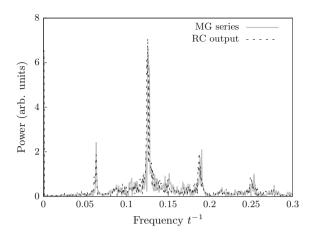

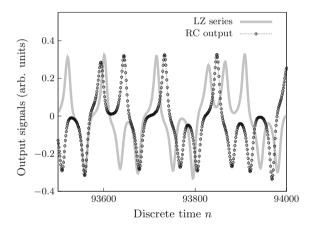

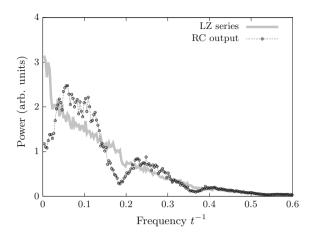

| •                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                    | 05                                                                   |

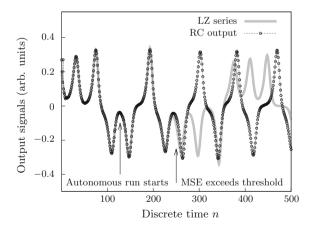

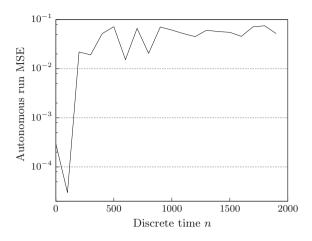

| 4.7.5 Lorenz Series Prediction                                                                                                                                                                                                                                                   | 10                                                                                                                                                                                                                                                                                                                                                 | 08                                                                   |

|                                                                                                                                                                                                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                  | 12                                                                   |

| 4.8 Challenges and Solutions                                                                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                                  | 16                                                                   |

| 4.9 Conclusion                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                    | 17                                                                   |

| References                                                                                                                                                                                                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                  | 19                                                                   |

| 5 Towards Online-Trained Analogue Readout Layer                                                                                                                                                                                                                                  | 1/                                                                                                                                                                                                                                                                                                                                                 | 23                                                                   |

| 5.1 Introduction                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                    | 23<br>24                                                             |

|                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                    | 24<br>25                                                             |

| <ul><li>5.2 Methods</li><li>5.3 Proposed Experimental Setup</li></ul>                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                    | 25<br>25                                                             |

| 5.3.1 Analogue Readout Layer                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                    | 25<br>25                                                             |

| 5.3.2 FPGA Board                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                    | 23<br>27                                                             |

| 5.4 Numerical Simulations                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                    | 27<br>28                                                             |

|                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                    | 20<br>30                                                             |

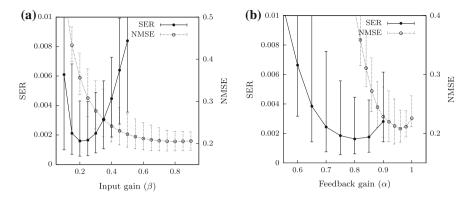

| 5.5 Results                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                    | 30<br>30                                                             |

|                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                    |                                                                      |

|                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                    | 32<br>24                                                             |

| 5.6 Conclusion                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                    | 34<br>34                                                             |

|                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                    | 54                                                                   |

|                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                    |                                                                      |

| 6 Real-Time Automated Tissue Characterisation for Intravascula                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                    |                                                                      |

| OCT Scans                                                                                                                                                                                                                                                                        | 1.                                                                                                                                                                                                                                                                                                                                                 | 37                                                                   |

| OCT Scans                                                                                                                                                                                                                                                                        | 1.<br>1.                                                                                                                                                                                                                                                                                                                                           | 37                                                                   |

| OCT Scans         6.1 Introduction         6.2 Feature Extraction                                                                                                                                                                                                                | 11<br>11<br>14                                                                                                                                                                                                                                                                                                                                     | 37<br>43                                                             |

| OCT Scans         6.1 Introduction         6.2 Feature Extraction         6.2.1 GLCM Features                                                                                                                                                                                    | · · · · 11<br>· · · · 11<br>· · · · 14<br>· · · · 14                                                                                                                                                                                                                                                                                               | 37<br>43<br>43                                                       |

| OCT Scans         6.1 Introduction         6.2 Feature Extraction         6.2.1 GLCM Features         6.2.2 Methods                                                                                                                                                              | · · · · 11<br>· · · · 12<br>· · · · 14<br>· · · · 14<br>· · · · 14                                                                                                                                                                                                                                                                                 | 37<br>43<br>43<br>46                                                 |

| OCT Scans         6.1 Introduction         6.2 Feature Extraction         6.2.1 GLCM Features         6.2.2 Methods         6.2.3 Operation Principle                                                                                                                            | 12            14            14            14            14            14            14            14            14                                                                                                                                                                                                                                 | 37<br>43<br>43<br>46<br>47                                           |

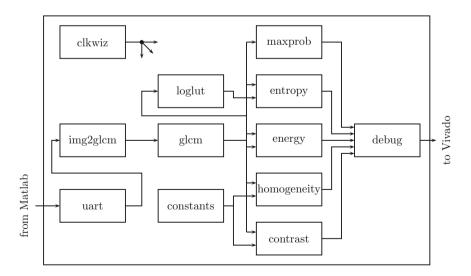

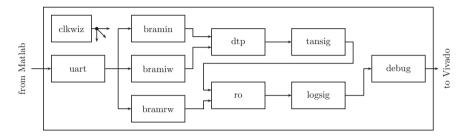

| OCT Scans6.1 Introduction6.2 Feature Extraction6.2.1 GLCM Features6.2.2 Methods6.2.3 Operation Principle6.2.4 FPGA Design                                                                                                                                                        | 12            14            14            14            14            14            14            14            14            14            14            14                                                                                                                                                                                       | 37<br>43<br>46<br>47<br>48                                           |

| OCT Scans6.1 Introduction6.2 Feature Extraction6.2.1 GLCM Features6.2.2 Methods6.2.3 Operation Principle6.2.4 FPGA Design6.2.5 Results                                                                                                                                           | 12            14            14            14            14            14            14            14            14            14            14            14            14            14                                                                                                                                                           | 37<br>43<br>43<br>46<br>47                                           |

| OCT Scans6.1 Introduction6.2 Feature Extraction6.2.1 GLCM Features6.2.2 Methods6.2.3 Operation Principle6.2.4 FPGA Design                                                                                                                                                        | 12            14            14            14            14            14            14            14            14            14            14            14            14            14            12            12                                                                                                                               | 37<br>43<br>46<br>47<br>48<br>50<br>51                               |

| OCT Scans6.1 Introduction6.2 Feature Extraction6.2.1 GLCM Features6.2.2 Methods6.2.3 Operation Principle6.2.4 FPGA Design6.2.5 Results                                                                                                                                           | 12            14            14            14            14            14            14            14            14            14            14            14            14            14            12            12                                                                                                                               | 37<br>43<br>46<br>47<br>48<br>50                                     |

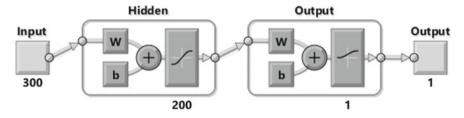

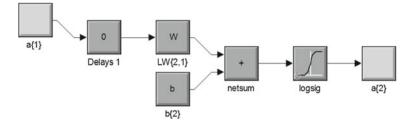

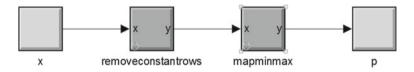

| OCT Scans6.1 Introduction6.2 Feature Extraction6.2.1 GLCM Features6.2.2 Methods6.2.3 Operation Principle6.2.4 FPGA Design6.2.5 Results6.2.6 Perspectives6.3 Artificial Neural Network6.3.1 Network Structure                                                                     | 12          14          14          14          14          14          14          14          14          14          14          14          14          12          12          12          12          12                                                                                                                                     | 37<br>43<br>43<br>46<br>47<br>48<br>50<br>51<br>51<br>51             |

| OCT Scans6.1 Introduction6.2 Feature Extraction6.2.1 GLCM Features6.2.2 Methods6.2.3 Operation Principle6.2.4 FPGA Design6.2.5 Results6.2.6 Perspectives6.3 Artificial Neural Network6.3.1 Network Structure6.3.2 Methods                                                        | 12          14          14          14          14          14          14          14          14          14          14          14          14          14          14          15          15          15          15                                                                                                                         | 37<br>43<br>46<br>47<br>48<br>50<br>51<br>51<br>51<br>55             |

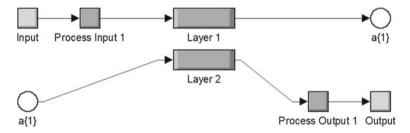

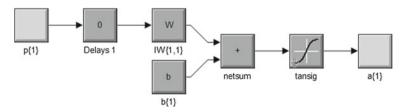

| OCT Scans6.1 Introduction6.2 Feature Extraction6.2.1 GLCM Features6.2.2 Methods6.2.3 Operation Principle6.2.4 FPGA Design6.2.5 Results6.2.6 Perspectives6.3 Artificial Neural Network6.3.1 Network Structure6.3.2 Methods6.3.3 Operation Principle                               | 12          14          14          14          14          14          14          14          14          14          14          14          15          15          15          15          15          15          15          15                                                                                                             | 37<br>43<br>46<br>47<br>48<br>50<br>51<br>51<br>51<br>55<br>55       |

| OCT Scans6.1 Introduction6.2 Feature Extraction6.2.1 GLCM Features6.2.2 Methods6.2.3 Operation Principle6.2.4 FPGA Design6.2.5 Results6.2.6 Perspectives6.3 Artificial Neural Network6.3.1 Network Structure6.3.2 Methods                                                        | 12          14          14          14          14          14          14          14          14          14          14          15          15          15          15          15          15          15          15          15          15          15          15                                                                         | 37<br>43<br>46<br>47<br>48<br>50<br>51<br>51<br>51<br>55<br>56<br>56 |

| OCT Scans6.1 Introduction6.2 Feature Extraction6.2.1 GLCM Features6.2.2 Methods6.2.3 Operation Principle6.2.4 FPGA Design6.2.5 Results6.2.6 Perspectives6.3 Artificial Neural Network6.3.1 Network Structure6.3.2 Methods6.3.3 Operation Principle6.3.4 FPGA Design6.3.5 Results | 12          14          14          14          14          14          14          14          14          14          14          14          15          15          15          15          15          15          15          15          15          15          15          15          15          15          15                         | 37<br>43<br>46<br>47<br>48<br>50<br>51<br>51<br>51<br>55<br>55       |

| OCT Scans6.1 Introduction6.2 Feature Extraction6.2.1 GLCM Features6.2.2 Methods6.2.3 Operation Principle6.2.4 FPGA Design6.2.5 Results6.2.6 Perspectives6.3 Artificial Neural Network6.3.1 Network Structure6.3.2 Methods6.3.3 Operation Principle6.3.4 FPGA Design              | 12          14          14          14          14          14          14          14          14          14          14          14          15          15          15          15          15          15          15          15          15          15          15          15          15          15          15          15          15 | 37<br>43<br>46<br>47<br>48<br>50<br>51<br>51<br>51<br>55<br>56<br>56 |

| 7  | Conclusion and Perspectives | 161 |

|----|-----------------------------|-----|

|    | References                  | 166 |

| Aι | Ithor's Curriculum Vitae    | 167 |

# Chapter 1 Introduction

In this chapter we will address three questions: (1) What is reservoir computing? (2) What does it have to do with optics and electronics? (3) What are FPGAs? That is a lot of information to cover, so let us get started right away!

#### 1.1 From Machine Learning to Reservoir Computing

Reservoir computing—what a peculiar concept! Are we talking about a bucket of water performing computations? The idea may seem weird, but...it is actually not far from reality! In fact, there has been an experiment carried out in a water tank, where ripples on the surface of water were sampled and used to process information [1]. But this is not exactly what reservoir computing is all about. Attributed to the machine learning (ML) field—a subfield of computer science [2–6] that studies data processing algorithms capable of learning from the data itself—reservoir computing is not an algorithm per se, but rather a set of ideas that significantly simplify another algorithm and make it more suitable for practical applications. This other algorithm, or, rather, a class of algorithms, is called artificial neural networks. To understand the whole story, we need a general overview of the said machine learning field.<sup>1</sup> The goal of this section is thus to present to the reader the bigger picture, following a topdown approach. We will start with an overview of machine learning, with some basic ideas and several examples. Then, we will dive into artificial neural networks, again leaving aside most of unnecessary technical details. Finally, within neural networks we will finally introduce the RC paradigm, now with all mathematical details needed to understand how it works.

<sup>&</sup>lt;sup>1</sup>This is obviously a debatable point. But it did work for me—my true revelation on reservoir computing, how and why it works, happened when I saw what is around-so I am going to stick to this plan.

<sup>©</sup> Springer International Publishing AG, part of Springer Nature 2018

P. Antonik, Application of FPGA to Real-Time Machine Learning,

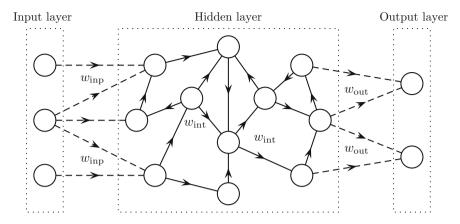

Fig. 1.1 Map of the machine learning field. Far from being the most exhaustive, it is sufficient to show what algorithms, or classes of algorithms can be found out there. Figure inspired by the Mindmap from Machine Learning Mastery

#### 1.1.1 Machine Learning Algorithms

ML enjoys a fast evolution in these days, as people are desperately looking for methods to efficiently process the huge amounts of data coming from everywhere, and ML offers several very promising solutions [7–12]. Figure 1.1 draws a more or less complete picture of the machine learning field. Here we will overview a few of these methods (the most popular ones) with their basic properties and applications, obviously simplifying the details to the bare minimum. The goal here is not to review the machine learning field, but to give the reader a broad view of the algorithms that can be found there.

- **Decision trees:** Commonly used in statistics and data mining, decision trees are predictive models for data classification based on its properties [7, 9, 13, 14]. In a simple decision tree, the leaves are labelled with all possible classes. On its way from the root to leaves, the input instances "travel" through decision nodes (where branches of the tree split), where data parameters define the following path.

- **Bayesian networks:** A Bayesian network is a probabilistic graphical modelling technique used in computational biology, bioinformatics, medicine, engineering, and many other domains [10, 15, 16]. A directed acyclic graph represents the data as a set of variables and their conditional dependencies, which allows to draw probabilistic relationships between data features.

- **k-nearest neighbour:** Instance-based algorithms, such as k-nearest neighbour [17–19], typically build a database of examples and compare the incoming data using a certain similarity metric in order to find the best match and make a prediction. They are often used for dimension reduction, i.e. removing unnecessary redundancies from very large sets of data.

- **Support vector machines:** Commonly employed as linear classifiers for e.g. text or image processing, SVMs [20–23] map the input data into a high-dimensional space, using specific algorithms, where different classes can be separated (clustered) by a set of hyperplanes.

- **Artificial neural networks**: Family of models, inspired by biological neural networks, used to estimate or approximate (generally unknown) functions depending on a large number of inputs [24–27]. They come in different shapes and flavours, and besides data processing, they are also used in neuroscience.

- **Deep learning:** A class of ML algorithms that cascade multiple information processing layers, each successive layer receiving the output of the previous one as input [28–31]. The layers learn multiple levels of data representation, that correspond to different levels of abstraction, and form together an hierarchy of concepts. The most successful deep learning methods involve neural networks and have shown breathtaking results in speech and image recognition, natural language processing, drug discovery and recommendation systems. Other less known deep architectures exist, such as multilayer kernel machines.

To process data, these algorithms need to be trained—in other words, taught what to do with the data. Remember, ML algorithms are not designed to perform well on a particular dataset, but rather to execute a certain versatile task. The training serves to fine-tune the algorithm for better performance on the dataset of interest. The training can be done using various techniques, commonly grouped into categories, based on their action principle.

- **Supervised learning:** The algorithm is presented with a labelled dataset, that is, where the output is known for each input, such as spam/not-spam classification or a set of tagged images [32, 33]. During the training process, the model is tuned to correctly classify all the inputs, and then tested on a new set of data, that was not used for training. This process is carried on until a desired level of accuracy is achieved on the test set.

- **Reinforcement learning**: Inspired by behavioural psychology, this methods is employed when the corrects outputs or labels are unavailable [34, 35]. Instead, the algorithm is supplied with a reward (or error) function and then optimised to maximise (or minimise) it. Such approach is commonly used in robotics, where exact movement patterns of different motors or actuators are unknown, and the robot is trained to optimise the reward function, given by e.g. the distance travelled.

- **Unsupervised learning**: As the name suggests, here the algorithm does not use any labelled dataset nor reward function [5, 36–38]. It is presented with the data alone and is supposed to find an underlying structure or some hidden insights. This case is the hardest to understand, as it looks like some kind of dark magic. Since I have never used such methods, we shall leave the details aside. A typical example of unsupervised learning is clustering, that is, the task of grouping a set of objects by similarity.

Other approaches exist, such as semi-supervised learning [39], but they lie beyond the scope of this introductory overview.

To sum up this section, numerous machine learning algorithms exist, based on various approaches and suited for different tasks. To process data, they need to be trained first, and this can also be done in various ways, depending on the task and the type of data available. Among all the methods lies the family of artificial neural networks. And since reservoir computing has something to do with neural networks, let us discuss them in detail in the next section.

#### 1.1.2 Artificial Neural Networks

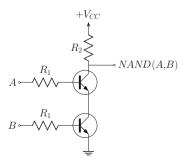

The first model of artificial neural networks (ANN), introduced in 1943 [40] split the research in two distinct approaches: the study of actual biological processes in the brain on one side, and application of neural networks to machine learning. The research stagnated after the discovery of a fatal flaw: basic neural networks (also known as perceptrons—we will introduce them very soon) were incapable of processing the basic exclusive-or (XOR) circuit! [41]. On top of that computers did not have enough power to handle large networks on the long run. Later on, the CMOS technology (that lead to an explosion of computational speed) and the novel backpropagation algorithm [42, 43] allowed to efficiently train large multi-layer networks. Recent advances in GPU-based implementations and the emergence of highly complex, deep neural networks made this approach very popular and brought breathtaking results in e.g. speech or text recognition and novel drug discovery.

Let us take a look inside those networks. They are composed of elementary computation units—neurons. A biological neuron is a cell capable of producing a rapid train of electric spikes. Its complex internal dynamics can be described by the well-known Hodgkin-Huxley model [44] that takes into account the exact three-dimensional morphology of the cell. Simulating such a precise model is extremely demanding in computational power, and so is, although of great interest for brain research, impractical for real-world applications. For this reason, artificial neurons have been introduced, keeping the spiking behaviour but greatly simplifying the internal dynamics. A plethora of models have been proposed to emulate artificial neurons (see e.g. [45–48]). All of them encode information into spike trains, just as we think biological neurons do. But one can simplify the neuron one step further and remove the spikes at all by defining the average spiking frequency *a*. Such neurons are called analogue neurons and their behaviour is described by the following simple equation

$$a = f\left(\sum w_i s_i\right),\tag{1.1}$$

where *a* is the output of the neuron (that can also be referred to as the current state of the neuron, or the activation),  $s_i$  are the inputs coming from the neighbour neurons in the network,  $w_i$  are the weights of these connections (thus making it possible to create weak or strong connections between neurons), and *f* is the activation function, that describes how the neuron reacts to its inputs. Crucially, this simplification removes

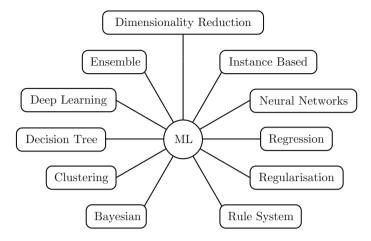

**Fig. 1.2** Example architecture of an artificial neural network. The neurons are grouped in three layers—input, hidden and output—based on their connections with the outside world. The network may contain several hidden layers (this example has only one)

the complex temporal dynamics of the neurons and make discrete-time computations possible. This, in turn, allows to simulate large numbers of neurons with relatively low computational power.

The neurons are gathered in network-like structures with three main characteristics.

- **Architecture:** It defines the size of the network and the connections between the nodes, which in turn defines how they exchange information. An example neural network is sketched in Fig. 1.2. The circles denote the nodes, or the neurons, and the arrows show the connections from the output of a neuron to the input of another. The neurons are commonly categorised into three layers, based on their role in the network. The input layer nodes receive signals from outside and output layer neurons produce output signals of the network. The other neurons, as they cannot be accessed from the outside of the network, are called hidden neurons, and can be grouped into one or several layers. All connections, depicted with arrows, are parametrised with associated weights—input, output or internal—which define the strength of the connections.

- Activation function: The activation function defines the individual behaviour of the neurons, that is, how they respond to input signals. To avoid unconstrained dynamics of the network, the activation function should be bounded, usually within [-1, 1]. The sigmoid function is one of the most popular choices, alongside the so-called linear rectifier function [49]. Other functions, such as hyperbolic tangent or sine, are also used.

- **Tunable weights:** Artificial neural networks are valued for their ability to learn by means of adjusting their weighted connections (input, output or internal). Under supervised learning paradigm, for instance, the network is fed with numerous input instances, and the output is compared to the desired output. Various training

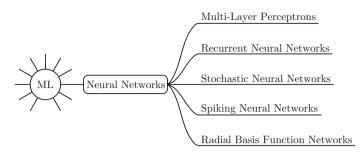

Fig. 1.3 Several examples of neural networks

algorithms can then be used to adjust the weights so that the network output signal matches as closely as possible to the target output.

Artificial neural networks come in many different shapes and flavours. We will limit this introduction to a few notable examples, shown in Fig. 1.3, leaving the complete list to specialised literature [49].

- **Multi-layer perceptron**: A MLP is a feedforward artificial neural network [27, 36, 50]. That is, the information flows in one direction, from input to output neurons (through the hidden ones) with no cycles or loops in the network.<sup>2</sup> Owing to a nonlinear activation function, MLPs are capable of partitioning data that is not linearly separable. They found many applications in speech or image recognition in the 1980s, but have been superseded by much simpler support vector machines (see Sect. 1.1.1) in the 1990s.

- **Recurrent neural network:** Unlike feedforward networks, RNNs are allowed to form directed cycles between neurons, which allows them to exhibit temporal behaviour and adds internal memory [31, 51, 52]. That is, the network can "remember" the previous inputs and its current state is no longer entirely defined by the current input. This makes them a powerful tool that can be applied to digital signal processing, speech and handwriting recognition.

- **Stochastic neural network:** Stochastic networks are built by introducing randomness into the system, either by means of a stochastic transfer function, or by assigning random weights [53, 54]. This makes them suitable for optimisation tasks, as local minima are avoided with these random fluctuations. They have found applications in e.g. bioinformatics and drug discovery.

- **Spiking neural networks:** Spiking neurons increase the level of realism by incorporating the temporal dynamics in their operating principle [55–58]. Similarly to biological neurons, spiking neurons do not produce an output at each update cycle, but rather fire a spike whenever their internal states reaches a certain threshold. They have been used in studies of biological neural circuits, since they can model simple central nervous systems. However, because of the increased computa-

<sup>&</sup>lt;sup>2</sup>Note that the example in Fig. 1.2 does contain several loops.

tional power required to simulate these realistic networks, they are yet to find useful applications in engineering.

Radial basis function networks: A radial basis function is a real-valued function whose values only depend on the distance from the origin. Neural networks, based on these functions, are composed of an input layer, one hidden layer with nonlinear radial basis activation function neurons and a linear output layer [59–61]. Such structures can, in principle, interpolate any continuous function and have been shown to be more advantageous on complex pattern classification problems. Mathematical proofs and further details can be found in [49].

This concludes our brief overview of machine learning and artificial neural networks. Let me say again that the purpose of this introduction was not to turn the reader into expert in machine learning, but merely show the general context of this work. In the next section we will focus on the main topic of interest—reservoir computing—with much more in-depth discussions.

#### 1.1.3 Reservoir Computing

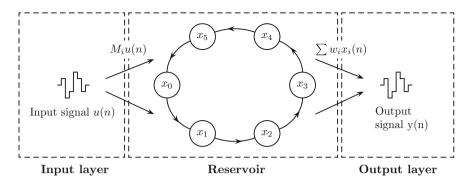

Reservoir Computing (RC) is a set of machine learning methods for designing and training artificial neural networks, introduced independently in [62] and in [63]. The idea behind these techniques is that one can exploit the dynamics of a recurrent nonlinear network to process time series without training the network itself, but simply adding a general linear readout layer and only training the latter. This results in a system that is significantly easier to train (since one only needs to optimise the readout weights), yet powerful enough to match other algorithms on a series of benchmark tasks.

These ideas can be applied to both recurrent and spiking recurrent neural networks, which gave birth to two concepts called Echo State Networks (ESN) [64] and Liquid State Machines (LSM) [63], that are grouped under the reservoir computing paradigm. An ESN is a sparsely connected, fixed RNN with random input and internal connections. The neurons of the hidden layer, commonly referred to as the reservoir, exhibit nonlinear response to the input signal due to a nonlinear activation function (hyperbolic tangent seems to be the most common choice). Liquid state machines rely on the same concept, but the reservoir consists of a "soup" of spiking neurons. The name "liquid" comes from an analogy to ripples on the surface of a liquid created by a falling object. Interestingly, this concept has actually been implemented in hardware, that is, as the name suggests…in a tank full of water! [1].

For hardware reasons, as will become clear in Sect. 1.2, in this work we will only deal with analogue neurons, leaving the spiking models aside. From now on, to simplify the ideas, I will make no distinction between Echo State Networks and Reservoir Computing.

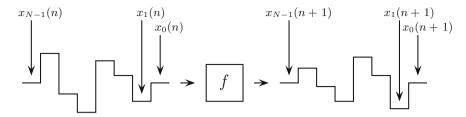

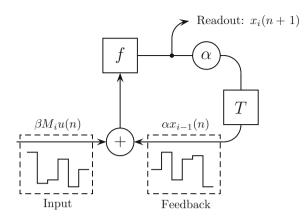

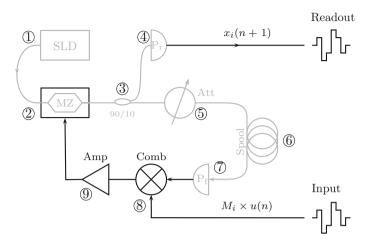

It is now time to introduce the math used describe the dynamics of a reservoir computer. Let us denote the neurons (also called nodes, or internal variables of the reservoir)  $x_i$ . As they are analogue neurons (see Sect. 1.1.2), we may consider that they evolve in discrete time  $n \in \mathbb{Z}$ , so we note them  $x_i(n)$ . The index *i* goes from 0 to N - 1, with N being the reservoir size, or the number of neurons in the network. To fix the ideas, let us consider N = 50, since this is a value commonly used in experiments. Remember Eq. 1.1 giving the output of an analogue neuron? The evolution equation of a reservoir node is fairly similar and given by

$$x_i(n+1) = f\left(\sum_{j=0}^{N-1} a_{ij} x_j(n) + b_i u(n)\right),$$

(1.2)

where f remains the nonlinear activation function, u(n) is the external input signal that is injected into the system, and  $a_{ij}$  and  $b_i$  are time-independent coefficients that determine the dynamics of the reservoir. Specifically,  $a_{ij}$  is called the interconnection matrix, since it defines the strengths of connections between all the neurons within the reservoir, with 1 being the strongest connection, and 0 meaning no connection. The vector  $b_i$  contains the input weights and defines how strong is the input to each neuron. These coefficients are usually drawn from a random distribution with zero mean. As an alternative point of view, this equation can be expressed as follows

Future state of the i-th neuron = Nonlinear

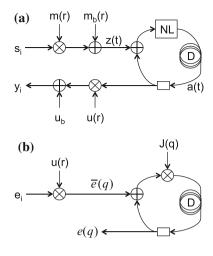

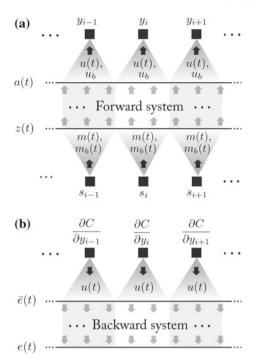

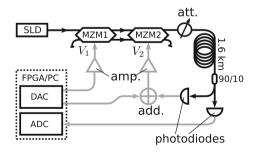

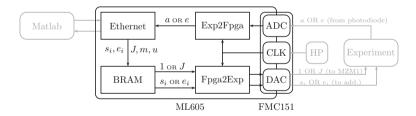

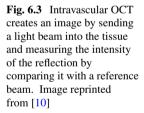

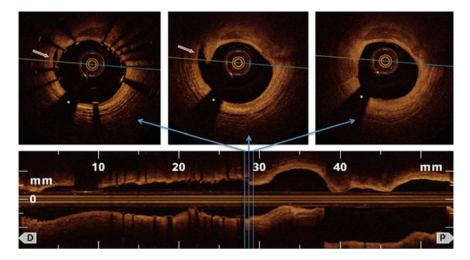

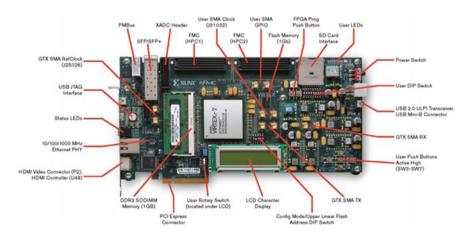

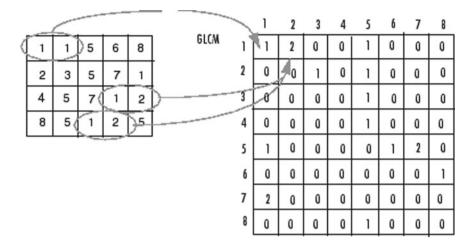

$$\begin{pmatrix} Previous states of \\ connected neurons \end{pmatrix}$$