Your complete and practical guide to understanding and utilizing modern electronics!

ITURE

-K

g

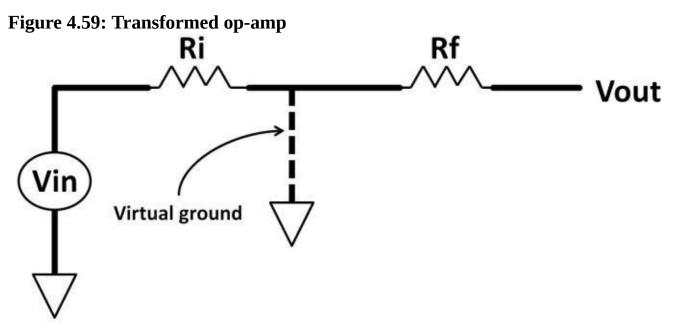

YOU'RE

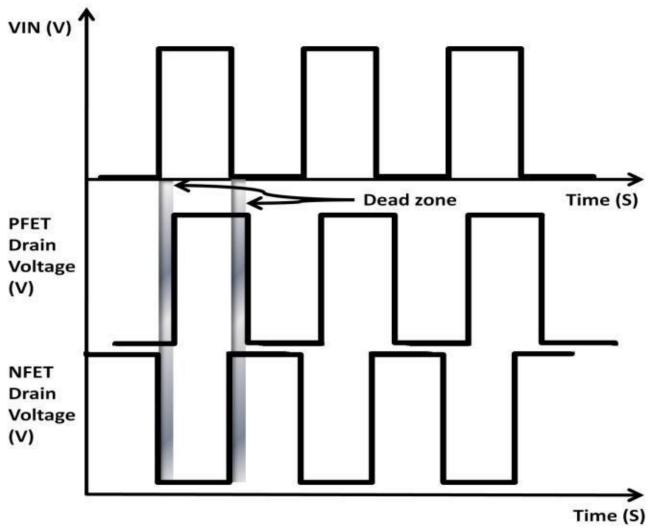

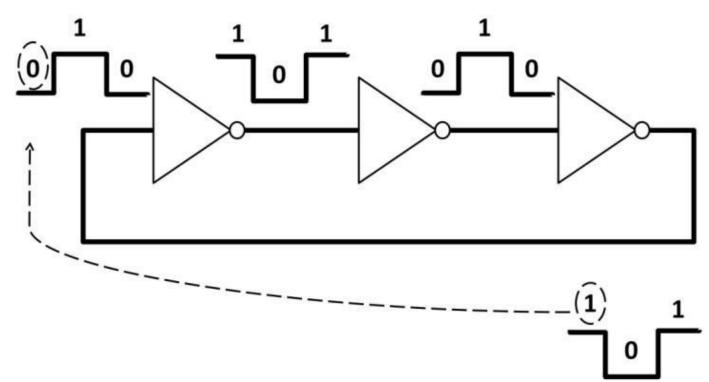

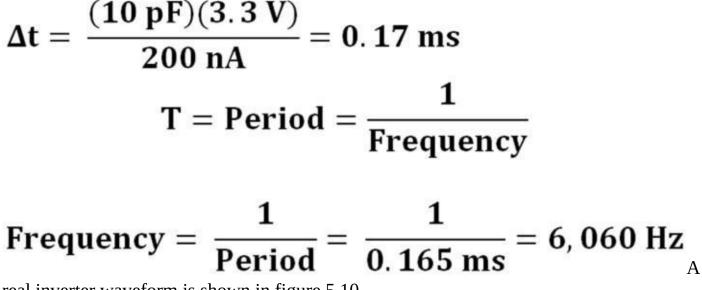

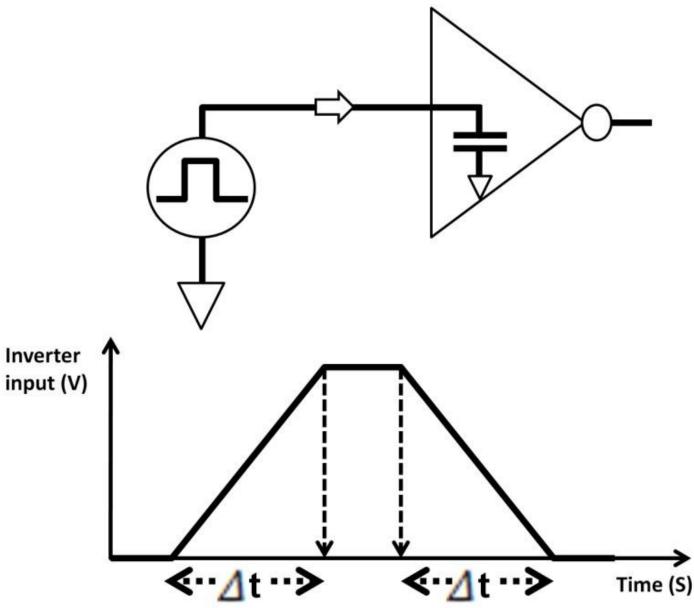

HERE

N- A-V

7

Q

## ALL-IN-ONE ELECTRONICS GUIDE

**Cammen Chan**

6 6

O

0

000

0

à

m

- 2 - 4

## **All-in-One Electronics Guide**

A comprehensive electronics overview for electronics engineers, technicians, students, educators, hobbyists, and anyone else who wants to learn about electronics

#### Your complete practical guide to understanding and utilizing modern electronics! By: Cammen Chan C & C Group of Companies LLC. Published by C & C Group of Companies LLC. Copyright 2015. All rights reserved.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher.

Website: http://www.ALLinOneElectronicsGuide.com E-mail: ALLinOneElectronicsGuide@gmail.com Facebook: http://www.facebook.com/ALLinOneElectronicsGuide Twitter: http://www.twitter.com/ai1\_electronics All trademarks mentioned herein are property of their respective companies.

Book Cover Editor: Flora Gillis Book Editor: Priscilla P. Flores Book Cover Designer: Kristin Fleming http://www.kristinfleming.com/

## ISBN-10: 1479117374 ISBN-13: 978-1479117376 Printed in the United States of America

III

#### About the Author

Cammen Chan has been working in the electronics industry since 1996. After receiving his bachelor of science degree in electronic engineering technology from the Wentworth Institute of Technology and master of science degree in electrical engineering from Boston University, he began his engineering career at IBM Microelectronics, then worked at Analog Devices Inc., National Semiconductor, and several technology startups. He has one US patent invention in the area of nanotechnology. Since 2009, Cammen has also been an adjunct faculty member at a number of US colleges and universities including ITT Technical Institute, DeVry University, Western International University, University of Advancing Technology, Chandler Gilbert Community College, Remington College, and Excelsior College. He teaches electronics engineering technology, information technology, mathematics, and emerging technologies. Cammen has taught all the subjects in this book in various formats such as on-site, online, and blended classes. Currently, Cammen is a technical training engineer at Microchip Technology in the Phoenix area.

IV

#### Introduction

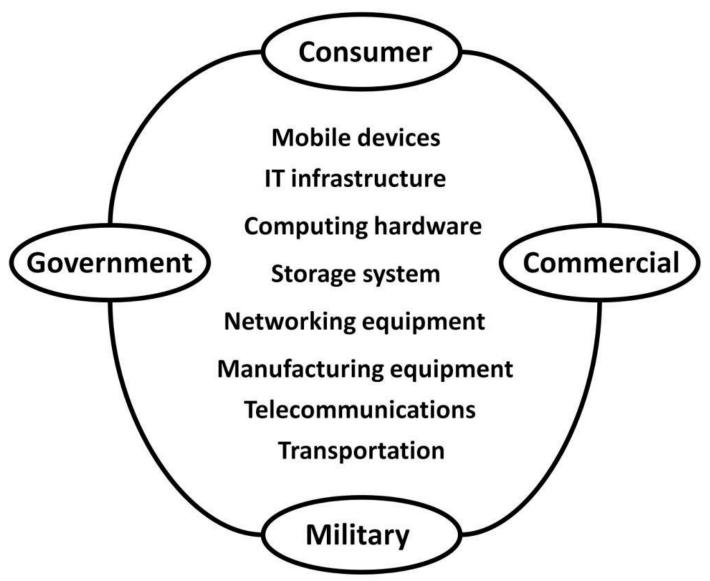

The semiconductor industry is a big business. The electronics industry is even bigger. The semiconductor industry alone was a US \$300 billion plus industry in 2012. The long-term trend of electronics is bright and promising. With increasing use of electronic devices in consumer, commercial, and industrial products and systems, the electronics industry is always growing. If you are considering becoming an electronics engineer, this book gives you the technical skills needed to "pass" the technical parts of interviews and the confidence to increase your chances of getting employed. If you are already an electronics technician or engineer, this book improves your ability to perform at the highest level at work in the electronics field. If you want to be a microelectronics engineer or are already one, you will find the microelectronics-related contents in this book applicable to your work. If you are an educator teaching electronics, this book is the perfect reference for you and your students with step-by-step technical examples and quizzes. If you are an electronics hobbyist, this book offers sampled electronic circuits (electronic components connected with each other by wires or traces) you can apply to your design. For everyone else interested in learning about electronics, this book provides a strong foundation of what you need to know when working with electronics.

The chapters are divided into various electronic principles levels, from basic to advanced, along with practical circuits and quizzes. Answers provide step-by-step explanations of how and why the answers were derived. Examples and circuits in later chapters build upon previous chapters, thus creating a consistent flow of learning and a gradual accumulation of knowledge. The level of mathematics is moderate without tedious and complicated math models and formulas. For students majoring in electrical engineering, this book is more than your typical academic electronics textbook that overwhelms you with excessive theories, formulas, and equations. Instead, the material covered in this book is easy to read, with plenty of diagrams, pictures, waveforms, and graphs, and is easy to understand. Accurately representing our non-ideal world, this book's technical contents greatly differ from most academic textbooks' false "ideal" perspective. The content is injected with real world quantities and characteristics. For experienced electronics professionals, educators, and hobbyists, this book affords a good reality check and comprehensive review to assist your career or your students, to better prepare for your next job interview, and to inspire your next electronics projects.

V

#### How This Book Is Organized

#### Chapter 1: Direct Current (DC)

First, learn direct current (DC) theories. Then, apply them in practical circuits. Basic electrical parameters, concepts, and theories are covered. This chapter closes with practical DC circuits.

#### **Chapter 2: Diodes**

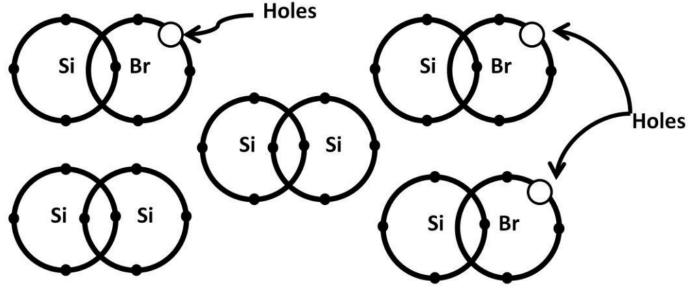

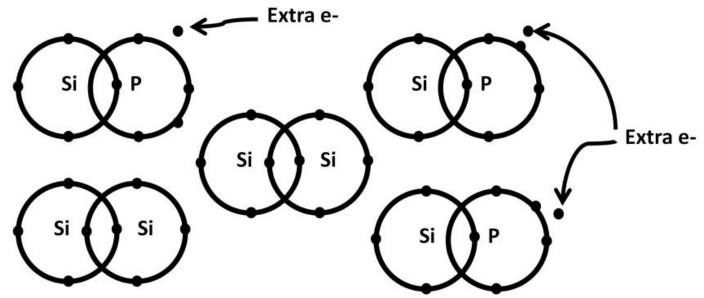

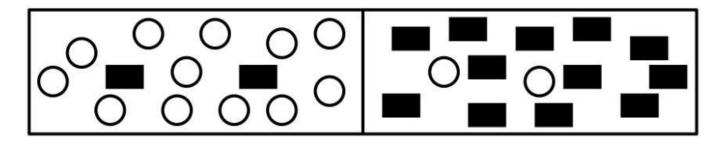

Zero in on diode, the building block of transistors. This chapter explains not only what a diode is made of but also the real world characteristics of diode and some practical diode circuits.

#### **Chapter 3: Alternating Current (AC)**

After comprehending DC and diodes, learn about AC, another critical electronics concept. From high-power electric plants to computers and wireless communications, AC operations take place in countless electronic systems. Get a good hold on AC definitions, common AC parameters, capacitors, inductors, and simple AC circuits.

#### **Chapter 4: Analog Electronics**

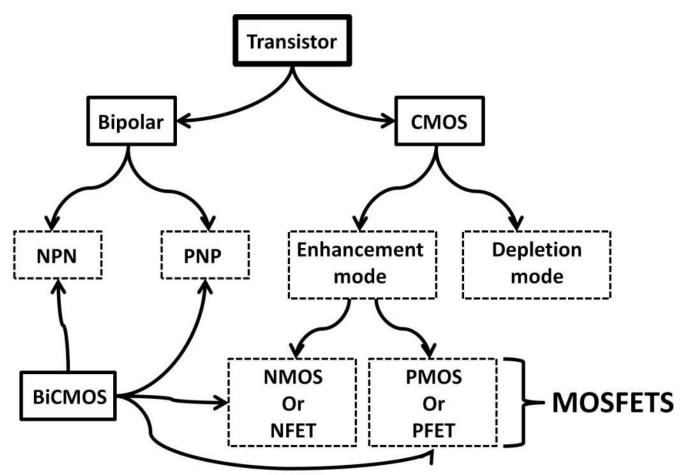

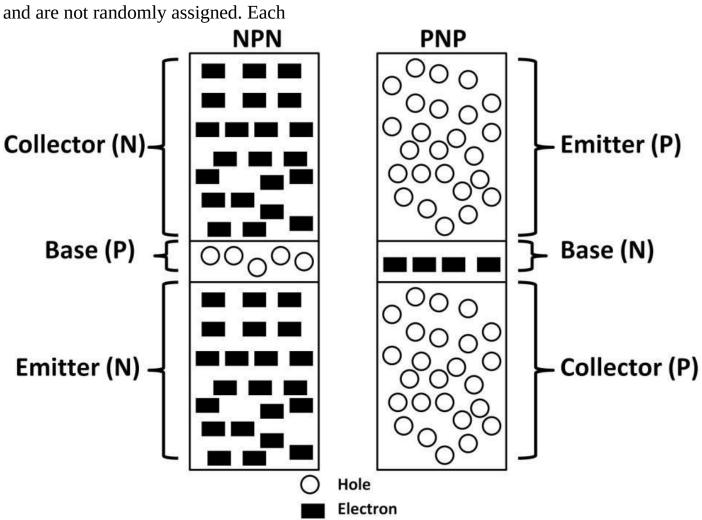

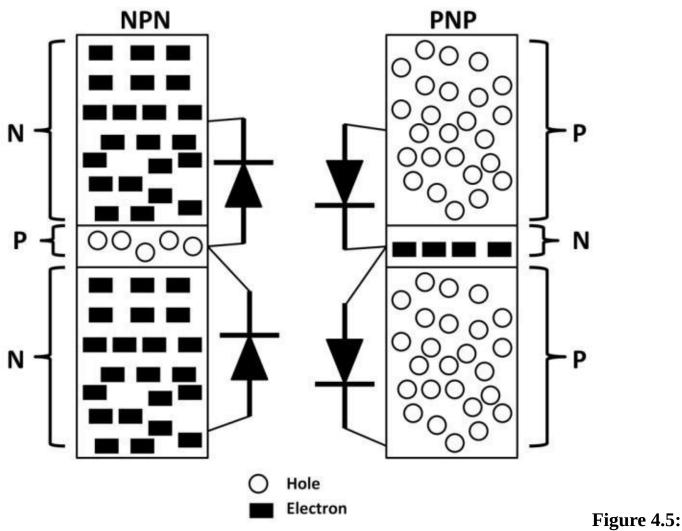

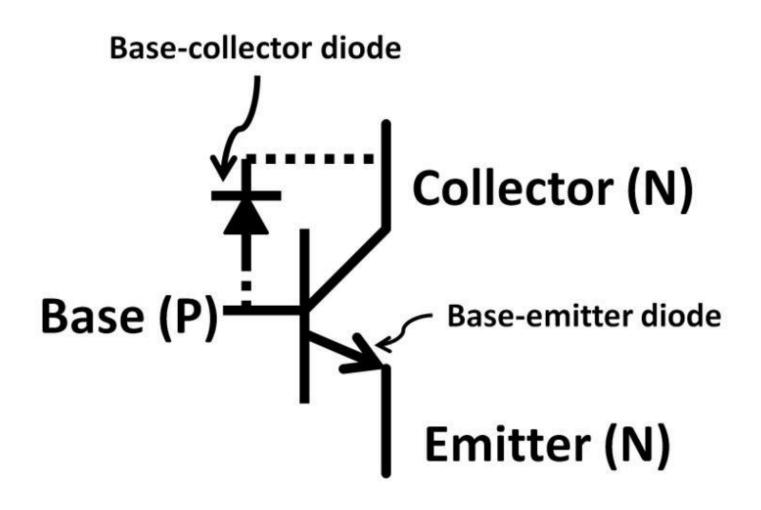

Analog electronics use a substantial amount of analog quantities. Transistors and operational amplifiers (op-amp) are the building blocks of mainstream electronic circuits and systems. Bipolar and Complimentary-Metal-Oxide-Semiconductor (CMOS) are the most common types of transistors. Bipolar transistors consist of two diodes. On the other hand, CMOS does not contain any active diodes. Although germanium, gallium, and arsenide can be used to build transistors, both bipolar and CMOS transistors primarily use silicon as the raw material. Performance differences between raw materials types must be considered to choose the correct transistor type. CMOS and bipolar transistors have similar voltage and current characteristics with major differences in fundamental operation. A solid understanding of these differences is essential for analyzing and designing transistors and op-amp circuits.

#### **Chapter 5: Digital Electronics**

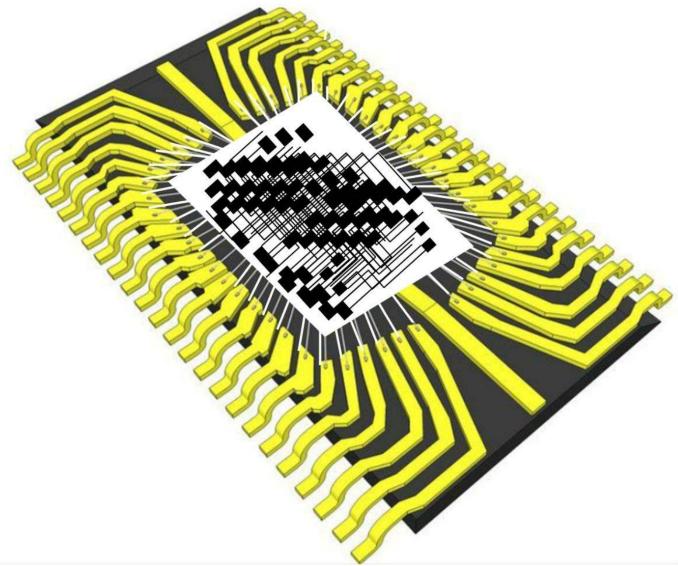

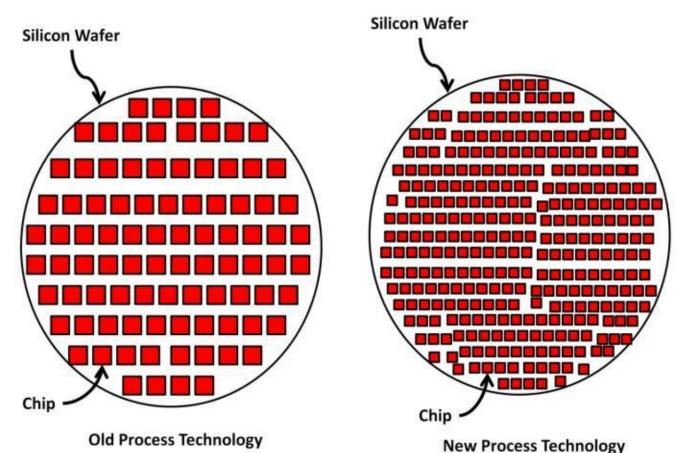

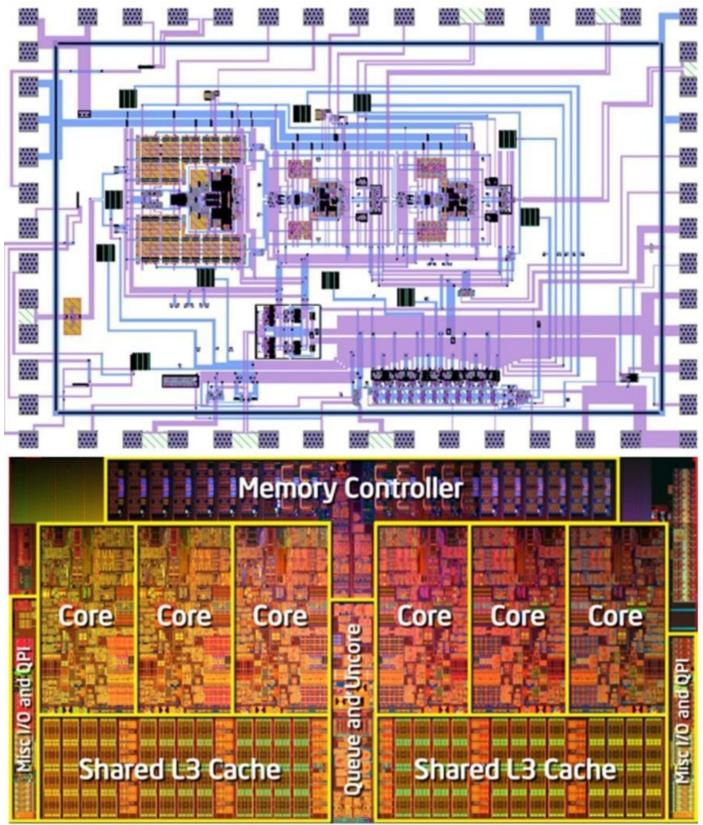

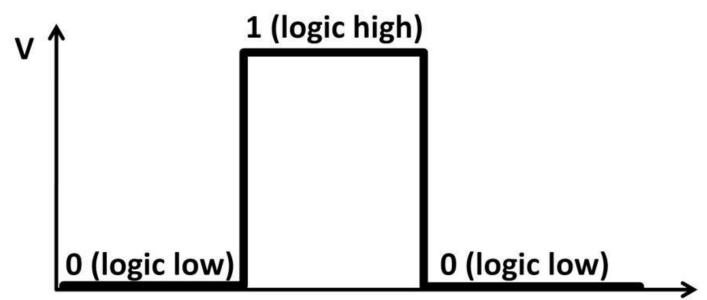

Basic digital electronics require an in-depth understanding of digital quantities, high (1) and low (0) logic level, logic gates, and circuits. It is considerably the best semiconductor technology choice for high-speed design and operations. In comparison to analog quantities, the simple two levels (1 and 0) offer distinct advantages over analog technology such as lower noise. For cost reasons, digital electronics present a good case for using CMOS transistor technology in digital systems. CMOS transistors are made in deep sub-microscopic scale with advanced chip manufacturing capability, while manufacturing throughputs continues to increase exorbitantly. For high speed, high-

density digital designs such as Application Specific Integrated Circuit (ASIC), Field Programmable Gate Array (FPGA), or microprocessors, digital designers often use software to write programs/code for generating CMOS design. Using VHDL or Verilog, instead

#### VI How This Book Is Organized

of manually placing transistors individually in schematics as in analog design, digital circuits are generated to represent the functional and behavioral models and operations of the target CMOS design. In recent years, BiCMOS process has gained popularity. As its name implies, this process combines both bipolar and CMOS devices, offering the best of both.

#### **Chapter 6: Communications**

Electronic communications are technology. It is an enormous businesses. Radios, cell phones, home and business computers connected to the internet by using either wired or wireless connections are just some examples. The vast majority of this technology is only possible due to the advanced development of electronic communication systems. Additionally, amplitude modulation, frequency modulation, and phase locked loops will be discussed in this chapter. Understanding basic communication theories, techniques, and parameters will greatly assist your work in the communications engineering field. the foundation of wired industry with its market and wireless communications

covering both consumers and

#### **Chapter 7: Microcontrollers**

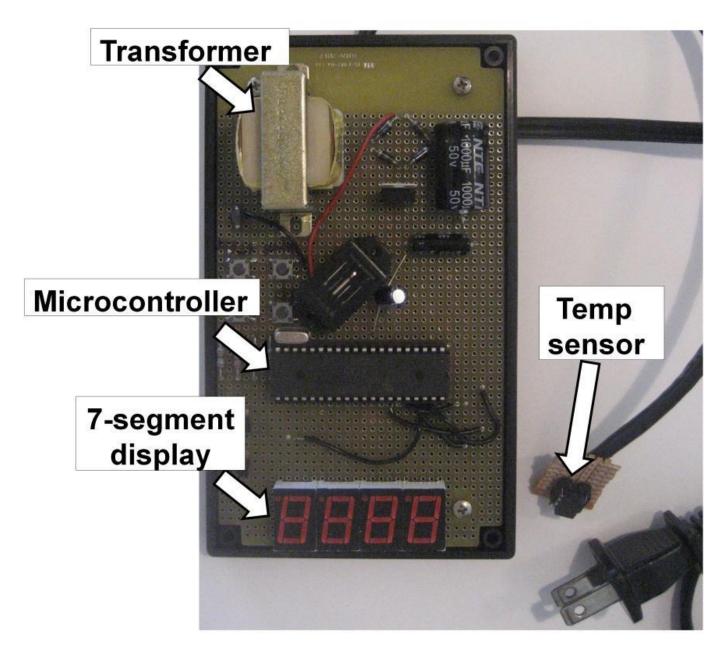

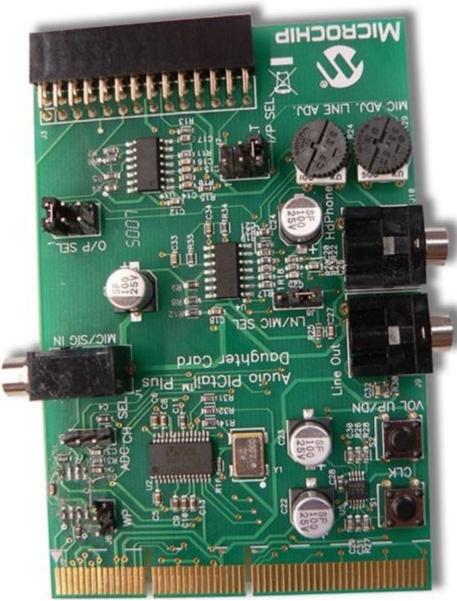

Microcontroller silicon chips have found their way into a variety of electronic products. One automobile alone has an average of eighty microcontrollers controlling the engine, steering wheel controls, GPS, audio systems, power seats, and others. Microcontrollers are embedded in many consumer and industrial electronics including personal computers, TV sets, home appliances, children's toys, motor control, security systems, and many more. The final products that use microcontrollers are embedded systems. These devices are field programmable: they allow system designers to program the chip to the needs of a specific application, while letting end users perform a limited amount of modification. For example, an end user turning on a microwave oven is actually "programming" the timer. However, the end user does not have access to the source code on the microcontroller, hence the name "embedded systems." Moreover, the same microcontroller can be used in multiple designs. For instance, dishwashers and refrigerators use the same microcontroller with each design having its own specific code downloaded to the microcontroller, resulting in two completely different applications. The microcontroller's field programming capabilities allows many applications to be designed at a very low cost. Comprehending microcontroller architecture and basic programming techniques will prepare you to excel in this field.

#### **Chapter 8: Programmable Logic Controllers**

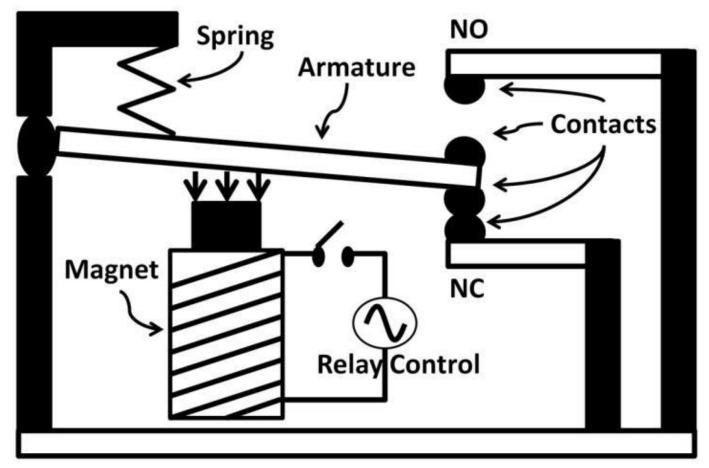

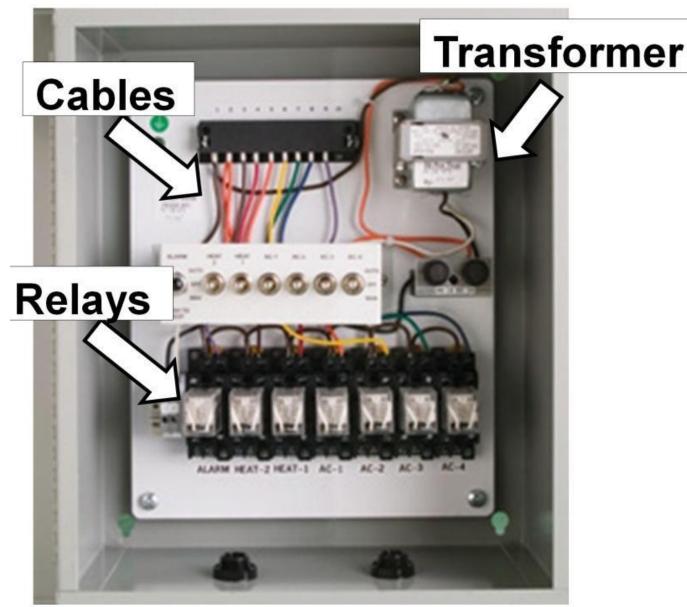

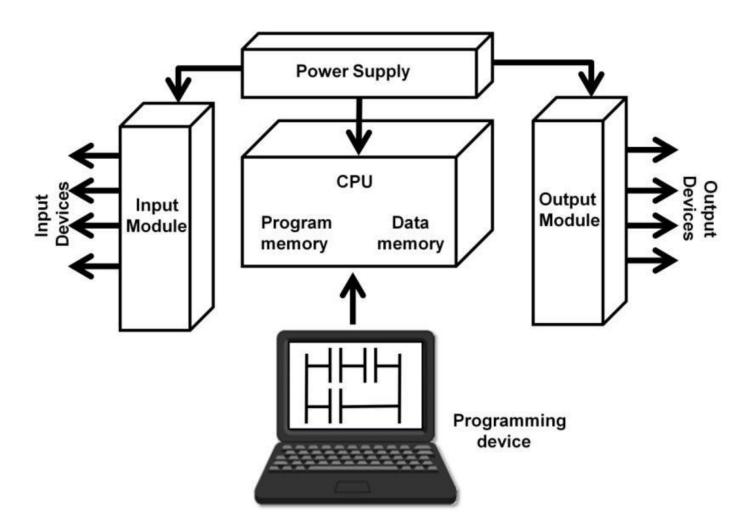

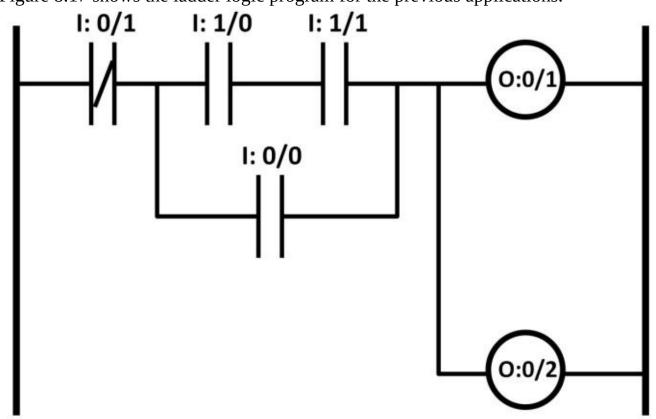

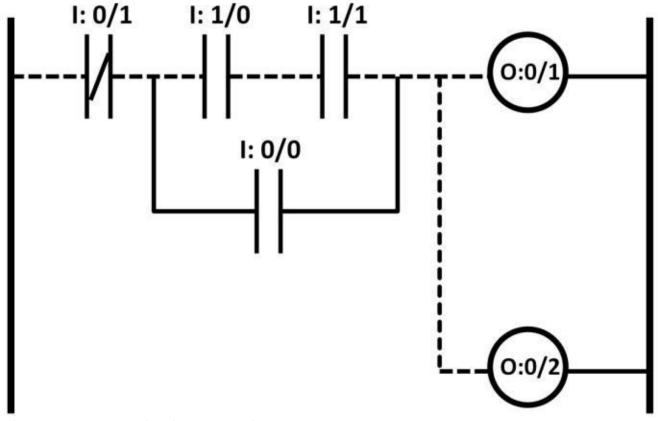

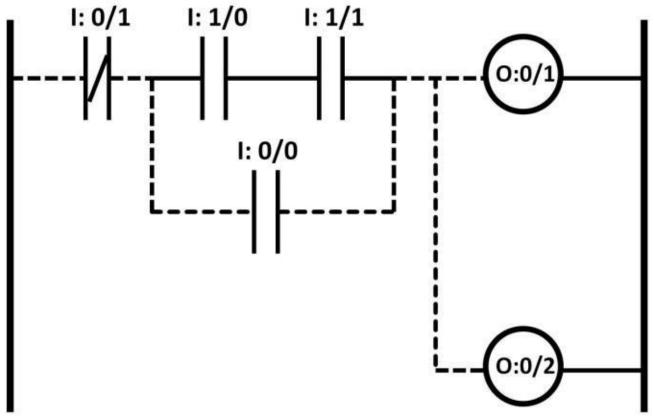

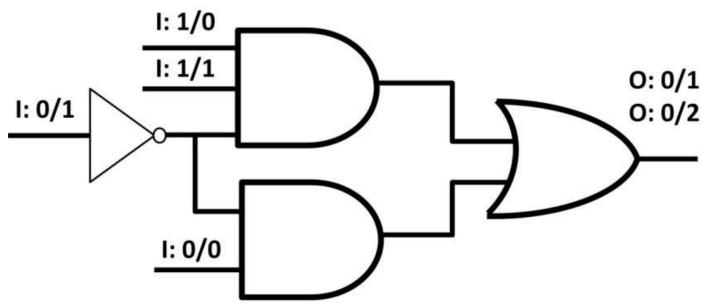

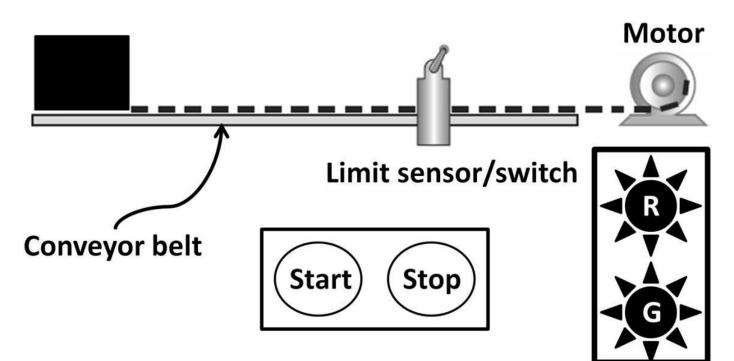

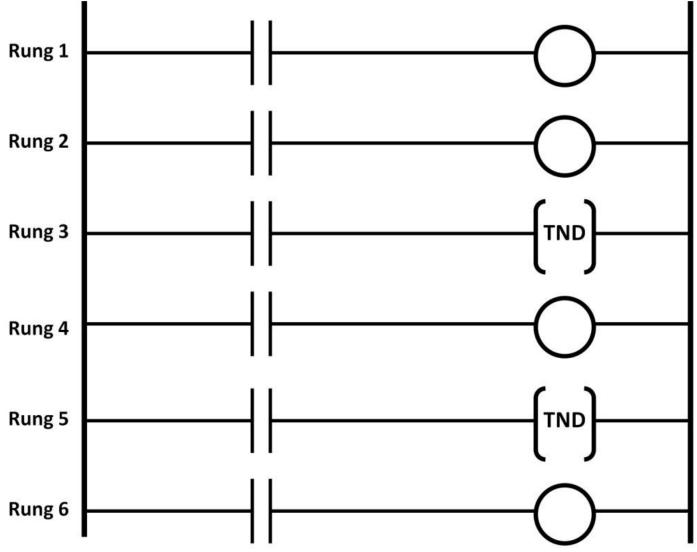

Programmable Logic Controllers (PLCs) are widely used in applications. Thus, it is worthwhile to study them in addition to consumer-based systems. Types and uses of PLCs are covered first, followed by an inside look at PLCs. Ladder logic programming, a graphical programming technique, is the heart of PLCs. In addition, after exploring practical PLC programs and applications, the chapter closes with PLCs troubleshooting techniques and future development.

#### How This Book Is Organized VII

industrial and commercial

#### **Chapter 9: Mental Math**

If you have to use a calculator to solve 1 / 1 k = 1 m, you are probably not making a good impression on interviewers or even coworkers. Using mental math to decipher simple arithmetic answers demonstrates solid mathematic, analytic, and problem solving capabilities. You can learn simple techniques to improve your mental math ability for calculating electronics arithmetic.

| Chapter 1: Direct Current (DC) | 1 | l |

|--------------------------------|---|---|

|--------------------------------|---|---|

| Current                          |                         |

|----------------------------------|-------------------------|

| - 1 Resistor                     |                         |

| - 1 Voltage                      |                         |

| - 5                              |                         |

| Definition                       |                         |

| - 5 Ohm's                        |                         |

| Law                              |                         |

| - 6 Power                        |                         |

| - 7 Voltage Source and Schematic | 7 Current Source        |

| and Schematics                   | 7 Current Source<br>- 8 |

| Electrons                        | 0                       |

| 8 Current versus                 |                         |

| Electrons                        | - 9                     |

| Kirchhoff's Voltage Law (KVL)    |                         |

|                                  | - 9 Kirchhoff's         |

| Current Law (KCL)                |                         |

| 11 Parallel Circuit              |                         |

|                 | - 12 Series<br>13<br>15 Voltage<br>19<br>22<br>24 |

|-----------------|---------------------------------------------------|

|                 | 13<br>15 Voltage<br>19<br>22<br>24<br>            |

|                 | 15 Voltage<br>19<br>22<br>24<br>                  |

|                 | 19<br>22<br>24<br>                                |

|                 | 19<br>22<br>24<br>                                |

|                 | 22<br>24<br>                                      |

|                 | 22<br>24<br>                                      |

|                 | 24                                                |

|                 | 24                                                |

|                 |                                                   |

|                 |                                                   |

|                 | 37                                                |

|                 | 37                                                |

|                 |                                                   |

|                 |                                                   |

|                 |                                                   |

| - 40 Diode I-V  | Curve                                             |

|                 |                                                   |

|                 |                                                   |

|                 |                                                   |

|                 | - 43                                              |

|                 |                                                   |

|                 |                                                   |

|                 |                                                   |

|                 | 49                                                |

|                 |                                                   |

|                 | 49                                                |

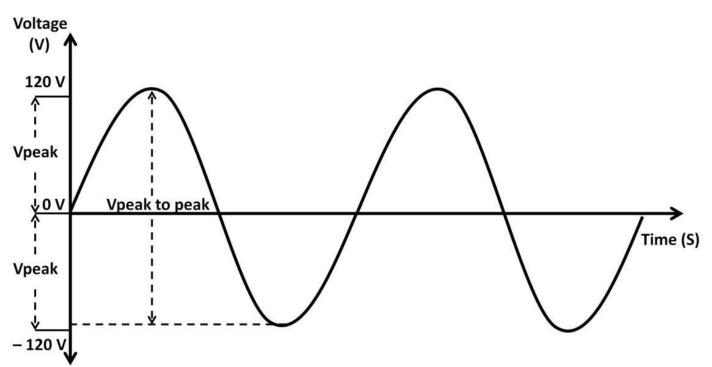

|                 | 50 Peak                                           |

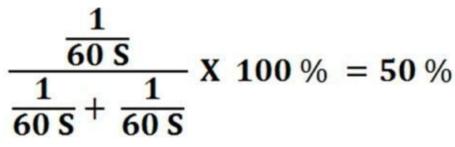

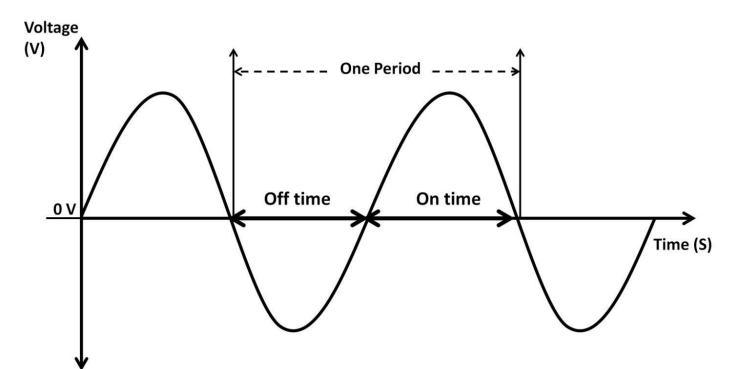

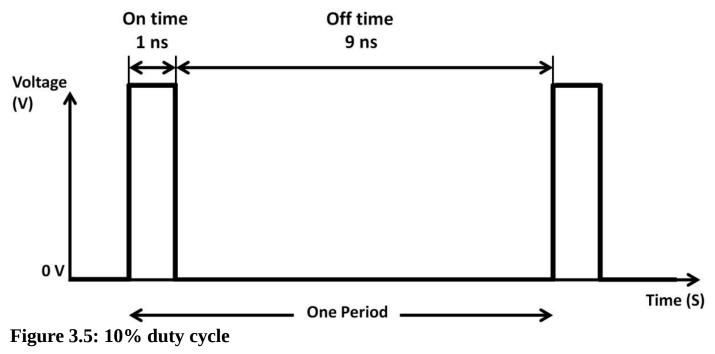

| - 52 Duty Cycle |                                                   |

|                 |                                                   |

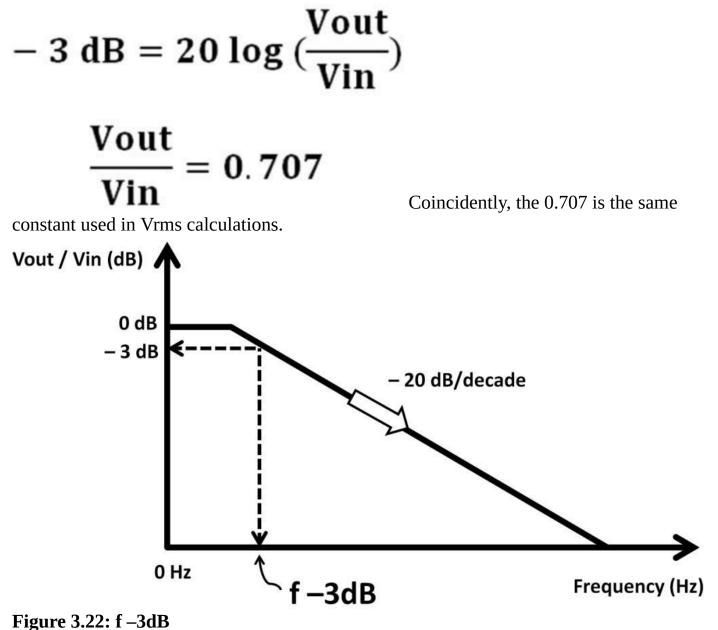

#### Vrms

| 54 Capacitors  |

|----------------|

| 5              |

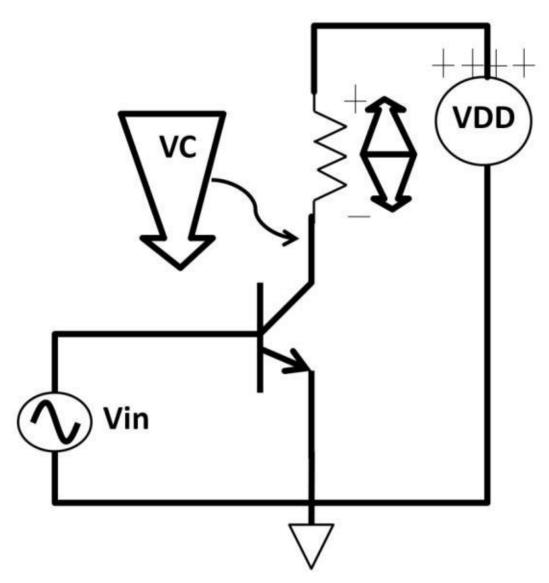

|                |

| 57 I (Δt) = C  |

|                |

|                |

| llel Capacitor |

| 63             |

| 63 Power       |

|                |

| 64 R C         |

| 64             |

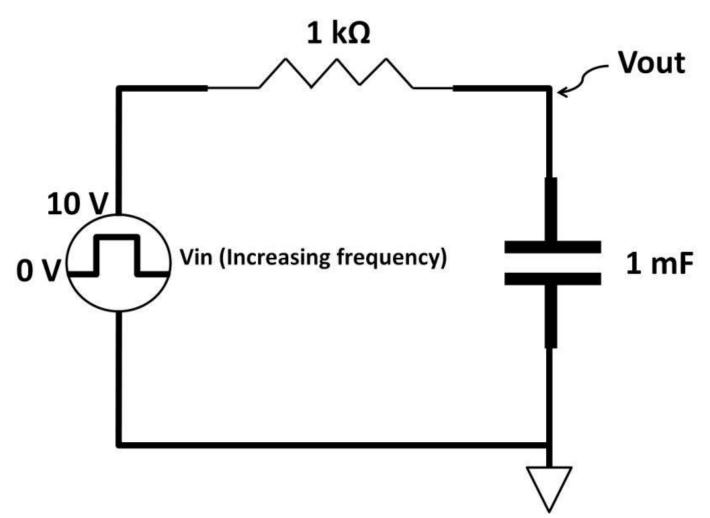

| 65 Low-        |

|                |

| 68             |

| 69             |

|                |

|                |

|                |

|                |

| 74 V (Δt) =    |

|                |

|                |

|                |

| ·              |

| 78 Series      |

| 79 High-       |

| - 80           |

| 00             |

| •              |

|                                       | 85 Ringing          |

|---------------------------------------|---------------------|

| and Bounce                            |                     |

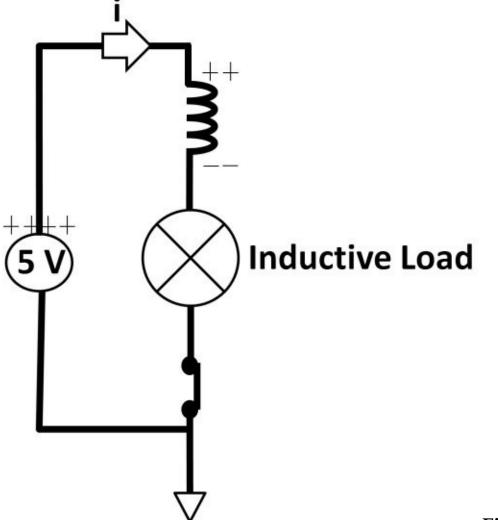

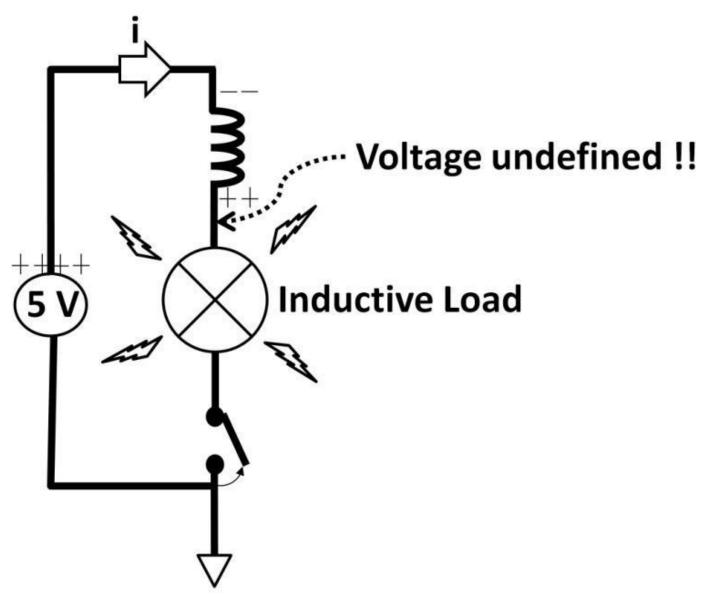

| · 86 Inductive                        |                     |

| Load                                  |                     |

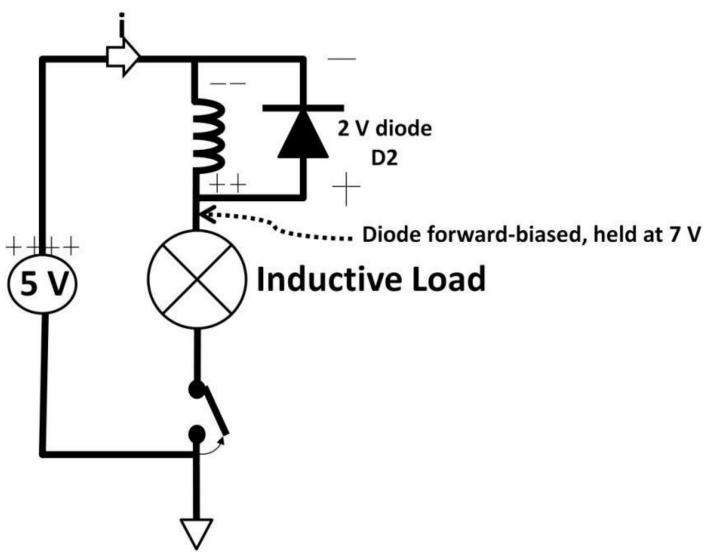

| 87 Diode Clamp                        |                     |

|                                       | 88                  |

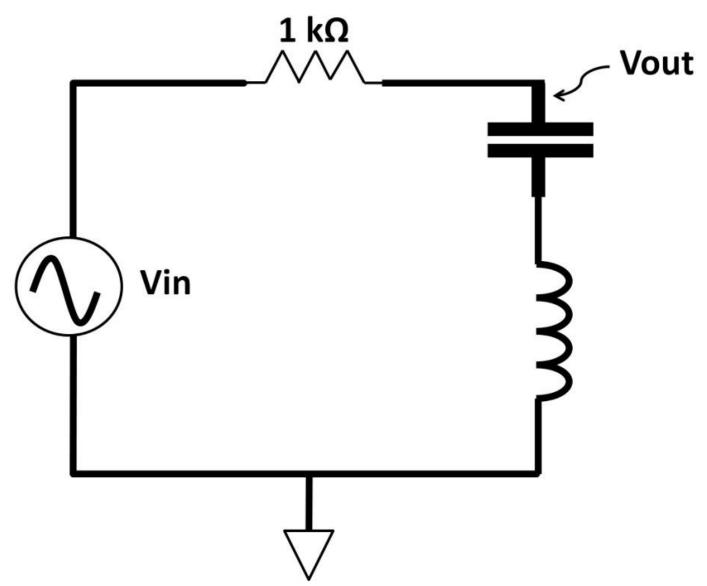

| Series R L C                          |                     |

| Circuit                               |                     |

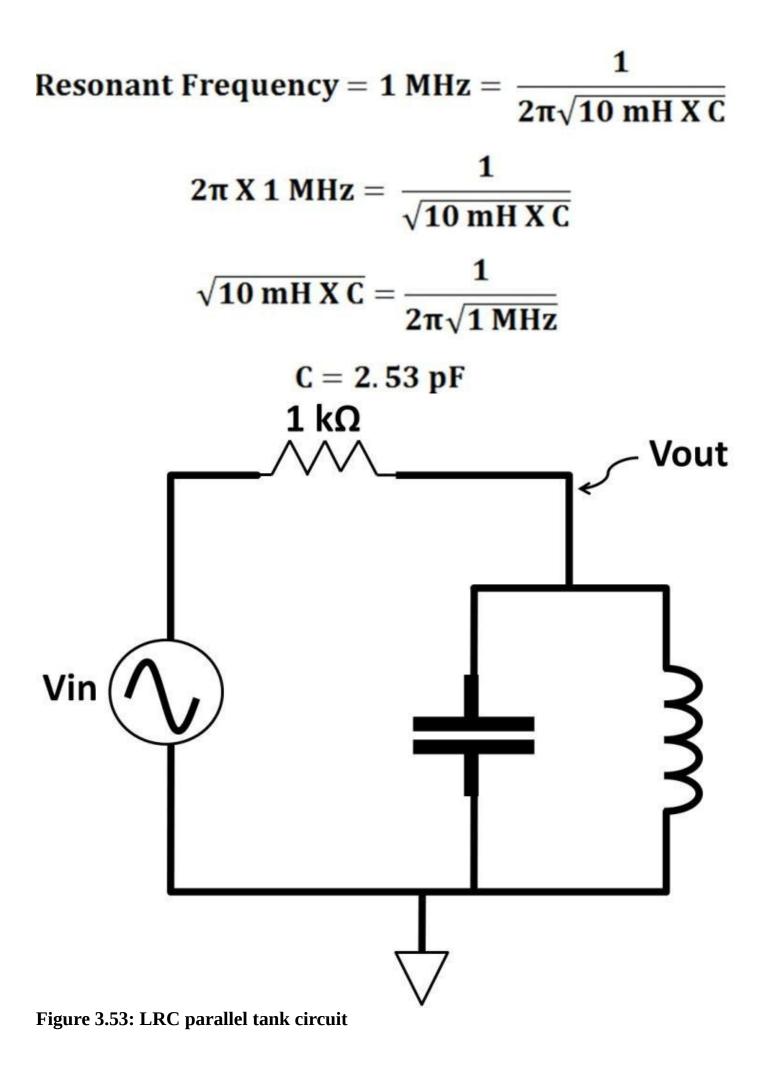

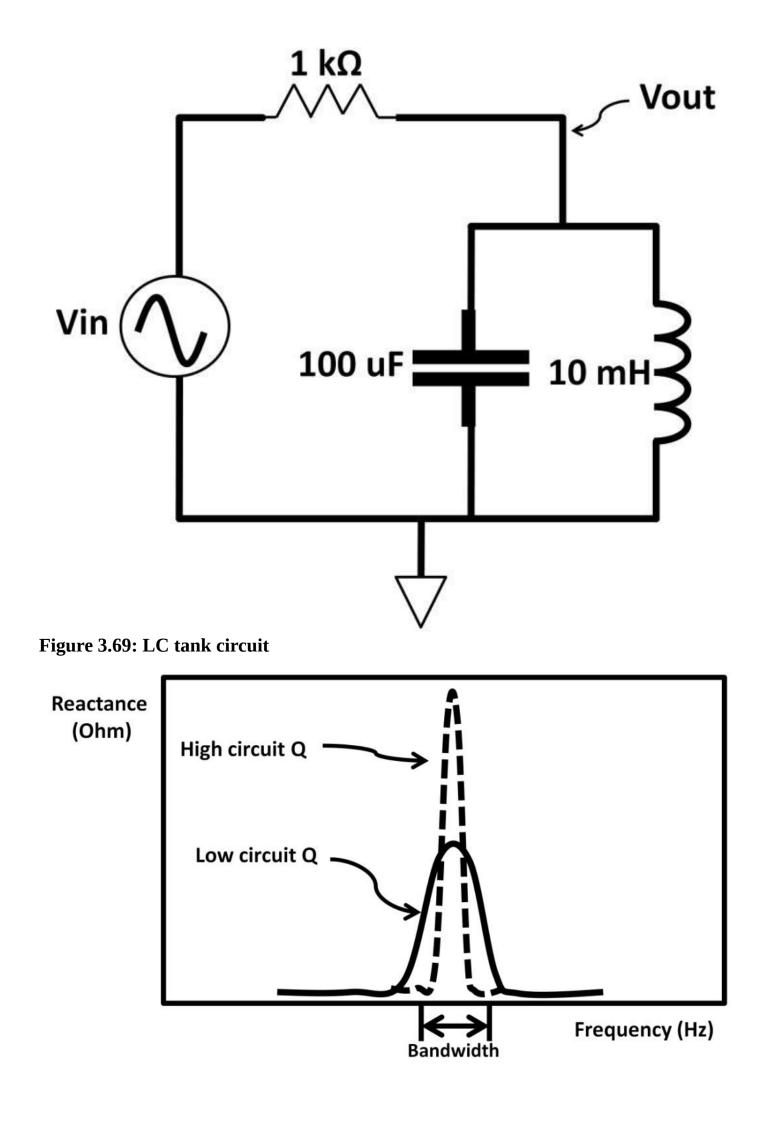

| 89 LRC Parallel (Tank)                |                     |

| Circuit                               | 91                  |

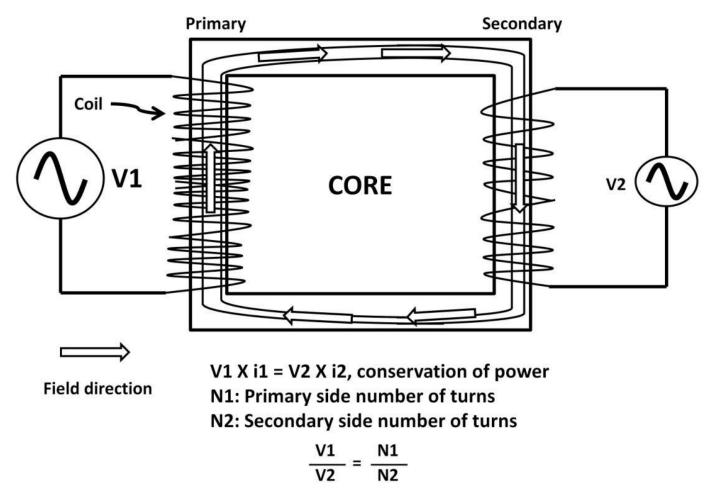

| Fransformers                          |                     |

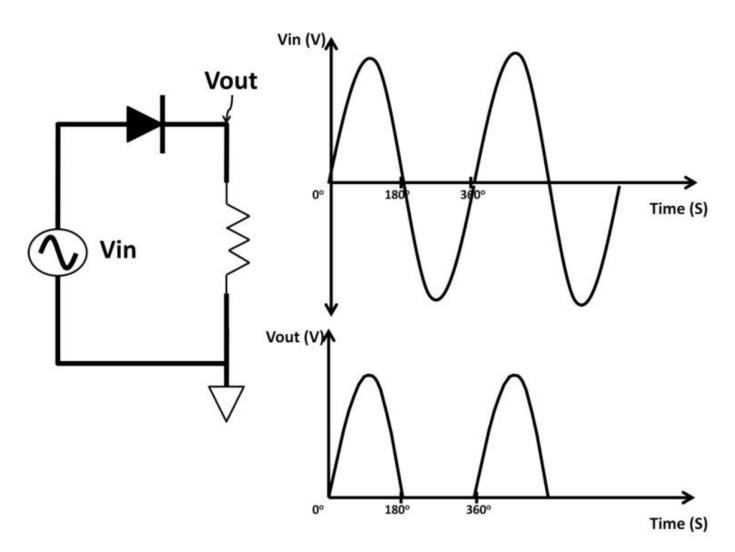

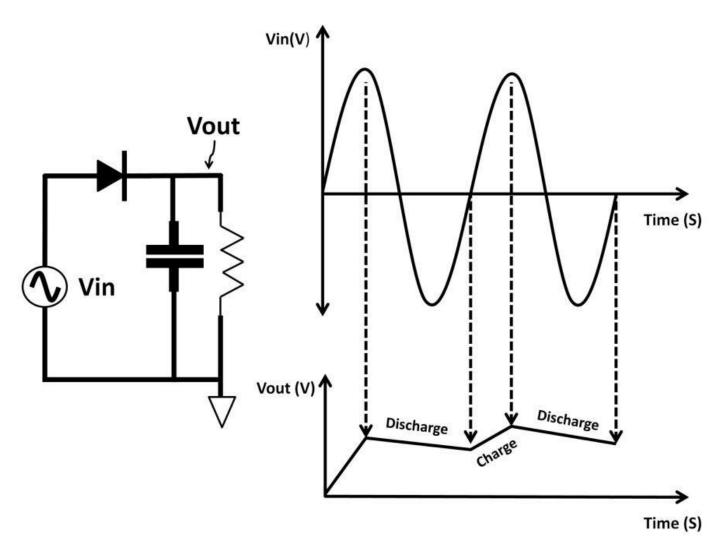

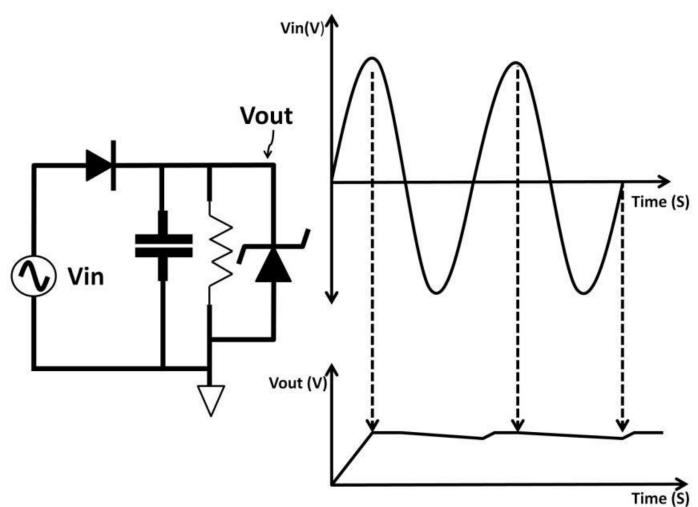

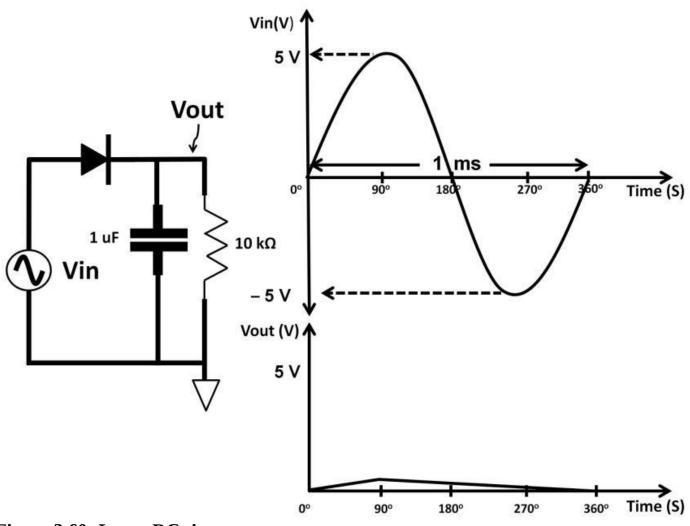

| - 93 Half-Wave                        |                     |

| Rectifier                             |                     |

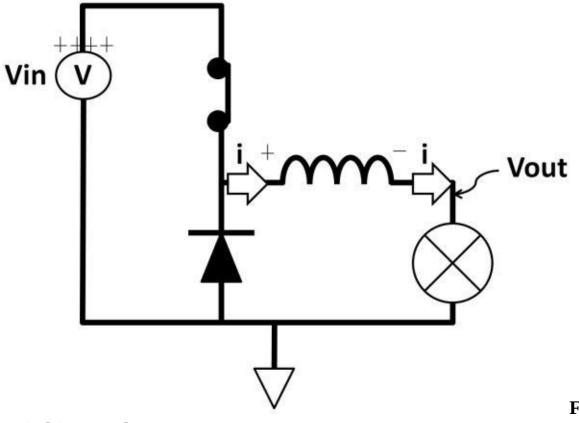

| 95 Switching versus Linear Regulators |                     |

|                                       | 97 Buck Regulator   |

|                                       | _                   |

| Summary                               |                     |

| 100 Quiz                              |                     |

| - 101                                 |                     |

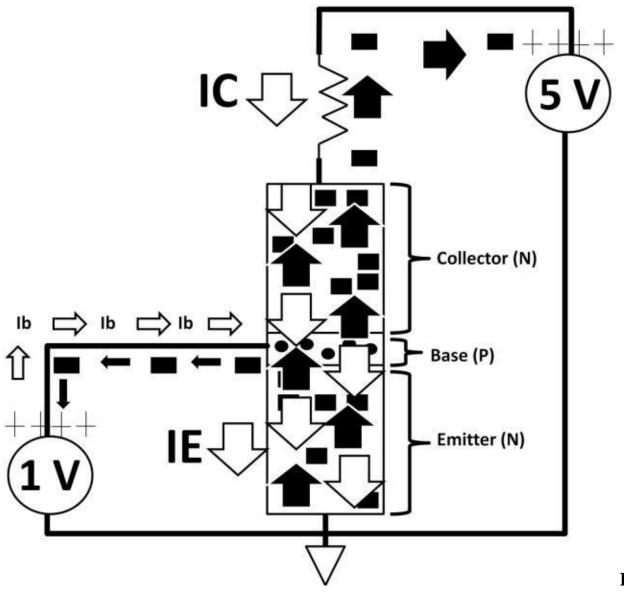

| Chapter 4: Analog Electronics         | 105                 |

| What Is Analog?                       |                     |

|                                       | 105                 |

| Analog IC Market                      |                     |

|                                       | 106 What            |

| Are Transistors Made Of?              |                     |

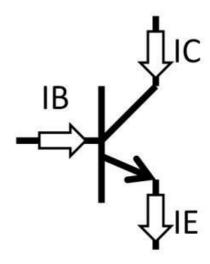

|                                       | 107 NPN and         |

| PNP                                   | -                   |

| 108 NPN and PNP Symbols               |                     |

|                                       | 109 Transistor      |

| Cross-Section                         | -                   |

| 110 Bipolar Transistor Terminal       |                     |

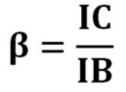

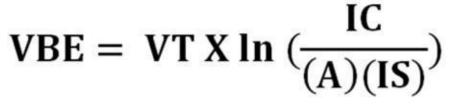

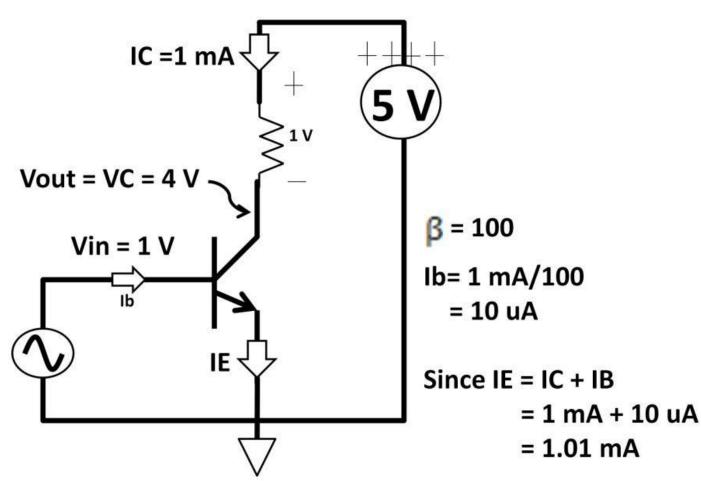

| Impedance                             | 111 IC, IB, IE, and |

| Beta (β)                              |                     |

| XII Table of Contents                 |                     |

| VBE                                   |                     |

| - 113 IF = IC + IB                    |                     |

- 113 IE = IC + IB

|                                                        | - 114                            |

|--------------------------------------------------------|----------------------------------|

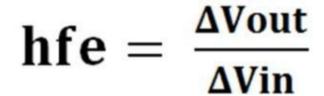

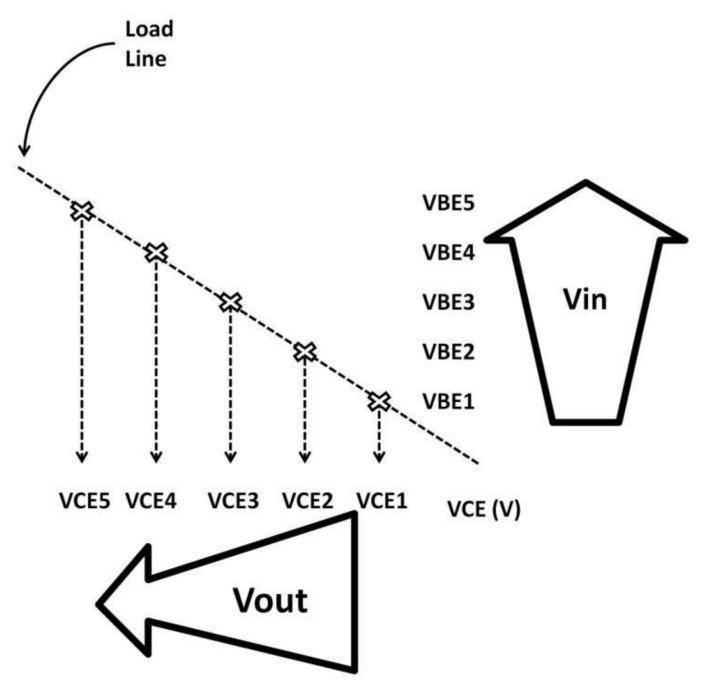

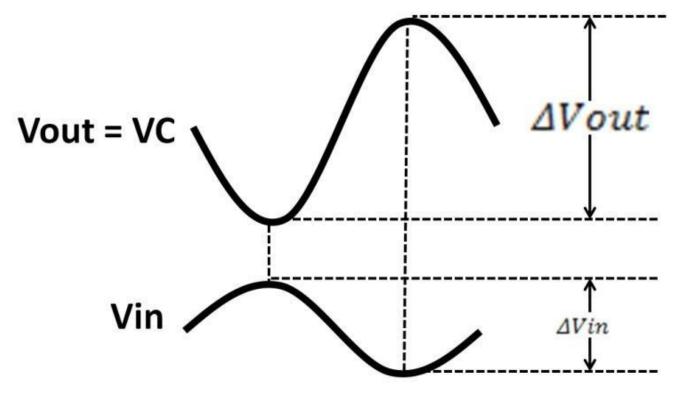

| Common Emitter Amplifier                               |                                  |

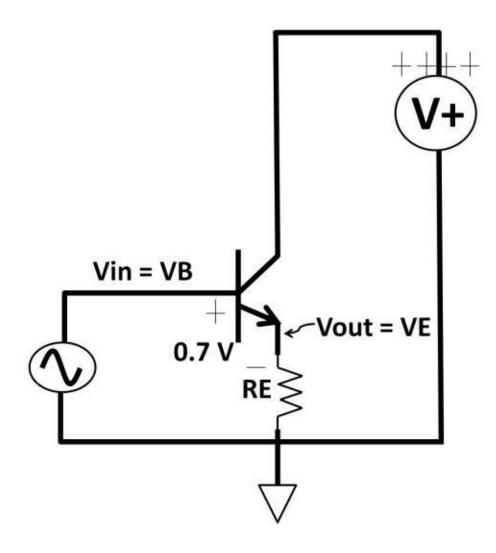

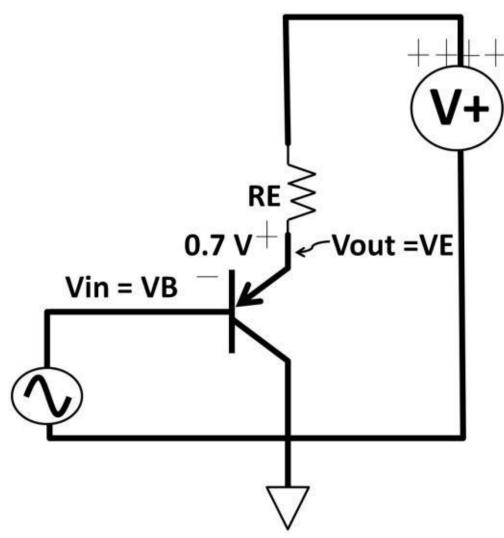

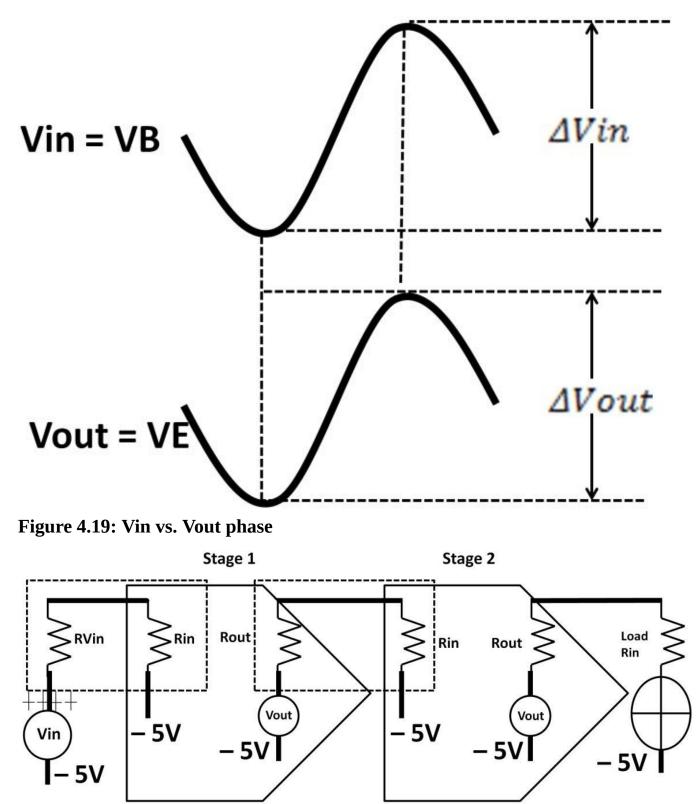

|                                                        | 115 Common                       |

| Collector Amplifier (Emitter Follower)                 |                                  |

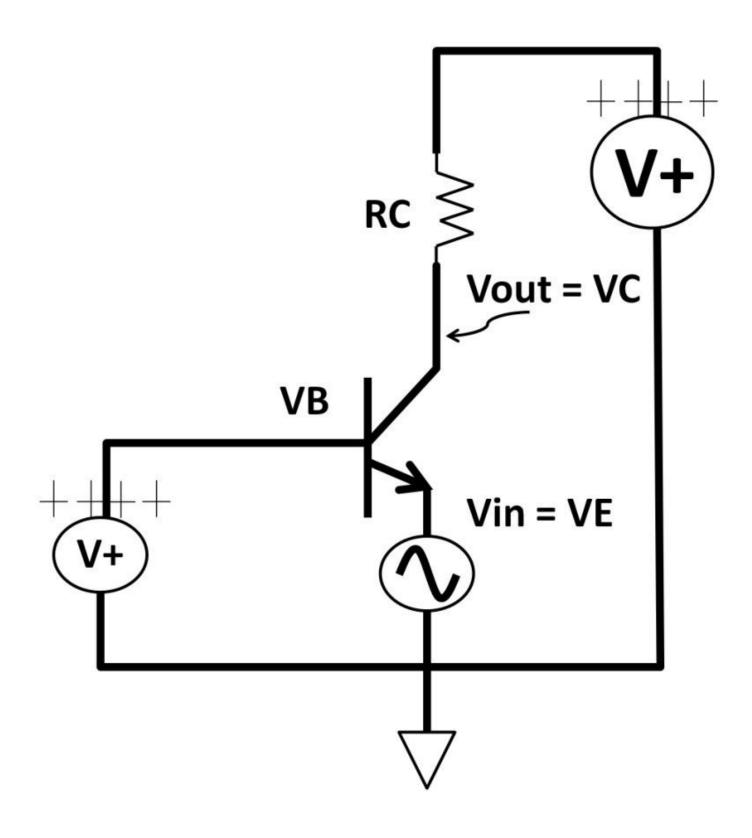

| 118 Common Base                                        |                                  |

| Amplifier<br>Single-Ended Amplifier Topologies Summary | 120                              |

| Single-Ended Amplifier Topologies Summary              |                                  |

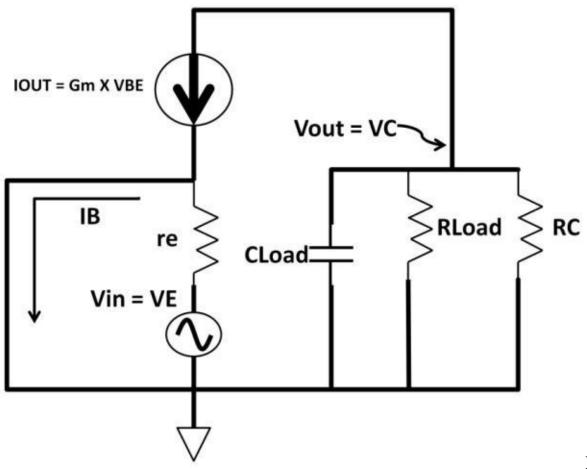

|                                                        | 121 Tranconductance (Gm), Small- |

| Signal Models                                          | 121 Common                       |

| Emitter Amplifier Input Impedance                      |                                  |

| 123 Common Emitter Amplifier Output Imped              |                                  |

|                                                        | 124 Common Collector Amplifier   |

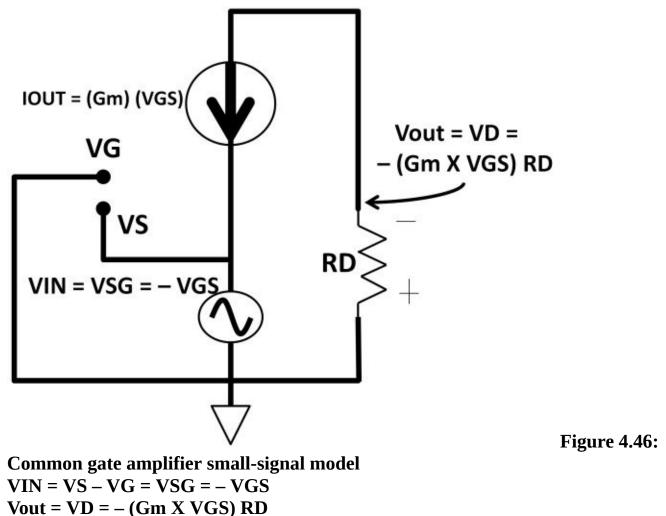

| Small-Signal Model                                     | 127 Common Base                  |

| Amplifier Small-Signal Model                           | - 128                            |

| Single-Ended Amplifier Summary                         |                                  |

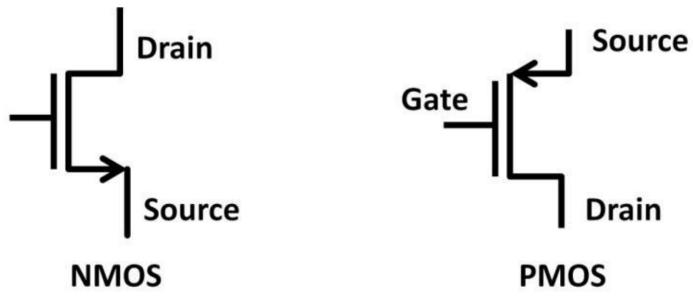

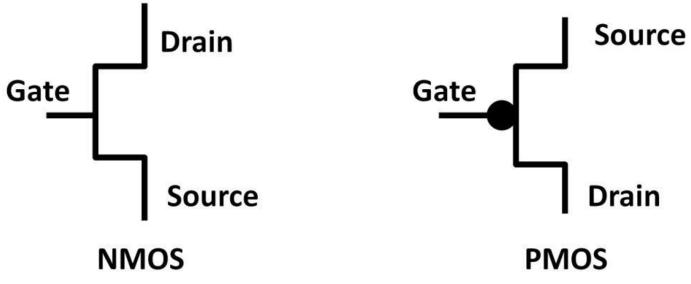

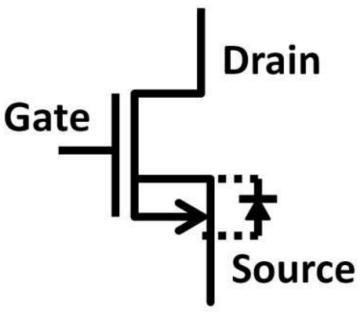

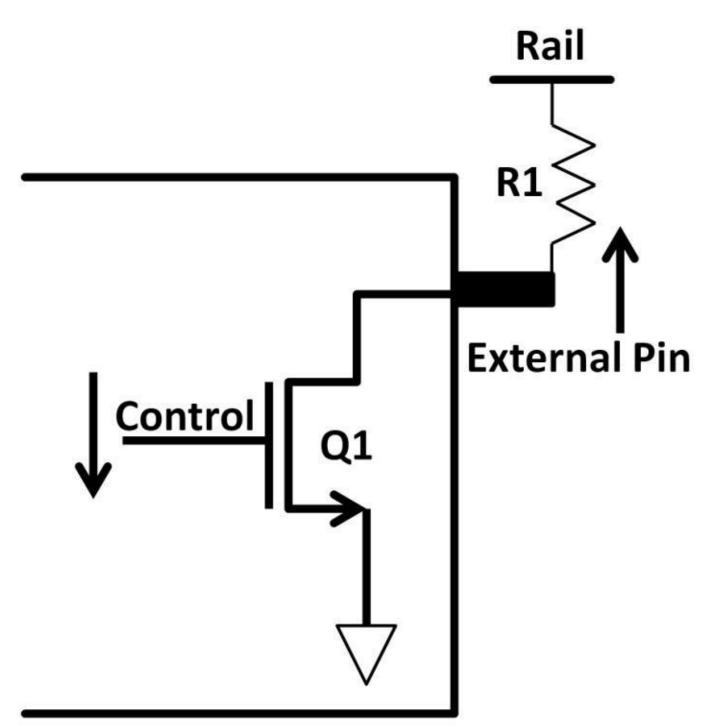

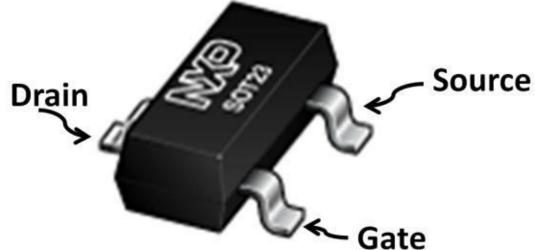

|                                                        | - 129 NMOS and PMOS              |

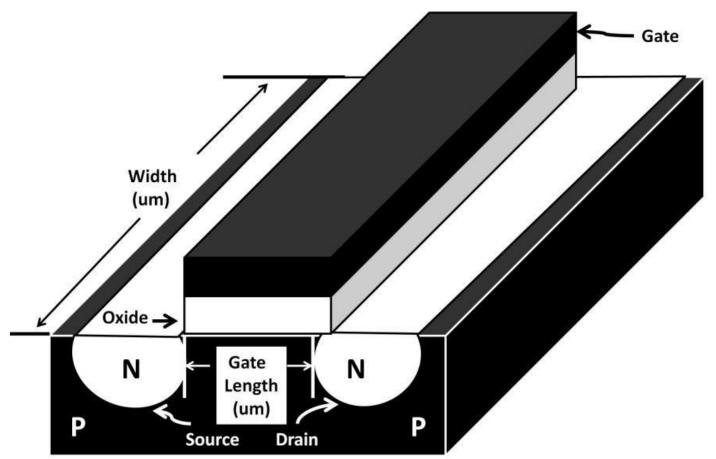

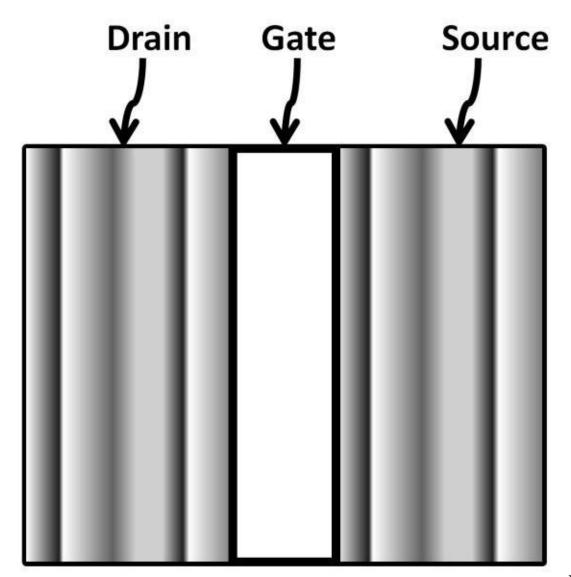

|                                                        | 130 3D                           |

| NFET                                                   |                                  |

|                                                        |                                  |

| 131 Drain Current and Threshold Voltage                |                                  |

|                                                        | - 132 NFET and PFET              |

| Symbols                                                | 132 IC                           |

| Layout                                                 |                                  |

| 134 VHDL and Verilog                                   |                                  |

|                                                        | 135                              |

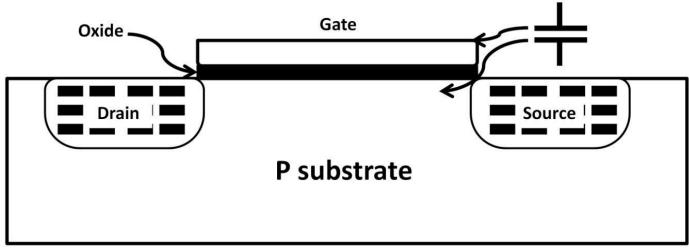

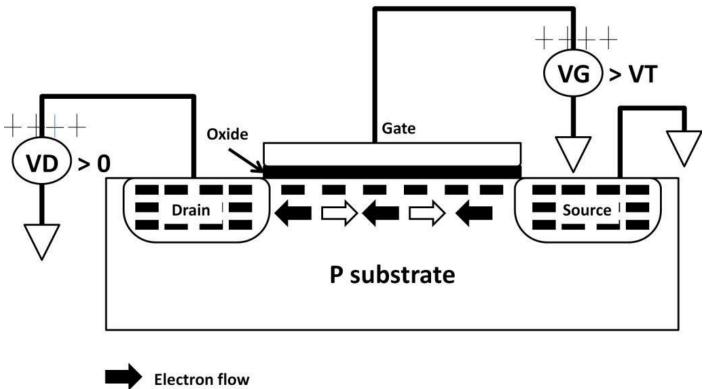

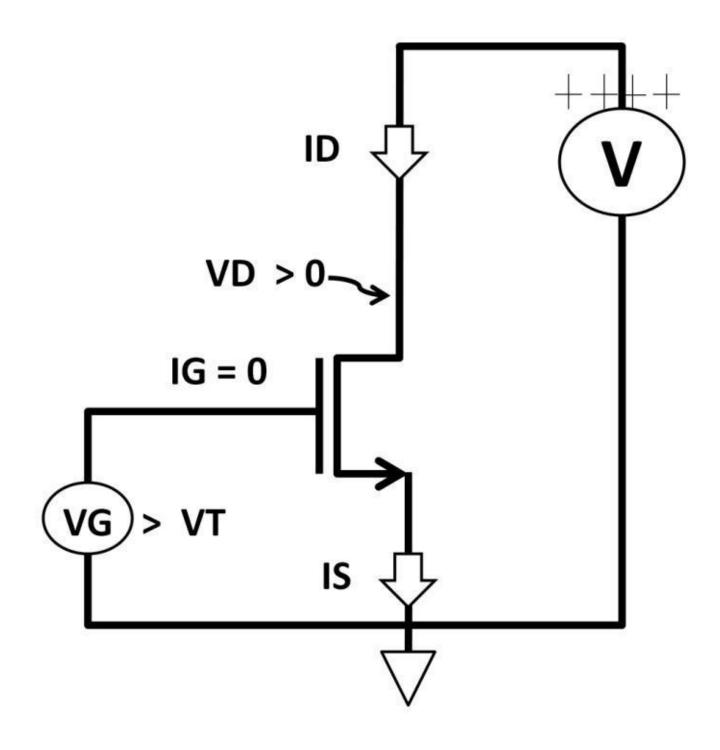

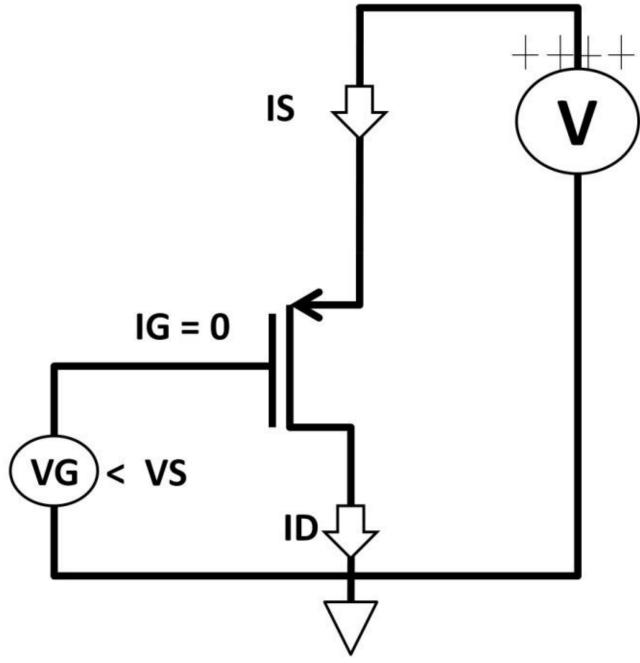

| <b>MOSFET Cross Section and Operations</b>             |                                  |

|                                                        | - 136 MOSFET On-Off              |

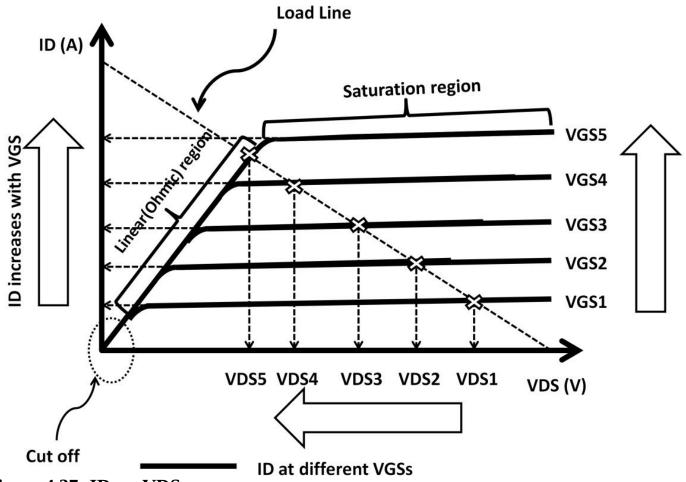

| Requirements                                           | 137 ID                           |

| versus VDS Curve                                       |                                  |

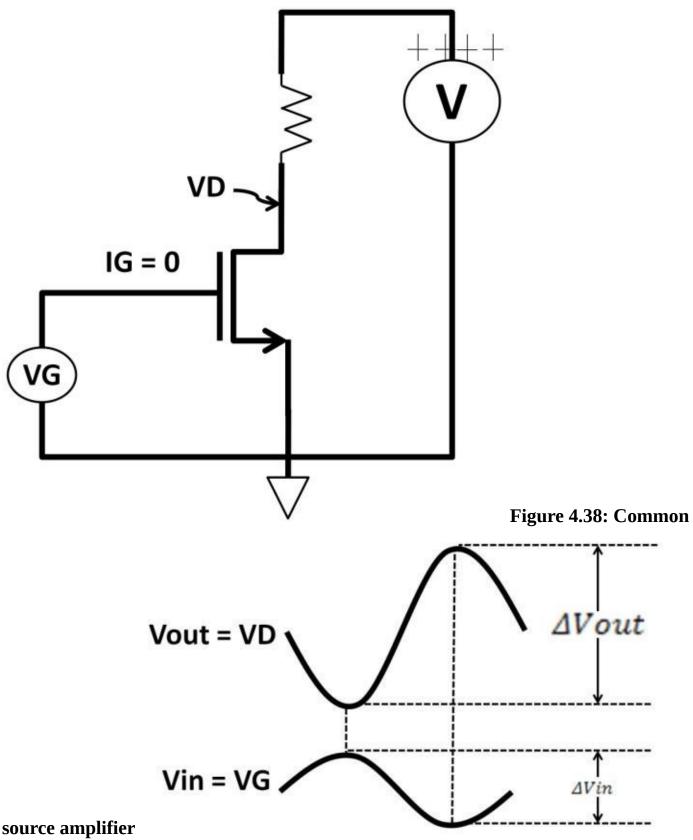

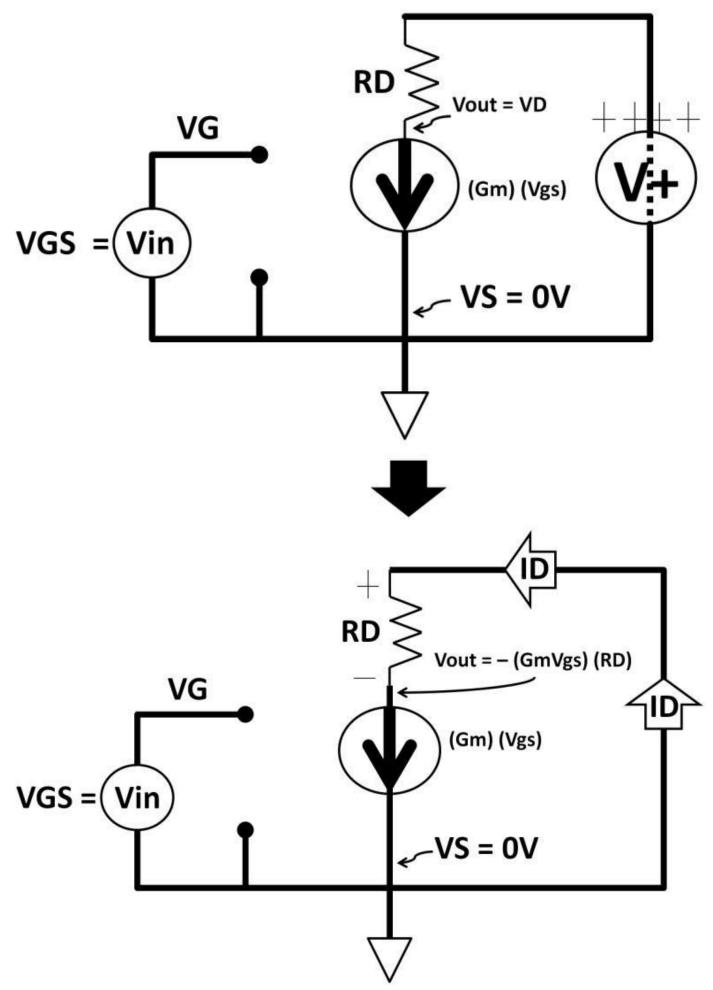

|                                                        | 139 CMOS                         |

| Source Amplifier                                       |                                  |

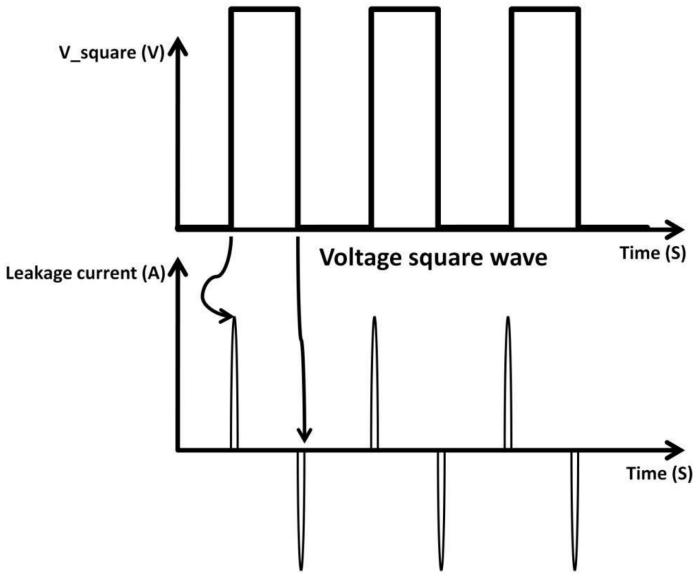

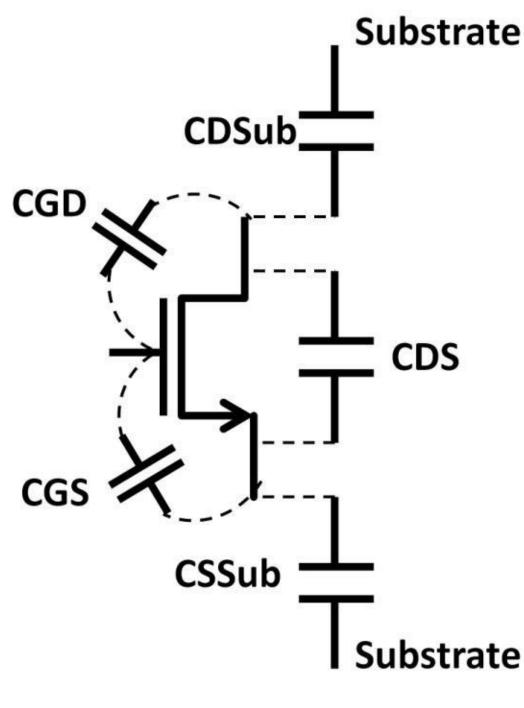

| - 139 MOSFET Parasitic                                 |                                  |

|                                                        | 142                              |

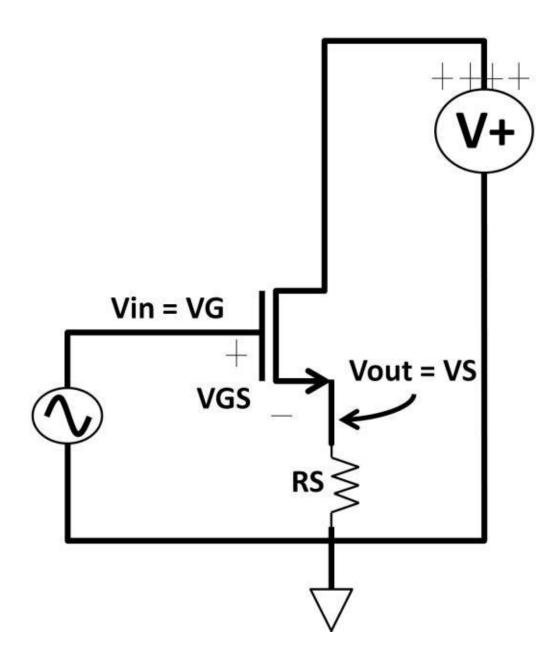

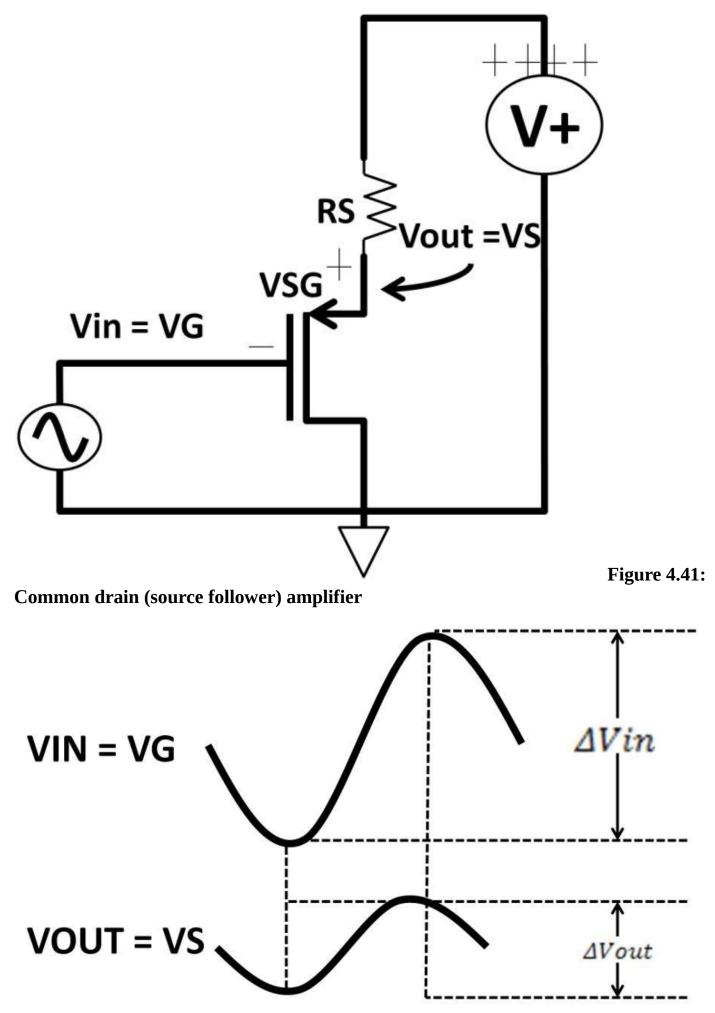

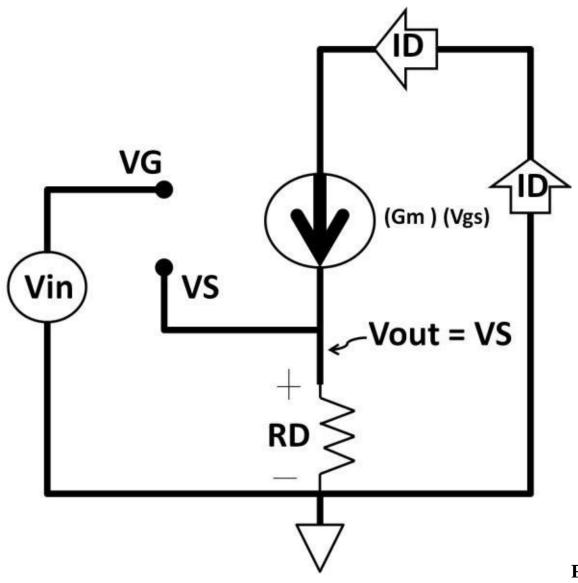

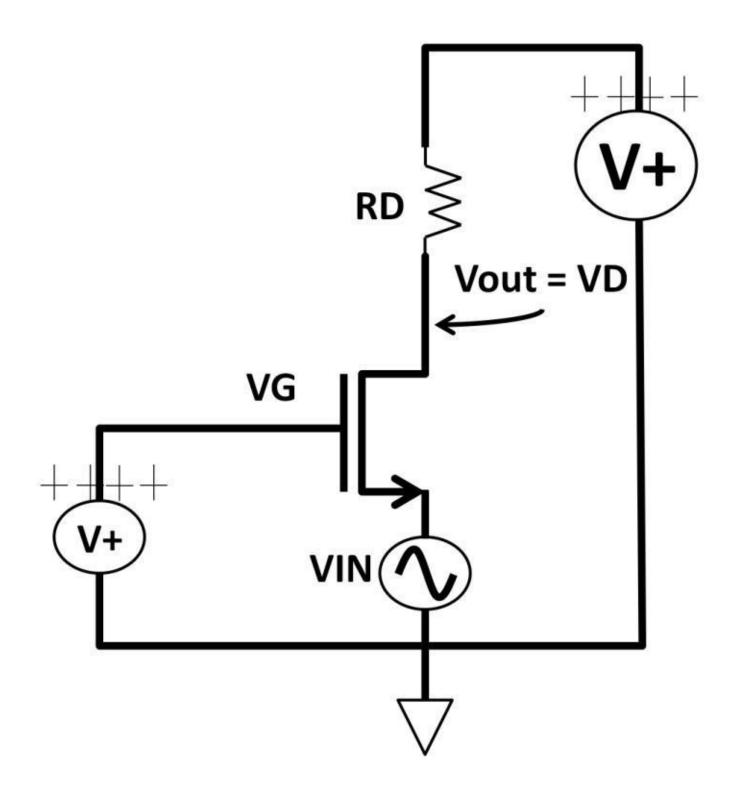

| Common Drain Amplifier (Source Follower)               |                                  |

|                                                        |                                  |

| Amplifier                                              | 145                              |

| Bipolar versus CMOS                                    |                                  |

|                                                        | 147                              |

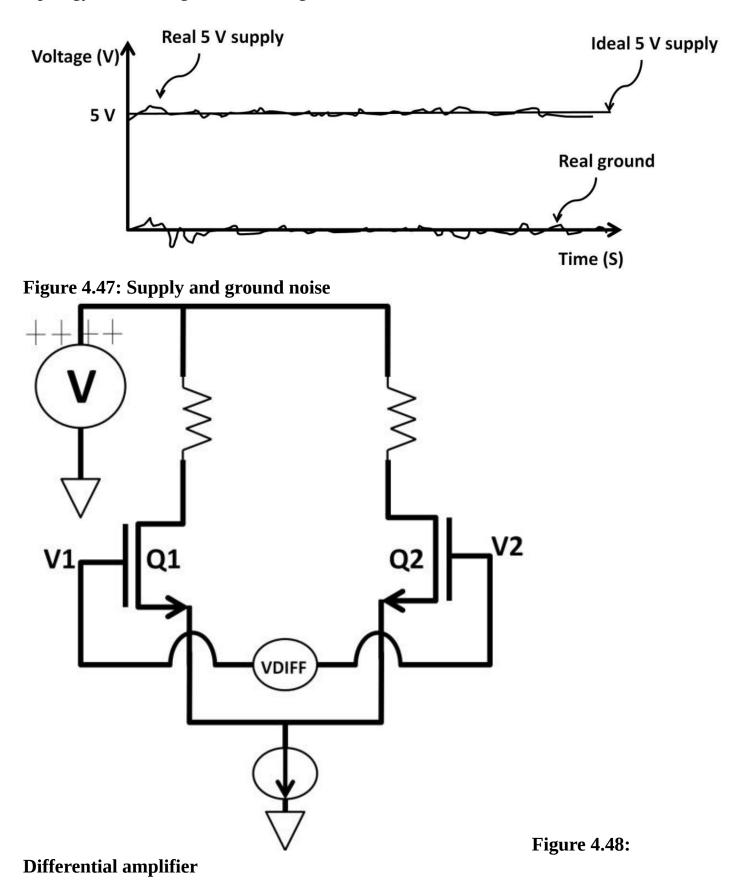

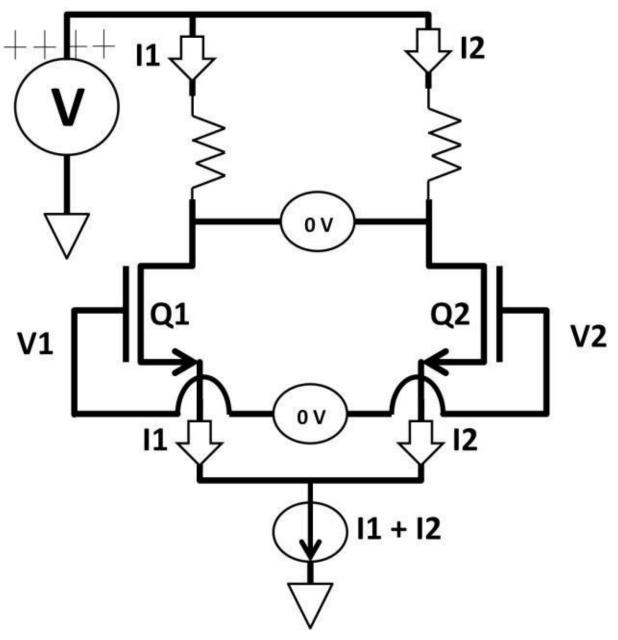

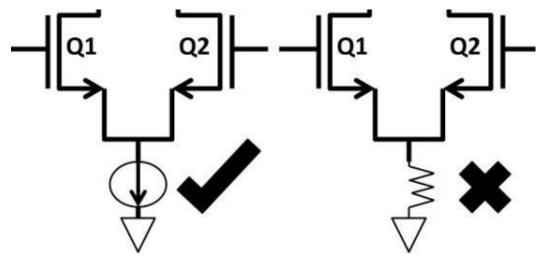

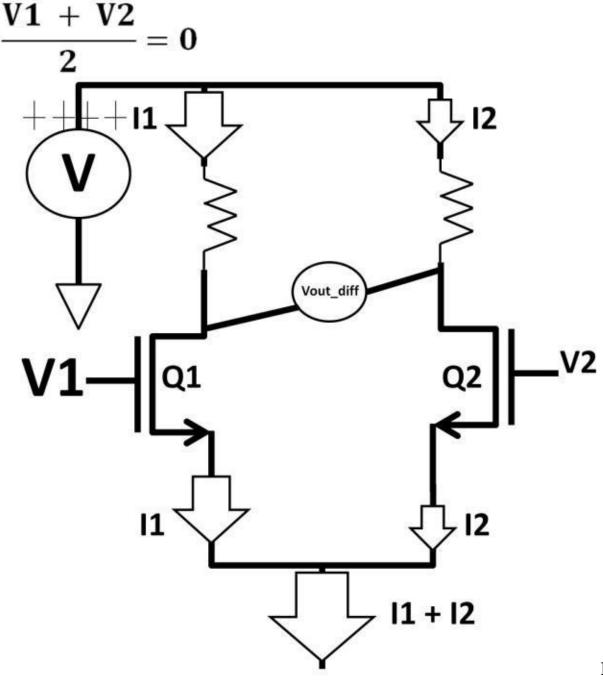

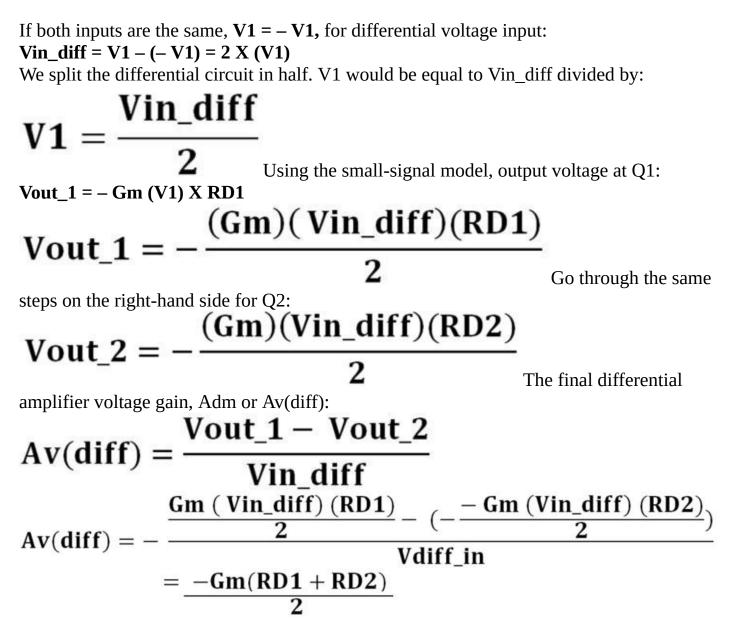

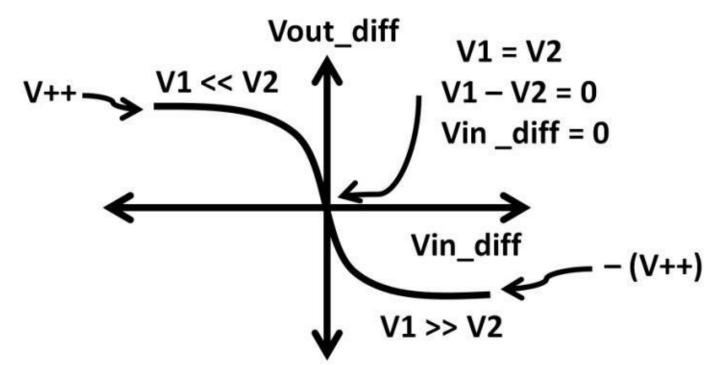

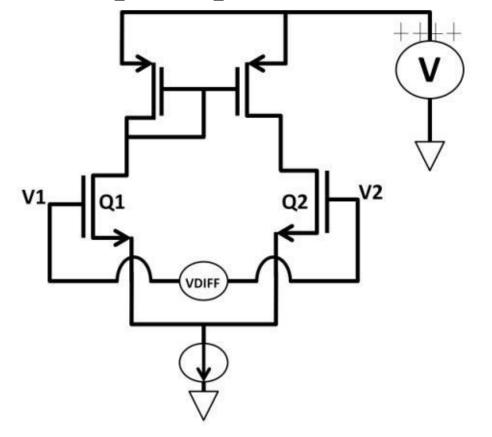

| Differential Amplifiers                                |                                  |

|                                                        | 148                              |

| Table of Contents XIII                                 |                                  |

**Common Mode**

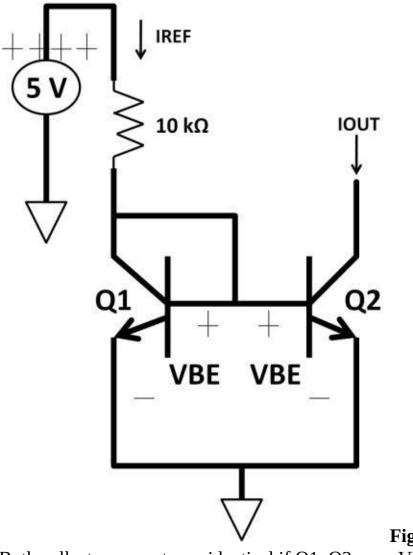

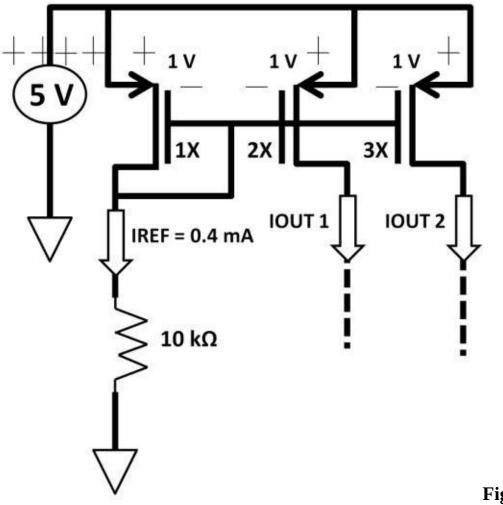

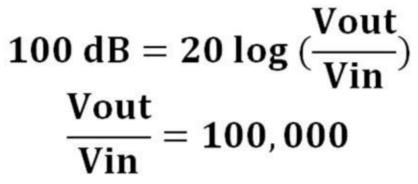

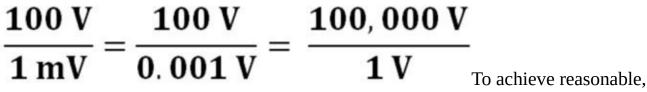

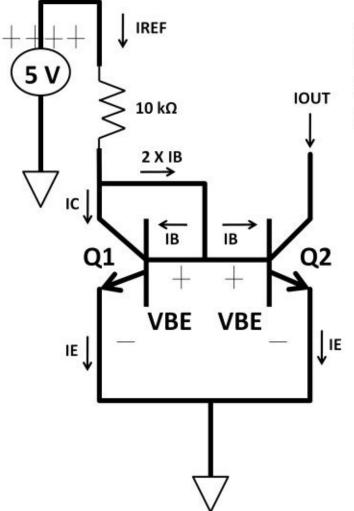

| Mirror                                |                       |

|---------------------------------------|-----------------------|

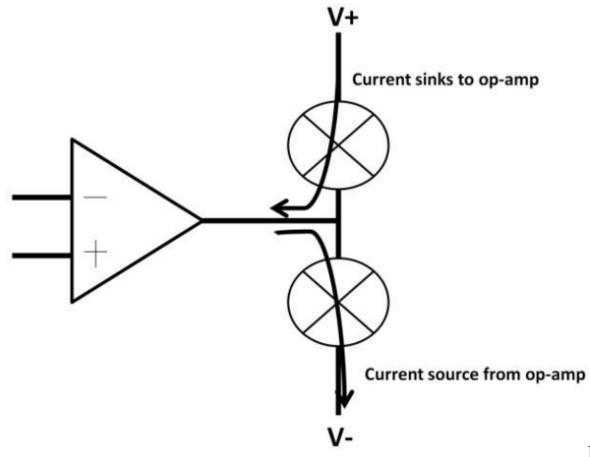

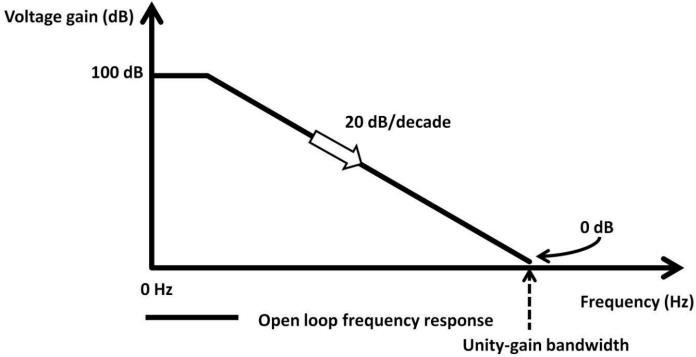

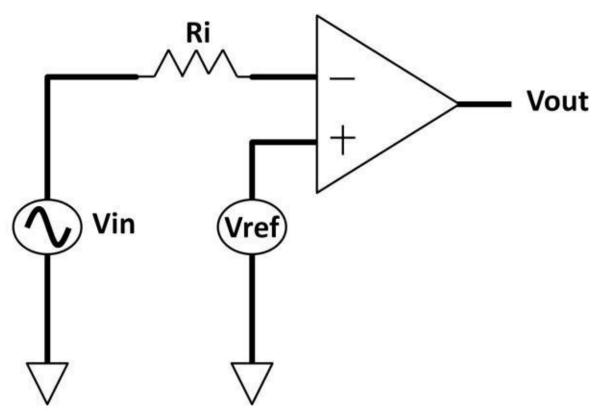

| 152 Op-Amp                            |                       |

| 153 Op-Amp Rules                      |                       |

|                                       | 155                   |

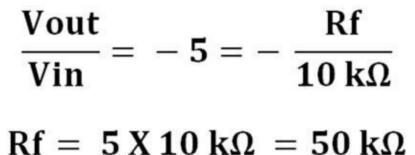

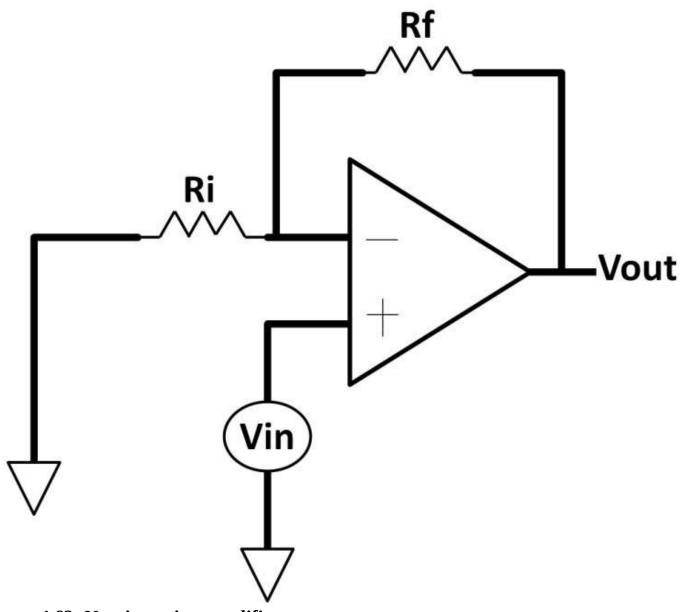

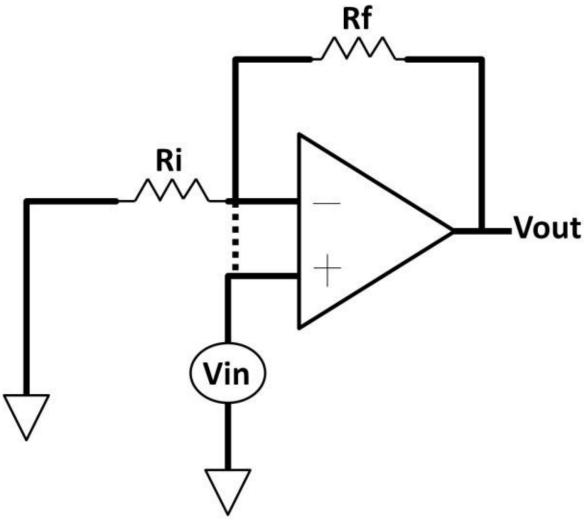

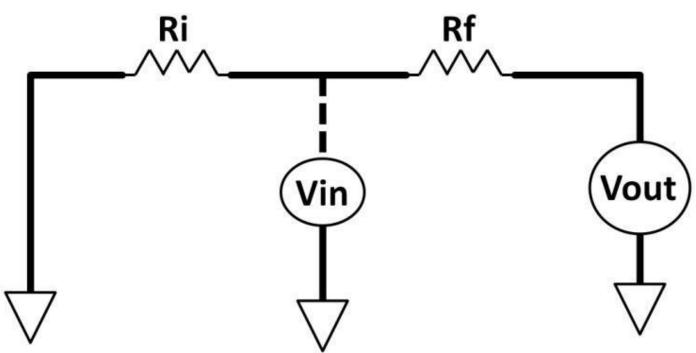

| Inverting Amplifier                   |                       |

|                                       | - 158 Non-            |

| Inverting Amplifier                   |                       |

|                                       | 160 Op-Amp            |

| Parameters                            |                       |

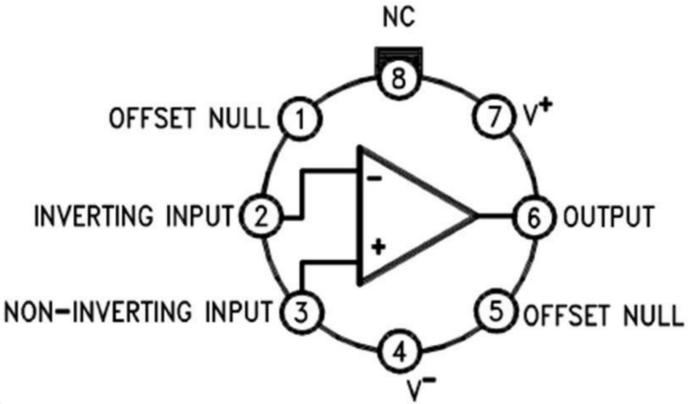

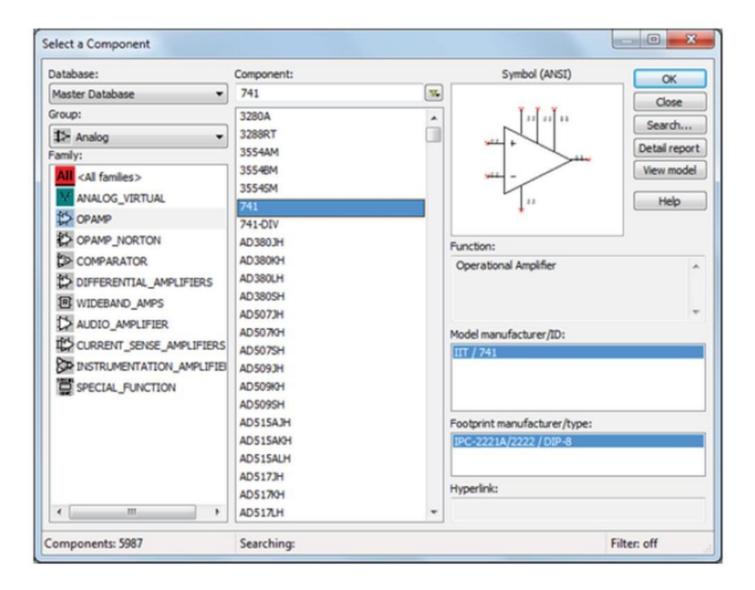

| 162 LM741                             |                       |

| 164 Current Mirror Inaccuracies       |                       |

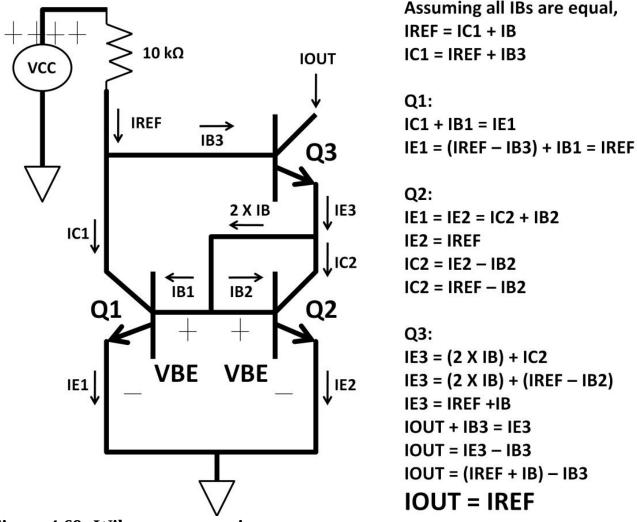

|                                       | 165 Wilson Current    |

| Mirror                                |                       |

| Bipolar                               |                       |

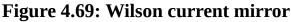

| Cascode                               |                       |

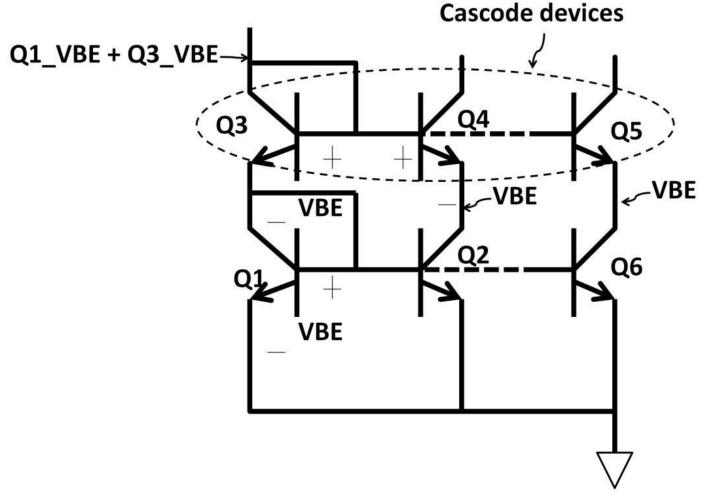

| 167 Darlington Pair                   |                       |

| •                                     | 168                   |

| CMOS Cacosde                          |                       |

|                                       | 170                   |

| Buffer (Voltage Follower)             |                       |

|                                       | 171 Summing           |

| Amplifier                             |                       |

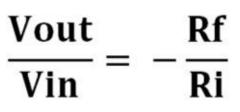

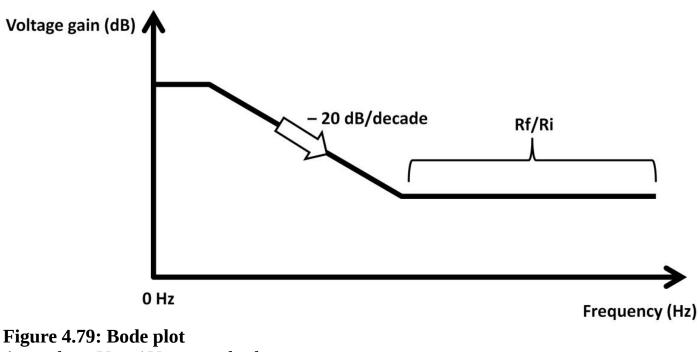

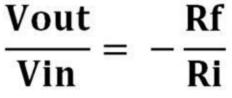

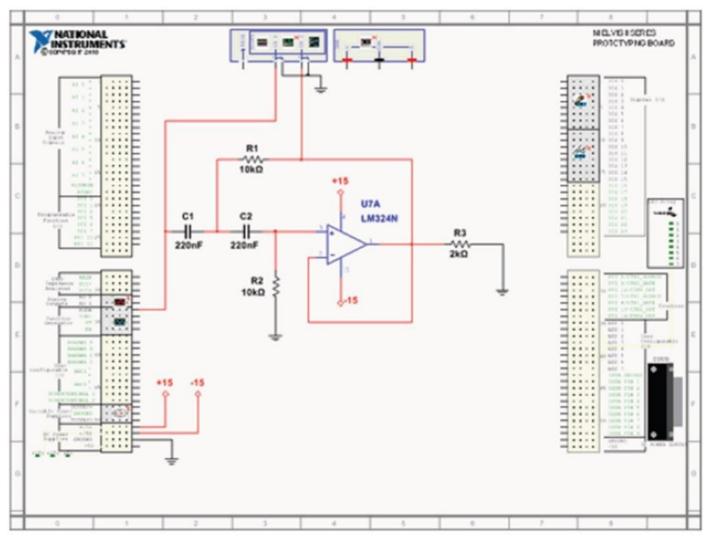

| 172 Active Low-Pass Filter            |                       |

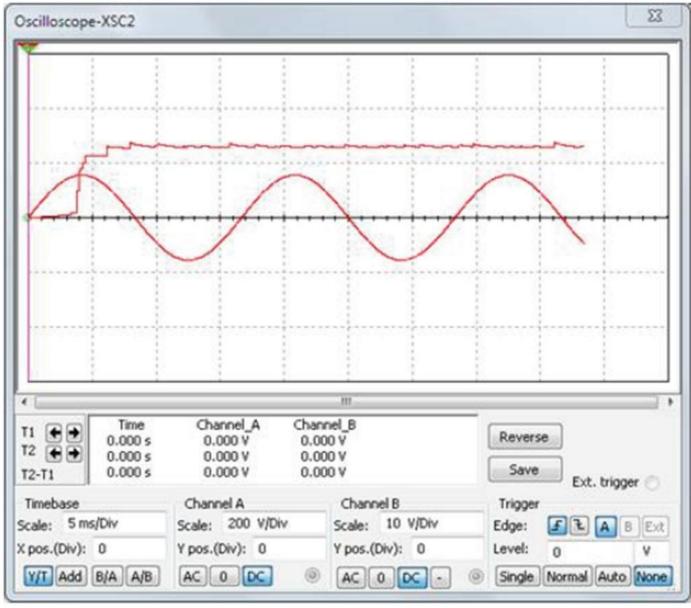

|                                       | 174 Circuit           |

| Simulator                             |                       |

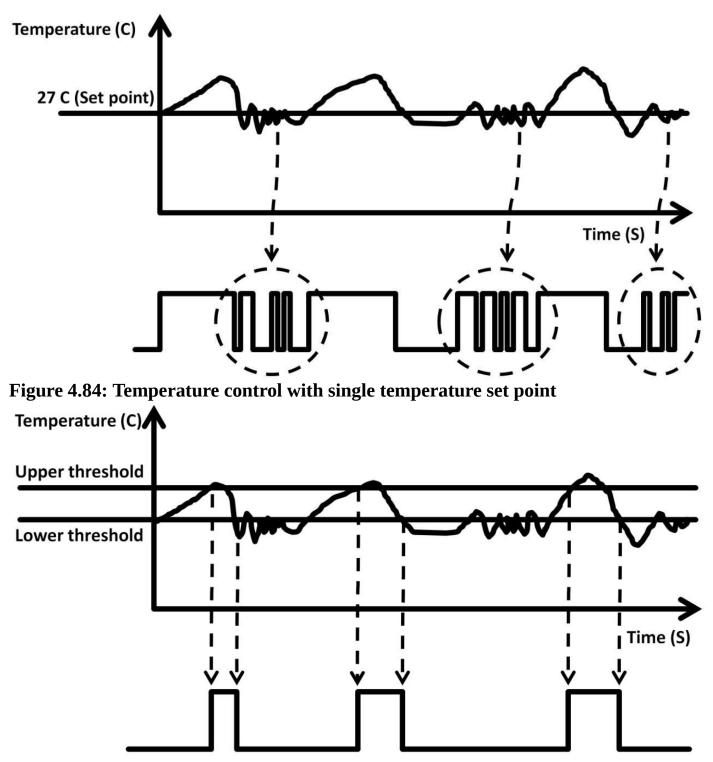

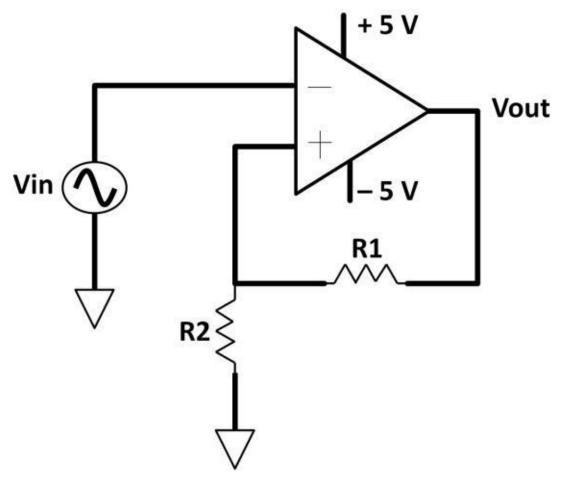

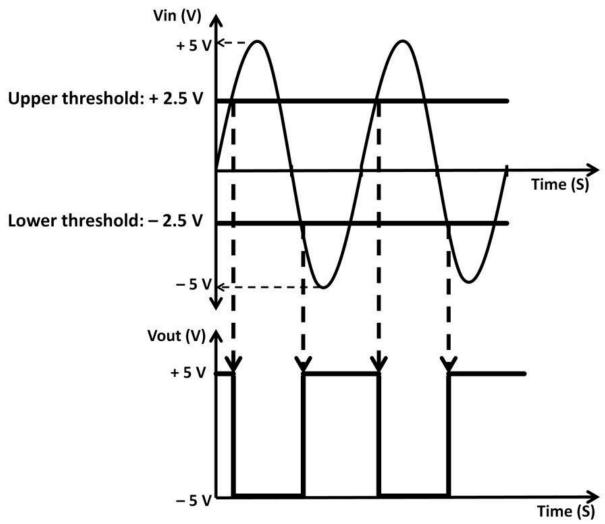

| - 176 Hysteresis                      | 170                   |

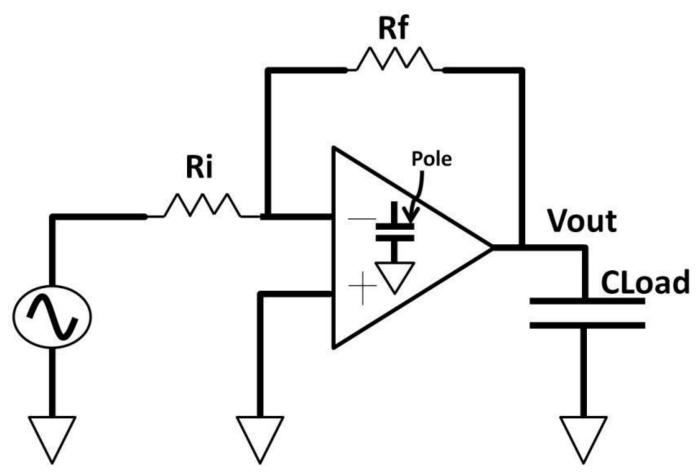

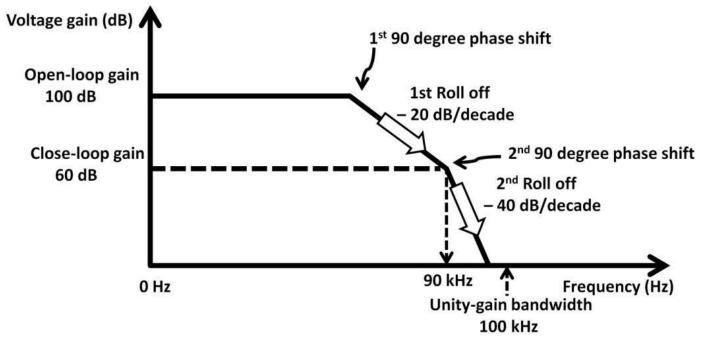

| Positive Feedback (Oscillation)       | - 179                 |

| · · · · · · · · · · · · · · · · · · · | - 182 Instrumentation |

| Amplifier                             |                       |

| Linear Regulator                      | 104                   |

| •                                     | 185 Low               |

| Drop-out (LDO) Regulator              |                       |

|                                       | - 186 Summary         |

|                                       |                       |

| 189 Quiz                              |                       |

| - 190                                 |                       |

| Chapter 5: Digital Electronics        | 195                   |

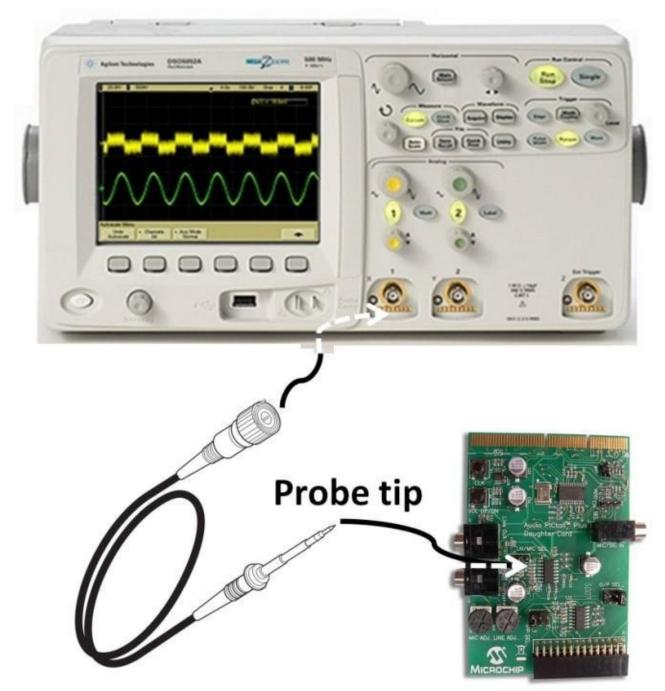

|                                       |                       |

|                                       |                       |

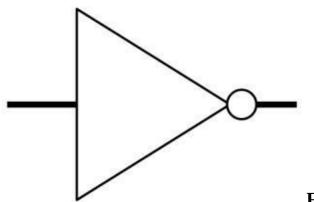

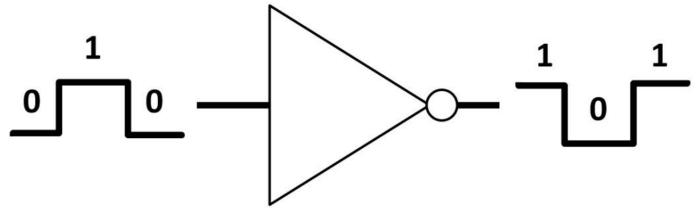

| Invortor                         |                 |

|----------------------------------|-----------------|

| Inverter                         |                 |

|                                  | 107 Invortor    |

| Action                           | 157 Inverter    |

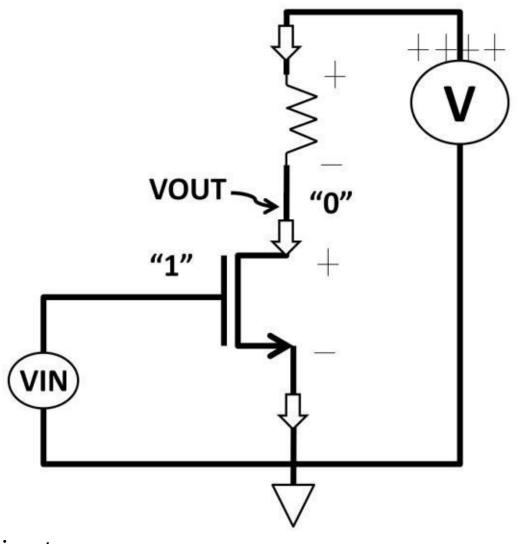

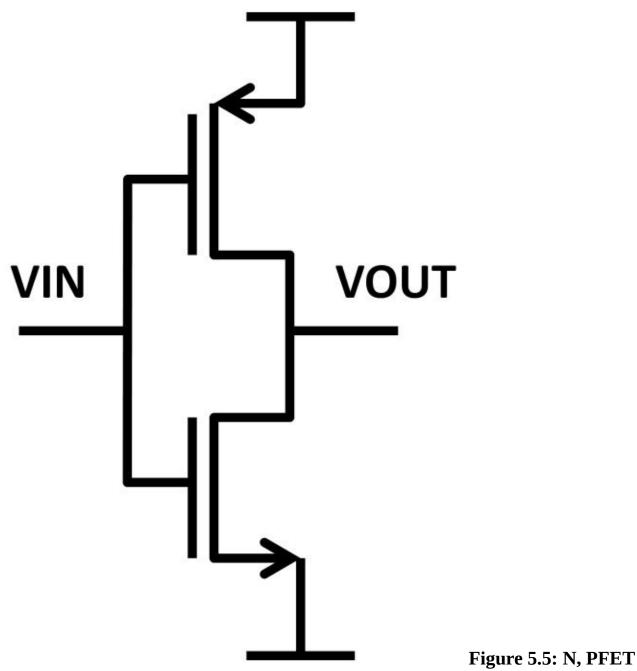

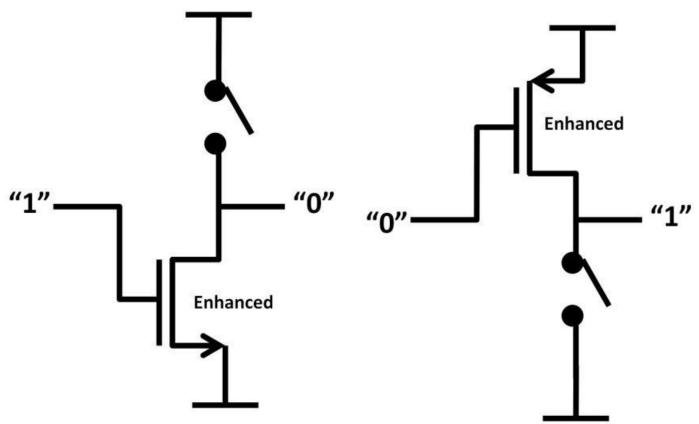

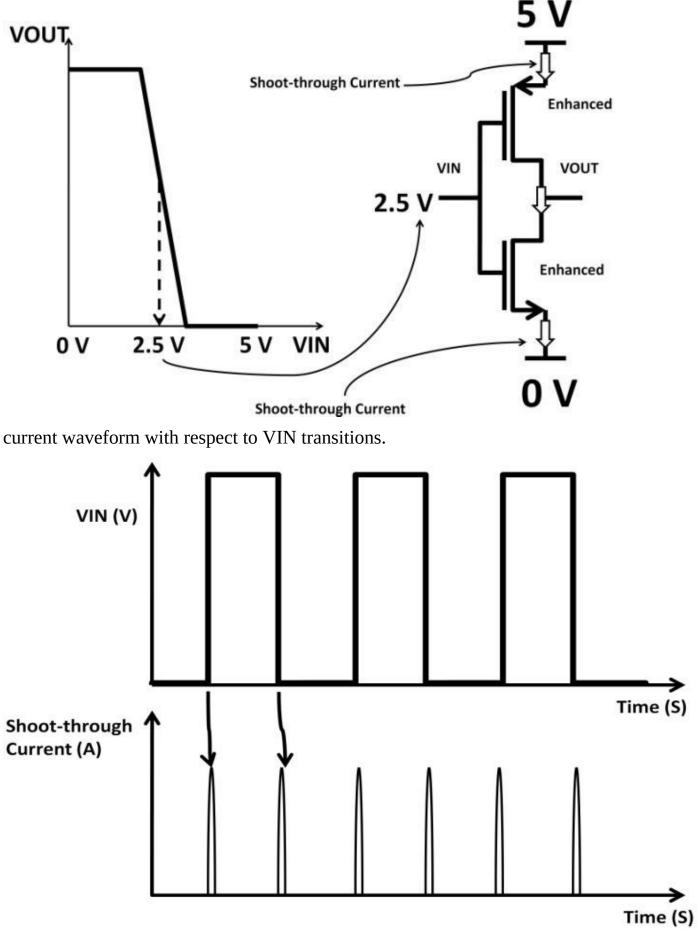

| 198 Shoot-Through                |                 |

| Current                          | - 199           |

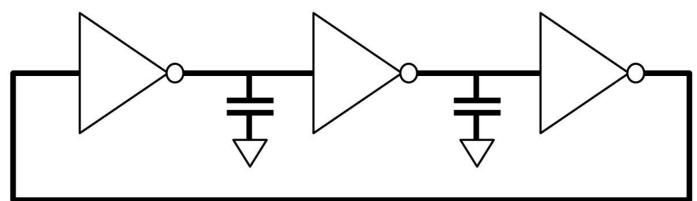

| Ring                             | 155             |

| Oscillator                       |                 |

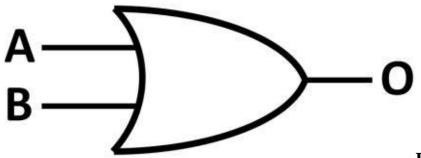

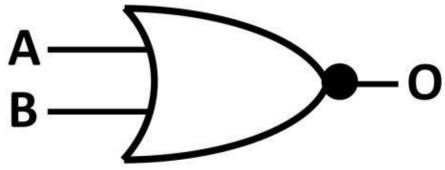

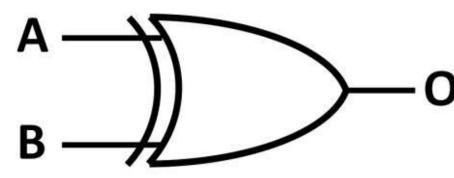

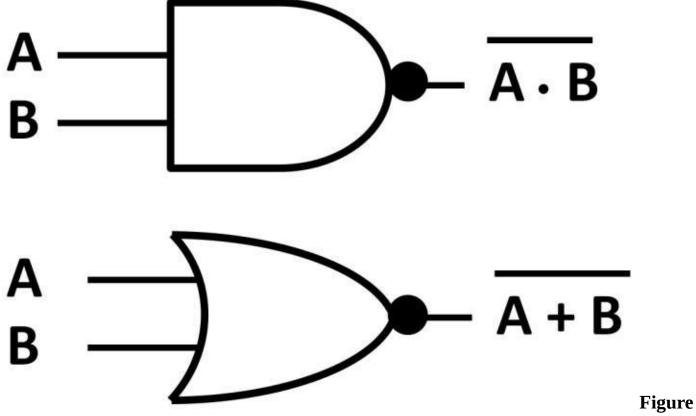

| - 200 OR Logic Gate              |                 |

| 0                                | - 202           |

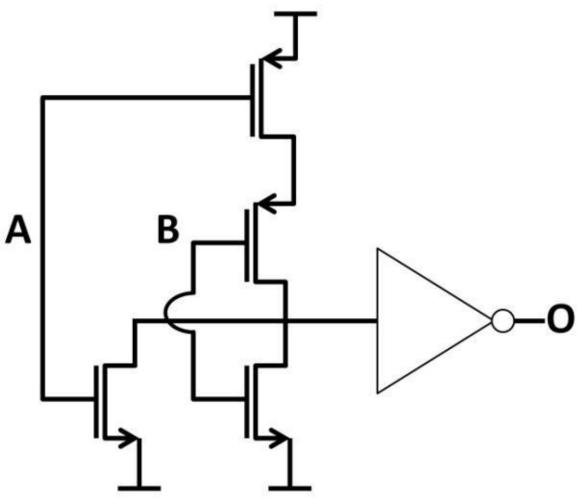

| OR Gate Schematic                | =v=             |

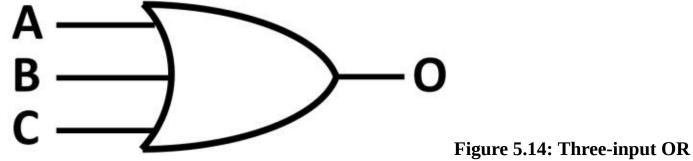

|                                  | - 202 Three-    |

| Input OR                         |                 |

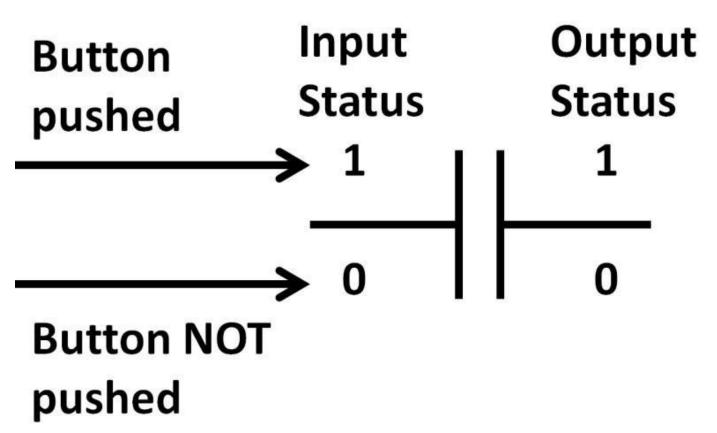

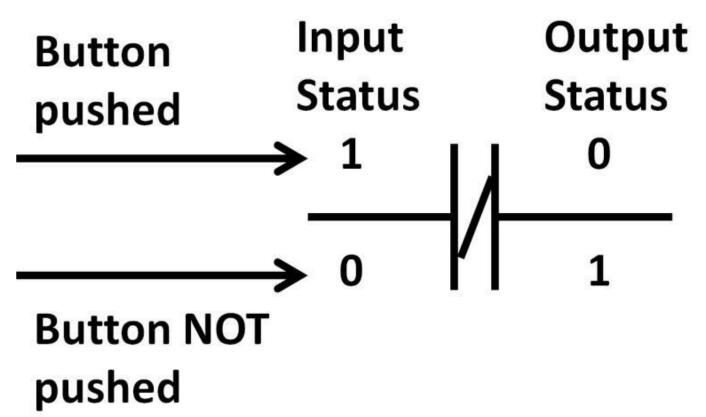

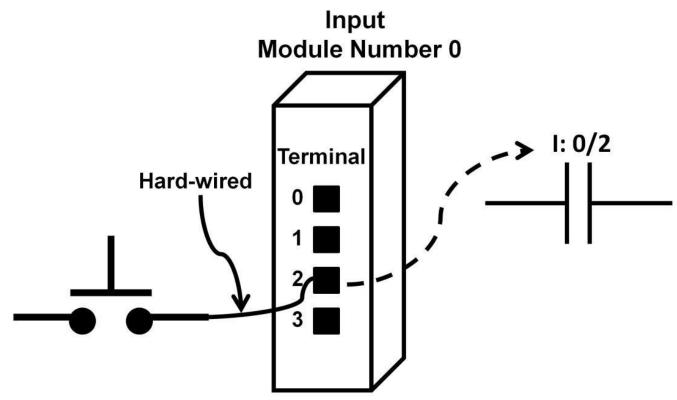

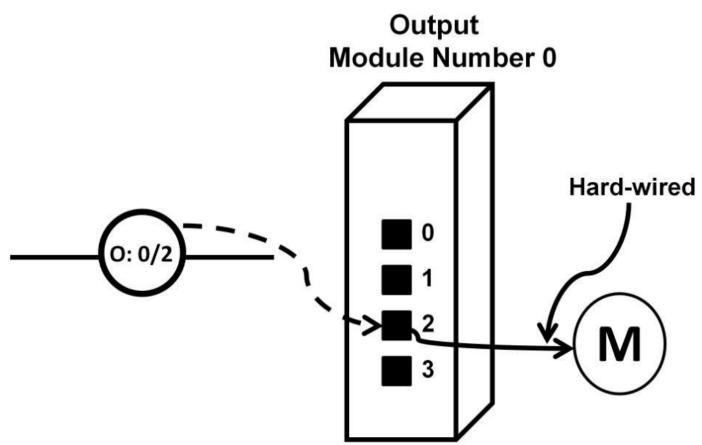

| Gate                             | - 203           |

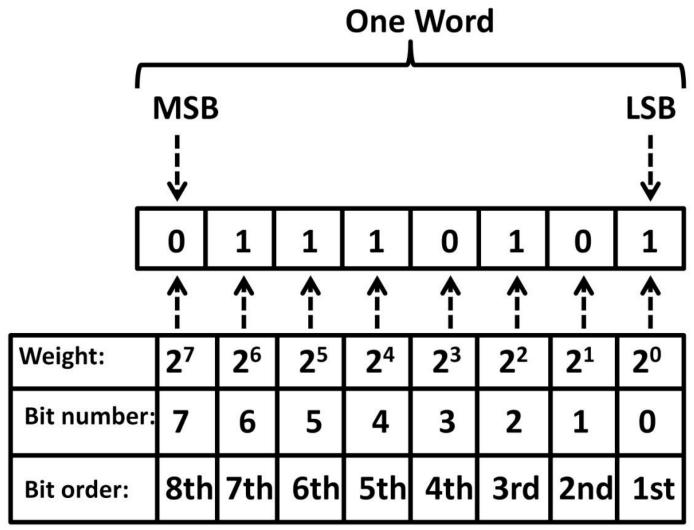

| LSB, MSB                         |                 |

| 202, 1102                        | <u>-</u>        |

| 204 NOR                          |                 |

| Gate                             |                 |

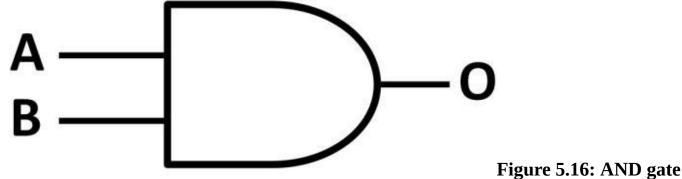

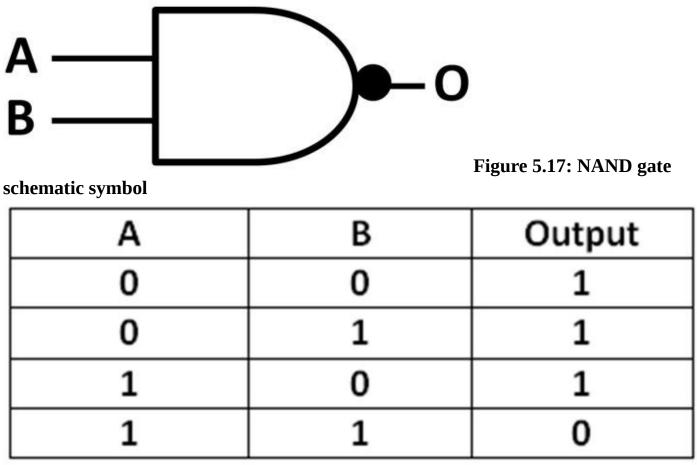

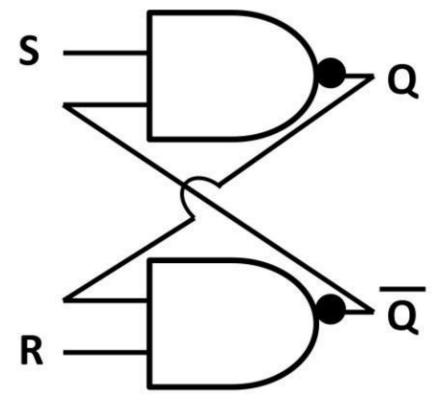

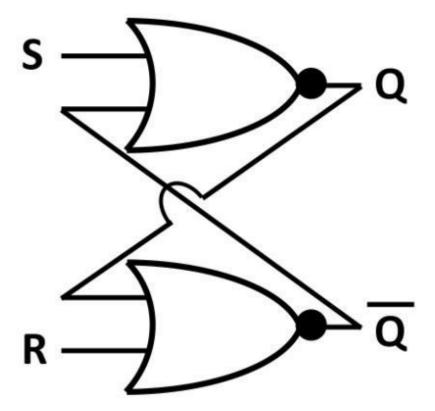

| - 204 AND and NAND               |                 |

| Gates                            | 205             |

| XOR Gate                         |                 |

| 206 Combinational Logic          |                 |

| •                                | 206 Boolean     |

| Algebra                          |                 |

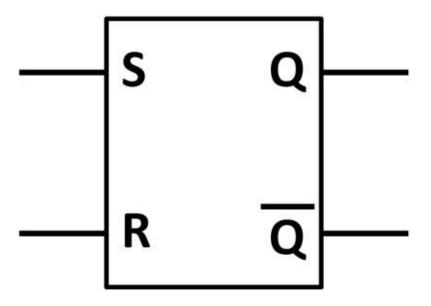

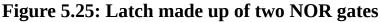

| 207 Latch                        |                 |

|                                  |                 |

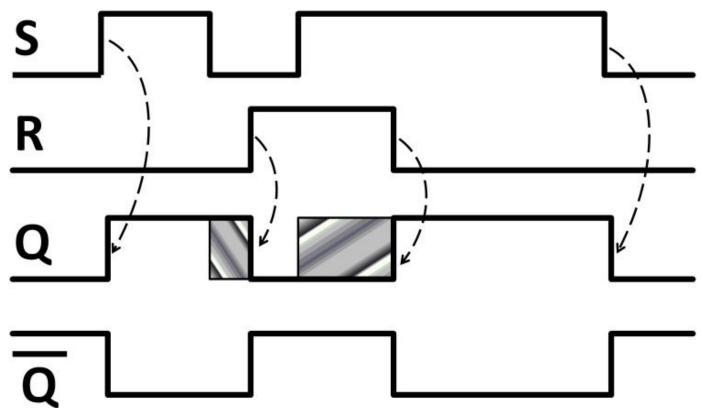

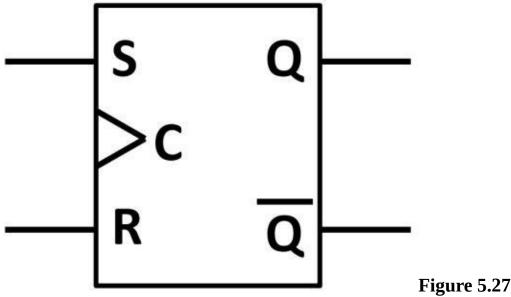

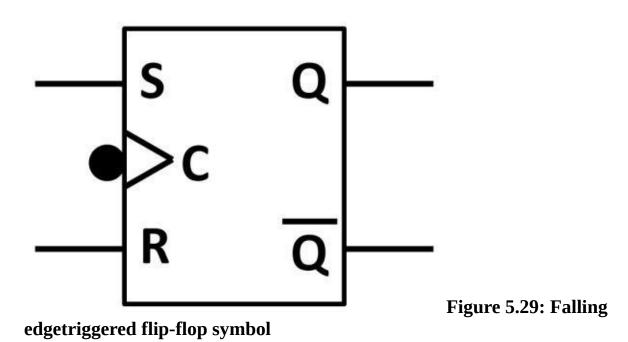

| - 208 Flip-                      |                 |

| Flop                             |                 |

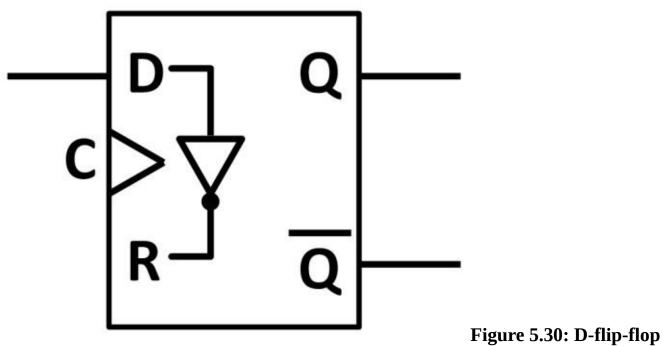

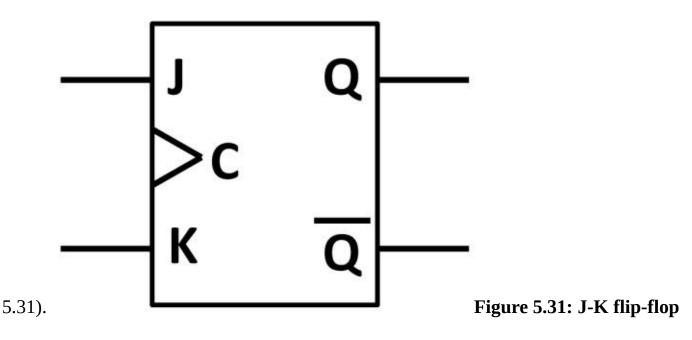

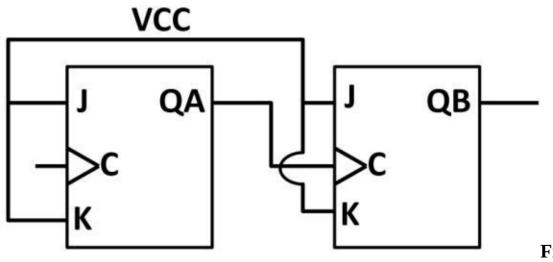

| - 210 D and J-K Flip-            |                 |

| Flops                            | 211             |

| Frequency                        |                 |

| Divider                          |                 |

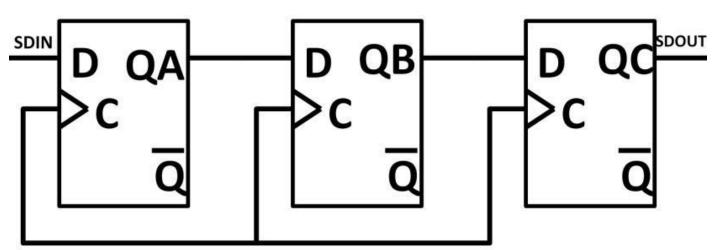

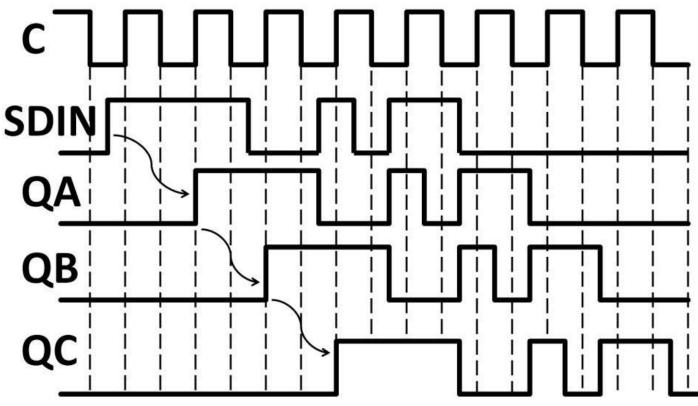

| 211 Shift                        |                 |

| Register                         |                 |

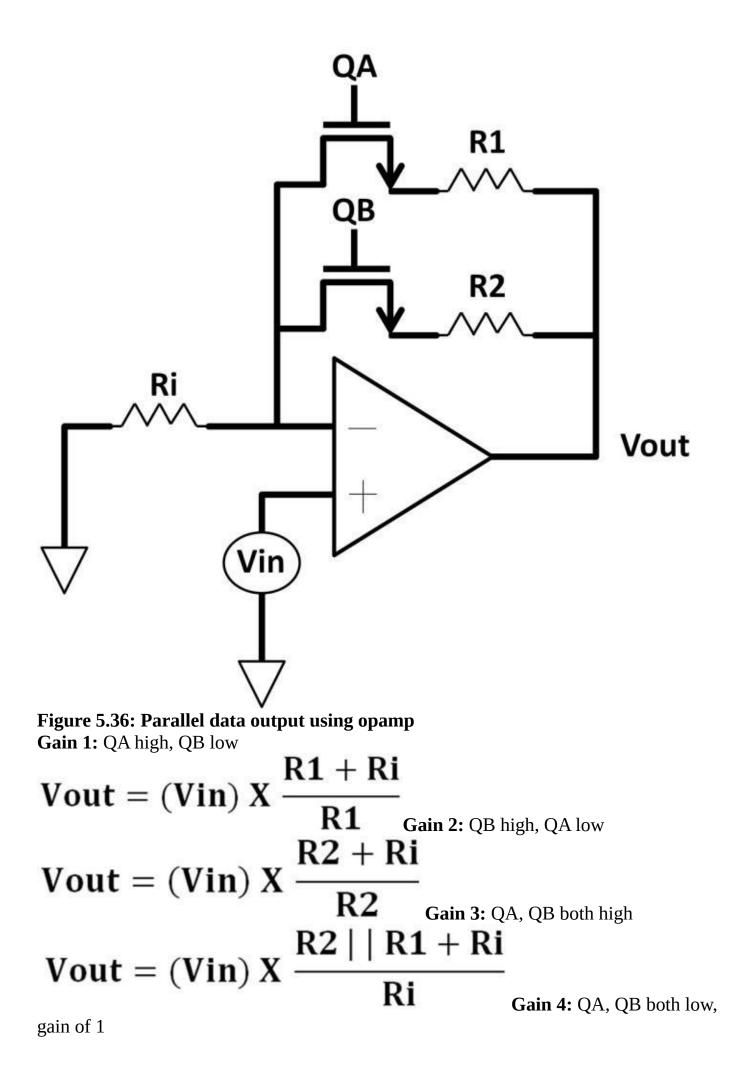

| - 213 Parallel Data Transmission |                 |

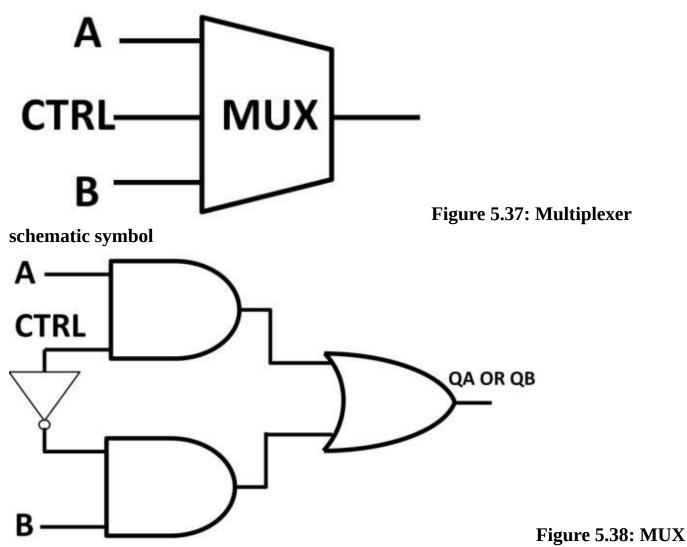

|                                  | 214 Multiplexer |

|                                  | - 215           |

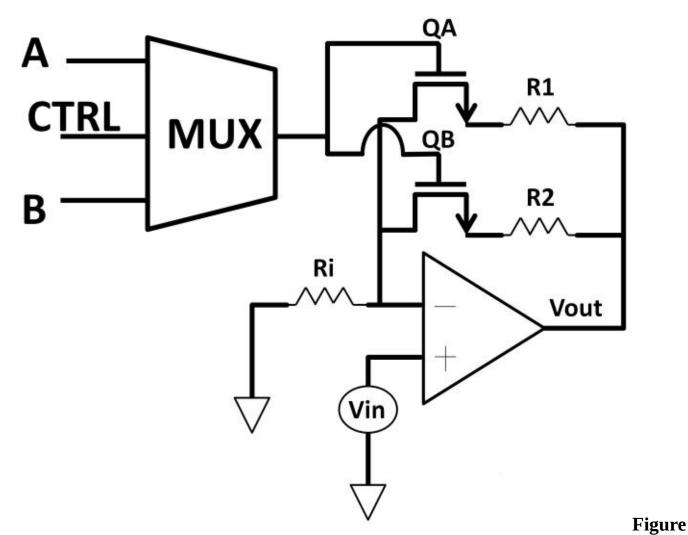

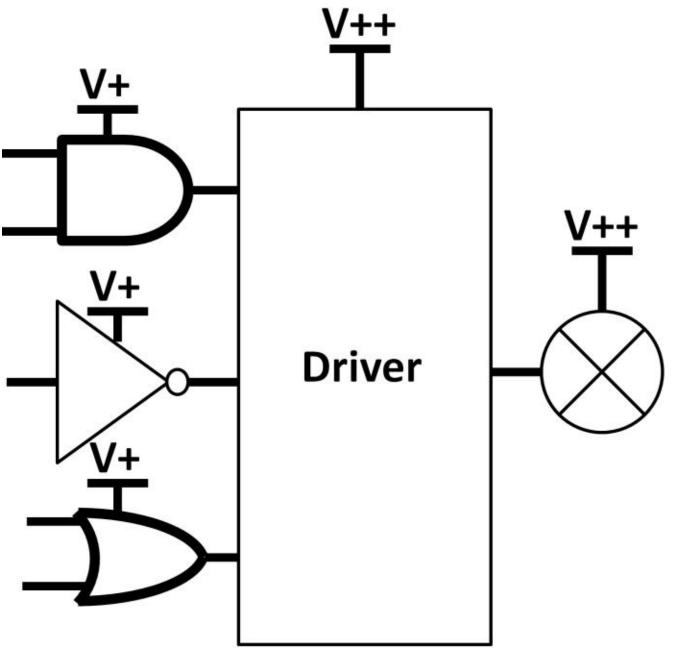

| Mixed-signal                     | 340             |

|                                  | 216             |

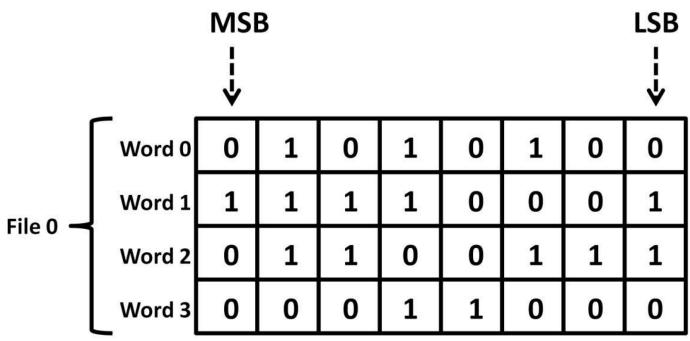

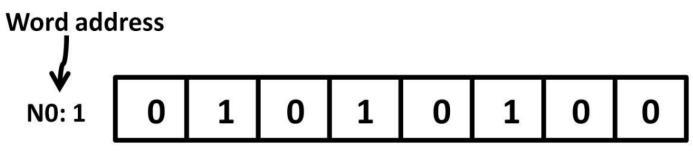

| Level Shifter                    | 017             |

| Multi I avor                     | 217             |

| Multi-Layer<br>Board             | 01 <i>7</i>     |

| Board                            | 217             |

| Digital Voltage Levels           |                 |

#### **Table of Contents XV**

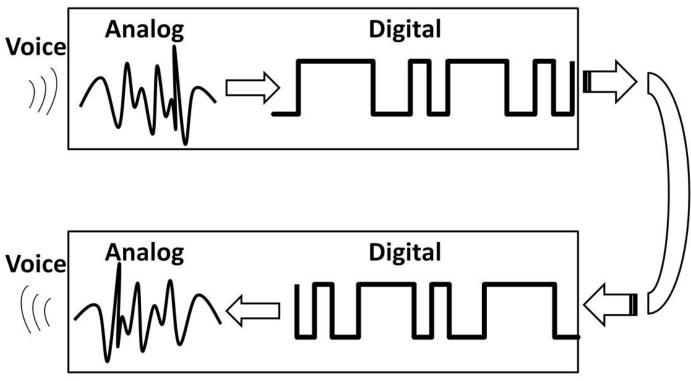

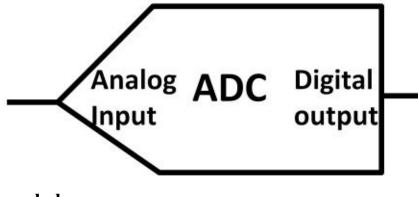

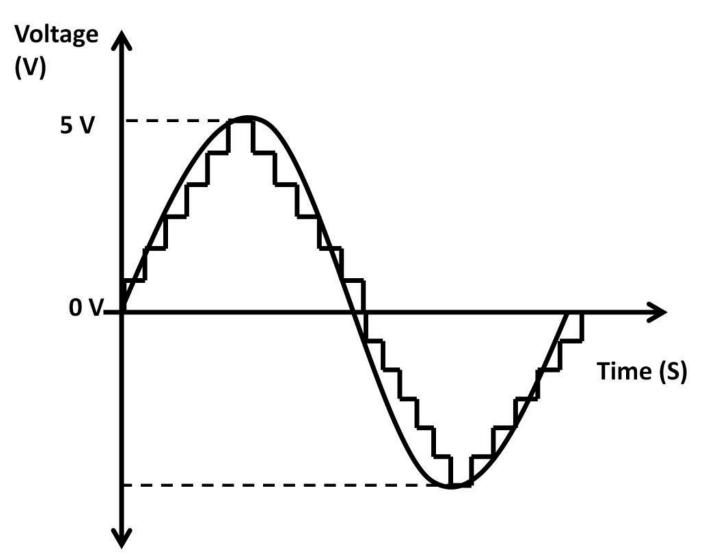

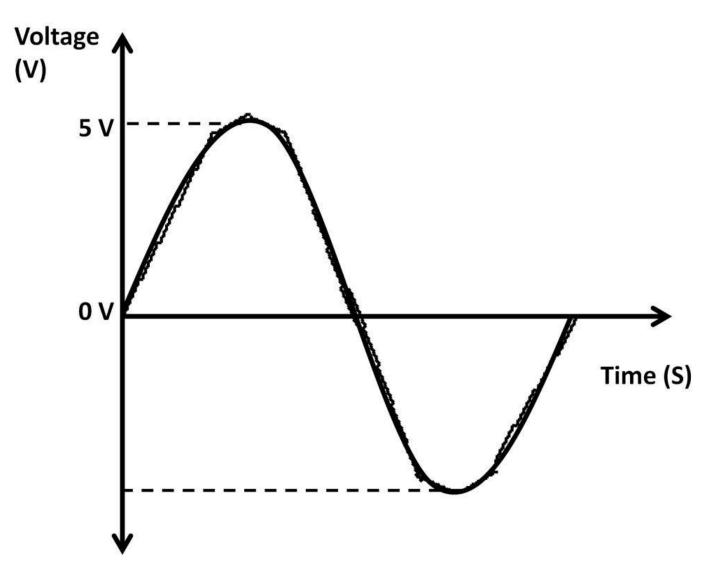

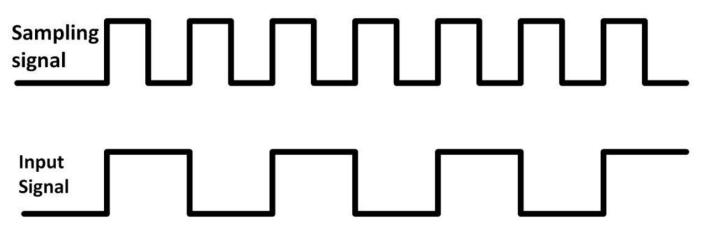

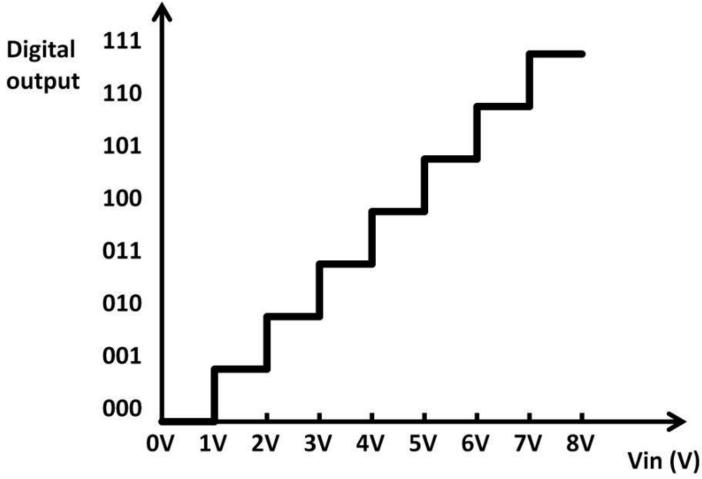

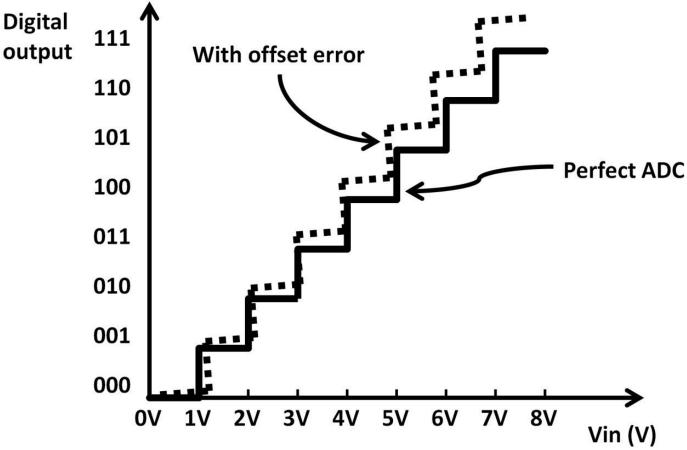

| Analog-to-Digital Converter                        | 219 Nyquist     |       |

|----------------------------------------------------|-----------------|-------|

| Frequency                                          |                 | _     |

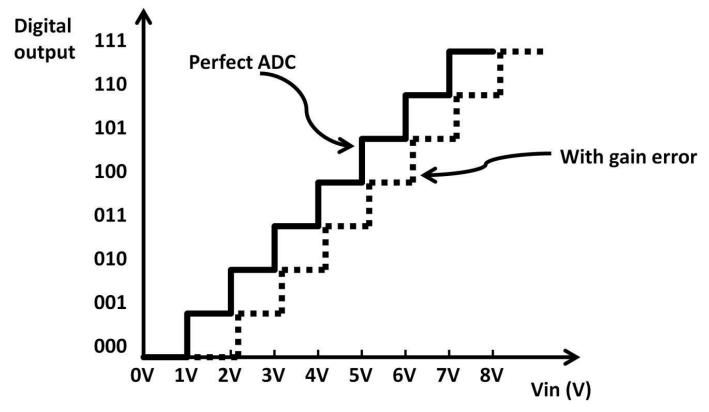

| 221 ADC Gain and Offset Errors                     | 222 Digital-to- |       |

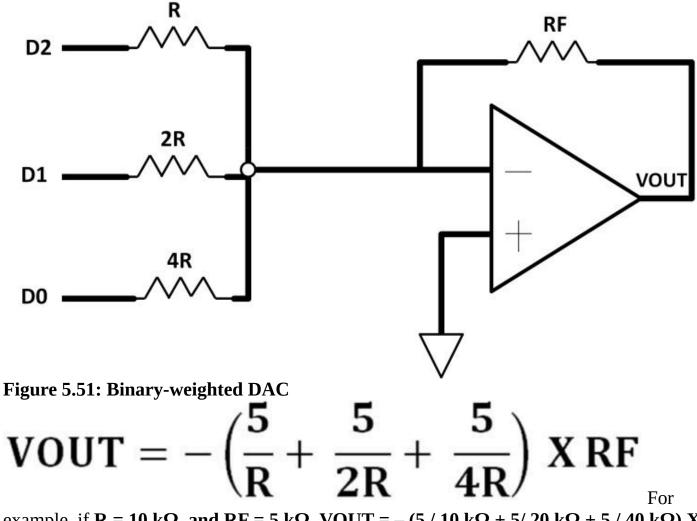

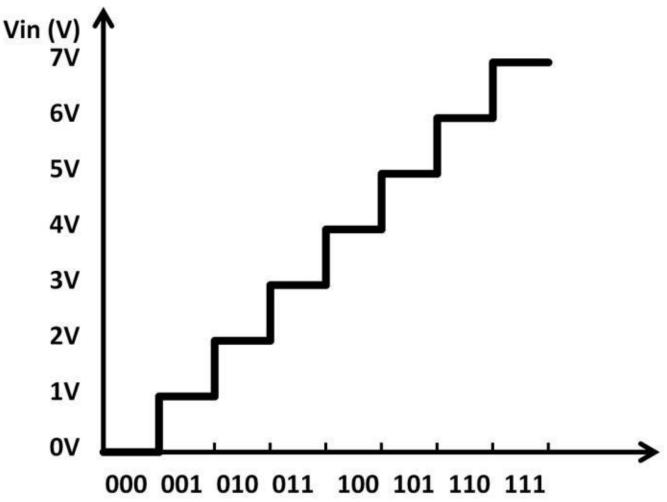

| Analog Converter                                   |                 |       |

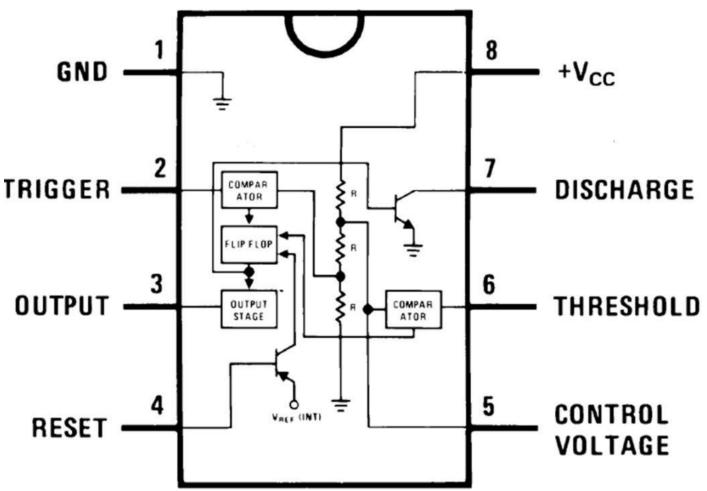

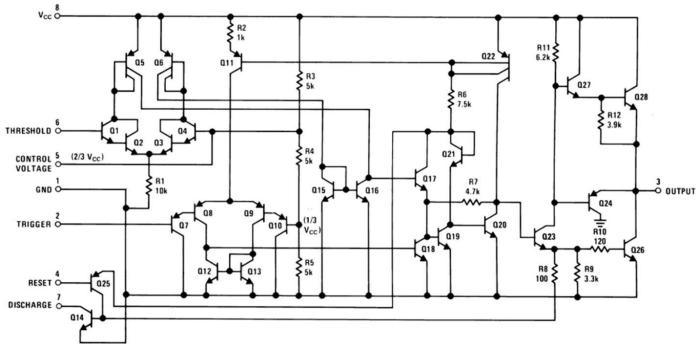

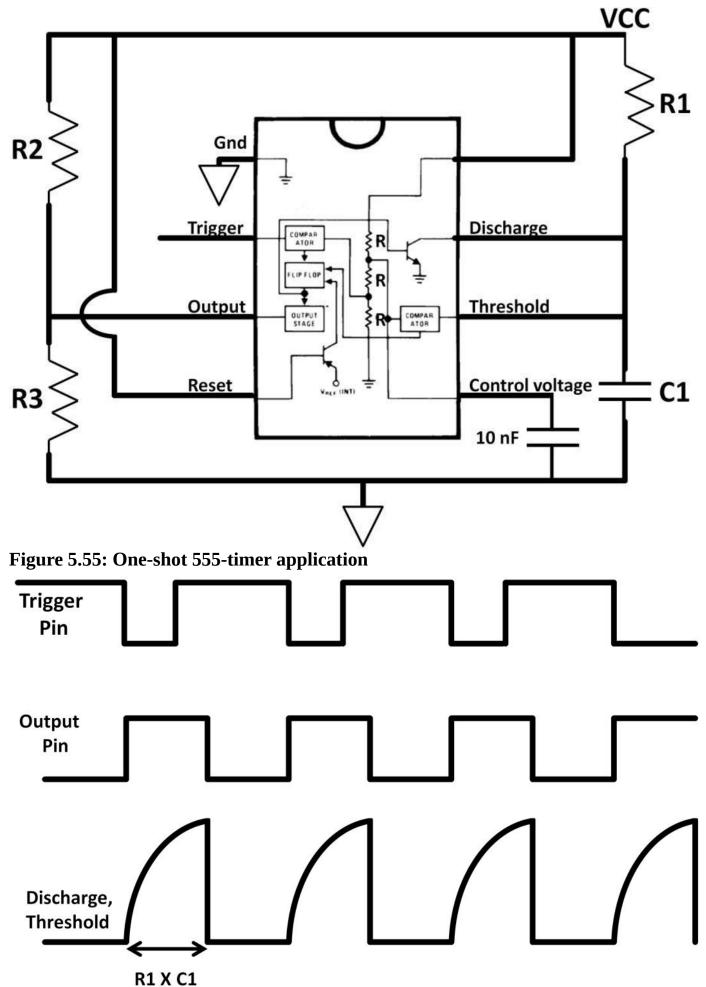

| 224 Binary-Weighted DAC                            | 225 555-        |       |

| Timer                                              |                 | - 226 |

| Summary                                            |                 | 0     |

| 230 Quiz                                           |                 |       |

| - 230                                              |                 |       |

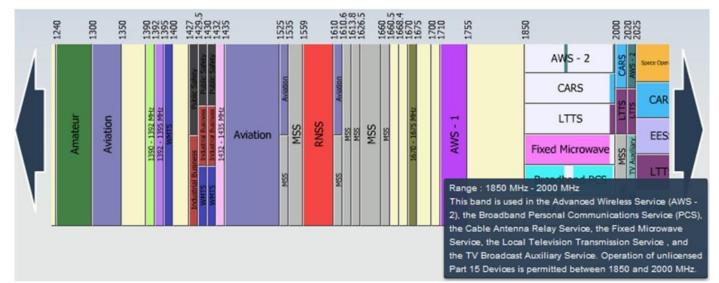

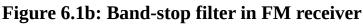

| Chapter 6: Communications                          | 231             |       |

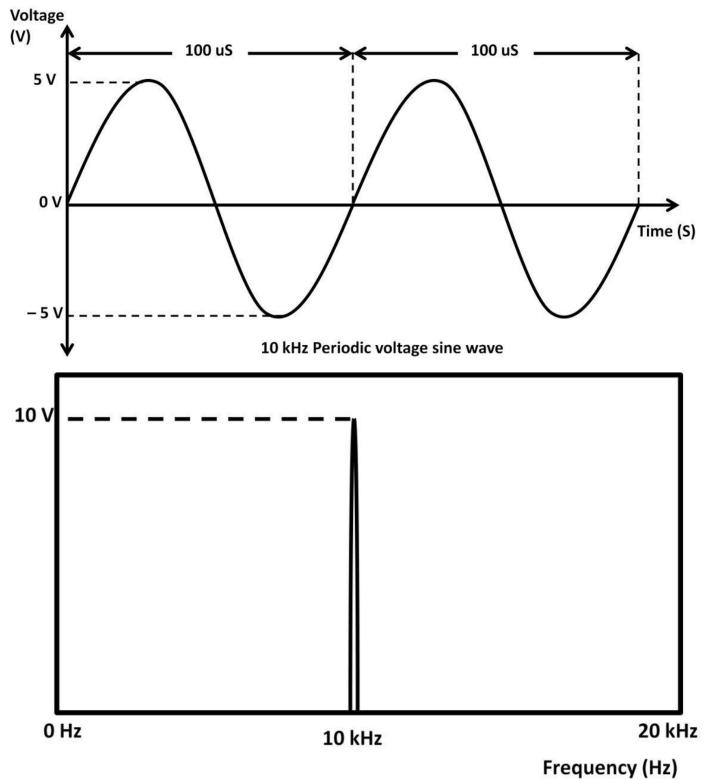

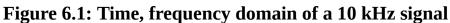

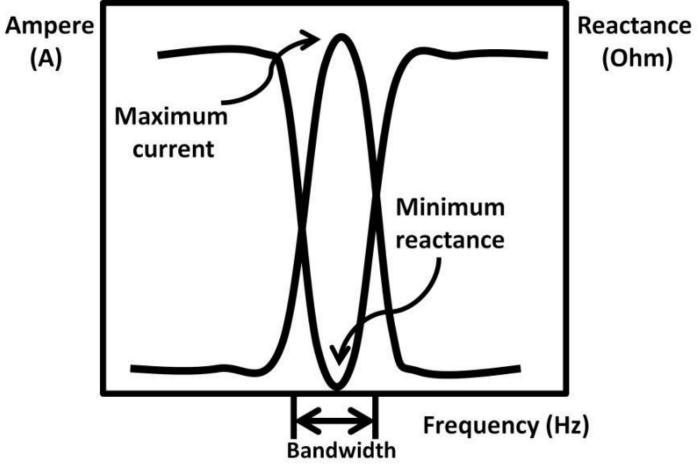

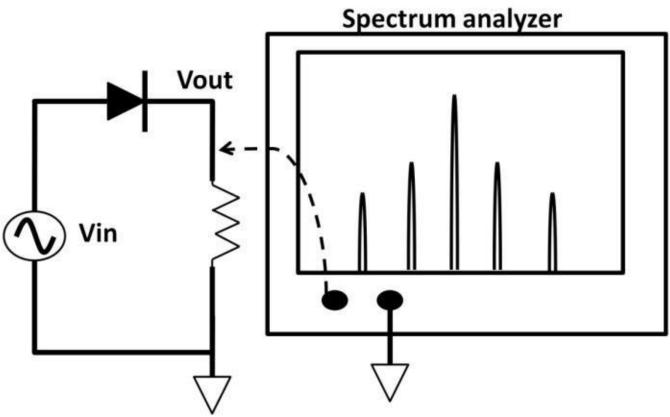

| Time versus Frequency Domains                      | 232 Harmonics,  |       |

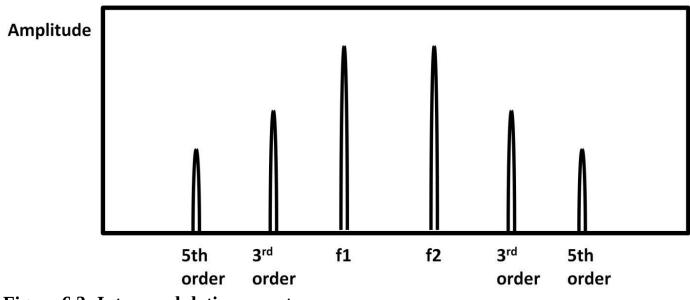

| Distortion, and Inter-modulation<br>234 Modulation |                 | -     |

| Bit Rate, USB, and Baud                            | 236 C = F λ     | 236   |

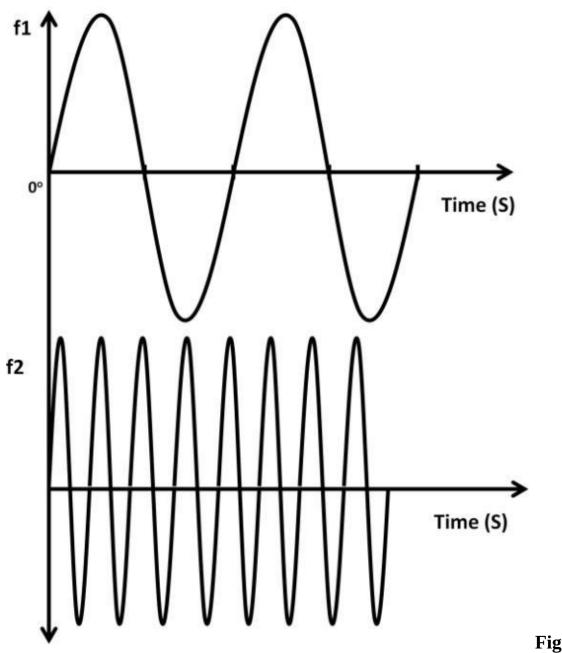

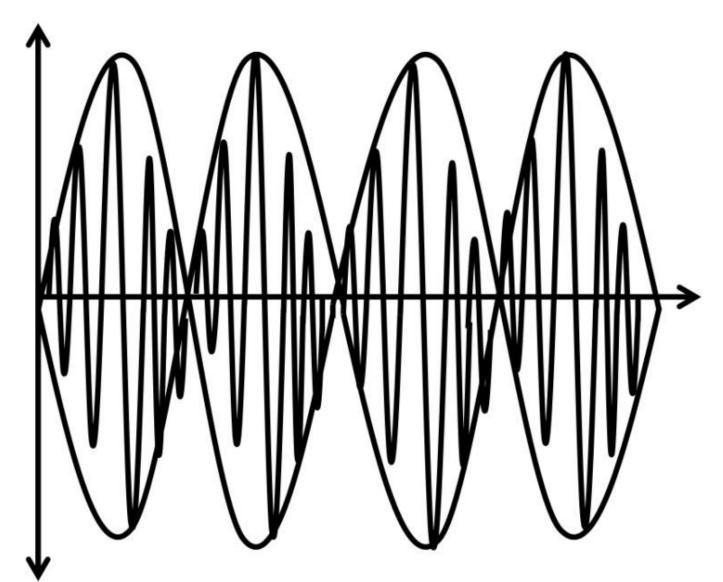

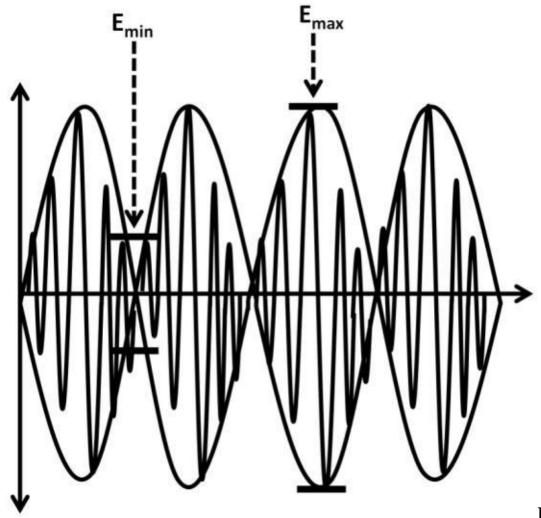

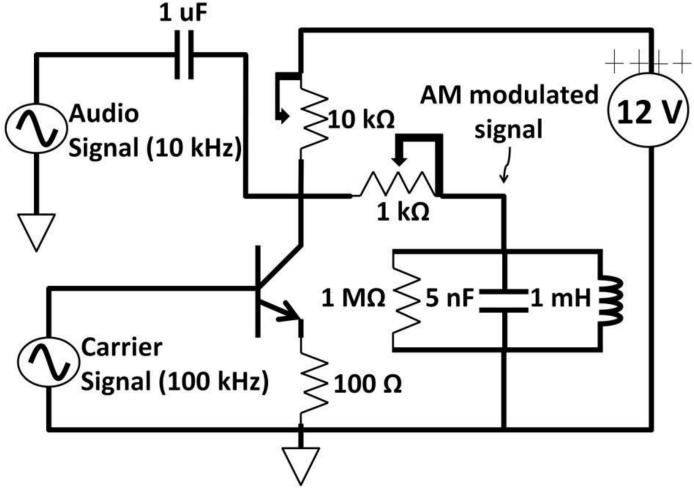

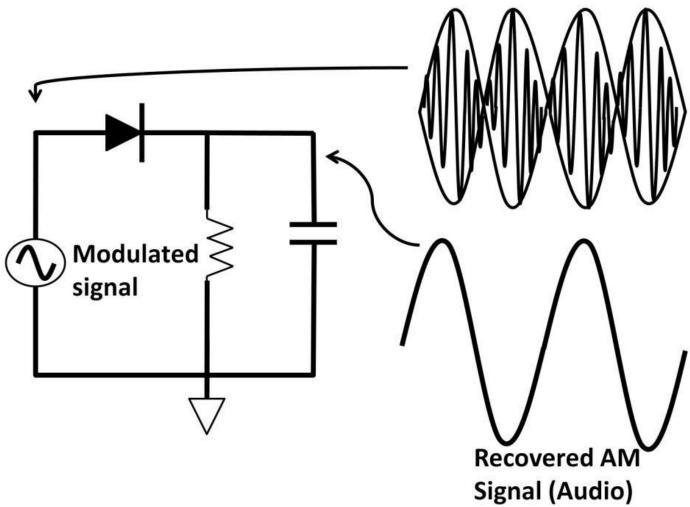

| 237 Amplitude Modulation                           | - 238           |       |

| Modulation Index and Bessel Chart                  |                 |       |

| Transmitter                                        |                 |       |

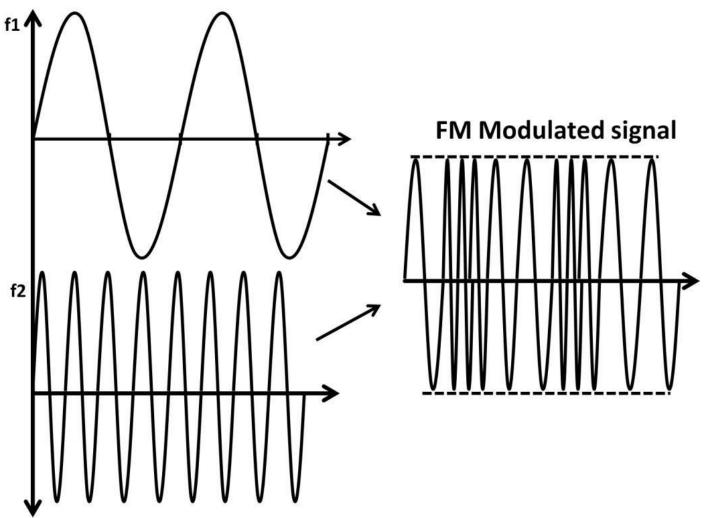

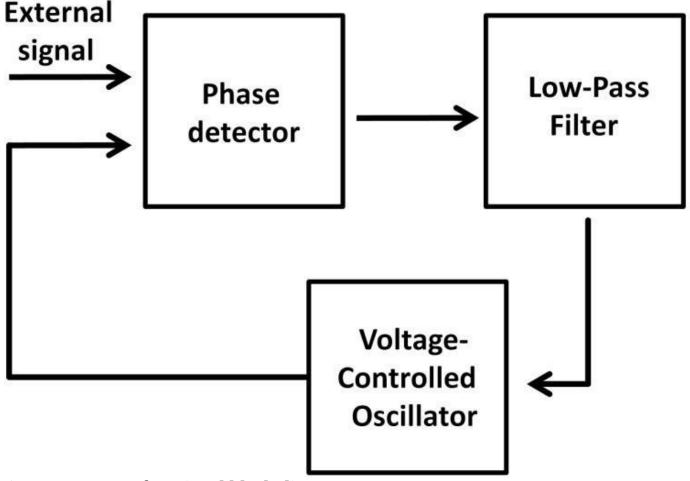

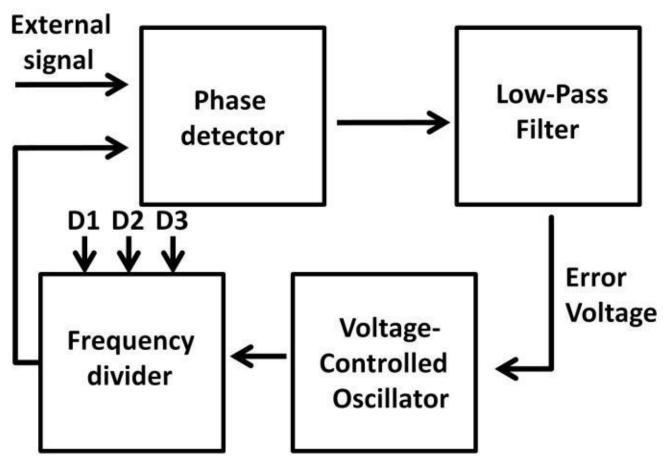

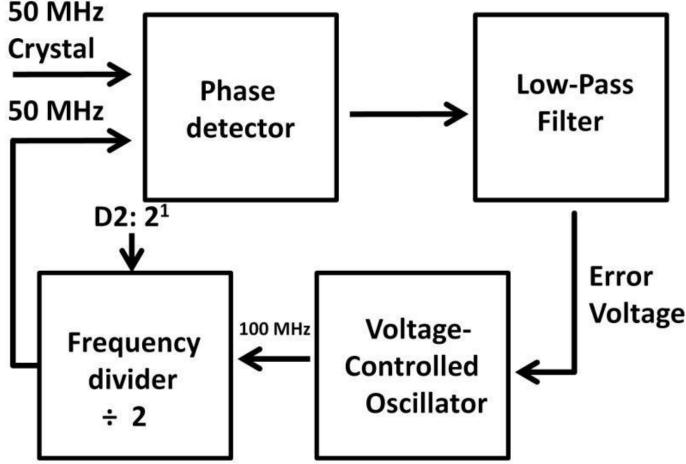

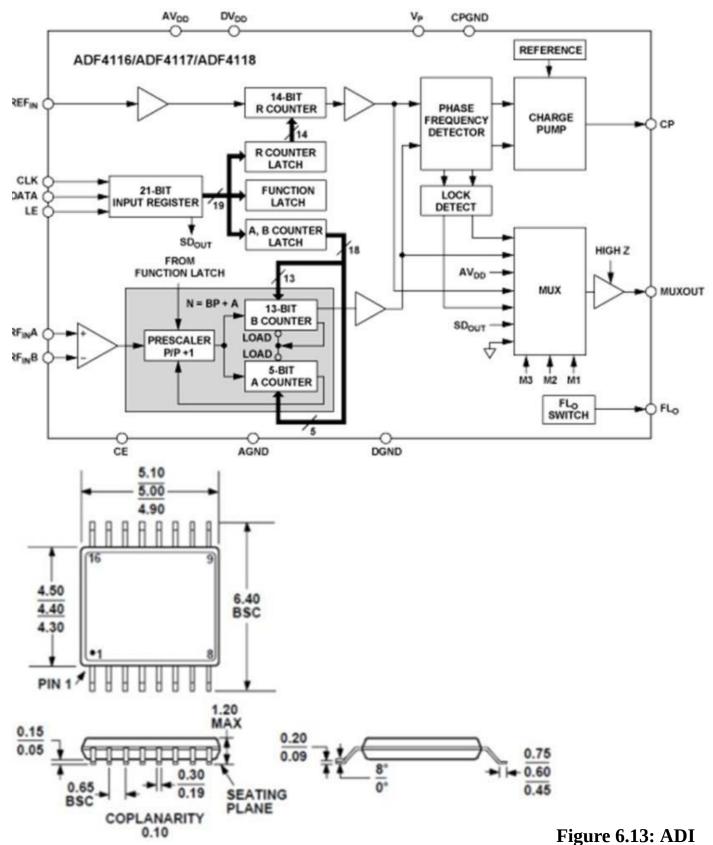

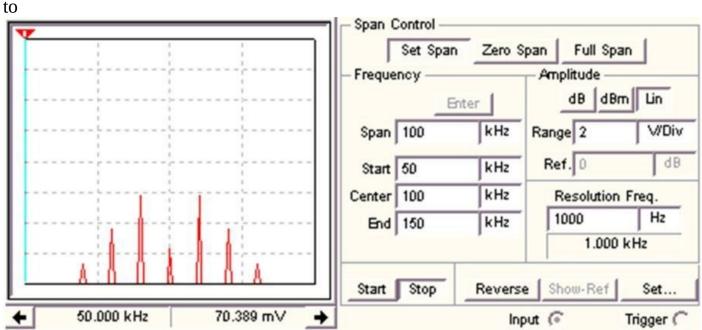

| - 240 Frequency Modulation                         | - 241 Phase     |       |

| Lock Loop (PLL)                                    | 242 Sumr        | nary  |

| 245 Quiz                                           |                 |       |

| - 245                                              |                 |       |

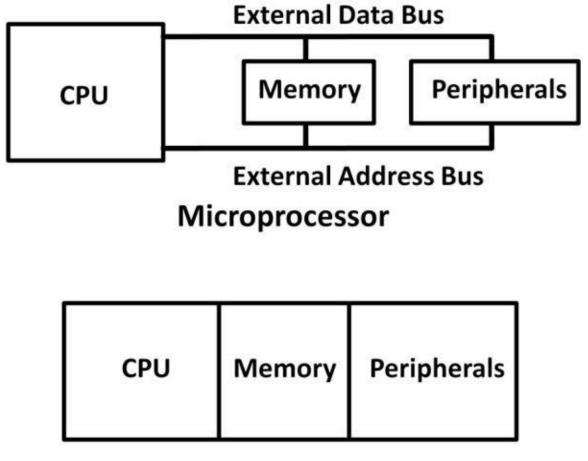

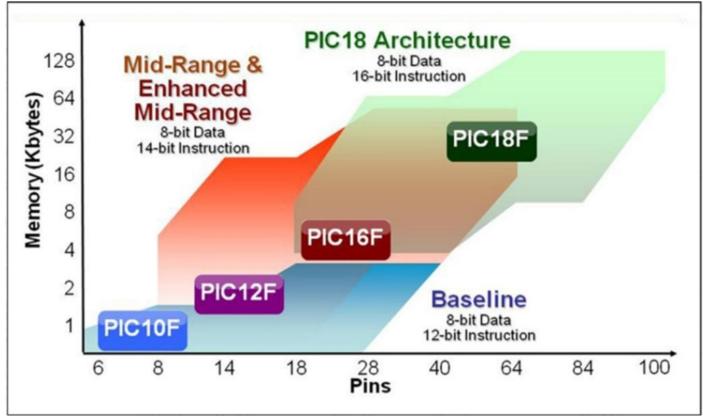

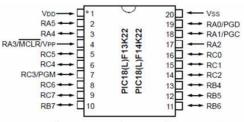

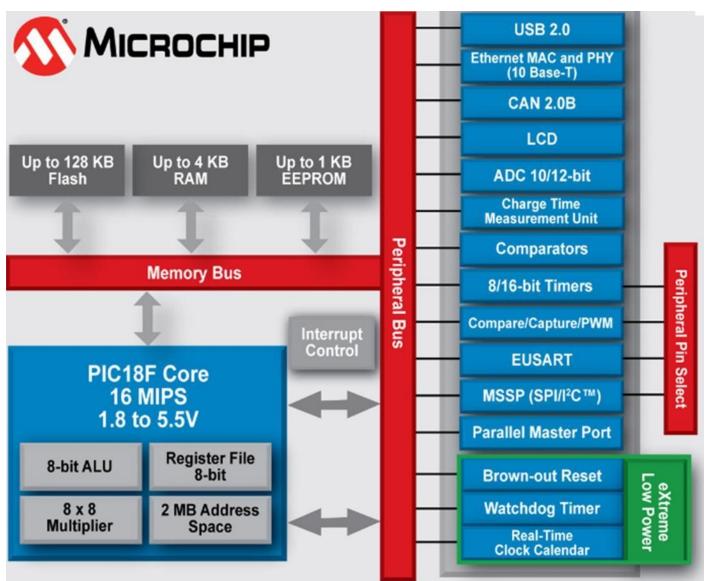

| Chanter 7. Microcontrollers                        | - 247           |       |

Chapter 7: Microcontrollers \_\_\_\_\_ - 247

| MCU                                       |                     |

|-------------------------------------------|---------------------|

| Parameters                                |                     |

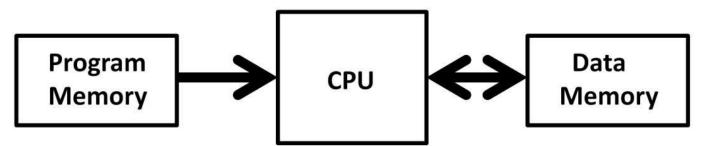

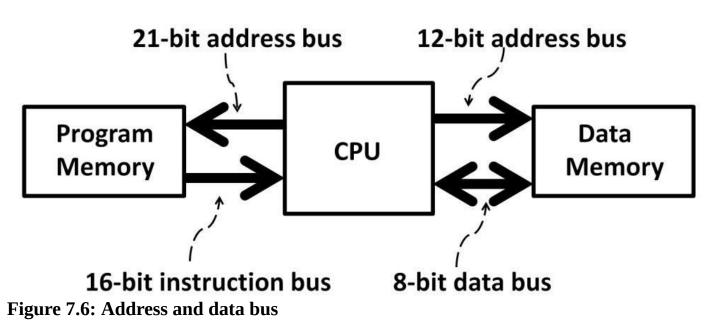

| - 248 Harvard Architecture                |                     |

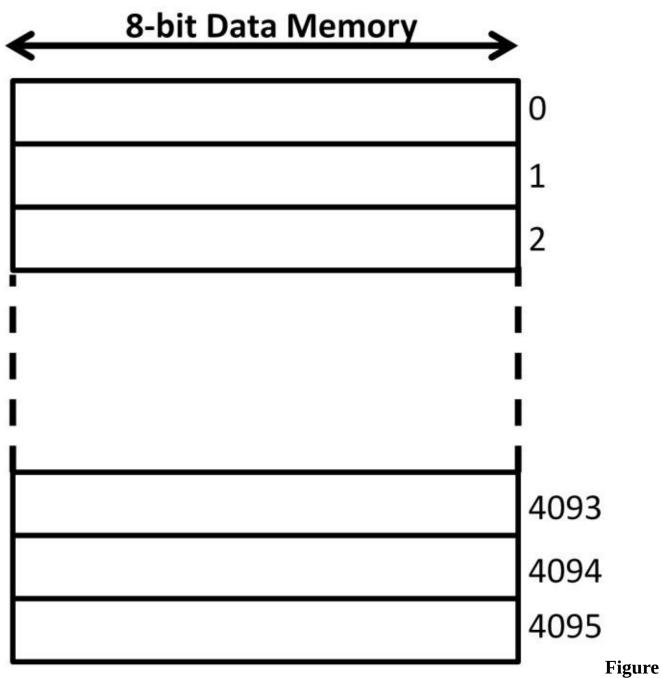

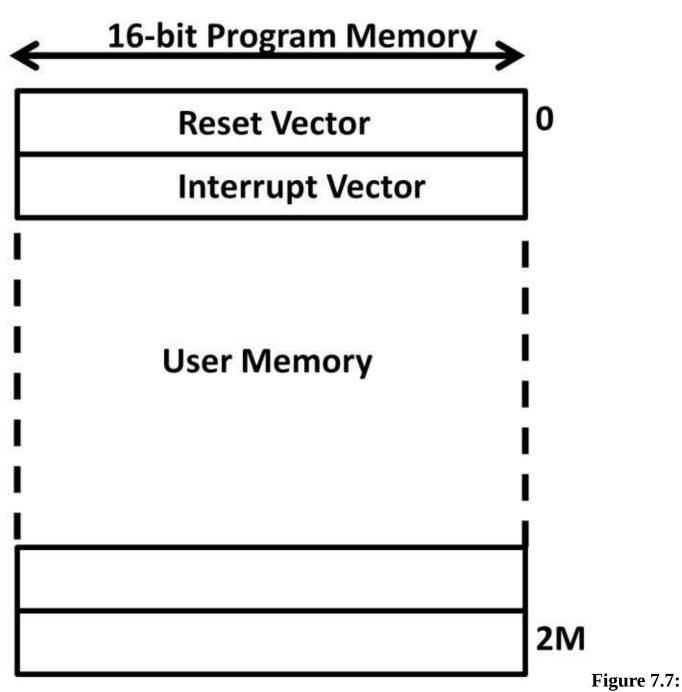

|                                           | 251 Data and        |

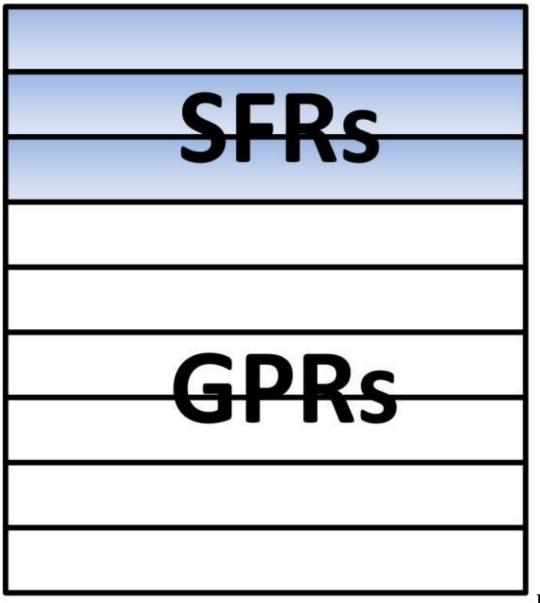

| Program Memory                            |                     |

| 251 MCU Instructions                      |                     |

|                                           | 255                 |

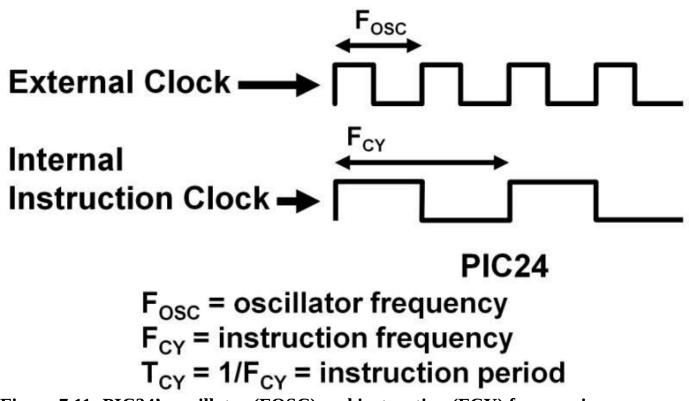

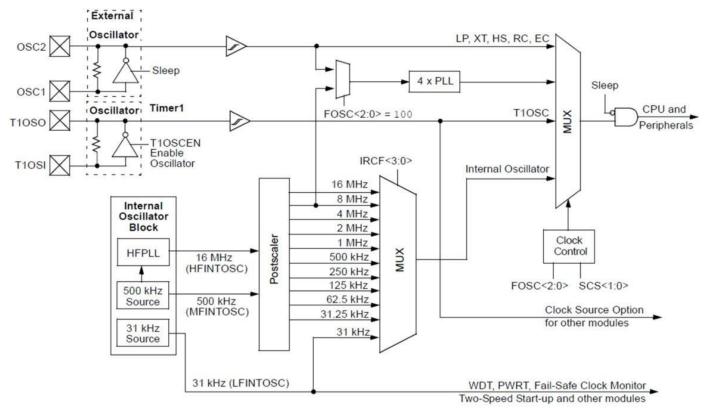

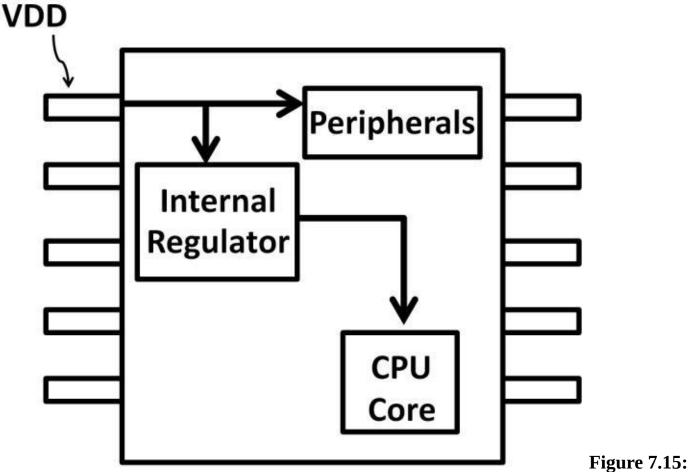

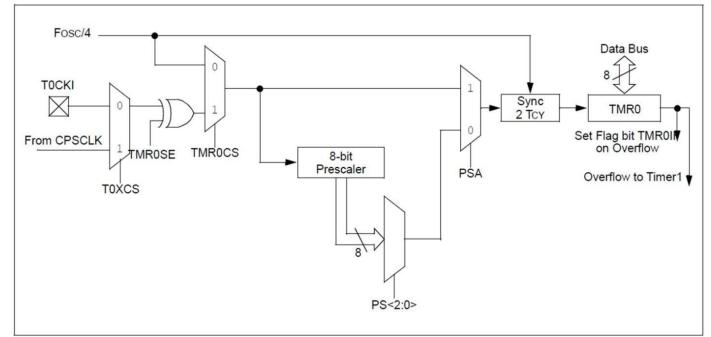

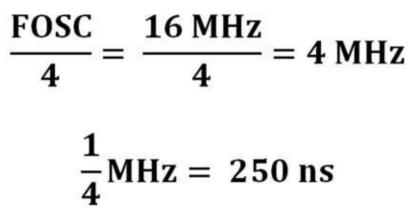

| Instruction Clock                         | 257                 |

| Internal Oscillator                       | 257                 |

|                                           | - 258               |

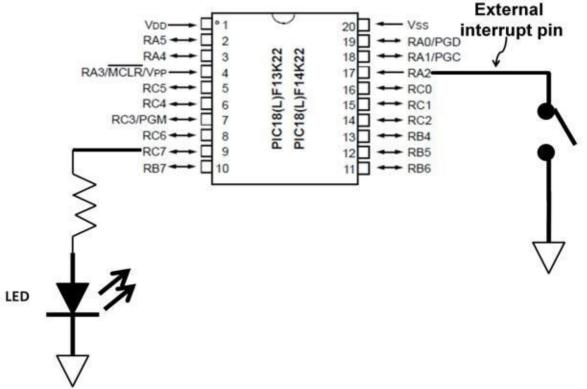

| Interrupt                                 | 200                 |

| 260 Special Features                      |                     |

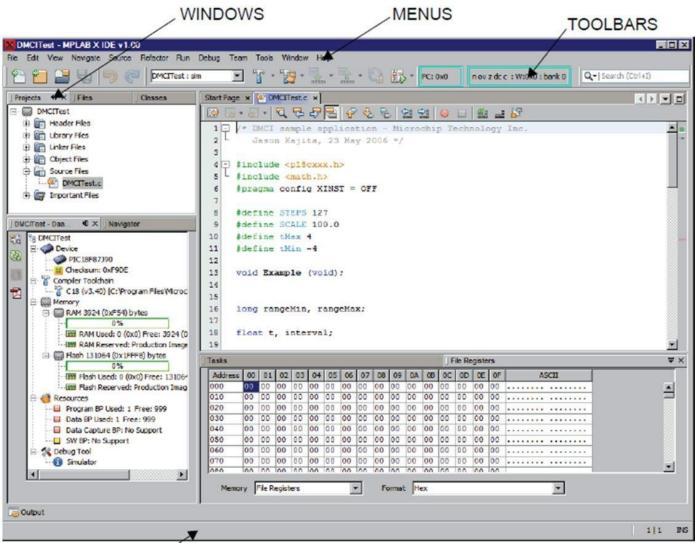

|                                           | - 261               |

| Development                               |                     |

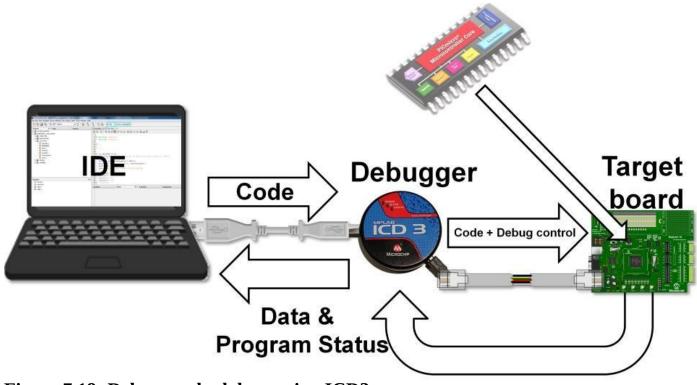

| Tools                                     | 262                 |

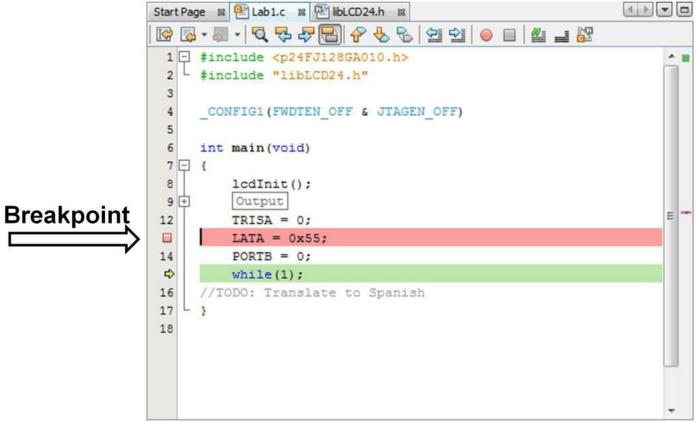

| Debugger                                  |                     |

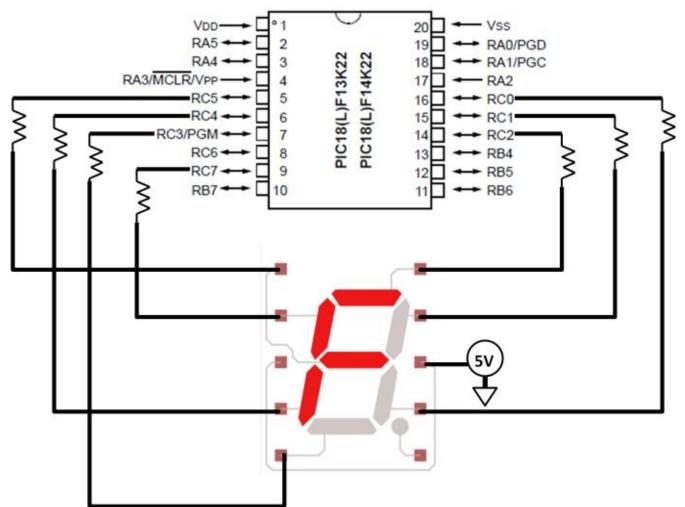

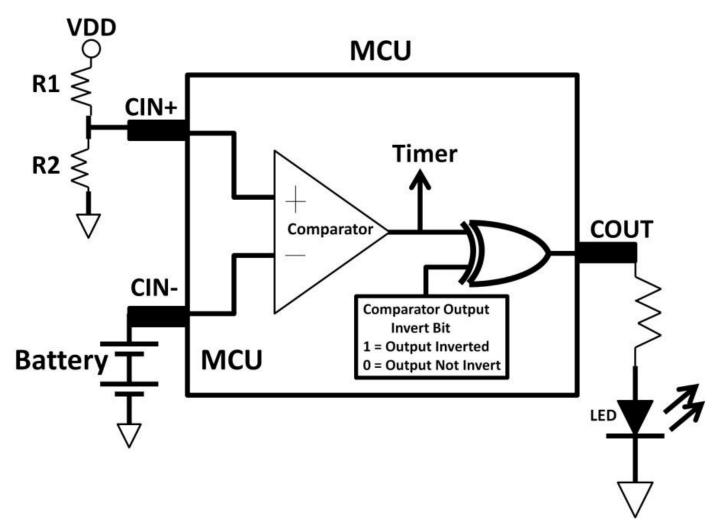

| - 263 Design Example:                     |                     |

| Comparator                                | 265                 |

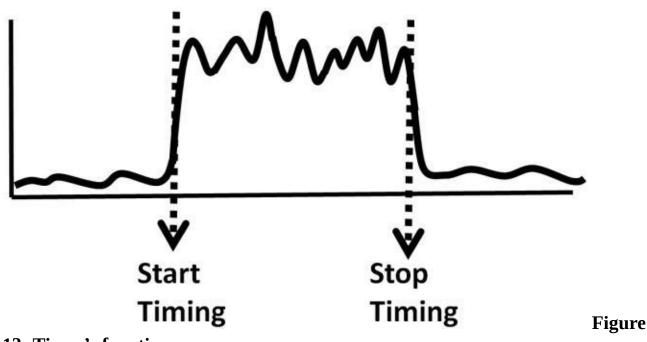

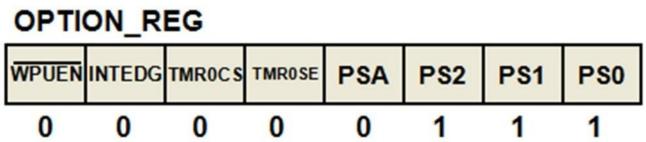

| Design Example: Timer                     |                     |

|                                           |                     |

| 271 Quiz                                  |                     |

| - 271                                     |                     |

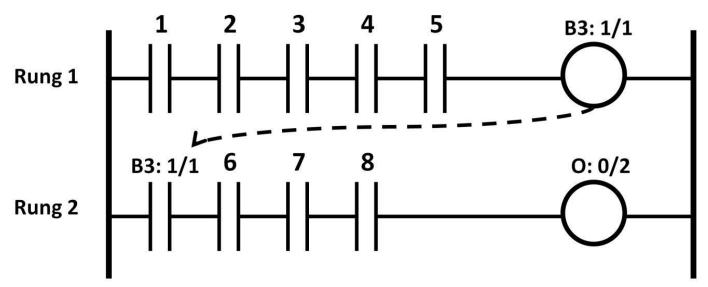

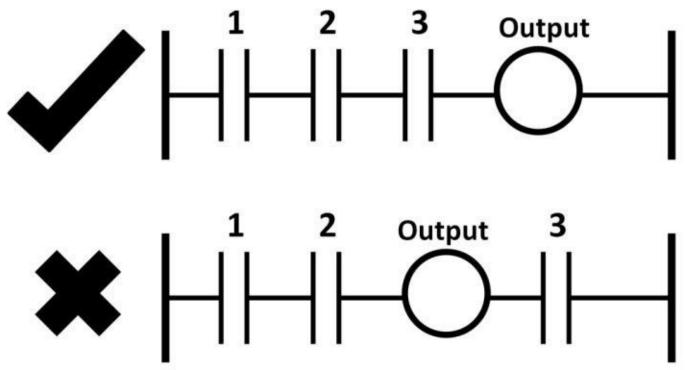

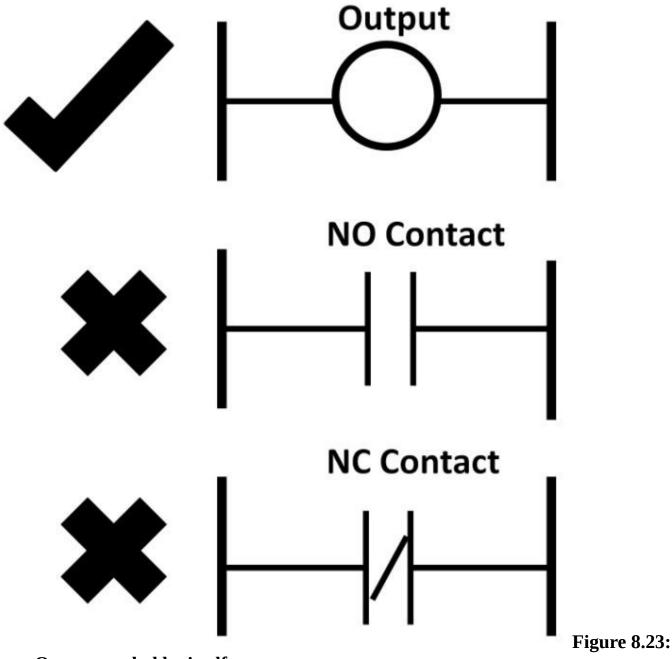

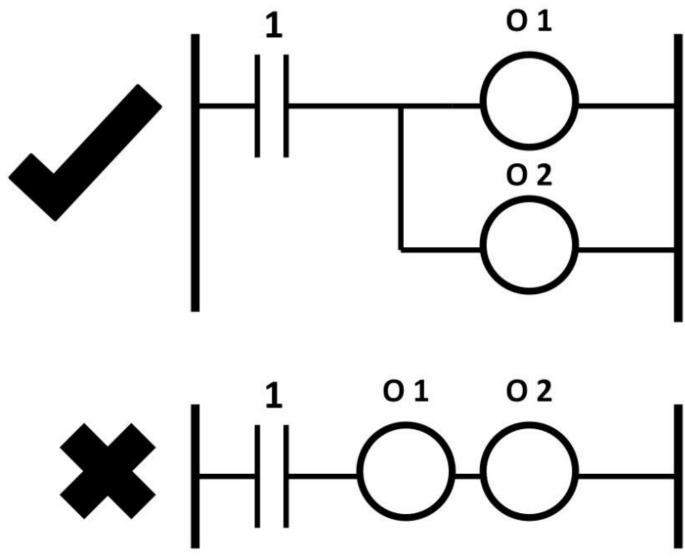

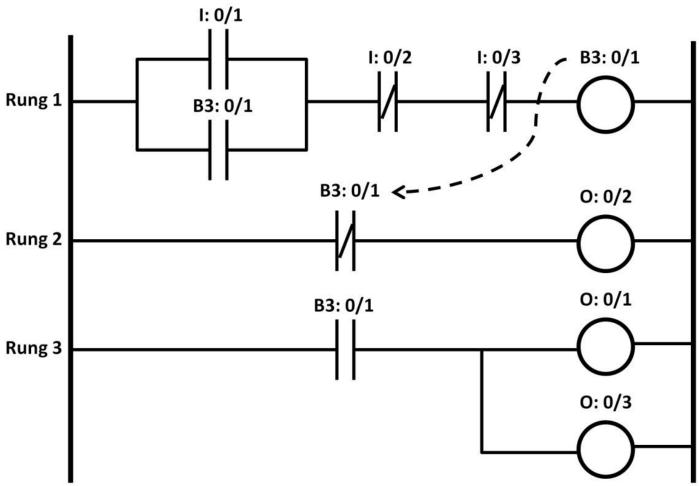

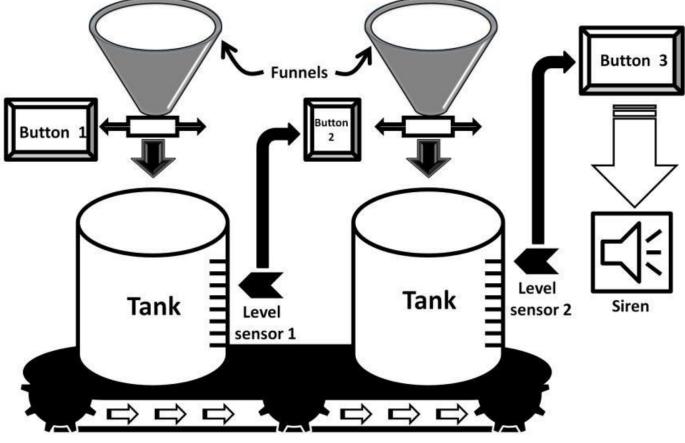

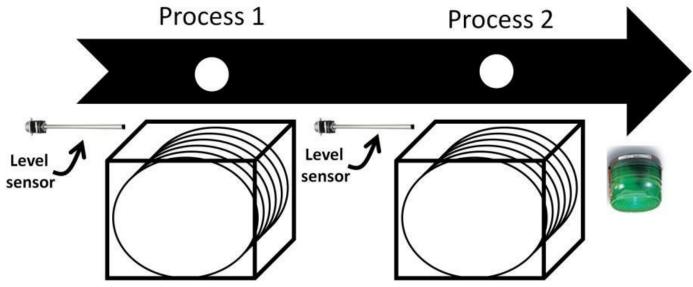

| Chapter 8: Programmable Logic Controllers | 273                 |

| History                                   |                     |

| 273 PLC Benefits                          |                     |

|                                           | 275                 |

| PLC Components                            | 276 PLC             |

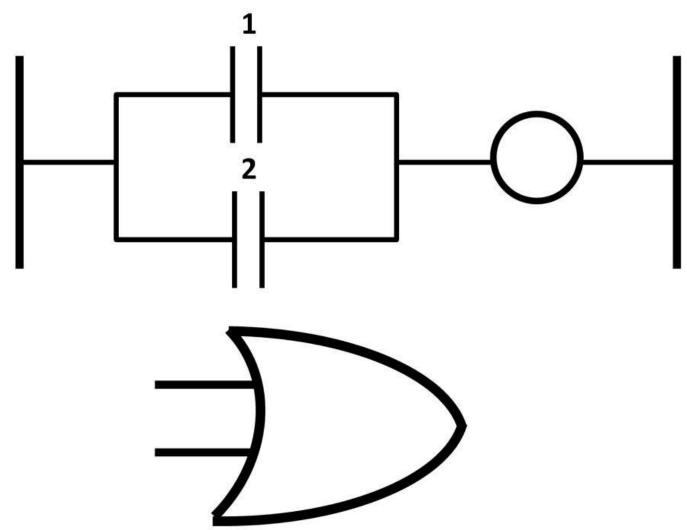

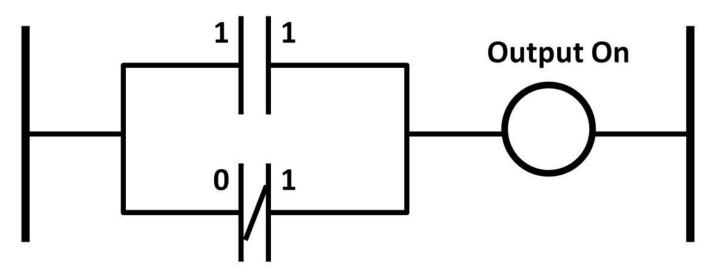

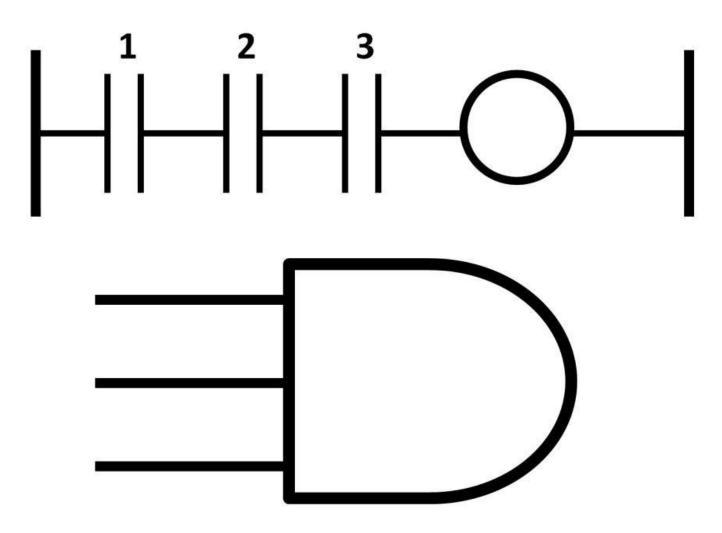

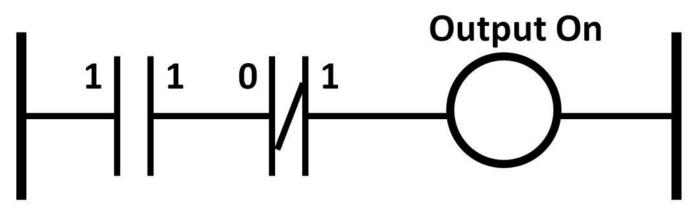

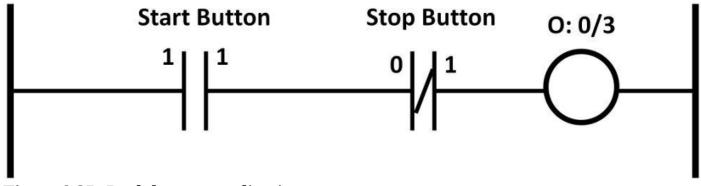

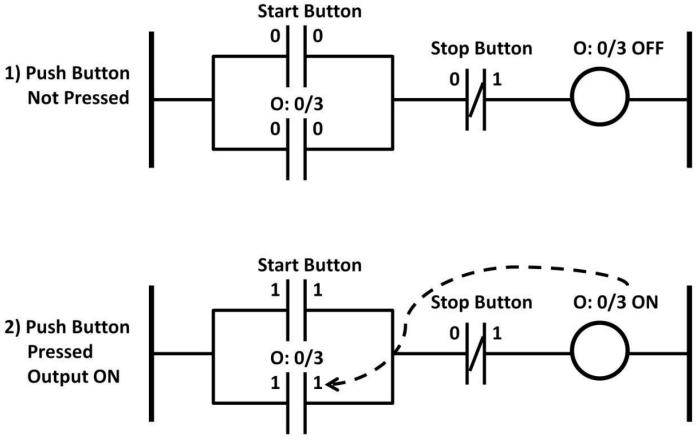

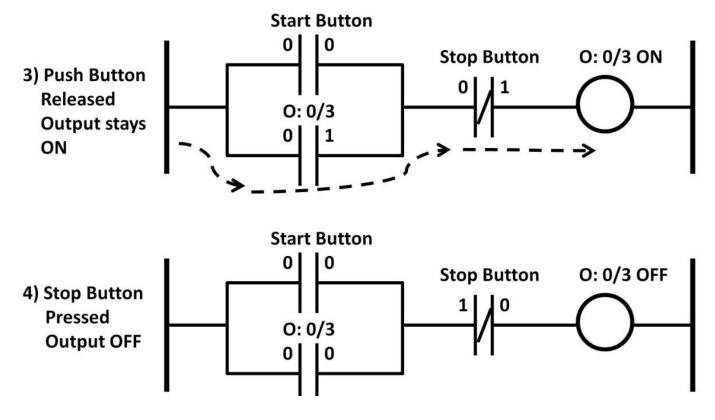

| Programming and Ladder Logic              | = 2701 EC           |

|                                           | 278 PLC Programming |

| Example                                   |                     |

| Programming Syntax                        |                     |

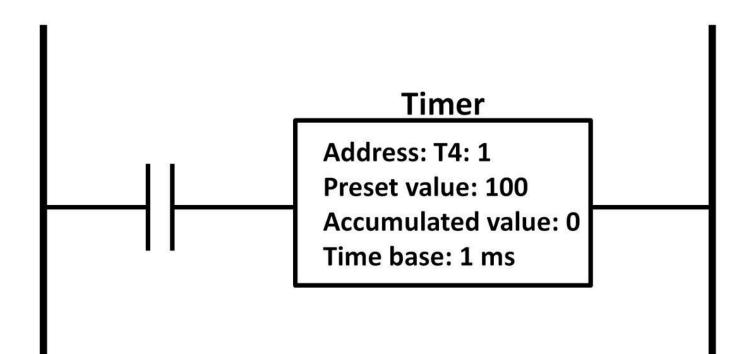

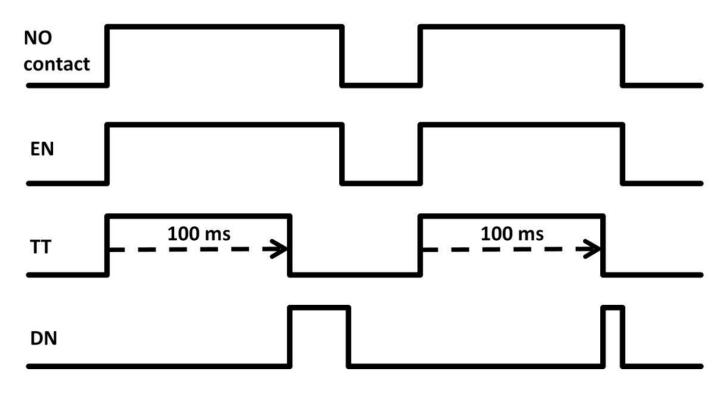

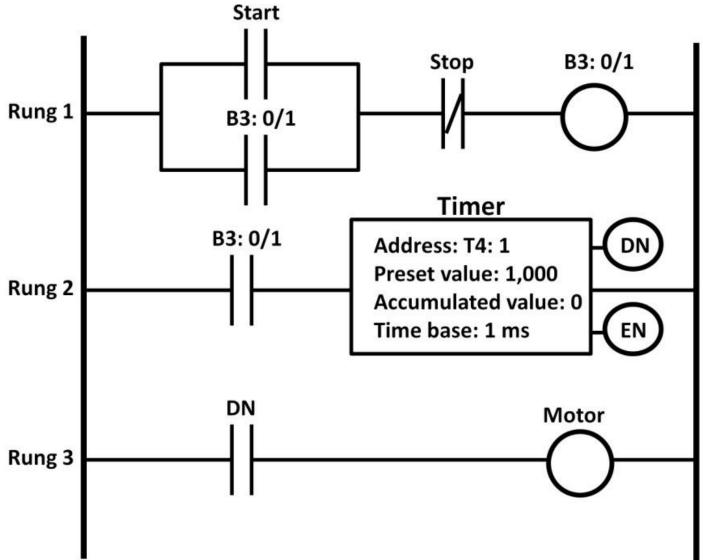

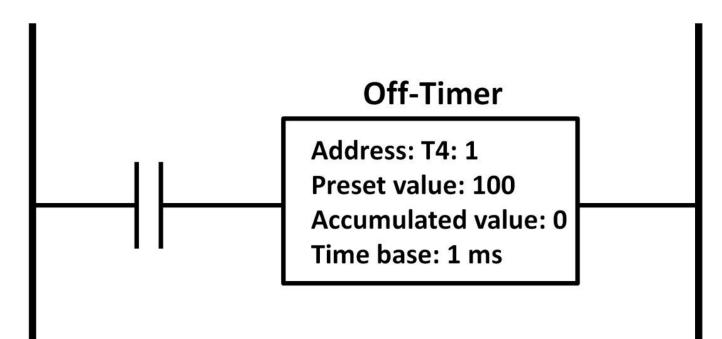

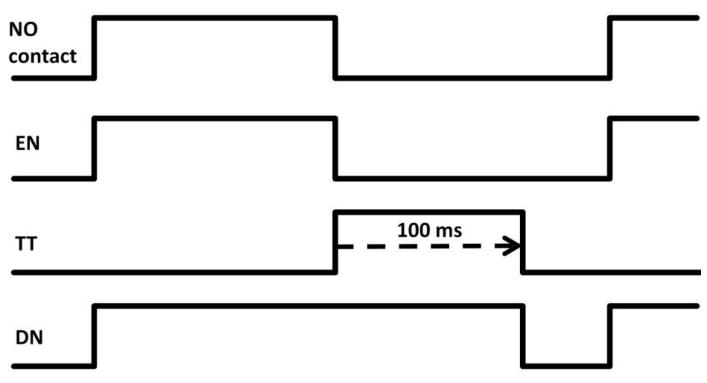

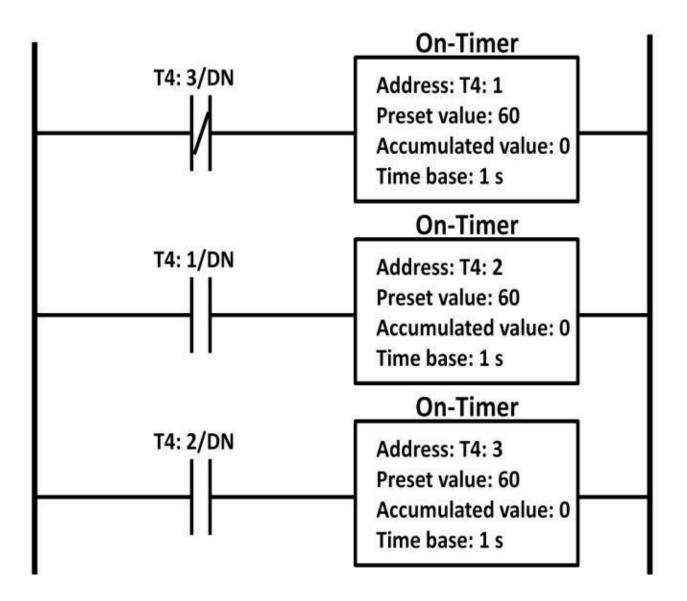

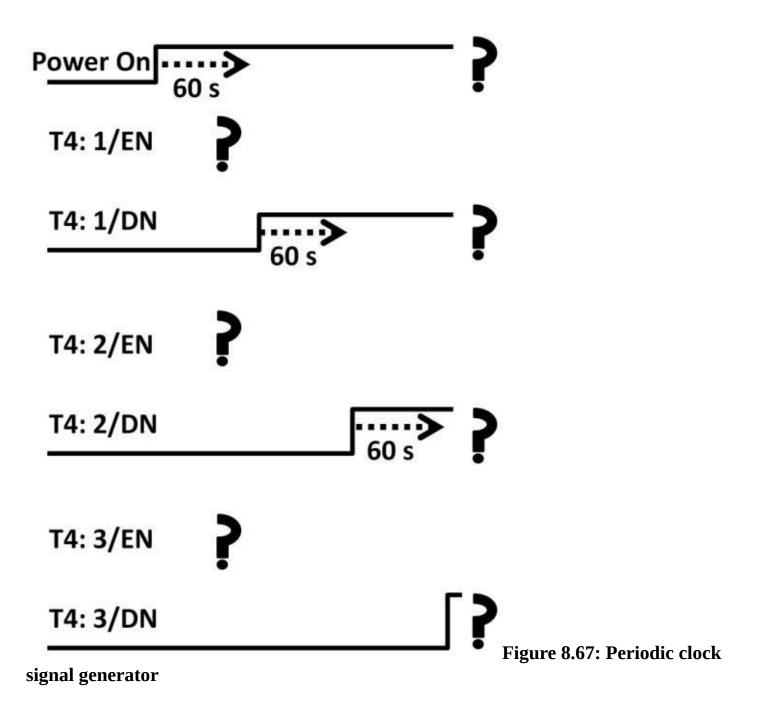

|                                           | 286 Timers          |

| 292 On-Timer                              |                     |

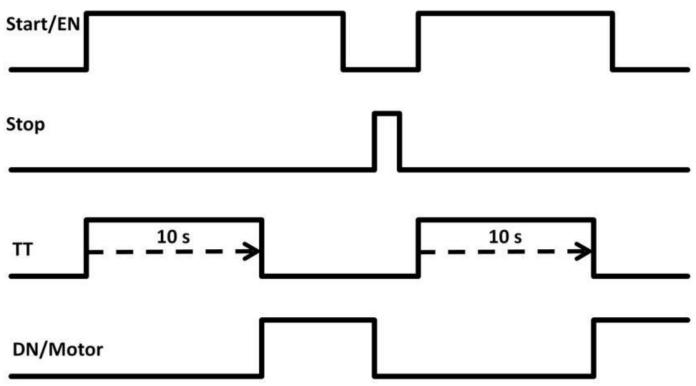

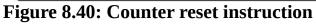

| 293 On-Timer Application                  |                     |

|                                           |                     |

| Timer                                     |                     |

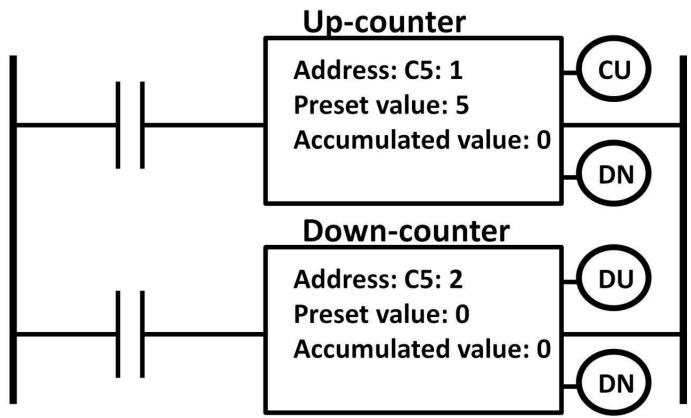

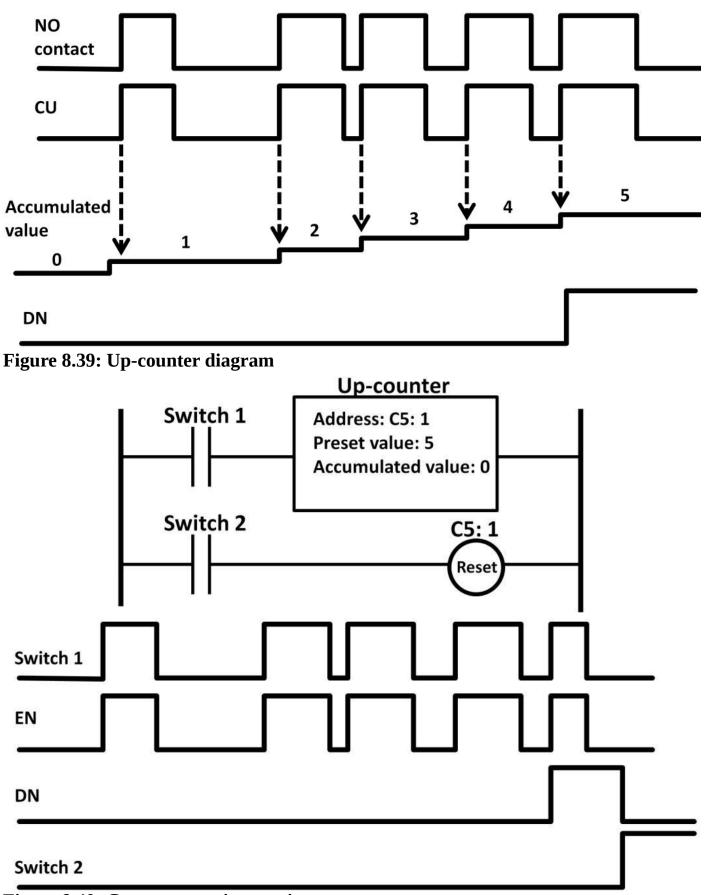

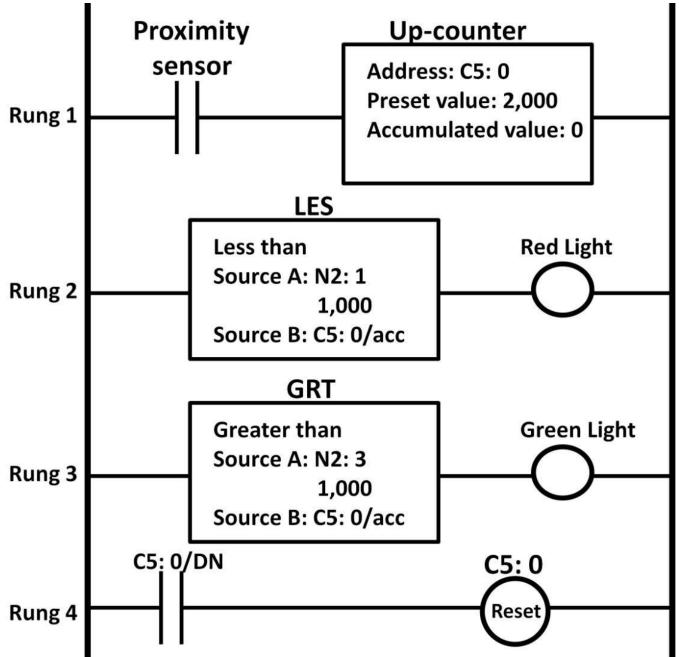

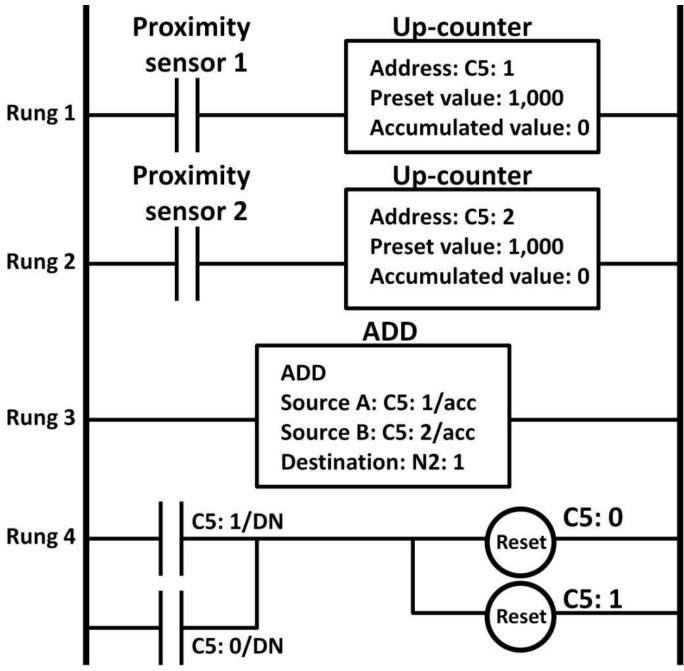

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                 | 296 Counter            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------------------|

| Program Control Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 297 Counter Application         |                        |

| Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Program Control Instructions    |                        |

| Jump to Subroutine Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Instructions                    | 300                    |

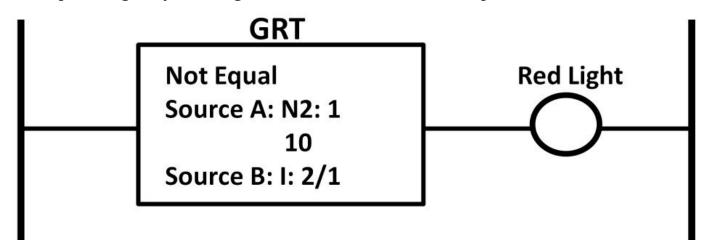

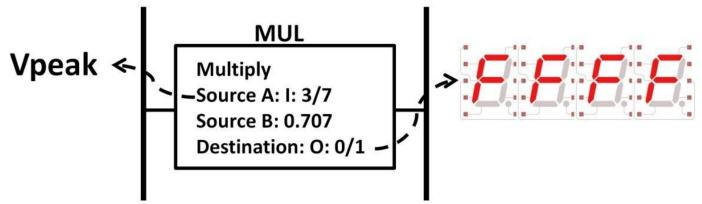

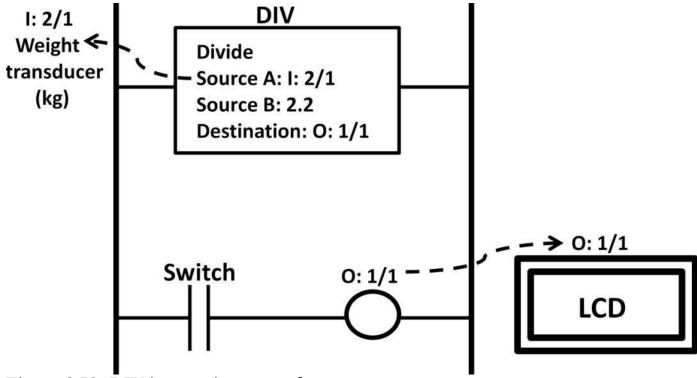

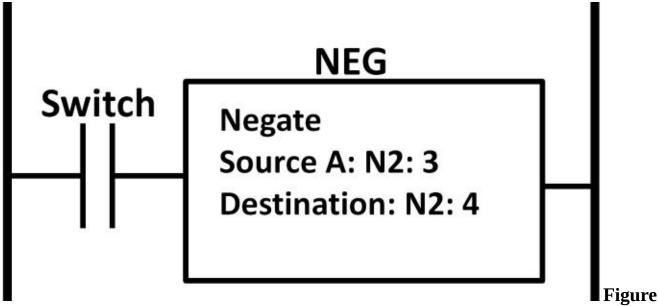

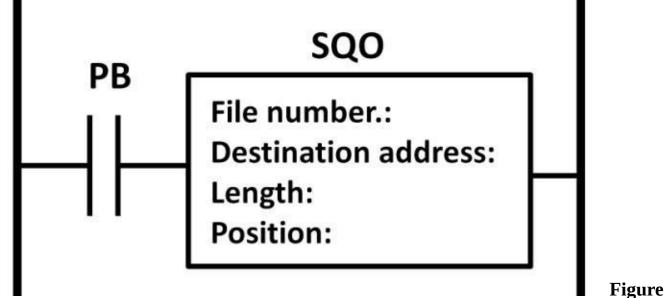

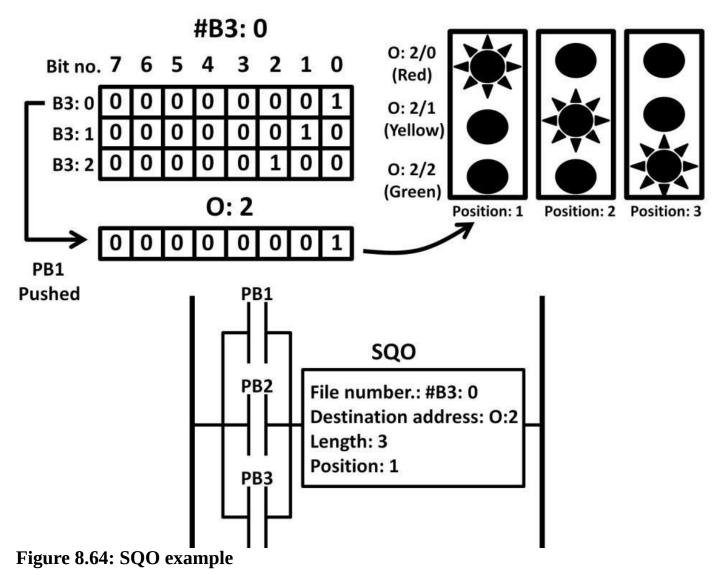

| Temporary End       - 304         Data Manipulation Instructions       - 304 PLC Data         Structure       - 305         305 MOV Instruction       - 306         MOV Instruction Application       - 307 Data Compare         Instructions       - 307 Data Compare         Instructions       - 307 Data Compare         Instructions       - 311         Sequencer Instructions       - 311         Sequencer Instructions       - 315 Trends         317 Summary       -         317 Quiz       -         - 318       -         Chapter 9: Mental Math       319 Decimal Numbers | Jump to Subroutine Instructions | 301 Nested Subroutines |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Table of Contents XVII          |                        |

| Data Manipulation Instructions       - 304 PLC Data         Structure       - 304 PLC Data         305 MOV Instruction       - 306         MOV Instruction Application       - 307 Data Compare         Instructions       - 307 Data Compare         Instructions       - 307 Data Compare         Instructions       - 308         Math Instructions       - 311         Sequencer Instructions       - 315 Trends         317 Summary       -         317 Quiz       -         - 318       -         Chapter 9: Mental Math       319 Decimal Numbers                               | Temporary End                   | - 304                  |

| Structure -   305 MOV Instruction -   MOV Instruction Application -   Instructions -   Math Instructions -   Sequencer Instructions -   - 311   Sequencer Instructions -   - 315 Trends   317 Summary -   317 Quiz -   - 318   Chapter 9: Mental Math                                                                                                                                                                                                                                                                                                                                  | 1                               |                        |

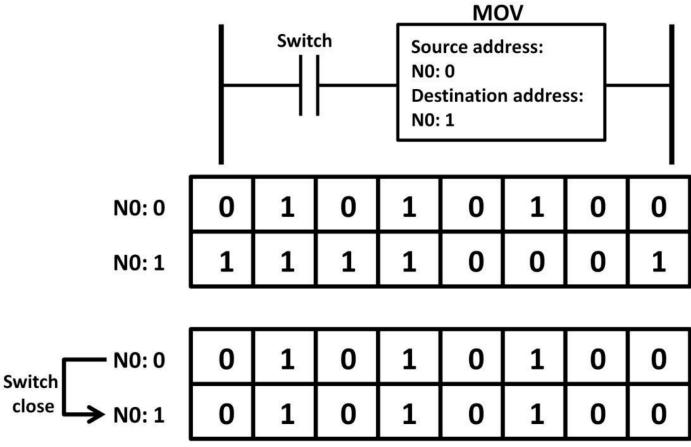

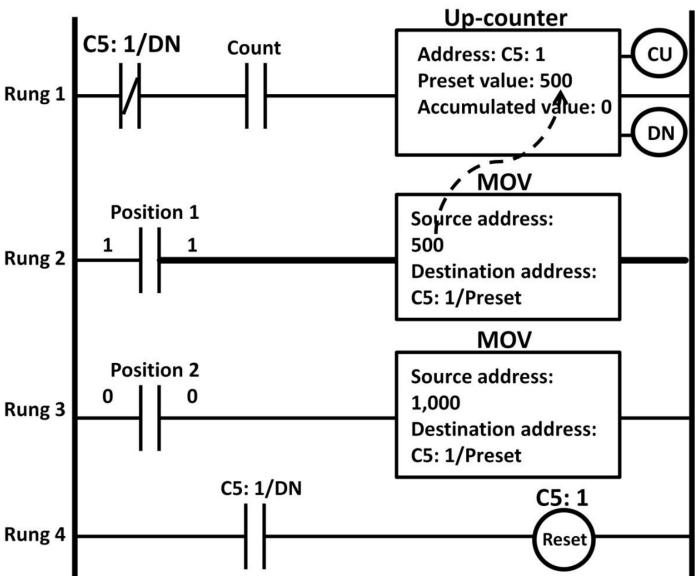

| 305 MOV Instruction       - 306         MOV Instruction Application       - 307 Data Compare         Instructions       - 308         Math Instructions       - 311         Sequencer Instructions       - 311         Sequencer Instructions       - 315 Trends         317 Summary       - 315 Trends         317 Quiz       - 318         Chapter 9: Mental Math       319         Multiples and Submultiples of Units       319 Decimal Numbers                                                                                                                                    |                                 |                        |

| MOV Instruction Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 305 MOV Instruction             |                        |

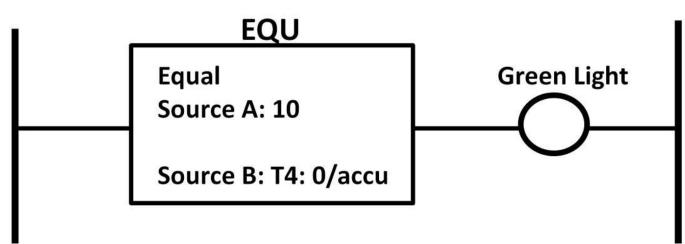

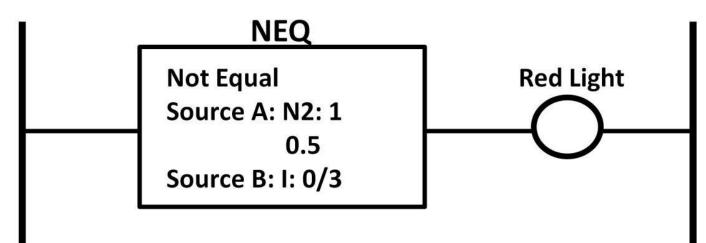

| Instructions 308<br>Math Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | MOV Instruction Application     |                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                 |                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Math Instructions               | - 311                  |

| 317 Summary       -         317 Quiz       -         - 318       -         Chapter 9: Mental Math                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -                               |                        |

| 317 Quiz<br>- 318<br>Chapter 9: Mental Math 319<br>Multiples and Submultiples of Units 319 Decimal Numbers<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                 |                        |

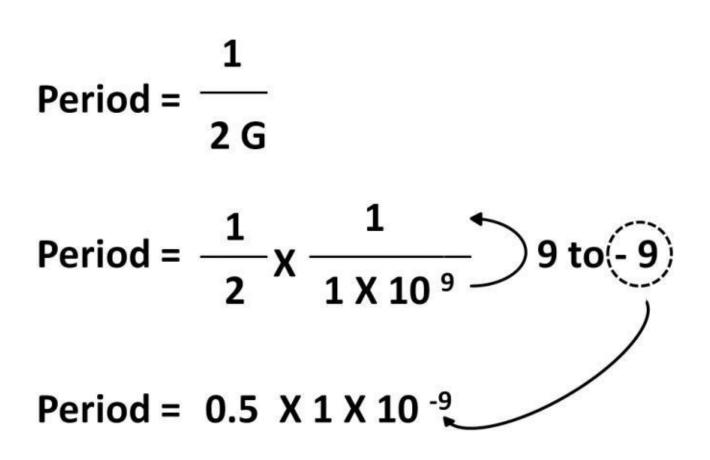

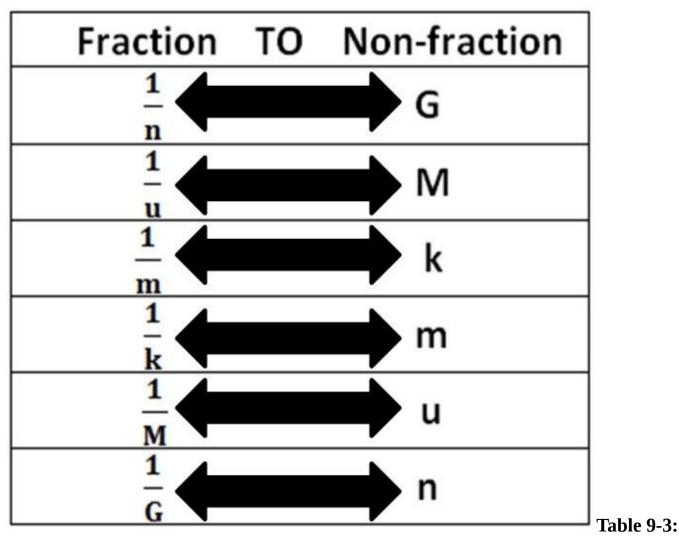

| Chapter 9: Mental Math 319 Multiples and Submultiples of Units 319 Decimal Numbers 320 Whole Numbers 320 Multiples Number Conversion 320 Submultiples Number Conversion 321                                                                                                                                                                                                                                                                                                                                                                                                            |                                 |                        |

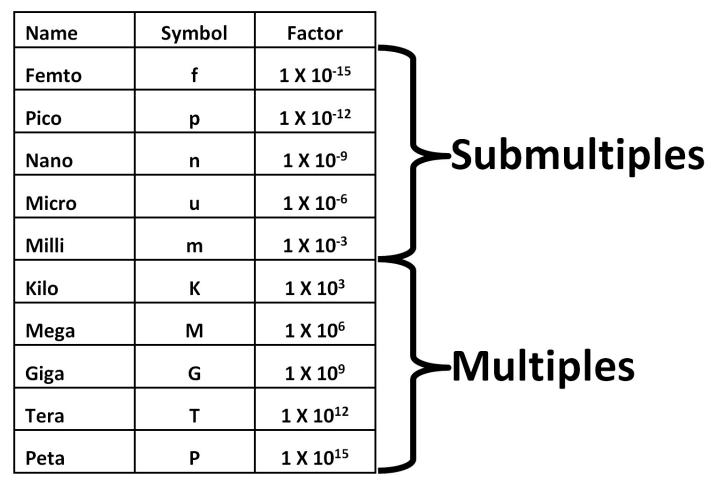

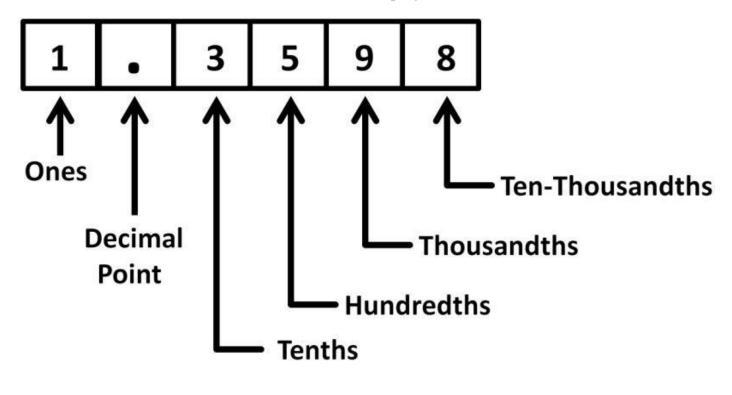

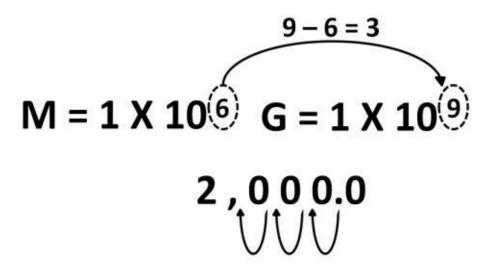

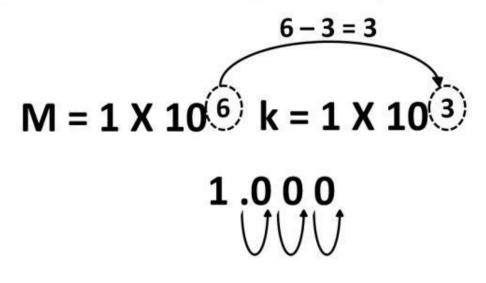

| Multiples and Submultiples of Units 319 Decimal Numbers 320 Whole Numbers 320 Multiples Number Conversion 320 Submultiples Number Conversion 321                                                                                                                                                                                                                                                                                                                                                                                                                                       | - 318                           |                        |

| 319 Decimal Numbers<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Chapter 9: Mental Math          | 319                    |

| Whole Numbers<br>320<br>Multiples Number Conversion<br>320 Submultiples<br>Number Conversion 321                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                 |                        |

| Multiples Number Conversion<br>320 Submultiples<br>Number Conversion 321                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Whole Numbers                   |                        |

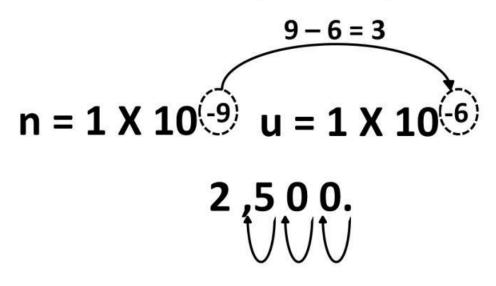

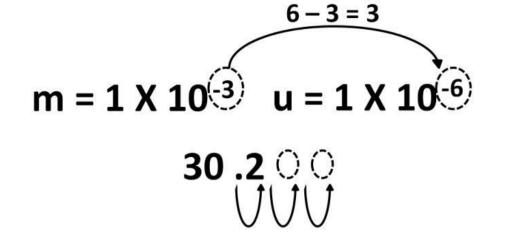

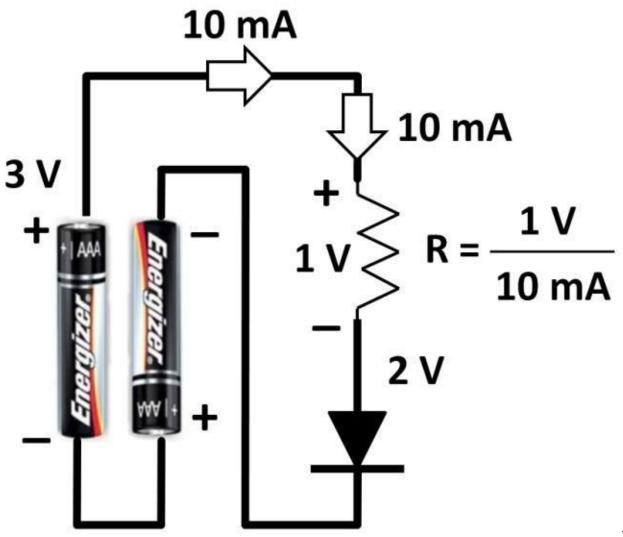

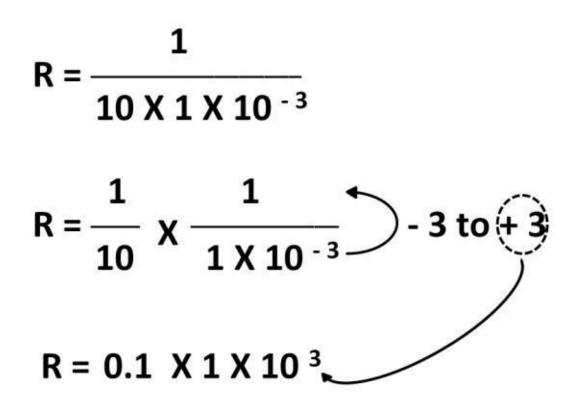

| Number Conversion 321                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Multiples Number Conversion     |                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                 |                        |

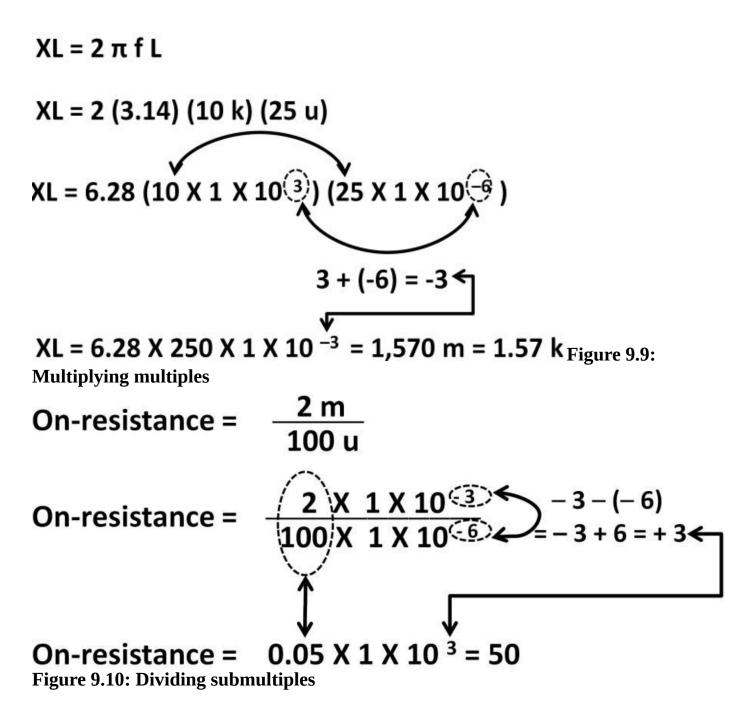

|                            | - 323 Multiplication and Division with |

|----------------------------|----------------------------------------|

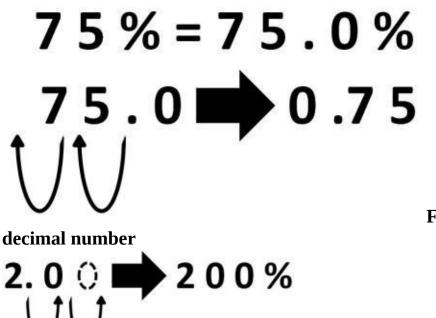

| Multiples and Submultiples | - 325 Percentage to                    |

| Decimals                   | - 326                                  |

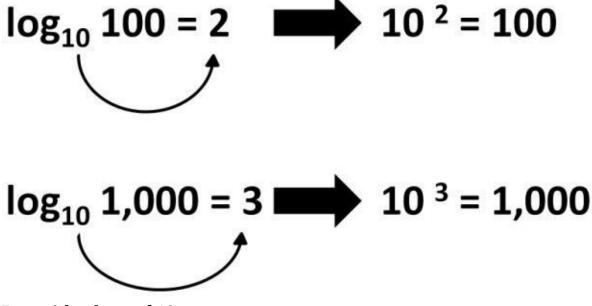

| Log to Real Number         |                                        |

|                            | - 326                                  |

| Summary                    |                                        |

| 328 Quiz                   |                                        |

| - 328                      |                                        |

| Abbreviations and Acronyms | - 329 Index                            |

|                            | 335                                    |

#### **Chapter 1: Direct Current (DC)**

Students majoring in electronics always start with a Direct Current (DC) class. DC is a basic electronic theory that you must learn and understand well. This is the first step to a successful career in electronics. Let's first define some DC parameters.

#### Current

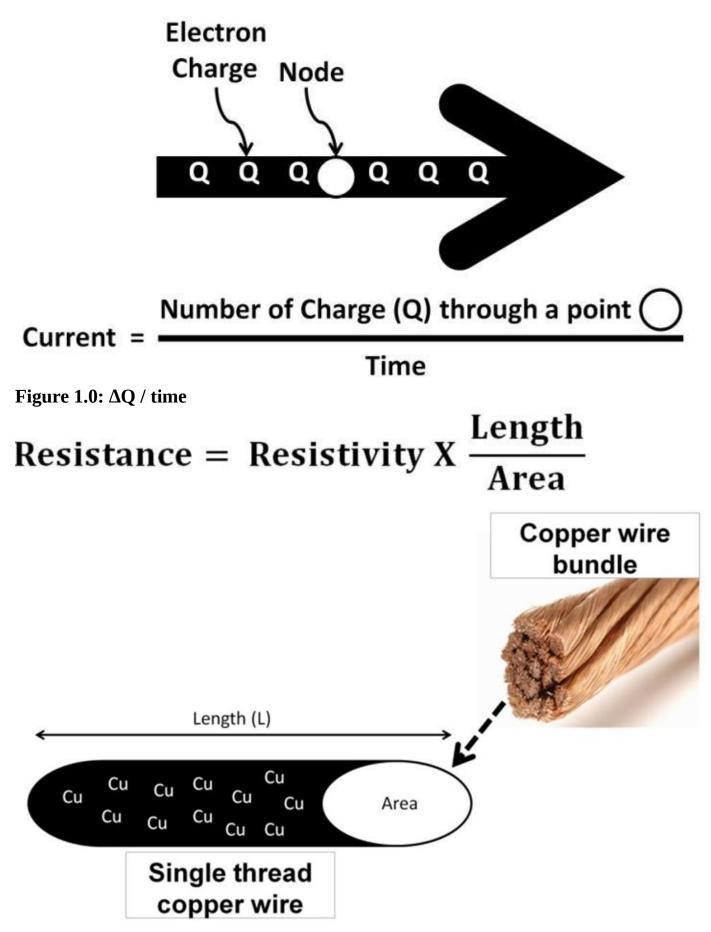

Electrical current is quantified as change ( $\Delta$  or delta) of electron charge (Q) with time. Think of it as flow rate in plumbing. measure of charges ( $\Delta$ Q) flowing through a point (node) with time (see figure 1.0). Current's unit is amperes (A) with "I" being its symbol.

Electrical current is a the number of electron

#### Current = $\Delta Q$ / Time Resistor

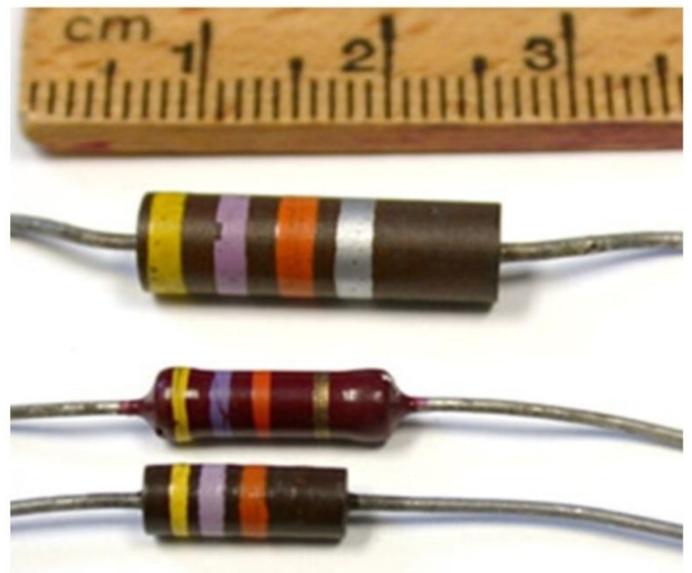

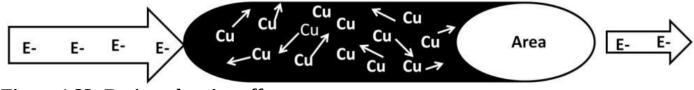

All materials possess resistance, which is a measure of the amount of resistor value. A resistor is a passive electronic device made exclusively for electronic systems. Resistors resist current flow for a given electrical voltage (voltage will be defined shortly). A passive device by definition does not generate energy but rather stores and/or dissipates energy. The most abundant materials used in resistors are copper (Cu) and aluminum (Al). Carbon, thin-film, metal film, and wire-wound are popular resistor types. Resistor size (resistance) is measured in unit Ohms ( $\Omega$ ) with "R" as the symbol. Resistors come in many physical forms. Wire-leads, surface-mount, integrated circuits (ICs) package are popular ones. Figure 1.1 on the next page shows a graphical view of a copper (Cu) wire bundle with a certain length and area exhibiting a finite resistance amount. Internet wires and cables found in residential and commercial dwellings are largely made of copper with a plastic shield on the outside. A resistor can be discrete (one device per item) or manufactured via an IC process housed in an IC package. We will explore more on semiconductor packages later in the chapter. Resistance for a given material strongly depends on the resistor dimension, where resistivity is unique to the materials type:

#### Figure 1.1: Copper wire

Common carbon resistors are measured in the order of several centimeters (see figure 1.1a).

#### Figure 1.1a: Carbon resistors

Due to the small carbon resistor sizes, color bands are used to indicate resistance values instead of printing them on the resistors. There are four bands. The first band on the left represents the first significant resistance digit. The second band is the second significant digit. The third band is the multiplier, and the last is tolerance. Tolerance determines the maximum percentage change in resistance from its nominal value. Table 1-1 shows the details among band color, digit values, multiplier, and tolerances.

|            | First-band | Second-band | Third-band | Fourth-band |

|------------|------------|-------------|------------|-------------|

| Band Color | Digit      | Digit       | Multiplier | Tolerance   |

|            | 0          | 0           | 1          |             |

| Brown      | 1          | 1           | 10         | 1 %         |

| Red        | 2          | 2           | 100        | 2 %         |

| Orange     | 3          | 3           | 1000       | 3 %         |

| Yellow     | 4          | 4           | 10000      | 4 %         |

| Green      | 5          | 5           | 100000     |             |

| Blue       | 6          | 6           | 1000000    |             |

| Violet     | 7          | 7           | 1000000    |             |

| Gray       | 8          | 8           | 10000000   |             |

| White      | 9          | 9           | 100000000  |             |

| Gold       |            |             |            | 5 %         |

| Silver     |            |             |            | 10 %        |

| None       |            |             |            | 20 %        |

#### Table 1-1: Resistor band color, digit values, multiplier, and tolerances

Let's apply this to an example. What is the resistance of the carbon resistor that has Brown, Orange, Red, and Gold bands? First, brown yields "1"; orange means digit "3"; red multiplier means "100"; gold represents 5% tolerance. The resistance is therefore calculated as:

#### 13 X 100 = 1,300 $\Omega$ or 1.3 k $\Omega$ with 5% tolerance.

Figure 1.1b:

Surface-mount resistor

Surface-mount resistors, on the other hand, are popular due to their miniature sizes. They are ideal for portable applications when small size is necessary. Figure 1.1b shows several surface-mount resistors. A surface-mount resistor can be measured as small as 0.2 mm (millimeter) X 0.4 mm (millimeter). Because surface-mount resistors are small, in order to determine their values, numbering codes are used instead of color bands. The numbers printed on the resistor are usually 3-digit numbers.

The first two numbers represent the first two digits of the resistor values while the third digit represents the number of zeros. For example, a resistor marked with 203 means **20 X 1,000 \Omega or 20 k\Omega**. A 105 resistor gives **10 X 10<sup>5</sup> \Omega or 1 M\Omega**. Resistors manufactured by microelectronics technology use different methods to determine resistances. Depending upon the chip manufacturing process, there can be multiple resistor types, ranging from metal and thin-film to poly resistors. The resistances are determined by the vertical and horizontal dimensions in conjunction with the sheet rho (pronounced as row) resistance. Sheet rho's units are in  $\Omega$  **per square (\Omega / square)**. For example, a Bipolar-CMOS (BiCMOS) process thin-film resistor's sheet rho is specified as **1,000 \Omega / square. Length** / **Width** defines the square numbers. If the resistor's length and width are drawn as 10 micrometers (um) by 10 micrometer (um) respectively, the number of square equates to **10 um / 10 um = 1**. The resistance is then calculated as:

## $\frac{Length}{Width}X \text{ Sheet Rho} = \frac{10 \text{ um}}{10 \text{ um}}X 1,000 = 1 \frac{10 \text{ square}}{10 \text{ square}}X 1,000 \frac{\Omega}{10 \text{ square}} = 1,000 \Omega$

Regarding the chip manufacturing process, in addition to sheet rho resistances, each process offers a slew of devices with a unique set of parameters. Below are some common ones you will likely encounter. Transistors' minimum geometries: CMOS uses gate length where bipolar transistors use emitter width. Transistors' maximum operating frequencies: capacitors' capacitance per unit area; temperature coefficient (it determines how much variations device parameter changes with temperature); maximum voltage supply and break down voltages; transistors' drawn versus manufactured dimensions, metal level numbers available, and many more. Further explanations of these parameters will be discussed later in this book. Full understanding of these parameters is necessary before deciding on a process to use for a particular chip design. Further details on microelectronic design will also be discussed in later chapters.

#### Voltage

Voltage is the potential difference (subtraction) between two points (nodes). The object of these points can be any material. The most common materials are electronic devices such as resistors, diodes, and transistors, which are the main focus of this book. Each electrical parameter has its own symbol and unit. They are summarized in table 2-1.

| Name       | Symbol | Unit       |  |

|------------|--------|------------|--|

| Current    | I      | Ampere (A) |  |

| Voltage    | V      | Volt (V)   |  |

| Resistance | R      | Ohms (Ω)   |  |

#### V, I, R symbols; units

Table 2-1:

#### Definition

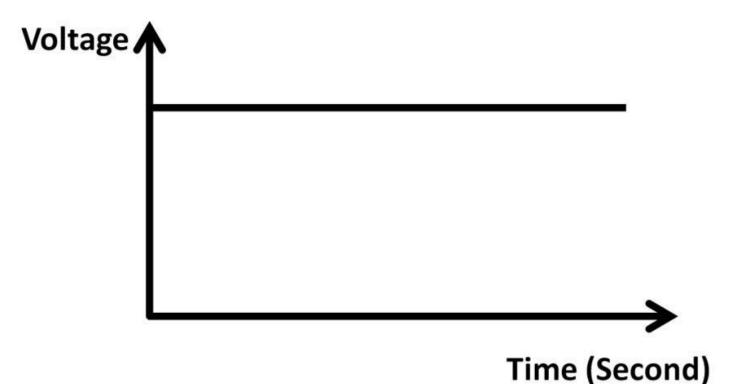

Direct current (DC) states that electrical current flows through a resistor without changes in amplitudes or frequencies. A waveform can be used to make clear such phenomenon. A waveform is a time (transient) domain graph that shows quantities such as voltage, current, or power on the vertical (Y-axis); time on the horizontal (X-axis) (see figure 1.2). In this waveform, the DC voltage level stays the same over time while the frequency of DC is zero. We will further define amplitude and frequency in chapter 3, AC.

Figure 1.2: Voltage vs. time in DC

#### Ohm's Law

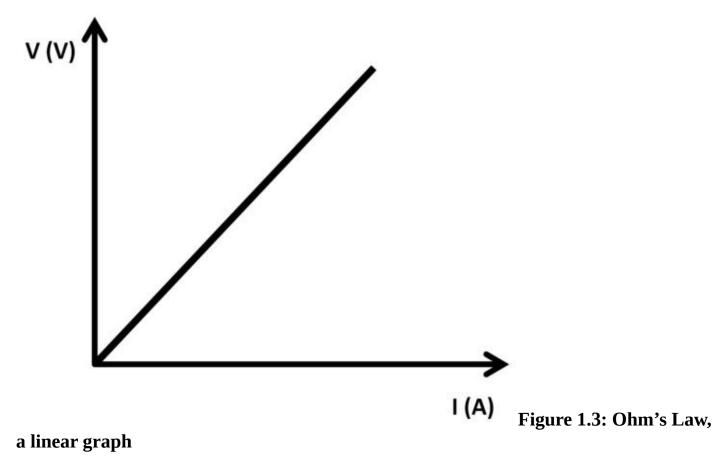

Ohm's law states that when there is a voltage developed (drop) across a resistor, i.e., voltage difference between two resistor ends (nodes), electrical current is bound to flow. The mathematical relationship between voltage (V), current (A or Amp), and resistance

**(**Ω):

#### Voltage = Current X Resistance

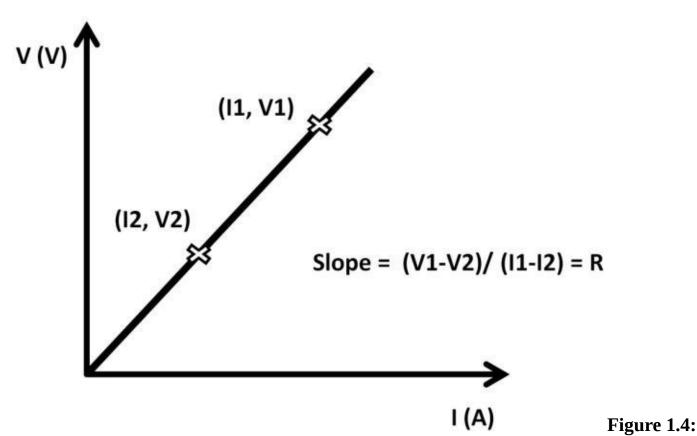

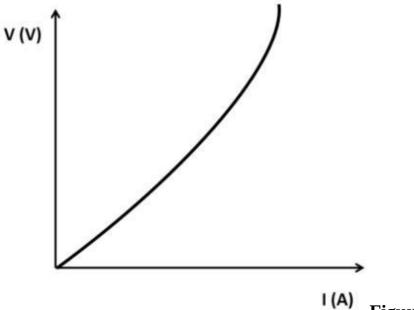

For a given resistor size, increasing voltage causes current to increase linearly. Thereby, Ohm's law is simply a linear function (see figure 1.3). We can apply the above linear relationship among voltage, current, resistor, and slope concept to calculate resistance. A V-I graph is shown in figure 1.4. Any two points can be used to calculate slope (resistance). Because this is a linear function (straight line), slope (resistance) is fixed.

Resistors are usually in large sizes—thousands of  $\Omega$ s, sometimes even more. This is because, for a given voltage, large resistance results in lower current (linear relationship). This is essential due to safety and power-saving reasons. Using Ohm's law, 1 V divided by 1 A equals 1  $\Omega$  resistance (1 V / 1 A = 1  $\Omega$ ). One ampere is a lot of current, in fact, current above 100 mA (milliamp) going through the human body is deemed lethal. To lower the current for a given voltage at a

#### **Slope equals resistance**

safe level, resistance needs to increase. For example, to lower the current to 1 mA, 1 V source yields:

#### R = (1 V / 1 mA) = 1,000 Ω or 1 kΩ Note: k = 1 X 10<sup>3</sup> = 1,000

Many portable electronic designs draw less than 1 mA of current to conserve battery life resulting in large values of R. This explains why thousands or even hundreds of thousands of  $\Omega$  are frequently seen.

#### Power

Power (P) definition:

#### $\mathbf{P} = \mathbf{I}^2 \mathbf{X} \mathbf{R} \text{ or } \mathbf{V}^2 / \mathbf{R}$

The unit of power is Watts (W) and its symbol is "P". A modern smartphone power amplifier consumes about 300 mW (milliwatt) in idle mode. With 4 V lithium-ion battery (a popular cell phone battery type), antenna load resistance can be calculated:

#### 300 mW = $4^2$ / R R = 53.33 $\Omega$

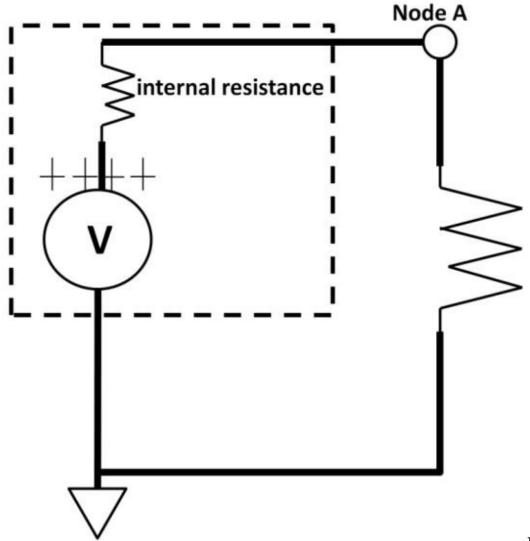

#### **Voltage Source and Schematic**

A voltage source is an electronic device that supplies voltage to an electronic load. The electronic load acts as an output that delivers or receives electrical energy to and from an

input. Load examples are motors, electric fans, lights, etc. An ideal DC voltage source has zero internal resistance, capable of sourcing (sending) and sinking (receiving) infinite current amount to and from the load. A non-ideal voltage source contains finite (non-zero) internal resistance and cannot supply or receive infinite current amount. The most common DC

#### Figure 1.5: Alkaline battery types

voltage source is alkaline household battery commonly used in portable electronics. Figure 1.5 shows several popular alkaline battery types (Energizer brand). Most alkaline batteries are cylindrically shaped except the 9 V type, which is rectangular. They differ in sizes, voltage ratings, and mAh. mAh stands for milliamp-hour, which is equivalent to electron charge.

It describes the electrical current capacity of a battery. Both AA, AAA, and D batteries and are rated at 1.5 V with different mAh ratings. A 9 V battery is rated at 9 V DC (1,800 – 2,600 mAh). If, for example, a portable device draws 100 mA discharge current to operate, the battery will last a minimum of 18 hours (1800 mAh / 100 mA = 18 hours). Other popular batteries are button-sized batteries (button cells) suitable for lightweight applications. They come in a wide range of types, sizes and voltage ranges. Button cells typically are rated at 1.5 V with less mAh (150 – 200 mAh).

#### **Current Source and Schematics**

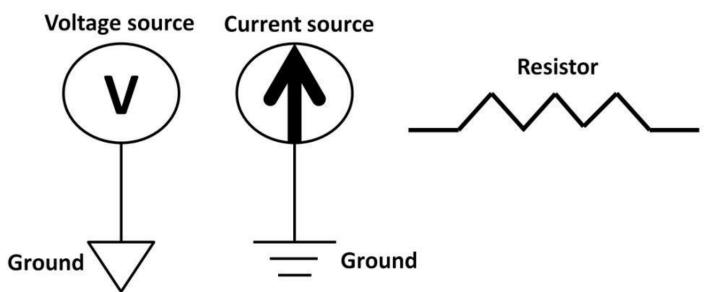

A current source is an electronic device that supplies electrical current to a load. An ideal current source has infinite output resistance capable of supplying an infinite amount of current. Most electronic designs can be graphically expressed in the form of schematics (electronic circuits). Schematics include graphical V, I, and R symbols, plus various electronic components and wires. Figure 1.5a shows schematic symbols of voltage and current sources with ground connected at the other end. Ground is an electrical connection that is referenced to zero voltage potential (0 V). Schematics can be hand drawn on paper,

although the majority of schematics are entered into computer software. This makes it very easy to design and modify electrical schematics. Popular electronic schematic software tools will be discussed in chapter 4, Analog Electronics. Ideally, ground is at absolute 0 V with zero resistance. Keep in mind real-world ground has non-zero resistance. The ground signal amplitude depends on multiple factors (mostly from electrical noise), which will be discussed later on. The current source symbol in figure 1.5a contains an arrow signifying the current flow direction. Both triangular and horizontal line ground symbols are interchangeable although some use the triangular symbol strictly for power ground; the horizontal symbol for signal ground. Triangular ground symbols are used throughout this book.

Figure 1.5a: Voltage, current, and resistor schematic symbols

#### Electrons

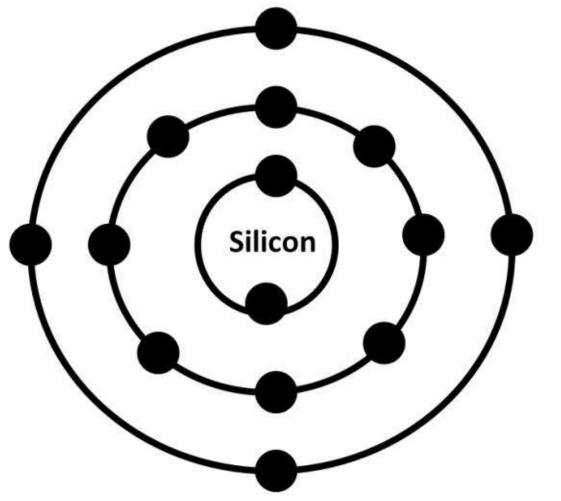

An atom is made up of tiny particles: protons (positive charge), neutrons (neutral), and electrons (negative charge). Protons and neutrons are in the center of an atom while electrons surround the nucleus. Electrons are ions (particles) containing negative charges. Difference in electron and proton numbers gives rise to various atom structures (chemical elements). In this book, we mainly microelectronics, such as silicon and attracted to positive charges (terminals and polarities). The symbol "Q" quantifies electron charges. The unit of Q is coulomb (C). One electron charge holds: focus on chemical elements that are used in

germanium. The negatively-charged electrons are

#### **One Electron Charge = 1.6 X 10<sup>-19</sup> C Current versus Electrons**

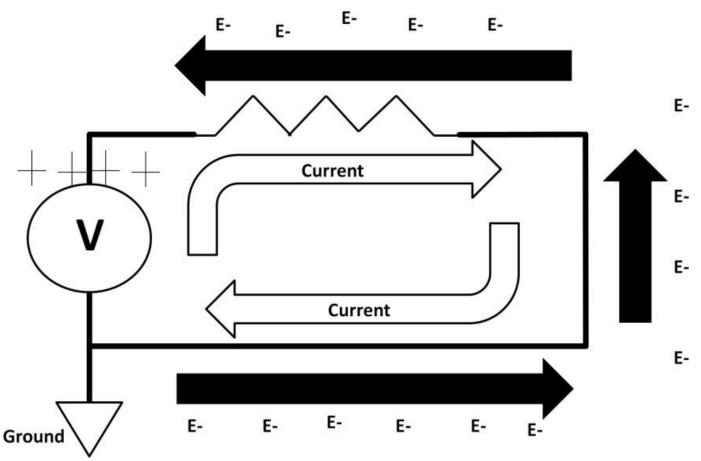

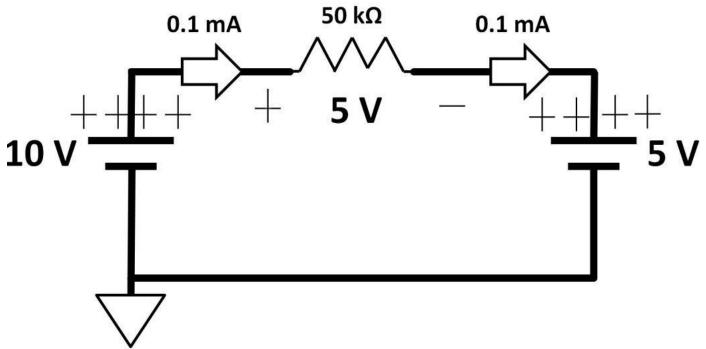

In figure 1.6, a positive voltage source (positive signs) is connected to a resistor with a wire. The other end of resistor connects to ground (negative polarity) creating a loop. Due to a positive charge at the voltage source, according to Ohm's law, a current is bound to flow through the resistor in clockwise direction (inner arrow) while electrons (E-) are flowing towards the positive charges arriving at the voltage source. Keep in mind the electron and current flow in reverse directions.

Figure 1.6: Electron vs. current flow

#### Kirchhoff's Voltage Law (KVL)

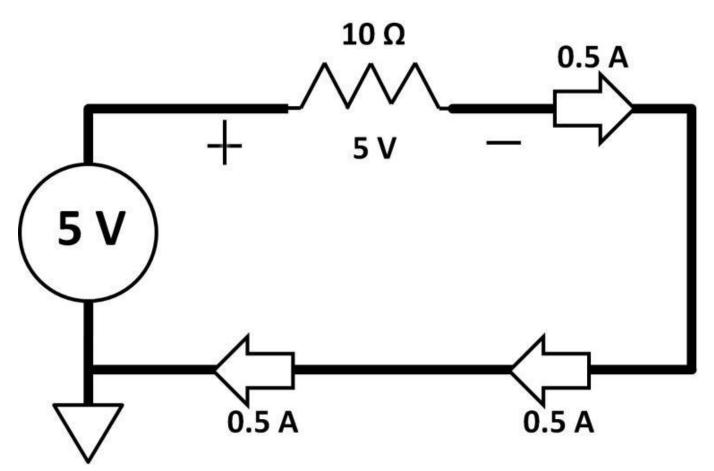

KVL states that the **sum of all voltages around a loop = 0**. A simple circuit in figure 1.7 applies and explains this theory. There is only one theory to apply: Ohm's law and we will use it twice. This circuit contains a 5 V voltage source connects to a 10  $\Omega$  resistor. We use Ground to close the loop. By using Ohm's law, current can be evaluated:

#### V = I X R I = V / RI = (5 V) / (10 Ω) = 0.5 A

This circuit is a series circuit. There is only one branch the current could go. We will visit more series circuits in a moment.

#### Figure 1.7: Series circuit

By using Ohm's law the second time, we could find out what the voltage drop is across the 10  $\Omega$  resistor, V\_resistor:

V\_resistor = I X R

#### V\_resistor = (0.5 A) X (10 Ω) = 5 V

Now, we could use all voltages in this circuit to see if KVL holds up.

## Sum of All Voltages Around a Loop = Voltage Source + Voltage Drop Across the Resistor.

#### 5 V + (-5 V) = 0 V

It checks out! Notice that the voltage drop across the resistor contains a negative sign (polarity). The reason is that the voltage on the left-hand side of the resistor was higher (+) than the voltage on the right-hand side of the resistor (-). The positive resistor sign "opposes" the positive polarity of voltage source, hence the negative sign in the KVL calculations (see figure 1.7). The importance of this circuit is twofold. First, it demonstrates how simple it is to apply and explain the circuit using Ohm's law and KVL. Secondly, despite the circuit's simplicity, any electronic circuit regardless of its complexity can always be explained by Ohm's law and KVL. Sometimes, you will hear statements such as; there is a "short" in an electronic circuit that caused damages. Applying Ohm's law easily explains it. In figure 1.7, if the 10  $\Omega$  resistor were "shorted" (zero resistance) and we applied Ohm's law,  $\mathbf{I} = \mathbf{V} / \mathbf{R}$ , where  $\mathbf{V} = 5 \mathbf{V}, \mathbf{R} = 0$ .  $\mathbf{I} = 5 \mathbf{V} / \mathbf{0}$   $\Omega = \text{infinite}$ . Current becomes infinitely large causing damage to the system. Realistically, any electronic system, no matter how shorted it becomes, possesses a finite amount of resistance.

#### Kirchhoff's Current Law (KCL)

KCL states that current going into (passing through) a point (node) is equal to current coming out of the same node. We could use the same circuit in figure 1.7 to examine this theory. This is a series circuit. The current goes into left-hand side (node) of the resistor, and thus is equal to the right side of the resistor. We will use a parallel circuit in the next segment to further explain KCL.

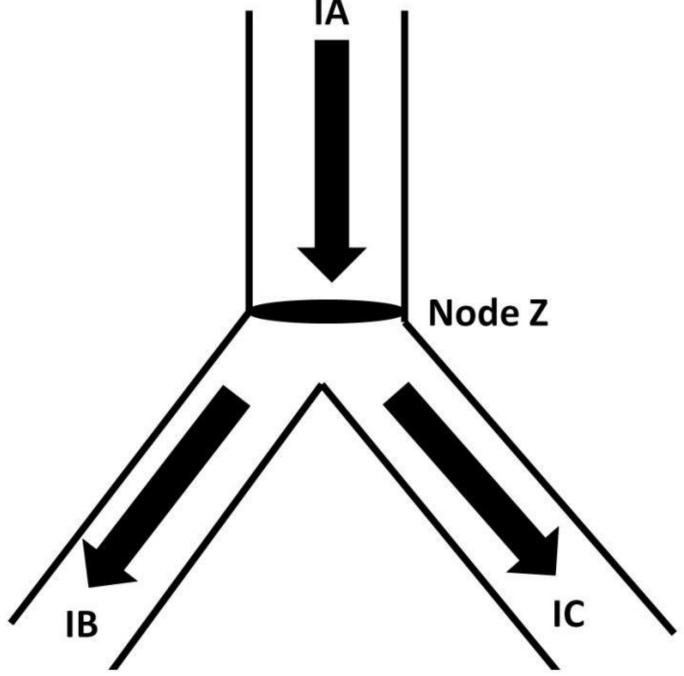

#### **Parallel Circuit**

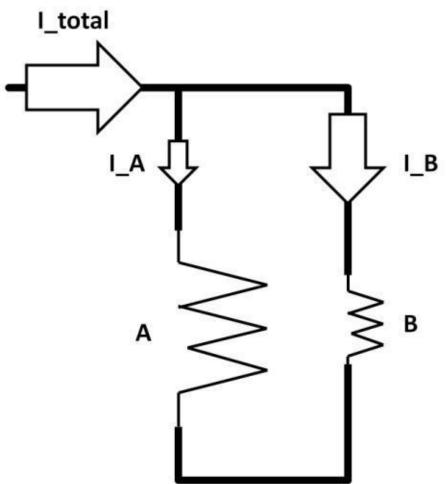

Series circuit states that current only flows in one direction. In parallel circuits however, current flows in more than one direction (see figure 1.8).

#### Figure 1.8: KCL

Current A (IA) goes into node Z and is equal to sum of both currents IB and IC, coming out of the same node (node Z). Mathematically, it's simply:

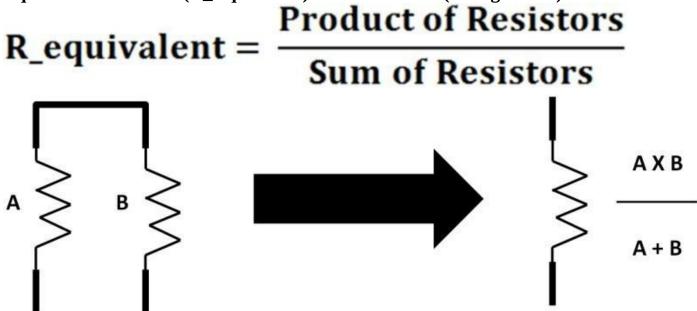

#### IA = IB + IC Parallel Resistor Rule

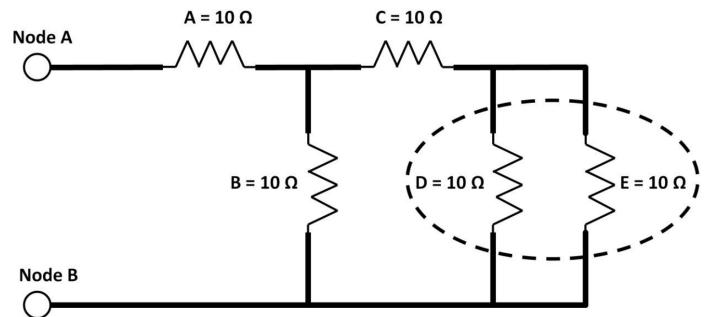

Equivalent resistance (R\_ equivalent) of two resistors (see figure 1.9):

#### Figure 1.9: Parallel resistor rule

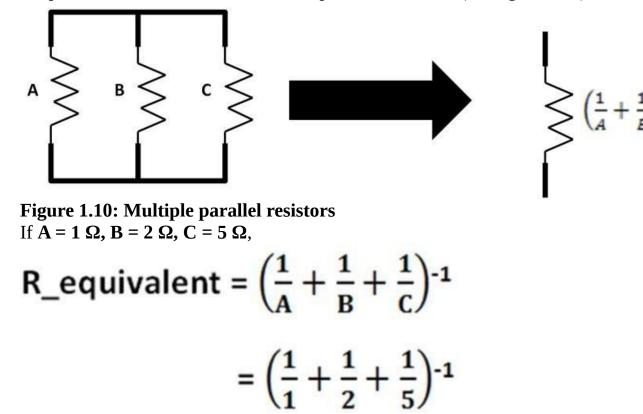

If the parallel (||) resistors number is two or more, the equivalent resistance is equal to the reciprocal of the sum of individual reciprocal resistances (see figure 1.10).

$$=\frac{10}{17} \Omega = 0.58 \Omega$$

You may notice that the equivalent resistance of multiple resistors is always slightly less than the smallest resistor among the resistor groups. From the above example, the equivalent resistance of 1  $\Omega$ , 2  $\Omega$ , and 5  $\Omega$  is 0.58  $\Omega$ . It's less than the smallest resistor value 1  $\Omega$ . This gives you a quick way of knowing if the equivalent resistance you come

up with makes sense or not. Note that if the resistor numbers in parallel are exactly the same sizes, the equivalence resistance is calculated as resistance of one resistor divided by the total resistor number, **e.g.**, **10** || **10** || **10** = **3.33**  $\Omega$  (**10** / **3** = **3.33**  $\Omega$ ). This rule, however, doesn't apply to parallel resistors that have different sizes.

#### Series Resistor Rule Equivalent resistance = Sum of all resistances (see figure 1.11).

#### Figure 1.11: Series resistor rule

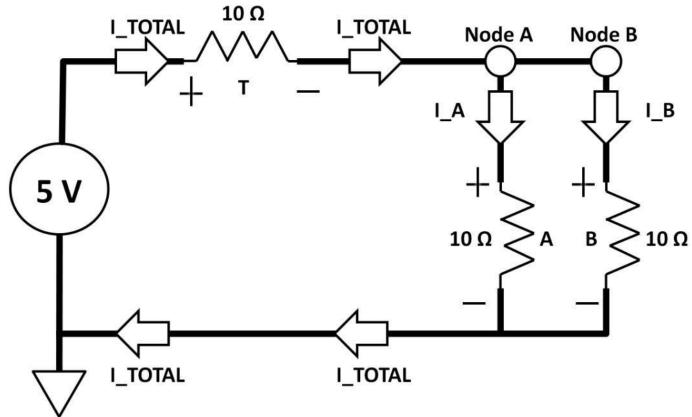

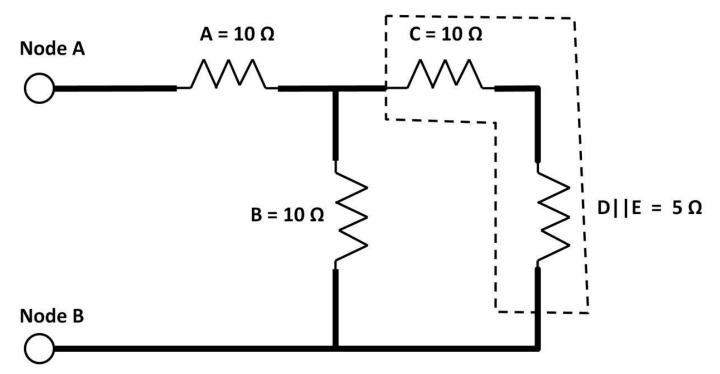

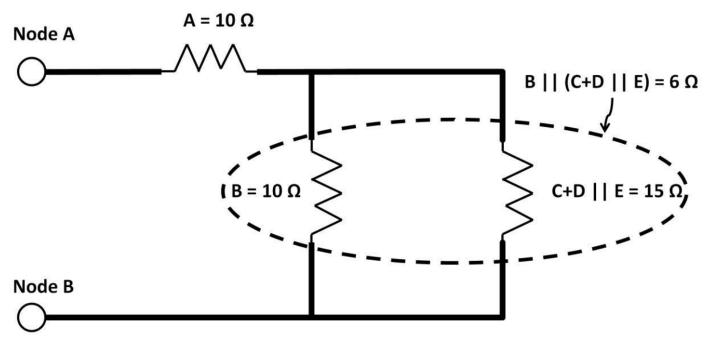

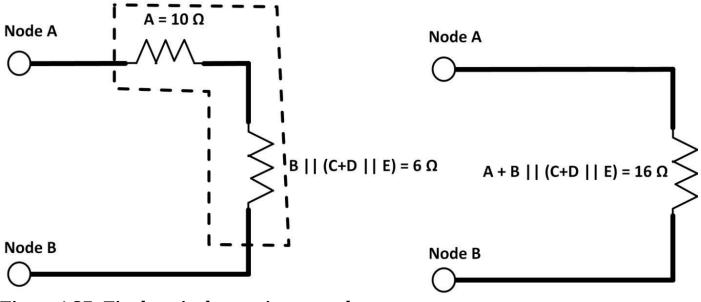

Let's use a simple parallel circuit to explain series and parallel resistor configurations. (See figure 1.12).

#### Figure 1.12: Simple parallel circuit

In this illustration, resistor A, B forms a parallel circuit. Total current (I\_TOTAL) going towards node A, B is divided into two separate branches, according to KCL. To calculate I\_A, I\_B, we first calculate the total resistance of the entire circuit. I\_TOTAL can then be found. The idea is to consolidate all three resistors T (10  $\Omega$ ), A (10  $\Omega$ ), and B (10  $\Omega$ ) into one resistor (Equivalence) and one voltage source. We can then use Ohm's law to calculate I\_TOTAL. According to figure 1.9, resistor A, B can be combined into one resistor, R\_eq:

# A || B = R\_eq = $\frac{10 \Omega X 10 \Omega}{10 \Omega + 10 \Omega} = 5 \Omega$

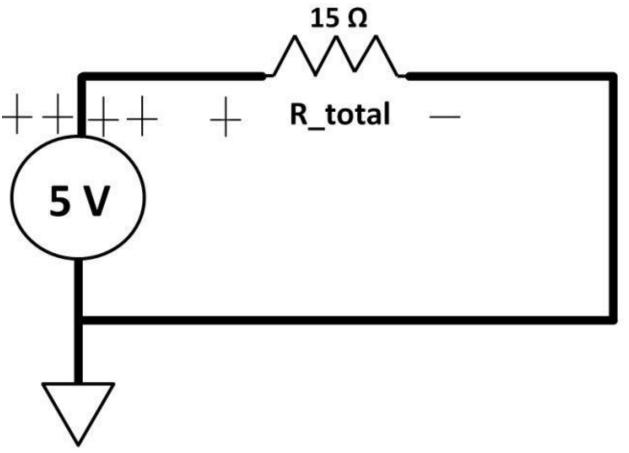

We then further consolidate the two resistors (T and R\_eq) into one resistor. We will call it R\_total. Using series resistor rule, **R\_total** = **T** + **R\_eq** = **10**  $\Omega$  + **5**  $\Omega$  = **15**  $\Omega$ . The consolidated one voltage source, one resistor circuit is shown in figure 1.13.

1.13: Simplified one voltage, one resistor circuit

We now can simply use Ohm's law to calculate **I\_TOTAL**. **I\_TOTAL** = **5 V** / **15**  $\Omega$  = **0.33 A**. At this point, we can apply KVL to make sure the analysis is valid. **5 V** + (– **0.33 A X 15**  $\Omega$ ) = **0 V** To figure out I\_A, I\_B, we first calculate the voltage drop across T using Ohm's law:

Figure

**Voltage Drop across T = (I\_TOTAL) X (T) = 0.33 A X 10 \Omega = 3.33 V Since voltage at left side of T is 5 V and the voltage drop across T is 3.33 V, the voltage at the right-hand side of T (node A and B) is:**

# Voltage Drop across T = (Voltage at Left Side of T) – (Voltage at Right Side of T) 5 V – (Voltage at the Right Side of T) = 3.33 V (Voltage at the Right Side of T) = 5 V – 3.33 V = 1.67 V

It's crucial to recognize that voltage across a device means the difference (subtraction) between two nodes. Now we can use Ohm's law again to calculate I\_A and I\_B. Because voltage at right side of T is common to node A and B (**Voltage at Node A = Voltage at Node B**):

I\_A = (Voltage at Node A) / A = 1.67 V / 10  $\Omega$  = 0.167 A I\_B = (Voltage at Node B) / B

#### $= 1.67 \text{ V} / 10 \Omega = 0.167 \text{ A}$

To prove the analysis is correct, simply use KCL which states that **I\_TOTAL** = **I\_A** + **I\_B** I\_A + I\_B = 0.167 A + 0.167 A = 0.33 A = I\_TOTAL, it checks out!

#### **Current Divider Rule**

The current divider rule states that the current on one branch is the total current multiplied by the ratio of total current. When seeking current A, the numerator contains resistor B and vice versa.

$$I_A = I_total X \left(\frac{B}{A + B}\right)$$

$$I_B = I_total X \left(\frac{A}{A + B}\right)$$

$$I_A and I_B can be easily calculated:$$

$$I_A = (0.33 \text{ A}) X \frac{10 \Omega}{10 \Omega + 10 \Omega} = 0.167 \text{ A}$$

$$I = (0.33 \text{ A}) X \frac{10 \Omega}{10 \Omega} = 0.167 \text{ A}$$

$$I_B = (0.33 \text{ A}) \times \frac{10 \Omega}{10 \Omega + 10 \Omega} = 0.167 \text{ A}$$

Notice if both resistor sizes are the same on each branch, the current amount will be equally divided in a parallel circuit. If the resistors A and B are different sizes, the current is less on the branch that has the larger resistor and vice versa. This concept is illustrated in figure 1.14.

In this example, **I\_total = 2 A, A = 20 \Omega, B= 10 \Omega:**

$$I_A = I_{total X} \left(\frac{B}{A+B}\right) = (2 A) X \left(\frac{10 \Omega}{10 \Omega + 20 \Omega}\right) = 0.66 A$$

I\_B = I\_total X

$$\left(\frac{A}{A+B}\right)$$

= (2 A) X  $\left(\frac{20 \Omega}{10 \Omega + 20 \Omega}\right)$  = 1.33 A

This shows that I\_A is less than I\_B (A's resistance > B's resistance). To further prove this is correct, apply KCL:

I\_total = I\_A + I\_B = 0.66 A + 1.33 A = 2 A It checks out!

Figure 1.14: Resistor size vs.

#### current amount

#### **Voltage Divider**

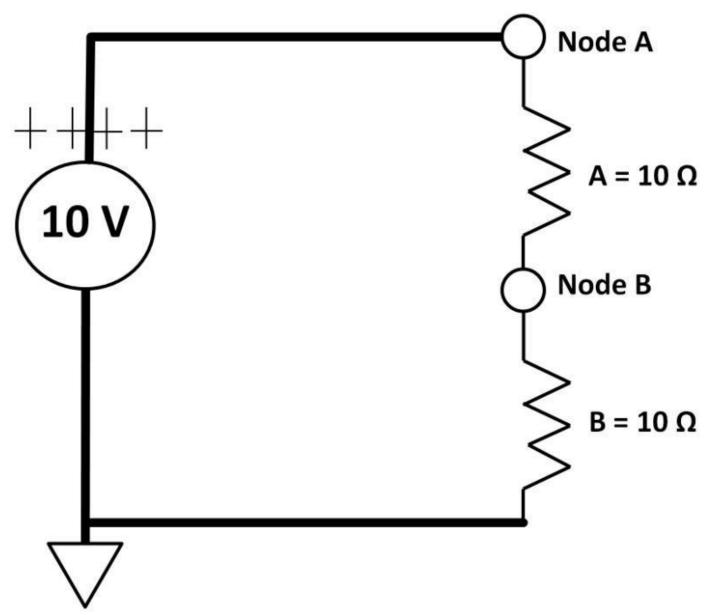

The voltage divider is used all too often. We will start with the definition then use simple circuits to explain it. Just like it sounds, a voltage divider "divides" voltage. The word "divides" does not mean there is a mathematical division; it means the voltage is "reduced" by the resistors. Below is a simple series circuit (see figure 1.15) to explain voltage divider.

Figure 1.15: Simple series resistor circuit

The explanation of this circuit is simple, not surprisingly, using Ohm's law. There is only one current branch in this series circuit. The current can be calculated using Ohm's law and the series resistor rule:

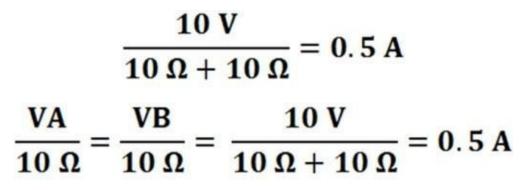

## $\frac{10 \text{ V}}{10 \Omega + 10 \Omega} = 0.5 \text{ A}$

The voltage at Node A is 10 V (connected to a 10 V voltage source). The voltage across (I R drop) resistor A is the potential difference between node A and B, i.e., **Voltage at Node A** – **Voltage at Node B** or it can be calculated using Ohm's law: **0.5 A X 10 \Omega = 5 V**

Once again, it's important to realize that voltage drop across a resistor is the potential difference between two nodes. Knowing that voltage at node A is 10 V, and voltage drop across resistor A is 5 V, voltage at node B can be found using voltage definition:

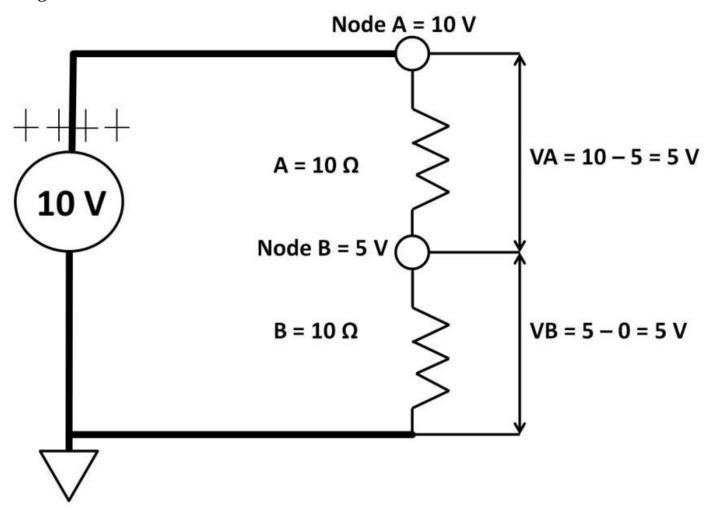

(Voltage Drop across A) = (Voltage at Node A) – (Voltage at Node B) 5 V = 10 V – Voltage at Node B **Voltage at Node B = (10 V – 5 V) = 5 V** For voltage drop across resistor B, it would be **Voltage at Node B – ground (0 V) = 5 – 0 = 5 V**. All voltage drops (I R drops) are shown in figure 1.16.

Figure 1.16: Voltages across A and B

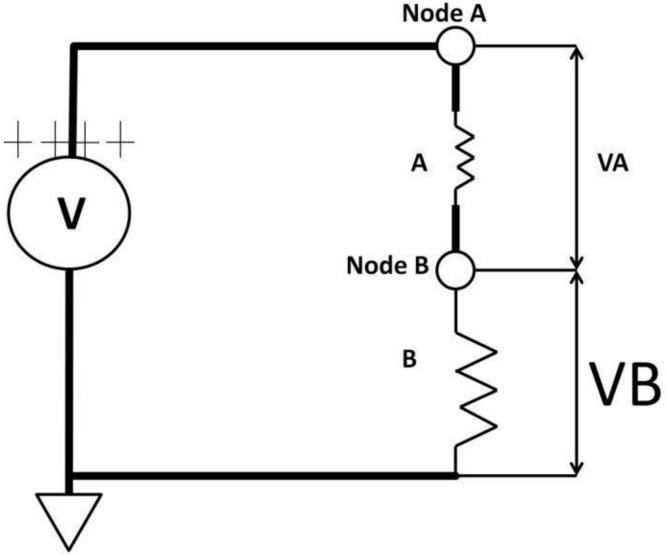

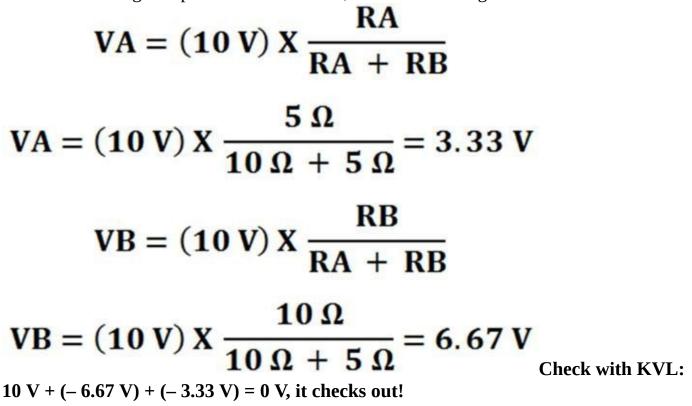

There are voltage drops across each resistor. Voltage was reduced (divided) from the 10 V voltage source. In other words, voltages across each resistor cannot exceed the 10 V voltage source. Some use this formula when it comes to voltage divider:

$$VA = (10 V) X \frac{RA}{RA + RB}$$

$$VB = (10 V) X \frac{RB}{RA + RB}$$

RA is in the numerator when calculating VA. RB is in the numerator when calculating VB. VA and VB are simply the ratio of individual resistance (RA, RB) over the sum of all resistances (RA + RB) in the circuit. If you look closely, the VA, VB formula comes from Ohm's law and series circuit rule. We know that the current going through A and B are the same (series circuit rule). VA / 10  $\Omega$  = VB / 10  $\Omega$ . This current can be calculated from the 10 V source in series with RA + RB (Ohm's law):

Thus,  $VA = VB = (10 \ \Omega) X 10 V / (10 \ \Omega + 10 \ \Omega)$ . This is essentially the voltage divider formula. Although the voltage divider formula does come in handy, one formula will not and cannot fit all because the resistor configurations may be totally different from one circuit to the next. It's much more intuitive to apply basic principles to analyze voltage divider circuits, in fact, any circuits. To see if we come up with the voltages correctly, we use KVL to prove it.

#### 10 V + (- 5 V) + (- 5 V) = 0 V, it checks out!

#### Figure 1.17: Voltage vs. resistor size

In the above example, there are only two resistors. Their sizes are the same. In real life, voltage dividers could have more than two resistors exhibiting a variety of sizes and connection configurations. Despite different voltage divider configurations, the method of determining voltages on any node, voltage drop across any resistor, and current through

each branch is the same: by using Ohm's law, KVL and KCL. One interesting fact is that if the resistance is larger than the other(s), such resistor would have the most voltage drop across it. This is demonstrated in figure 1.17, where resistor B value is larger than A, thus voltage

drop across B is larger than A. This observation is exactly opposite to the current divider rule where larger R sought smaller I and vice versa. In figure 1.17, let's assume

#### $RA = 5 \Omega$ , $RB = 10 \Omega$

To seek the voltage drops across RA and RB, we use the voltage divider formula:

This example shows that, in a series circuit, if resistance (RA) is higher, there is more voltage drop (VA) across RA than RB. Regardless of resistor values or circuit configurations, KVL and Ohm's law always hold true.

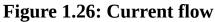

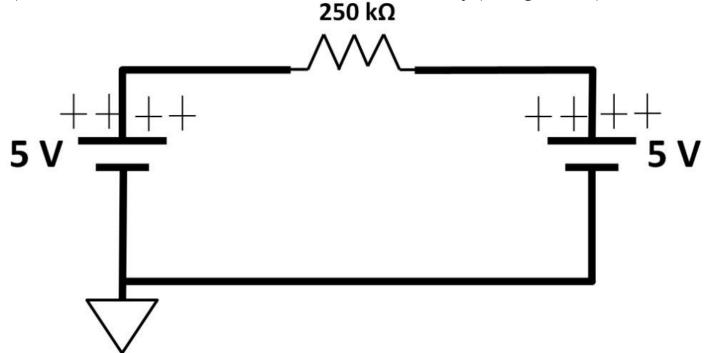

#### **Superposition Theorems**

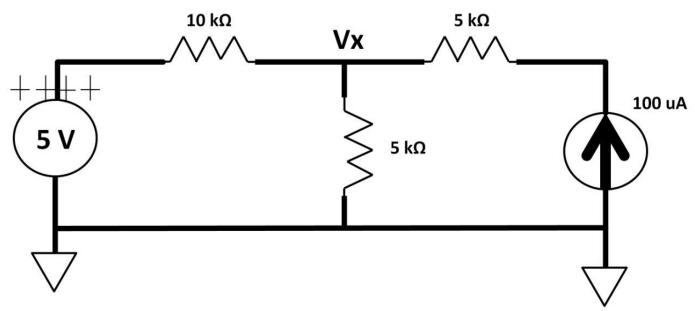

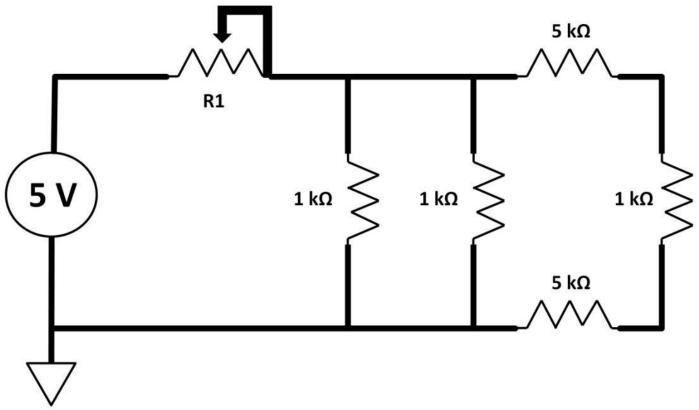

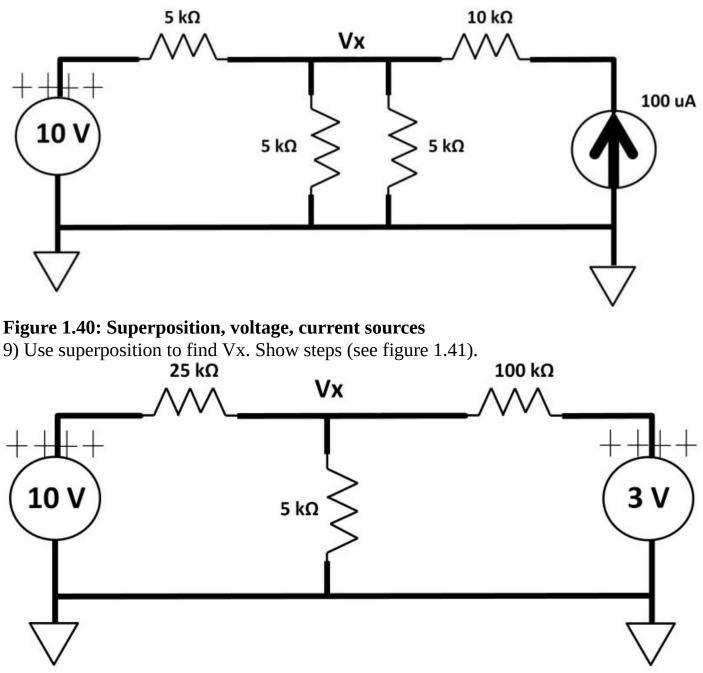

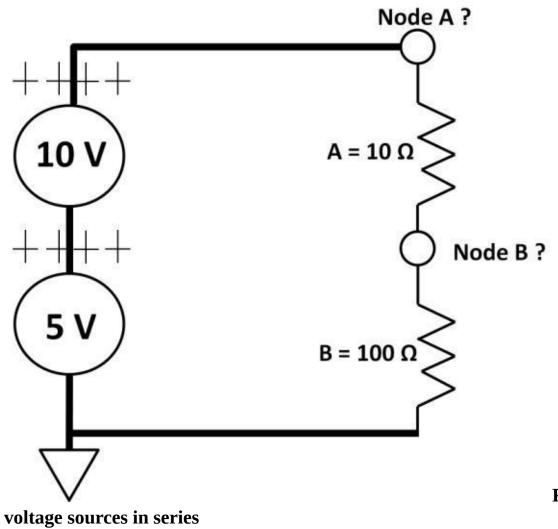

So far, we've focused only on one voltage source circuit. Practical circuits have more than one voltage and/or current source. Numerous theories exist which attempt to explain how the circuits are analyzed in academic textbooks (Thevenin, Norton, and Mesh, just to name a few). I decided to use superposition because of its simplicity. By definition, superposition states that if a circuit contains multiple voltage or current sources, any voltage at a node within the circuit is the algebraic voltage sum found by calculating individual voltage one at a time. Furthermore, any voltage source will be seen as a short to ground when calculating other voltages in the remaining circuit. Any current source will be seen as open circuit. Let's use a simple example to understand superposition (see figure 1.18).

#### Figure 1.18: Superposition circuit example

The goal is to find out what the voltage is at Vx if the current source pushes out 100 uA (100 microamperes, 100 X  $10^{-6}$  A) current and DC voltage source is 5 V. Steps:

1) Isolate the circuit into two separate ones.

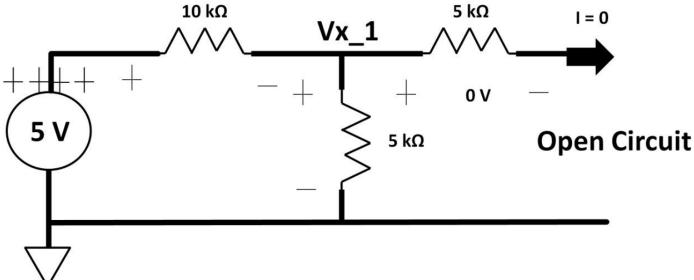

2) Start with the voltage source on the left; force the current source open. Then calculate Vx\_1. The individual circuit is shown in figure 1.19.

#### Figure 1.19: Superposition circuit 1

Noticed the 5 k $\Omega$  resistor (upper right) has zero I R drop (voltage across it) because of the open circuit on the right resulting in no current flowing through it. Ohm's law says, **V** = **I X R** = **0 X** 5 k $\Omega$  = **0 V**. Vx\_1 is then viewed as a voltage between 10 k $\Omega$  and the vertical 5 k $\Omega$  (voltage divider):

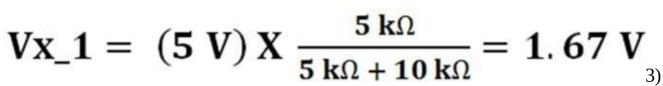

Second circuit: The 5 V DC source is shorted to ground (see figure 1.20).

#### Figure 1.20: Superposition circuit 2

Use parallel resistor rule, 10 k $\Omega$  and the vertical 5 k $\Omega$  can be combined:

# $\frac{\mathbf{5} \,\mathbf{k} \Omega \,\mathbf{X} \,\mathbf{10} \,\mathbf{k} \Omega}{\mathbf{5} \,\mathbf{k} \Omega + \mathbf{10} \,\mathbf{k} \Omega} = \mathbf{3}.\,\mathbf{33} \,\mathbf{k} \Omega$

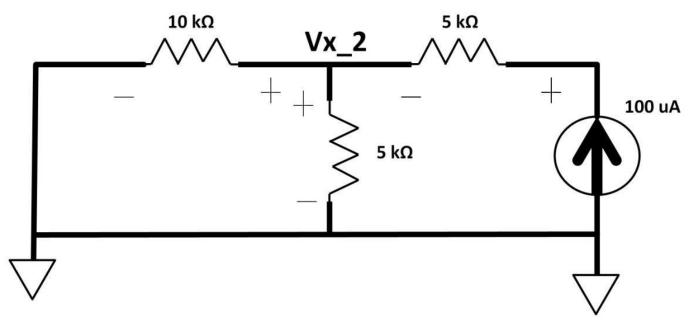

By inspection, figure 1.20 is transformed to figure 1.21. This is a series circuit where the voltage drop across 3.33 k $\Omega$  is between Vx\_2 and ground (0 V). Ohm's law states that **Vx\_2 = 100 uA X 3.33 k\Omega = 0.333 V when a 100 uA fixed current source flows through** 3.33 k $\Omega$ .

#### Figure 1.21: Circuit 2 transformation

The resulting Vx can now be found by summing Vx\_1 and Vx\_2:  $Vx_1 + Vx_2 = 1.67 V + 0.33 V = 2 V$

#### **DC Circuits**

1) What is the difference between an ideal and non-ideal voltage source? This question leads to the understanding of voltage source and voltage divider non-ideal characteristics.

Rules:

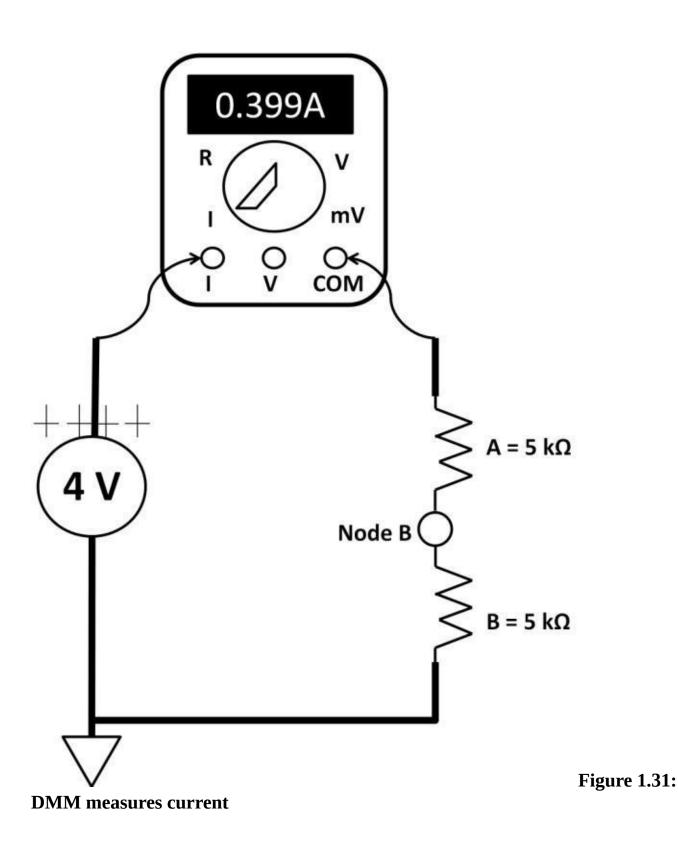

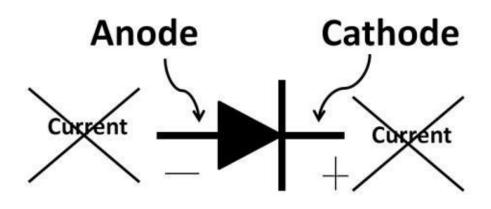

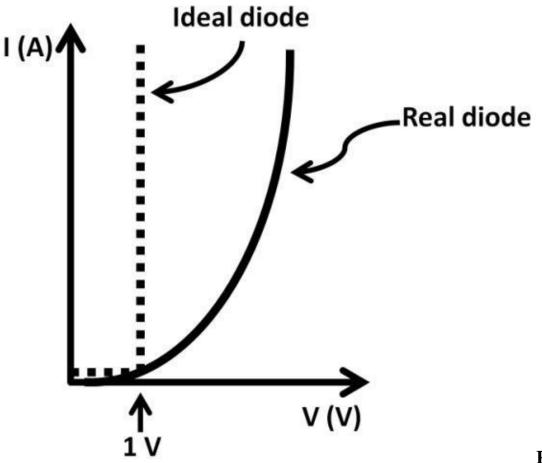

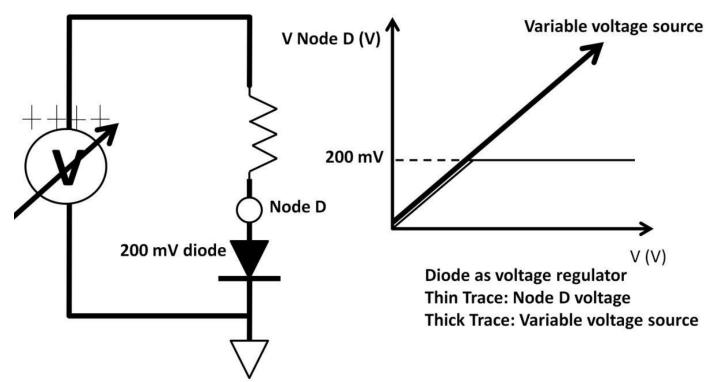

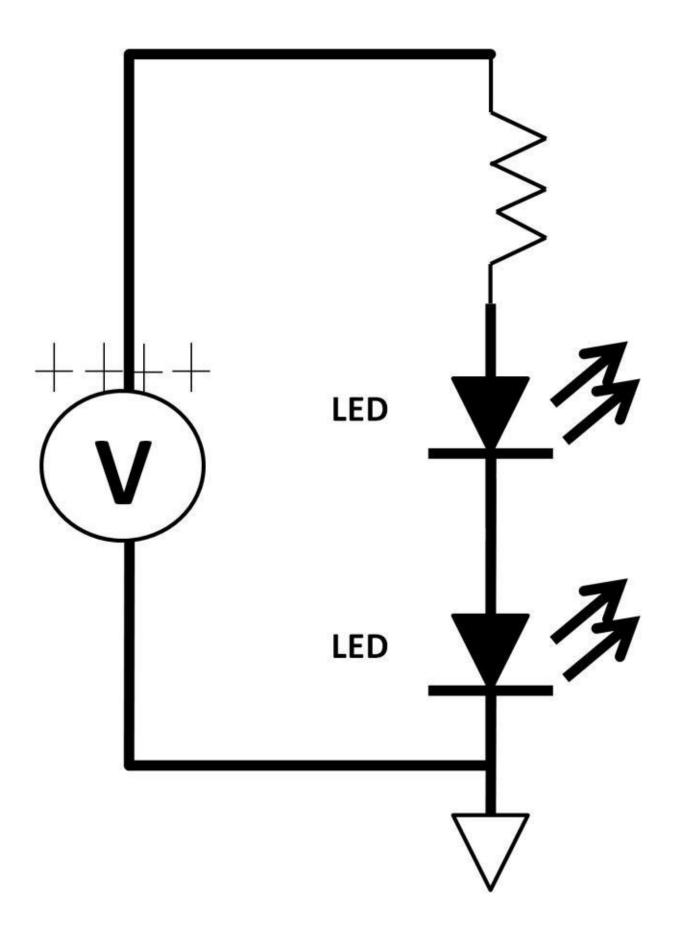

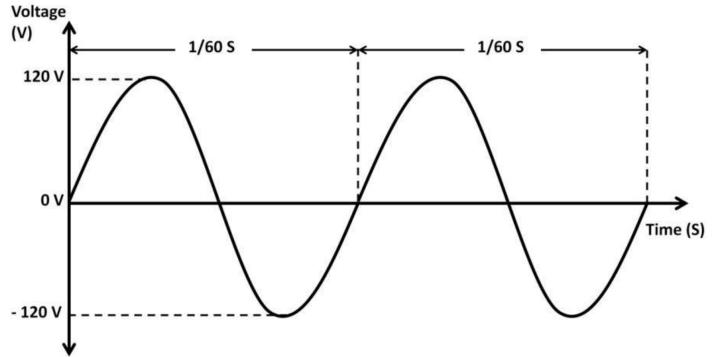

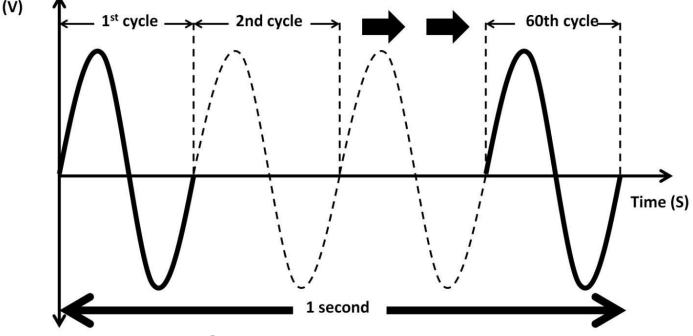

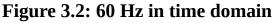

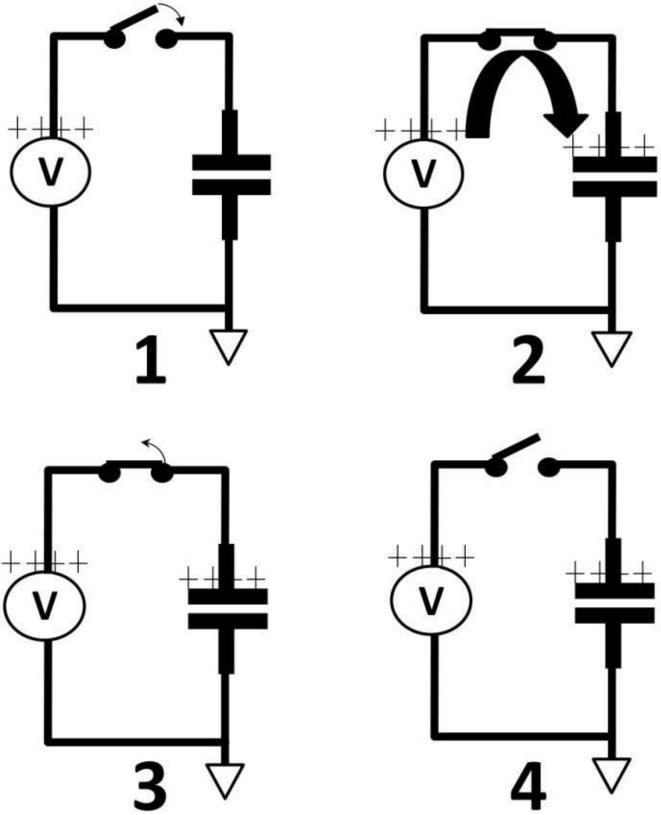

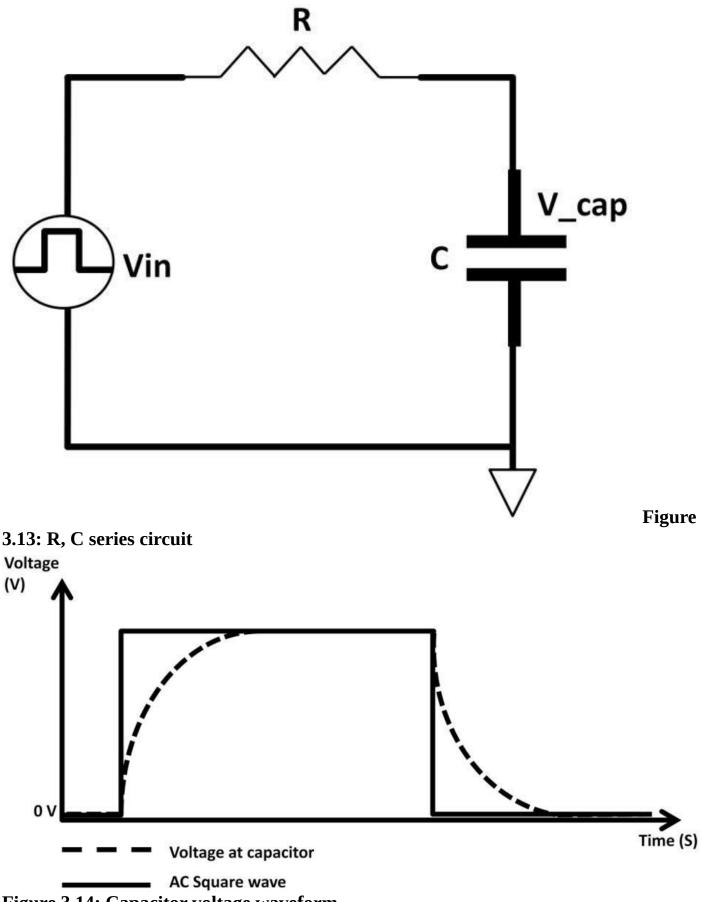

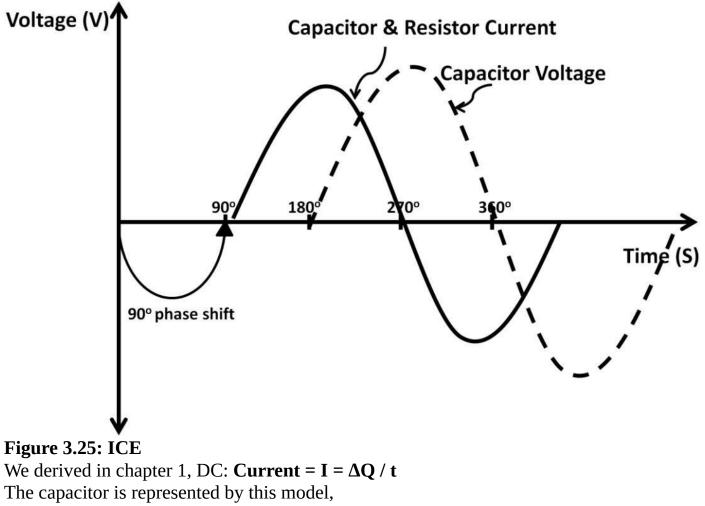

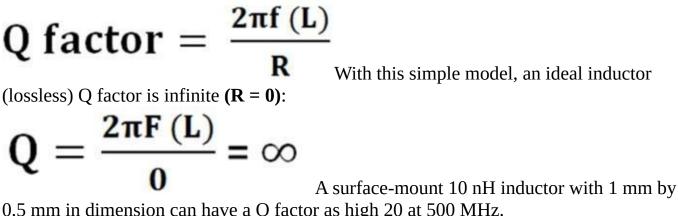

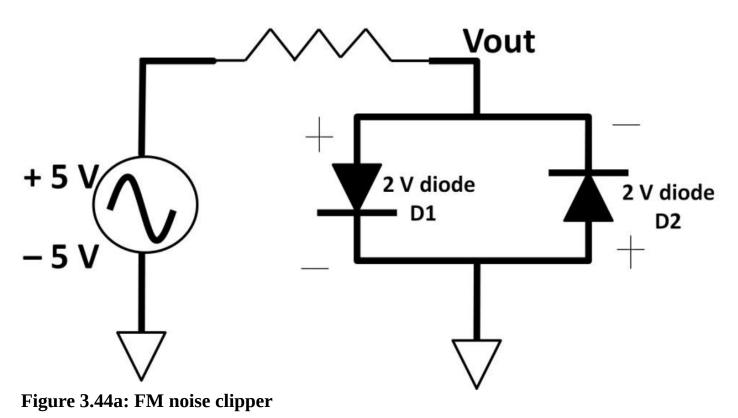

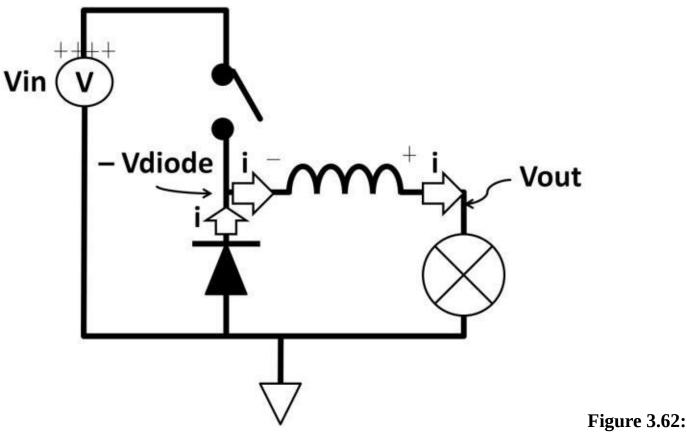

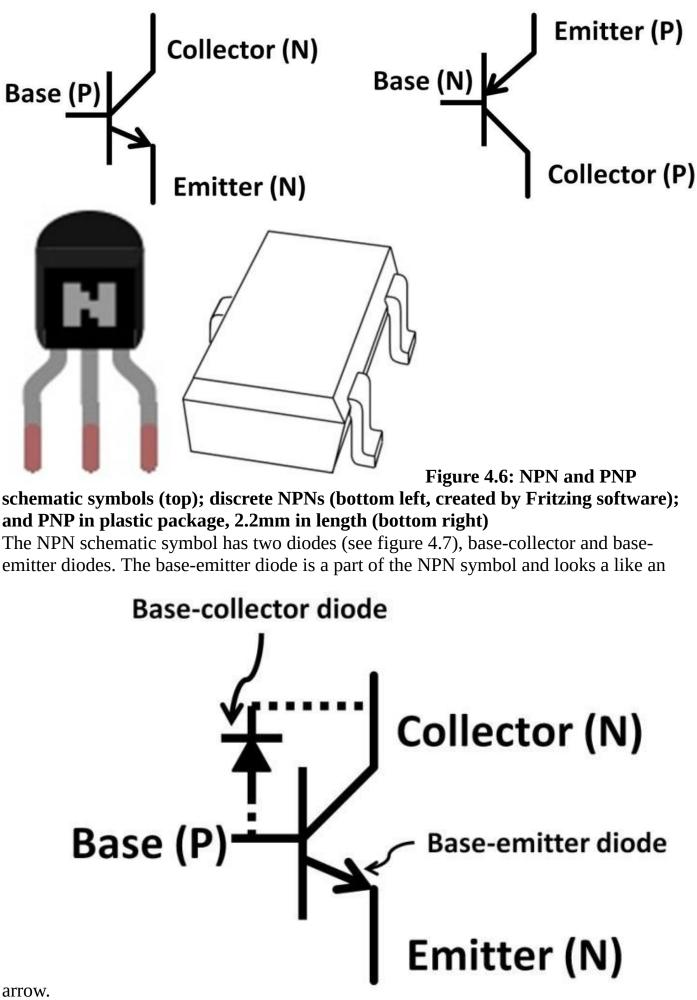

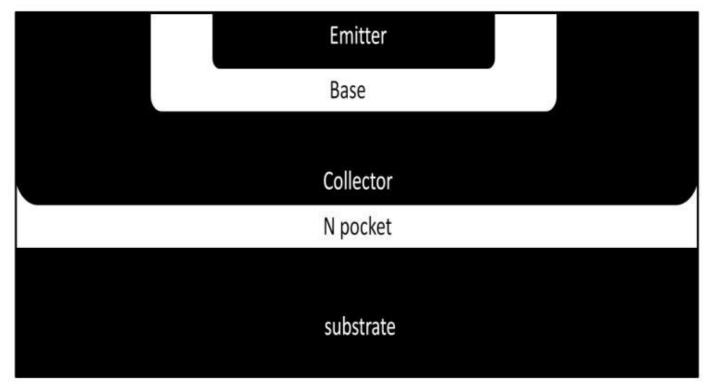

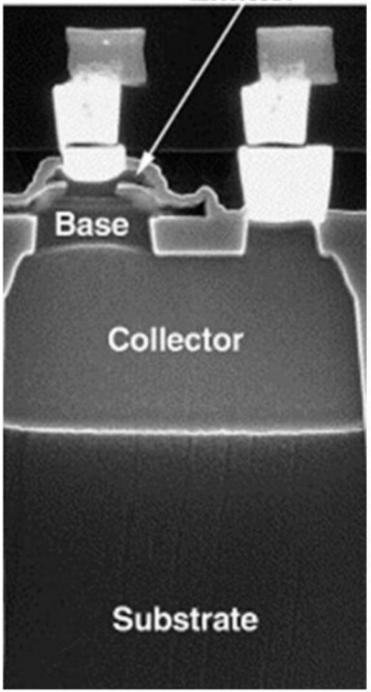

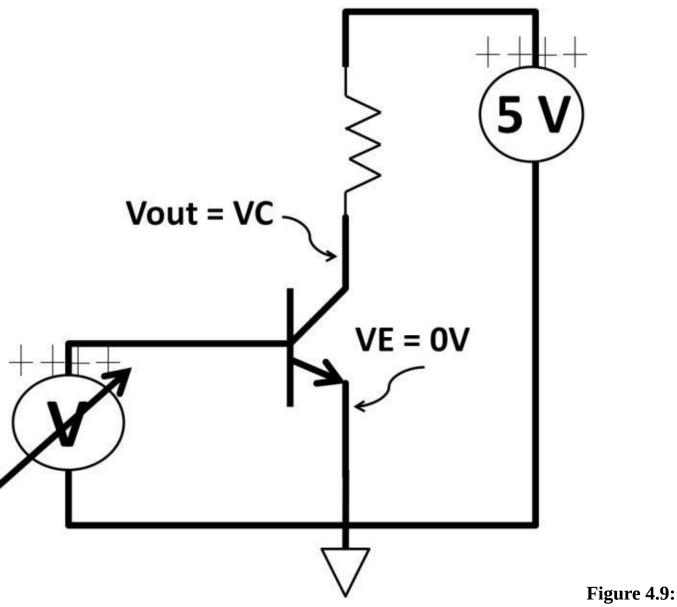

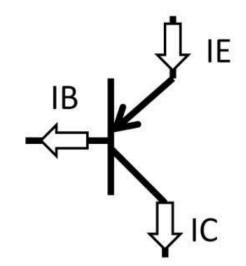

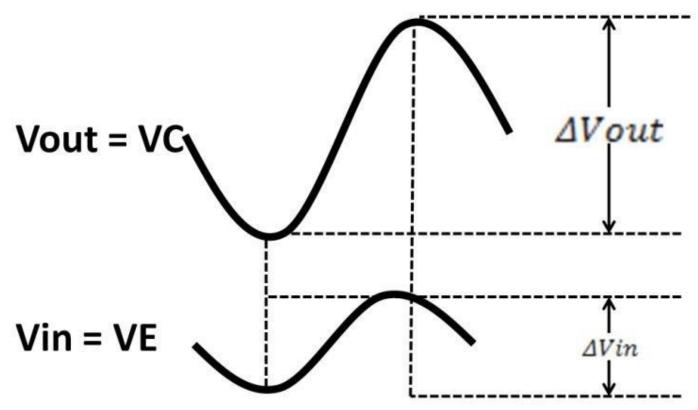

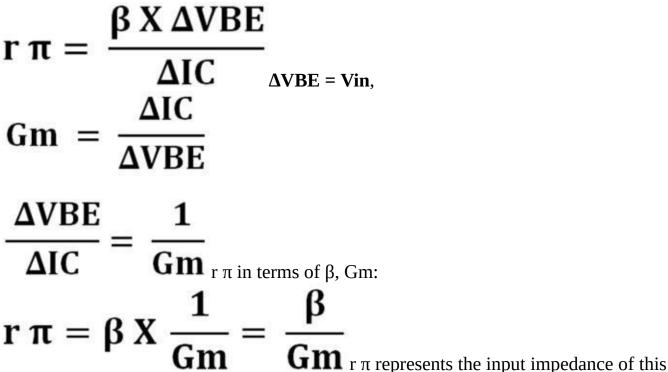

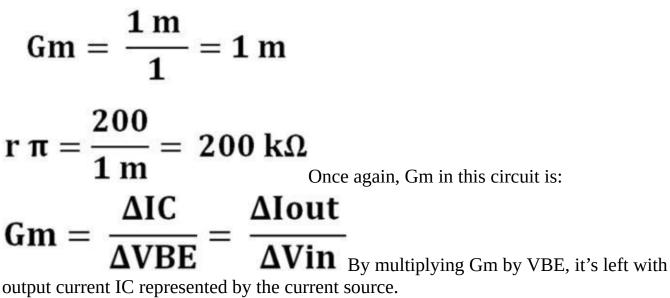

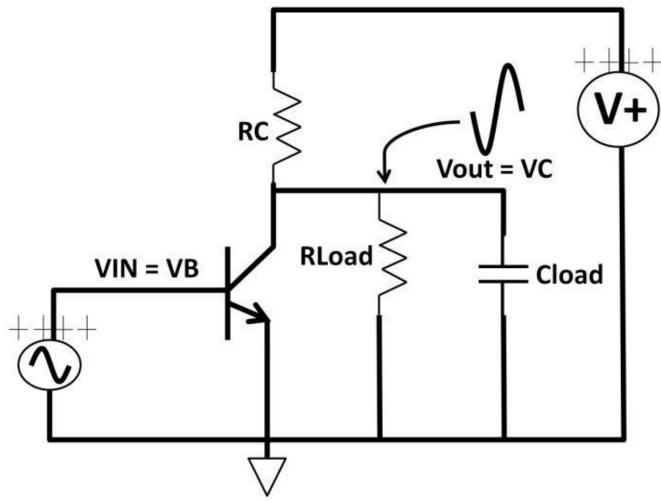

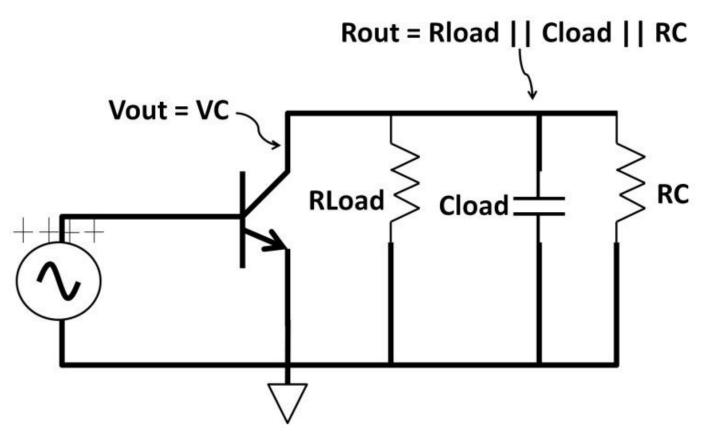

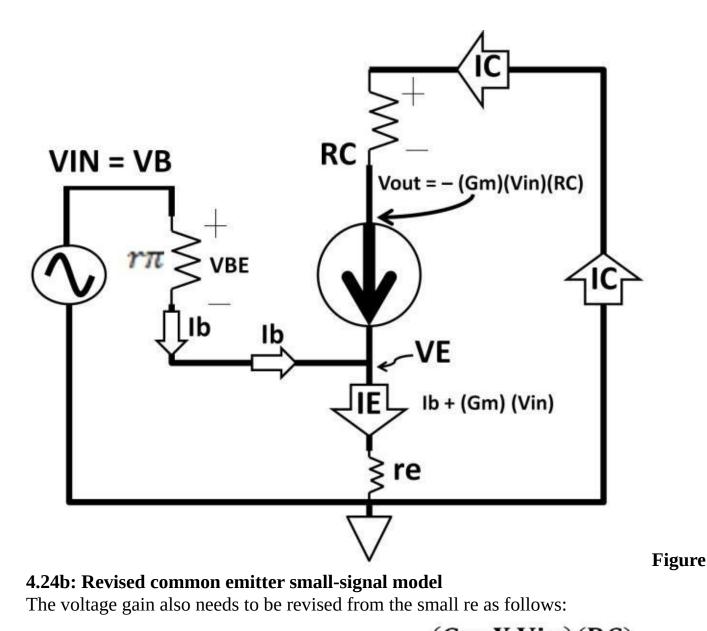

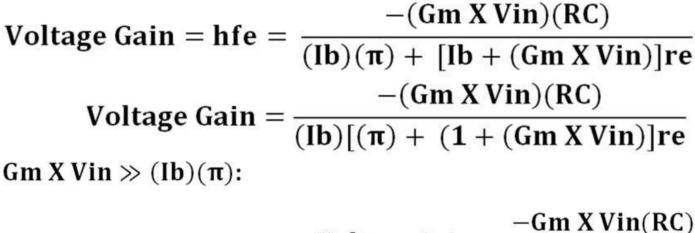

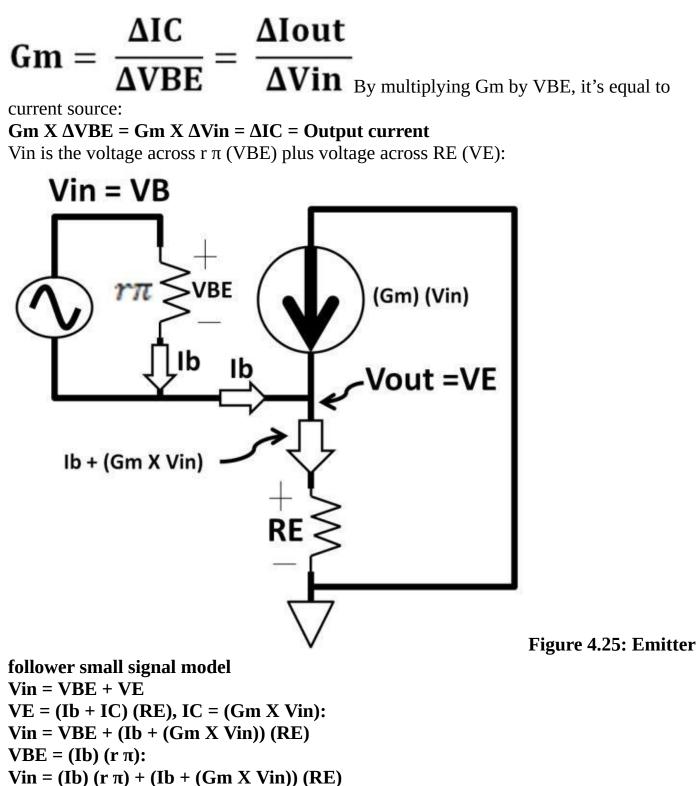

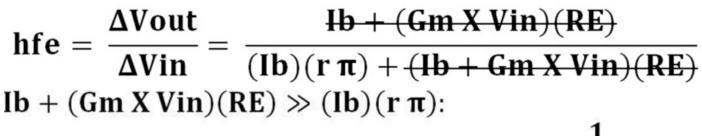

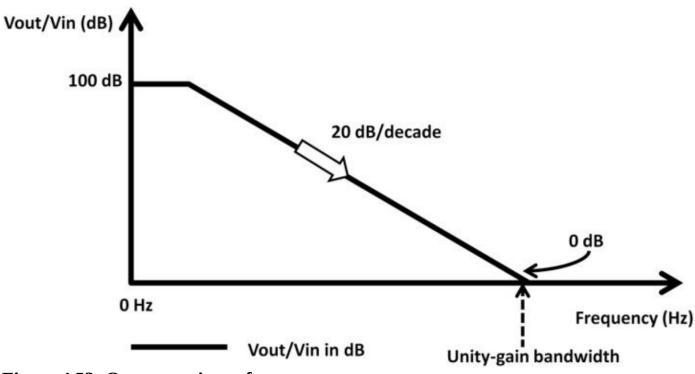

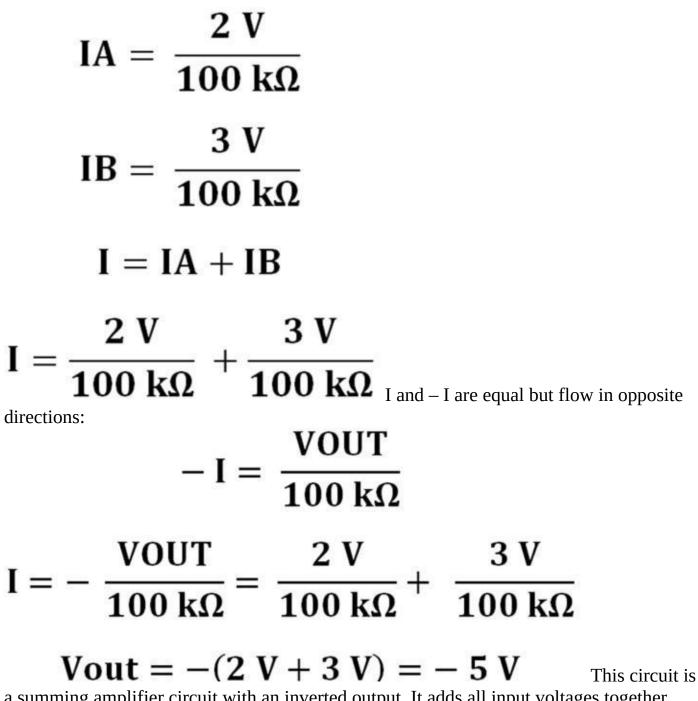

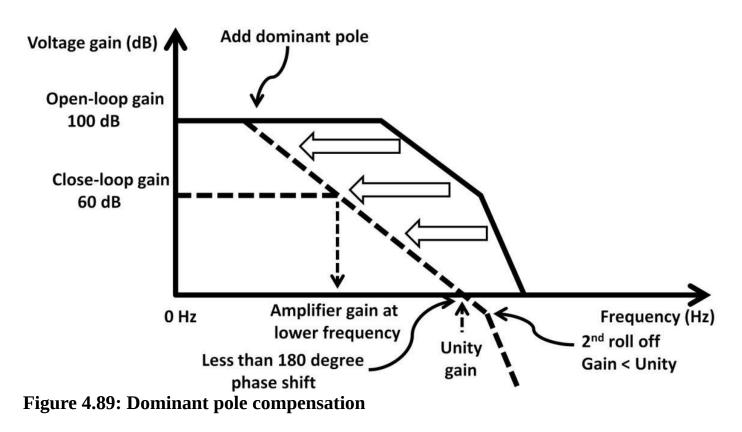

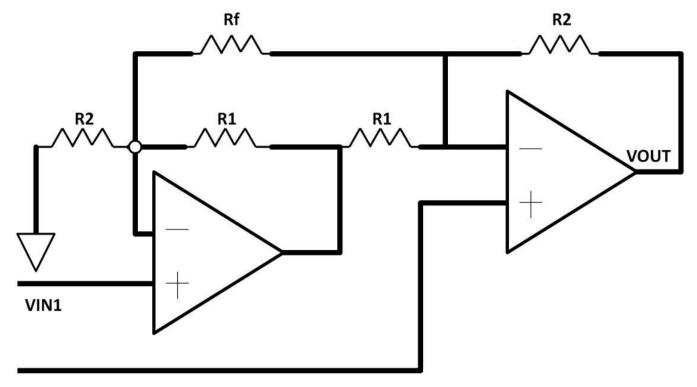

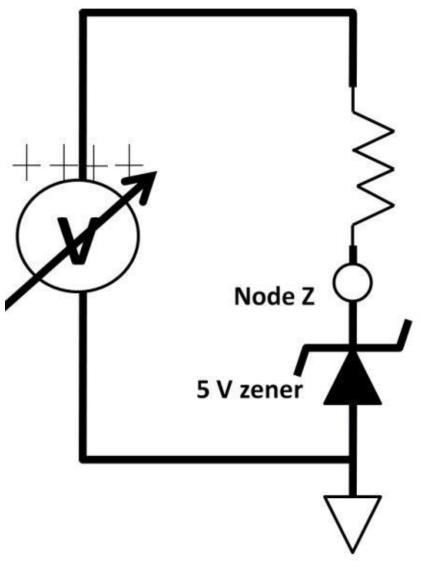

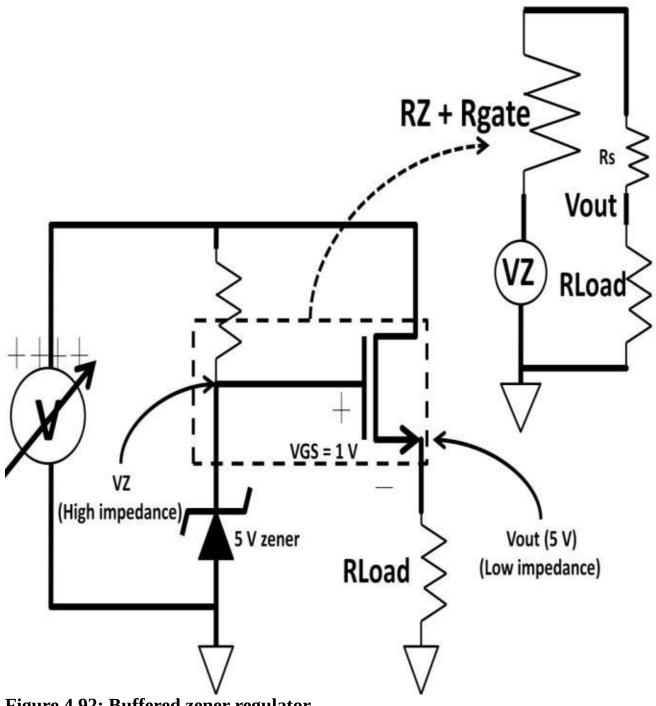

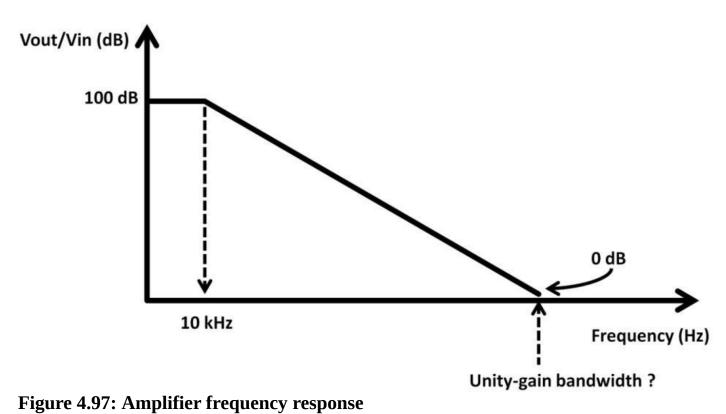

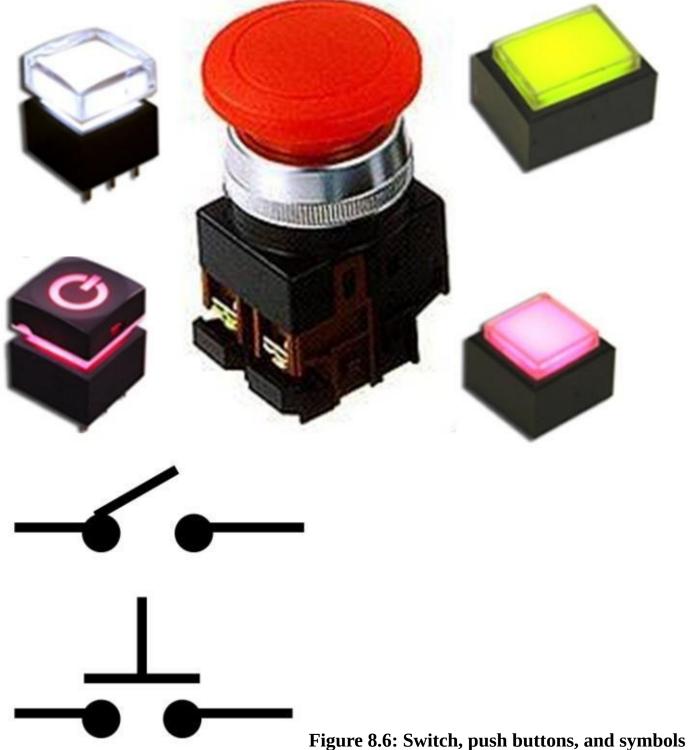

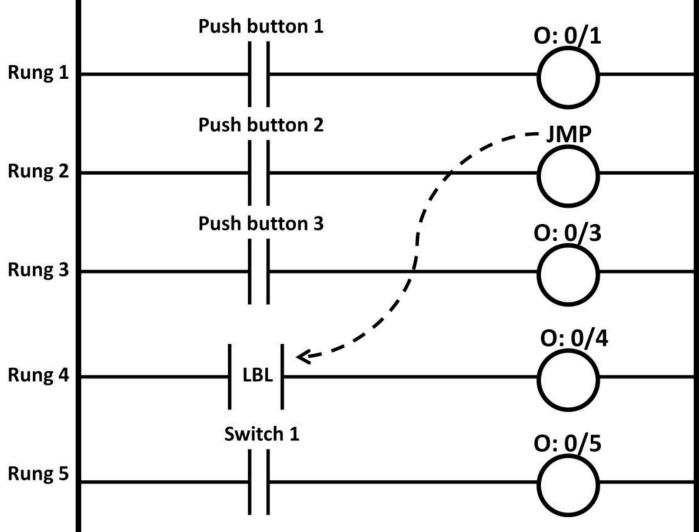

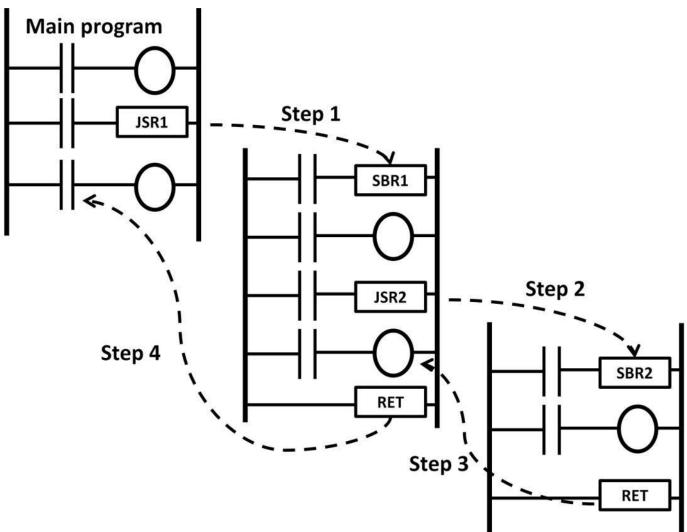

Ideal voltage source: Zero internal resistance