# Embedded System Design

Daniel D. Gajski • Samar Abdi Andreas Gerstlauer • Gunar Schirner

# Embedded System Design

Modeling, Synthesis and Verification

Daniel D. Gajski Center for Embedded Computer Systems University of California, Irvine 2010, AIR Bldg. Irvine, CA 92697-2620 USA gajski@uci.edu

Andreas Gerstlauer

Department of Electrical &

Computer Engineering

University of Texas at Austin

1 University Station C0803

Austin, TX 78712

USA

gerstl@ece.utexas.edu

Samar Abdi Center for Embedded Computer Systems University of California, Irvine 2010, AIR Bldg. Irvine, CA 92697-2620 USA sabdi@uci.edu

Gunar Schirner

Center for Embedded Computer Systems

University of California, Irvine

2010, AIR Bldg.

Irvine, CA 92697-2620

USA

hschirne@uci.edu

ISBN 978-1-4419-0503-1 e-ISBN 978-1-4419-0504-8 DOI 10.1007/978-1-4419-0504-8 Springer Dordrecht Heidelberg London New York

Library of Congress Control Number: 20099931042

© Springer Science+Business Media, LLC 2009

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden.

The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

## **Preface**

## RATIONALE

In the last twenty five years, design technology, and the EDA industry in particular, have been very successful, enjoying an exceptional growth that has been paralleled only by advances in semiconductor fabrication. Since the design problems at the lower levels of abstraction became humanly intractable and time consuming earlier then those at higher abstraction levels, researchers and the industry alike were forced to devote their attention first to problems such as circuit simulation, placement, routing and floorplanning. As these problems become more manageable, CAD tools for logic simulation and synthesis were developed successfully and introduced into the design process. As design complexities have grown and time-to-market have shrunk drastically, both industry and academia have begun to focus on levels of design that are even higher then layout and logic. Since higher levels of abstraction reduce by an order of magnitude the number of objects that a designer needs to consider, they have allowed industry to design and manufacture complex application-oriented integrated circuits in shorter periods of time.

Following in the footsteps of logic synthesis, register-transfer and high-level synthesis have contributed to raising abstraction levels in the design methodology to the processor level. However, they are used for the design of a single custom processor, an application-specific or communication component or an interface component. These components, along with standard processors and memories, are used as components in systems whose design methodology requires even higher levels of abstraction: system level. A system-level design focuses on the specification of the systems in terms of some models of computations using some abstract data types, as well as the transformation or refinement of that specification into a system platform consisting of a set of processor-level components, including generation of custom software and hardware components. To this point, however, in spite of the fact that sys-

tems have been manufactured for years, industry and academia have not been sufficiently focused on developing and formalizing a system-level design technology and methodology, even though there was a clear need for it. This need has been magnified by appearance of embedded systems, which can be used anywhere and everywhere, in plains, trains, houses, humans, environment, and manufacturing and in any possible infrastructure. They are application specific and tightly constrained by different requirements emanating from the environment they operate in. Together with ever increasing complexities and market pressures, this makes their design a tremendous challenge and the development of a clear and well-defined system-level design technology unavoidable.

There are two reasons for emphasizing more abstract, system-level methodologies. The first is the fact that high-level abstractions are closer to a designer's usual way of reasoning. It would be difficult to imagine, for example, how a designer could specify, model and communicate a system design by means of a schematic or hundred thousand lines of VHDL or Verilog code. The more complex the design, the more difficult it is for the designer to comprehend its functionality when it is specified on register-transfer level of abstraction. On the other hand, when a system is described with an application-oriented model of computation as a set of processes that operate on abstract data types and communicate results through abstract channels, the designer will find it much easier to specify and verify proper functionality and to evaluate various implementations using different technologies. The second reason is that embedded system are usually defined by the experts in application domain who understand application very well, but have only basic knowledge of design technology and practice. System-level design technology allows them to specify, explore and verify their embedded system products without expert knowledge of system engineering and manufacturing.

It must be acknowledged that research on system design did start many years ago; at the time, however, it remained rather focused to specific domains and communities. For example, the computer architecture community has considered ways of partitioning and mapping computations to different architectures, such as hypercubes, multiprocessors, massively parallel or heterogeneous processors. The software engineering community has been developing methods for specifying and generating software code. The CAD community has focused on system issues such as specification capture, languages, and modeling. However, simulation languages and models are not synthesizable or verifiable for lack of proper design meaning and formalism. That resulted in proliferation of models and modeling styles that are not useful beyond the modeler's team. By introduction of well-defined model semantics, and corresponding model transformations for different design decision, it is possible to generate models automatically. Such models are also synthesizable and verifiable. Furthermore, model automation relieves designers from error-prone model coding and even

learning the modeling language. This approach is appealing to application experts since they need to know only the application and experiment with a set of design decisions. Unfortunately, a universally accepted theoretical framework and CAD environments that support system design methodologies based on these concepts are not commercially available yet, although some experimental versions demonstrated several orders of magnitude productivity gain. On the other hand, embedded-system design-technology based on these concepts has matured to the point that a book summarizing the basic ideas and results developed so far will help students and practitioners in embedded system design.

In this book, we have tried to include ideas and results from a wide variety of sources and research projects. However, due to the relative youth of this field, we may have overlooked certain interesting and useful projects; for this we apologize in advance, and hope to hear about those projects so they may be incorporated into future editions. Also, there are several important system-level topics that, for various reasons, we have not been able to cover in detail here, such as testing and design for test. Nevertheless, we believe that a book on embedded system techniques and technology will help upgrade computer science and engineering education toward system-level and toward application oriented embedded systems, stimulate design automation community to move beyond system level simulation and develop system-level synthesis and verification tools and support the new emerging embedded application community to become more innovative and self-sustaining.

## **AUDIENCE**

This book is intended for four different groups within the embedded system community. First, it should be an introductory book for application-product designers and engineers in the field of mechanical, civil, bio-medical, electrical, and environmental, energy, communication, entertainment and other application fields. This book may help them understand and design embedded systems in their application domain without an expert knowledge of system design methods bellow system-level. Second, this book should also appeal to system designers and system managers, who may be interested in embedded system methodology, software-hardware co-design and design process management. They may use this book to create a new system level methodology or to upgrade one existing in their company. Third, this book can also be used by CAD-tool developers, who may want to use some of its concepts in existing or future tools for specification capture, design exploration and system modeling, synthesis and verification. Finally, since the book surveys the basic concepts and principles of system-design techniques and methodologies, including software and hardware, it could be valuable to advanced teachers and academic

programs that want to teach software and hardware concepts together instead of in non-related courses. That is particularly needed in today's embedded systems where software and hardware are interchangeable. From this point, the book would also be valuable for an advanced undergraduate or graduate course targeting students who want to specialize in embedded system, design automation and system design and engineering. Since the book covers multiple aspects of system design, it would be very useful reference for any senior project course in which students design a real prototype or for graduate project for system-level tool development.

## **ORGANIZATION**

This book has been organized into eight chapters that can be divided into four parts. Chapter 1 and 2 present the basic issues in embedded system design and discuss various system-design methodologies that can be used in capturing system behavior and refining it into system implementation. Chapter 3 and 4 deal with different models of computations and system modeling at different levels of abstraction as well as system synthesis from those models. Chapter 5, 6, and 7 deal with issues and possible solutions in synthesis and verification of software and hardware component needed in a embedded system platform. Finally, Chapter 8 reviews the key developments and selected current academic and commercial tools in the field of system design, system software and system hardware as well as case study of embedded system environments.

Given an understanding of the basic concepts defined in Chapter 1 and 2, each chapter should be self-contained and can be read independently. We have used the same writing style and organization in each chapter of the book. A typical chapter includes an introductory example, defines the basic concepts, it describes the main problems to be solved. It contains a description of several possible solutions, methods or algorithms to the problems that have been posed, and explains the advantages and disadvantages of each approach. Each chapter also includes relationship to previously published work in the field and discusses some open problems in each topic.

This book could be used in several different courses. One course would be for application experts with only a basic knowledge of computers engineering. It would emphasize application issues, system specification in application oriented models of computation, system modeling and exploration as presented in Chapter 1 - 4. The second course for embedded system designers would emphasize system languages, specification capture, system synthesis and verification with emphasis on Chapter 3, Chapter 4, and Chapter 7. The third course may emphasize system development with component synthesis and tools as described in Chapter 5 - Chapter 8. In which ever it is used, though, we feel that

*PREFACE* ix

this book will help to fill the vacuum in computer science and engineering curriculum where there is need and demand for emphasis on teaching embedded system design techniques in addition to supporting lower levels of abstraction dealing with circuit, logic and architecture design.

We hope that the material selection and the writing style will approach your expectations; we welcome your suggestions and comments.

Daniel Gajski, Andreas Gerstlauer, Samar Abdi, Gunar Schirner

## Acknowledgments

This book was in the making for many years: from concepts to methodologies to experiments. Many generations of researchers at the Center for Embedded Systems at UCI participated in finding and proving what works and what does not. We would like to thank the members of the first generation that established basic principles of embedded systems: Frank Vahid, Sanjiv Narayan, Jie Gong and Smita Bakshi. We would also like to acknowledge the second generation that brought us SpecC and System on Chip Environment: Jianwen Zhu, Rainer Doemer, Lukai Cai, Haobo Yu, Sequin Zhao, Dongwan Shin, and Jerry Peng. And the third generation that made Embedded System Environment available: Lochi Yu, Hansu Cho, Yongyun Hwang, Ines Viskic. In addition, we would like to acknowledge the NISC team: Mehrdad Reshadi, Bita Gorjiara and Jelena Trajkovic for their high-level synthesis contributions and Pramod Chandraria for his work on design drivers.

We would also like to thank Quoc-Viet Dang, who helped us with book formatting, figure creation, generation, and without whom this book would not be possible. We also want to thank our editors Matt Nelson and Brian Thill who made the sentences readable and ideas flow without interruptions. We also want to thank Simone Lacina from grafikdesign-lacina.de for an excellent and artistic cover.

However, the highest credits go to Grace Wu and Melanie Kilian for making our center work flawlessly while we were working and thinking about the book.

Last but not the least, we would like to thank Carl Harris from Springer for encouragement and asking at every conference in the last 5 years the same question: "When is the Orange book coming?"

## **Contents**

| face                                   | V                                                                                                     |

|----------------------------------------|-------------------------------------------------------------------------------------------------------|

| knowledgments                          | xi                                                                                                    |

| t of Figures                           | xix                                                                                                   |

| t of Tables                            | XXV                                                                                                   |

| INTRODUCTION                           | 1                                                                                                     |

| 1.1 System-Design Challenges           | 1                                                                                                     |

| 1.2 Abstraction Levels                 | 3                                                                                                     |

| 1.2.1 Y-Chart                          | 3                                                                                                     |

| 1.2.2 Processor-Level Behavioral Model | 5                                                                                                     |

| 1.2.3 Processor-level structural model | 7                                                                                                     |

| 1.2.4 Processor-level synthesis        | 10                                                                                                    |

| •                                      | 13                                                                                                    |

| •                                      | 14                                                                                                    |

|                                        | 14                                                                                                    |

| •                                      | 18                                                                                                    |

| _                                      | 20                                                                                                    |

| 1.3.2 Model Algebra                    | 21                                                                                                    |

| 1.4 System-Level Models                | 23                                                                                                    |

| 1.5 Platform Design                    | 27                                                                                                    |

| 1.6 System Design Tools                | 29                                                                                                    |

| 1.7 Summary                            | 32                                                                                                    |

| SYSTEM DESIGN METHODOLOGIES            | 35                                                                                                    |

| 2.1 Bottom-up Methodology              | 35                                                                                                    |

| 2.2 Top-down Methodology               | 37                                                                                                    |

| 2.3 Meet-in-the-middle Methodology     | 38                                                                                                    |

|                                        | knowledgments of Figures of Tables  INTRODUCTION  1.1 System-Design Challenges 1.2 Abstraction Levels |

| X | 1 | V |

|---|---|---|

|   |   |   |

|    | 2.4 Platform Methodology              | 40  |

|----|---------------------------------------|-----|

|    | 2.5 FPGA Methodology                  | 43  |

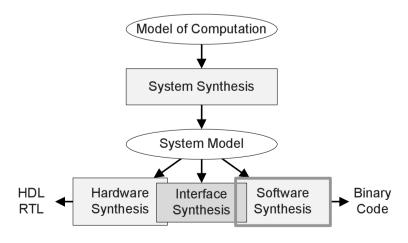

|    | 2.6 System-level Synthesis            | 44  |

|    | 2.7 Processor Synthesis               | 45  |

|    | 2.8 Summary                           | 47  |

| 3. | MODELING                              | 49  |

|    | 3.1 Models of Computation             | 50  |

|    | 3.1.1 Process-Based Models            | 52  |

|    | 3.1.2 State-Based Models              | 58  |

|    | 3.2 System Design Languages           | 65  |

|    | 3.2.1 Netlists and Schematics         | 66  |

|    | 3.2.2 Hardware-Description Languages  | 66  |

|    | 3.2.3 System-Level Design Languages   | 68  |

|    | 3.3 System Modeling                   | 68  |

|    | 3.3.1 Design Process                  | 69  |

|    | 3.3.2 Abstraction Levels              | 71  |

|    | 3.4 Processor Modeling                | 72  |

|    | 3.4.1 Application Layer               | 73  |

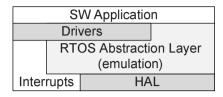

|    | 3.4.2 Operating System Layer          | 75  |

|    | 3.4.3 Hardware Abstraction Layer      | 78  |

|    | 3.4.4 Hardware Layer                  | 80  |

|    | 3.5 Communication Modeling            | 83  |

|    | 3.5.1 Application Layer               | 84  |

|    | 3.5.2 Presentation Layer              | 88  |

|    | 3.5.3 Session Layer                   | 90  |

|    | 3.5.4 Network Layer                   | 92  |

|    | 3.5.5 Transport Layer                 | 93  |

|    | 3.5.6 Link Layer                      | 94  |

|    | 3.5.7 Stream Layer                    | 98  |

|    | 3.5.8 Media Access Layer              | 99  |

|    | 3.5.9 Protocol and Physical Layers    | 100 |

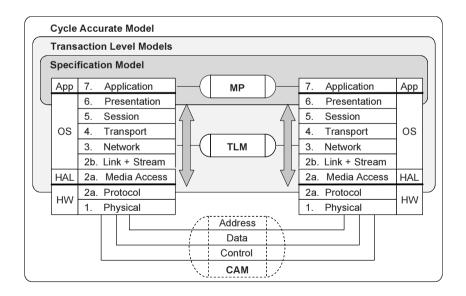

|    | 3.6 System Models                     | 102 |

|    | 3.6.1 Specification Model             | 103 |

|    | 3.6.2 Network TLM                     | 104 |

|    | 3.6.3 Protocol TLM                    | 106 |

|    | 3.6.4 Bus Cycle-Accurate Model (BCAM) | 107 |

|    | 3.6.5 Cycle-Accurate Model (CAM)      | 108 |

Contents xv

|    | 3.7 | Summ    | ary                                   | 109 |

|----|-----|---------|---------------------------------------|-----|

| 4. | SYS | STEM S  | SYNTHESIS                             | 113 |

|    | 4.1 | System  | n Design Trends                       | 114 |

|    |     | -       | Based Design                          | 117 |

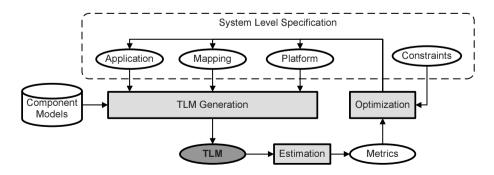

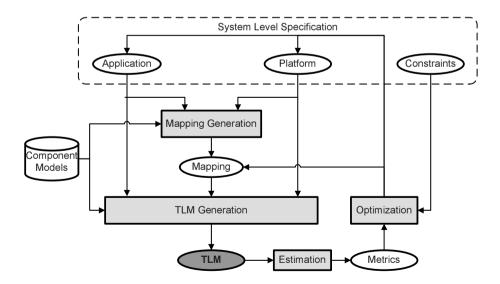

|    |     |         | natic TLM Generation                  | 120 |

|    |     |         | Application Modeling                  | 122 |

|    |     |         | Platform Definition                   | 123 |

|    |     |         | Application to Platform Mapping       | 124 |

|    |     |         | TLM Based Performance Estimation      | 126 |

|    |     | 4.3.5   | TLM Semantics                         | 130 |

|    | 4.4 | Autom   | atic Mapping                          | 132 |

|    |     | 4.4.1   | GSM Encoder Application               | 134 |

|    |     | 4.4.2   | Application Profiling                 | 135 |

|    |     | 4.4.3   | Load Balancing Algorithm              | 138 |

|    |     | 4.4.4   | Longest Processing Time Algorithm     | 142 |

|    | 4.5 | Platfor | rm Synthesis                          | 146 |

|    |     | 4.5.1   | Component data models                 | 147 |

|    |     | 4.5.2   | Platform Generation Algorithm         | 148 |

|    |     | 4.5.3   | Cycle Accurate Model Generation       | 151 |

|    |     | 4.5.4   | Summary                               | 152 |

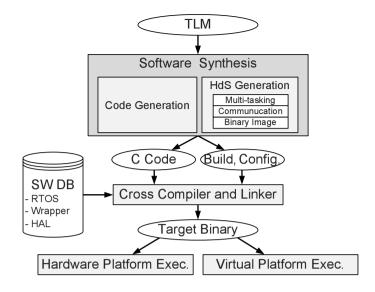

| 5. | SOF | TWAR    | RE SYNTHESIS                          | 155 |

|    | 5.1 | Prelim  | inaries                               | 156 |

|    |     | 5.1.1   | Target Languages for Embedded Systems | 157 |

|    |     | 5.1.2   | RTOS                                  | 159 |

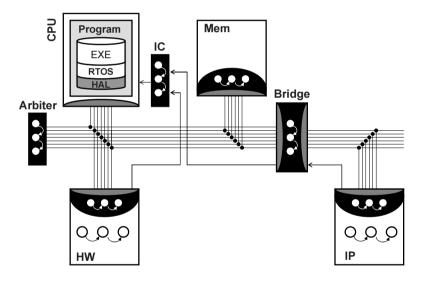

|    | 5.2 | Softwa  | are Synthesis Overview                | 162 |

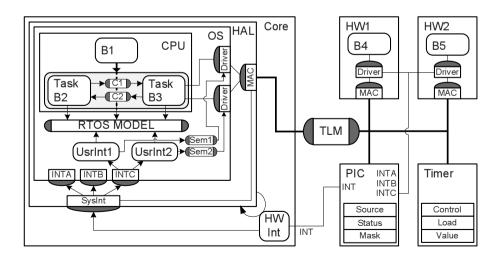

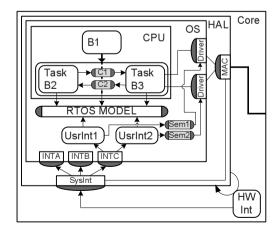

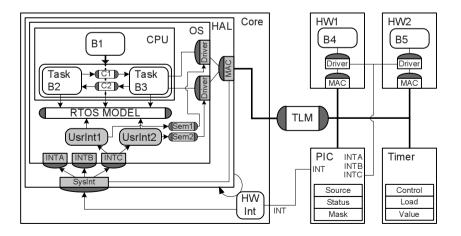

|    |     | 5.2.1   | Example Input TLM                     | 164 |

|    |     | 5.2.2   | Target Architecture                   | 166 |

|    | 5.3 | Code (  | Generation                            | 167 |

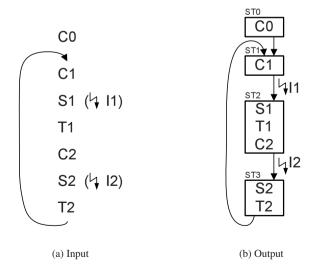

|    | 5.4 | Multi-  | Task Synthesis                        | 173 |

|    |     | 5.4.1   | RTOS-based Multi-Tasking              | 173 |

|    |     | 5.4.2   | Interrupt-based Multi-Tasking         | 176 |

|    | 5.5 | Interna | al Communication                      | 181 |

|    | 5.6 | Extern  | al Communication                      | 182 |

|    |     | 5.6.1   | Data Formatting                       | 183 |

|    |     | 5.6.2   | Packetization                         | 185 |

|    |     | 5.6.3   | Synchronization                       | 186 |

|    |     | 5.6.4   | Media Access Control                  | 191 |

| <b>EMBEDDED</b> | SYSTEM | DESIGN: |

|-----------------|--------|---------|

|                 |        |         |

|              |    | • |

|--------------|----|---|

| $\mathbf{v}$ | 17 | 1 |

| $^{\Lambda}$ | v  |   |

| 5.7 Startup Code                                   | 193 |

|----------------------------------------------------|-----|

| 5.8 Binary Image Generation                        | 194 |

| 5.9 Execution                                      | 195 |

| 5.10Summary                                        | 196 |

| 6. HARDWARE SYNTHESIS                              | 199 |

| 6.1 RTL Architecture                               | 201 |

| 6.2 Input Models                                   | 204 |

| 6.2.1 C-code specification                         | 204 |

| 6.2.2 Control-Data Flow Graph specification        | 205 |

| 6.2.3 Finite State Machine with Data specification | 207 |

| 6.2.4 RTL specification                            | 208 |

| 6.2.5 HDL specification                            | 209 |

| 6.3 Estimation and Optimization                    | 211 |

| 6.4 Register Sharing                               | 216 |

| 6.5 Functional Unit Sharing                        | 220 |

| 6.6 Connection Sharing                             | 224 |

| 6.7 Register Merging                               | 227 |

| 6.8 Chaining and Multi-Cycling                     | 229 |

| 6.9 Functional-Unit Pipelining                     | 232 |

| 6.10Datapath Pipelining                            | 235 |

| 6.11Control and Datapath Pipelining                | 237 |

| 6.12Scheduling                                     | 240 |

| 6.12.1RC scheduling                                | 243 |

| 6.12.2TC scheduling                                | 244 |

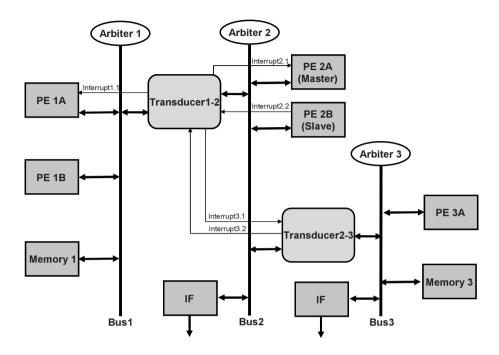

| 6.13Interface Synthesis                            | 248 |

| 6.14Summary                                        | 253 |

| 7. VERIFICATION                                    | 255 |

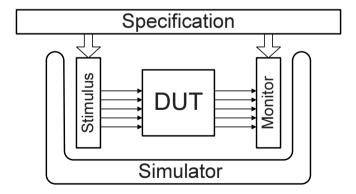

| 7.1 Simulation Based Methods                       | 257 |

| 7.1.1 Stimulus Optimization                        | 260 |

| 7.1.2 Monitor Optimization                         | 262 |

| 7.1.3 SpeedUp Techniques                           | 263 |

| 7.1.4 Modeling Techniques                          | 264 |

| 7.2 Formal Verification Methods                    | 265 |

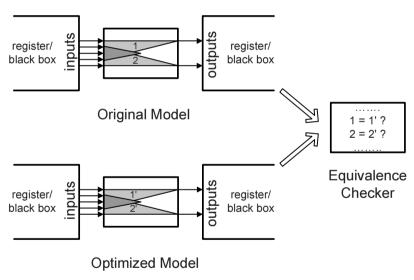

| 7.2.1 Logic Equivalence Checking                   | 266 |

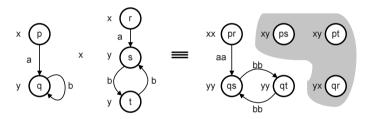

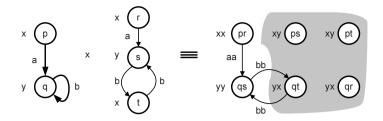

| 7.2.2 FSM Equivalence Checking                     | 268 |

| 7.2.3 Model Checking                              | 270 |

|---------------------------------------------------|-----|

| 7.2.4 Theorem Proving                             | 273 |

| 7.2.5 Drawbacks of Formal Verification            | 275 |

| 7.2.6 Improvements to Formal Verification Methods | 275 |

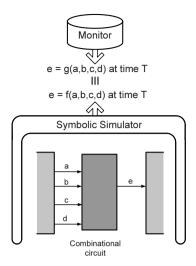

| 7.2.7 Semi-formal Methods: Symbolic Simulation    | 276 |

| 7.3 Comparative Analysis of Verification Methods  | 276 |

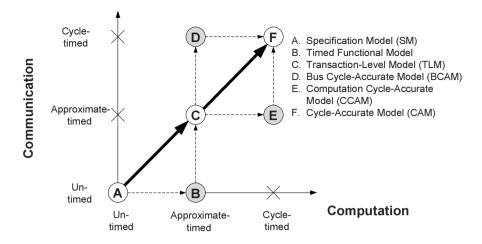

| 7.4 System Level Verification                     | 278 |

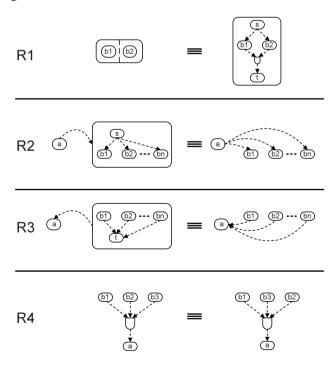

| 7.4.1 Formal Modeling                             | 280 |

| 7.4.2 Model Algebra                               | 282 |

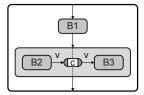

| 7.4.3 Verification by Correct Refinement          | 283 |

| 7.5 Summary                                       | 285 |

| 8. EMBEDDED DESIGN PRACTICE                       | 287 |

| 8.1 System Level Design Tools                     | 287 |

| 8.1.1 Academic Tools                              | 289 |

| 8.1.2 Commercial Tools                            | 296 |

| 8.1.3 Outlook                                     | 299 |

| 8.2 Embedded Software Design Tools                | 300 |

| 8.2.1 Academic Tools                              | 301 |

| 8.2.2 Commercial Tools                            | 303 |

| 8.2.3 Outlook                                     | 305 |

| 8.3 Hardware Design Tools                         | 306 |

| 8.3.1 Academic Tools                              | 308 |

| 8.3.2 Commercial Tools                            | 314 |

| 8.3.3 Outlook                                     | 319 |

| 8.4 Case Study                                    | 319 |

| 8.4.1 Embedded System Environment                 | 320 |

| 8.4.2 Design Driver: MP3 Decoder                  | 324 |

| 8.4.3 Results                                     | 327 |

| 8.5 Summary                                       | 333 |

| References                                        | 335 |

| Index                                             | 349 |

|                                                   |     |

# **List of Figures**

| 1.1  | Y-Chart                                         | 3  |

|------|-------------------------------------------------|----|

| 1.2  | FSMD model                                      | 5  |

| 1.3  | CDFG model                                      | 6  |

| 1.4  | Instruction-set flow chart                      | 8  |

| 1.5  | Processor structural model                      | 9  |

| 1.6  | Processor synthesis                             | 11 |

| 1.7  | System behavioral model                         | 13 |

| 1.8  | System structural model                         | 15 |

| 1.9  | System synthesis                                | 16 |

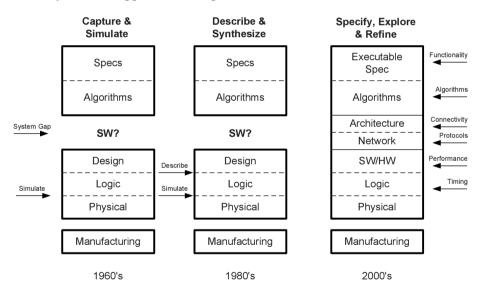

| 1.10 | Evolution of design flow over the past 50 years | 17 |

| 1.11 | Missing semantics                               | 20 |

| 1.12 | Model equivalence                               | 22 |

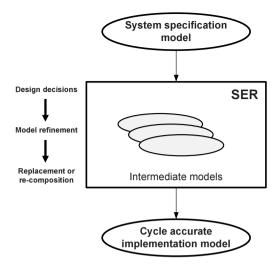

| 1.13 | SER Methodology                                 | 23 |

| 1.14 | System TLM                                      | 25 |

| 1.15 | System CAM                                      | 26 |

| 1.16 | Platform architecture                           | 28 |

| 1.17 | General system environment                      | 29 |

| 1.18 | System tools                                    | 31 |

| 2.1  | Bottom-up methodology                           | 36 |

| 2.2  | Top-down methodology                            | 37 |

| 2.3  | Meet-in-the-middle methodology (option 1)       | 39 |

| 2.4  | Meet-in-the-middle methodology (option 2)       | 40 |

| 2.5  | Platform methodology                            | 41 |

| 2.6  | System methodology                              | 42 |

| 2.7  | FPGA methodology                                | 43 |

|      |                                                 |    |

XX List of Figures

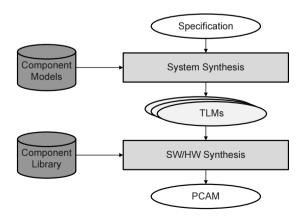

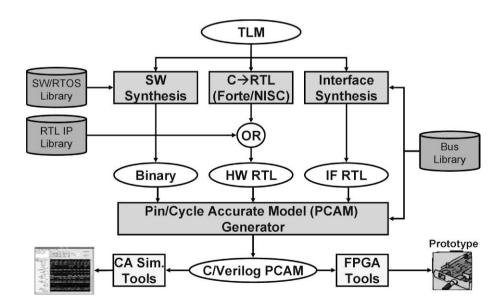

| 2.8  | System-level synthesis                                        | 44  |

|------|---------------------------------------------------------------|-----|

| 2.9  | Processor synthesis                                           | 46  |

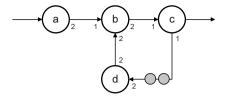

| 3.1  | Kahn Process Network (KPN) example                            | 54  |

| 3.2  | Synchronous Data Flow (SDF) example                           | 56  |

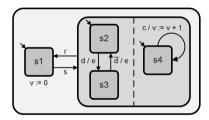

| 3.3  | Finite State Machine with Data (FSMD) example                 | 60  |

| 3.4  | Hierarchical, Concurrent Finite State Machine (HCFSM) example | 61  |

| 3.5  | Process State Machine (PSM) example                           | 64  |

| 3.6  | System design and modeling flow                               | 69  |

| 3.7  | Model granularities                                           | 71  |

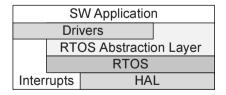

| 3.8  | Processor modeling layers                                     | 73  |

| 3.9  | Application layer                                             | 74  |

| 3.10 | Operating system layer                                        | 75  |

| 3.11 | Operating system modeling                                     | 76  |

| 3.12 | Task scheduling                                               | 77  |

| 3.13 | Hardware abstraction layer                                    | 79  |

| 3.14 | Interrupt scheduling                                          | 80  |

| 3.15 | Hardware layer                                                | 81  |

| 3.16 | Application layer synchronization                             | 86  |

| 3.17 | Application layer storage                                     | 87  |

| 3.18 | Application layer channels                                    | 88  |

| 3.19 | Presentation layer                                            | 89  |

| 3.20 | Session layer                                                 | 91  |

| 3.21 | Network layer                                                 | 92  |

| 3.22 | Communication elements                                        | 93  |

| 3.23 | Link layer                                                    | 95  |

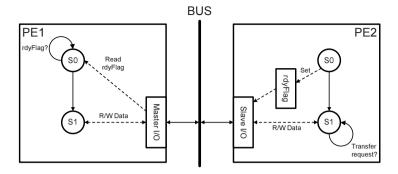

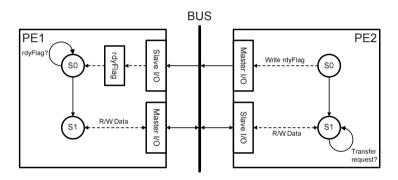

| 3.24 | Link layer synchronization                                    | 96  |

| 3.24 | Link layer synchronization (con't)                            | 97  |

| 3.25 | Media access layer                                            | 99  |

| 3.26 | Protocol layer                                                | 100 |

| 3.27 | Physical layer                                                | 101 |

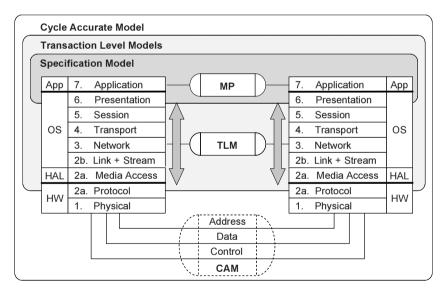

| 3.28 | System models                                                 | 102 |

| 3.29 | Specification model                                           | 104 |

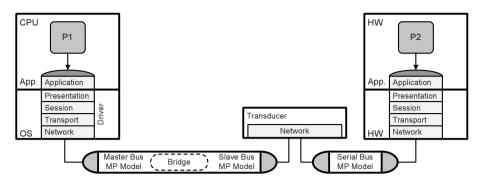

| 3.30 | Network TLM                                                   | 105 |

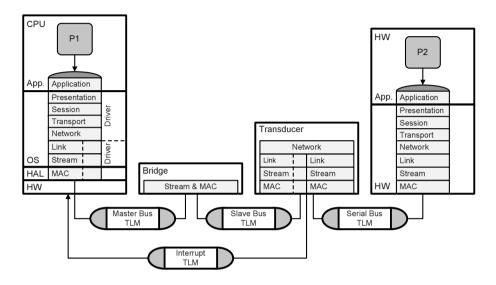

| 3.31 | Protocol TLM                                                  | 106 |

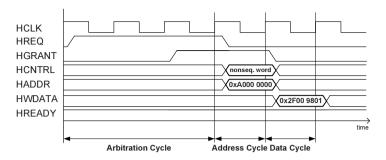

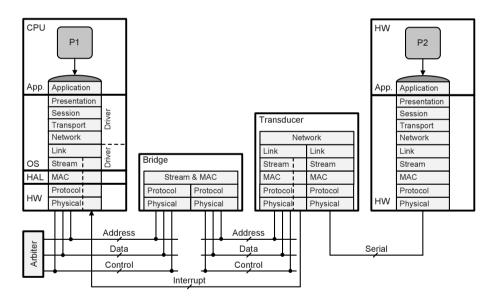

| 3.32 | Bus Cycle-Accurate Model (BCAM)                               | 107 |

| 3.33 | Cycle-Accurate Model (CAM)                                    | 108 |

| List of Figures | xxi |

|-----------------|-----|

|                 |     |

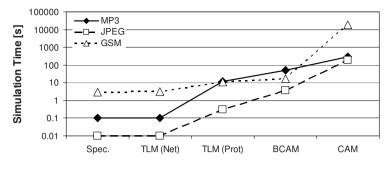

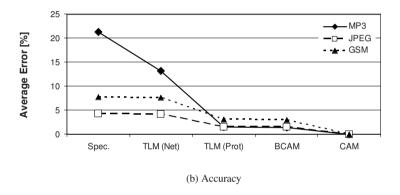

| 3.34 | Modeling results                                              | 110 |

|------|---------------------------------------------------------------|-----|

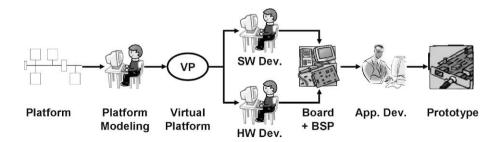

| 4.1  | A traditional board-based system design process.              | 114 |

| 4.2  | A virtual platform based development environment.             | 115 |

| 4.3  | A model based development flow of the future.                 | 116 |

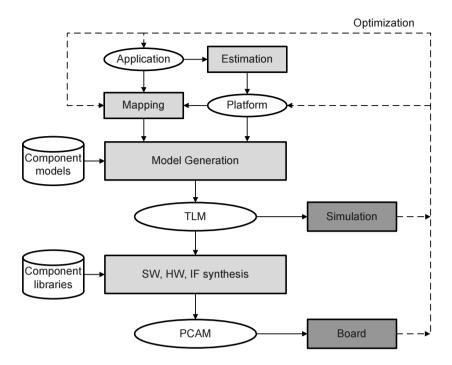

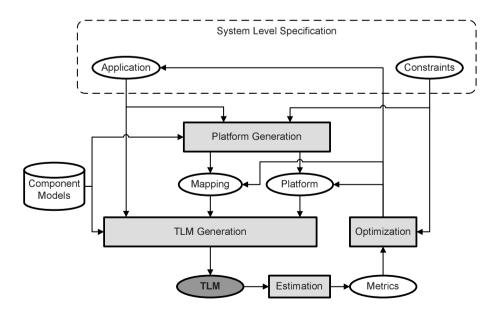

| 4.4  | TLM based design flow.                                        | 117 |

| 4.5  | Modeling layers for TLM.                                      | 118 |

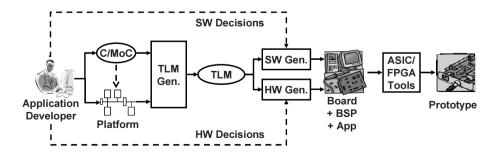

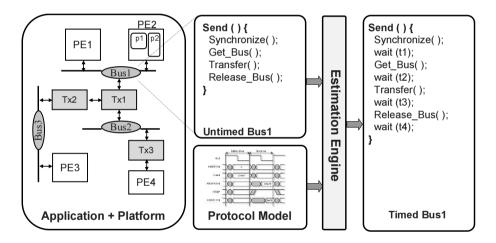

| 4.6  | System synthesis flow with given platform and mapping.        | 120 |

| 4.7  | A simple application expressed in PSM model of computation.   | 122 |

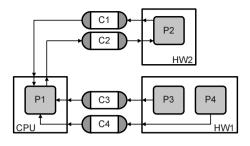

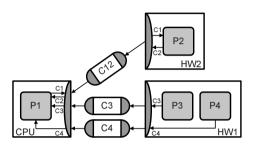

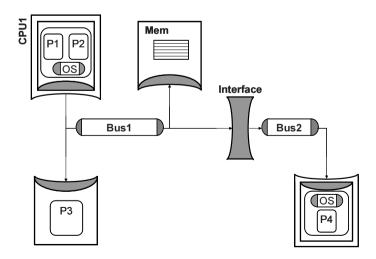

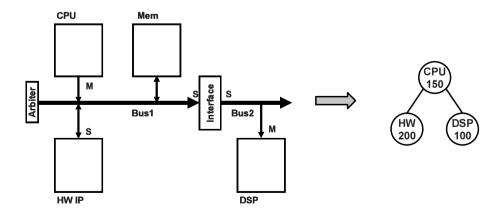

| 4.8  | A multicore platform specification.                           | 123 |

| 4.9  | Mapping from application model to platform.                   | 124 |

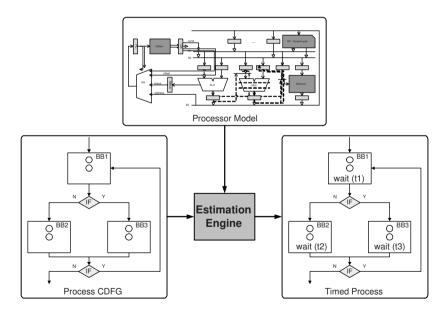

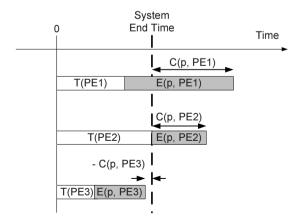

| 4.10 | Computation timing estimation.                                | 125 |

| 4.11 | Communication timing estimation.                              | 128 |

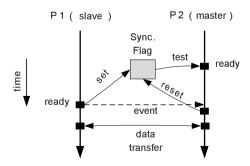

| 4.12 | Synchronization Modeling with Flags and Events.               | 128 |

| 4.13 | Automatically Generated TLM from system specification.        | 131 |

| 4.14 | System synthesis with fixed platform.                         | 133 |

| 4.15 | Application example: GSM Encoder                              | 134 |

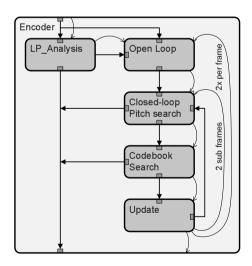

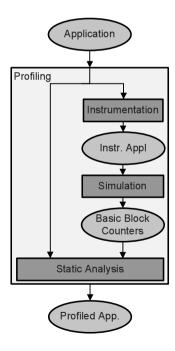

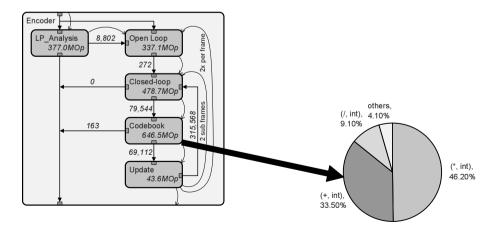

| 4.16 | Application profiling steps.                                  | 135 |

| 4.17 | Profiled statistics of GSM encoder.                           | 137 |

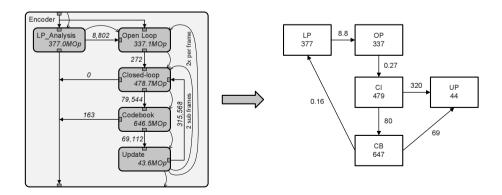

| 4.18 | Abstraction of profiled statistics into an application graph. | 138 |

| 4.19 | Creation of platform graph.                                   | 139 |

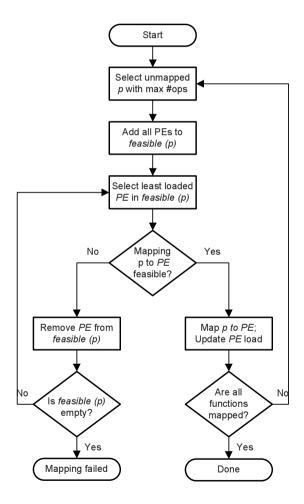

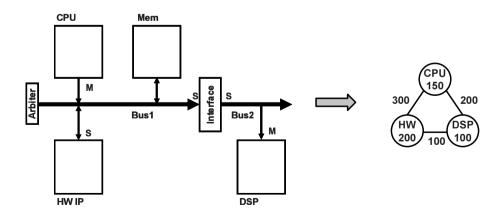

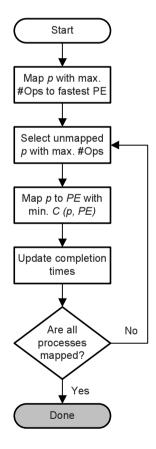

| 4.20 | Flowchart of load balancing algorithm for mapping generation. | 140 |

| 4.21 | Platform graph with communication costs.                      | 142 |

| 4.22 | LPT cost function computation.                                | 143 |

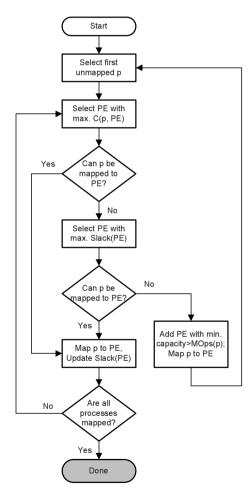

| 4.23 | Flowchart of LPT algorithm for mapping generation.            | 145 |

| 4.24 | System synthesis from application and constraints.            | 146 |

| 4.25 | Flowchart of a greedy algorithm for platform generation.      | 149 |

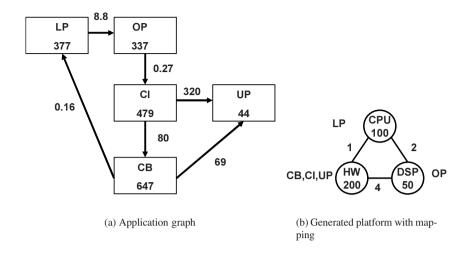

| 4.26 | Illustration of platform generation on a GSM Encoder example. | 150 |

| 4.27 | Cycle accurate model generation from TLM.                     | 152 |

| 5.1  | Synthesis overview                                            | 155 |

| 5.2  | Software synthesis flow                                       | 163 |

| 5.3  | Input system TLM example                                      | 164 |

| 5.4  | Generic target architecture                                   | 166 |

| 5.5  | Task specification                                            | 169 |

| 5.6  | Software execution stack for RTOS-based multi-tasking         | 173 |

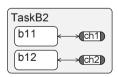

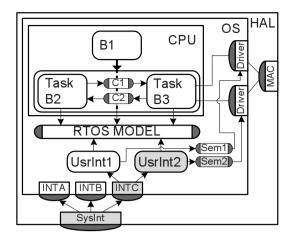

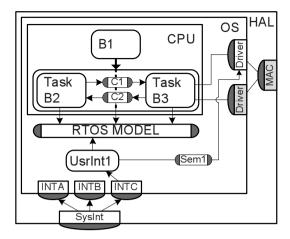

| 5.7  | Multi-task example model                                      | 175 |

| 5.8  | Software execution stack for interrupt-based multi-tasking    | 177 |

| xxii | List of Figures |

|------|-----------------|

| AAII | Lisi of Figures |

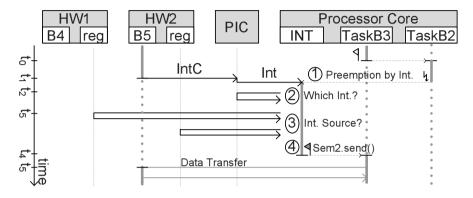

| 5.9  | Interrupt-based multi-tasking example                      | 178 |

|------|------------------------------------------------------------|-----|

| 5.10 | Internal communication                                     | 181 |

| 5.11 | External communication                                     | 183 |

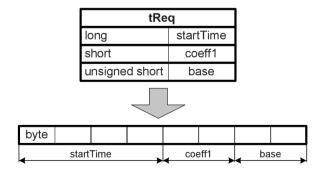

| 5.12 | Marshalling example                                        | 184 |

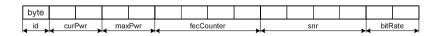

| 5.13 | Packetization                                              | 185 |

| 5.14 | Chain for interrupt-based synchronization                  | 187 |

| 5.15 | Events in interrupt-based synchronization                  | 188 |

| 5.16 | Polling-based synchronization                              | 190 |

| 5.17 | Events in polling-based synchronization                    | 190 |

| 5.18 | Transferring a packet using bus primitives                 | 191 |

| 5.19 | Binary image generation                                    | 195 |

| 5.20 | ISS-based Virtual platform                                 | 196 |

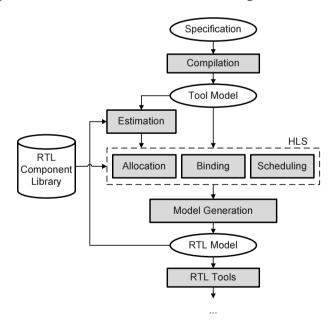

| 6.1  | HW synthesis design flow                                   | 199 |

| 6.2  | High-level block diagram                                   | 201 |

| 6.3  | RTL diagram with FSM controller                            | 202 |

| 6.4  | RTL diagram with programmable controller                   | 203 |

| 6.5  | CDFG for Ones counter                                      | 206 |

| 6.6  | FSMD specification                                         | 207 |

| 6.7  | RTL Specification                                          | 208 |

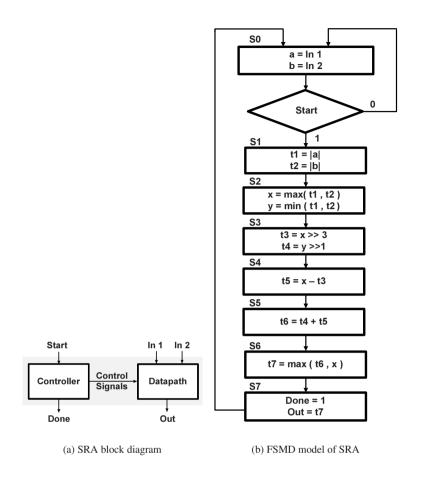

| 6.8  | Square-root algorithm (SRA)                                | 212 |

| 6.9  | Gain in register sharing                                   | 217 |

| 6.10 | General partitioning algorithm                             | 218 |

| 6.11 | Variable merging for SRA example                           | 219 |

| 6.12 | SRA datapath with register sharing                         | 220 |

| 6.13 | Gain in functional unit sharing                            | 221 |

| 6.14 | Functional unit merging for SRA                            | 222 |

| 6.15 | SRA design after register and unit merging                 | 224 |

| 6.16 | SRA Datapath with labeled connections                      | 225 |

| 6.17 | Connection merging for SRA                                 | 227 |

| 6.18 | SRA Datapath after connection merging                      | 227 |

| 6.19 | Register merging                                           | 228 |

| 6.20 | Datapath schematic after register merging                  | 229 |

| 6.21 | Modified FSMD models for SRA algorithm                     | 230 |

| 6.22 | Datapath with chained functional units                     | 231 |

| 6.23 | SRA datapath with chained and multi-cycle functional units | 232 |

| 6.24 | Functional unit pipelining                                 | 234 |

| Lis | st of Fig | gures                                                           | xxiii |

|-----|-----------|-----------------------------------------------------------------|-------|

|     | 6.25      | Datapath pipelining                                             | 236   |

|     | 6.26      | Control and datapath pipelining                                 | 239   |

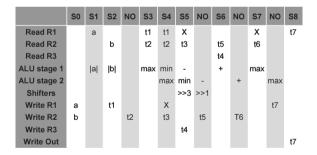

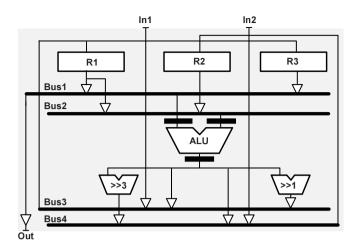

|     | 6.27      | C and CDFG                                                      | 241   |

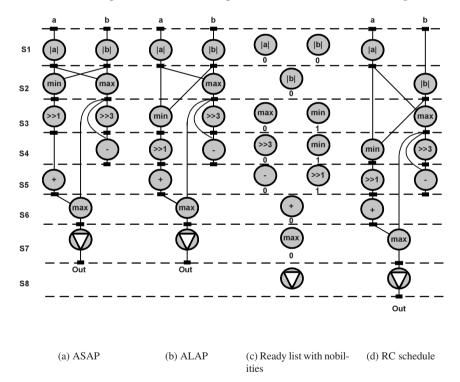

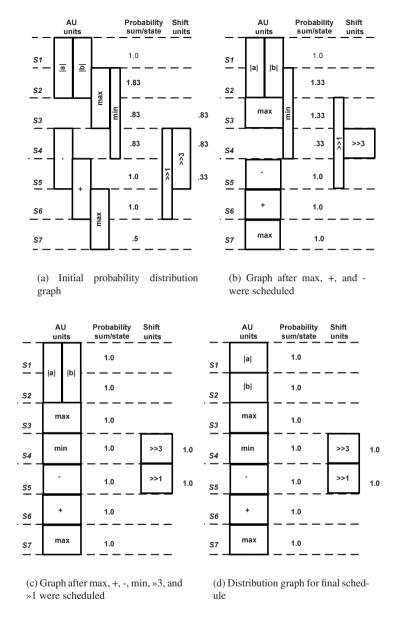

|     | 6.28      | ASAP, ALAP, and RC schedules for SRA                            | 243   |

|     | 6.29      | RC algorithm                                                    | 245   |

|     | 6.30      | TC algorithm                                                    | 245   |

|     | 6.31      | ASAP, ALAP, and RC schedules for SRA                            | 246   |

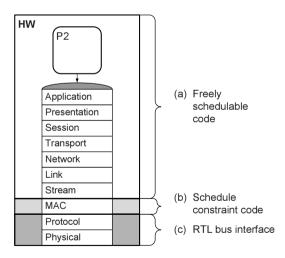

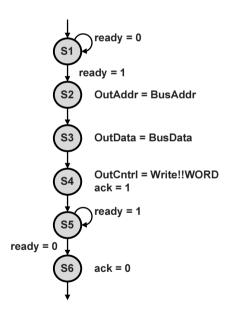

|     | 6.32      | Distribution graphs for TC scheduling of the SRA example        | 247   |

|     | 6.33      | HW Synthesis timing constraints                                 | 249   |

|     | 6.34      | FSMD for MAC driver                                             | 250   |

|     | 6.35      | Custom HW component with bus interface                          | 251   |

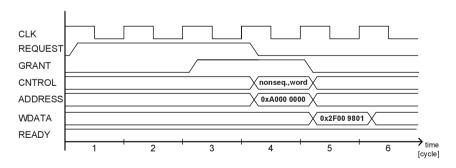

|     | 6.36      | A typical bus protocol                                          | 252   |

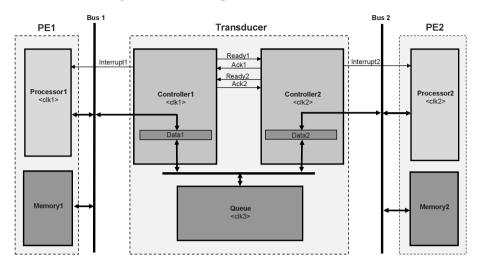

|     | 6.37      | Transducer structure                                            | 253   |

|     | 7.1       | A typical simulation environment                                | 257   |

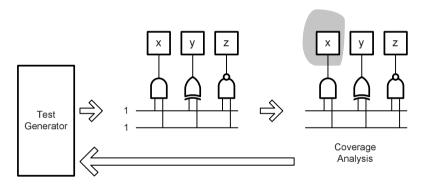

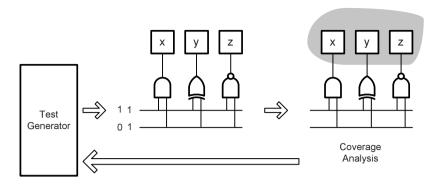

|     | 7.2       | A test case that covers only part of the design.                | 261   |

|     | 7.3       | Coverage analysis results in a more useful test case.           | 262   |

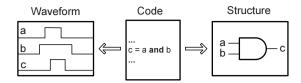

|     | 7.4       | Graphical visualization of the design helps debugging.          | 263   |

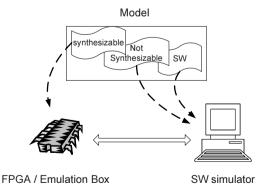

|     | 7.5       | A typical emulation setup.                                      | 263   |

|     | 7.6       | Logic equivalence checking by matching of cones.                | 266   |

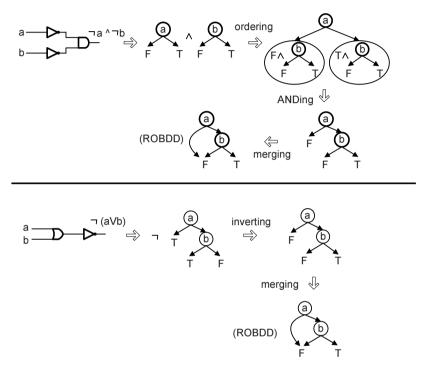

|     | 7.7       | DeMorgan's law illustrated by ROBDD equivalence.                | 267   |

|     | 7.8       | Equivalence checking of sequential design using product FSMs.   | 269   |

|     | 7.9       | Product FSM for with a reachable error state.                   | 270   |

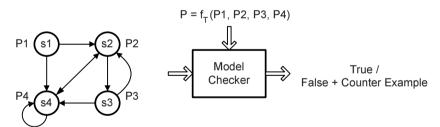

|     | 7.10      | A typical model checking scenario.                              | 270   |

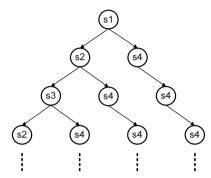

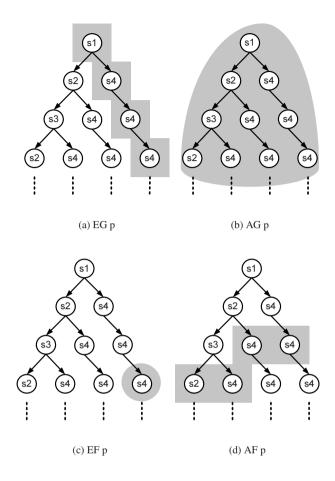

|     | 7.11      | A computation tree derived from a state transition diagram.     | 271   |

|     | 7.12      | Various temporal properties shown on the computation tree.      | 272   |

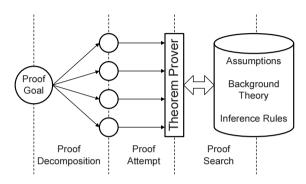

|     | 7.13      | Proof generation process using a theorem prover.                | 273   |

|     | 7.14      | Associativity of parallel behavior composition.                 | 273   |

|     | 7.15      | Basic laws for a theory of system models.                       | 274   |

|     | 7.16      | Symbolic simulation of Boolean circuits.                        | 277   |

|     | 7.17      | System level models.                                            | 279   |

|     | 7.18      | A simple hierarchical specification model.                      | 280   |

|     | 7.19      | Behavior partitioning and the equivalence of models.            | 280   |

|     | 7.20      | Equivalence of models resulting from channel mapping.           | 281   |

|     | 7.21      | Model refinement using functionality preserving transformations | 3284  |

|     | 8.1       | Metropolis framework                                            | 289   |

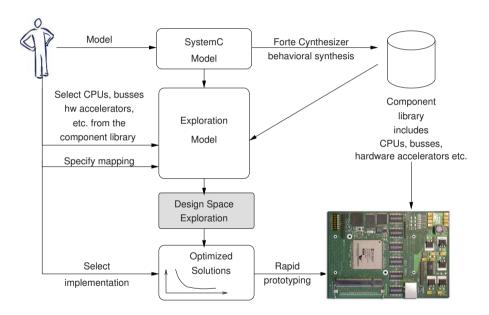

|     | 8.2       | SystemCoDesigner tool flow                                      | 290   |

| xxiv | List of Figures |

|------|-----------------|

| ΑΛΙΥ | List of rigures |

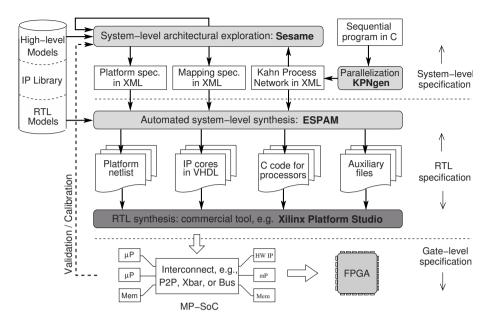

| 8.3  | Daedalus tool flow                                        | 292 |

|------|-----------------------------------------------------------|-----|

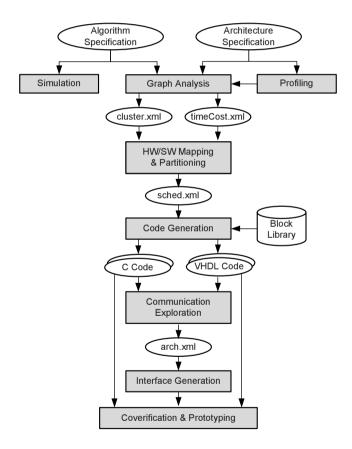

| 8.4  | PeaCE tool flow                                           | 293 |

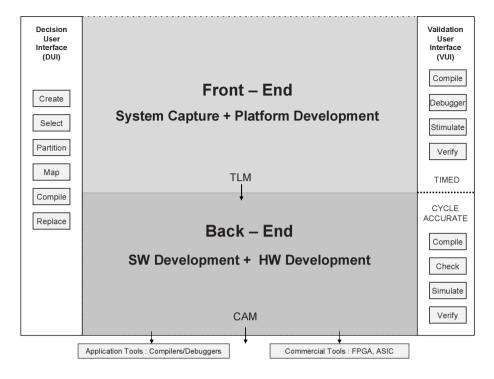

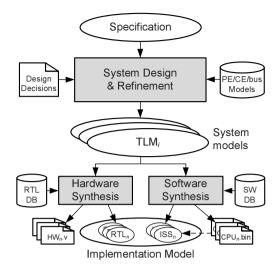

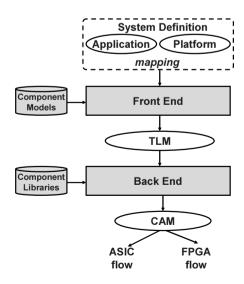

| 8.5  | SCE tool flow                                             | 295 |

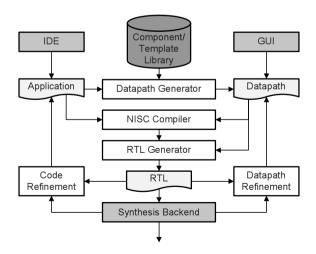

| 8.6  | NISC technology tools                                     | 310 |

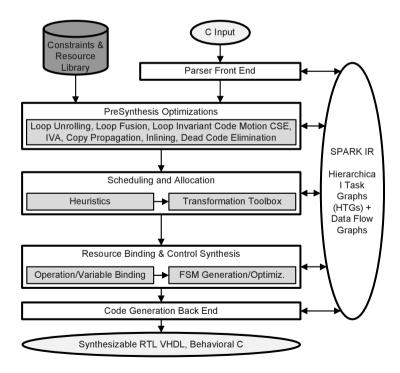

| 8.7  | The SPARK Synthesis Methodology                           | 311 |

| 8.8  | xPilot Synthesis System                                   | 313 |

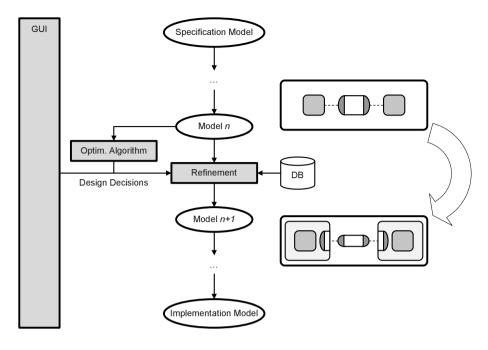

| 8.9  | ESE tool flow                                             | 320 |

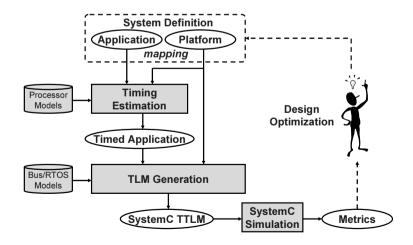

| 8.10 | System level design with ESE front end                    | 321 |

| 8.11 | SW-HW synthesis with ESE back end                         | 323 |

| 8.12 | MP3 decoder application model                             | 324 |

| 8.13 | MP3 decoder platform SW+4                                 | 326 |

| 8.14 | Execution speed and accuracy trade-offs for embedded sys- |     |

|      | tem models                                                | 328 |

| 8.15 | MP3 manual design quality                                 | 329 |

| 8.16 | Automatically generated MP3 design quality                | 330 |

| 8.17 | Development productivity gains from model automation      | 331 |

| 8.18 | Validation productivity gain from using TLM vs. CAM       | 332 |

## **List of Tables**

| 3.1 | Processor models                                | 82  |

|-----|-------------------------------------------------|-----|

| 3.2 | Communication layers                            | 84  |

| 4.1 | A sample capacity table of platform components. | 147 |

| 6.1 | Input logic table                               | 209 |

| 6.2 | Output logic table                              | 209 |

| 6.3 | Variable usage                                  | 213 |

| 6.4 | Operation usage                                 | 214 |

| 6.5 | SRA connectivity                                | 215 |

| 6.6 | Connection usage table                          | 226 |

| 7.1 | A comparison of various verification schemes.   | 278 |

## Chapter 1

## INTRODUCTION

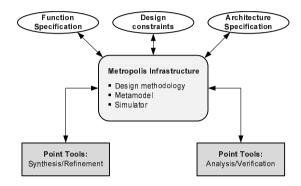

In this chapter we will look at the emergence of system design theory, practice and tools. We will first look into the needs of system-level design and the driving force behind its emergence: increase in design complexity and widening of productivity gap. In order to find an answer to these challenges and find a systematic approach for system design, we must first define design-abstraction levels; this will allow us to talk about design-flow needs on processor and systems levels of abstraction. An efficient design-flow will employ clear and clean semantics in its languages and modeling, which is also, required by synthesis and verification tools. We will then analyze the system-level design flow and define necessary models, define each model separately and its use in the system design flow. We will also discuss the components and tools necessary for system design. We will finish with prediction on future directions in system design and the prospects for system design practice and tools.

## 1.1 SYSTEM-DESIGN CHALLENGES

Driven by ever-increasing market demands for new applications and by technological advances that allow designers to put complete many-processor systems on a single chip (MPSoCs), system complexities are growing at an almost exponential rate. Together with the challenges inherent in the embedded-system design process with its very tight constraints and market pressures, not the least of which is reliability, we are finding that traditional design methods, in which systems are designed directly at the low hardware or software levels, are fast becoming infeasible. This leads us to the well-known productivity gap generated by the disparity between the rapid paces at which design complexity has increased in comparison to that of design productivity [99].

One of the commonly-accepted solutions for closing the productivity gap as proposed by all major semiconductor roadmaps is to raise the level of abstraction in the design process. In order to achieve the acceptable productivity gains and to bridge the semantic gap between higher abstraction levels and low-level implementations, the goal now is to automate the system-design process as much as possible. We must apply design-automation techniques for modeling, simulation, synthesis, and verification to the system-design process. However, automation is not easy if a system-abstraction level is not well-defined, if components on any particular abstraction level are not well-known, if system-design languages do not have clear semantics, or if the design rules and modeling styles are not clear and simple. In the following chapters, we will show how to answer for those challenges through sound system-design theories, practices, and tools.

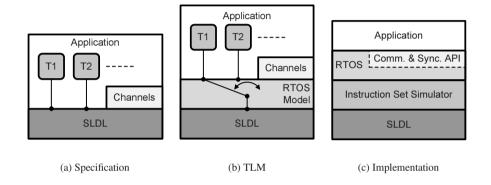

On the modeling and simulation side, several approaches exist for the virtual prototyping of complete systems. These approaches are typically based on some variant of C-based description, such as C-based System-Level Design Languages (SLDLs) like SystemC [150] or SpecC [171]. These virtual prototypes can be assembled at various levels of detail and abstraction.

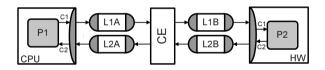

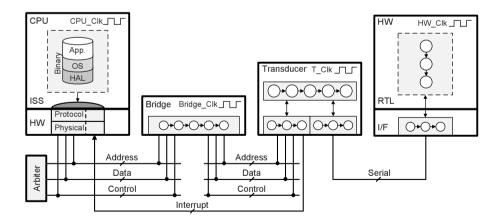

The most common approach in the system design of a many-processor platform is to perform co-simulation of software (SW) and hardware (HW) components. Both standard and application-specific processors are simulated on nstruction-set level with an Instruction Set Simulator (ISS). The custom HW components or Intellectual Property (IP) components are modeled with a timed functional model and integrated together with the processor models into a Transaction-Level Model (TLM) representing the platform communication between components.

In algorithmic-level approaches in designing MPSoCs, we use domainspecific application modeling, which is based on more formalized models of computation, such as process networks or process state machines. These modeling approaches are often supported by graphical capture of models in terms of block diagrams, which hide the details of any underlying internal language. On the other hand, the code can be generated in a specific target language such as C by model-based-design tools from such graphical input.

Such simulation-centric approaches enable the horizontal integration of various components in different application domains. However, approaches for the vertical integration for system synthesis and verification across component or domain boundaries are limited. At best, there are some solutions for the C-based synthesis of single custom hardware units. But no commercial solutions for synthesis and verification at the system level, across hardware and software boundaries, currently exist.

In order to understand system-level possibilities more fully, however, we must step back and explain the different abstraction levels involved in system design.

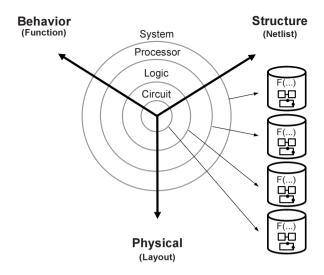

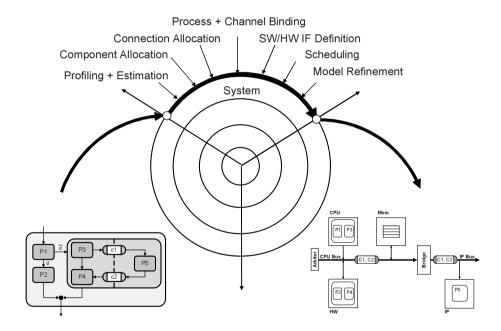

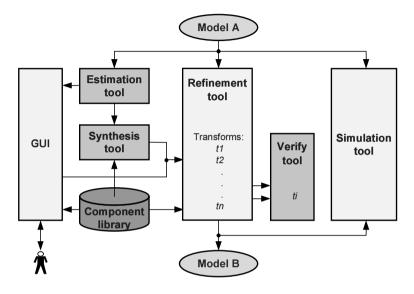

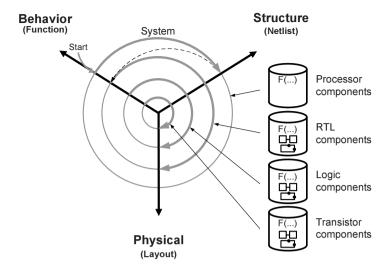

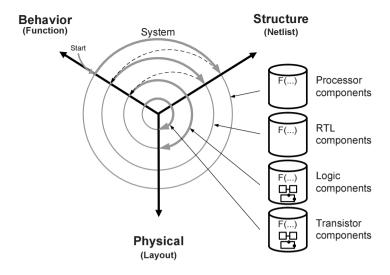

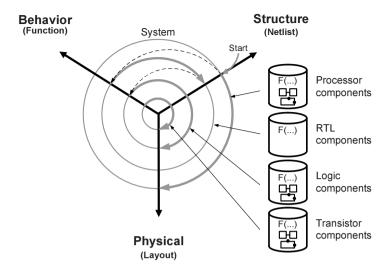

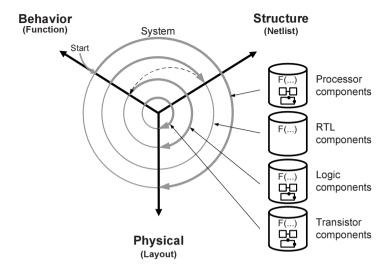

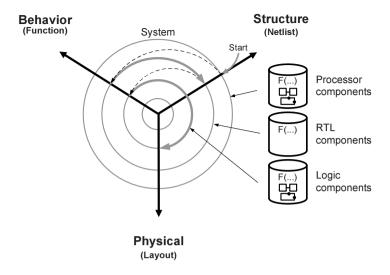

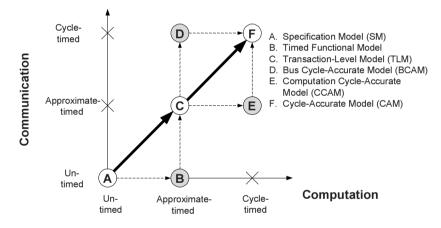

FIGURE 1.1 Y-Chart

## 1.2 ABSTRACTION LEVELS

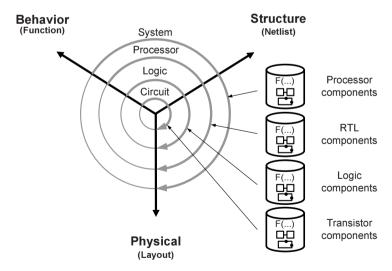

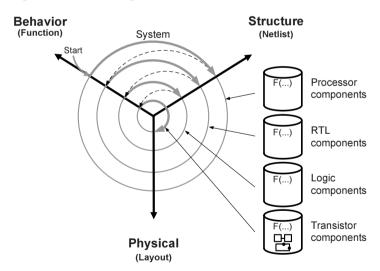

The growing capabilities of silicon technology over the previous decades has forced design methodologies and tools to move to higher levels of abstraction. In order to explain the relationship between different design methodologies on different abstraction levels, we will use the Y-Chart, which was developed in 1983 in order to explain differences between different design tools and different design methodologies in which these tools were used [60].

#### 1.2.1 Y-CHART

The Y-Chart makes the assumption that each design, no matter how complex, can be modeled in three basic ways, which emphasize different properties of the same design. As shown in Figure 1.1, the Y-Chart has three axes representing three aspects of every design: behavior (sometimes called functionality or specification), design structure (also called netlist or a block diagram), and physical design (usually called layout or board design). Behavior represents a design as a black box and describes its outputs in terms of its inputs over time. The black-box behavior does not indicate in any way how to build the black box or what its structure is. That is given on the structure axis, where the black box is represented as a set of components and connections. Naturally, the behavior of the black box can be derived from its component behaviors and their connectivity. However, such a derived behavior may be difficult to understand since it is obscured by the details of each component and connection. Physical

design adds dimensionality to the structure. It specifies the size (height and width) of each component, the position of each component, as well as each port and connection on the silicon chip, printed circuit board, or any other container.

The Y-Chart can also represent design on different abstraction levels, which are identified by concentric circles around the origin. Typically, four levels are used: circuit, logic, processor, and system levels. The name of each abstraction level is derived from the types of the components generated on that abstraction level. Thus the components generated on the circuit level are standard cells which consist of N-type or P-type transistors, while on the logic level we use logic gates and flip-flops to generate register-transfer components. These are represented by storage components such as registers and register files and by functional units such as ALUs and multipliers. On the processor level, we generate standard and custom processors, or special-hardware components such as memory controllers, arbiters, bridges, routers, and various interface components. On the system level, we design standard or embedded systems consisting of processors, memories, buses, and other processor components.

On each abstraction level, we also need a database of components to be used in building the structure for a given behavior. This process of converting the given behavior into a structure on each abstraction level is called synthesis. Once a structure is defined and verified, we can proceed to the next lower abstraction level by further synthesizing each of the components in the structure. On the other hand, if each component in the database is given with its structure and physical dimensions, we can proceed with physical design, which consists of floorplanning, placement, and routing on the chip or PC board. Thus each component in the database may have up to three different models representing three different axes in the Y-Chart: behavior or function; structure, which contains the components from the lower level of abstraction; and the physical layout of its structure.

Fortunately, all three models for each component are not typically needed most of the time. Most of the methodologies presently in use perform design or synthesis on the system and processor levels, where every system component except standard processors and memories is synthesized to the logic level, before the physical design is performed on the logic level. Therefore, for the top three abstraction levels, we only need a functional model of each component with estimates of the key metrics such as performance, delay, power, cost, size, reliability, testability, etc. Once the design is represented in terms of logic gates and flip-flops, we can use standard cells for each logic component and perform layout placement and routing. On the other hand, some components on the processor-and-system levels may be obtained as IPs and not synthesized. Therefore, their structure and physical design are known, at least partially, on the level higher than logic level. In that case, the physical design then may contain components of different sizes and from different levels of abstraction.

In order to introduce system-level design methodologies we must look first at the design process on each of processor and system abstraction levels.

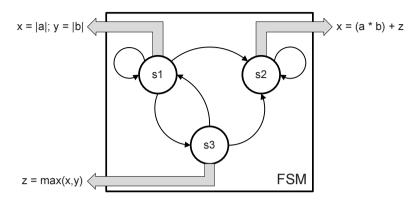

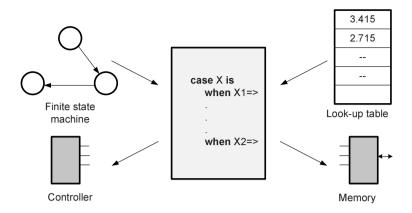

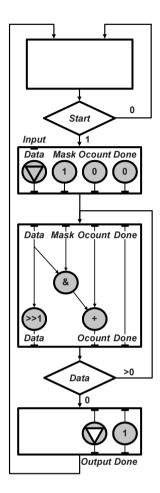

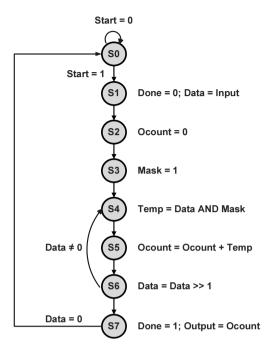

FIGURE 1.2 FSMD model

#### 1.2.2 PROCESSOR-LEVEL BEHAVIORAL MODEL

We design components of different granularity on each abstraction level. On the processor level, we define and design computational components or processing elements (PEs). Each PE can be a dedicated or custom component that computes some specific functions, or it can be a general or standard PE that can compute any function specified in some standard programming language. The functionality or behavior of each PE can be specified in several different ways.

In the early days of computers, their functionality was specified with mathematical expressions or formulas. The functionality of a PE can be also specified with an algorithm in some programming language, or with a flow chart in graphical form. Some simple control functionality, such as controllers or component interfaces, can be specified using the dominant model of computer science, called a Finite State Machine (FSM). A FSM is defined with a set of states and a set of transitions from state to state, which are taken when some input variables reach the required value. Furthermore, each FSM generates some values for output variables in each state or during each transition. A FSM model can be made clock-accurate if each state is considered to take one clock cycle. In general, a FSM model is useful for computations requiring several hundred states at most.

The original FSM model uses binary variables for inputs and outputs. This FSM model can be extended using standard integer or floating-point variables and computing their values in each state or during each transition by a set of arithmetic expressions or programming statements. This way we can extend

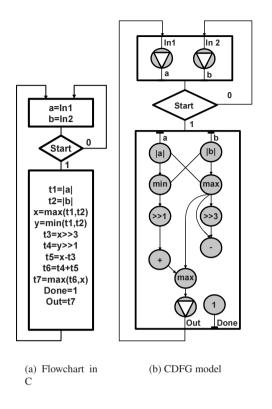

the FSM model to the model of a Finite State Machine with Data (FSMD) [61]. For example, Figure 1.2 shows a FSMD with three states, SI, S2, and S3, and with arcs representing state changes under different inputs. Each state executes a computation represented by one or more arithmetic expressions or programming statements. For example, in state S1, the FSMD in Figure 1.2 computes two functions, x = |a| and y = |b|, and in state S3 it computes the function z = max(x, y). A FSMD model is usually not clock-accurate since computation in each state may take more than one clock cycle.

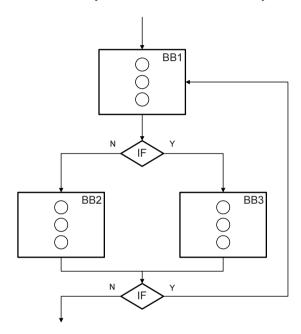

FIGURE 1.3 CDFG model

As mentioned above, a FSMD model is not adequate to represent the computation expressed by standard programming languages such as C. In general, programming languages consist of if statements, loops, and expressions. An if statement has two parts, then and else, in which then is executed if the conditional expression given in the if statement is true, otherwise the else part is executed. In each of the then or else parts, the if statement computes a set of expressions called a Basic Block (BB). The if statement can also be used in the loop construct to represent loop iterations, which are executed as long as the condition in the if statement is true. Therefore, any programming-language code can be represented by a Control-Data Flow Graph (CDFG) consisting of if diamonds, which represent if conditions, and BB blocks, which represent computation [151]. Figure 1.3 shows such a CDFG, this one representing a loop with an if statement inside the loop iteration. In each iteration, the loop con-

struct executes BB1 and BB2 or BB3 depending on the value of the if statement. At the end, the loop is exited if all iterations are executed.

A CDFG shows explicitly the control dependencies between loop statements, if statements, and BBs, as well as the data dependences among operations inside a BB. It can be converted to a FSMD by assigning a state to each BB and one state for the computation of each if conditional. Note that each state in such a FSMD may need several clock cycles to execute its assigned BB or if condition. Therefore, a CDFG can be considered to be a FSMD with superstates, which require multiple clock cycles to execute.

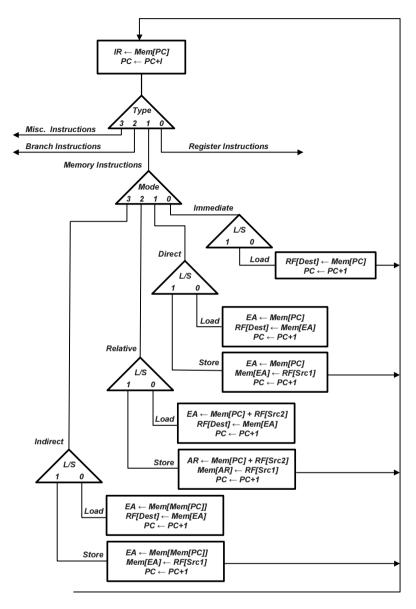

A standard or custom PE can be also described with an Instruction Set (IS) flow chart that describes the fetch, decode, and execute stages of each instruction. A partial IS flow chart is given in Figure 1.4. The fetch stage consists of fetching the new instruction into the Instruction Register (IR)  $(IR \leftarrow Mem[PC])$  and incrementing the Program Counter  $(PC \leftarrow PC + 1)$ . In the decode stage, we decode the type and mode of the fetched instruction. In Figure 1.4, there are four types of instructions: register, memory, branch, and miscellaneous instructions. In the case of memory instructions, there are four modes: immediate, direct, relative, and indirect. Each mode contains load and store instructions. Each instruction execution is in turn described by a BB, which may take several clock cycles to execute, depending on the processor implementation structure. For example, the memory-store instruction with indirect addressing computes an Effective Address (EA) by fetching the next instruction pointed to by the PC and uses it to fetch the address of the memory location in which the data will be stored  $(EA \leftarrow Mem[Mem[PC]])$ . Then it stores the data from the Register File (RF) indicated by the Src1 part of the instruction (RF[Src1]) into the memory at location EA  $(Mem[EA] \leftarrow RF[Src1])$ . Finally, it increments the PC  $(PC \leftarrow PC + 1)$  and goes to the fetch phase.

The above-described IS flow chart can be converted to a FSMD, where each of the fetch, decode, and execute stages may need one or more states or clock cycles to execute.

In addition to FSMD, CDFG, and IS flow-chart models, other representations can be used to specify the behavior of a PE. They provide differing types of the information needed for the synthesis of PEs. The guideline for choosing one over the other is that more detailed information makes PE synthesis easier.

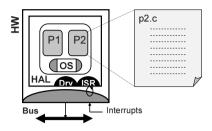

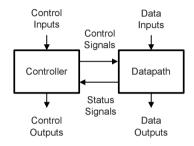

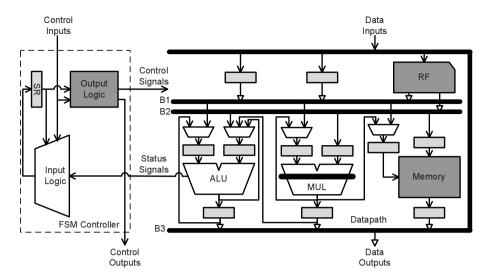

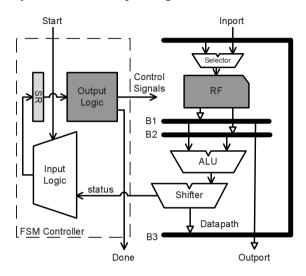

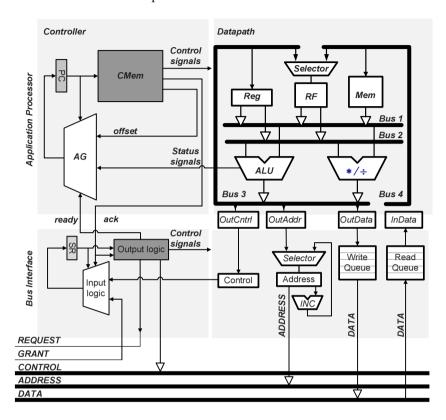

## 1.2.3 PROCESSOR-LEVEL STRUCTURAL MODEL

A processor's behavioral model, whether defined by a program in C, CDFG, FSMD, or by an IS, can be implemented with a set of register-transfer components; such a structural model usually consists of a controller and a datapath. A datapath consists of a set of storage elements (such as registers, register files, and memories), a set of functional units (such as ALUs, multipliers, shifters, and

FIGURE 1.4 Instruction-set flow chart

other custom functional units), and a set of busses. All of these register-transfer components may be allocated in different quantities and types and connected arbitrarily through busses or a network-on-chip (NOC). Each component may take one or more clock cycles to execute, each component may be pipelined, and each component may have input or output latches or registers. In addition,

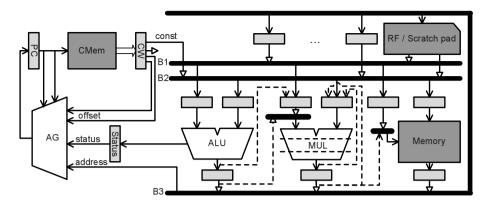

FIGURE 1.5 Processor structural model

the entire datapath can be pipelined in several stages in addition to components being pipelined by themselves. The choice of components and datapath structure depends on the metrics to be optimized for particular implementation.

An example of such a datapath is shown in Figure 1.5. It consists of a set of registers and a Register file (RF) or a Scratchpad memory. These storage elements are connected to the functional units ALU and MUL, and to a Memory by three busses, B1, B2, and B3. Each of these units has input and output registers. An ALU can execute an arithmetic or logic operation in one clock cycle from its input to its output register, while a two-stage pipelined multiplier MUL needs three clock cycles from its input to its output register. On the other hand. Memory is not pipelined and requires two clock cycles from its address register to the output data register. In addition to pipelined functional units such as the MUL, the whole datapath itself is pipelined. In such pipelined datapath each operation may take several clock cycles to execute. For example, it takes three clock cycles from the RF through the ALU input register, the ALU output register, and back to the RF. On the other hand, it takes five clock cycles through the MUL, since the MUL is pipelined itself. In order to speed up the execution for complex expressions such as a(b+c), the datapath allows (b+c) to be sent directly to the MUL through a data-forwarding path without going back to RF. In Figure 1.5, such a path is shown going from the ALU output into the left input register of the MUL. At the same time, this path can also be implemented by a connection from the ALU output register to the left MUL input. In this case, we need a short bus, usually implemented with a selector, to select the ALU output register or the MUL input register as the left inputs to the MUL. A similar selector is also shown for the Memory-address input, which may come from the address register or the MUL output register.

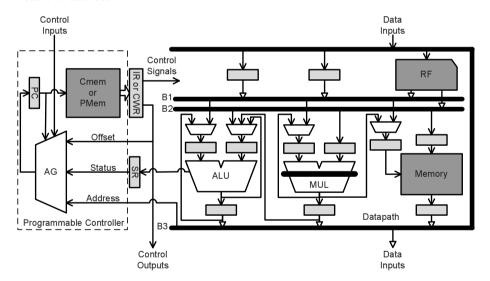

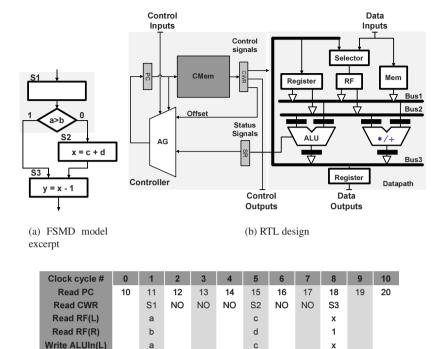

The controller defines the state of the processor clock cycle per clock cycle and issues the control signals for the datapath accordingly. The structure of the

controller and its implementation depends on whether the processor is a standard processor (such as Xeon, ARM, or a DSP) or a custom-design processor or Intellectual Property (IP) function specifically synthesized for a particular application and platform. In the case of a standard processor, the controller is programmable with a program counter (PC), program memory (PMem), and an address generator (AG) that defines the next address to be loaded into the PC. On each clock cycle, an instruction is fetched from the program memory at the address specified by the PC, loaded into an instruction register (IR), decoded, and then the decoded control signals are applied to the datapath for instruction execution. The results of the conditional evaluation, called status signals, are applied to the AG for selection of the next instruction. Like the datapath, the controller can be pipelined by introducing a status register and pipelining instructions from the PC to the IR, through the Datapath and status register and then back to the PC.

In the case of specific IPs or IF components, the controller could be implemented with hardwired logic gates. In terms of digital-design terminology, the PC is then called a State register, the program memory is called output logic, and the AG is called next-state logic.

In the case of specific custom processors, the controller can be implemented with programmability concepts typical of standard processors, and control signal generation of IP implementations. This is shown in Figure 1.5, in which program memory is replaced with control memory (CMem) and instruction register with control word register (CW). CMem stores decoded control words instead of instructions. Figure 1.5 also illustrates how the whole processor is pipelined, including the control and datapath pipelining. On each clock cycle, one control word is fetched from CMem and stored in the CW register. Then the data in the RF are forwarded to a functional unit input register in the next clock cycle, and after one or more clock cycles, the result is stored in the output register and/or in the status register. Finally, in the next clock cycle, the value in the status register is used to select the new address for the PC, while the result from the output register is stored back into the RF or forwarded to another input register.

Selecting components and the structure of a PE and defining register-transfer operations performed in each clock cycle is the task of processor-level synthesis.

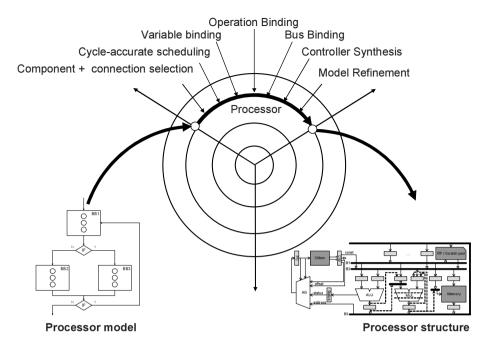

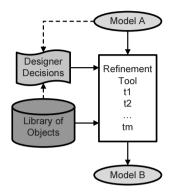

## 1.2.4 PROCESSOR-LEVEL SYNTHESIS

Synthesis of standard processors starts with the instruction set (IS) of the processor. In order to achieve the highest processor performance this process is done manually since standard processors try to achieve the highest performance and minimal power consumption at minimal cost. The second reason for synthesizing processors manually is to minimize the design size and therefore

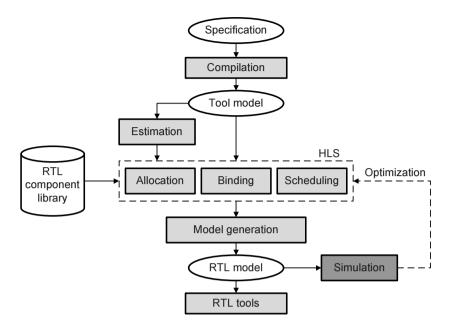

FIGURE 1.6 Processor synthesis

fabrication cost for high-volume production. In contrast, the design or synthesis of a custom processor or a custom IP starts with the C code of an algorithm, which is usually converted to the corresponding CDFG or FSMD model before synthesis and ends up with a custom processor containing the number and type of components connected as required by the given behavioral model. This generation is usually called high-level synthesis or register-transfer synthesis or occasionally just processor synthesis. It consists of five individual tasks.

(a) Allocation of components and connections. In processor synthesis, the components are selected from the register-transfer library. It is important to select at least one component for each operation in the behavioral model. Also, it may be necessary to select components that implement some frequently-used functions in the behavioral model. The library must also include a component's characteristics and its metrics, which will be used by the other synthesis tasks. The connectivity among components can be added after binding and scheduling tasks; that way we end up with minimal connectivity. However, we do not know the exact connectivity delays during binding and scheduling. Therefore, it is convenient to also add connections, buses, or a network on a chip, which will allow us to estimate more precisely all the delays.

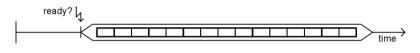

(b) **Cycle-accurate scheduling.** All operations required in the behavioral model must be scheduled into cycles. In other words, for each operation, such as a = b op c, the variables b and c must be read from their storage components and brought to the input of a functional unit that can execute operation op, and after operation op is executed in the functional unit the result must be brought to its storage destination. Furthermore, each BB in the given behavioral model may be scheduled into several clock cycles where some of the operations can even be scheduled in the same clock cycle if the datapath structure allows such parallelism. Note that each operation by itself may take several clock cycles in a pipelined datapath.

- (c) **Binding of variables, operations and transfers**. Each variable must be bound to a storage unit. In addition, several variables with non-overlapping life-times can be bound to the same storage units to save on storage cost. Operations in the behavioral model must be bound to one of the functional units capable of executing this operation. If there are several units with such capability, the binding algorithm must optimize the selection. Storage and functional unit binding also depends on connectivity binding, since for every variable and every operation in each clock cycle there must be a connection between the storage component and the functional unit and back to a storage component to which variables and operation are bound.

- (d) **Synthesis of controller**. The controller can be programmable with a readwrite program memory or just a read-only memory for fixed-functionality IPs. The controller can be also implemented with logic gates for small control functions. As mentioned earlier, the program memory can store instructions or just control words which may be longer then instructions but require no decoding.

- (e) **Model refinement.** A new processor model can be generated in several different styles with complete, partial, or no binding. For example, the statement a = b + c executing in state (n) can be written:

- (1) without any binding: a = b + c:

- (2) with storage binding of a to RF(1), b to RF(3), and c to RF(4): RF(1) = RF(3) + RF(4);

- (3) with storage and functional unit binding with + bound to ALU1: RF(1) = ALU1(+,RF(3),RF(4));

- (4) or with storage, functional unit, and connectivity binding:

Bus1 = RF(3); Bus2 = RF(4); Bus3 = ALU1

(+,Bus1,Bus2); RF(1) = Bus3;

A structural model can be also written as a netlist of register-transfer components, in which each component is defined by its behavior from the component library.

Tasks (a), (b), and (c) can be performed together or in any specific order, but they are interdependent. If they are performed together, the synthesis algorithm becomes very complex and unpredictable. One strategy is to perform allocation first, followed by binding and then scheduling. Another possibility is to do a complete allocation first, followed by storage binding, while combining unit and connectivity binding with scheduling.

Any of the above tasks can be performed manually or automatically. If they are all done automatically, we call the above process processor-level or highlevel synthesis. On the other hand, if (a) to (d) are performed manually and only (e) is done automatically, we call the process model refinement. Obviously, many other strategies are possible, as demonstrated by the number of designautomation tools available that perform some of the above tasks automatically and leave the rest for the designer to complete.

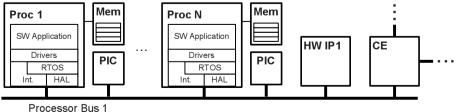

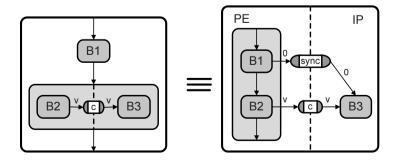

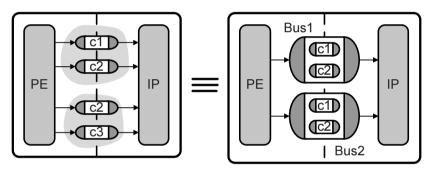

FIGURE 1.7 System behavioral model

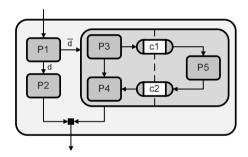

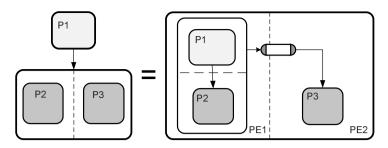

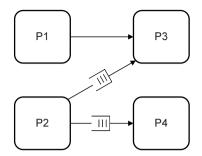

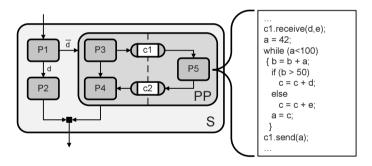

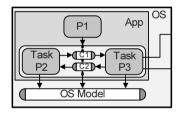

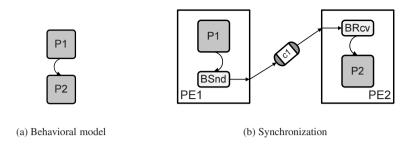

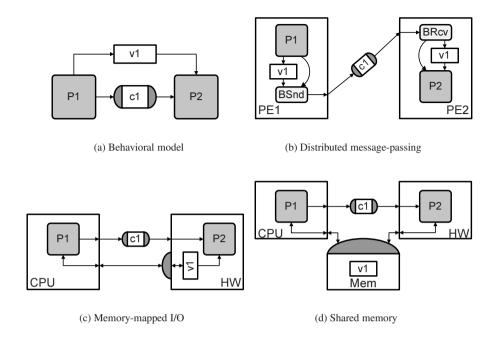

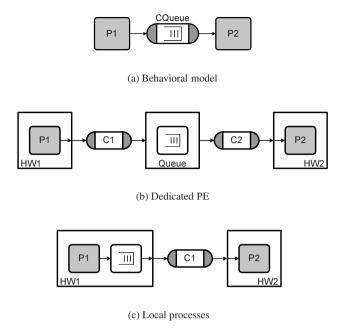

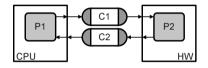

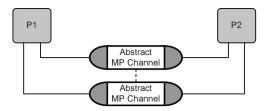

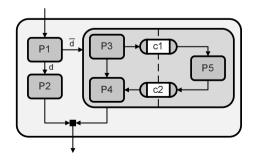

## 1.2.5 SYSTEM-LEVEL BEHAVIORAL MODEL

Processor-level behavioral models such as the CDFG can be used for specifying a single processor, but will not suffice for describing a complete system that consist of many communicating processors. A system-level model must represent multiple processes running in parallel in SW and HW. The easiest way to do this is to use a model which retains the concept of states and transitions as in a FSM but which extends the computation in each state to include processes or procedures written in a programming language such as C/C++. Furthermore, in order to represent a many-processor platform working in parallel or in pipelined mode, we must introduce concurrency and pipelining. Since processes in a system run concurrently, we need a synchronization mechanism for data exchange, such as the concept of a channel, to encapsulate data com-

munication. Also, we need a model which supports hierarchy, so as to allow designers to write complex system specifications without difficulty. Figure 1.7 illustrates such a model of hierarchical sequential-parallel processes, which is usually called a Process State Machine (PSM). This particular PSM is a system-level behavior or system specification, consisting of processes P1 to P5. The system starts with P1, which in turn triggers process P2 if condition d is true, or another process consisting of P3, P4, and P5 if condition d is not true. P3 and P4 run sequentially and in parallel with P5, as indicated by the vertical dashed line. When either P2 is finished or the sequential-parallel composition of P3, P4, and P5 is finished, the execution ends.

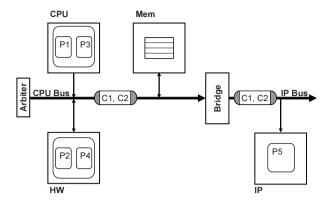

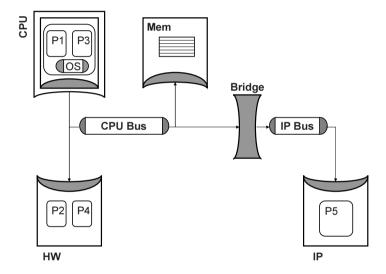

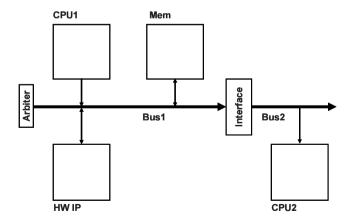

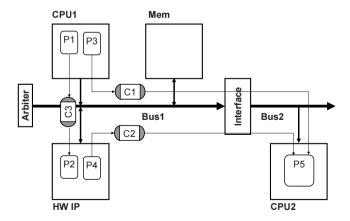

## 1.2.6 SYSTEM STRUCTURAL MODEL

A system-level structural model is a block diagram or a netlist of system components used for computation, storage, and communication. Processing Elements (PEs) can be standard processors or custom-made processors. They can also be application-specific processors or any other imported IPs or specialfunctions hardware components. Storage components are local or shared memories which may also be included in other processing components. Communication Elements (CE) are buses or routers possibly connected in a Networkon-Chip (NOC). If input-output protocols of some system component do not match, we will need to insert Interface Components (IF) such as transducers, bridges, arbiters, and interrupt controllers. Figure 1.8 shows a simple system platform consisting of a CPU processor with a local memory, an IP component, a specially-designed custom HW component (HW), and the shared memory (Mem). They are all connected through two buses, the CPU bus and IP bus. Since CPU and IP buses use different protocols, a special IF unit (Bridge) is included. The HW unit has the IF for the CPU bus protocol already built into it. Since the CPU bus has CPU and HW components competing for the bus, a special IF component (Arbiter) is added to grant bus access to one of the requesting components.

A system structural model is generated from the given behavioral model by the process called system synthesis.

## 1.2.7 SYSTEM SYNTHESIS

System synthesis starts with system-level behavioral model, such as the one shown in Figure 1.7, and generates the system structure, which consists of standard or custom PEs, CEs, and SW/HW IF components, as shown in Figure 1.8. Standard components, including their functionality and structure, can be found in the system-level component library, while custom components must be de-

FIGURE 1.8 System structural model

fined and synthesized on the processor level before they can be included in the library. According to the given definition, the behavioral model is a usually a composition of two objects: processes and channels. The structural model, on the other hand, uses different objects: processes are executed by PEs such as standard processors, custom processors, and IPs, and channels are implemented by buses or NoCs with well-defined protocols. The behavioral model can be converted into an optimized system platform by the following set of tasks, as shown in Figure 1.9:

- (a) Profiling and estimation. Synthesis starts by profiling the application code in each process and collecting statistics about types and frequency of operations, bus transfers, function calls, memory accesses, and about other statistics that are then used to estimate design metrics for the optimization of the platform or application code. These estimated metrics include performance, cost, bus traffic, power consumption, memory sizes, security, reliability, fault tolerance, among others;

- (b) Component and connection allocation. Next, components from the library of standard and custom processors, memories, IPs, and custom-functionality components must be allocated and connected with buses through bridges or routers. It is also possible to start with a completely defined platform, which is very useful for application and system software upgrades and product versioning;

- (c) Process and channel binding. Processes are assigned to PEs, variables to memories (local and global), and channels to busses. This requires an optimized partitioning of processes, variables, and connection traffic to minimize the platform-design metrics;

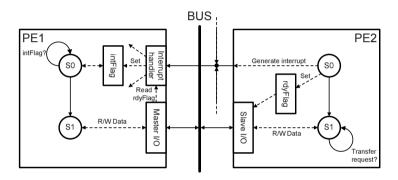

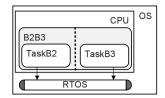

(d) **Process scheduling**. Parallel processes running on the same PE must be statically or dynamically scheduled. This requires generating a real-time operating system for dynamic scheduling;

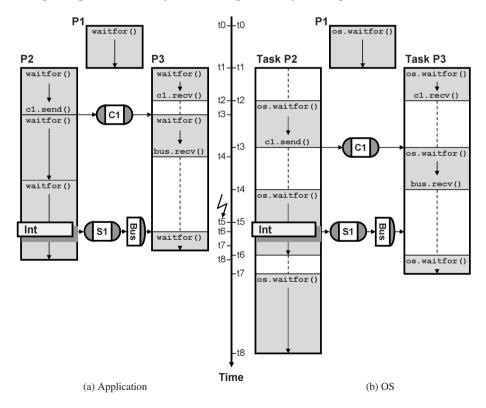

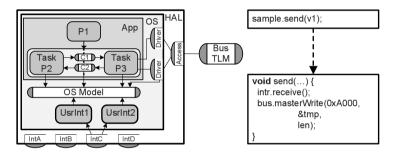

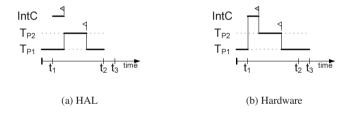

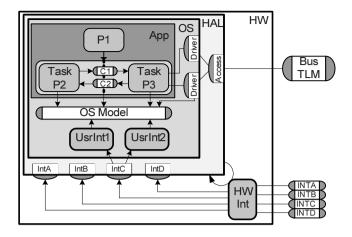

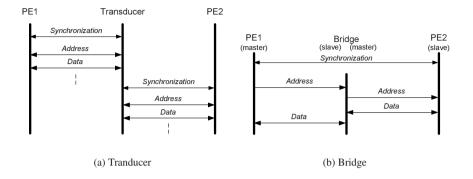

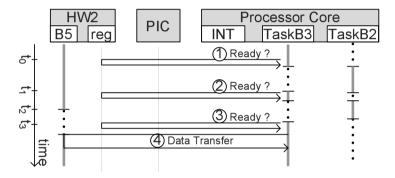

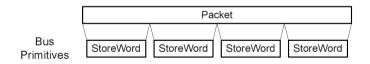

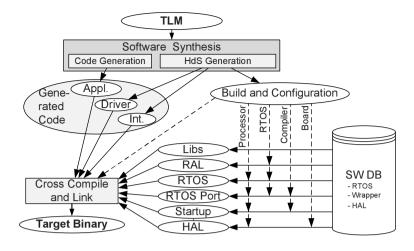

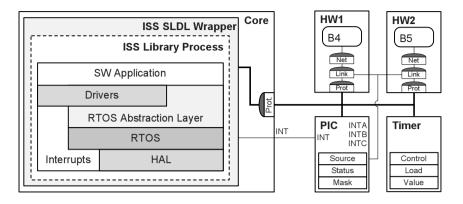

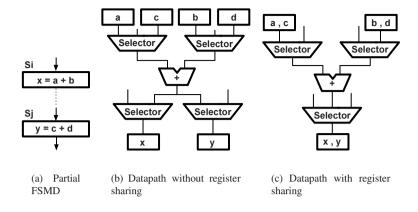

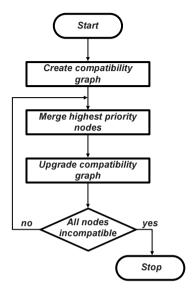

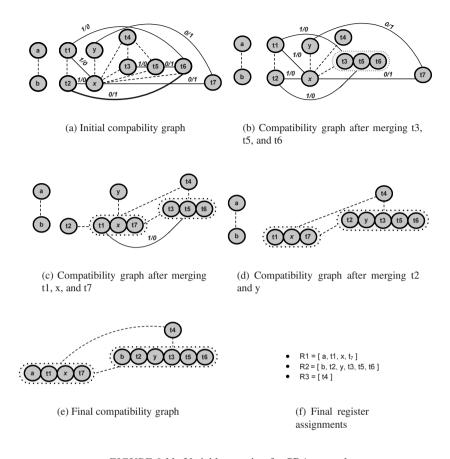

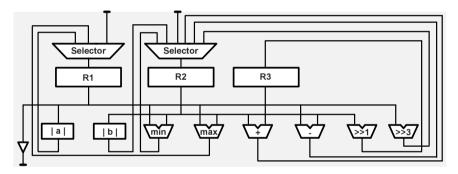

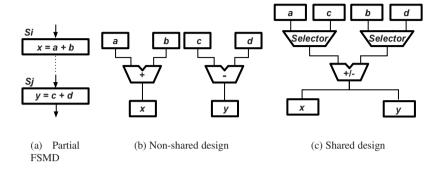

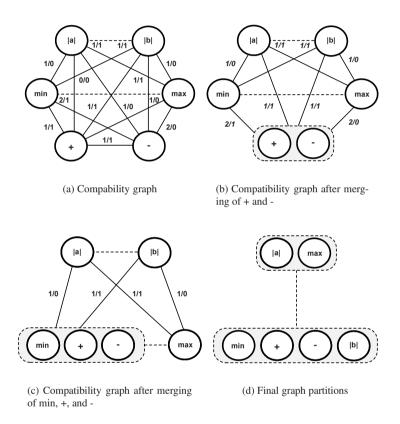

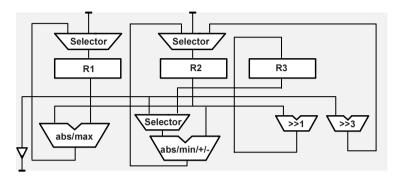

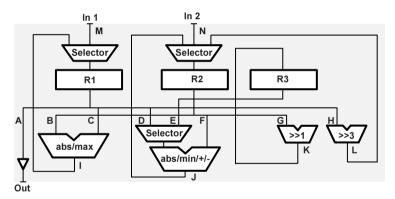

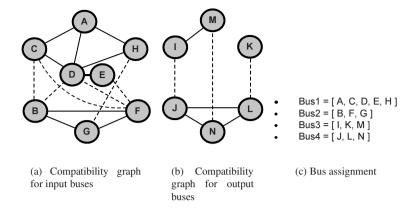

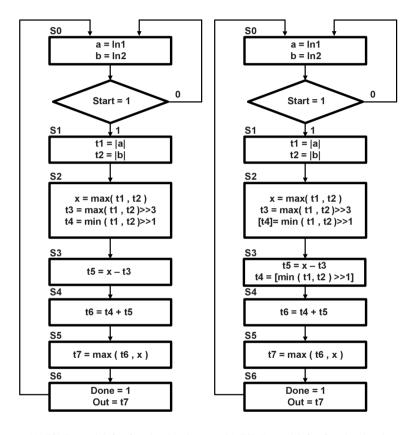

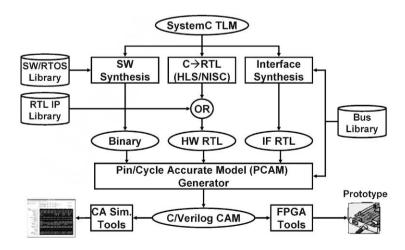

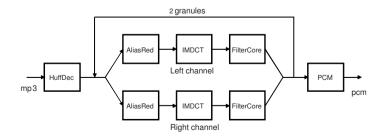

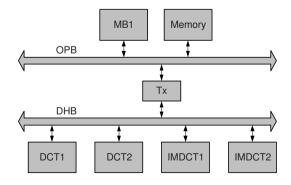

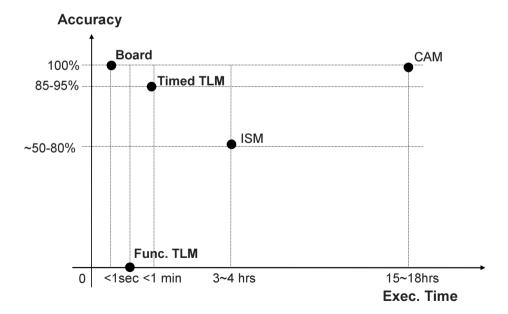

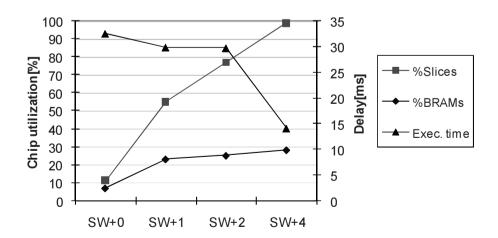

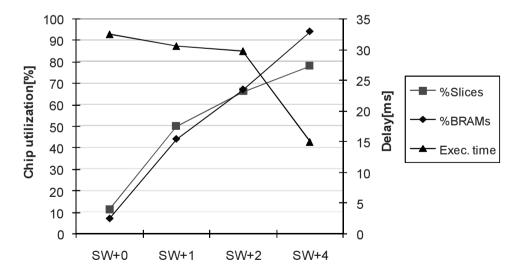

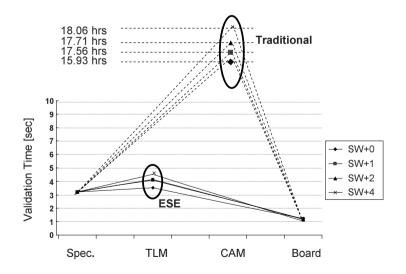

- (e) IF component insertion. Required IF components must be inserted into the platform from a library or synthesized on the processor level before being added to the library. Such additional SW IF components include system firmware components such as device drivers, routing, messaging and interrupt routines, and HW IF components to connect platform components with incompatible protocols and facilitate communication synchronization or message queuing. Examples of these HW IF components would include interrupt controllers and memory controllers.